Burr Brown Corporation DAC7611UB-2K5, DAC7611UB, DAC7611U-2K5, DAC7611U, DAC7611PB Datasheet

...

®

1

DAC7611

®

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111

Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

DAC7611

12-Bit Serial Input

DIGITAL-TO-ANALOG CONVERTER

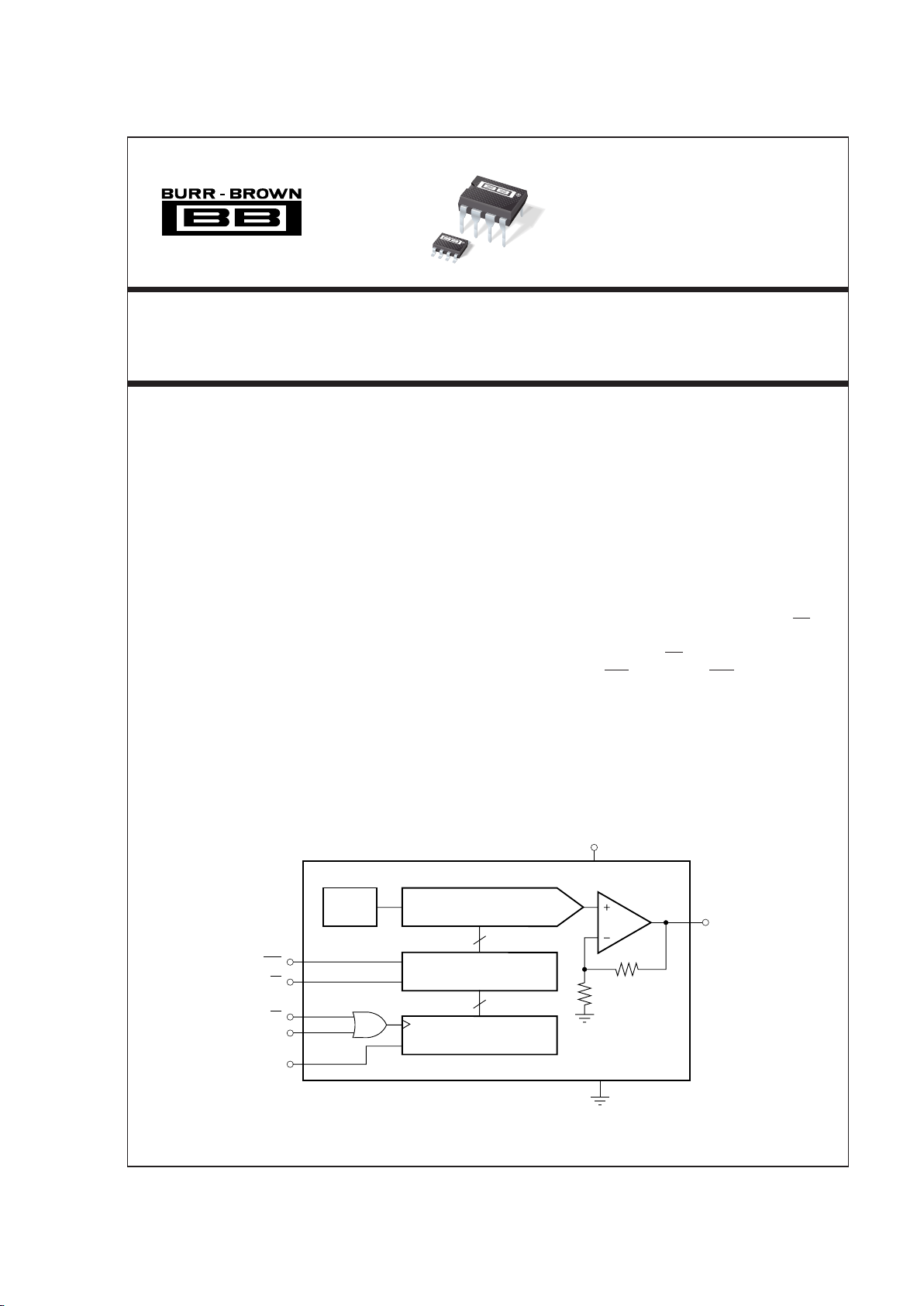

DESCRIPTION

The DAC7611 is a 12-bit digital-to-analog converter

(DAC) with guaranteed 12-bit monotonicity performance over the industrial temperature range. It requires a single +5V supply and contains an input shift

register, latch, 2.435V reference, DAC, and high speed

rail-to-rail output amplifier. For a full-scale step, the

output will settle to 1 LSB within 7µs. The device

consumes 2.5mW (0.5mA at 5V).

The synchronous serial interface is compatible with a

wide variety of DSPs and microcontrollers. Clock

(CLK), serial data in (SDI), and load strobe (LD)

comprise the serial interface. In addition, two control

pins provide a chip select (CS) function and an asynchronous clear (CLR) input. The CLR input can be

used to ensure that the DAC7611 output is 0V on

power-up or as required by the application.

The DAC7611 is available in an 8-lead SOIC or 8-pin

plastic DIP package and is fully specified over the

industrial temperature range of –40°C to +85°C.

DAC7611

DAC7611

© 1997 Burr-Brown Corporation PDS-1402A Printed in U.S.A. April, 1998

FEATURES

● LOW POWER: 2.5mW

● FAST SETTLING: 7

µs to 1 LSB

● 1mV LSB WITH 4.095V FULL-SCALE

RANGE

● COMPLETE WITH REFERENCE

● 12-BIT LINEARITY AND MONOTONICITY

OVER INDUSTRIAL TEMP RANGE

● ASYNCHRONOUS RESET TO 0V

● 3-WIRE INTERFACE: Up to 20MHz Clock

● ALTERNATE SOURCE TO DAC8512

12-Bit DAC

Ref

DAC Register

Serial Shift Register

12

12

CLR

LD

CS

CLK

SDI

V

DD

GND

V

OUT

DAC7611

APPLICATIONS

● PROCESS CONTROL

● DATA ACQUISITION SYSTEMS

● CLOSED-LOOP SERVO-CONTROL

● PC PERIPHERALS

● PORTABLE INSTRUMENTATION

®

2

DAC7611

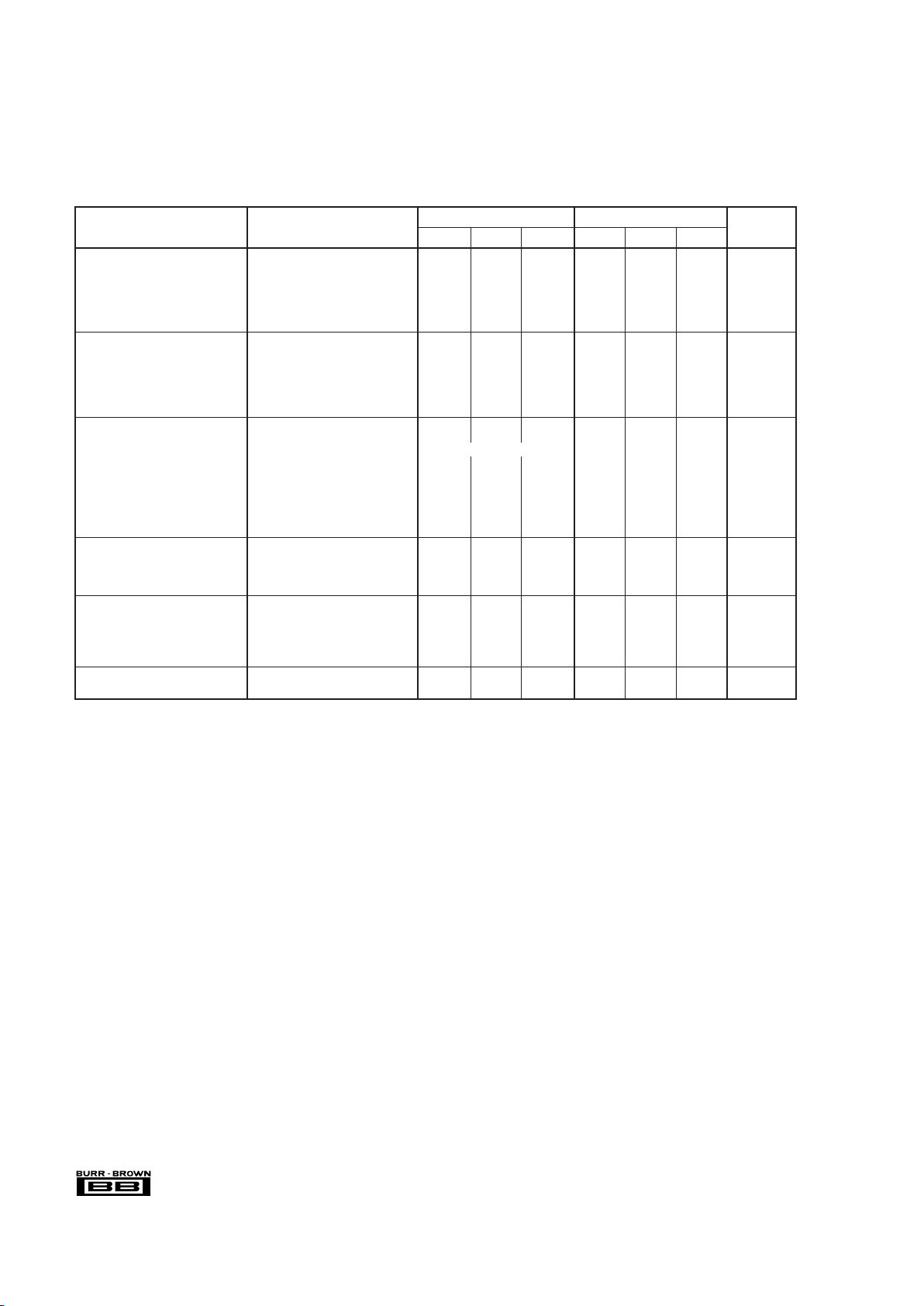

SPECIFICATIONS

ELECTRICAL

At TA = –40°C to +85°C, and VDD = +5V, unless otherwise noted.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes

no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject to change

without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant

any BURR-BROWN product for use in life support devices and/or systems.

DAC7611P, U DAC7611PB, UB

PARAMETER CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

ACCURACY

Resolution 12 ✻ Bits

Relative Accuracy

(1)

–2 ±1/2 +2 –1 ±1/4 +1 LSB

Differential Nonlinearity Guaranteed Monotonic –1 ±1/2 +1 –1 ±1/4 +1 LSB

Zero-Scale Error Code 000

H

–1 +1 +3 ✻✻✻ LSB

Full Scale Voltage Code FFF

H

4.079 4.095 4.111 4.087 4.095 4.103 V

ANALOG OUTPUT

Output Current Code 800

H

±5 ±7 ✻✻ mA

Load Regulation R

LOAD

≥ 402Ω, Code 800

H

13 ✻✻ LSB

Capacitive Load No Oscillation 500 ✻ pF

Short Circuit Current ±70 ✻ mA

Short Circuit Duration GND or V

DD

Indefinite ✻

DIGITAL INPUT

Data Format Serial ✻

Data Coding Straight Binary ✻

Logic Family TTL ✻

Logic Levels

V

IH

2.4 ✻ V

V

IL

0.8 ✻ V

I

IH

±10 ✻ µA

I

IL

±10 ✻ µA

DYNAMIC PERFORMANCE

Settling Time

(2)

(tS) To ±1 LSB of Final Value 7 ✻ µs

DAC Glitch 15 ✻ nV-s

Digital Feedthrough 2 ✻ nV-s

POWER SUPPLY

V

DD

+4.75 +5.0 +5.25 ✻✻✻ V

I

DD

VIH = 5V, VIL = 0V, No Load, at Code 000

H

0.5 1 ✻✻ mA

Power Dissipation V

IH

= 5V, VIL = 0V, No Load 2.5 5 ✻✻ mW

Power Supply Sensitivity ∆V

DD

= ±5% 0.001 0.004 ✻✻%/%

TEMPERATURE RANGE

Specified Performance –40 +85 ✻✻°C

✻ Same specification as for DAC7611P, U.

NOTES: (1) This term is sometimes referred to as Linearity Error or Integral Nonlinearity (INL). (2) Specification does not apply to negative-going transitions where

the final output voltage will be within 3 LSBs of ground. In this region, settling time may be double the value indicated.

®

3

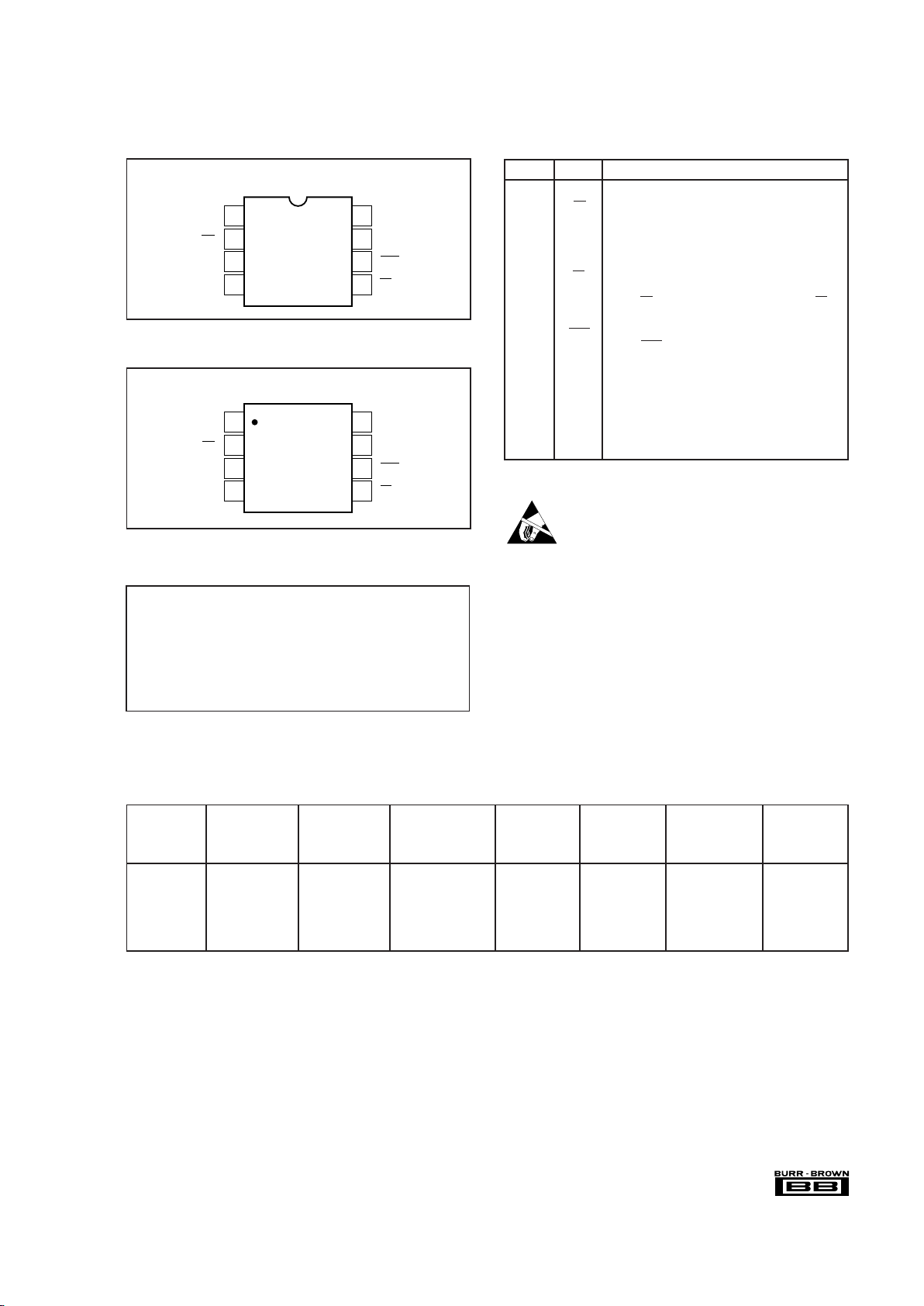

DAC7611

1

2

3

4

8

7

6

5

V

DD

CS

CLK

SDI

V

OUT

GND

CLR

LD

DAC7611

PIN CONFIGURATION

Top View DIP

PIN CONFIGURATION

Top View SOIC

VDD to GND .......................................................................... –0.3V to 6V

Digital Inputs to GND ............................................. –0.3V to V

DD

+ 0.3V

V

OUT

to GND ........................................................... –0.3V to VDD + 0.3V

Power Dissipation ........................................................................ 325mW

Thermal Resistance,

θ

JA

............................................................ 150°C/W

Maximum Junction Temperature ................................................. +150°C

Operating Temperature Range ...................................... –40°C to +85°C

Storage Temperature Range ........................................ –65°C to +150°C

Lead Temperature (soldering, 10s)............................................. +300°C

NOTE: (1) Stresses above those listed under “Absolute Maximum Ratings”

may cause permanent damage to the device. Exposure to absolute maximum

conditions for extended periods may affect device reliability.

ABSOLUTE MAXIMUM RATINGS

(1)

1

2

3

4

8

7

6

5

V

DD

CS

CLK

SDI

V

OUT

GND

CLR

LD

DAC7611

PIN DESCRIPTION

PIN LABEL DESCRIPTION

1V

DD

Power Supply

2 CS Chip Select (active LOW).

3 CLK Synchronous Clock for the Serial Data Input.

4 SDI Serial Data Input. Data is clocked into the internal

serial register on the rising edge of CLK.

5 LD Loads the Internal DAC Register. NOTE: The DAC

register is a transparent latch and is transparent

when LD is LOW (regardless of the state of CS or

CLK).

6 CLR Asynchronous Input to Clear the DAC Register.

When CLR is strobbed LOW, the DAC register is set

to 000

H

and the output voltage to 0V.

7 GND Ground

8V

OUT

Voltage Output. Fixed output voltage range of approximately 0V to 4.095V (1mV/LSB). The internal

reference maintains this output range over time,

temperature, and power supply variations (within

the values defined in the specifications section).

ELECTROSTATIC

DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown

recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling

and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits

may be more susceptible to damage because very small

parametric changes could cause the device not to meet its

published specifications.

PACKAGE/ORDERING INFORMATION

MINIMUM

RELATIVE DIFFERENTIAL SPECIFICATION PACKAGE

ACCURACY NONLINEARITY TEMPERATURE DRAWING ORDERING TRANSPORT

PRODUCT (LSB) (LSB) RANGE PACKAGE NUMBER

(1)

NUMBER

(2)

MEDIA

DAC7611P ±2 ±1 –40°C to +85°C 8-Pin DIP 006 DAC7611P Rails

DAC7611U ±2 ±1 –40 °C to +85°C 8-Lead SOIC 182 DAC7611U Rails

"" " " ""DAC7611U/2K5 Tape and Reel

DAC7611PB ±1 ±1 –40°C to +85°C 8-Pin DIP 006 DAC7611PB Rails

DAC7611UB ±1 ±1 –40 °C to +85°C 8-Lead SOIC 182 DAC7611UB Rails

"" " " ""DAC7611UB/2K5 Tape and Reel

NOTES: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book. (2) Models with a slash (/) are

available only in Tape and Reel in the quantities indicated (e.g., /2K5 indicates 2500 devices per reel). Ordering 2500 pieces of “DAC7611/2K5” will get a single

2500-piece Tape and Reel. For detailed Tape and Reel mechanical information, refer to Appendix B of Burr-Brown IC Data Book.

®

4

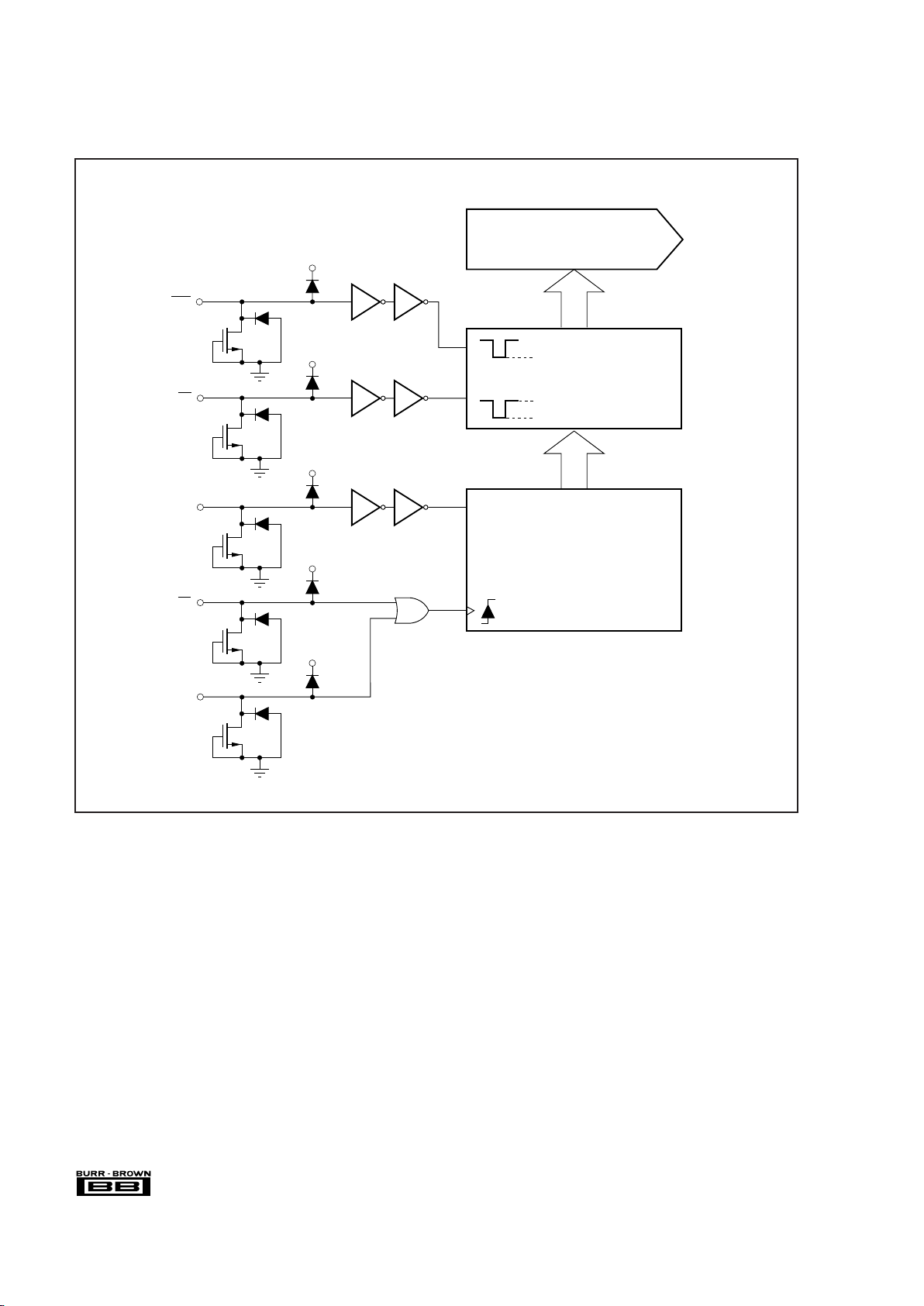

DAC7611

EQUIVALENT INPUT LOGIC

DAC

Register

Serial Shift Register

DAC

Switches

Force to 000

H

Transparent

Latched

Data

12

12

ESD protection

diodes to V

DD

and GND

CLR

LD

SDI

CS

CLK

Loading...

Loading...