Burr Brown Corporation DAC7545LU, DAC7545LP, DAC7545KU, DAC7545KP, DAC7545JU Datasheet

...

1

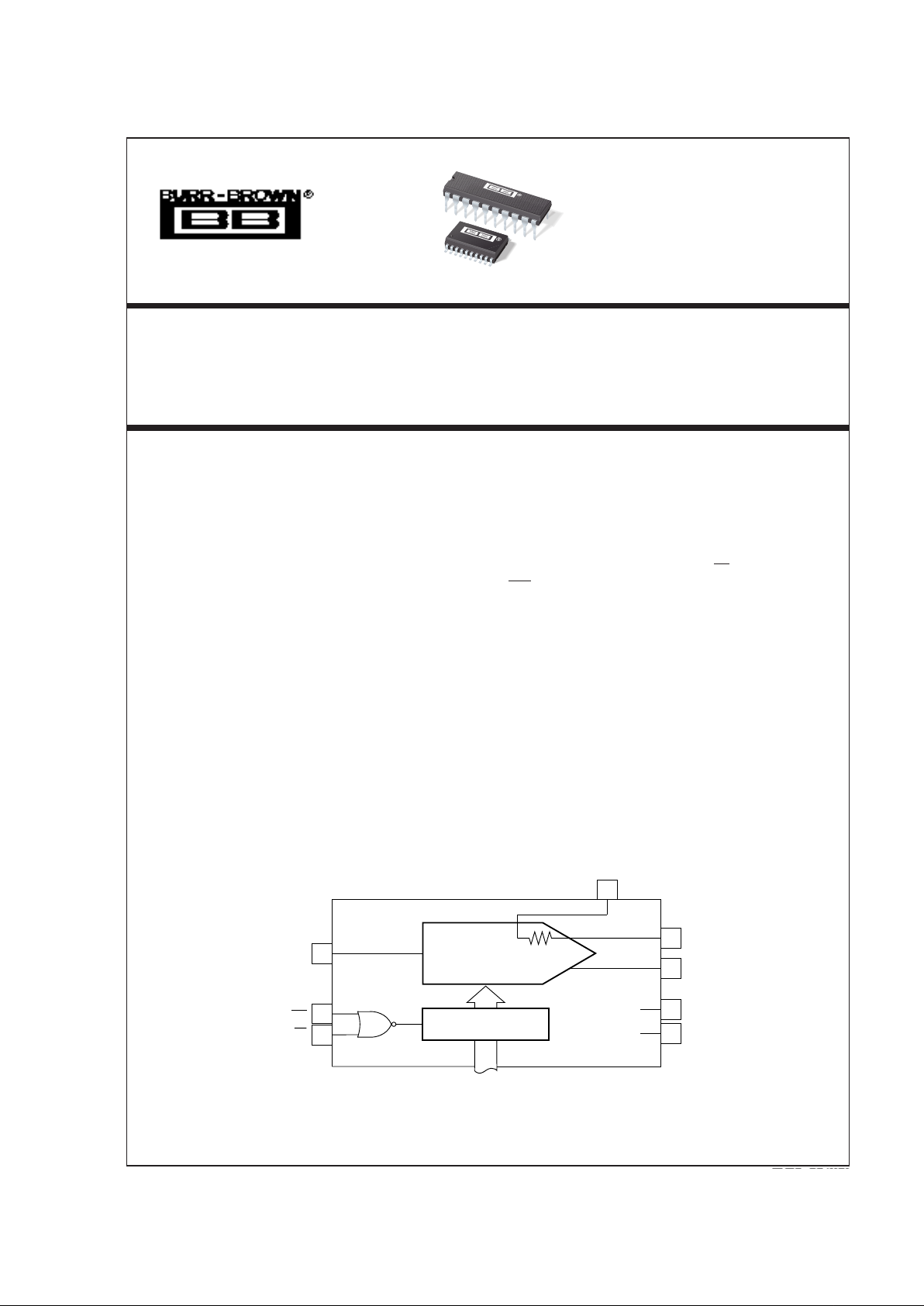

DAC7545

CMOS 12-Bit Multiplying

DIGITAL-TO-ANALOG CONVERTER

Microprocessor Compatible

FEATURES

● FOUR-QUADRANT MULTIPLICATION

● LOW GAIN TC: 2ppm/

°C typ

● MONOTONICITY GUARANTEED OVER

TEMPERATURE

● SINGLE 5V TO 15V SUPPLY

● TTL/CMOS LOGIC COMPATIBLE

● LOW OUTPUT LEAKAGE: 10nA max

● LOW OUTPUT CAPACITANCE: 70pF max

● DIRECT REPLACEMENT FOR AD7545,

PM-7545

DESCRIPTION

The DAC7545 is a low-cost CMOS, 12-bit fourquadrant multiplying, digital-to-analog converter with

input data latches. The input data is loaded into the

DAC as a 12-bit data word. The data flows through to

the DAC when both the chip select (CS) and the write

(WR) pins are at a logic low.

Laser-trimmed thin-film resistors and excellent CMOS

voltage switches provide true 12-bit integral and differential linearity. The device operates on a single

+5V to +15V supply and is available in 20-pin plastic

DIP or 20-lead plastic SOIC packages. Devices are

specified over the commercial.

The DAC7545 is well suited for battery or other low

power applications because the power dissipation is

less than 0.5mW when used with CMOS logic inputs

and V

DD

= +5V.

12-Bit

Multiplying DAC

AGND

OUT 1

DB

11

-DB

0

(

Pins 4-15

)

WR

CS

17

Input

Data Latches

12

12

16

19

V

REF

20

R

FB

1

2

18

3

V

DD

DGND

DAC7545

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111

Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

©

1987 Burr-Brown Corporation PDS-747F Printed in U.S.A. August, 1997

DAC7545

DAC7545

2

DAC7545

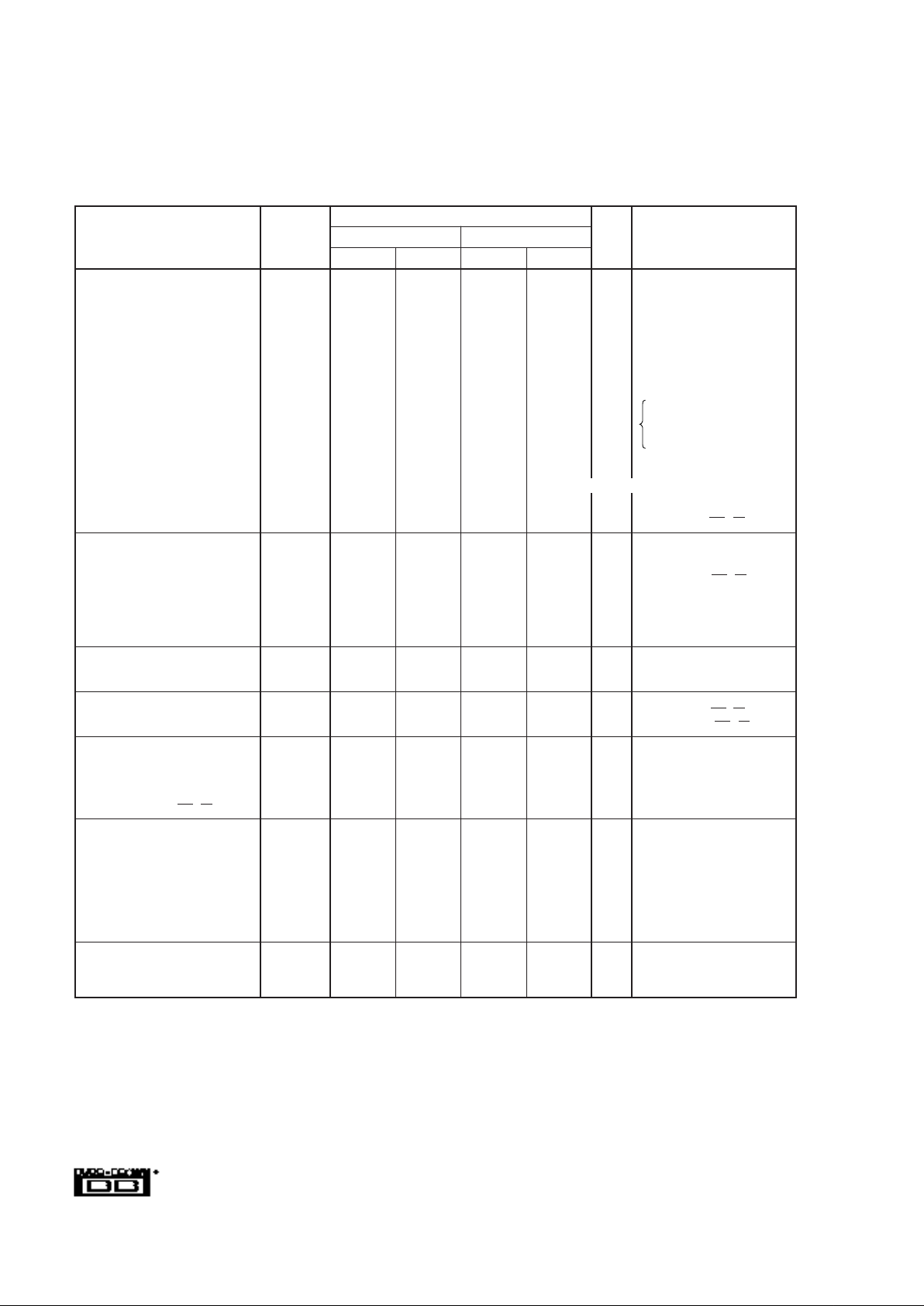

SPECIFICATIONS

ELECTRICAL

V

REF

= +10V, V

OUT 1

= 0V, ACOM = DCOM, unless otherwise specified.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN

assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject

to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not

authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

NOTES: (1) Temperature ranges—J, K, L, GL: –40°C to +85°C. (2) This includes the effect of 5ppm max, gain TC. (3) Guaranteed but not tested. (4) DB0-DB11 = 0V

to V

DD

or VDD to 0V. (5) Typical. (6) Minimum. (7) Logic inputs are MOS gates. Typical input current (+25°C) is less than 1nA. (8) Sample tested at +25°C to ensure

compliance.

DAC7545

V

DD

= +5V V

DD

= +15V

PARAMETER GRADE T

A

= +25°CT

MAX-TMIN

(1)

TA = +25°CT

MAX-TMIN

(1)

UNITS TEST CONDITIONS/COMMENTS

STATIC PERFORMANCE

Resolution All 12 12 12 12 Bits

Accuracy J ±2 ±2 ±2 ±2 LSB

K ±1 ±1 ±1 ±1 LSB

L ±1/2 ±1/2 ±1/2 ±1/2 LSB

GL ±1/2 ±1/2 ±1/2 ±1/2 LSB

Differential Nonlinearity J ±4 ±4 ±4 ±4 LSB 10-Bit Monotonic, T

MIN

to T

MAX

K ±1 ±1 ±1 ±1 LSB 10-Bit Monotonic, T

MIN

to T

MAX

L ±1 ±1 ±1 ±1 LSB 12-Bit Monotonic, T

MIN

to T

MAX

GL ±1 ±1 ±1 ±1 LSB 12-Bit Monotonic, T

MIN

to T

MAX

Gain Error (with internal RFB)

(2)

J ±20 ±20 ±25 ±25 LSB D/A register loaded with FFFH.

K ±10 ±10 ±15 ±15 LSB Gain error is adjustable using

L ±5 ±6 ±10 ±10 LSB the circuits in Figures 2 and 3.

GL ±2 ±3 ±6 ±7 LSB

Gain Temperature Coefficient

(3)

(∆Gain/∆Temperature) All ±5 ±5 ±10 ±10 ppm/°C Typical value is 2ppm/°C

for V

DD

= +5

DC Supply Rejection

(3)

(∆Gain/∆VDD) All 0.015 0.03 0.01 0.02 %/% ∆VDD ±5%

Output Leakage Current at Out 1 J, K, L, GL 10 50 10 50 nA DB

0

-DB11 = 0V; WR, CS = 0V

DYNAMIC PERFORMANCE

Current Settling Time

(3)

All2222µs To 1/2LSB. Out1 Load = 100Ω

DAC output measured from

falling edge of WR. CS = 0V

Propagation Delay

(3)

(from digital input All

change to 90% of final analog output) 300 250 ns Out

1

Load = 100Ω. C

EXT

= 13pF

(4)

Glitch Energy All 400 250 nV-s

(5)

V

REF

= ACOM

AC Feedback at I

OUT

1 All 5 5 5 5 mVp-p

(5)

V

REF

= ±10V, 10kHz Sine Wave

REFERENCE INPUT

Input Resistance (pin 19 to AGND) All 7 7 7 7 kΩ

(6)

Input resistance TC = 300ppm/°C

(5)

25 25 25 25 kΩ

AC OUTPUTS

Output Capacitance

(3)

: C

OUT 1

All 70 70 70 70 pF DB0-DB11 = 0V; WR, CS = 0V

C

OUT 2

All 200 200 200 200 pF DB0-DB11 = VDD; WR, CS = 0V

DIGITAL INPUTS

V

IH

(Input HIGH Voltage) All 2.4 2.4 13.5 13.5 V

(6)

VIL (Input LOW Voltage) All 0.8 0.8 1.5 1.5 V

I

IN

(Input Current)

(7)

All ±1 ±10 ±1 ±10 µAVIN = 0 or V

DD

Input Capacitance

(3)

: DB0-DB

11

All5555pFV

IN

= 0V

WR, CS All 20 20 20 20 pF V

IN

= 0V

SWITCHING CHARACTERISTICS

(8)

Chip Select to Write Setup Time, t

CS

All 280 380 180 200 ns

(6)

See Timing Diagram

200 270 120 150 ns

(5)

Chip Select to Write Hold Time, t

CH

All0000ns

(6)

Write Pulse Width, t

WR

All 250 400 160 240 ns

(6)

tCS ≥ tWR, tCH ≥ 0

175 280 100 170 ns

(5)

Data Setup Time, t

DS

All 140 210 90 120 ns

(6)

100 150 60 80 ns

(5)

Data Hold Time, t

DH

All 10 10 10 10 ns

(6)

POWER SUPPLY, I

DD

All 2 2 2 2 mA All Digital Inputs VIL or V

IH

All 100 500 100 500 µA All Digital Inputs 0V or V

DD

All 10 10 10 10 µA

(5)

All Digital Inputs 0V or V

DD

3

DAC7545

TEMPERATURE RELATIVE GAIN ERROR (LSB)

PRODUCT PACKAGE RANGE ACCURACY (LSB) V

DD

= +5V

DAC7545JP Plastic DIP –40°C to +85°C ±2 ±20

DAC7545KP Plastic DIP –40°C to +85°C ±1 ±10

DAC7545LP Plastic DIP –40°C to +85°C ±1/2 ±5

DAC7545GLP Plastic DIP –40°C to +85°C ±1/2 ±2

DAC7545JU Plastic SOIC –40°C to +85°C ±2 ±20

DAC7545KU Plastic SOIC –40°C to +85°C ±1 ±10

DAC7545LU Plastic SOIC –40°C to +85°C ±1/2 ±5

DAC7545GLU Plastic SOIC –40°C to +85°C ±1/2 ±2

PACKAGE DRAWING

PRODUCT PACKAGE NUMBER

(1)

DAC7545JP 20-Pin PDIP 222

DAC7545KP 20-Pin PDIP 222

DAC7545LP 20-Pin PDIP 222

DAC7545GLP 20-Pin PDIP 222

DAC7545JU 20-Pin SOIC 221

DAC7545KU 20-Pin SOIC 221

DAC7545LU 20-Pin SOIC 221

DAC7545GLU 20-Pin SOIC 221

NOTE: (1) For detailed drawing and dimension table, please see end of data

sheet, or Appendix C of Burr-Brown IC Data Book.

ABSOLUTE MAXIMUM RATINGS

(1)

TA = +25°C, unless otherwise noted.

V

DD

to DGND ........................................................................... –0.3V, +17

Digital Input to DGND ...............................................................–0.3V, V

DD

V

RFB

, V

REF

, to DGND ........................................................................ ±25V

V

PIN 1

to DGND ......................................................................... –0.3V, V

DD

AGND to DGND ........................................................................–0.3V, V

DD

Power Dissipation: Any Package to +75°C .................................... 450mW

Derates above +75°C by ................................ 6mW/°C

Operating Temperature:

Commercial J, K, L, GL .................................................. –40°C to +85°C

Storage Temperature...................................................... –65°C to +150°C

Lead Temperature (soldering, 10s)................................................ +300°C

NOTE: (1) Stresses above those listed above may cause permanent damage to

the device. This is a stress rating only and functional operation of the device at

these or any other condition above those indicated in the operational sections of

this specification is not implied. Exposure to absolute maximum rating conditions

for extended periods may affect device reliability.

PIN CONNECTIONS

ELECTROSTATIC

DISCHARGE SENSITIVITY

Any integral circuit can be damaged by ESD. Burr-Brown

recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling

and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits

may be more susceptible to damage because very small

parametric changes could cause the device not to meet

published specifications.

PACKAGE INFORMATION

DAC7545

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

OUT 1

AGND

DGND

(MSB) DB

11

DB

10

DB

9

DB

8

DB

7

DB

6

DB

5

R

FB

V

REF

V

DD

WR

CS

DB

0

(LSB)

DB

1

DB

2

DB

3

DB

4

ORDERING INFORMATION

Top View DIP/SOIC

Loading...

Loading...