Burr Brown Corporation DAC715PB, DAC715, DAC715UL, DAC715UK, DAC715UB Datasheet

...

®

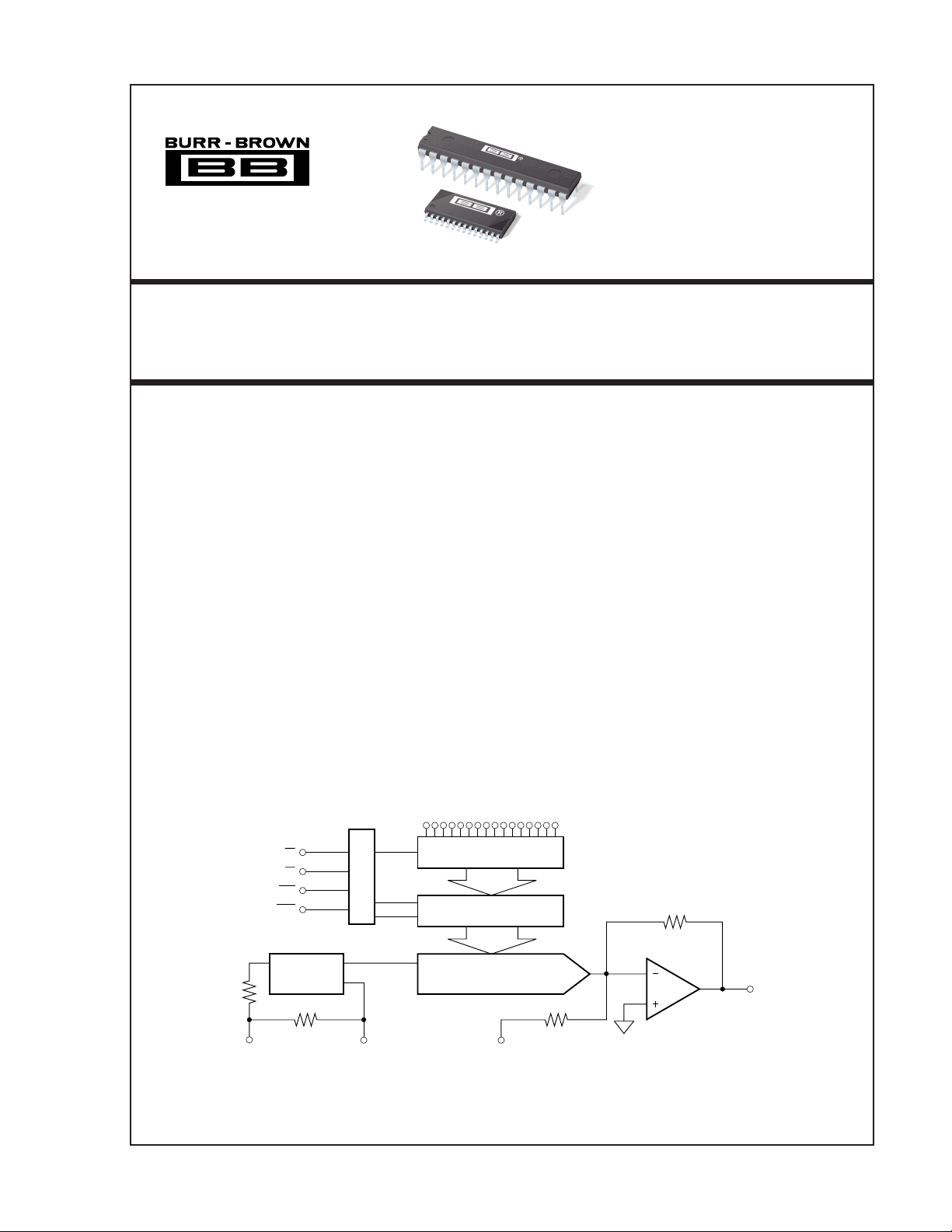

DAC715

DAC715

FPO

DAC715

16-BIT DIGITAL-TO-ANALOG CONVERTER

with 16-Bit Bus Interface

FEATURES

● HIGH-SPEED 16-BIT PARALLEL DOUBLE-

BUFFERED INTERFACE

● VOLTAGE OUTPUT: 0 to +10V

● 13-, 14-, 15-BIT LINEARITY GRADES

● 16-BIT MONOTONIC OVER

TEMPERATURE (L GRADE)

● POWER DISSIPATION: 600mW max

● GAIN AND OFFSET ADJUST: Convenient

for Auto-Cal D/A Converters

● 28-LEAD DIP AND SOIC PACKAGES

D0 D15

A

1

A

0

WR

CLR

DESCRIPTION

The DAC715 is a complete monolithic digital-toanalog converter including a +10V temperature compensated reference, current-to-voltage amplifier, 16-bit

parallel interface that is double buffered, and an asynchronous clear function which immediately sets the

output voltage to one-half of full-scale.

The output voltage range is 0 to +10V while operating

from ±12V or ±15V supplies. The gain and bipolar

offset adjustments are designed so that they can be set

via external potentiometers or external D/A converters.

The output amplifier is protected against short circuit to

ground.

The 28-pin DAC715 is available in a 0.3" plastic DIP

and wide-body plastic SOIC package. The DAC715P,

U, PB, and UB are specified over the –40°C to +85°C

temperature range while the DAC715PK, UK, PL, and

UL are specified over the 0°C to +70°C range.

Input Latch

16

D/A Latch

16

Reference

Circuit

Gain Adjust

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111

Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

© 1995 Burr-Brown Corporation PDS-1306D Printed in U.S.A. July, 1997

V

REF OUT

+10V

16-Bit D/A Converter

Offset Adjust

V

OUT

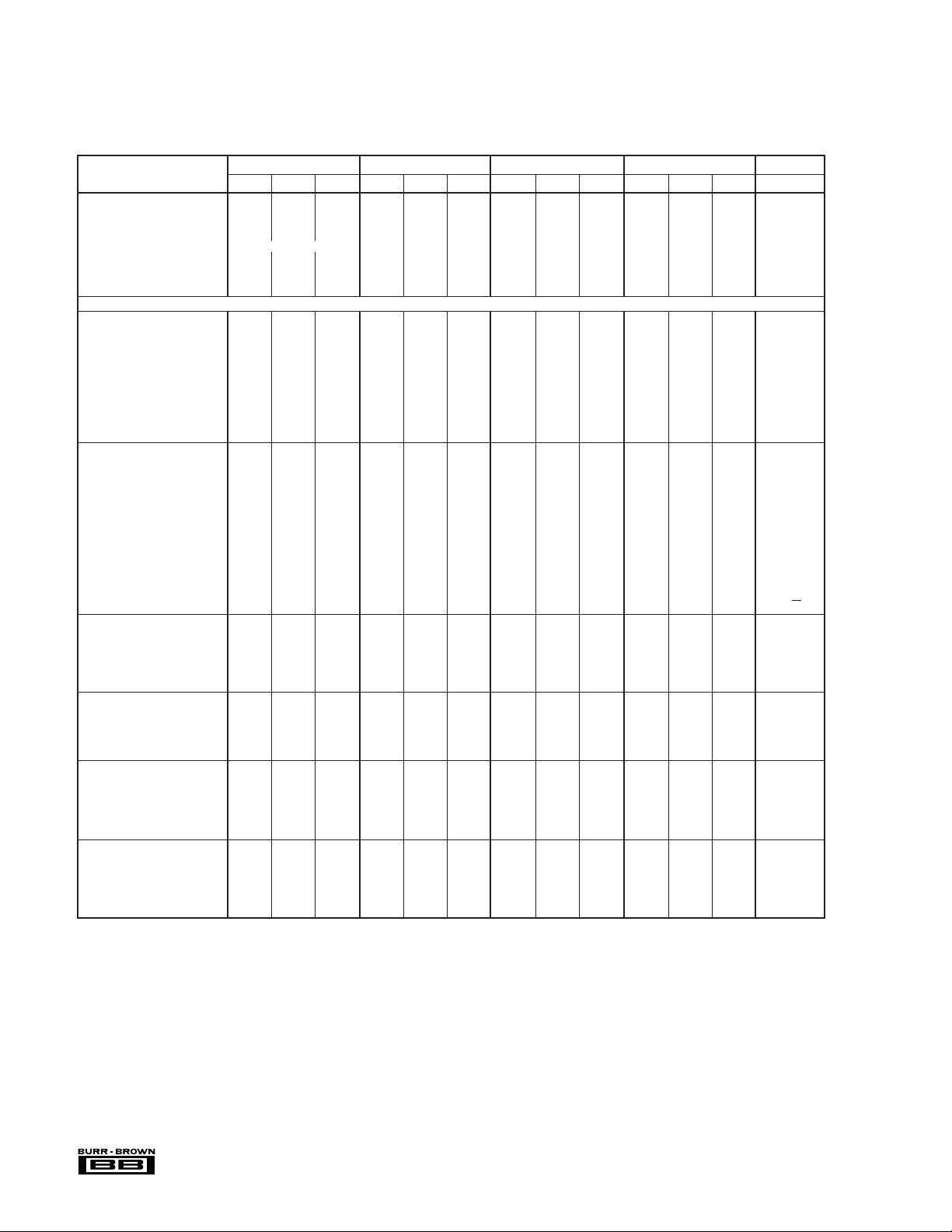

SPECIFICATIONS

ELECTRICAL

At TA = +25°C, V

PARAMETER MIN TYP MAX MIN TYP MAX MIN TYP MAX MIN TYP MAX UNITS

INPUT

RESOLUTION 16 ✻✻ ✻Bits

DIGITAL INPUTS

Input Code Binary Two’s Complement ✻✻✻

Logic Levels

TRANSFER CHARACTERISTICS

ACCURACY

Linearity Error ±4 ±2 ±2 ±2 LSB

to T

T

MIN

Differential Linearity Error ±4 ±2 ±2 ±1 LSB

to T

T

MIN

Monotonicity Over Temp 13 14 15 16 Bits

Gain Error

to T

T

MIN

Offset Error

T

to T

MIN

Power Supply Sensitivity Of Full Scale ±0.003 ✻✻ ✻% FSR/%V

DYNAMIC PERFORMANCE

Settling Time (to ±0.003%FSR,

10V Output Step 6 10 ✻✻ ✻✻ ✻✻ µs

1 LSB Output Step

Output Slew Rate 10 ✻✻✻V/µs

Total Harmonic Distortion + Noise

0dB, 1001Hz, f

–20dB, 1001Hz, f

–60dB, 1001Hz, f

SINAD

1001Hz, f

Digital Feedthrough

Digital-to-Analog Glitch Impulse

Output Noise Voltage

(includes Reference) 120 ✻✻ ✻nV√Hz

ANALOG OUTPUT

Output Voltage Range

, –VCC = ±11.4V 0 to +10 ✻✻✻ V

+V

CC

Output Current ±5 ✻✻✻ mA

Output Impedance 0.1 ✻✻ ✻Ω

Short Circuit to ACOM

Duration Indefinite ✻✻ ✻

REFERENCE VOLTAGE

Voltage +9.975 +10.000 +10.025 ✻✻✻✻✻✻✻✻✻ V

to T

T

MIN

Output Resistance 1 ✻✻✻Ω

Source Current 2 ✻✻✻ mA

Short Circuit to ACOM, Duration Indefinite ✻✻ ✻

POWER SUPPLY REQUIREMENTS

Voltage: +V

–V

CC

Current (no load, ±15V Supplies)

+V

CC

–V

CC

Power Dissipation 525 600 ✻✻ ✻✻ ✻✻ mW

TEMPERATURE RANGE

Specification All Grades

Storage –60 +150 ✻✻✻✻✻✻°C

Thermal Resistance

DIP Package 75 ✻✻✻°C/W

SOIC Package 75 ✻✻✻°C/W

✻

Specifications are the same as grade to the left.

NOTES: (1) Digital inputs are TTL and +5V CMOS compatible over the specification temperature range. (2) FSR means Full Scale Range. For example, for a 0 to +10V output, FSR = 10V.

(3) Errors externally adjustable to zero. (4) Maximum represents greater than the 3σ limit. Not 100% tested for this parameter. (5) For the worst case code changes: FFFF

FFFF

. These are Binary Two’s Complement (BTC) codes. (6) Typical supply voltages times maximum currents.

H

= ±15V, and after a 10-minute warm-up, unless otherwise noted.

CC

DAC715P, U DAC715PB, UB DAC715PK, UK DAC715PL, UL

(1)

: V

IH

V

IL

(VI = +2.7V) ±10 ✻✻ ✻µA

I

IH

(VI = +0.4V) ±10 ✻✻ ✻µA

I

IL

MAX

MAX

(3)

MAX

(3)

MAX

5kΩ ll 500pF Load)

(5)

= 100kHz 0.005 ✻✻✻%

S

= 100kHz 0.03 ✻✻✻%

S

= 100kHz 3.0 ✻✻ ✻%

S

= 100kHz 87 ✻✻✻dB

S

(5)

MAX

CC

+2.0 +VCC – 1.4 ✻✻✻✻✻✻V

0 +0.8 ✻✻✻✻✻ ✻V

±8 ±4 ±2 ±2 LSB

±8 ±4 ±2 ±1 LSB

±0.1 ±0.1 ✻✻%

±0.2 ±0.15 ✻✻%

±0.1 ✻✻ ✻% FSR

±0.2 ✻✻ ✻% FSR

±30 ✻✻ ✻PPM FSR/%V

(4)

4 ✻✻✻µs

(5)

2 ✻✻✻nV-s

15 ✻✻✻nV-s

+9.960 +10.040 ✻✻✻✻✻ ✻V

+11.4 +15 +16.5 ✻✻✻✻✻✻ ✻✻✻ V

–16.5 –15 –11.4 ✻✻✻✻✻✻✻✻✻ V

13 15 ✻✻ ✻✻ ✻✻ mA

22 25 ✻✻ ✻✻ ✻✻ mA

(2)

CC

CC

–40 +85 ✻✻0 +70 ✻✻°C

θ

JA

to 0000H and 0000H to

H

®

DAC715

2

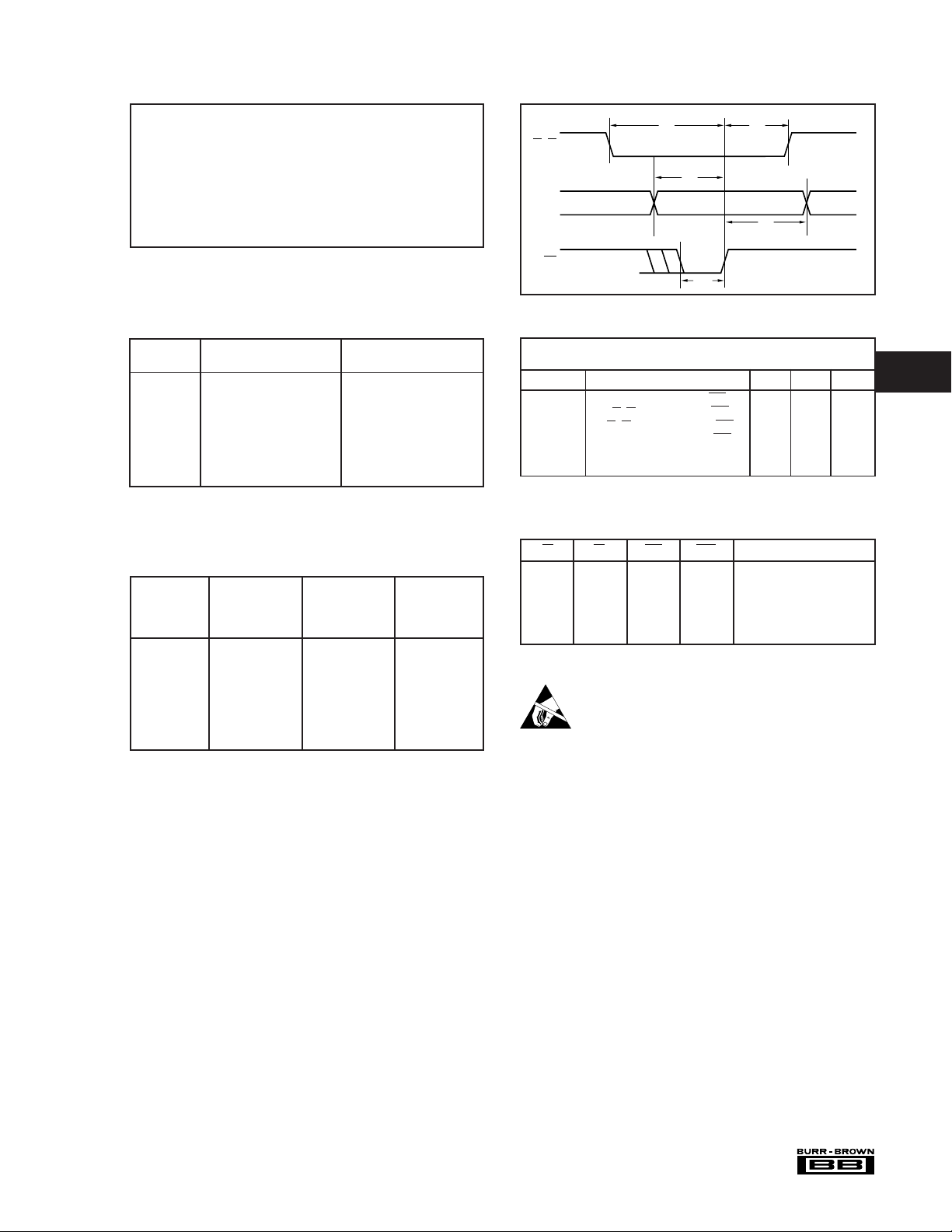

ABSOLUTE MAXIMUM RATINGS

+VCC to COMMON ...................................................................... 0V, +17V

–V

to COMMON ...................................................................... 0V, –17V

CC

+V

CC

Digital Inputs to COMMON .....................................................–1V to +V

External Voltage Applied to BPO and Range Resistors..................... ±V

V

REF OUT

V

OUT

Power Dissipation .......................................................................... 750mW

Storage Temperature...................................................... –60°C to +150°C

Lead Temperature (soldering, 10s)................................................ +300°C

NOTE: (1) Stresses above those listed under “Absolute Maximum Ratings” may

cause permanent damage to the device. Exposure to absolute maximum

conditions for extended periods may affect device reliability.

...........................................................................................................................

to –V

CC

...................................................... Indefinite Short to COMMON

............................................................ Indefinite Short to COMMON

(1)

34V

CC

CC

TIMING DIAGRAM

A

, A

0

1

D0-D15

WR

t

AW

t

DW

t

WP

t

AH

t

DH

PACKAGE INFORMATION

PRODUCT PACKAGE NUMBER

PACKAGE DRAWING

DAC715P Plastic DIP 246

DAC715U Plastic SOIC 217

DAC715PB Plastic DIP 246

DAC715UB Plastic SOIC 217

DAC715PK Plastic DIP 246

DAC715UK Plastic SOIC 217

DAC715PL Plastic DIP 246

DAC715UL Plastic SOIC 217

NOTE: (1) For detailed drawing and dimension table, please see end of data

sheet, or Appendix C of Burr-Brown IC Data Book.

(1)

ORDERING INFORMATION

DIFFERENTIAL

PRODUCT PACKAGE RANGE at +25

TEMPERATURE ERROR MAX

DAC715P Plastic DIP –40°C to +85°C ±4LSB

DAC715U Plastic SOIC –40°C to +85°C ±4LSB

DAC715PB Plastic DIP –40°C to +85°C ±2LSB

DAC715UB Plastic SOIC –40°C to +85°C ±2LSB

DAC715PK Plastic DIP 0°C to 70°C ±2LSB

DAC715UK Plastic SOIC 0°C to 70°C ±2LSB

DAC715PL Plastic DIP 0°C to 70°C ±1LSB

DAC715UL Plastic SOIC 0°C to 70°C ±1LSB

LINEARITY

°C

TIMING SPECIFICATIONS

TA = –40°C to +85°C, +VCC = +12V or +15V, –VCC = –12V or –15V.

SYMBOL PARAMETER MIN MAX UNITS

t

DW

t

AW

t

AH

t

DH

(1)

t

WP

t

CP

NOTES: (1) For single-buffered operation, t

Data Valid to End of WR 50 ns

A0, A1 Valid to End of WR 50 ns

A0, A1 Hold after End of WR 10 ns

Data Hold after end of WR 10 ns

Write Pulse Width 50 ns

CLEAR Pulse Width 200 ns

is 80ns min. Refer to page 10.

WP

TRUTH TABLE

A

011 → 0 → 1 1 Load Input Latch

101 → 0 → 1 1 Load D/A Latch

111 → 0 → 1 1 No Change

0 0 0 1 Latches Transparent

X X 1 1 No Change

X X X 0 Reset D/A Latch

A

0

WR CLR DESCRIPTION

1

ELECTROSTATIC

DISCHARGE SENSITIVITY

Electrostatic discharge can cause damage ranging from performance degradation to complete device failure. Burr-Brown

Corporation recommends that all integrated circuits be handled

and stored using appropriate ESD protection methods.

ESD damage can range from subtle performance degradation

to complete device failure. Precision integrated circuits may

be more susceptible to damage because very small parametric

changes could cause the device not to meet published specifications.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes

no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject to change

without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant

any BURR-BROWN product for use in life support devices and/or systems.

3

DAC715

®

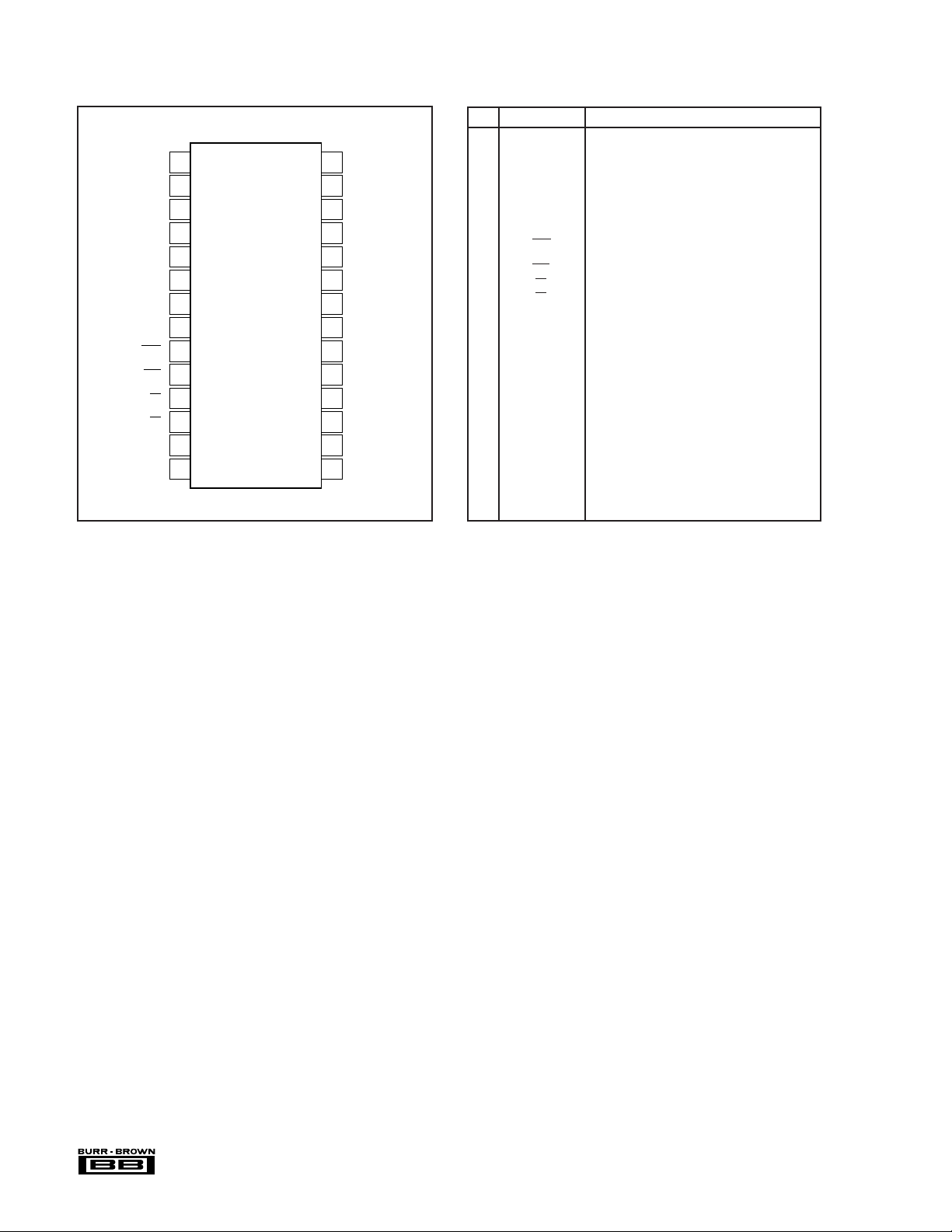

PIN CONFIGURATION

V

+V

–V

CLR

D14

OUT

WR

1

2

3

4

5

6

7

CC

8

CC

9

10

11

A

1

12

A

0

13

14

DCOM

ACOM

Offset Adjust

V

REF OUT

Gain Adjust

D15 (MSB)

DAC715

28

27

26

25

24

23

22

21

20

19

18

17

16

15

D0 (LSB)

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

PIN DESCRIPTIONS

PIN LABEL DESCRIPTION

1 DCOM Digital Ground

2 ACOM Analog Ground

3V

4 Offset Adjust Offset Adjust

5V

6 Gain Adjust Gain Adjust

7+V

8–V

9 CLR CLEAR. Sets D/A output to Half Scale

OUT

REF OUT

CC

CC

10 WR Write (Active Low)

11 A

12 A

13 D15 Data Bit 15 (Most Significant Bit)

1

0

14 D14 Data Bit 14

15 D13 Data Bit 13

16 D12 Data Bit 12

17 D11 Data Bit 11

18 D10 Data Bit 10

19 D9 Data Bit 9

20 D8 Data Bit 8

21 D7 Data Bit 7

22 D6 Data Bit 6

23 D5 Data Bit 5

24 D4 Data Bit 4

25

26

27

28

D3 Data Bit 3

D2 Data Bit 2

D1 Data Bit 1

D0 Data Bit 0 (Least Significant Bit)

0 to +10V D/A Output

Voltage Reference Output

+12V to +15V Supply

–12V to –15V Supply

(Active Low)

Enable for D/A latch (Active Low)

Enable for Input latch (Active Low)

®

DAC715

4

Loading...

Loading...