®

AFE1104

1

AFE1104E

HDSL/MDSL ANALOG FRONT END

FEATURES

● COMPLETE ANALOG INTERFACE

● T1, E1, AND MDSL OPERATION

● CLOCK SCALEABLE SPEED

● SINGLE CHIP SOLUTION

● +5V ONLY (5V OR 3.3V DIGITAL)

● 250mW POWER DISSIPATION

● 48-PIN SSOP

● –40

°C TO +85°C OPERATION

DESCRIPTION

Burr-Brown’s Analog Front End greatly reduces the

size and cost of an HDSL or MDSL system by providing all of the active analog circuitry needed to connect

PairGain Technologies SPAROW HDSL digital signal processor to an external compromise hybrid and a

1:2 HDSL line transformer. All internal filter responses as well as the pulse former output scale with

clock frequency—allowing the AFE1104 to operate

over a range of bit rates from 196kbps to 1.168Mbps.

Functionally, this unit is separated into a transmit and

a receive section. The transmit section generates, filters, and buffers outgoing 2B1Q data. The receive

section filters and digitizes the symbol data received

on the telephone line and passes it to the SPAROW.

The HDSL Analog Interface is a monolithic device

fabricated on 0.6µCMOS. It operates on a single +5V

supply. It is housed in a 48-pin SSOP package.

©

1996 Burr-Brown Corporation PDS-1331A Printed in U.S.A. August, 1996

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111

Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

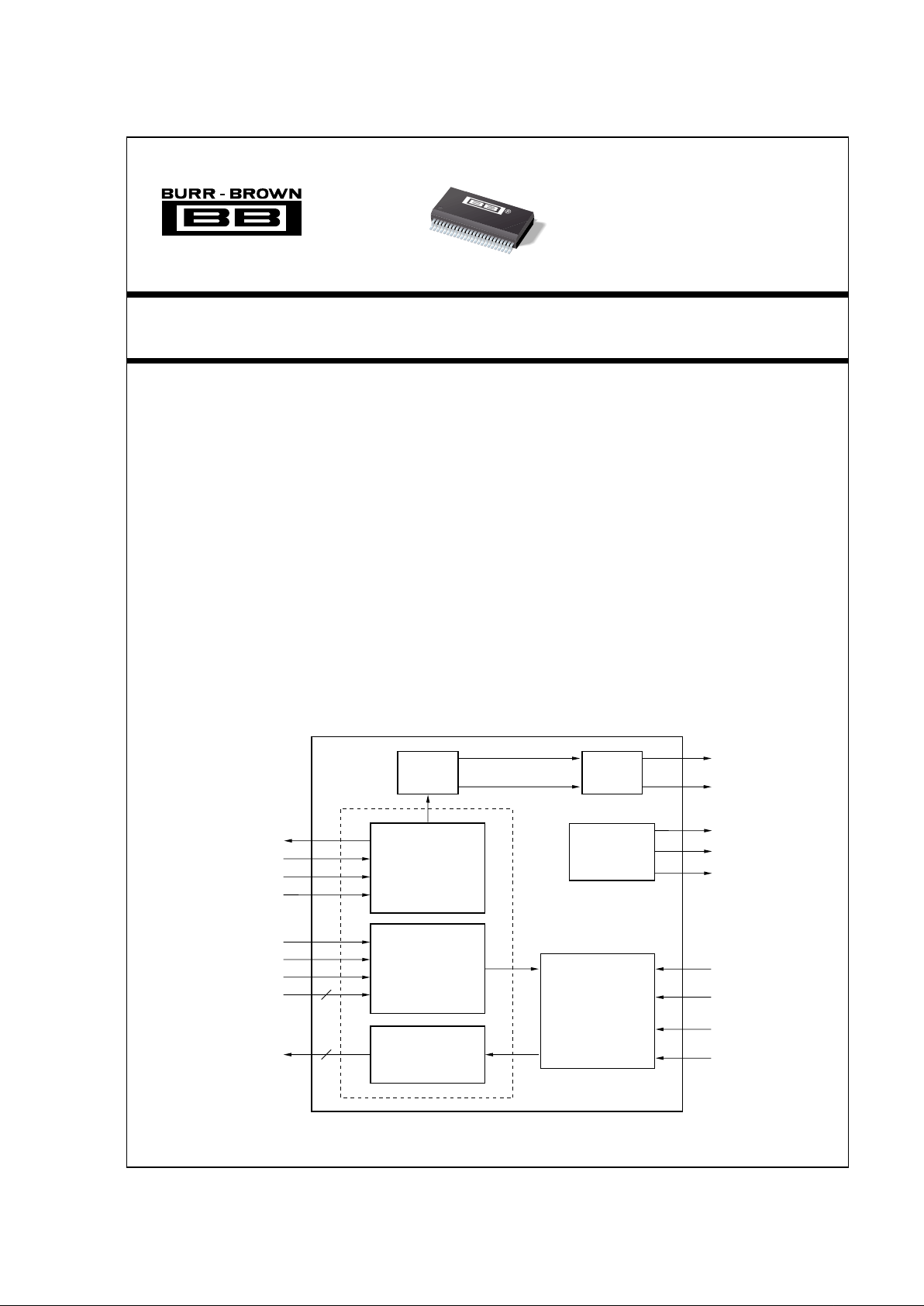

AFE1104

®

Pulse

Former

PLL

OUT

PLL

IN

txDAT

txCLK

rxGAIN

rxD13 - rxD0

Line

Driver

Voltage

Reference

Delta-Sigma

Modulator

Transmit

Control

rxSYNC

rxCLK

rxLOOP

Receive

Control

Decimation

Filter

14

2

txLINE

N

txLINE

P

REF

P

V

CM

REF

N

rxLINE

P

rxLINE

N

rxHYB

P

rxHYB

N

Patents Pending

2

®

AFE1104

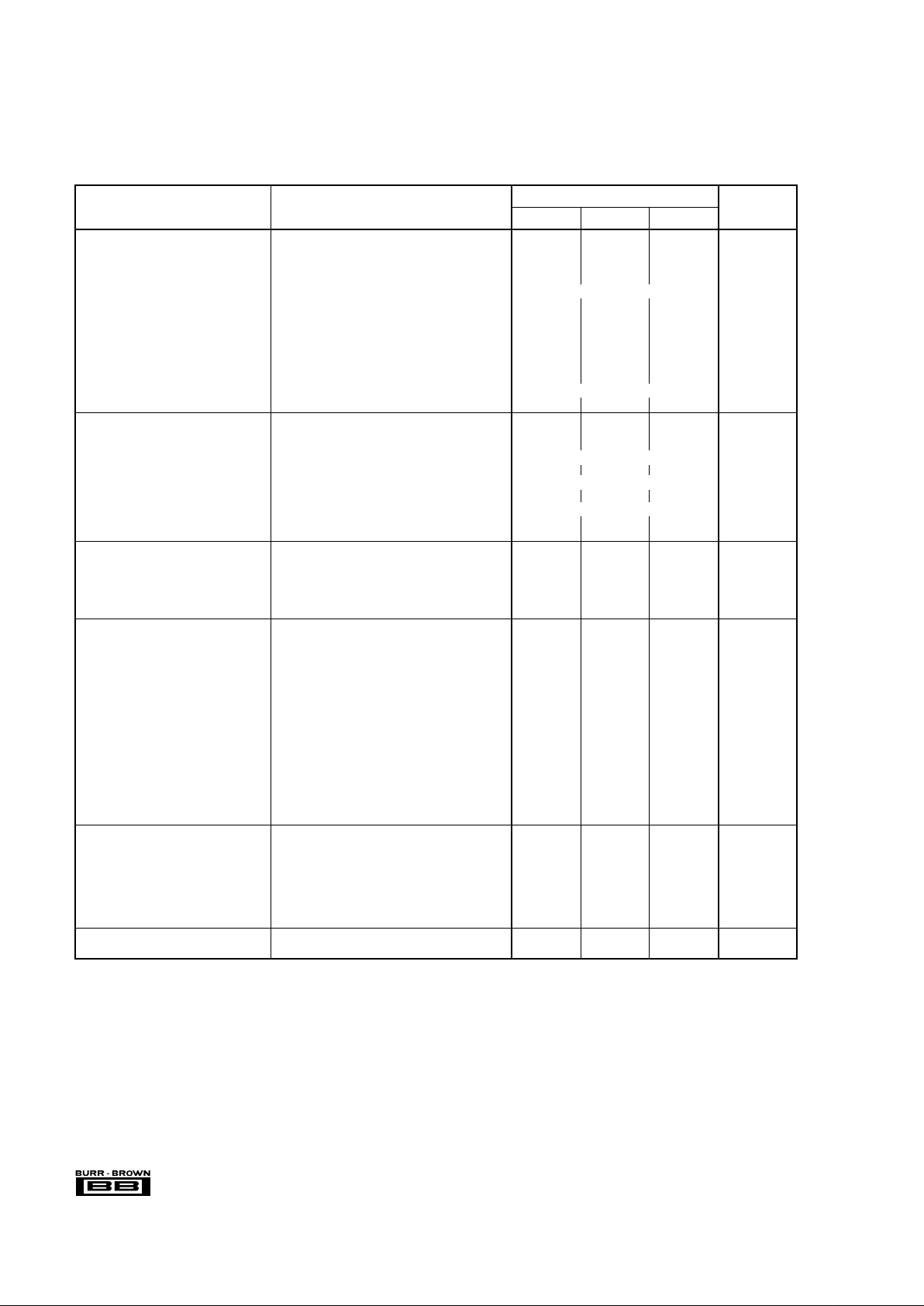

SPECIFICATIONS

Typical at 25°C, AVDD = +5V, DVDD = +3.3V, ftx = 584kHz (E1 rate), unless otherwise specified.

AFE1104E

PARAMETER COMMENTS MIN TYP MAX UNITS

RECEIVE CHANNEL

Number of Inputs Differential 2

Input Voltage Range Balanced Differential

(1)

±3.0 V

Common-Mode Voltage 1.5V CMV Recommended +1.5 V

Input Impedance All Inputs See Typical Performance Curves

Input Capacitance 10 pF

Input Gain Matching Line Input vs Hybrid Input ±2%

Resolution 14 Bits

Programmable Gain Four Gains: 0dB, 3.25dB, 6dB, and 9dB 0 9 dB

Settling Time for Gain Change 6 Symbol

Periods

Gain + Offset Error Tested at Each Gain Range 5 %FSR

(2)

Output Data Coding Two’s Complement

Output Data Rate, rxSYNC

(3)

98 584 kHz

TRANSMIT CHANNEL

Transmit Symbol Rate, f

tx

98 584 kHz

T1 Transmit –3dB Point Bellcore TA-NWT-3017 Compliant 196 kHz

T1 Rate Power Spectral Density

(4)

See Typical Performance Curves

E1 Transmit –3dB Point ETSI RTR/TM-03036 Compliant 292 kHz

E1 Rate Power Spectral Density

(4)

See Typical Performance Curves

Transmit Power

(4, 5)

13 14 dBm

Pulse Output See Typical Performance Curves

Common-Mode Voltage, V

CM

AVDD/2 V

Output Resistance

(6)

DC to 1MHz 1 Ω

TRANSCEIVER PERFORMANCE

Uncanceled Echo

(7)

rxGAIN = 0dB, Loopback Enabled –67 dB

rxGAIN = 0dB, Loopback Disabled –67 dB

rxGAIN = 3.25dB, Loopback Disabled –69 dB

rxGAIN = 6dB, Loopback Disabled –71 dB

rxGAIN = 9dB, Loopback Disabled –73 dB

DIGITAL INTERFACE

(6)

Logic Levels

V

IH

|IIH| < 10µADV

DD

–1 DVDD +0.3 V

V

IL

|IIL| < 10µA –0.3 +0.8 V

V

OH

IOH = –20µADV

DD

–0.5 V

V

OL

IOL = 20µA +0.4 V

Receive Channel Interface

t

rx1

rxCLK Period 35 215 ns

rxCLK Duty Cycle 45 55 %

t

rx2

rxSYNC to rxCLK Setup Time 10 ns

t

rx3

rxCLK to rxSYNC Hold Time 10 ns

t

rx4

rxCLK to rxD13 - rxD0 Delay 50 ns

Transmit Channel Interface

t

tx1

txCLK Period 1.7 10.2 µs

t

tx2

txCLK Pulse Width 50 ns

t

tx3

Basic txDAT Pulse Unit t

tx1

/96 ns

POWER

Analog Power Supply Voltage Specification 5 V

Analog Power Supply Voltage Operating Range 4.75 5.25 V

Digital Power Supply Voltage Specification 3.3 V

Digital Power Supply Voltage Operating Range 3.15 5.25 V

Power Dissipation

(4, 5, 8)

DVDD = 3.3V 250 mW

Power Dissipation

(4, 5, 8)

DVDD = 5V 300 mW

PSRR 60 dB

TEMPERATURE RANGE

Operating

(6)

–40 +85 °C

NOTES: (1) With a balanced differential signal, the positive input is 180° out of phase with the negative input, therefore the actual voltage swing about the common

mode voltage on each pin is ±1.5V to achieve a differential input range of ±3.0V or 6Vp-p. (2) FSR is Full-Scale Range. (3) The output data is available at twice the

symbol rate with interpolated values. (4) With a pseudo-random equiprobable sequence of HDSL pulses; 13.5dBm applied to the transformer (27dBm output from

txLINE

P

and txLINEN). (5) See the Discussion of Specifications section of this data sheet for more information. (6) Guaranteed by design and characterization. (7)

Uncanceled Echo is a measure of the total analog errors in the transmitter and receiver sections including the effect of non-linearity and noise. See the Discussion

of Specifications section of this data sheet for more information. (8) Power dissipation includes only the power dissipated within the component and does not include

power dissipated in the external loads. See the Discussion of Specifications section for more information.

®

AFE1104

3

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN

assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject

to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not

authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

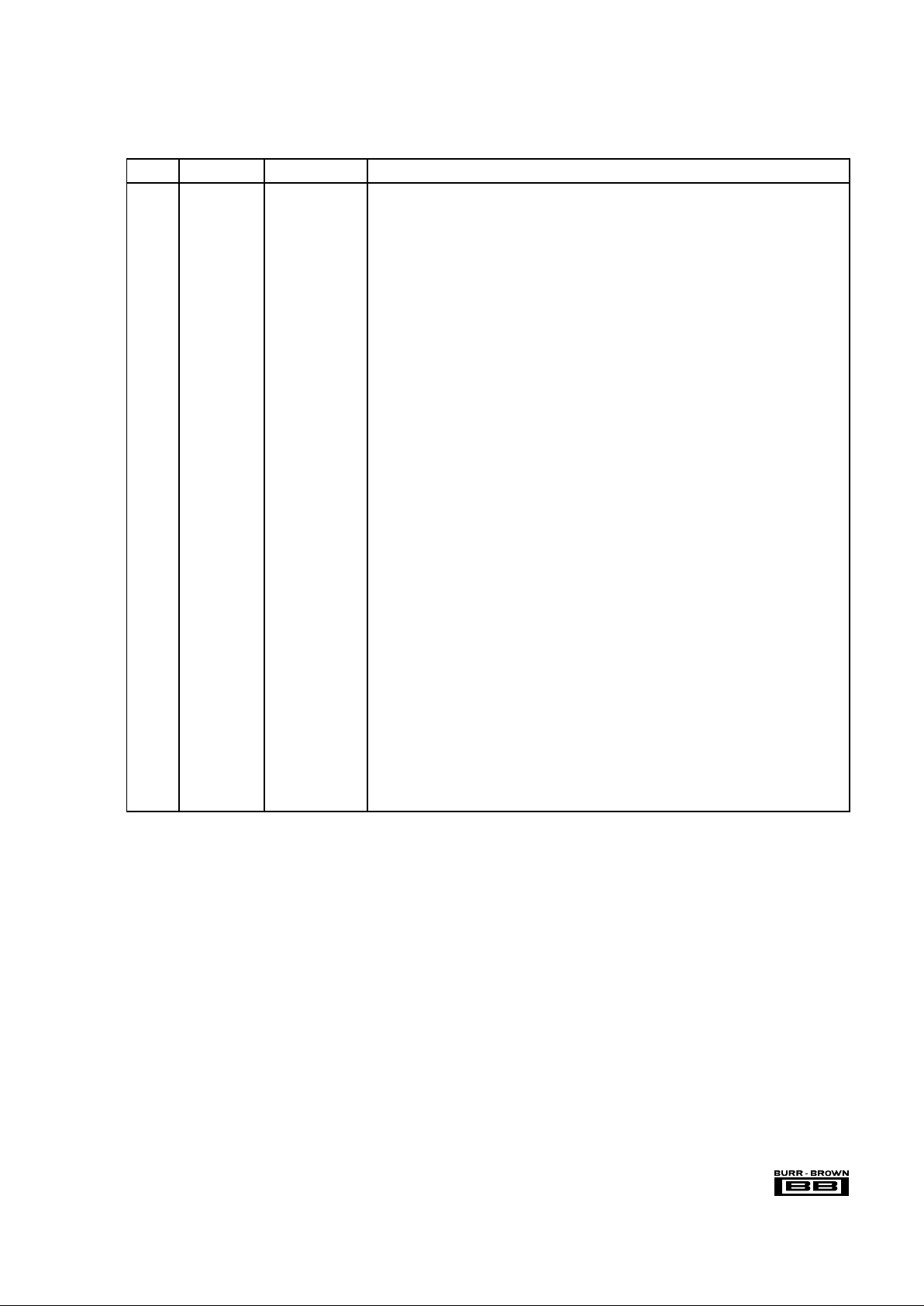

PIN DESCRIPTIONS

PIN # TYPE NAME DESCRIPTION

1 Ground PGND Analog Ground for PLL

2 Power PV

DD

Analog Supply (+5V) for PLL

3 Input txCLK Transmit Symbol Clock (392kHz for T1, 584kHz for E1)

4 Ground DGND Digital Ground

5 Input txDAT DAC+ Line from SPAROW

6 Output rxD0 ADC Output Bit-0

7 Output rxD1 ADC Output Bit-1

8 Output rxD2 ADC Output Bit-2

9 Output rxD3 ADC Output Bit-3

10 Output rxD4 ADC Output Bit-4

11 Output rxD5 ADC Output Bit-5

12 Ground DGND Digital Ground

13 Power DV

DD

Digital Supply (+3.3V to +5V)

14 Output rxD6 ADC Output Bit-6

15 Output rxD7 ADC Output Bit-7

16 Output rxD8 ADC Output Bit-8

17 Output rxD9 ADC Output Bit-9

18 Output rxD10 ADC Output Bit-10

19 Output rxD11 ADC Output Bit-11

20 Output rxD12 ADC Output Bit-12

21 Output rxD13 ADC Output Bit-13

22 Input rxCLK A/D Clock (18.816MHz for T1, 28.03MHz for E1)

23 Input rxSYNC ADC Sync Signal (392kHz for T1, 584kHz for E1)

24 Input rxGAIN0 Receive Gain Control Bit-0

25 Input rxGAIN1 Receive Gain Control Bit-1

26 Input rxLOOP Loopback Control Signal (loopback is enabled by positive signal)

27 Power AV

DD

Analog Supply (+5V)

28 Input rxHYB

N

Negative Input from Hybrid Network

29 Input rxHYB

P

Positive Input from Hybrid Network

30 Input rxLINE

N

Negative Line Input

31 Input rxLINE

P

Positive Line Input

32 Ground AGND Analog Ground

33 Ground AGND Analog Ground

34 Output REF

P

Positive Reference Output, Nominally 3.5V

35 Output V

CM

Common-Mode Voltage (buffered), Nominally 2.5V

36 Output REF

N

Negative Reference Output, Nominally 1.5V

37 Power AV

DD

Analog Supply (+5V)

38 Ground AGND Analog Ground

39 Output txLINE

N

Transmit Line Output Negative

40 Power AV

DD

Analog Supply (+5V)

41 Output txLINE

P

Transmit Line Output Positive

42 Ground AGND Analog Ground

43 NC NC Connection to Ground Recommended

44 NC NC Connection to Ground Recommended

45 NC NC Connection to Ground Recommended

46 NC NC Connection to Ground Recommended

47 Output PLL

OUT

PLL Filter Output

48 Input PLL

IN

PLL Filter Input

Loading...

Loading...