Burr Brown Corporation ADS825E-1K, ADS825E, ADS822E-1K, ADS822 Datasheet

®

For most current data sheet and other product

information, visit www.burr-brown.com

ADS822

ADS825

ADS822

ADS825

10-Bit, 40MHz Sampling

TM

ANALOG-TO-DIGITAL CONVERTERS

FEA TURES

● HIGH SNR: 60dB

● HIGH SFDR: 72dBFS

● LOW POWER: 190mW

● INTERNAL/EXTERNAL REFERENCE OPTION

● SINGLE-ENDED OR

FULLY DIFFERENTIAL ANALOG INPUT

● PROGRAMMABLE INPUT RANGE

● LOW DNL: 0.5LSB

● SINGLE +5V SUPPLY OPERATION

DESCRIPTION

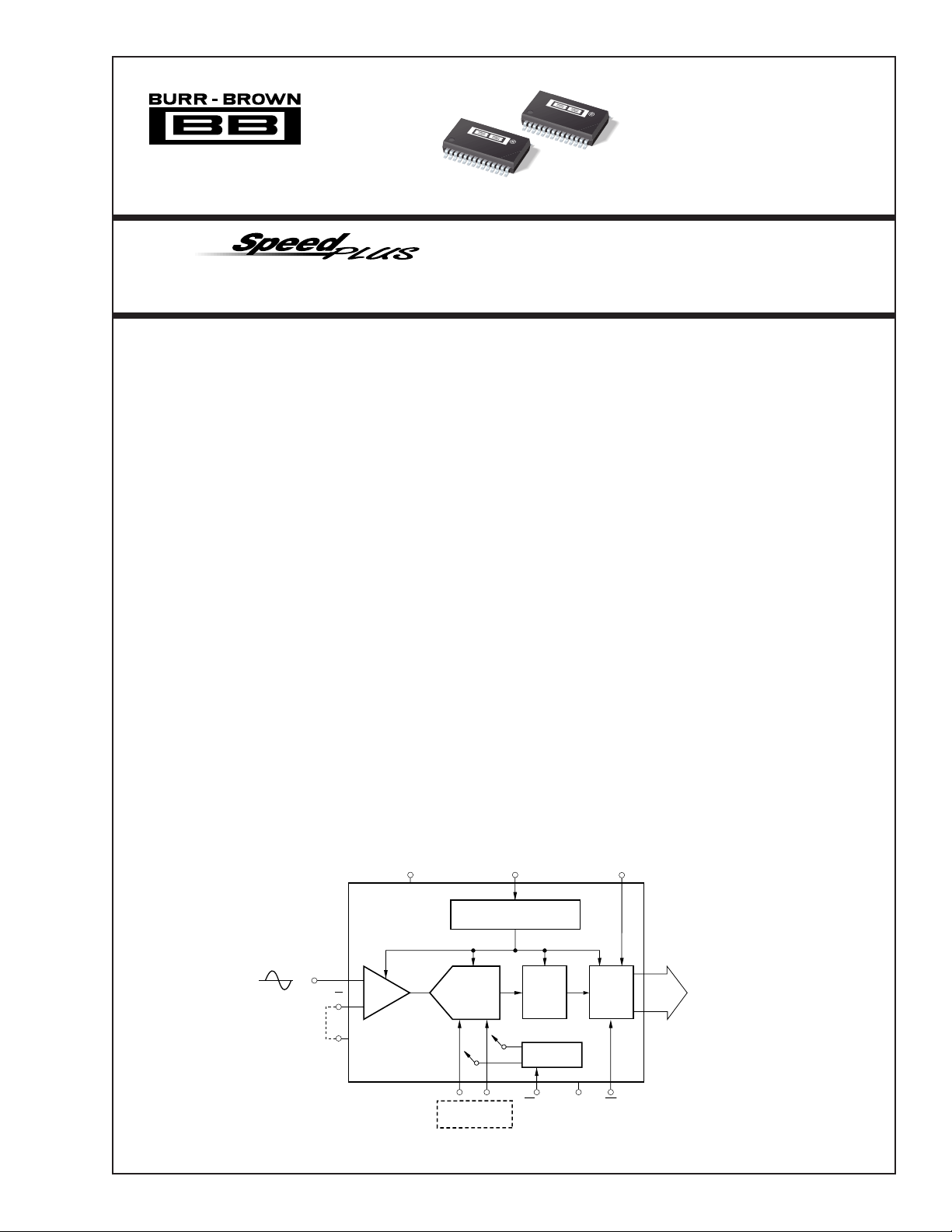

The ADS822 and ADS825 are pipeline, CMOS analog-to-digital

converters that operate from a single +5V power supply. These

converters provide excellent performance with a single-ended

input and can be operated with a differential input for added

spurious performance. These high-performance converters include a 10-bit quantizer, high-bandwidth track-and-hold, and a

high-accuracy internal reference. They also allow for the user to

disable the internal reference and utilize external references. This

external reference option provides excellent gain and offset

matching when used in multi-channel applications or in applications where full-scale range adjustment is required.

●

+3V OR +5V LOGIC I/O COMPATIBLE (ADS825)

● POWER DOWN: 20mW

● 28-LEAD SSOP PACKAGE

APPLICATIONS

● MEDICAL IMAGING

● TEST EQUIPMENT

● COMPUTER SCANNERS

● COMMUNICATIONS

● VIDEO DIGITIZING

The ADS822 and ADS825 employ digital error correction techniques to provide excellent differential linearity for demanding

imaging applications. Its low distortion and high SNR give the

extra margin needed for medical imaging, communications,

video, and test instrumentation. The ADS822 and ADS825 offer

power dissipation of 190mW and also provide a power-down

mode, thus reducing power dissipation to only 20mW. The

ADS825 is +3V or +5V Logic I/O compatible.

The ADS822 and ADS825 are specified at a maximum sampling

frequency of 40MHz and a single-ended input range of 1.5V to

3.5V. The ADS822 and ADS825 are available in a 28-lead SSOP

package and are pin-for-pin compatible with the 10-bit, 60MHz

ADS823 and ADS826, and the 10-bit, 70MHz ADS824, providing an upgrade path to higher sampling frequencies.

+V

S

ADS822

ADS825

IN

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111

Twx: 910-952-1111 • Internet: http://www.burr-brown.com/ • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

©

1997 Burr-Brown Corporation PDS-1385E Printed in U.S.A. October, 1999

INV

CM

T/H

IN

Pipelined

A/D Core

Optional External

Reference

CLK VDRV

Timing

Circuitry

10-Bit

Correction

Reference

Error

Logic

Internal

3-State

Outputs

OEPDInt/Ext

D0

•

•

•

D9

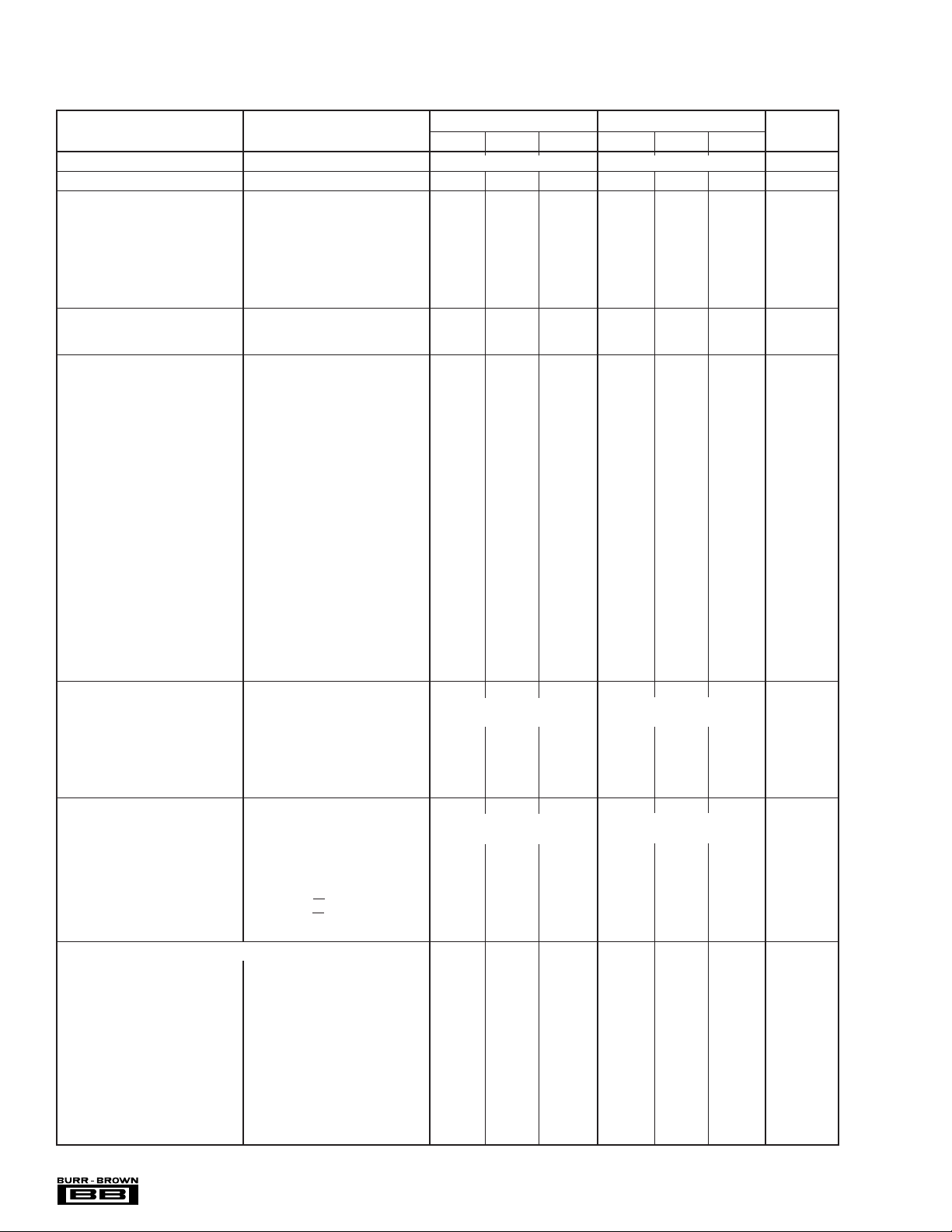

SPECIFICATIONS

At TA = full specified temperature range, VS = +5V, single-ended input range = 1.5V to 3.5V, and sampling rate = 40MHz, external reference, unless otherwise noted.

ADS822E ADS825E

PARAMETER CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

RESOLUTION 10 Guaranteed 10 Guaranteed Bits

SPECIFIED TEMPERATURE RANGE Ambient Air –40 to +85 –40 to +85 °C

ANALOG INPUT

Standard Single-Ended Input Range 2Vp-p 1.5 3.5 ✻✻V

Optional Single-Ended Input Range 1Vp-p 2 3 ✻✻V

Common-Mode Range 2.5 ✻ V

Optional Differential Input Range 2Vp-p 2 3 ✻✻V

Analog Input Bias Current 1 ✻ µA

Input Impedance 1.25 || 5 ✻ MΩ || pF

Track-Mode Input Bandwidth –3dBFS Input 300 ✻ MHz

CONVERSION CHARACTERISTICS

Sample Rate 10k 40M ✻✻Samples/s

Data Latency 5 ✻ Clk Cyc

DYNAMIC CHARACTERISTICS

Differential Linearity Error

(largest code error)

f = 1MHz ±0.25 ±1.0 ✻✻ LSB

f = 10MHz ±0.5 ✻ LSB

No Missing Codes Guaranteed Guaranteed

Integral Nonlinearity Error, f = 1MHz ±0.5 ±2.0 ✻✻ LSBs

Spurious Free Dynamic Range

(2)

Referred to Full Scale

f = 1MHz 72 71 dBFS

f = 10MHz 63 66 60 65 dBFS

Two-Tone Intermodulation Distortion

(4)

f = 9.5MHz and 9.9MHz (–7dB each tone) –67 ✻ dBc

Signal-to-Noise Ratio (SNR) Referred to Full Scale

f = 1MHz 60 ✻ dB

f = 10MHz 57 60 ✻✻ dB

Signal-to-(Noise + Distortion) (SINAD) Referred to Full Scale

f = 1MHz 59 ✻ dB

f = 10MHz 56 58 ✻✻ dB

Effective Number of Bits

(5)

, f = 1MHz 9.5 ✻ Bits

Output Noise Input Tied to Common-Mode 0.2 ✻ LSBs rms

Aperture Delay Time 3 ✻ ns

Aperture Jitter 1.2 ✻ ps rms

Overvoltage Recovery Time 2 ✻ ns

Full-Scale Step Acquisition Time 5 ✻ ns

DIGITAL INPUTS

Logic Family

Convert Command Start Conversion

High Level Input Current

Low Level Input Current (V

High Level Input Voltage +3.5 +2.0 V

(6)

(VIN = 5VDD) 100 ✻ µA

= 0V) 10 ✻ µA

IN

CMOS-Compatible

Rising Edge of Convert Clock

TTL, +3V/+5V CMOS-Compatible

Rising Edge of Convert Clock

Low Level Input Voltage +1.0 +0.8 V

Input Capacitance 5 ✻ pF

DIGITAL OUTPUTS

Logic Family

Logic Coding

Low Output Voltage (I

High Output Voltage, (I

Low Output Voltage, (I

High Output Voltage, (I

3-State Enable Time OE = H to L 2 40 ✻✻ ns

= 50µA to 1.6mA) VDRV = 5V +0.1 ✻ V

OL

= 50µA to 0.5mA) +4.9 ✻ V

OH

= 50µA to 1.6mA) VDRV = 3V +0.1 ✻ V

OL

= 50µA to 0.5mA) +2.8 ✻ V

OH

CMOS-Compatible

Straight Offset Binary

CMOS-Compatible

Straight Offset Binary

3-State Disable Time OE = L to H 2 10 ✻✻ ns

Output Capacitance 5 ✻ pF

ACCURACY (Internal Reference, 2Vp-p, Unless Otherwise Noted)

Zero Error (referred to –FS) at 25°C ±1.0 ±3.0 ✻✻ % FS

Zero Error Drift (referred to –FS) 5 ✻ ppm/°C

Midscale Offset Error at 25°C ±0.29 % FS

(7)

Gain Error

Gain Error Drift

Gain Error

Gain Error Drift

(7)

(8)

(8)

Power Supply Rejection of Gain ∆ V

REFT Tolerance Deviation From Ideal 3.5V ±10 ±25 ✻✻ mV

at 25°C ±1.5 ±2.5 ✻✻ % FS

38 ✻ ppm/°C

at 25°C ±0.75 ±1.5 ✻✻ % FS

25 ✻ ppm/°C

= ±5% 70 ✻ dB

S

REFB Tolerance Deviation From Ideal 1.5V ±10 ±25 ✻✻ mV

External REFT Voltage Range REFB + 0.8 3.5 V

External REFB Voltage Range 1.25 1.5 REFT – 0.8 ✻✻✻ V

– 1.25 ✻✻✻ V

S

Reference Input Resistance REFT to REFB 1.6 ✻ kΩ

(1)

(3)

®

ADS822, ADS825

2

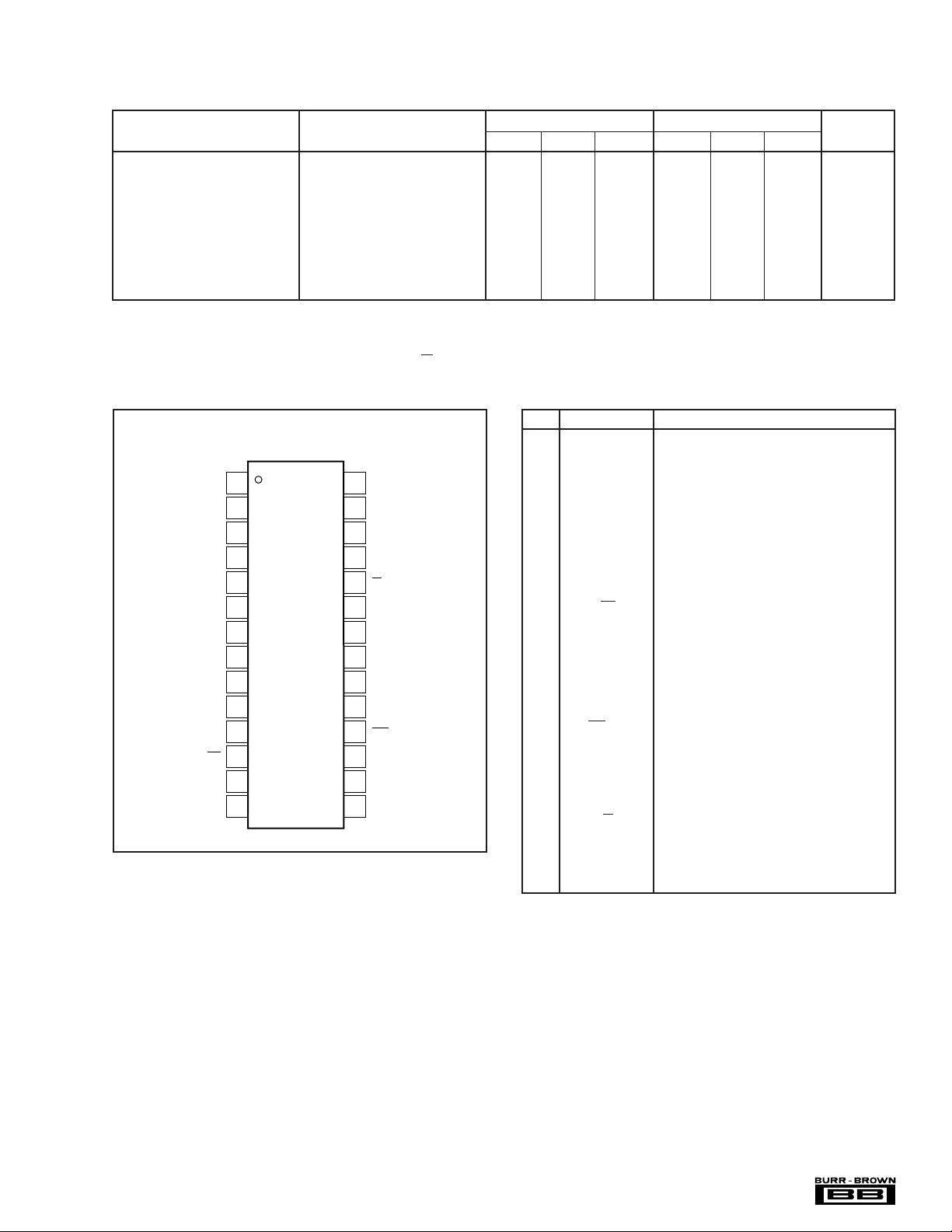

SPECIFICATIONS (Cont.)

At TA = full specified temperature range, VS = +5V, single-ended input range = 1.5V to 3.5V, and sampling rate = 40MHz, external reference, unless otherwise noted.

ADS822E ADS825E

PARAMETER CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

POWER SUPPLY REQUIREMENTS

Supply Voltage: +V

Supply Current: +I

Power Dissipation: VDRV = 5V External Reference 200 230 ✻✻ mW

VDRV = 3V External Reference 190 ✻ mW

VDRV = 5V Internal Reference 250 ✻ mW

VDRV = 3V Internal Reference 240 ✻ mW

Power Down Operating 20 ✻ mW

Thermal Resistance,

28-Lead SSOP 89 ✻ °C/W

✻ Indicates the same specifications as the ADS822E.

NOTES: (1) ADS825E accepts a +3V clock input. (2) Spurious Free Dynamic Range refers to the magnitude of the largest harmonic. (3) dBFS means dB relative to Full Scale. (4) Two-tone intermodulation

distortion is referred to the largest fundamental tone. This number will be 6dB higher if it is referred to the magnitude of the two-tone fundamental envelope. (5) Effective number of bits (ENOB) is defined

by (SINAD – 1.76) /6.02. (6) A 50kΩ pull-down resistor is inserted internally on OE pin. (7) Includes internal reference. (8) Excludes internal reference.

S

S

θ

JA

Operating +4.75 +5.0 +5.25 ✻✻✻ V

Operating (External Reference) 40 ✻ mA

(1)

PIN CONFIGURATION

Top View SSOP

GND

Bit 1 (MSB)

Bit 2

Bit 3

Bit 4

Bit 5

Bit 6

Bit 7

Bit 8

Bit 9

Bit 10 (LSB)

OE

PD

CLK

1

2

3

4

5

6

7

ADS822

ADS825

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VDRV

+V

S

GND

IN

IN

CM

REFT

ByT

ByB

REFB

INT/EXT

RSEL

GND

+V

S

PIN DESCRIPTIONS

PIN DESIGNATOR DESCRIPTION

1 GND Ground

2 Bit 1 Data Bit 1 (D9) (MSB)

3 Bit 2 Data Bit 2 (D8)

4 Bit 3 Data Bit 3 (D7)

5 Bit 4 Data Bit 4 (D6)

6 Bit 5 Data Bit 5 (D5)

7 Bit 6 Data Bit 6 (D4)

8 Bit 7 Data Bit 7 (D3)

9 Bit 8 Data Bit 8 (D2)

10 Bit 9 Data Bit 9 (D1)

11 Bit 10 Data Bit 10 (D0) (LSB)

12 OE Output Enable. HI = high impedance state

13 PD Power Down. HI = enable; LO = disable

14 CLK Convert Clock Input

15 +V

16 GND Ground

17 RSEL Input Range Select. HI = 2V; LO = 1V

18 INT/EXT

19 REFB Bottom Reference

20 ByB Bottom Ladder Bypass

21 ByT Top Ladder Bypass

22 REFT Top Reference

23 CM Common-Mode Voltage Output

24 IN Complementary Input (–)

25 IN Analog Input (+)

26 GND Analog Ground

27 +V

28 VDRV Output Logic Driver Supply Voltage

S

S

LO = normal operation (internal pull-down

resistor)

+5V Supply

Reference Select. HI = external, LO = internal

+5V Supply

®

3

ADS822, ADS825

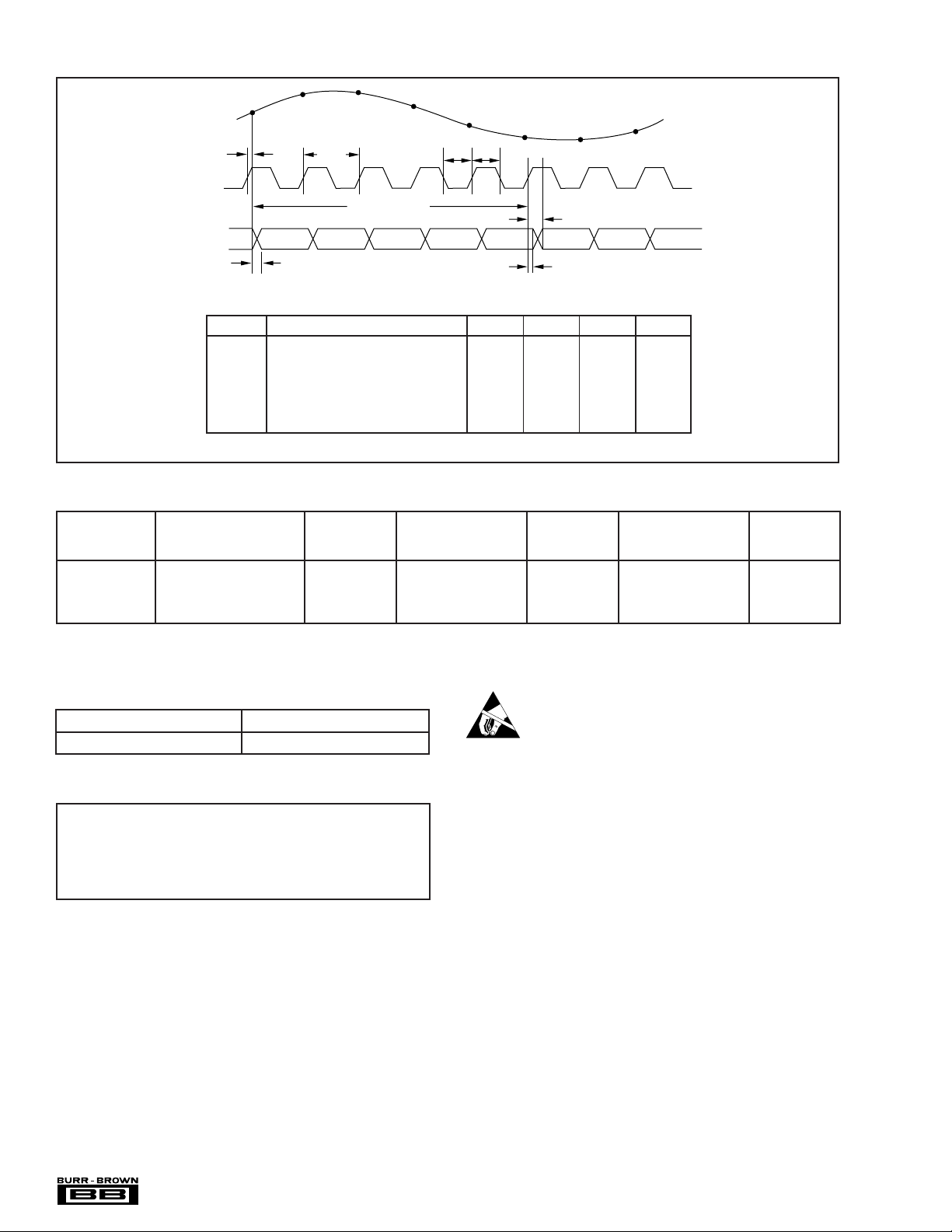

TIMING DIAGRAM

Analog In

N

Clock

SYMBOL DESCRIPTION MIN TYP MAX UNITS

t

CONV

t

L

t

H

t

D

t

1

t

2

N+1

t

D

N–5 N–4 N–3 N–2 N–1 N N+1 N+2Data Out

Data Invalid

New Data Delay Time, CL = 15pF max 12 ns

N+2

t

CONV

5 Clock Cycles

Convert Clock Period 25 100µsns

Clock Pulse Low 11.5 12.5 ns

Clock Pulse High 11.5 12.5 ns

Aperture Delay 3 ns

Data Hold Time, CL = 0pF 3.9 ns

N+3

N+4

tLt

N+5

H

N+6

t

2

t

1

N+7

PACKAGE/ORDERING INFORMATION

PACKAGE SPECIFIED

PRODUCT PACKAGE NUMBER RANGE MARKING NUMBER

DRAWING TEMPERATURE PACKAGE ORDERING TRANSPORT

ADS822E SSOP-28 324 –40°C to +85°C ADS822E ADS822E Rails

" " " " " ADS822E/1K Tape and Reel

ADS825E SSOP-28 324 –40°C to +85°C ADS825E ADS825E Rails

" " " " " ADS825E/1K Tape and Reel

NOTE: (1) Models with a slash (/) are available only in Tape and Reel in the quantities indicated (e.g., /1K indicates 1000 devices per reel). Ordering 1000 pieces

of ADS822E/1K” will get a single 1000-piece Tape and Reel.

(1)

MEDIA

DEMO BOARD ORDERING INFORMATION

PRODUCT DEMO BOARD

ADS822E DEM-ADS822E

ELECTROSTATIC

DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown

ABSOLUTE MAXIMUM RATINGS

+VS....................................................................................................... +6V

Analog Input............................................................. –0.3V to (+V

Logic Input ...............................................................–0.3V to (+V

Case Temperature ......................................................................... +100°C

Junction Temperature .................................................................... +150°C

Storage Temperature..................................................................... +150°C

+ 0.3V)

S

+ 0.3V)

S

recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling

and installation procedures can cause damage.

ESD damage can range from subtle performance degradation

to complete device failure. Precision integrated circuits may

be more susceptible to damage because very small parametric

changes could cause the device not to meet its published

specifications.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility

for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject to change without notice. No patent rights

or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life

support devices and/or systems.

®

ADS822, ADS825

4

Loading...

Loading...