Burr Brown Corporation ADS7809UB-1K, ADS7809UB, ADS7809U-1K, ADS7809U, ADS7809PB Datasheet

...

©

1992 Burr-Brown Corporation PDS-1154D Printed in U.S.A., November, 1996

ADS7809

ADS7809

®

ADS7809

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111

Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

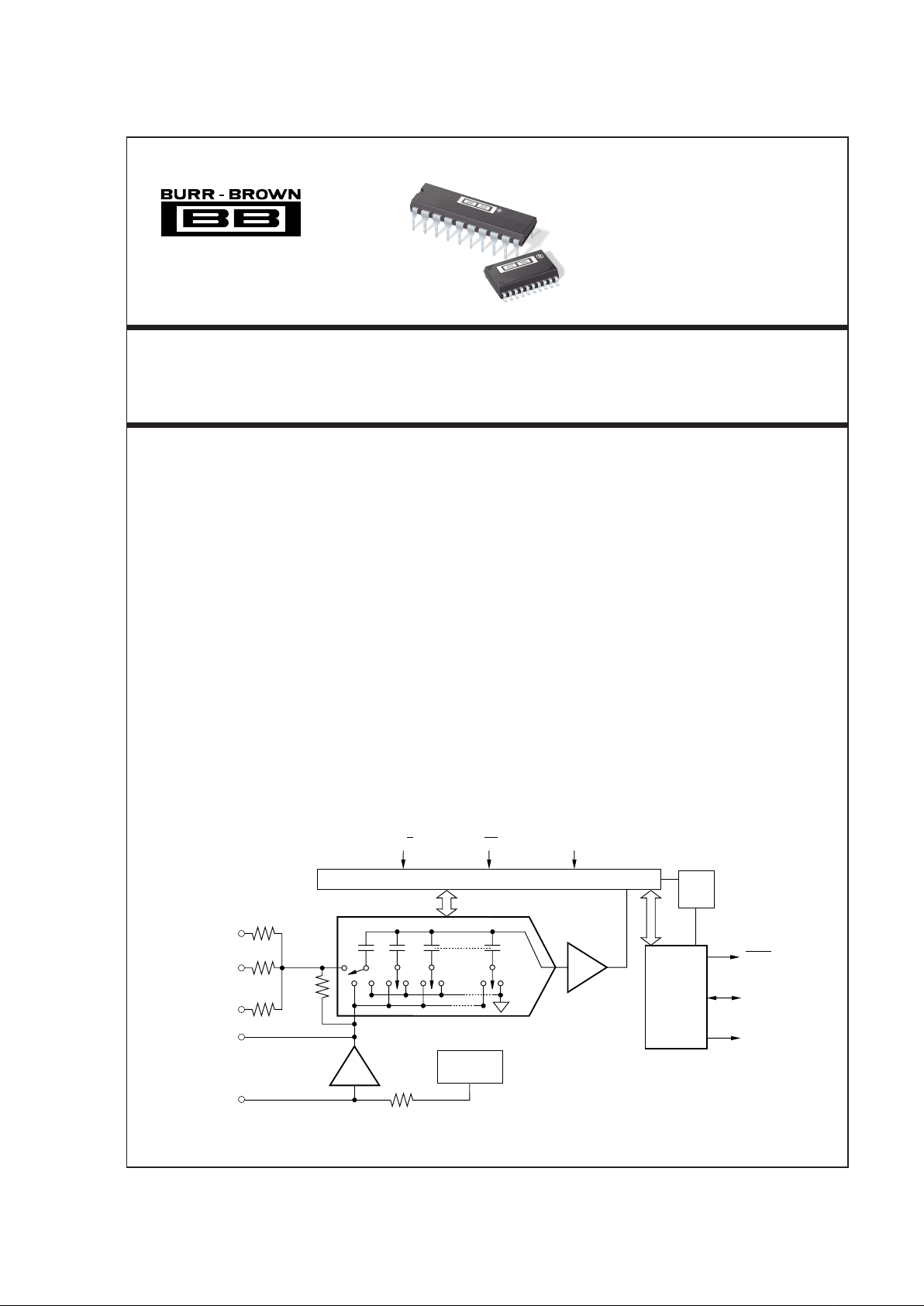

16-Bit 10µs Serial CMOS Sampling

ANALOG-to-DIGITAL CONVERTER

FEATURES

● 100kHz SAMPLING RATE

● 86dB SINAD WITH 20kHz INPUT

●

±2 LSB INL

● DNL: 16 BITS “No Missing Codes”

● SIX SPECIFIED INPUT RANGES

● SERIAL OUTPUT

● SINGLE +5V SUPPLY OPERATION

● PIN-COMPATIBLE WITH 12-BIT ADS7808

● USES INTERNAL OR EXTERNAL

REFERENCE

● 100mW MAX POWER DISSIPATION

● 20-PIN 0.3" PLASTIC DIP AND SOIC

● SIMPLE DSP INTERFACE

DESCRIPTION

The ADS7809 is a complete 16-bit sampling analogto-digital using state-of-the-art CMOS structures. It

contains a 16-bit capacitor-based SAR A/D with S/H,

reference, clock, and a serial data interface. Data can

be output using the internal clock, or can be synchronized to an external data clock. The ADS7809 also

provides an output synchronization pulse for ease of

use with standard DSP processors.

The ADS7809 is specified at a 100kHz sampling rate,

and guaranteed over the full temperature range. Lasertrimmed scaling resistors provide various input ranges

including ±10V and 0V to 5V, while an innovative

design operates from a single +5V supply, with power

dissipation under 100mW.

The 20-pin ADS7809 is available in a plastic 0.3" DIP

and in an SOIC, both fully specified for operation over

the industrial –40°C to +85°C range.

10kΩ

CDAC

4kΩ

20kΩ

5kΩ

Internal

+2.5V Ref

Clock

BUSY

Data Clock

Serial Data

Successive Approximation Register and Control Logic

Serial

Data

Out

Comparator

Buffer

20kΩ

R/C CS

Power

Down

R1

IN

R2

IN

R3

IN

REF

CAP

DEMO BOARD

AVAILABLE

®

ADS7809

2

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN

assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject

to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not

authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

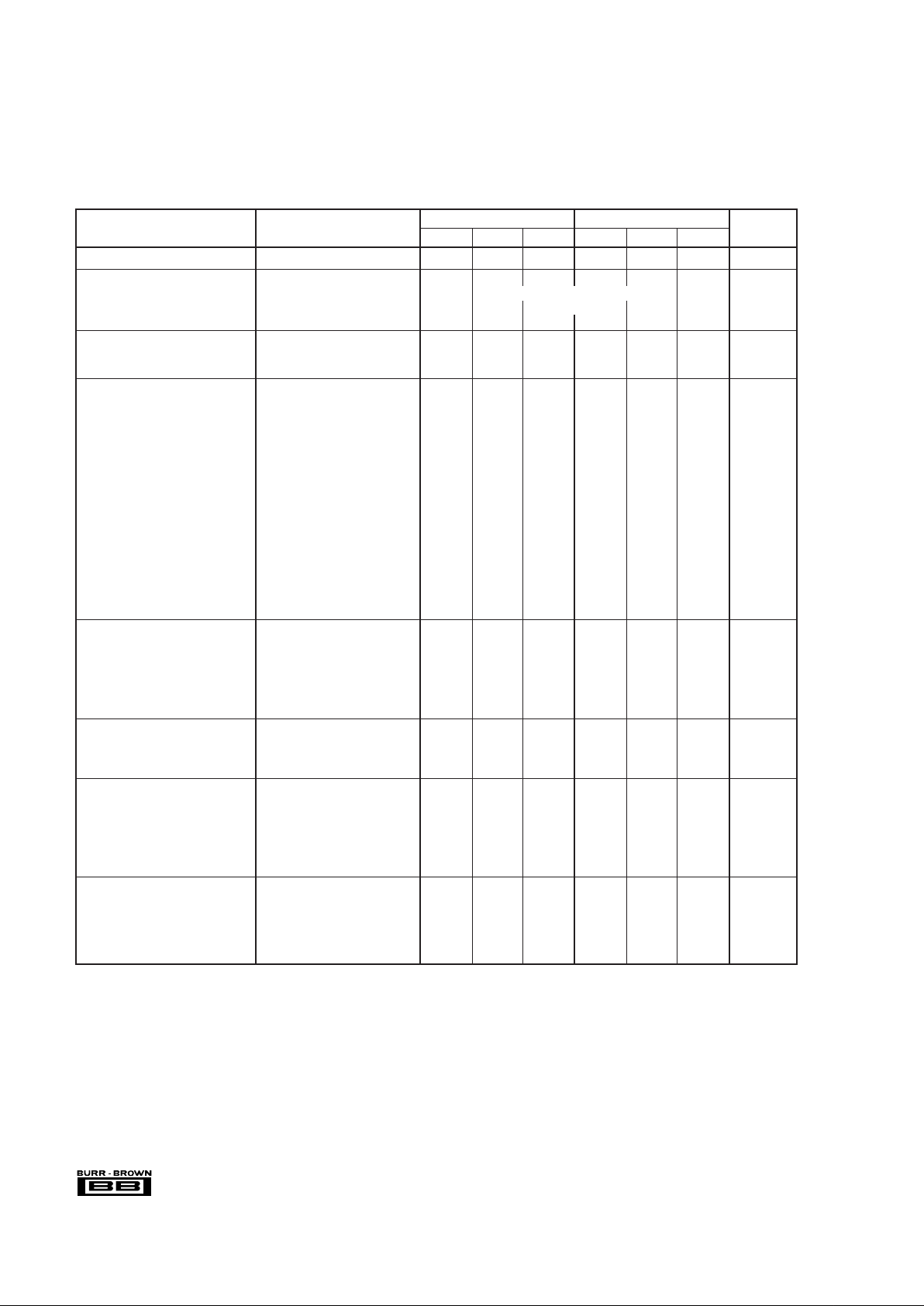

SPECIFICATIONS

ELECTRICAL

At TA = –40°C to +85°C, fS = 100kHz, V

DIG

= V

ANA

= +5V, using internal reference and fixed resistors as shown in Figure 4, unless otherwise specified.

ADS7809P, U ADS7809PB, UB

PARAMETER CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

RESOLUTION 16 ✻ Bits

ANALOG INPUT

Voltage Ranges ±10, 0V to 5V, etc. (See Table I)

Impedance See Table I

Capacitance 35 ✻ pF

THROUGHPUT SPEED

Complete Cycle Acquire and Convert 10 ✻ µs

Throughput Rate 100 ✻ kHz

DC ACCURACY

Integral Linearity Error ±3 ±2 LSB

(1)

Differential Linearity Error +3, –2 ±1 LSB

No Missing Codes 15 16 Bits

Transition Noise

(2)

1.3 ✻ LSB

Full Scale Error

(3,4)

±0.5 ✻ %

Full Scale Error Drift ±7 ✻ ppm/°C

Full Scale Error

(3,4)

Ext. 2.5000V Ref ±0.5 ✻ %

Full Scale Error Drift Ext. 2.5000V Ref ±2 ✻ ppm/°C

Bipolar Zero Error

(3)

Bipolar Ranges ±10 ✻ mV

Bipolar Zero Error Drift Bipolar Ranges ±2 ✻ ppm/°C

Unipolar Zero Error

(3)

0V tp 10V Ranges ±5 ✻ mV

Unipolar Zero Error

(3)

0V to 4V, 0V to 5V Ranges ±3 ✻ mV

Unipolar Zero Error Drift Unipolar Ranges ± 2 ✻ ppm/°C

Recovery to Rated Accuracy 1µF Capacitor to CAP 1 ✻ ms

after Power Down

Power Supply Sensitivity +4.75V < V

D

< +5.25V ±8 ✻ LSB

(V

DIG

= V

ANA

= VD)

AC ACCURACY

Spurious-Free Dynamic Range f

IN

= 20kHz 90 100 96 ✻ dB

(5)

Total Harmonic Distortion f

IN

= 20kHz –100 –90 ✻ –94 dB

Signal-to-(Noise+Distortion) f

IN

= 20kHz 83 88 86 ✻ dB

–60dB Input 30 32 dB

Signal-to-Noise f

IN

= 20kHz 83 88 86 ✻ dB

Full-Power Bandwidth

(6)

250 ✻ kHz

SAMPLING DYNAMICS

Aperture Delay 40 ✻ ns

Transient Response FS Step 2 ✻ µs

Overvoltage Recovery

(7)

150 ✻ ns

REFERENCE

Internal Reference Voltage No Load 2.48 2.5 2.52 ✻✻✻ V

Internal Reference Source Current 1 ✻ µA

(Must use external buffer)

External Reference Voltage Range 2.3 2.5 2.7 ✻✻✻ V

For Specified Linearity

External Reference Current Drain Ext. 2.5000V Ref 100 ✻ µA

DIGITAL INPUTS

Logic Levels

V

IL

–0.3 +0.8 ✻✻V

V

IH

+2.0 VD +0.3V ✻✻V

I

IL

VIL = 0V ±10 ✻ µA

I

IH

VIH = 5V ±10 ✻ µA

®

ADS7809

3

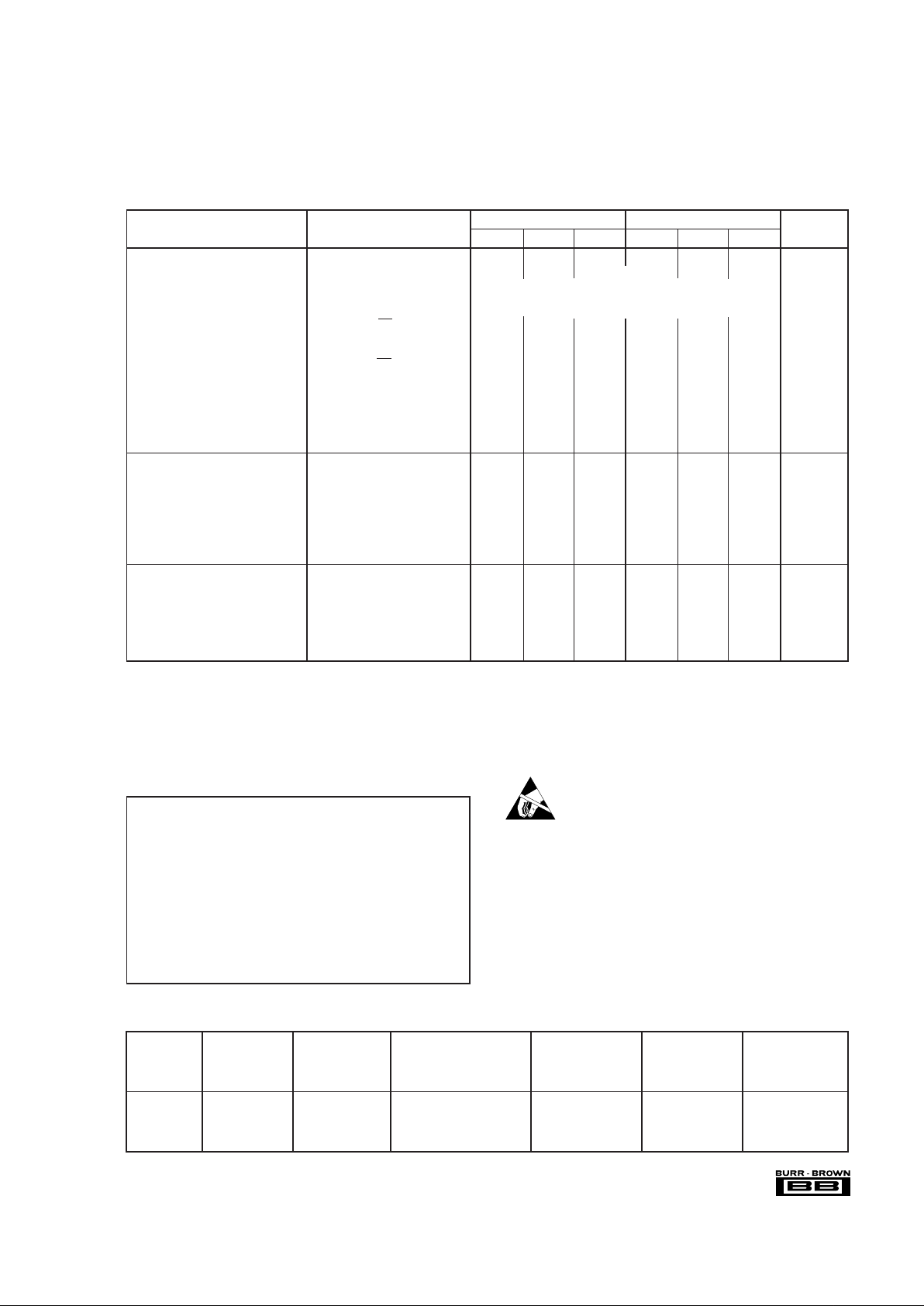

SPECIFICATIONS (CONT)

ELECTRICAL

At TA = –40°C to +85°C, fS = 100kHz, V

DIG

= V

ANA

= +5V, using internal reference and fixed resistors as shown in Figure 4, unless otherwise specified.

ADS7809P, U ADS7809PB, UB

PARAMETER CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

DIGITAL OUTPUTS

Data Format Serial 16 bits

Data Co Binary Two’s Complement or Straight Binary

Pipeline Delay Conversion results only available after completed conversion.

Data Clock Selectable for internal or external data clock

Internal EXT/INT LOW 2.3 ✻ MHz

(Output Only When

Transmitting Data)

External EXT/INT HIGH 0.1 10 ✻✻MHz

(Can Run Continually)

V

OL

I

SINK

= 1.6mA +0.4 ✻ V

V

OH

I

SOURCE

= 500µA+4 ✻ V

Leakage Current High-Z State, ±5 ✻ µA

V

OUT

= 0V to V

DIG

Output Capacitance High-Z State 15 ✻ pF

POWER SUPPLIES

Specified Performance

V

DIG

Must be ≤ V

ANA

+4.75 +5 +5.25 ✻✻✻ V

V

ANA

+4.75 +5 +5.25 ✻✻✻ V

I

DIG

0.3 ✻ mA

I

ANA

16 ✻ mA

Power Dissipation: PWRD LOW V

ANA

= V

DIG

= 5V, fS = 100kHz 100 ✻ mW

PWRD HIGH 50 ✻ µW

TEMPERATURE RANGE

Specified Performance –40 +85 ✻✻°C

Derated Performance –55 +125 ✻✻°C

Storage –65 +150 ✻✻°C

Thermal Resistance (

θ

JA

)

Plastic DIP 75 ✻ °C/W

SOIC 75 ✻ °C/W

✻Same as specification for ADS7809P, U.

NOTES: (1) LSB means Least Significant Bit. For the ±10V input range, one LSB is 305µV. (2) Typical rms noise at worst case transitions and temperatures. (3)

As measured with fixed resistors shown in Figure 4. Adjustable to zero with external potentiometer. (4) For bipolar input ranges, full scale error is the worst case

of –Full Scale or +Full Scale untrimmed deviation from ideal first and last code transitions, divided by the transition voltage (not divided by the full-scale range) and

includes the effect of offset error. For unipolar input ranges, full scale error is the deviation of the last code transition divided by the transition voltage. It also includes

the effect of offset error. (5) All specifications in dB are referred to a full-scale ±10V input. (6) Full-Power Bandwidth defined as Full-Scale input frequency at which

Signal-to-(Noise+Distortion) degrades to 60dB. (7) Recovers to specified performance after 2 x FS input overvoltage.

Analog Inputs: R1IN.......................................................................... ±25V

R2

IN

.......................................................................... ±25V

R3

IN

.......................................................................... ±25V

CAP ..................................... V

ANA

+0.3V to AGND2 –0.3V

REF ....................................... Indefinite Short to AGND2,

......................................................................... Momentary Short to V

ANA

Ground Voltage Differences: DGND, AGND2 .................................±0.3V

V

ANA

......................................................................................................7V

V

DIG

to V

ANA

....................................................................................... +0.3

V

DIG

.......................................................................................................7V

Digital Inputs .............................................................–0.3V to V

DIG

+0.3V

Maximum Junction Temperature .................................................. +165°C

Internal Power Dissipation ............................................................700mW

Lead Temperature (soldering, 10s) .............................................. +300°C

ABSOLUTE MAXIMUM RATINGS

GUARANTEED MINIMUM

MAXIMUM NO MISSING SIGNAL-TO- SPECIFICATION PACKAGE

LINEARITY CODE LEVEL (NOISE + DISTORTION) TEMPERATURE DRAWING

PRODUCT ERROR (LSB) (LSB) RATIO (dB) RANGE (

°C) PACKAGE NUMBER

(1)

ADS7809P ±3 15 83 –40 to +85 20-Pin Plastic DIP 222

ADS7809PB ±2 16 86 –40 to +85 20-Pin Plastic DIP 222

ADS7809U ±3 15 83 –40 to +85 20-Lead SOIC 221

ADS7809UB ±2 16 86 –40 to +85 20-Lead SOIC 221

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

PACKAGE/ORDERING INFORMATION

ELECTROSTATIC

DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown

recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling

and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits

may be more susceptible to damage because very small

parametric changes could cause the device not to meet its

published specifications.

Loading...

Loading...