Burr Brown PGA103P, PGA103U Datasheet

®

®

PGA103

Programmable Gain

AMPLIFIER

FEATURES

● DIGITALLY PROGRAMABLE GAINS:

G=1, 10, 100V/V

● CMOS/TTL-COMPATIBLE INPUTS

● LOW GAIN ERROR:

● LOW OFFSET VOLTAGE DRIFT: 2µV/

±0.05% max, G=10

°C

● LOW QUIESCENT CURRENT: 2.6mA

● LOW COST

● 8-PIN PLASTIC DIP, SO-8 PACKAGES

APPLICATIONS

● DATA ACQUISITION SYSTEMS

● GENERAL PURPOSE ANALOG BOARDS

● MEDICAL INSTRUMENTATION

V+ V–

DESCRIPTION

The PGA103 is a programmable-gain amplifier for

general purpose applications. Gains of 1, 10, or 100 are

digitally selected by two CMOS/TTL-compatible inputs. The PGA103 is ideal for systems that must

handle wide dynamic range signals.

The PGA103’s high speed circuitry provides fast settling time, even at G=100 (8µs to 0.01%). Bandwidth

is 250kHz at G=100, yet quiescent current is only

2.6mA. It operates from ±4.5V to ±18V power

supplies.

The PGA103 is available in 8-pin plastic DIP and

SO-8 surface-mount packages, specified for the –40°C

to +85°C temperature range.

8

6

4

V

IN

GAIN A1A

100

International Airport Industrial Park • Mailing Address: PO Box 11400 • Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd. • Tucson, AZ 85706

Tel: (520) 746-1111 • Twx: 910-952-1111 • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

©

1993 Burr-Brown Corporation PDS-1208B Printed in U.S.A. November, 1993

PGA103

1

2

0

1

0

10

0

0

1

1

0

1

7

V

3

O

VO = G • V

IN

PGA103

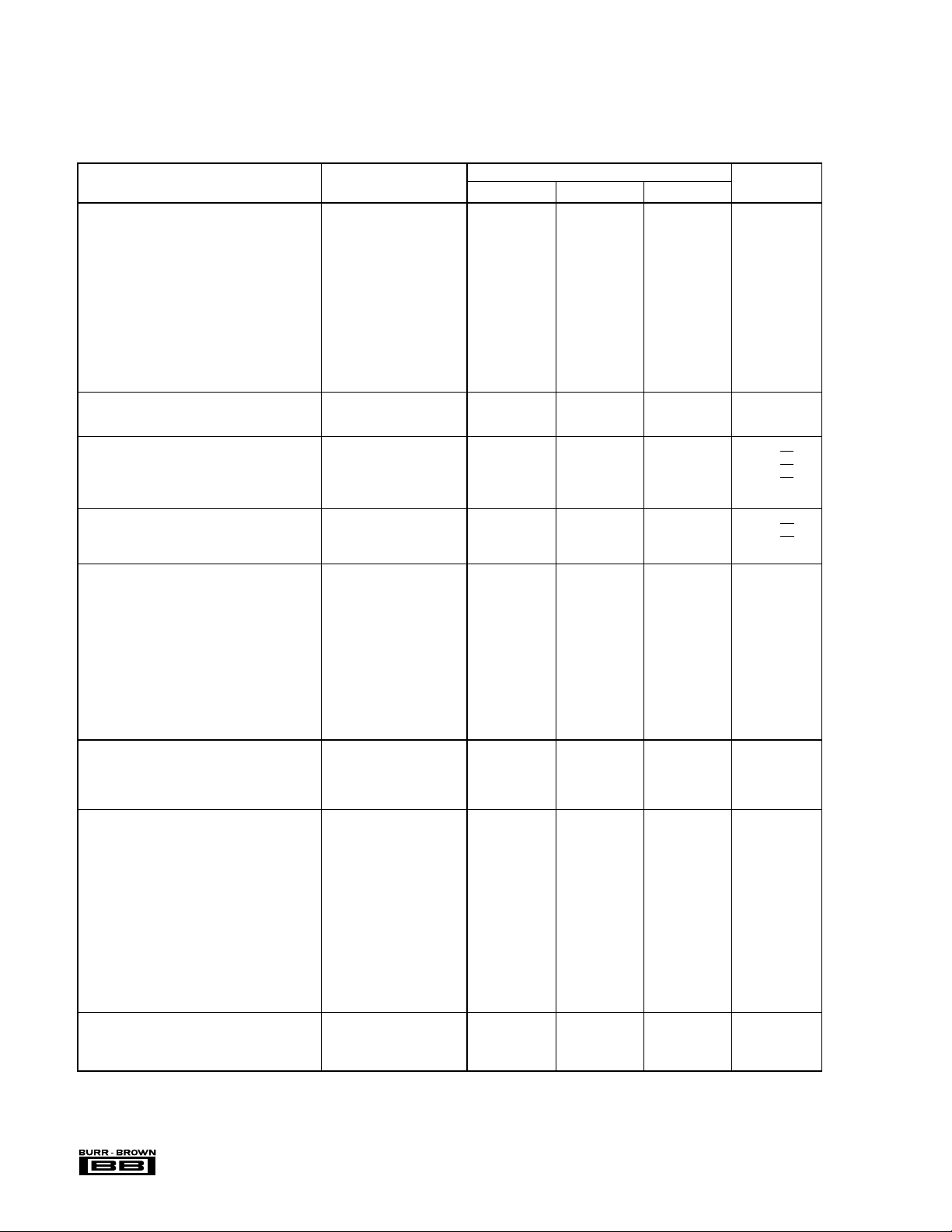

SPECIFICATIONS

ELECTRICAL

TA = +25°C, VS = ±15V, RL = 2kΩ unless otherwise specified.

PGA103P, U

PARAMETER CONDITIONS MIN TYP MAX UNITS

INPUT

Offset Voltage, RTI

G = 1 T

G = 10 ±100 ±500 µV

G = 100 ±100 ±500 µV

vs Temperature T

G = 1 ±5 µV/°C

G = 10 ±2 µV/°C

G = 100 ±2 µV/°C

vs Power Supply V

G = 1 30 70 µV/V

G = 10 10 35 µV/V

G = 100 10 35 µV/V

Impedance 10

INPUT BIAS CURRENT

Initial Bias Current ±50 ±150 nA

vs Temperature ±100 pA/°C

NOISE VOLTAGE, RTI G = 100, R

f = 10Hz 16 nV/√Hz

f = 100Hz 11 nV/√Hz

f = 1kHz 11 nV/√Hz

f

= 0.1Hz to 10Hz 0.6 µVp-p

B

NOISE CURRENT

f = 10Hz 2.8 pA/√Hz

f = 1kHz 0.3 pA/√Hz

f

= 0.1Hz to 10Hz 76 pAp-p

B

GAIN

Gain Error

G = 1 ±0.005 ±0.02 %

G = 10 ±0.02 ±0.05 %

G = 100 ±0.04 ±0.2 %

Gain vs Temperature

G = 1 ±2 ppm/°C

G = 10 ±10 ppm/°C

G = 100 ±30 ppm/°C

Nonlinearity

G = 1 ±0.001 ±0.003 % of FSR

G = 10 ±0.002 ±0.005 % of FSR

G = 100 ±0.004 ±0.01 % of FSR

OUTPUT

Voltage, Positive (V+) –3.5 (V+) –2.5 V

Negative (V–) +3.5 (V–) +2.5 V

Load Capacitance, max 1000 pF

Short-Circuit Current ±25 mA

FREQUENCY RESPONSE

Bandwidth, –3dB

G = 1 1.5 MHz

G = 10 750 kHz

G = 100 250 kHz

Slew Rate V

Settling Time, 0.1%

G = 1 2 µs

G = 10 2.2 µs

G = 100 6.5 µs

Settling Time, 0.01%

G = 1 2.5 µs

G = 10 2.5 µs

G = 100 8 µs

Overload Recovery 50% Overdrive 2.5 µs

DIGITAL LOGIC INPUTS

Digital Low Voltage –5.6 0.8 V

Digital Low or High Current 1 µA

Digital High Voltage 2V+V

= +25°C ±200 ±1500 µV

A

= T

to T

A

MIN

MAX

= ±4.5V to ±18V

S

8

|| 2 Ω || pF

= 0Ω

S

= ±10V 9 V/µs

O

®

PGA103

2

®

SPECIFICATIONS (CONT)

ELECTRICAL

TA = +25°C, VS = ±15V, RL = 2kΩ unless otherwise specified.

PGA103P, U

PARAMETER CONDITIONS MIN TYP MAX UNITS

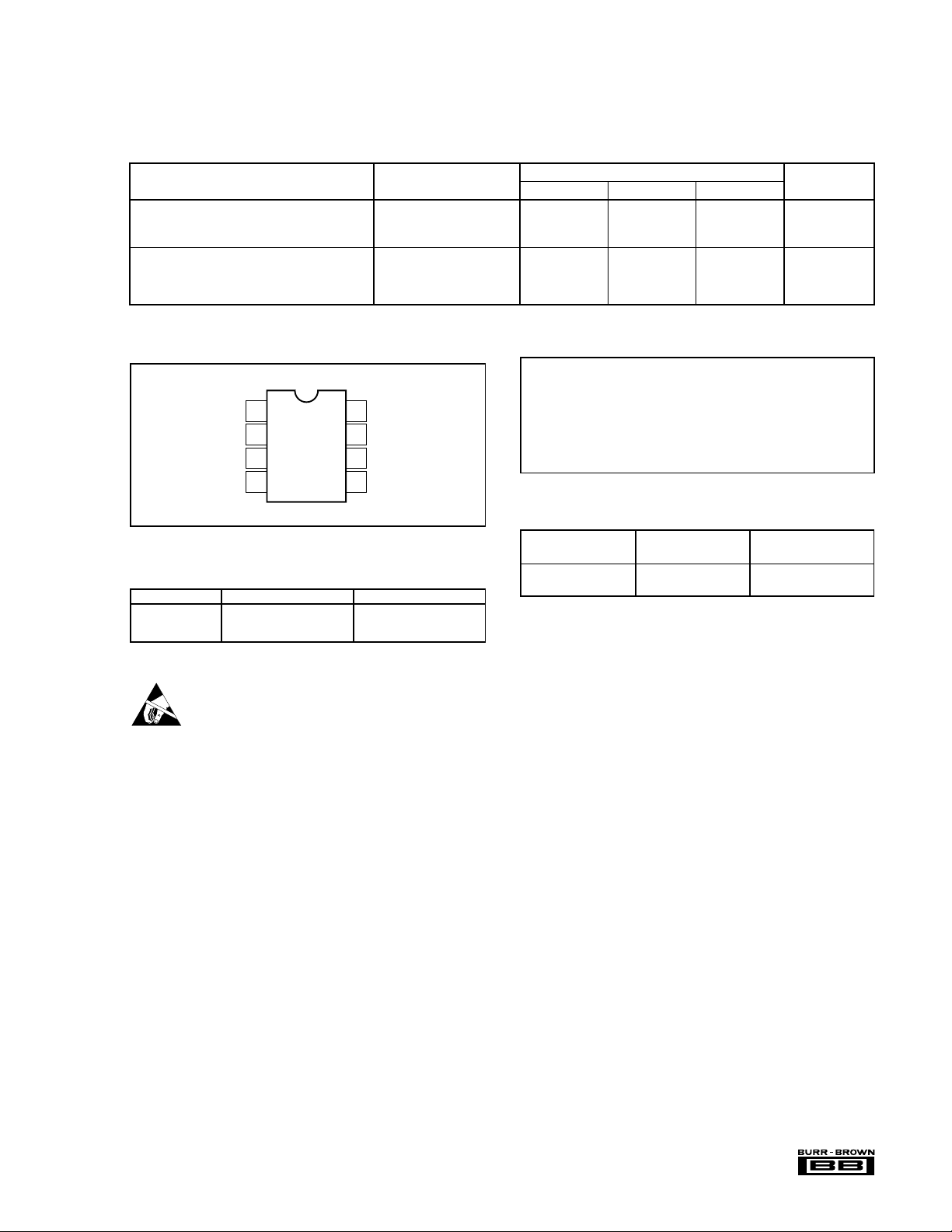

POWER SUPPLY

Voltage Range ±4.5 ± 15 ±18 V

Current V

TEMPERATURE RANGE

Specification –40 +85 °C

Operating –40 +125 °C

θ

: P or U Package 100 °C/W

JA

PIN CONFIGURATION ABSOLUTE MAXIMUM RATINGS

Top View DIP/SO-8

Ground

V

1

A

0

2

A

1

3

4

IN

8

V+

7

V

O

6

V–

5

NC

ORDERING INFORMATION

MODEL PACKAGE TEMPERATURE RANGE

PGA103P 8-Pin Plastic DIP –40°C to +85°C

PGA103U SO-8 Surface-Mount –40°C to +85°C

= 0V ±2.6 ±3.5 mA

IN

Supply Voltage................................................................................. ±18V

Analog Input Voltage Range ..................................................... V– to V+

Logic Input Voltage Range ........................................................ V– to V+

Output Short Circuit (to ground) ............................................ Continuous

Operating Temperature ................................................ –40°C to +125°C

Storage Temperature.................................................... –40°C to +125°C

Junction Temperature ................................................................... +150°C

Lead Temperature (soldering,10s) .............................................. +300°C

PACKAGE INFORMATION

MODEL PACKAGE NUMBER

PGA103P 8-Pin Plastic DIP 006

PGA103U SO-8 Surface-Mount 182

NOTE: (1) For detailed drawing and dimension table, please see end of data

sheet, or Appendix D of Burr-Brown IC Data Book.

PACKAGE DRAWING

(1)

ELECTROSTATIC

DISCHARGE SENSITIVITY

Any integrated circuit can be damaged by ESD. Burr-Brown

recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and

installation procedures can cause damage.

ESD damage can range from subtle performance degradation

to complete device failure. Precision integrated circuits may

be more susceptible to damage because very small parametric

changes could cause the device not to meet published specifications.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes

no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject to change

without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant

any BURR-BROWN product for use in life support devices and/or systems.

3

PGA103

Loading...

Loading...