Burr Brown PCM1600Y, PCM1600Y-2K, PCM1601Y, PCM1601Y-1K Datasheet

24-Bit, 96kHz Sampling, 6-Channel,

Enhanced Multi-Level, Delta-Sigma

DIGITAL-TO-ANALOG CONVERTER

PCM1600

PCM1601

®

TM

DESCRIPTION

The PCM1600

(1)

and PCM1601

(1)

are CMOS monolithic integrated circuits which feature six 24-bit audio

digital-to-analog converters and support circuitry in

either a LQFP-48 or MQFP-48 package. The digitalto-analog converters utilize Burr-Brown’s enhanced

multi-level, delta-sigma architecture, which employ

4th-order noise shaping and 8-level amplitude quantization to achieve excellent signal-to-noise performance

and a high tolerance to clock jitter.

The PCM1600 and PCM1601 accept industry-standard audio data formats with 16- to 24-bit audio data.

Sampling rates up to 100kHz are supported. A full set

of user-programmable functions are accessible through

a 4-wire serial control port which supports register

write and readback functions.

FEATURES

● 24-BIT RESOLUTION

●

ANALOG PERFORMANCE:

Dynamic Range: 105dB typ

SNR: 104dB typ

THD+N: 0.0018% typ

Full-Scale Output: 3.1Vp-p typ

●

8x OVERSAMPLING INTERPOLATION FILTER:

Stopband Attenuation: –82dB

Passband Ripple: ±0.002dB

● SAMPLING FREQUENCY: 10kHz to 100kHz

● ACCEPTS 16, 18, 20, AND 24-BIT AUDIO DATA

● DATA FORMATS: Standard, I2S, and Left-Justified

● SYSTEM CLOCK: 256fS, 384fS, 512fS, or 768f

S

●

USER-PROGRAMMABLE FUNCTIONS:

Digital Attenuation: 0dB to –63dB, 0.5dB/Step

Soft Mute

Zero Detect Mute

Zero Flags for Each Output Channel

Digital De-Emphasis

Digital Filter Roll-Off: Sharp or Slow

●

DUAL SUPPLY OPERATION:

+5V Analog, +3.3V Digital

●

5V TOLERANT DIGITAL LOGIC INPUTS

●

PACKAGES

(1)

: LQFP-48 (PCM1600)

and MQFP-48 (PCM1601)

© 1999 Burr-Brown Corporation PDS-1523C Printed in U.S.A. March, 2000

APPLICATIONS

● INTEGRATED A/V RECEIVERS

● DVD MOVIE AND AUDIO PLAYERS

● HDTV RECEIVERS

● CAR AUDIO SYSTEMS

● DVD ADD-ON CARDS FOR HIGH-END PCs

● DIGITAL AUDIO WORKSTATIONS

● OTHER MULTI-CHANNEL AUDIO SYSTEMS

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111

Twx: 910-952-1111 • Internet: http://www.burr-brown.com/ • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

NOTE: (1) The PCM1600 and PCM1601 utilize the same die and are

electrically the same. All references to the PCM1600 apply equally

to the PCM1601.

For most current data sheet and other product

information, visit www.burr-brown.com

PCM1601

PCM1600

®

2

PCM1600, PCM1601

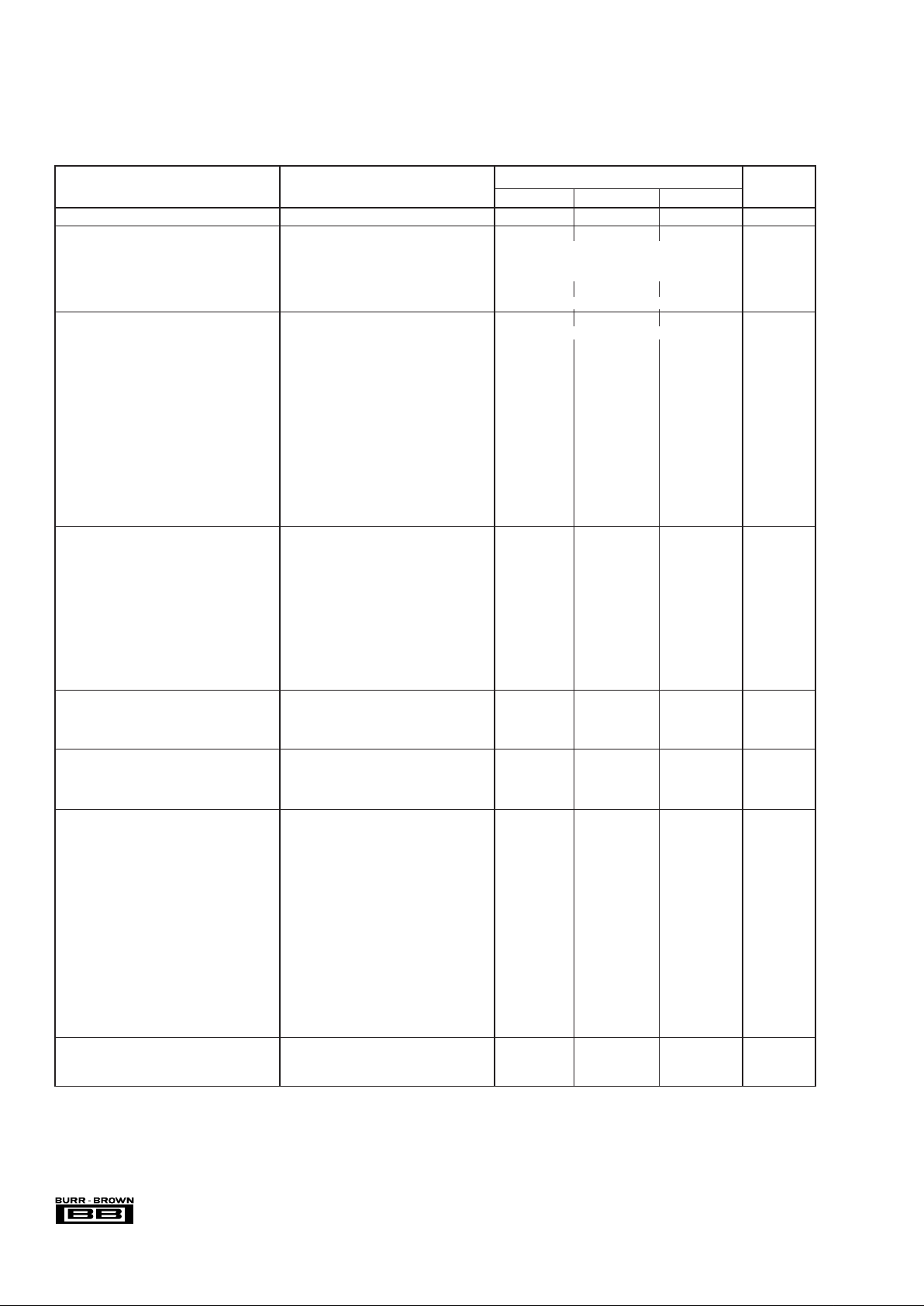

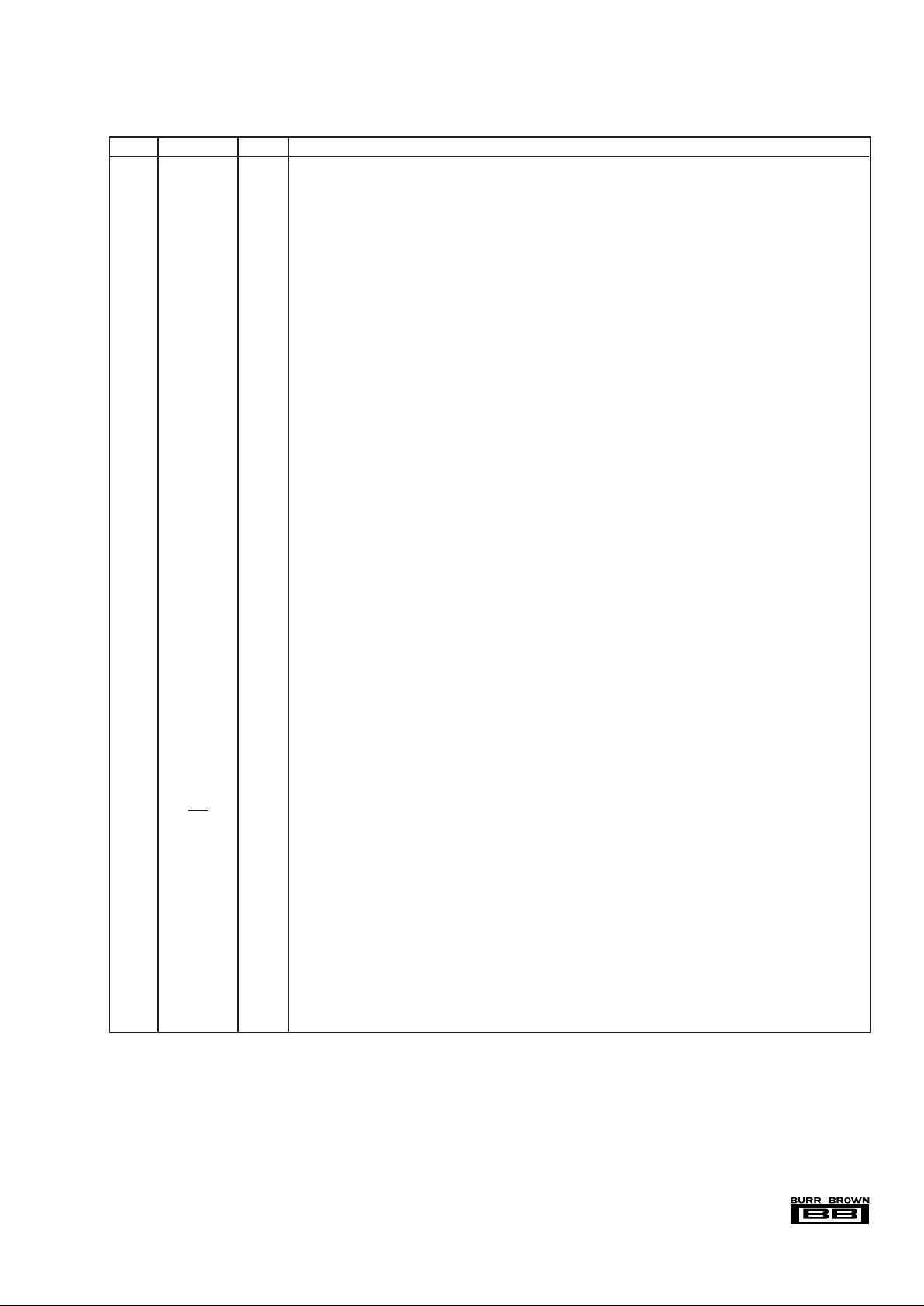

SPECIFICATIONS

All specifications at +25°C, +VCC = +5V, +V

DD

= +3.3V, system clock = 384fS (fS = 44.1kHz) and 24-bit data, unless otherwise noted.

PCM1600Y, PCM1601Y

PARAMETER CONDITIONS MIN TYP MAX UNITS

RESOLUTION 24 Bits

DATA FORMAT

Audio Data Interface Formats User Selectable Standard, I

2

S, Left-Justified

Data Bit Length User Selectable 16, 18, 20, 24-Bit

Audio Data Format MSB-First, Binary Two’s Complement

Sampling Frequency (f

S

) 10 100 kHz

System Clock Frequency 256, 384, 512, 768f

S

DIGITAL INPUT/OUTPUT

Logic Family TTL-Compatible

Input Logic Level

V

IH

2.0 V

V

IL

0.8 V

Input Logic Current

I

IH

(1)

VIN = V

DD

0.1 µA

I

IL

(1)

VIN = 0V –0.1 µA

I

IH

(2)

VIN = V

DD

65 100 µA

I

IL

(2)

VIN = 0V –0.1 µA

Output Logic Level

V

OH

(3)

I

OH

= –2mA 2.4 V

V

OL

(3)

I

OL

= +2mA 1.0 V

V

OH

(4)

I

OH

= –4mA 2.4 V

V

OL

(4)

I

OL

= +4mA 1.0 V

DYNAMIC PERFORMANCE

(5)

THD+N, V

OUT

= 0dB fS = 44.1kHz 0.0018 0.0045 %

f

S

= 96kHz 0.0035 %

V

OUT

= –60dB fS = 44.1kHz 0.65 %

f

S

= 96kHz 0.75 %

Dynamic Range EIAJ, A-Weighted, f

S

=44.1kHz 100 105 dB

A-Weighted, f

S

= 96kHz 104 dB

Signal-to-Noise Ratio

(6)

EIAJ, A-Weighted, fS =44.1kHz 98 104 dB

A-Weighted, f

S

= 96kHz 103 dB

Channel Separation fS = 44.1kHz 96 102 dB

fS = 96kHz 101 dB

Level Linearity Error V

OUT

= –90dB ±0.5 dB

DC ACCURACY

Gain Error ±1.0 % of FSR

Gain Mismatch, Channel-to-Channel ±1.0 % of FSR

Bipolar Zero Error V

O

= 0.5VCC at Bipolar Zero ±30 mV

ANALOG OUTPUT

Output Voltage Full Scale (0dB) 62% of V

CC

Vp-p

Center Voltage 50% V

CC

V

Load Impedance AC Load 5 kΩ

DIGITAL FILTER PERFORMANCE

Filter Characteristics 1, Sharp Roll-Off

Passband ±0.002dB 0.454f

S

Hz

–3dB 0.490f

S

Hz

Stopband 0.546f

S

Hz

Passband Ripple ±0.002 dB

Stopband Attenuation Stopband = 0.546f

S

–75 dB

Stopband = 0.567f

S

–82 dB

Filter Characteristics 2, Slow Roll-Off

Passband ±0.002dB 0.274f

S

Hz

–3dB 0.454f

S

Hz

Stopband 0.732f

S

Hz

Passband Ripple ±0.002 dB

Stopband Attenuation Stopband = 0.732f

S

–82 dB

Delay Time 34/f

S

sec

De-Emphasis Error ±0.1 dB

ANALOG FILTER PERFORMANCE

Frequency Response f = 20kHz –0.03 dB

f = 44kHz –0.20 dB

®

3 PCM1600, PCM1601

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes

no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject to change

without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant

any BURR-BROWN product for use in life support devices and/or systems.

POWER SUPPLY REQUIREMENTS

Voltage Range, V

DD

+3.0 +3.3 +3.6 V

V

CC

+4.5 +5.0 +5.5 V

Supply Current, I

DD

(7)

fS = 44.1kHz 20 28 mA

f

S

= 96kHz 42 mA

I

CC

fS = 44.1kHz 40 56 mA

f

S

= 96kHz 42 mA

Power Dissipation f

S

= 44.1kHz 266 409 mW

f

S

= 96kHz 349 mW

TEMPERATURE RANGE

Operation 0 +70 °C

Storage –55 +125 °C

Thermal Resistance,

θ

JA

100 °C/W

NOTES: (1) Pins 38, 40, 41, 45-47 (SCLKI, BCK, LRCK, DATA1, DATA2, DATA3). (2) Pins 34-37 (MDI, MC, ML, RST). (3) Pins 1-6, 48 (ZERO1-6, ZEROA).

(4) Pin 39 (SCLKO). (5) Analog performance specifications are tested with Shibasoku #725 THD Meter 400Hz HPF, 30kHz LPF on, average mode with 20kHz

bandwidth limiting. The load connected to the analog output is 5kΩ or larger, AC-coupled. (6) SNR is tested with Infinite Zero Detection off. (7) CLKO is disabled.

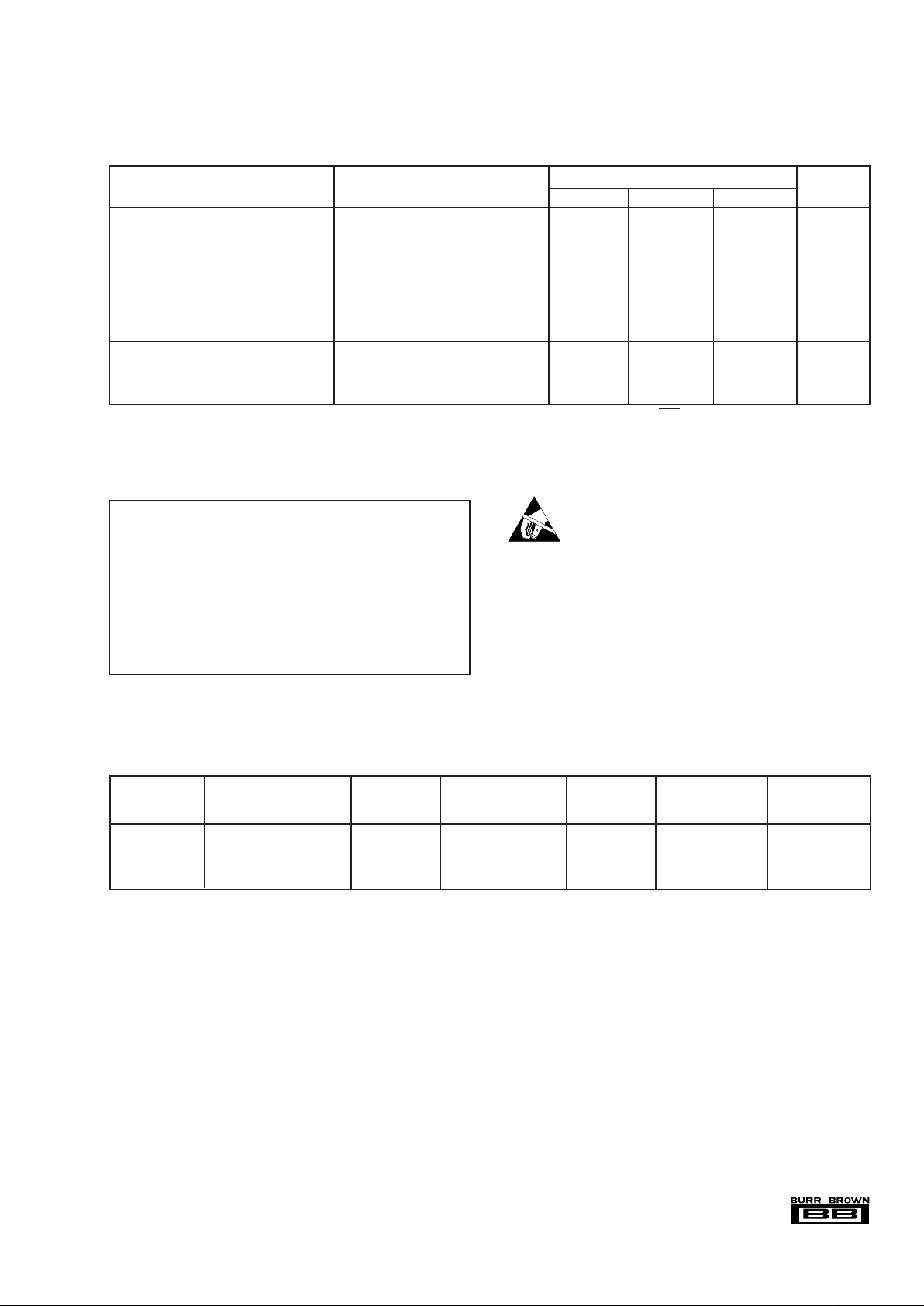

SPECIFICATIONS (Cont.)

All specifications at +25°C, +VCC = +5V, +V

DD

= +3.3V, system clock = 384fS (fS = 44.1kHz) and 24-bit data, unless otherwise noted.

PCM1600Y, PCM1601Y

PARAMETER CONDITIONS MIN TYP MAX UNITS

ELECTROSTATIC

DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown

recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling

and installation procedures can cause damage.

ESD damage can range from subtle performance degradation

to complete device failure. Precision integrated circuits may

be more susceptible to damage because very small parametric

changes could cause the device not to meet its published

specifications.

Power Supply Voltage, VDD.............................................................. +4.0V

V

CC

.............................................................. +6.5V

+VCC to +VDD Difference ................................................................... ±0.1V

Digital Input Voltage........................................................... –0.2V to +5.5V

Digital Output Voltage

(1)

........................................... –0.2V to (VDD + 0.2V)

Input Current (except power supply)............................................... ±10mA

Power Dissipation .......................................................................... 650mW

Operating Temperature Range ............................................. 0°C to +70°C

Storage Temperature...................................................... –55°C to +125°C

Lead Temperature (soldering, 5s) ................................................ +260°C

Package Temperature (IR reflow, 10s) .......................................... +235°C

NOTE: (1) Pin 33 (MDO) when output is disabled.

ABSOLUTE MAXIMUM RATINGS

PACKAGE SPECIFIED

DRAWING TEMPERATURE PACKAGE ORDERING TRANSPORT

PRODUCT PACKAGE NUMBER RANGE MARKING NUMBER

(1)

MEDIA

PCM1600Y 48-Lead LQFP 340 0°C to +70°C PCM1600Y PCM1600Y 250-Piece Tray

"""""PCM1600Y/2K Tape and Reel

PCM1601Y 48-Lead MQFP 359 0°C to +70°C PCM1601Y PCM1601Y 84-Piece Tray

"""""PCM1601Y/1K Tape and Reel

NOTE: (1) Models with a slash (/) are available only in Tape and Reel in the quantities indicated (e.g., /2K indicates 2000 devices per reel). Ordering 2000 pieces

of “PCM1600Y/2K” will get a single 2000-piece Tape and Reel.

PACKAGE/ORDERING INFORMATION

®

4

PCM1600, PCM1601

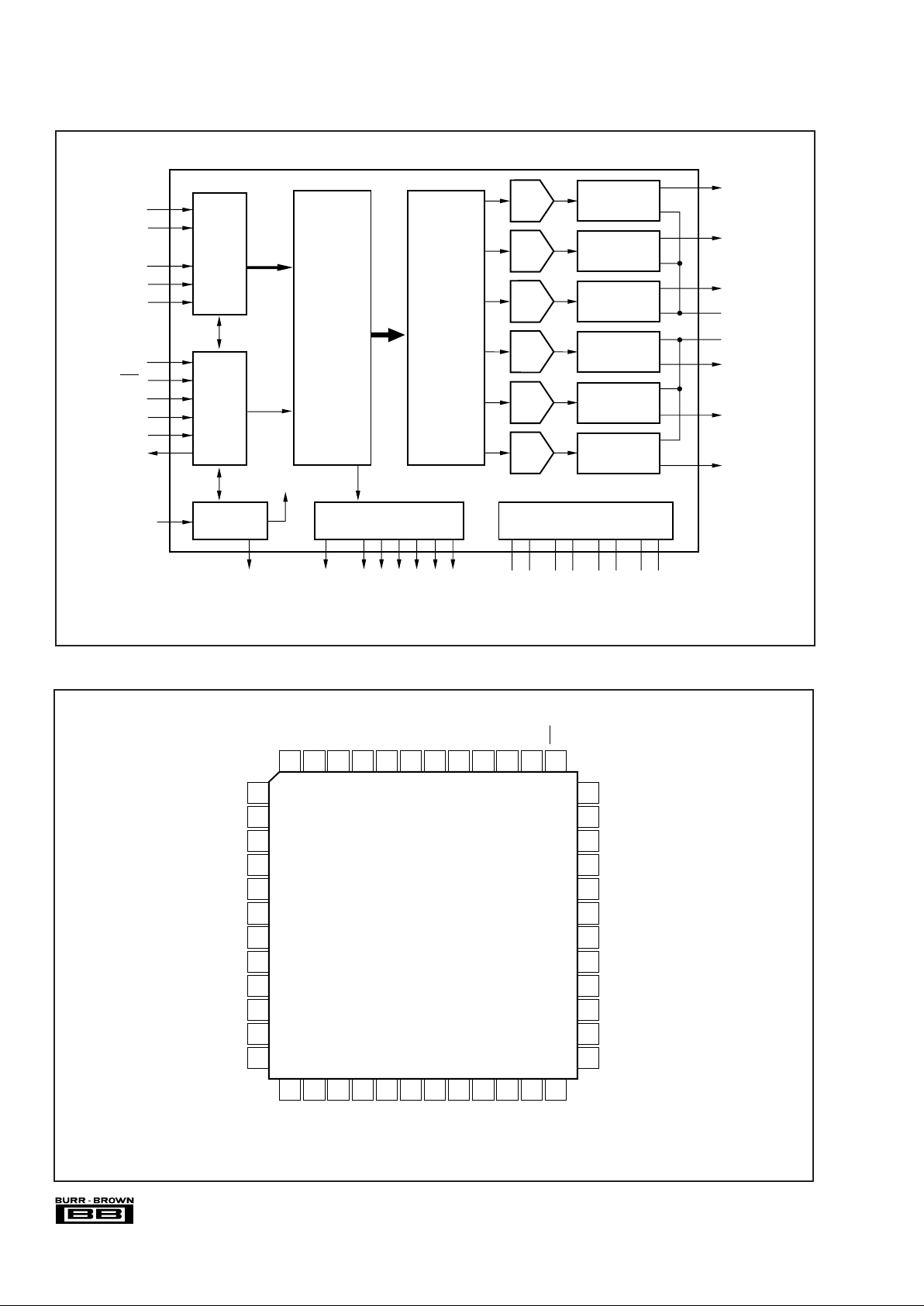

PIN CONFIGURATION

Top View LQFP, MQFP

BLOCK DIAGRAM

36

35

34

33

32

31

30

29

28

27

26

25

ML

MC

MDI

MDO

NC

NC

V

CC

0

AGND0

V

CC

1

AGND1

V

CC

2

AGND2

ZEROA

DATA3

DATA2

DATA1

DGND

VDDTEST

LRCK

BCK

SCLKO

SCLKI

RST

V

OUT

2

V

OUT

1

V

COM

2

V

COM

1

AGND6

V

CC

6

AGND5

V

CC

5

AGND4

V

CC

4

AGND3

V

CC

3

1

2

3

4

5

6

7

8

9

10

11

12

ZERO1

ZERO2

ZERO3

ZERO4

ZERO5

ZERO6

AGND

V

CC

V

OUT

6

V

OUT

5

V

OUT

4

V

OUT

3

48 47 46 45 44 43 42

41 40 39 38

13 14 15 16 17 18 19 20 21 22 233724

PCM1600

PCM1601

Audio

Serial

I/F

Output Amp and

Low-Pass Filter

DAC

DAC

DAC

DAC

DAC

DAC

8x

Oversampling

Digital Filter

with

Function

Controller

Enhanced

Multi-level

Delta-Sigma

Modulator

Output Amp and

Low-Pass Filter

Output Amp and

Low-Pass Filter

Output Amp and

Low-Pass Filter

Output Amp and

Low-Pass Filter

Output Amp and

Low-Pass Filter

BCK

LRCK

DATA1

DATA2

DATA3

Serial

Control

I/F

System Clock

Manager

Zero Detect

Power Supply

TEST

RST

ML

MC

MDI

MDO

V

OUT

1

V

OUT

2

V

OUT

5

V

OUT

6

V

OUT

3

V

COM

1

V

COM

2

V

OUT

4

ZERO1

ZERO2

ZERO3

ZERO4

ZERO5

ZERO6

V

DD

DGND

ZEROA

SCLKI

System Clock

SCLKO

V

CC

AGND

V

CC

0

AGND0

V

CC

1-6

AGND1-6

®

5 PCM1600, PCM1601

PIN NAME I/O DESCRIPTION

1 ZERO1 O Zero Data Flag for V

OUT

1.

2 ZERO2 O Zero Data Flag for V

OUT

2.

3 ZERO3 O Zero Data Flag for V

OUT

3.

4 ZERO4 O Zero Data Flag for V

OUT

4.

5 ZERO5 O Zero Data Flag for V

OUT

5.

6 ZERO6 O Zero Data Flag for V

OUT

6.

7 AGND — Analog Ground

8V

CC

— Analog Power Supply, +5V

9V

OUT

6 O Voltage Output of Audio Signal Corresponding to Rch on DATA3.

10 V

OUT

5 O Voltage Output of Audio Signal Corresponding to Lch on DATA3.

11 V

OUT

4 O Voltage Output of Audio Signal Corresponding to Rch on DATA2.

12 V

OUT

3 O Voltage Output of Audio Signal Corresponding to Lch on DATA2.

13 V

OUT

2 O Voltage Output of Audio Signal Corresponding to Rch on DATA1.

14 V

OUT

1 O Voltage Output of Audio Signal Corresponding to Lch on DATA1.

15 V

COM

2 O Common Voltage Output. This pin should be bypassed with a 10µF capacitor to AGND.

16 V

COM

1 O Common Voltage Output. This pin should be bypassed with a 10 µF capacitor to AGND.

17 AGND6 — Analog Ground

18 V

CC

6 — Analog Power Supply, +5V

19 AGND5 — Analog Ground

20 V

CC

5 — Analog Power Supply, +5V

21 AGND4 — Analog Ground

22 V

CC

4 — Analog Power Supply, +5V

23 AGND3 — Analog Ground

24 V

CC

3 — Analog Power Supply, +5V

25 AGND2 — Analog Ground

26 V

CC

2 — Analog Power Supply, +5V

27 AGND1 — Analog Ground

28 V

CC

1 — Analog Power Supply, +5V

29 AGND0 — Analog Ground

30 V

CC

0 — Analog Power Supply, +5V

31 NC — No Connection. Must be open.

32 NC — No Connection. Must be open.

33 MDO O Serial Data Output for Function Register Control Port

(3)

34 MDI I Serial Data Input for Function Register Control Port

(1)

35 MC I Shift Clock for Function Register Control Port

(1)

36 ML I Latch Enable for Function Register Control Port

(1)

37 RST I System Reset, Active LOW

(1)

38 SCLKI I System Clock In. Input frequency is 256, 384, 512 or 768fS.

(2)

39 SCLKO O Buffered Clock Output. Output frequency is 256, 384, 512, or 768fS and one-half of 256, 384, 512, or 768f

S.

40 BCK I Shift Clock Input for Serial Audio Data

(2)

41 LRCK I Left and Right Clock Input. This clock is equal to the sampling rate, fS.

(2)

42 TEST — Test Pin. This pin should be connected to DGND.

(1)

43 V

DD

— Digital Power Supply, +3.3V

44 DGND — Digital Ground for +3.3V

45 DATA1 I Serial Audio Data Input for V

OUT

1 and V

OUT

2

(2)

46 DATA2 I Serial Audio Data Input for V

OUT

3 and V

OUT

4

(2)

47 DATA3 I Serial Audio Data Input for V

OUT

5 and V

OUT

6

(2)

48 ZEROA I Zero Data Flag. Logical “AND” of ZERO1 through ZERO6.

NOTES: (1) Schmitt-Trigger input with internal pull-down, 5V tolerant. (2) Schmitt-Trigger input, 5V tolerant. (3) Tri-state output.

PIN ASSIGNMENTS

®

6

PCM1600, PCM1601

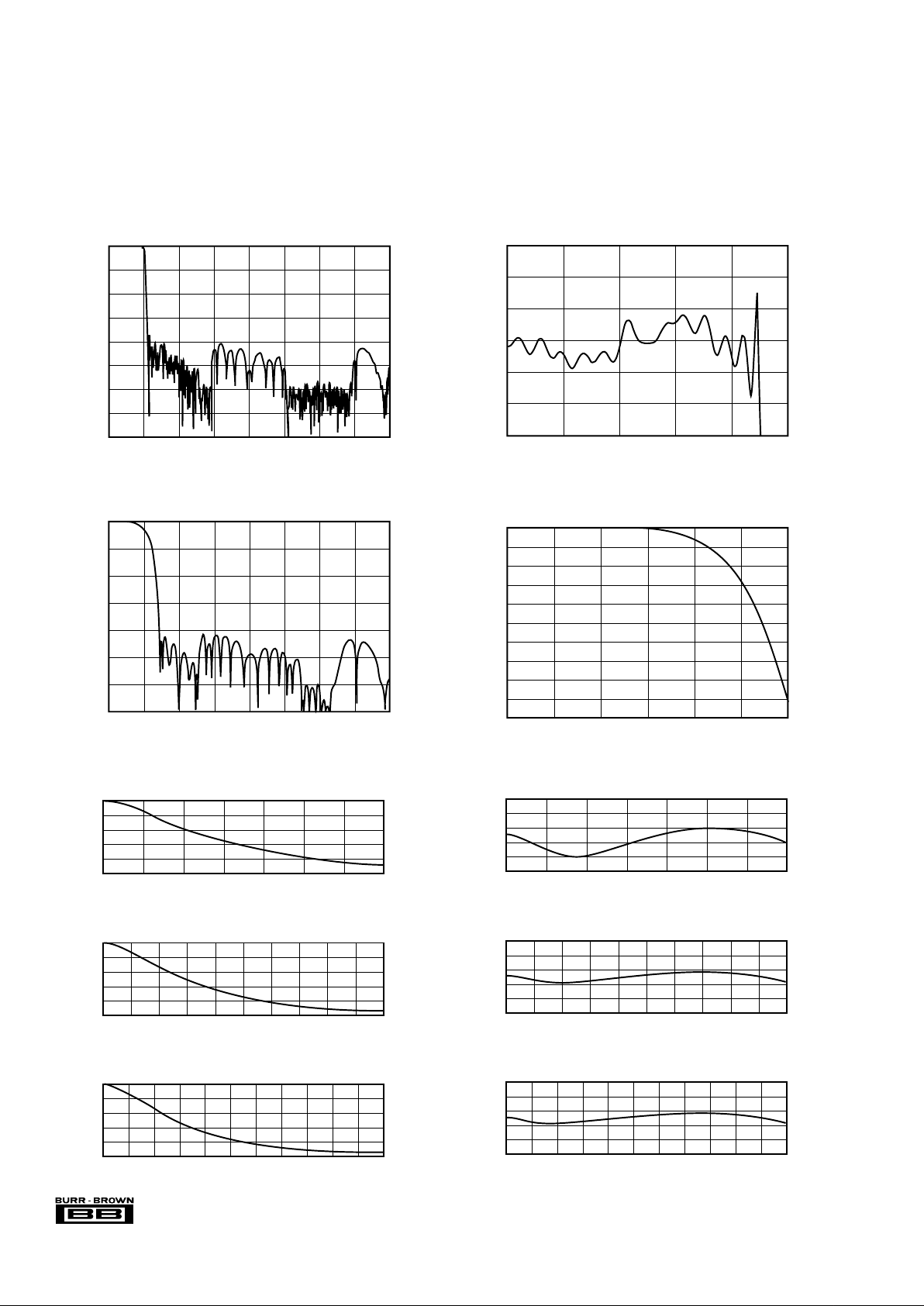

TYPICAL PERFORMANCE CURVES

All specifications at +25°C, VCC = 5V, VDD = 3.3V, SYSCLK = 384fS (fS = 44.1kHz), and 24-bit input data, unless otherwise noted.

DIGITAL FILTER

Digital Filter (De-Emphasis Off, fS = 44.1kHz)

0 0.5 1 1.5 2 2.5 3 3.5 4

0

–20

–40

–60

–80

–100

–120

–140

–160

Amplitude (dB)

FREQUENCY RESPONSE

(Sharp Roll-Off)

Frequency (x f

S

)

PASSBAND RIPPLE

(Sharp Roll-Off)

Frequency (x f

S

)

Amplitude (dB)

0.003

0.002

0.001

0

–0.001

–0.002

–0.003

0 0.1 0.2 0.3 0.4 0.5

FREQUENCY RESPONSE

(Slow Roll-Off)

Frequency (x f

S

)

Amplitude (dB)

0

–20

–40

–60

–80

–100

–120

–140

0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

TRANSITION CHARACTERISTICS

(Slow Roll-Off)

Frequency (x f

S

)

Amplitude (dB)

0

–2

–4

–6

–8

–10

–12

–14

–16

–18

–20

0 0.1 0.2 0.3 0.4 0.5 0.6

DE-EMPHASIS FREQUENCY RESPONSE (fS = 32kHz)

02468101214

Frequency (kHz)

0

–2

–4

–6

–8

–10

Level (dB)

DE-EMPHASIS FREQUENCY RESPONSE (fS = 48kHz)

0246810121416182022

Frequency (kHz)

0

–2

–4

–6

–8

–10

Level (dB)

DE-EMPHASIS FREQUENCY RESPONSE (fS = 44.1kHz)

02468101214161820

Frequency (kHz)

0

–2

–4

–6

–8

–10

Level (dB)

DE-EMPHASIS ERROR (fS = 32kHz)

02468101214

Frequency (kHz)

0.5

0.3

0.1

–0.1

–0.3

–0.5

0.5

0.3

0.1

–0.1

–0.3

–0.5

0.5

0.3

0.1

–0.1

–0.3

–0.5

Level (dB)

DE-EMPHASIS ERR0R (fS = 48kHz)

0246810121416182022

Frequency (kHz)

Level (dB)

DE-EMPHASIS ERROR (fS = 44.1kHz)

02468101214161820

Frequency (kHz)

Level (dB)

De-Emphasis Error

®

7 PCM1600, PCM1601

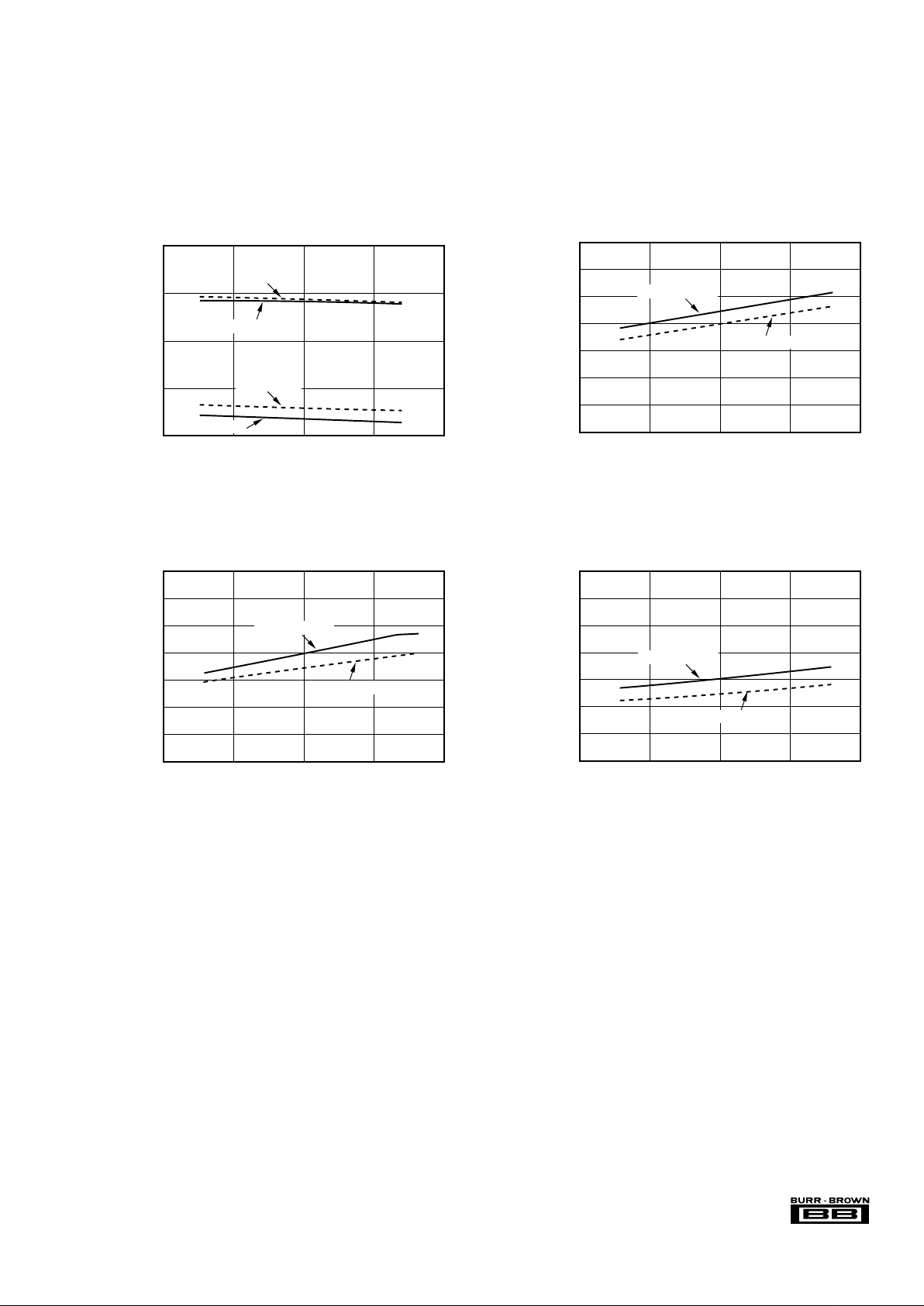

TYPICAL PERFORMANCE CURVES (Cont.)

All specifications at +25°C, VCC = 5V, VDD = 3.3V, SYSCLK = 384fS (fS = 44.1kHz), and 24-bit input data, unless otherwise noted.

ANALOG DYNAMIC PERFORMANCE

Supply Voltage Characteristics

TOTAL HARMONIC DISTORTION + NOISE vs V

CC

(VDD = 3.3V)

V

CC

(V)

THD+N (%)

10

1

0.1

0.01

0.001

4.0 4.5 5.0 5.5 6.0

44.1kHz, 384f

S

44.1kHz, 384f

S

96kHz, 384f

S

–60dB

0dB

96kHz, 384f

S

DYNAMIC RANGE vs V

CC

(VDD = 3.3V)

V

CC

(V)

Dynamic Range (dB)

110

108

106

104

102

100

98

96

4.0 4.5 5.0 5.5 6.0

96kHz, 384f

S

44.1kHz, 384f

S

SIGNAL-TO-NOISE RATIO vs V

CC

(VDD = 3.3V)

V

CC

(V)

SNR (dB)

110

108

106

104

102

100

98

96

4.0 4.5 5.0 5.5 6.0

96kHz, 384f

S

44.1kHz, 384f

S

CHANNEL SEPARATION vs V

CC

(VDD = 3.3V)

V

CC

(V)

Channel Separation (dB)

110

108

106

104

102

100

98

96

4.0 4.5 5.0 5.5 6.0

96kHz, 384f

S

44.1kHz, 384f

S

®

8

PCM1600, PCM1601

TOTAL HARMONIC DISTORTION + NOISE

vs TEMPERATURE

(V

DD

= 3.3V)

Temperature (°C)

THD+N (%)

10

1

0.1

0.01

0.001

–25 0 25 50 75 100

44.1kHz, 384f

S

44.1kHz, 384f

S

96kHz, 384f

S

–60dB

0dB

96kHz, 384f

S

DYNAMIC RANGE vs TEMPERATURE

(V

DD

= 3.3V)

Temperature (°C)

Dynamic Range (dB)

110

108

106

104

102

100

98

96

–25 0 25 50 75 100

96kHz, 384f

S

44.1kHz, 384f

S

TYPICAL PERFORMANCE CURVES (Cont.)

All specifications at +25°C, VCC = 5V, VDD = 3.3V, SYSCLK = 384fS (fS = 44.1kHz), and 24-bit input data, unless otherwise noted.

ANALOG DYNAMIC PERFORMANCE (con.t)

Temperature Characteristics

SIGNAL-TO-NOISE RATIO vs TEMPERATURE

(V

DD

= 3.3V)

Temperature (°C)

SNR (dB)

110

108

106

104

102

100

98

96

–25 0 25 50 10075

96kHz, 384f

S

44.1kHz, 384f

S

CHANNEL SEPARATION vs TEMPERATURE

(V

DD

= 3.3V)

Temperature (°C)

Channel Separation (dB)

110

108

106

104

102

100

98

96

–25 0 25 50 75 100

96kHz, 384f

S

44.1kHz, 384f

S

®

9 PCM1600, PCM1601

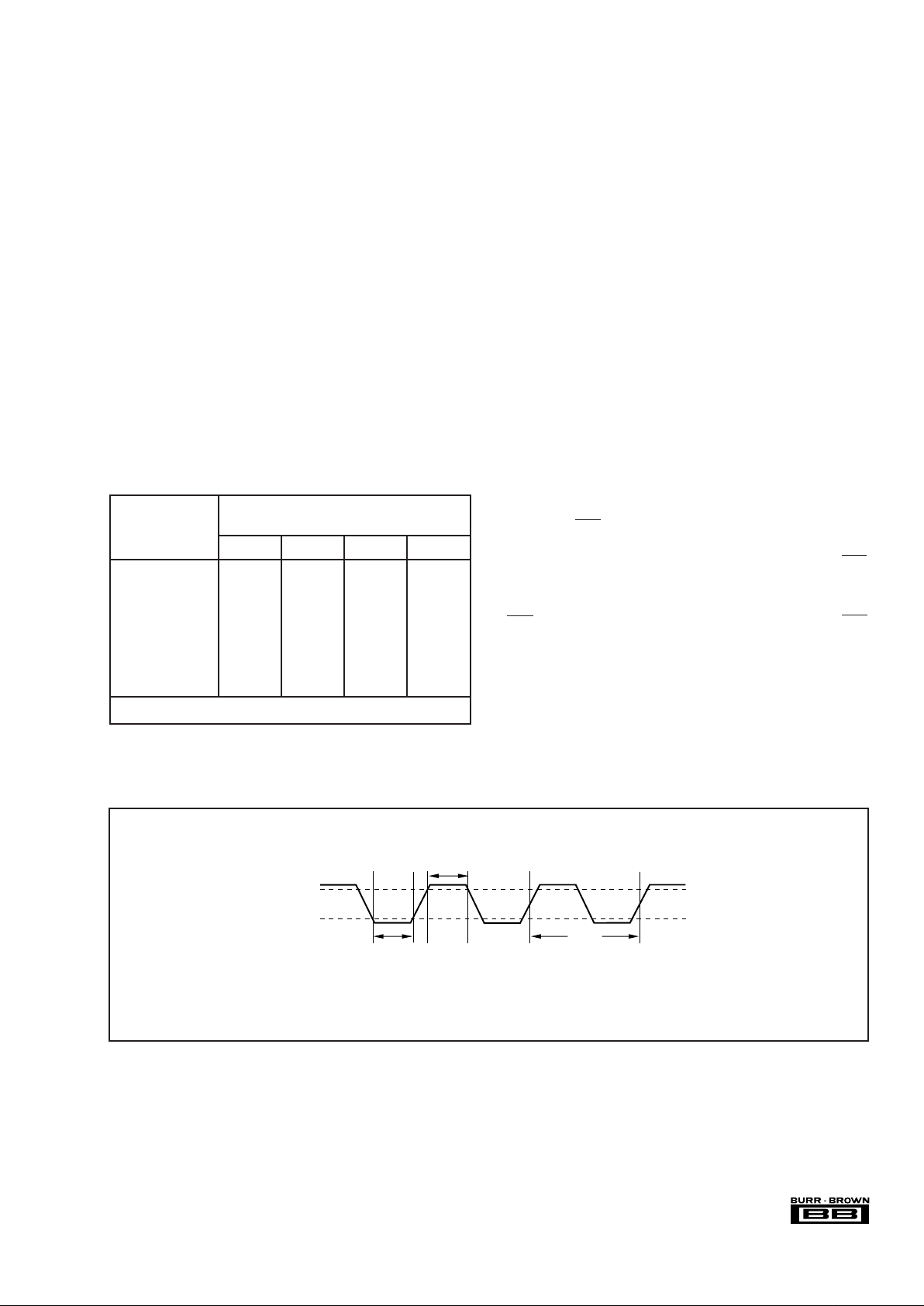

FIGURE 1. System Clock Input Timing.

SYSTEM CLOCK AND RESET

FUNCTIONS

SYSTEM CLOCK INPUT

The PCM1600 and PCM1601 require a system clock for

operating the digital interpolation filters and multi-level

delta-sigma modulators. The system clock is applied at the

SCLKI input (pin 38). For sampling rates from 10kHz

through 64kHz, the system clock frequency may be 256,

384, 512, or 768 times the sampling frequency, fS. For

sampling rates above 64kHz, the system clock frequency

may be 256, 384, or 512 times the sampling frequency.

Table I shows examples of system clock frequencies for

common audio sampling rates.

Figure 1 shows the timing requirements for the system clock

input. For optimal performance, it is important to use a clock

source with low phase jitter and noise. Burr-Brown’s

PLL1700 multi-clock generator is an excellent choice for

providing the PCM1600 system clock source.

SYSTEM CLOCK OUTPUT

A buffered version of the system clock input is available at

the SCLKO output (pin 39). SCLKO can operate at either

full (f

SCLKI

) or half (f

SCLKI

/2) rate. The SCLKO output

frequency may be programmed using the CLKD bit of

Control Register 9. The SCLKO output pin can also be

enabled or disabled using the CLKE bit of Control Register

9. The default is SCLKO enabled.

POWER-ON AND EXTERNAL RESET FUNCTIONS

The PCM1600 includes a power-on reset function. Figure 2

shows the operation of this function.

The system clock input at SCLKI should be active for at

least one clock period prior to VDD = 2.0V. With the system

clock active and VDD > 2.0V, the power-on reset function

will be enabled. The initialization sequence requires 1024

system clocks from the time VDD > 2.0V. After the initialization period, the PCM1600 will be set to its reset default

state, as described in the Mode Control Register section of

this data sheet.

The PCM1600 also includes an external reset capability

using the RST input (pin 37). This allows an external

controller or master reset circuit to force the PCM1600 to

initialize to its reset default state. For normal operation, RST

should be set to a logic ‘1’.

Figure 3 shows the external reset operation and timing. The

RST pin is set to logic ‘0’ for a minimum of 20ns. The RST

pin is then set to a logic ‘1’ state, which starts the initialization sequence, which lasts for 1024 system clock periods.

After the initialization sequence is completed, the PCM1600

will be set to its reset default state, as described in the Mode

Control Registers section of this data sheet.

t

SCLKIH

t

SCLKIH

f

SCLKI

System Clock Pulse Width High t

SCLKIH

: 7ns min

System Clock Pulse Width Low t

SCLKIL

: 7ns min

2.0V

0.8V

“H”

“L”

SCLKI

SAMPLING

FREQUENCY (f

S

) 256f

S

384f

S

512f

S

768f

S

22.05kHz 5.6448 8.4670 11.2896 16.9340

24kHz 6.1440 9.2160 12.2880 18.4320

32kHz 8.1920 12.2880 16.3840 24.5760

44.1kHz 11.2896 16.9340 22.5792 33.8688

48kHz 12.2880 18.4320 24.5760 36.8640

64kHz 16.3840 24.5760 32.7680 49.1520

88.2kHz 22.5792 33.8688 45.1584 See Note 1

96kHz 24.5760 36.8640 49.1520 See Note 1

NOTE: (1) The 768fS system clock rate is not supported for fS > 64kHz.

TABLE I. System Clock Rates for Common Audio Sampling

Frequencies.

SYSTEM CLOCK FREQUENCY (MHz)

SCLKI (Pin 38)

Loading...

Loading...