Page 1

PRELIMINARY HARDWARE DATA MODULE

BCM7405

General Information

5300 California Avenue • Irvine, CA 92617 • Phone: 949-926-5000 • Fax: 949-926-5203 06/29/07

2/24/2008 9T6WP

7405-1HDM00-R

Page 2

REVISION HISTORY

Revision # Date Change Description

7405-1HDM00-R 06/29/07 Preliminary release.

Broadcom Corporation

5300 California Avenue

Irvine, CA 92617

© 2007 by Broadcom Corporation

All rights reserved

Printed in the U.S.A.

®

Broadcom

Broadcom Corporation and/or its affiliates in the United States, certain other countries and/or the EU. Any other trademarks

or trade names mentioned are the property of their respective owners.

This hardware data module (including, without limitation, the Broadcom component(s) identified herein) is not designed,

intended, or certified for use in any military, nuclear, medical, mass transportation, aviation, navigations, pollution control,

hazardous substances management, or other high risk application. BROADCOM PROVIDES THIS HARDWARE DATA

MODULE "AS-IS", WITHOUT WARRANTY OF ANY KIND. BROADCOM DISCLAIMS ALL WARRANTIES, EXPRESSED

AND IMPLIED, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS

FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT.

, the pulse logo, Connecting everything®, and the Connecting everything logo are among the trademarks of

2/24/2008 9T6WP

Page 3

Preliminary Hardware Data Module BCM7405

06/29/07

TABLE OF CONTENTS

Document Overview.................................................................................................................................. 1-1

Overview .............................................................................................................................................. 1-2

Functional Description ............................................................................................................................. 1-3

Top-Level Overview ............................................................................................................................. 1-4

Features........................................................................................................................................ 1-5

Video Data Flow................................................................................................................................... 1-8

Overview ....................................................................................................................................... 1-8

Compressed Video Input .............................................................................................................. 1-8

Personal Video Recording ............................................................................................................ 1-9

Digital Video Decompression........................................................................................................ 1-9

ITU-R 656 Input ............................................................................................................................ 1-9

Video Processing .......................................................................................................................... 1-9

Video Encoder ............................................................................................................................ 1-10

Video DACs ................................................................................................................................ 1-10

Data Transport Processor .................................................................................................................. 1-11

Overview ..................................................................................................................................... 1-11

Features...................................................................................................................................... 1-11

Functional Overview ................................................................................................................... 1-13

Data Transport I/O Connections ................................................................................................. 1-16

Data Transport Input Bands

Throughput Data Rate

PID Parser

Packet Input Buffer

.......................................................................................................................... 1-17

............................................................................................................. 1-17

PID/Packet Substitution and Generation Module

Multistream CableCard Interface

Condition Access Descramblers (The Downstream Descramblers)

NDS ICAM Module

Copy Protection

PES Parser

......................................................................................................................... 1-21

.............................................................................................................. 1-20

.................................................................................................................. 1-20

PSI Section Filter and Processor

................................................................................................ 1-16

........................................................................................................ 1-16

................................................................ 1-18

........................................................................................ 1-19

................................... 1-20

........................................................................................ 1-21

Memory Buffer Manager

Interrupt Controller

Record Audio Video Engine (RAVE)

Document 7405-1HDM00-R Page iii

..................................................................................................... 1-22

.............................................................................................................. 1-22

................................................................................... 1-22

Broadcom Corporation

2/24/2008 9T6WP

Page 4

BCM7405 Preliminary Hardware Data Module

06/29/07

Audio/Video Interface

Playback

..............................................................................................................................1-25

Playback Sync Extractor

Remux Module

PCR Recovery Block

Serial STC Broadcast Module

..........................................................................................................1-25

.....................................................................................................1-26

....................................................................................................................1-26

...........................................................................................................1-27

.............................................................................................1-28

Broadcom Security Processor............................................................................................................1-28

Advanced Video Decoder ...................................................................................................................1-29

VC-1

....................................................................................................................................1-30

MPEG-2

MPEG-4 Part2

DivX

XVID

MPEG-1/H.261/H.263

...............................................................................................................................1-30

.....................................................................................................................1-30

.....................................................................................................................................1-30

....................................................................................................................................1-31

.........................................................................................................1-31

Features ......................................................................................................................................1-31

Supported Picture Sizes..............................................................................................................1-31

Output Data Format.....................................................................................................................1-31

AVD Block Diagram and Data Flow Description .........................................................................1-32

Advanced Audio Module.....................................................................................................................1-33

Features ......................................................................................................................................1-34

Overview of Audio Module ..........................................................................................................1-35

Video and Graphics Display ...............................................................................................................1-36

Overview .....................................................................................................................................1-36

Features

Video Subsystem

Graphics Subsystem

..............................................................................................................................1-36

................................................................................................................1-36

...........................................................................................................1-38

Top Level Partitioning..................................................................................................................1-38

Video (Broadcom Video Network) Subblock Description ............................................................1-39

AVC/MPEG-2/VC-1 Feeder

Video Feeder

Graphics Feeder

Video Scaler

.......................................................................................................................1-40

..................................................................................................................1-40

........................................................................................................................1-41

Motion Adaptive De-interlacer

Film Grain Technology

.................................................................................................1-40

.............................................................................................1-41

........................................................................................................1-42

Compositor

Page iv Document 7405-1HDM00-R

..........................................................................................................................1-42

Broadcom Corporation

2/24/2008 9T6WP

Page 5

Preliminary Hardware Data Module BCM7405

06/29/07

Capture Block

..................................................................................................................... 1-42

Digital Noise Reduction ............................................................................................................. 1-43

DNR Operations

.................................................................................................................. 1-43

Digital Contour Removal ............................................................................................................. 1-43

Graphics Subblock Description...................................................................................................1-44

Scaler Overview

Feeder Architecture (Source and Destination)

Color Keying and Color Matrix Architecture

Compositor Architecture

ROP Architecture

Capture Architecture

.................................................................................................................. 1-45

.................................................................... 1-46

........................................................................ 1-47

..................................................................................................... 1-48

................................................................................................................ 1-49

........................................................................................................... 1-49

Digital Video Decoder (ITU-R-656)............................................................................................. 1-50

VBI Decoding

...................................................................................................................... 1-50

Analog Video Encoder ................................................................................................................ 1-50

VBI Encoding

...................................................................................................................... 1-52

Video DACs ................................................................................................................................ 1-53

Digital Video Encoder ................................................................................................................. 1-53

Safe Mode

Supported Modes

Supported PC Scan Rates

........................................................................................................................... 1-53

................................................................................................................ 1-54

.................................................................................................. 1-55

RF Modulator ..................................................................................................................................... 1-56

Overview ..................................................................................................................................... 1-56

Features...................................................................................................................................... 1-56

Typical Usage Modes ................................................................................................................. 1-57

Supported Television Standards

Audio Transmission Modes

Baseband BTSC Composite Output Mode

Sound IF Output Mode

........................................................................................................ 1-58

Unsupported Audio Mode

......................................................................................... 1-57

................................................................................................. 1-58

......................................................................... 1-58

................................................................................................... 1-58

Memory Controller ............................................................................................................................. 1-59

Overview ..................................................................................................................................... 1-59

DRAM Physical Layer Controller ................................................................................................ 1-61

Memory Configurations Supported

..................................................................................... 1-61

DRAM Transaction Layer Controller........................................................................................... 1-62

Arbitration

Document 7405-1HDM00-R Page v

............................................................................................................................ 1-62

Broadcom Corporation

2/24/2008 9T6WP

Page 6

BCM7405 Preliminary Hardware Data Module

06/29/07

Buses

DDR-SDRAM Memory Image Organization

Digital Video Compression Standards

Memory Accesses for Video Decompression

..................................................................................................................................1-62

........................................................................1-62

.................................................................................1-62

......................................................................1-62

DDR Clock Generation ................................................................................................................1-62

MIPS4380 Processor Core.................................................................................................................1-63

Overview .....................................................................................................................................1-63

Architecture .................................................................................................................................1-63

Micro-Architecture .......................................................................................................................1-64

EJTAG Debug Support................................................................................................................1-64

Major Functional Blocks ..............................................................................................................1-65

Execution Unit

Multiply Divide Unit

Floating-Point Unit

.....................................................................................................................1-65

..............................................................................................................1-66

...............................................................................................................1-66

eDSP Extended Instructions .......................................................................................................1-67

MIPS16e Application-Specific Extension ....................................................................................1-67

Memory Management Unit with TLB ...........................................................................................1-67

System Control Coprocessor (CP0) ............................................................................................1-68

Instruction Cache ........................................................................................................................1-68

Data Cache .................................................................................................................................1-68

Level-Two Cache ........................................................................................................................1-69

Readahead Cache ......................................................................................................................1-69

Little and Big Endianness of Byte Ordering.................................................................................1-69

Debugging Support Unit ..............................................................................................................1-70

Peripherals .........................................................................................................................................1-71

Overview .....................................................................................................................................1-71

Peripheral Control Unit ................................................................................................................1-71

Keypad Controller........................................................................................................................1-71

LED Controller.............................................................................................................................1-71

IR Receiver Controller .................................................................................................................1-71

IR Blaster Controller ....................................................................................................................1-72

UHF Receiver..............................................................................................................................1-74

UART...........................................................................................................................................1-75

General Description

.............................................................................................................1-75

Functional Description

Page vi Document 7405-1HDM00-R

.........................................................................................................1-76

Broadcom Corporation

2/24/2008 9T6WP

Page 7

Preliminary Hardware Data Module BCM7405

06/29/07

Generic I/O Port Controller ......................................................................................................... 1-77

SPI Master .................................................................................................................................. 1-77

Programmable Queue

Wraparound Transfer Mode

Programmable Transfer Length

Programmable Transfer Delay

Programmable Queue Pointer

......................................................................................................... 1-78

................................................................................................ 1-78

.......................................................................................... 1-78

............................................................................................ 1-78

............................................................................................ 1-78

BSC Master ................................................................................................................................ 1-78

BSC Master Interface Operation

......................................................................................... 1-79

BSC Slave .................................................................................................................................. 1-79

BSC Operation

.................................................................................................................... 1-79

PWMs ......................................................................................................................................... 1-80

Timer/Counters ........................................................................................................................... 1-80

Smart Card Interfaces................................................................................................................. 1-80

Features

.............................................................................................................................. 1-81

M-Card CPU Interface ................................................................................................................ 1-82

Introduction

Input and Output Processes

......................................................................................................................... 1-82

............................................................................................... 1-83

PCI and External Bus Interface ..................................................................................................1-84

Advanced Connectivity Interface ................................................................................................ 1-89

Ethernet

Serial ATA Controller

USB

Soft Modem

PCI

.............................................................................................................................. 1-89

.......................................................................................................... 1-89

..................................................................................................................................... 1-90

......................................................................................................................... 1-91

...................................................................................................................................... 1-91

JTAG Interface............................................................................................................................ 1-91

Testability........................................................................................................................................... 1-92

Overview ..................................................................................................................................... 1-92

Production Testing ...................................................................................................................... 1-92

Scan

.................................................................................................................................... 1-92

Built-In Self-Test

................................................................................................................. 1-92

Functional Testing ...................................................................................................................... 1-92

Test Modes

Test Buses

......................................................................................................................... 1-92

.......................................................................................................................... 1-92

On-Board Testing ....................................................................................................................... 1-92

Broadcom Corporation

Document 7405-1HDM00-R Page vii

2/24/2008 9T6WP

Page 8

BCM7405 Preliminary Hardware Data Module

06/29/07

JTAG

...................................................................................................................................1-92

EJTAG

.................................................................................................................................1-92

Power Features ..................................................................................................................................1-93

Power Modes for DDR DRAM Memory Controller ......................................................................1-93

Power-Up Sequence ...................................................................................................................1-94

Hardware Signal Descriptions................................................................................................................1-95

Pin Definition Notations ......................................................................................................................1-96

Pin Labels....................................................................................................................................1-96

Pin Type ......................................................................................................................................1-96

Power-On Strap Settings..................................................................................................................1-147

Timing and AC Characteristics ............................................................................................................1-149

Data Transport Input Timing.............................................................................................................1-150

MPOD Input Timing ..........................................................................................................................1-151

Data Transport Output Timing..........................................................................................................1-152

RMX Serial Output Port Timing (Clock/Data/Sync Mode) .........................................................1-152

MPOD Output Timing .......................................................................................................................1-153

I2S Audio/Compressed I2S Output Timing.......................................................................................1-154

SPDIF Audio Output Timing .............................................................................................................1-155

DAC Audio Output Timing ................................................................................................................1-156

256Fs Audio Clock Output Timing....................................................................................................1-157

PCI Interface Timing.........................................................................................................................1-158

EBI Timing ........................................................................................................................................1-159

Asynchronous Read Transfer....................................................................................................1-159

Asynchronous Write Transfer....................................................................................................1-160

Synchronous Read Transfer .....................................................................................................1-161

Synchronous Write Transfer......................................................................................................1-162

DDR Interface Timing .......................................................................................................................1-163

HDMI and DVO.................................................................................................................................1-165

ITU656 Output Timing ......................................................................................................................1-166

Timing For ITU656 Output at vo_656 Pins ...............................................................................1-166

Timing For Alternate 656 Output at vi0_656 Pins .....................................................................1-167

Serial Teletext Port Output Timing ............................................................................................1-167

Timing For Serial Teletext Output at rmx_data1 Pin .................................................................1-167

Crystal Requirements............................................................................................................................1-168

Crystal Requirements .......................................................................................................................1-169

Broadcom Corporation

Page viii Document 7405-1HDM00-R

2/24/2008 9T6WP

Page 9

Preliminary Hardware Data Module BCM7405

06/29/07

3rd Overtone Crystal Oscillator.................................................................................................1-169

External Components ............................................................................................................... 1-170

SATA Crystal ............................................................................................................................ 1-170

Electrical Characteristics ..................................................................................................................... 1-171

Absolute Maximum Ratings ............................................................................................................. 1-172

Recommended Operating Conditions .............................................................................................. 1-172

Thermal Data ......................................................................................................................................... 1-173

Thermal Data ................................................................................................................................... 1-174

Mechanical Characteristics.................................................................................................................. 1-175

Mechanical Drawings ....................................................................................................................... 1-176

Ordering Information ............................................................................................................................ 1-179

Ordering Information ........................................................................................................................ 1-180

Broadcom Corporation

Document 7405-1HDM00-R Page ix

2/24/2008 9T6WP

Page 10

BCM7405 Preliminary Hardware Data Module

06/29/07

Broadcom Corporation

Page x Document 7405-1HDM00-R

2/24/2008 9T6WP

Page 11

Preliminary Hardware Data Module BCM7405

06/29/07

LIST OF FIGURES

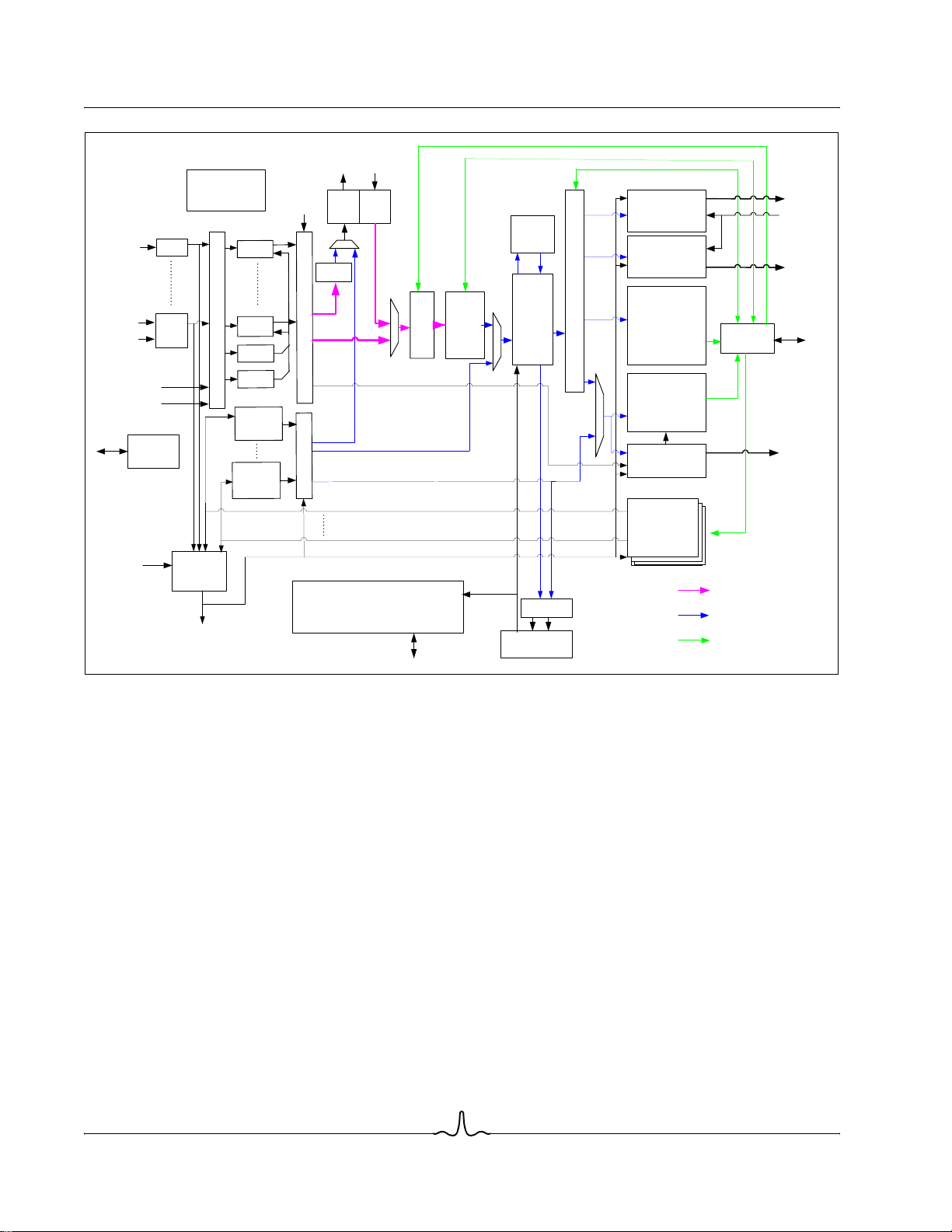

Figure 1-1: Functional Block Diagram ............................................................................................................. 1-7

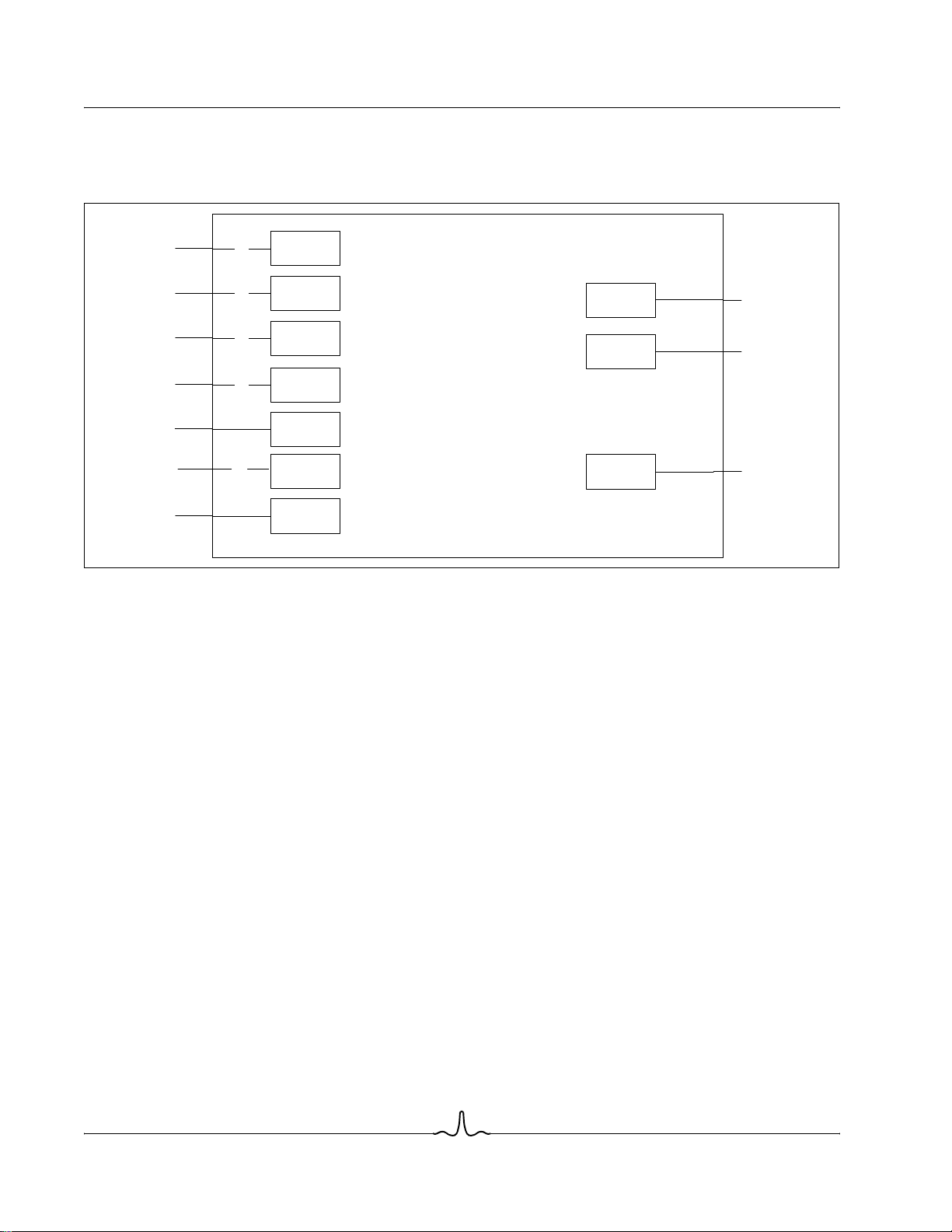

Figure 1-2: Video Data Flow Diagram ............................................................................................................. 1-8

Figure 1-3: Data Transport and Broadcom Security Processor Block Diagram ............................................ 1-14

Figure 1-4: Data Transport I/O Connections Diagram ................................................................................... 1-16

Figure 1-5: Advanced Video Decoding Module Block Diagram..................................................................... 1-32

Figure 1-6: Audio Block Diagram................................................................................................................... 1-33

Figure 1-7: Video and Graphics Block Diagram ............................................................................................ 1-38

Figure 1-8: Video Display Engine Block Diagram.......................................................................................... 1-39

Figure 1-9: DNR Position in BVN .................................................................................................................. 1-43

Figure 1-10: Memory-to-Memory Compositor Block Diagram ....................................................................... 1-45

Figure 1-11: Stripe Example.......................................................................................................................... 1-46

Figure 1-12: Color Keying Flow ..................................................................................................................... 1-48

Figure 1-13: VEC Block Diagram .................................................................................................................. 1-52

Figure 1-14: RF Modulator Block Diagram .................................................................................................... 1-56

Figure 1-15: Memory Controller Partition ...................................................................................................... 1-60

Figure 1-16: Block Diagram of the CPU ........................................................................................................ 1-65

Figure 1-17: Little and Big Endian Byte Ordering .......................................................................................... 1-69

Figure 1-18: Flash IR Scheme Example........................................................................................................ 1-72

Figure 1-19: IR Blaster Block Diagram .......................................................................................................... 1-72

Figure 1-20: Analog Front End of UHF Receiver with External Components................................................ 1-74

Figure 1-21: Digital Front End of UHF Receiver ............................................................................................ 1-75

Figure 1-22: UART Functional Block Diagram .............................................................................................. 1-76

Figure 1-23: Asynchronous Serial Data Waveform (01001011 Data, 8-bit Character, Even Parity) ............. 1-76

Figure 1-24: Variable-Frequency PWM Generation Diagram........................................................................ 1-80

Figure 1-25: Smart Card Interface Block Diagram ........................................................................................ 1-81

Figure 1-26: M-Card CPU Interface............................................................................................................... 1-82

Figure 1-27: MCIF Interfaces......................................................................................................................... 1-83

Figure 1-28: EBI Synchronous Read Cycle Between Two PCI Cycles ......................................................... 1-85

Figure 1-29: EBI Asynchronous Read Cycle Between Two PCI Cycles ....................................................... 1-86

Figure 1-30: EBI Asynchronous Write Cycle Between Two PCI Cycles........................................................ 1-87

Figure 1-31: EBI Synchronous Write Cycle Between Two PCI Cycles ......................................................... 1-88

Figure 1-32: SATA Core Block Diagram........................................................................................................ 1-90

Broadcom Corporation

Document 7405-1HDM00-R Page xi

2/24/2008 9T6WP

Page 12

BCM7405 Preliminary Hardware Data Module

06/29/07

Figure 1-33: Soft Modem Connections ..........................................................................................................1-91

Figure 1-34: Power-Up Sequence Waveforms Without On-chip Voltage Regulator......................................1-94

Figure 1-35: Data Transport Input Band Timing ..........................................................................................1-150

Figure 1-36: MPOD Input Timing .................................................................................................................1-151

Figure 1-37: RMX Serial Output Port Timing (Clock/Data/Sync Mode) .......................................................1-152

Figure 1-38: MPOD Output Timing ..............................................................................................................1-153

Figure 1-39: I2S Audio/Compressed I2S Output Timing Diagram ...............................................................1-154

Figure 1-40: SPDIF Audio Output Timing Diagram......................................................................................1-155

Figure 1-41: DAC Audio Output Timing Diagram.........................................................................................1-156

Figure 1-42: 256Fs Audio Clock Output Timing Diagram ............................................................................1-157

Figure 1-43: PCI Interface Timing Diagram .................................................................................................1-158

Figure 1-44: Async Read Timing Diagram ...................................................................................................1-159

Figure 1-45: Async Write Timing Diagram ...................................................................................................1-160

Figure 1-46: Synchronous Read Timing Diagram........................................................................................1-161

Figure 1-47: Synchronous Write Timing Diagram ........................................................................................1-162

Figure 1-48: Write Cycle Timing ..................................................................................................................1-163

Figure 1-49: Read Cycle Timing ..................................................................................................................1-163

Figure 1-50: Clock-to-Data Timing...............................................................................................................1-165

Figure 1-51: ITU656 Output Timing Diagram...............................................................................................1-166

Figure 1-52: Serial Teletext Port Output Timing Diagram ............................................................................1-167

Figure 1-53: Example: Vendor (TXC) Part Number for 3OT Crystal: 7EA0000023 .....................................1-170

Figure 1-54: 976-FCBGA+HS Package (With Heat Sink) ............................................................................1-176

Figure 1-55: 976-FCBGA+HS Package (Without Heat Sink).......................................................................1-177

Broadcom Corporation

Page xii Document 7405-1HDM00-R

2/24/2008 9T6WP

Page 13

Preliminary Hardware Data Module BCM7405

06/29/07

LIST OF TABLES

Table 1-1: Document Overview ....................................................................................................................... 1-2

Table 1-2: Video DAC Configuration ............................................................................................................. 1-10

Table 1-3: Definition of Terms ....................................................................................................................... 1-15

Table 1-4: Decode and Display Formats ....................................................................................................... 1-37

Table 1-5: Color and Alpha Selection............................................................................................................ 1-48

Table 1-6: Digital Video Decoder Supported Modes ..................................................................................... 1-50

Table 1-7: VBI Decoding ............................................................................................................................... 1-50

Table 1-8: Analog Video Encoder.................................................................................................................. 1-51

Table 1-9: VBI Encoding................................................................................................................................ 1-52

Table 1-10: DVI Supported Modes ................................................................................................................ 1-54

Table 1-11: ITU-656 Supported Modes ......................................................................................................... 1-54

Table 1-12: DVI PC Scan Clock Rates.......................................................................................................... 1-55

Table 1-13: PC Display Support .................................................................................................................... 1-55

Table 1-14: Supported Modulation Standards ............................................................................................... 1-57

Table 1-15: RFM Audio Usage Modes for Normal Operation........................................................................ 1-58

Table 1-16: FPU Latency and Repeat Rate .................................................................................................. 1-67

Table 1-17: Power Estimate .......................................................................................................................... 1-93

Table 1-18: Power Configuration Example.................................................................................................... 1-93

Table 1-19: Pin Descriptions ......................................................................................................................... 1-96

Table 1-20: Power-On Strap Settings.......................................................................................................... 1-147

Table 1-21: Data Transport Input Band Timing Parameters........................................................................ 1-150

Table 1-22: MPOD Input Timing Parameters .............................................................................................. 1-151

Table 1-23: RMX Serial Output Port Timing (Clock/Data/Sync Mode) Parameters .................................... 1-152

Table 1-24: MPOD Output Timing Parameters ........................................................................................... 1-153

Table 1-25: I2S Audio/Compressed I2S Output Timing Parameters........................................................... 1-154

Table 1-26: SPDIF Audio Output Timing Parameters ................................................................................. 1-155

Table 1-27: DAC Audio Output Timing Parameters .................................................................................... 1-156

Table 1-28: 256Fs Audio Clock Output Timing Parameters ........................................................................ 1-157

Table 1-29: PCI Interface Timing Parameters ............................................................................................. 1-158

Table 1-30: Async Read Timing Parameters............................................................................................... 1-159

Table 1-31: Async Write Timing Parameters ............................................................................................... 1-160

Table 1-32: Synchronous Read Timing Parameters ................................................................................... 1-161

Table 1-33: Synchronous Write Timing Parameters.................................................................................... 1-162

Broadcom Corporation

Document 7405-1HDM00-R Page xiii

2/24/2008 9T6WP

Page 14

BCM7405 Preliminary Hardware Data Module

06/29/07

Table 1-34: DDR Interface Timing Parameters............................................................................................1-164

Table 1-35: Nominal DVO Output Propagation Delays................................................................................1-165

Table 1-36: Timing for ITU656 Output at vo_656 Pins ................................................................................1-166

Table 1-37: Timing for Alternate 656 Output at vi0_656 Pins ......................................................................1-167

Table 1-38: Timing for Serial Teletext Output at rmx_data1 Pin..................................................................1-167

Table 1-39: Electrical Specifications ............................................................................................................1-169

Table 1-40: SATA Crystal Electrical Characteristics ....................................................................................1-170

Table 1-41: Absolute Maximum Ratings ......................................................................................................1-172

Table 1-42: Recommended Operating Conditions.......................................................................................1-172

Table 1-43: Thermal Data (Without External Heat Sink, 2s2p Board) .........................................................1-174

Table 1-44: Ordering Information.................................................................................................................1-180

Broadcom Corporation

Page xiv Document 7405-1HDM00-R

2/24/2008 9T6WP

Page 15

Preliminary Hardware Data Module BCM7405

06/29/07 Document Overview

General Information

DOCUMENT OVERVIEW

Overview ............................................................................................................................................ 1-2

Broadcom Corporation

Document 7405-1HDM00-R Page 1-1

2/24/2008 9T6WP

Page 16

BCM7405 Preliminary Hardware Data Module

Document Overview 06/29/07

OVERVIEW

The highlighted portion of Table 1-1 outlines information contained within the BCM7405.

Table 1-1: Document Overview

Document # Document Title Description

7405-1HDM0x General Information This document contains the following information:

• A Functional Description containing brief summaries of each functional

block contained within the BCM7405.

• Hardware Signal Descriptions

• Timing and AC Characteristics

• Electrical Characteristics

• Mechanical Drawing

• Ordering Information

7405-2HDM0x Front-End Functions The BCM7405 does not contain Front-End Functions

7405-3HDM0x Data Transport, Audio,

Video, and Graphics

7405-4HDM0x I/O Devices This document contains information on the following functionality:

7405-5HDM0x CPU Information This document contains information on the following functionality:

This document contains information on the following functionality:

• Data Transport Processor

• Advanced Audio Module

• Advanced Video Decoder

• Video and Graphics Display Module

• Broadcom Video Network (BVN) Components

• ITU656 Input

• Video Encoder Design

• High-Definition Multimedia Interface (HDMI)

• Memory-To-Memory Compositor

• RF Modulator

• Peripheral Module

• DDR-SDRAM Controller

• Memory Bus Architecture

• Shared EBI and PCI Bus

• Ethernet Controller and Interface

• Serial ATA 1.0 Host Controller

• Soft Modem Codec Interface

• Universal Serial Bus (USB) Host Interface

• Test BSC Slave Interface

• MIPS32™ CPU Core

Broadcom Corporation

Page 1-2 Overview Document 7405-1HDM00-R

2/24/2008 9T6WP

Page 17

Preliminary Hardware Data Module BCM7405

06/29/07 Functional Description

General Information

FUNCTIONAL DESCRIPTION

Top-Level Overview ........................................................................................................................... 1-4

Video Data Flow................................................................................................................................. 1-8

Data Transport Processor ................................................................................................................ 1-11

Broadcom Security Processor.......................................................................................................... 1-28

Advanced Video Decoder................................................................................................................. 1-29

Advanced Audio Module .................................................................................................................. 1-33

Video and Graphics Display ............................................................................................................. 1-36

RF Modulator.................................................................................................................................... 1-56

Memory Controller............................................................................................................................ 1-59

MIPS4380 Processor Core............................................................................................................... 1-63

Peripherals ....................................................................................................................................... 1-71

Testability ......................................................................................................................................... 1-92

Power Features ................................................................................................................................ 1-93

Broadcom Corporation

Document 7405-1HDM00-R Page 1-3

2/24/2008 9T6WP

Page 18

BCM7405 Preliminary Hardware Data Module

Functional Description 06/29/07

TOP-LEVEL OVERVIEW

The BCM7405 is a next-generation high-definition satellite, cable, and IP set-top box solution offering integrated AVC

(H.264/MPEG-4 Part 10), MPEG-4 Part 2, MPEG-2, and VC-1 video decoding technology. It also supports DivX, H.263, and

XviD formats. The BCM7405 combines a data transport processor, high-definition video decoder, advanced-audio decoder,

2D graphics processing, high-quality video scaling and motion adaptive de-interlacing, six video DACs, stereo high-fidelity

audio DACs, a MIPS 4380 class processor with FPU, and a peripheral control unit providing a variety of set-top box control

functions.

The Data Transport Processor is an MPEG-2 DVB-compliant transport stream message/PES parser and demultiplexer. It is

capable of simultaneously processing 255 PIDs via 128 PID channels in up to six independent external transport stream

inputs and five internal playback channels. The data transport supports decryption for up to 128 PID channels in all streams.

All 128 PID channels can be used by the Record, Audio, and Video interface engine (RAVE), PCR processors, message

filter as well as for output via the high-speed transport or remux module. The data transport module RAVE supports 24

channels. Each RAVE channel can be configured as either a record channel for PVR functionality or as an AV channel to

interface to audio and video decoders. The transport provides 1DES/3DES/DVB/Multi2/AES descrambling support.

memory-to-memory DMA security module may be programmed for supporting AES/1DES/3DES/CSS/CPRM/CPPM/DTCP

copy protection algorithms/standards.

The BCM7405 features an enhanced Broadcom Secure Processor providing secure boot key generation, management, and

protection.

A

An advanced video decoder is featured in the BCM7405, capable of supporting high-definition AVC, VC-1, and ATSC

MPEG-2 streams. AVC support is up to High Profile Level 4.1. New tools in the AVC Fidelity Range extensions are

supported, including 8x8 transform and spatial prediction modes, and adaptive quantization matrix. The video decoder also

supports high-definition VC-1 (Advanced Profile Level 3, Main, and Simple Profiles) and ATSC compliant MPEG-2, Main

Profile at Main and High Levels. The BCM7405 has an advanced programmable audio processor capable of decoding a

broad range of formats including Dolby Digital, Dolby Digital Plus, AAC 5.1, AAC+ Level 2, AAC+ Level 4, WMA, and MPEG

1 Layer 1, 2, and 3 with simultaneous pass-through support. 3D SRS Audio is also supported. The audio processor also

supports advanced transcoding to DTS as an example. Available audio outputs are an SPDIF and one pair of analog outputs.

High-quality video and graphics processing are integrated into the chip, featuring advanced studio quality 2D graphics

processing while still maintaining efficient use of memory bandwidth. Also included are motion adaptive de-interlacing with

3:2 pull-down, and Letterbox Detection. Digital Noise Reduction support is also included; this reduces mosquito noise and

MPEG artifacts, including block noise. Digital contour removal is also supported for low bit rate AVC streams.

The BCM7405 has a dual-stream analog video encoder with Macrovision™ that supports the following output standards:

NTSC-M, NTSC-J, PAL-BDGHIN, PAL-M, PAL-Nc, and SECAM. The following output formats are supported: composite, Svideo, SCART1, SCART2, RGB and YPrPb component. The following output resolutions are supported: 480i, 480p, 576i,

576p, 720p, and 1080i. Six output DACs are available to be shared amongst the output functions. The BCM7405 also

supports output over an HDMI interface and a Channel 3/4 RF Modulator. An ITU-R-656 output port with Teletext sideband

is available if an interface to an additional external video encoder is desired. A high-definition digital video output port is also

available.

The BCM7405 incorporates a complete R4000 family FPU-based microprocessor subsystem, including caches with bridging

to memory and a local bus. NAND and NOR flash is supported. Integrated peripherals include three UARTS, two ISO7816

smart card interfaces, counter/timers, GPIO, LED/keypad controller, IR receivers, IR blaster, UHF remote control receiver,

an integrated soft modem system side device, and BSC and SPI controllers. Advanced connectivity features include two

USB 2.0/1.1 ports, an additional independent USB 2.0/1.1 port, a serial ATA port, an Ethernet port with MAC with an

integrated PHY and a dedicated Media Independent Interface (MII).

Broadcom Corporation

Page 1-4 Top-Level Overview Document 7405-1HDM00-R

2/24/2008 9T6WP

Page 19

Preliminary Hardware Data Module BCM7405

06/29/07 Functional Description

The Macrovision enabled version of this device may only be sold or distributed to authorized Macrovision buyers. If you have

a Macrovision enabled device, then the following applies:

This device is protected by U.S. patent numbers 4,631,603,4,577,216 and 4,819,098 and other intellectual property

rights. The use of Macrovision's copy protection technology in the device must be authorized by Macrovision and is

intended for home and other limited pay-per-view uses only, unless otherwise authorized in writing by Macrovision.

Reverse engineering or disassembly is prohibited.

FEATURES

• Advanced AVC/MPEG-2/VC-1 video decoder supporting the following:

- High profile up to level 4.1 H.264/AVC streams (up to Mbps) at 30 frames/sec.

- High or main profile level 3.1 H.264/AVC streams at 60 frames/sec

- New tools in the AVC fidelity range extensions

• 8 x 8 transform and spatial prediction modes

• Adaptive quantization matrix

• DivX 3.11, 4.1, 5.x progressive and interlaced

- VC-1 advanced profile @ level 3

- VC-1 simple and main profile

- HD MPEG-2 4:2:0 streams (up to 125 Mbps) at 30 frames/sec

- SD MPEG-2 4:2:0 streams at 60 frames/sec

- Still picture decode

- HD +SD simultaneous decode

- MPEG4 P2 SP/ASP L5 SD Progressive/Interlaced

• Advanced Audio Processor supporting decode of the following formats:

- AAC LC, AAC LC+SBR Level 2, AAC+ Level 2, AAC+ Level 4

- Dolby Digital, Dolby Digital Plus

- MPEG I Layer 1, 2

- MPEG I Layer 3 (MP3)

- Windows Media Audio (WMA)

-WMA pro

- AAC HE 5.1 decode plus DTS 5.1 encode SPDIF output

- AAC HE 5.1 decode plus AC3 5.1 encode SPDIF output

- MP3 encoding

• One pair of stereo high-fidelity audio DAC

• 3D SRS Audio Support

2

• One I

• One I

• One SPDIF output

• Advanced 2D-effects graphic engines

• Digital Noise Reduction (DNR)

• Digital Contour Removal

S input port

2

S output port

- Studio quality text and graphics at HD resolution

- Supports multiple layers and windows

- Reduces MPEG artifacts including block noise reduction

- Reduces mosquito noise

Broadcom Corporation

Document 7405-1HDM00-R Top-Level Overview Page 1-5

2/24/2008 9T6WP

Page 20

BCM7405 Preliminary Hardware Data Module

Functional Description 06/29/07

- Removes banding effects in low bit rate video applications

• Motion adaptive de-interlacer (MAD) with reverse 3:2/2:2 pull-down

• Letter box detection

• ITU-R-656 Digital input. Film grain technology.

• Video encoder

- Supports one SD/HD video stream

- Additionally supports one SD video stream scaled down from the HD content or independent SD.

- NTSC-M, NTSC-J, PAL-BDGHIN, PAL-M, PAL-Nc, SECAM Analog Outputs

- 480i/480p/576i/576p/720p/1080i output formats

- Component RGB or YPrPb Output

- Macrovision 7.1 Support

- Euro-SCART

- Displays component, S-video, and composite via six on-chip DACs

• HDMI/DVI with HDCP 1.2

• ITU-R-656 and 12-bit double clocked 24 bpp HD DVO Outputs

• Next generation Broadcom Security Processor supporting external codes and keys

• AES/1DES/3DES/CPRM/CPPM/CSS/DTCP copy protection algorithms/standards

• DVB, ARIB, and DC2-compliant transport demux with 1DES/3DES/DVB/Multi2/AES descramblers

• V.92 capable soft modem with:

- Integrated SiLab Si305X System Side Device

- Optional five-wire external interface

• 33 MHz PCI 2.3 with 5 volt tolerance

• On chip VCXOs

• Two DDR DRAM controllers

- Primary 64-/32-bit DDR controller

- Optional 32-/16-bit DDR controller

• Dual USB 2.0 host controller with dual port integrated transceiver

- Additional USB 2.0/1.1 host/client controller independent from the dual USB 2.0 controller

• Dual serial ATA-II interface

- SATA ports support hot plug and external SATA drives

• MIPS 4380 class processor with FPU

• RF Modulator with BTSC encoder

• Dual Ethernet

- First MAC to connect to internal integrated 10/100 BASE-T PHY

- Second MAC to connect to MII interface

The BCM7405 incorporates a complete MIPS 4380 Floating Point CPU microprocessor subsystem. including with bridging

to memory and a local bus, where external peripherals can be attached. Integrated peripherals include the following:

• Three UARTS

• UARTC is 16550 compatible

• Two ISO7816 smart card interfaces

• Counter/timers

• GPIO

• LED/keypad controller

Broadcom Corporation

Page 1-6 Top-Level Overview Document 7405-1HDM00-R

2/24/2008 9T6WP

Page 21

Preliminary Hardware Data Module BCM7405

06/29/07 Functional Description

• Two IR receivers

• IR blaster

• UHF remote control receiver

• BSC and SPI controllers

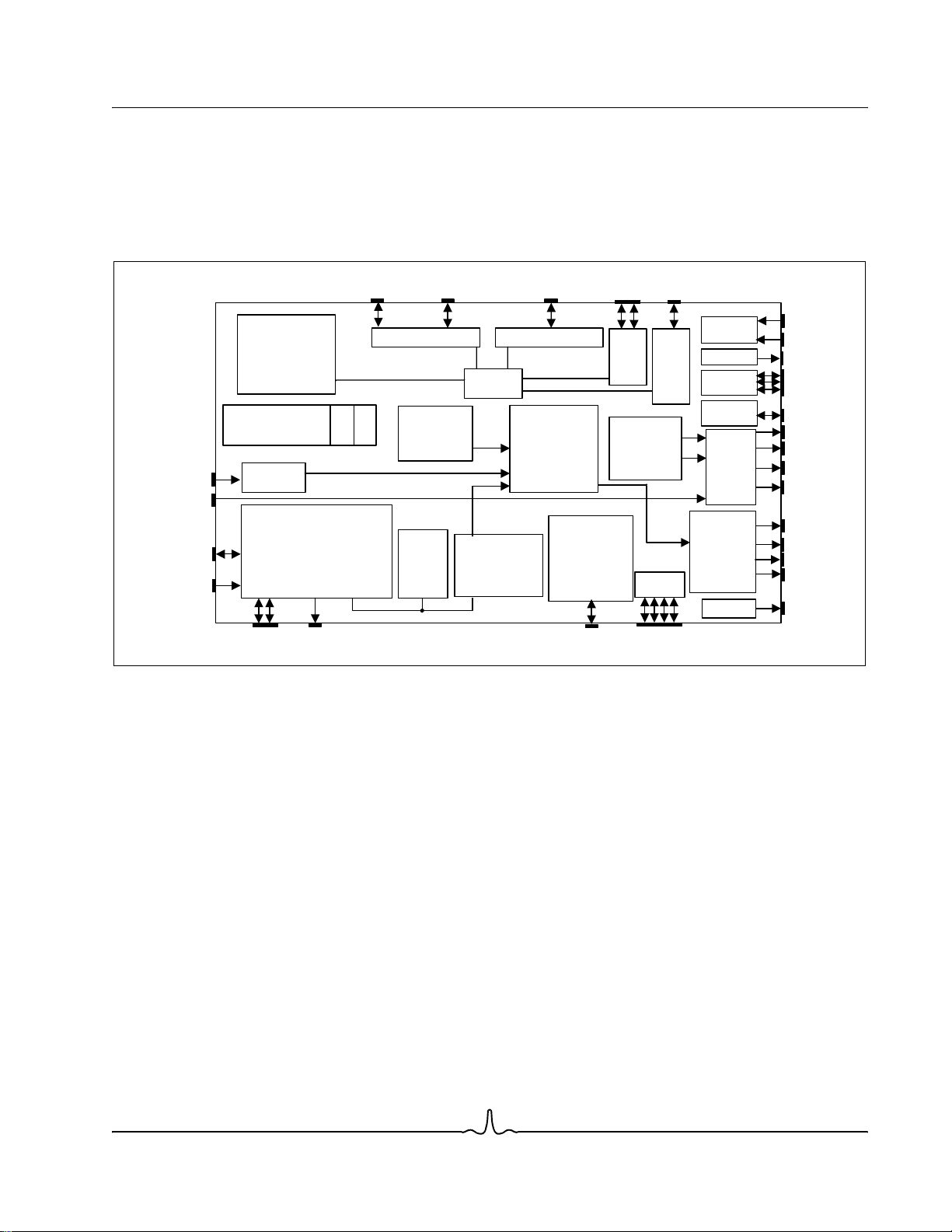

Figure 1-1 on page 1-7 shows the BCM7405 functional block diagram.

ITU-R-656

2

S In

I

MCARD/

SCARD

Transport Input x6

PCI 2.3 and Flash

400 MHz

MIPS32/16e

32KI and 64KD

MMU and FPU

8K RAC

128K L2

Secur e Pr ocessor

ITU-R-656

Decoder

MPEG-2/DVB Transport with

Descrambling and Conditional

Access Support

ISO7816 I/F

x2

R

O

M

RMX

x2

DMA

Configurable

64-bit DDR2

Video

-Scalers

- Compositors

- Digital noise

reduction

- Delinterlacing

Soft Modem,

Si305X,

Ethernet

10/100

BASE-T

nd

Enet MAC

2

Gateway

Services

USB 2.0 x2

Dual Serial

ATA-2

Bus Bridge DRAM Controller

O

T

P

Advanced

2D Graphics

Display

Engine

Dual

PVR

Engine

w/T r ick

Modes

High definition

AVC/MPEG-2//

MPEG-4/VC-1

Video Decoder

Figure 1-1: Functional Block Diagram

Dual

USB

2.0

Multiformat

Audio

Decoder

BSC

BSC x4

USB 2.0

Host/Client

USB

2.0

Composite

NTSC/PAL

IR/UHF

RX

IR TX

Tr iple

UARTs

GPIO

PCM

Audio

Engine

and

DACs

Dual

VEC with

six DACs

RF Mod.

IR In x2

UHF In

IR Out

UARTx3

GPIO

L

R

SPDIF

I2S Out

HD/SD Video

SD Video

ITU-R-656/TTX

HDMI

Channel 3/4

Broadcom Corporation

Document 7405-1HDM00-R Top-Level Overview Page 1-7

2/24/2008 9T6WP

Page 22

BCM7405 Preliminary Hardware Data Module

Functional Description 06/29/07

VIDEO DATA FLOW

OVERVIEW

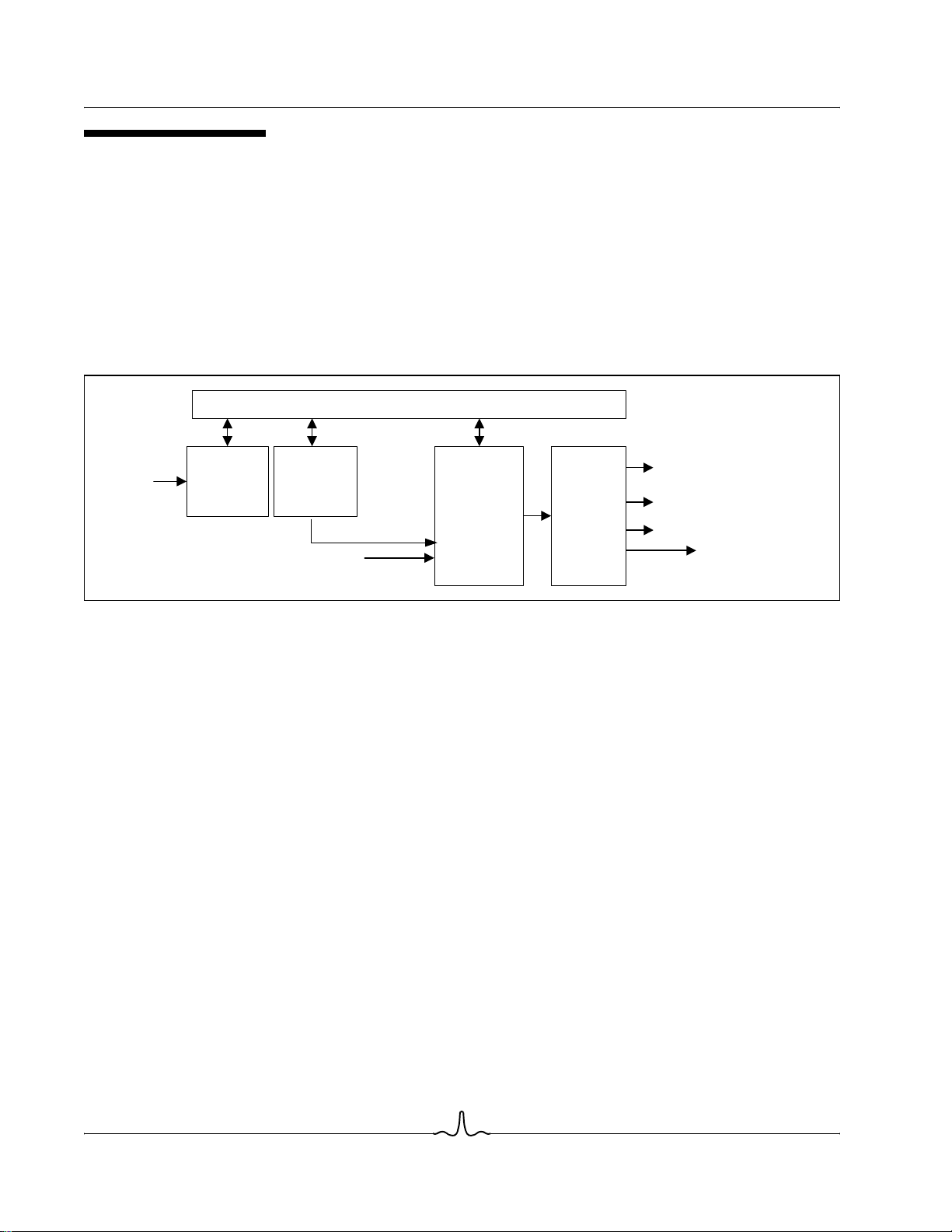

At the top level, video signals flow through the video portion of the BCM7405 as compressed digital data or digitized

baseband analog video. From the appropriate decoder (AVC/MPEG-2/VC-1 decompression or ITU-R-656 video decoding),

the video data passes to the video processing stage where any scaling can be applied and the resulting video can be stored

to memory for later display. During this video processing, any graphics or additional video can be combined just before being

displayed. The manipulated video is then sent to the VEC(s) for display through either the analog DAC outputs, the ITU-R656 output, and/or through the HDMI interface. Figure 1-2 illustrates this high-level data flow.

DRAM Memory

Data

Transport

Processing

AVC/MPEG-2/

VC-1 Video

Decoder

ITU-R-656

Video

Processing

(Scaling,

Capture,

Compositing)

Video

Encoder(s)

Six Video DACs

HDMI output

HD DVO output

ITU-R-656

Figure 1-2: Video Data Flow Diagram

COMPRESSED VIDEO INPUT

Compressed video data normally enters the device in the form of MPEG transport streams. These come through the Data

transport that parses the stream and performs preprocessing. Video can also be stored directly into DRAM via local or

network peripherals—such as the HDD (for PVR), home networking (Ethernet) and so on.

The data transport is responsible for the following functions:

• Error detection in the video stream

• Locking the time base to PCR/SCR embedded within the stream

• Extracting PTS and DTS timestamps

• Extraction of start codes (and building index tables for these codes)

A detailed description of the data transport is provided in “Data Transport Processor” on page 1-11.

Broadcom Corporation

Page 1-8 Video Data Flow Document 7405-1HDM00-R

2/24/2008 9T6WP

Page 23

Preliminary Hardware Data Module BCM7405

06/29/07 Functional Description

PERSONAL VIDEO RECORDING

Processing of compressed streams for Personal Video Recording (PVR) extends the normal processing by adding a number

of capabilities. In recording for PVR, the transport packets associated with the program selected are recorded to a circular

buffer in DRAM for transfer to the hard disk drive (HDD). The compressed data is optionally scrambled using the mem-tomem security block. In addition, the video elementary stream (ES) data contained within the selected PID is searched for

the presence and location of selected start codes, such as PES packet headers, sequence start codes, picture start codes,

and the first slice start codes within each picture. Sufficient data from the compressed streams following the start codes is

also retained to determine the picture type (I, B, or P) and other pertinent information. All of this selected information is written

to memory in a circular buffer to facilitate additional processing by the Host MIPS as required, and to record the data to the

HDD. The PES packets can be recorded as an alternative to Transport streams.

In PVR playback, the transport processor reads linked lists of compressed audio and video from DRAM, optionally

descrambling it using mem-to-mem security block, and processes it for decompression and display in a manner that is similar

in many ways to normal (non-stored) decoding. The PVR playback supports special capabilities for fast and slow decoding

and descrambling, and data flow management in the absence of a physical time base associated with the stream (as would

normally be present in broadcast operation).

DIGITAL VIDEO DECOMPRESSION

Decompression of digital video is performed by the AVC/MPEG-2/VC-1 processor. The decoder extracts compressed video

and index tables from DRAM (created by the data transport). The video is decoded or decompressed and the resultant is

stored back into DRAM in picture (frame or field) buffers in YCrCb 4:2:0 format. The decoder needs multiple picture buffers

to account for differing time bases and decode rates.

ITU-R 656 INPUT

The BCM7405 supports an ITU-R 656 video input. The input has a dedicated VBI decoder to handle Teletext, NABTS, Close

Caption, CGMS-A, Gemstar, and WSS.

VIDEO PROCESSING

The display engine takes in uncompressed video from either the AVC/MPEG-2/VC-1 decoder or the digital ITU-R-656 input.

The display engine can scale the video in horizontal and vertical directions and either display the video immediately (in-line)

or capture it to memory for later viewing. Scaling is optional, and may be needed for normal display of digital or analog video.

The scaling function incorporates a format conversion capability for converting between various standard definition (SD) and

HD formats of video signals and those required by the displays. Capture of video to memory is used either when it is

advisable to minimize peak DRAM bandwidth requirements, or when it is unavoidable due to the constraints of the video

input and output timing. In general, capturing to memory when scaling reduces peak DRAM bandwidth when the scale factor

is less than 1.0. The video and graphics processing is further expanded in “Video and Graphics Display” on page 1-36.

Broadcom Corporation

Document 7405-1HDM00-R Video Data Flow Page 1-9

2/24/2008 9T6WP

Page 24

BCM7405 Preliminary Hardware Data Module

Functional Description 06/29/07

VIDEO ENCODER

The VEC supports a variety of analog video standards (NTSC [all variations], PAL [all variations], SECAM, 480i, 480p, 576i,

576p, 720p, 1080i, 1080p24, and 1080p30) as well as HDMI digital video standards. 1080p50 and 1080p60 display formats

are not supported.

Each VEC also receives encoded VBI signals from associated VBI encoders. The VBI data combines with the appropriate

lines of video. This arrangement supports Closed Caption, NABTS, Teletext, CGMS-A, Gemstar, SCTE20/21, AMOL I/II,

analog pass-through, and other VBI formats on the CVBS and Y/C outputs.

The VEC outputs either an HD or SD stream on the first television output, and a scaled down version of an HD image on the

second television output. The BCM7405 provides a single user experience that allows for simultaneous outputs of the same

content for high definition and standard definition televisions.

VIDEO DACS

The BCM7405 integrates a set of six 10-bit video DACs, using Broadcom’s proven high-speed CMOS DAC technology.

These DACs are configured to support SCART1 as well as component, S-Video (Y/C), and composite video (CVBS) outputs.

Table 1-2 outlines the configuration parameters.

Table 1-2: Video DAC Configuration

Usage Mode Video Display 1 Video Display 2

Unless otherwise noted, each box indicates the analog format that is provided for the indicated usage mode. Each display

has its own graphics compositor, which can be independently controlled.

3:3 Configuration Component (including 480P RGB) Composite and S-Video of the same

content as video display 1.

4:2 Configuration Component (including 480P RGB) + Composite Composite or S-Video of the same

content as video display 1.

Broadcom Corporation

Page 1-10 Video Data Flow Document 7405-1HDM00-R

2/24/2008 9T6WP

Page 25

Preliminary Hardware Data Module BCM7405

06/29/07 Functional Description

DATA TRANSPORT PROCESSOR

OVERVIEW

The data transport processor is an MPEG-2/DIRECTV transport stream message/PES parser and demultiplexer. It can

simultaneously process 255 PID filters via 255 PID channels in up to six independent external transport stream inputs and

five internal playback channels, with decryption for all 255 PID channels. It supports message/PES parsing for 128 PID

channels with storage to 128 external DRAM buffers, and it provides 512 4-byte generic section filters that can be cascaded

to provide effectively longer filters (up to 64-bytes or 128 filters of 16-bytes each). The data transport module provides two

sets of a two-channel remux output. The data transport module has a RAVE (record, audio, and video interface engine)

function, which can be configured to support 24 channels. Each RAVE channel can be configured as record channel for PVR

functionality or as an AV channel to interface audio and video decoders.

FEATURES

• Capable of processing six independent external transport stream inputs and five internal playback channels

simultaneously.

• MPEG and DIRECTV transport streams can be processed concurrently.

• Supports ARIB.

• Supports TSMF as defined by Japan Cable Television Engineering Association spec JCTEA STC-007-2.

• Maximum input band transport stream rate supported is 100 Mbps.

• Maximum combined transport stream burst rate can be greater than 216 Mbps based on usage.

• Maximum combined transport stream average rate after PID filtering is 216 Mbps.

• Supports 255 PID filters via 255 PID channels.

• Supports a 255-entry Primary PID table for parsing MPEG transport packets. Primary PID table entries can be

arbitrarily assigned to any of the parser bands. The parser bands are processed uniquely, even in cases when they use

the same PID.

• Supports a 255-entry Secondary PID table for parsing MPEG transport packets. Each entry in Secondary PID table is

associated with PID table entry and packets with primary or secondary PID can be mapped to same PID channel for

PID merge function.

• Mode to store complete transport packet in the external DRAM message buffers.

• PES packet extraction for up to 128 PID channels.

• PSI section extraction for up to 128 PID channels with filtering.

• Only PID channels 0-127 are routed to Message filer.

• Supports 512 generic filters capable of filtering up to 4 bytes each for PID channels 0-127. These filters can be

cascaded to provide effectively longer filters (up to 64-bytes).

• Each generic filter includes a 4-byte inclusion mask and a 4-byte exclusion mask for independent inclusion and

exclusion per bit filtering.

• Generic filters are divided into 16 banks, each with 32 4-byte filters. Banks of 4-byte filters can be cascaded to make up

groups of filters that are effectively up to 64 bytes wide. Each PID channel can independently select one group of filters.

Each PID channel can use any number up to 32 filters in that group. Each PID channel can independently select its own

programmable generic filter offset.

• Includes a special addressing mode for filtering of MPEG and Private stream messages for PID channels 0-127.

• The special addressing mode filter and the generic section filters can be enabled simultaneously for each PID channel.

• Data extracted from the parser bands is stored in one or more of the 128 message buffers and/or using RAVE (record,

audio and video interface engine) in the external system DRAM.

• Supports 10 external DRAM message buffer sizes: 1K, 2K, 4K, 8K, 16K, 32K, 64K, 128K, 256K, and 512K bytes.

Broadcom Corporation

Document 7405-1HDM00-R Data Transport Processor Page 1-11

2/24/2008 9T6WP

Page 26

BCM7405 Preliminary Hardware Data Module

Functional Description 06/29/07

• Each message buffer is associated with a PID channel.

• Section filter supports the capability to overwrite the CRC of a valid MPEG PSI message with a fixed pattern or with the

section filter match tag, or append of filter match tag to each saved message.

• Error handling of messages.

• Messages written into the message buffer are optionally 32-bit word aligned. Message length is unchanged.

• Supports 24 RAVE channels. Each RAVE channel can be configured as a record channel for PVR or as an AV channel

to interface to audio and video decoders.

• Each record channel can record up to 128 PID channels from a transport stream.

• Supports up to six transport parser index tables for use in PVR applications.

• Supports up to 32 SCDs (Start Code Detect Table). One SCD is required for each AV channel and up to eight SCDs

can be assigned to each record channel for Start Code Detect Index Table.

• Supports parsing of Transport/PES data to ES and generate CDB/ ITBs for audio/video decoders.

• Five independent playback channels to provide data to the video, audio and/or two remux modules.

• Supports data transport local timestamp insertion for record and playback of transport streams.

• PID filter, Packet Substitution, and PCR correction support for two dual-channel remux Interface blocks with a maximum

100 Mbps rate. Combines any two transport streams from the available input streams or playback channels.