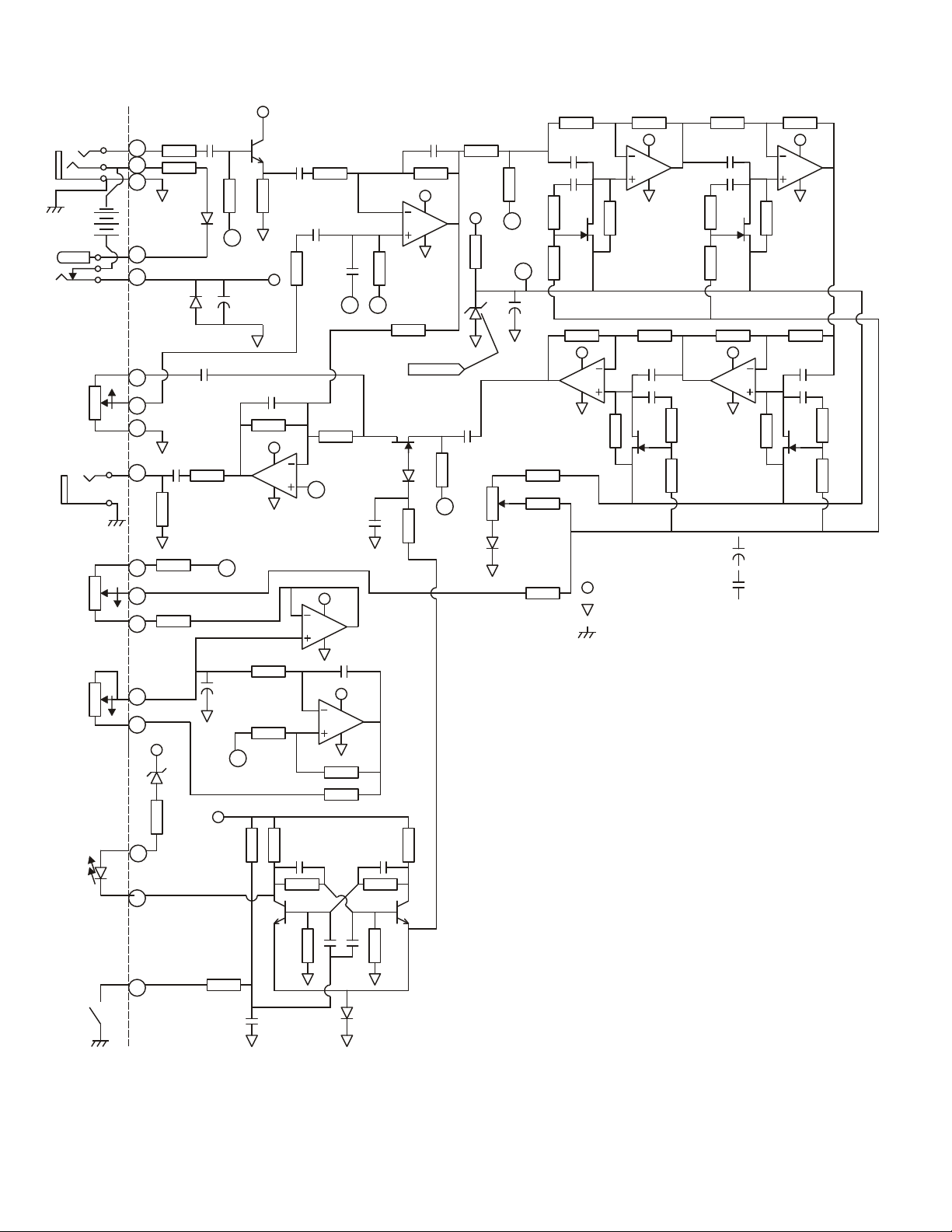

Boss PH-1r scheme

+

Input

9V

2

6

11

7

10

Copyright 2007

REGEN

8

1

12

OUT

DEPTH

B100k

RATE

C1M

5

3

4

14

13

9

+

Copyright 2007

Check

Cancel

15

17

16

473

10K

100

PD

PD

1uF

R.G. Keen

1uF

470

100K

10K

68K

ZD

3.9K

VR

15/16

Tant

+

VR

1M

470K

IC1A

VR

2SC732Gr

10K

+

100uF

16V

47p

47K

+

1

150K

150K

56K

100K

R.G. Keen

2SC1685

(x2)

100

103

Boss PH-1r

1uF

47K

IC1B

6

5

333

12K

2

3

470P

22K

VR

+

IC4A

+

470K

4.7K

56K

220P

VR

101

0.01

IC4B

470P

SD

47K

VR

47K

2SK30Y

SD

473

56K

100K

56K

220P

47p

47K

+

8

4

NOTE 1

VR

1M

10K

1.5K

7

+

1.8K

ZD

1uF

1M

B100K

SD

Notes:

1. Bias voltage setting zener, probably 3.0-5.0V. Output of all opamps in

the signal circuits will sit near this voltage. Used for Vr throughout the circuit..

2. Component values from RevK of the PCB. Tracing from Rev R

3. Details where I was unclear I filled in with info from the PH-1.

The PH-1r is slightly different from other 4-stage phasers of nearly the same

vintage. The differences are probably what account for its following.

The input signal is buffered, then divided by two to lower the overal signal

level in the phase stages. This cuts JFET distortion from the JFET variable

resistors used for phasing. The gain is later made up in the output buffer/

mixer.

The JFETs are also set up in the drain-feedback circuit for linearizing

the JFET’s response as a voltage variable resist or. Again, this cuts the

prominent JET distortion of other phasers.

Note the schematic conventions: Where two lines intersect in a T,

they connect. Where a wire crosses another, there is a semicircle. Unless

I made a mistake, there are no intersections with four segments meeting

at 90 degrees each.

Special thanks to Ry Hoffman, whose help made this possible to compile.

Please note that it is always possible I made a mistake in tracing. If you

find an error, please let me know.

R.G .Keen Dec 2007

Co pyright R.G. Keen 2007. All rights reserved.

103

103 103

1.5K

VR

4.7uF

47K

1M

2.2M

330K

330K

10K

+

1

IC2A

100K

IC1, 2, 3 = JRC4558D

IC4 = TL022

+

VR

Bias

Adjust

10K

+ +

IC2B

100K

10K

2

3

= +9V on the PCB

= PCB gnd

= box/chassis gnd

103

103

330K

All phase

330K

10K

103

330K

330K

IC3A

2SK30A

GR

JFETs

100K

10K

+

100K

= polarized, + at top

= NP

PD = 1A rectifier

SD = signal diode

ZD = zener diode

10K

IC3B

10K

103

103

330K

330K

Loading...

Loading...