Page 1

1

2

3 4 5 6 7 8 9 10

11

A

B

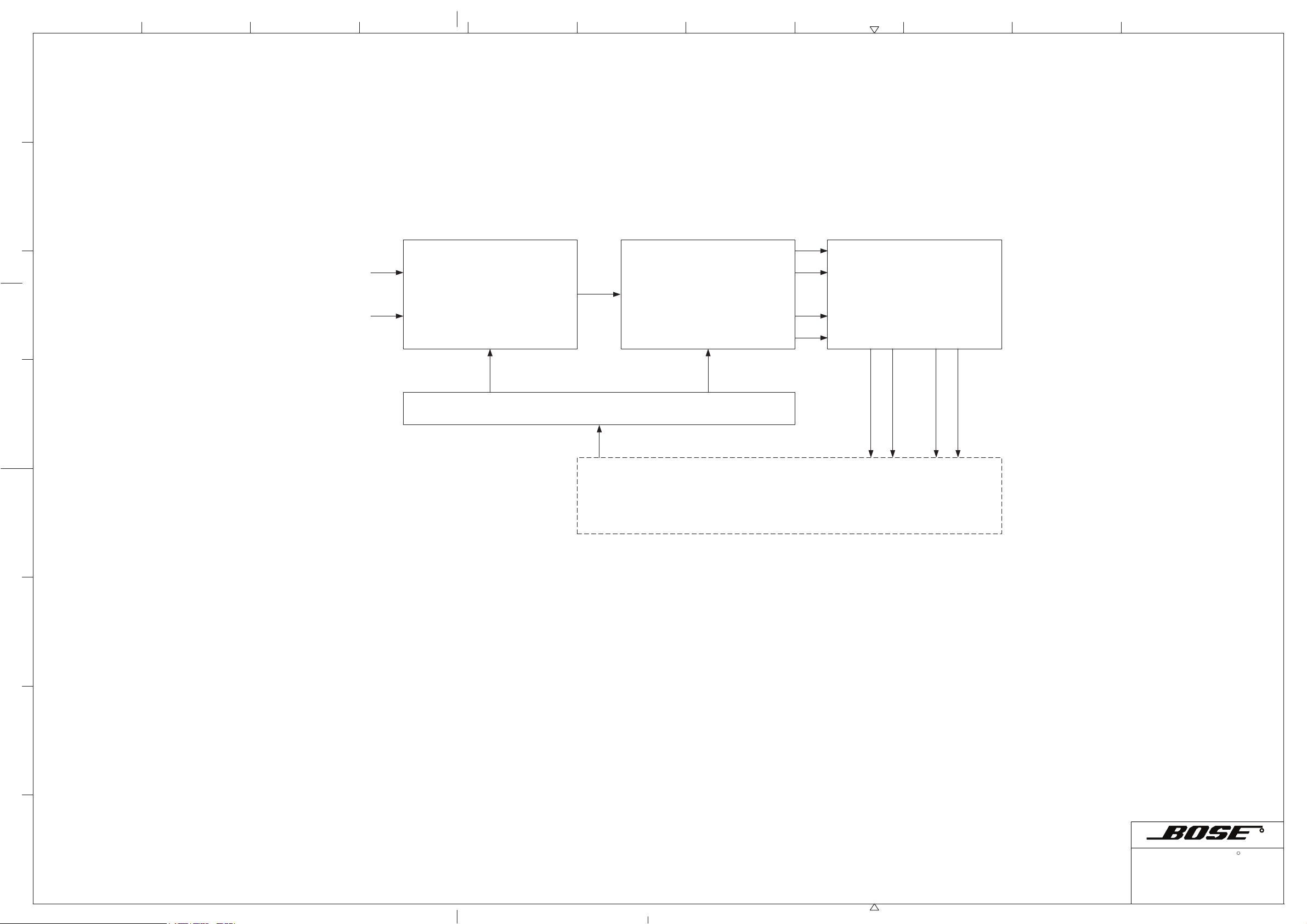

Optical Input

(1) DIR

C

SPDIF Input

Page = 2 of 5

(2) DSP

Page = 3 of 5

(3) SRC-BiDir

Page = 4 of 5

(4) CPU (I2C)

D

Page = 5 of 5

MB circuit diagram

E

F

G

BLOCK DIAGRAM

OT1-200121

R

H

AuBit

FRAMINGHAM, MA 01701-9168

ControlSpace

ESP-88C/ESP-00 Processors

Dolby/DTS PCB Assy., Rev. B

Part Number 302210

Sheet 1 of 5

R

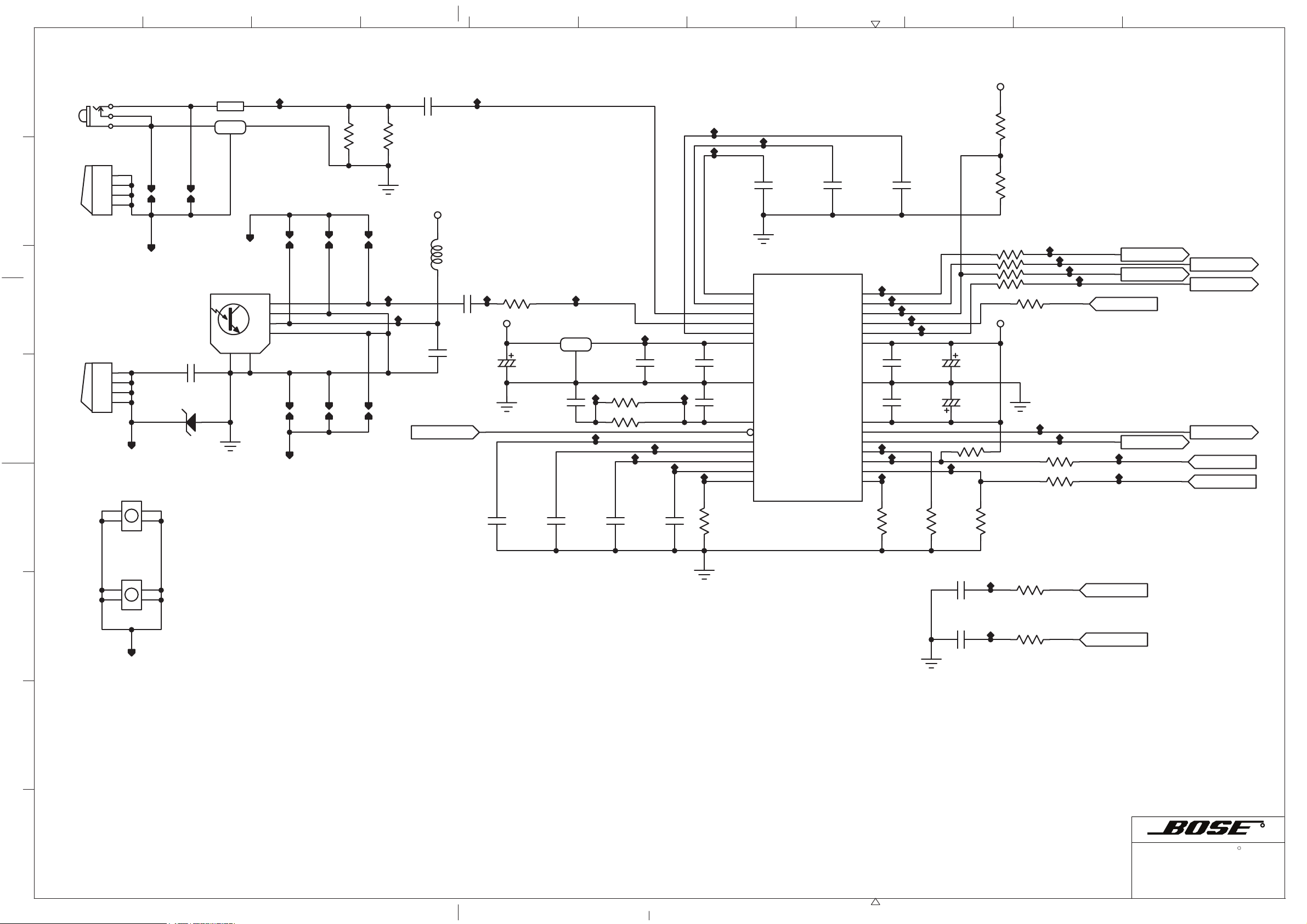

Page 2

SPDIFIN

CN100

A

MR552LS(BLK)

B

C

D

E

1

1

2

3

FG103

OPEN

1

2

3

4

OPTIN

FG102

OPEN

1

2

3

4

FG101

FG

Z107

GAP

FG

D100

OPEN

2

L102

BK2125HM102

3

O1I

G

2

Z106

GAP

M100

TORX173

C102

OPEN

5C16

3 4 5 6 7 8 9 10

PP117

L101

NFM21CC223

Z102

GAP

FG

1

OUT

2

GND

3

VCC

4

GND

C2

Z105

GAP

FG

Z101

GAP

Z104

GAP

R101

150

Z100

GAP

Z103

GAP

C104

0.022u

R100

150

PP104

PP116

/RSTDIR

D5V

L100

47uH

C119

0.022u

PP133

D3R3V

C103

0.1uZ

C108

0.022u

PP118

16V10u

0.022u

R102

150

NFM21CC223

1

C101

C115

0.022u

C118

PP119

L103

I

O

G

2

PP130

C117

0.022u

3

PP124

PP132

R106

33k

R105

3.3k

PP122

C116

0.022u

C100

0.1uZ

PP131

PP123

PP121

PP127

PP129

C107

0.022u

C110

1000p

C109

1000p

PP120

R107

10k

9

10

11

12

13

14

1

RXP3

2

RXP2

3

RXP1

4

RXP0

5

RXN

6

VA

7

AGND

8

___

FILT

RST

RXP4

RXP5

RXP6

__

RXP7

AD0/CS

PP128

C106

0.022u

M101

CS8416

CDOUT/SDA

0.022u

OLRCK

OSCLK

SDOUT

OMCK

RMCK

VD

DGND

VL

GPO0

GPO1

GPO2/AD2

CCLK/SCL

CDIN/AD1

C105

28

27

26

25

24

23

22

21

20

19

18

17

16

15

PP113

PP112

PP111

C111

0.1uZ

C113

0.1uZ

PP125

PP115

PP126

R103

10k

PP110

PP109

R104

10k

C112

16V10u

C114

16V10u

PP114

D3R3V

R112

10k

Selection of

soft/hard mode

R111

OPEN

RA100

RA33

1

8

2

7

3

6

4

5

D3R3V

R109

OPEN

R114

0

R110

OPEN

PP108

PP107

PP106

PP105

R108

33

256FS

OMCK = 256FS

PP103

PP102

R113

0

AFSX1

AXR1[4]

DIRFLG1

PP101

PP100

11

ACLKX1

AHCLKX1

DIRFLG0

I2C1_SDA

I2C1_SCL

FG100

C121

22p

PP135

R116

33

I2C1_SDA

C120

F

22p

PP134

R115

33

I2C1_SCL

G

G

(1)DIR

OT1-200121

R

H

AuBit

FRAMINGHAM, MA 01701-9168

ControlSpace

ESP-88C/ESP-00 Processors

Dolby/DTS PCB Assy., Rev. B

Part Number 302210

Sheet 2 of 5

R

Page 3

1

2

3 4 5 6 7 8 9 10

11

A

B

C

D

E

F

C185

6.3V

G

470u

H

MxASP0 Audio Signals

AXR0[5]=ESP Audioー0

AXR0[6]=ESP Audioー1

AXR0[7]=ESP Audioー2

AXR0[8]=ESP Audioー3

AXR0[6]

AXR0[8]

LRCLKE

AXR1[4]

AXR1[2]

AXR1[0]

MxASP1 Audio Signals

AXR1[0]=Dolbyー0

AXR1[1]=Dolbyー1

AXR1[2]=Dolbyー2

AXR1[3]=Dolbyー3

AXR1[4]=DIR

AXR0[5]

AXR0[7]

BCLKE

256FS

AXR1[3]

AXR1[1]

D3R3V

C171

0.1uZ

PP230

P_RST

AHCLKX1

ACLKX1

AFSX1

/RSTDSP

DSPTMS

DSPTRSTn

X150

CX5-24.576MHZ

C198

470p

DSP0TDI

DSPEMU0

DSPTCK

C200

12p

DSP0TDO

DSPEMU1

TCK-RET

C186

D1R2V

0.047u

L150

5.2uH

C187

1000p

C170

0.1uZ

R178

1M

PP160

R175

33

PP158

C199

12p

PP255

R177

33

PP163

RA154

RA33

4

5

3

6

2

7

1

8

R190

33

4

5

3

6

2

7

1

8

RA155

RA33

C172

C173

0.1uZ

0.1uZ

PP254

R176

33

PP261

PP262

PP263

PP264

R163

0

C197

470p

D3R3V

NFM21CC223

M150

TPS54312PWP

1

AGND

2

VSENSE

3

NC

SS/ENA

4

PWRGD

VBIAS

5

BOOT

6

PH

7

PH

8

PH

PGND

9

PH

PH

PGND

PGND

10

PP265

L151

1

RT

FSEL

VIN

VIN

VIN

PP164

PP166

PP232

PP234

I

2

PP236

D3R3V

3

O

G

20

19

PP161

18

17

16

15

14

13

12

11

16V100u

PP165

PP167

PP233

PP235

D1R2V

PP260

C201

16V10u

R152

68k

PP162

C188

D3R3V

C168

0.1uZ

1

VSS

2

AHCLKX0/AHCLKX2

3

AMUTE0

4

AMUTE1

5

AHCLKX1

6

VSS

7

ACLKX1

8

CVDD

9

ACLKR1

10

DVDD

11

AFSX1

12

AFSR1

13

_____

VSS

14

RESET

15

VSS

16

CVDD

17

CLKIN

18

VSS

19

TMS

20

____

CVDD

21

TRST

22

OSCVSS

23

OSCIN

24

OSCOUT

25

OSCVDD

26

VSS

27

PLLHV

28

TDI

29

TDO

30

VSS

31

______

DVDD

32

EMU[0]

33

______

CVDD

34

EMU[1]

35

TCK

36

VSS

C196

0.1uZ

PP279

PP176

C190

PP175

0.1uZ

D5V

T D

C189

0.1uZ

T A

C169

0.1uZ

4

5

C167

0.1uZ

143

144

AFSX0

AHCLKR0/AHCLKR1

T A

C166

0.1uZ

R185

PP231

D1R2V

D3R3V

130

131

132

133

134

135

136

137

138

139

140

141

142

VSS

AFSR0

ACLKX0

ACLKR0

VSS

CVDD

DVDD

AXR0[10]/AXR1[3]

AXR0[11]/AXR1[2]

AXR0[12]/AXR1[1]

AXR0[13]/AXR1[0]

AXR0[14]/AXR2[1]

AXR0[15]/AXR2[0]

T

A

1

7

33

PP256

PP253

124

125

126

127

128

129

VSS

VSS

DVDD

CVDD

AXR1[5]/SPI1SOMI

AXR1[4]/SPI1SIMO

M154

TMS320DA708RFP

EM_CAS

______38EM_WE

_____39EM_WE_DQM[0]

__40VSS41EM_D[7]42DVDD43EM_D[6]44CVDD45EM_D[5]46EM_D[4]47VSS48EM_D[3]49EM_D[2]50DVDD51EM_D[1]52EM_D[0]53CVDD54VSS55EM_D[15]56EM_D[14]57CVDD58EM_D[13]59EM_D[12]60DVDD61EM_D[11]62VSS63EM_D[10]64EM_D[9]65CVDD66EM_D[8]67EM_WE_DQM[1]

37

PP237

PP238

PP239

PP240

123

RA151

RA33

876

T

T

T

L

C

D

A

W

S

Q

E

123

4

876

5

RA163

RA33

T

T

T

T

D

D

D

D

0

0

0

0

5

6

7

4

PP244

PP243

PP242

PP241

123

4

5

T

T

D

D

0

0

2

3

876

RA162

T

T

D

D

0

0

1

0

RA33

4

5

T

T

T

D

D

D

1

1

1

3

4

5

R179

33

122

123

CVDD

______

AXR0[7]/SPI1_CLK

PP248

PP247

PP246

PP245

123

RA161

RA33

876

T

D

1

2

Spec of 128Mbit-SDRAM

T

T

T

T

T

A

A

A

A

A

1

1

1

1

1

2

3

4

5

6

876

123

5

RA156

RA33

4

PP257

PP258

PP259

BOOT MODE SELECT

R186

10k

R187

10k

R188

10k

R189

10k

D3R3V

RY_BY

109

110

111

112

113

114

115

116

117

118

119

120

121

VSS

VSS

VSS

AXR0[4]

AXR0[5]/SPI1S*

AXR0[6]/SPI1E*

______

AXR0[1]

AXR0[2]

AXR0[3]

__68DVDD69VSS70EM_CLK71EM_CKE72VSS

DVDD

AXR0[0]

SPI0_SIMO

SPI0CLK/I2C0SCL

SPI0SCS/I2C1SCL

SPI0SOMI/I2C0SDA

SPI0ENA/I2C1SDA

VSS

_____

EM_OE

_

DVDD

EM_RW

________

CVDD

EM_CS[2]

______

VSS

________

EM_RAS

EM_CS[0]

EM_BA[0]

VSS

EM_BA[1]

EM_A[10]

DVDD

EM_A[0]

CVDD

EM_A[1]

EM_A[2]

VSS

EM_A[3]

CVDD

EM_A[4]

EM_A[5]

VSS

DVDD

EM_A[6]

EM_A[7]

VSS

CVDD

EM_A[8]

EM_A[9]

EM_A[11]

DVDD

D1R2V

D3R3V

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

R171

OPEN

R174

10k

R170

10k

R173

OPEN

R169

OPEN

R172

10k

PP153

PP154

I2C1=Slave Mode

ADDRESS[0]= CS8416

ADDRESS[1]= EEPROM

ADDRESS[2]= DSP

ADDRESS[3]= NC

D1R2V

D3R3V

PP281

PP177

PP280

PP157

PP156

PP155

PP278

PP266

PP267

PP268

PP269

PP270

PP271

PP272

PP273

PP274

PP275

PP276

PP277

D3R3V

C195

6.3V470u

D1R2V

C194

6.3V470u

R182

OPEN

R184

OPEN

R180

OPEN

R181

33

R183

33

RA152

1

2

3

4

RA153

1

2

3

4

RA157

1

2

3

4

RA158

1

2

3

4

RA159

1

2

3

4

RA164

RA10k

10

RA33

RA33

RA33

RA33

RA33

8

7

6

5

8

7

6

5

8

7

6

5

8

7

6

5

8

7

6

5

15

2

3

4

6

7

8

9

R162

10k

PP152

PP151

PP150

T OE

T CS2

T RAS

T CS0

T BA0

T BA1

T A10

T A00

T A01

T A02

T A03

T A04

T A05

T A06

T A07

T A08

T A09

T A11

T A12

T A13

T A14

T A15

T A16

T A17

NCA19

NCA20

NCA21

BANK = 4

WIDTH = 16

DEPTH = 2M

MAX CE = 2pin

ColumnA= A8`A0(DSP=EA10-EA2)

RowA= A11`A0(DSP=EA13-EA2)

BANK Select = A12/A13(DSP=EA14/15)

Precarge = A10(EA12)

PINCAP5

PINCAP7

PINCAP6

R164

10k

R165

10k

R166

10k

R167

10k

R168

10k

I2C0_SDA

SPI0SIM0

I2C0_SCL

C192

22p

PP159

I2C1_SCL

I2C1_SDA

R156

33

I2C-BUS

D3R3V

C160

C161

0.1uZ

0.1uZ

0.1uZ

D3R3V

DECOUPLING FOR SD-RAM

C163

C164

0.1uZ

0.1uZ

C165

0.1uZ

D3R3V

C154

C155

0.1uZ

0.1uZ

0.1uZ

D1R2V

C151

0.1uZ

C150

0.1uZ

C152

0.1uZ

T CLK

C159

C156

0.1uZ

D3R3V

C162

0.1uZ

C153

I2C1=Master Mode

Optional EEPROM

(Full Address)

T A00

T A01

T A02

T A03

T A04

T A05

T A06

T A07

T A08

T A09

T A10

T A11

T BA1

T BA0

T LDQ

T UDQ

T CKE

T CLK

T CAS

T CS0

T RAS

T WE

T CS0

T CKE

NCA21

NCA20

NCA19

T A17

T A16

T A15

T A14

T A13

T A12

T A11

T A10

T A09

T A08

T A07

T A06

T A05

T A04

T A03

T A02

T A01

T A00

T BA1

T CS2

T OE

T WE

I2C1_SCL

I2C1_SDA

PP199

PP198

PP195

PP194

PP191

PP190

PP187

PP186

PP183

PP182

PP181

PP180

D3R3V

R158

10k

R157

10k

PP217

PP218

PP228

PP227

PP224

PP223

PP222

D3R3V

C191

0.1uZ

PP197

PP196

PP193

PP192

PP189

PP188

PP185

PP184

PP179

PP178

PP219

PP220

PP226

PP225

8

7

6

5

M152

IS42S16800B-7TL

23

A0

24

A1

25

A2

26

A3

29

A4

30

A5

31

A6

32

A7

33

A8

34

A9

22

A10

35

A11

21

BA1(A12)

20

BA0(A13)

15

LDQM

39

UDQM

37

CKE

38

CLK

___

17

__

CAS

19

___

CS

18

__

RAS

16

WE

54

Vss

41

Vss

28

Vss

6

VSSQ

12

VSSQ

52

VssQ

46

VssQ

M153

M29W800DB70N6

13

NC(A21)

10

NC(A20)

9

NC(A19)

16

A18

A17

A16

1

A15

2

A14

3

A13

4

A12

5

A11

6

A10

7

A9

8

A8

A7

A6

A5

A4

A3

A2

A1

A0

__

__

CE

__

OE

WE

_____

RESET

A-1/DQ15

17

48

18

19

20

21

22

23

24

25

26

28

11

12

VCC

WP

SCL

SDA

RY_BY

D3R3V

PP252

PP251

PP250

PP249

123

4

RA160

RA33

876

5

T

T

T

T

D

D

D

D

0

1

0

1

8

1

9

0

PP174

PP173

PP172

RA33

DSPTMS

DSP0TDO

DSPTCK

123

4

RA150

876

5

T

T

T

C

C

U

K

L

D

E

K

Q

DSP JTAG

DSP0TDI

TCK-RET

DSPEMU0

R150

10k

1 2

3

5

7 8

9 10

11

13

CN150

OPEN

R151

10k

4

6

12

14

DSPTRSTn

DSPEMU1

/RSTDSP

2

Q153

OPEN

D1R2V D1R2V

C176

C177

0.1uZ

0.1uZ

D3R3V

1

3

PP171

R153

R155

OPEN

Q151

OPEN

2

C175

0.1uZ

C174

0.1uZ

0

1

3

PP169

3

1

R154

OPEN

D150

2

OPEN

PP168

3

Q152

OPEN

1

D1R2V

C183

C184

0.1uZ

0.1uZ

M151

OPEN

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

NC

NC

VCC

VCC

VCC

VCCQ

VCCQ

VccQ

VccQ

__

NC(WP)

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

____

BYTE

__

RY/BY

VCC

VSS

VSS

AP15V

2

PP170

C182

0.1uZ

A0

A1

A2

GND

D3R3V

1

2

3

4

2

4

5

7

8

10

11

13

42

44

45

47

48

50

51

53

40

36

D3R3V

1

14

27

3

9

49

43

D3R3V

14

45

43

41

39

36

34

32

30

44

42

40

38

35

33

31

29

47

15

37

27

46

PP229

Q150

OPEN

3

PP215

PP211

PP207

PP203

PP216

PP221

2

1

C181

0.1uZ

PP214

PP213

PP212

PP210

PP209

PP208

PP206

PP205

PP204

PP202

PP201

PP200

D3R3V

R160

C193

0.1uZ

P_RST

R159

10k

10k

C179

0.1uZ

D3R3V

C158

0.1uZ

T D00

T D01

T D02

T D03

T D04

T D05

T D06

T D07

T D08

T D09

T D10

T D11

T D12

T D13

T D14

T D15

T D15

T D14

T D13

T D12

T D11

T D10

T D09

T D08

T D07

T D06

T D05

T D04

T D03

T D02

T D01

T D00

R161

33

C178

0.1uZ

C157

0.1uZ

C180

0.1uZ

(2)DSP

OT1-200121

R

FRAMINGHAM, MA 01701-9168

ControlSpace

ESP-88C/ESP-00 Processors

Dolby/DTS PCB Assy., Rev. B

Part Number 302210

Sheet 3 of 5

AuBit

R

Page 4

1

2

3 4 5 6

7 8

9 10

11

A

B

C

512FS

/RSTSRC

AFSX1

ACLKX1

AXR1[0]

R306

10k

RA312

RA33

1

8

2

7

3

6

4

5

RA313

RAOPEN

1

8

2

7

3

6

4

5

PP303

D3R3V

R337

47k

D2R5V

C329

16V10u

PP355

PP354

PP358

PP357

PP356

PP353

C328

0.1uZ

1

XTO

2

XTI

3

VD

4

GND

5

RST

6

BYPASS

7

ILRCK

8

ISCLK

9

SDIN

10

MCLKOUT

M304

CS8421

SRCNLOCK

MSSEL

OLRCK

OSCLK

SDOUT

TDMIN

SAIF

SAOF

VL

GND

20

19

18

17

16

15

14

13

12

11

PP366

PP365

0.1uZ

PP363

PP362

PP361

PP360

PP359

C326

R342

18k

R343

1M

PP364

16V10u

D3R3V

R338

2.2k

R339

68k

C327

R340

1k

R341

1k

D3R3V

RA315

1

2

3

4

RA314

RAOPEN

1

2

3

4

RA33

C321

0.1uZ

PP330

PP331

PP332

PP333

PP334

R324

18k

R323

1M

PP329

16V10u

D3R3V

R328

2.2k

R327

68k

C320

R326

1k

R325

1k

D3R3V

RA304

RA33

1

2

3

4

RA305

RAOPEN

1

2

3

4

SRCUL2

8

7

6

5

LRCLKE

BCLKE

SDOUT2

SRCDIR2

8

7

6

5

PP327

D3R3V

SRCUL0

512FS

10k

R329

47k

R304

/RSTSRC

RA307

8

7

6

5

LRCLKE

BCLKE

SDOUT0

AFSX1

ACLKX1

AXR1[2]

SRCDIR0

8

7

6

5

RA33

8

1

7

2

6

3

5

4

RA306

RAOPEN

8

1

2

7

6

3

5

4

D2R5V

C318

16V10u

PP338

PP335

PP336

PP337

PP339

C319

0.1uZ

1

2

3

4

5

6

7

8

9

10

M302

CS8421

SRCNLOCK

XTO

XTI

VD

GND

RST

BYPASS

ILRCK

ISCLK

SDIN

MCLKOUT

SAIF

SAOF

GND

MSSEL

OLRCK

OSCLK

SDOUT

TDMIN

VL

PP328

20

19

18

17

16

15

14

13

12

11

PP301

E

D

F

512FS

/RSTSRC

AFSX1

ACLKX1

AXR1[1]

R305

10k

RA311

RA33

1

8

2

7

3

6

4

5

RA310

RAOPEN

1

8

2

7

3

6

4

5

PP302

D3R3V

R336

47k

D2R5V

C322

16V10u

PP351

PP348

PP349

PP350

PP352

C323

0.1uZ

1

XTO

2

XTI

3

VD

4

GND

5

RST

6

BYPASS

7

ILRCK

8

ISCLK

9

SDIN

10

MCLKOUT

M303

CS8421

SRCNLOCK

MSSEL

OLRCK

OSCLK

SDOUT

TDMIN

SAIF

SAOF

VL

GND

20

19

18

17

16

15

14

13

12

11

PP340

PP341

0.1uZ

PP343

PP344

PP345

PP346

PP347

C325

R331

18k

R330

1M

PP342

D3R3V

R335

2.2k

R334

68k

C324

16V10u

R333

1k

R332

1k

D3R3V

RA308

1

2

3

4

RA309

RAOPEN

1

2

3

4

RA33

C317

0.1uZ

PP317

PP318

PP319

PP320

PP321

R317

18k

R316

1M

PP316

16V10u

D3R3V

R321

2.2k

R320

68k

C316

R319

1k

R318

1k

D3R3V

RA300

1

2

3

4

RA301

RAOPEN

1

2

3

4

RA33

SRCUL3

8

7

6

5

LRCLKE

BCLKE

SDOUT3

SRCDIR3

8

7

6

5

PP314

D3R3V

SRCUL1

512FS

10k

R322

47k

R303

/RSTSRC

RA303

8

7

6

5

LRCLKE

BCLKE

SDOUT1

AFSX1

ACLKX1

AXR1[3]

SRCDIR1

8

7

6

5

RA33

8

1

7

2

6

3

4

5

RA302

RAOPEN

1

8

2

7

6

3

5

4

D2R5V

C314

16V10u

PP325

PP322

PP323

PP324

PP326

C315

0.1uZ

1

2

3

4

5

6

7

8

9

10

M301

CS8421

SRCNLOCK

XTO

XTI

VD

GND

RST

BYPASS

ILRCK

ISCLK

SDIN

MCLKOUT

SAIF

SAOF

GND

MSSEL

OLRCK

OSCLK

SDOUT

TDMIN

VL

PP315

20

19

18

17

16

15

14

13

12

11

PP300

M300

GND

3

FB

PP304

D300

DAN217

1

3

2

4

R300

39k

R302

33k

R301

390k

C304

0.1uZ

VD=2.5V

C300

0.1uZ

D2R5V

16V10u

C301

(3)SRC-BiDir

OT1-200121

R

FRAMINGHAM, MA 01701-9168

ControlSpace

ESP-88C/ESP-00 Processors

Dolby/DTS PCB Assy., Rev. B

Part Number 302210

R

PP313

G

PP305

AFSX1

ACLKX1

H

AXR1[0]

AXR1[1]

R307

33

R308

33

R312

33

R311

33

PP306

PP310

PP309

C305

22p

C306

22p

C310

22p

C309

22p

512FS

LRCLKE

BCLKE

AXR1[2]

AXR1[3]

R315

33

R314

33

R313

33

R310

33

R309

33

PP312

PP311

PP308

PP307

C313

22p

C312

22p

C311

22p

C308

22p

C307

22p

D5V

16V10u

C302

TPS73601DCQ

1

IN2OUT

5

EN

C303

0.1uZ

Sheet 4 of 5

AuBit

Page 5

1

2

3 4 5 6

7 8 9 10

11

HD64F3664FP-MODE

.....:USER:BOOT:WRITER

TEST = 0 : 0 : 1

/NMI = 1 : 0 : X

P85 = X : 1 : X

PB0 = X : X : 0

PB1 = X : X : 0

PB2 = X : X : 0

PP457

P83

P82

P81

P80

P87

P86

P85

P84

PP458

PP459

PP455

PP456

PP460

D3R3V

R436

OPEN

R438

CID3

CID1

SRCDIR3

SRCDIR1

OPEN

CID2

CID0

SRCDIR2

SRCDIR0

D3R3V

C428

0.1uZ

C431

22p

R443

33

R442

33

LRCLKE

BCLKE

PP417

256FS

512FS

/EXTRES

/CPUCS

C430

22p

R452

33

R453

OPEN

74AC273

3

D1

4

D2

7

D3

8

D4

13

D5

14

D6

17

D7

18

D8

11

___

CLK

1

CLR

R435

OPEN

R437

OPEN

D3R3V

9

Q

_

8

Q

M401

10

S

D

CP

R

13

C433

22p

R445

33

PP490

PP408

PP489

D5V

C417

0.1uZ

C416

0.1uZ

5V

2

Q1

5

Q2

6

Q3

9

Q4

12

Q5

15

Q6

16

Q7

19

Q8

M403B

74VHC74

12

11

D3R3V

D3R3V

S

5

Q

_

6

Q

R

4

1

C429

0.1uZ

D

CP

D3R3V

D5V

C439

0.1uZ

RA400

RA10k

9

8

7

6

4

3

2

1 5

R440

10k

R439

10k

R450

33

R451

33

M403A

74VHC74

2

PP488

3

D5V

C410

470p

PP423

R40933R410

R425

R424

R427

R426

10

D3R3V

RXD

/RESET

SDATA1

MCLK

BCLK

LRCLK

AGND

PP485

PP486

PP487

D5V

330

330

330

330

C400

470p

PP422

R403

33

D5V

TXD

C411

470p

PP424

33

SDATA0

74VHC541

18

Q0

17

Q1

16

Q2

15

Q3

14

Q4

13

Q5

12

Q6

11

Q7

D5V

PP425

R411

33

R422

330

R423

330

R420

330

R421

330

GRN

D3

D3R3VD3R3V

C401

470p

PP421

R404

33

AP15V

M405

D3R3V

C412

470p

3

2

E2

E1

SRCUL0

SRCUL1

SRCUL2

SRCUL3

GRN

RED

D2

1

L-42WUM/1EGW

I0

I1

I2

I3

I4

I5

I6

I7

D403

D3R3V

C402

470p

PP420

R405

33

87BFN-030R-3F

2

3

4

5

6

7

8

9

19

1

CN402A

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

PP419

R406

R471

R472

R473

R474

D1

RED RED RED

D0

1

3

2

L-42WUM/1EGW

D3R3V

C403

470p

PP418

33

R407

/CS

SDATA2

MCLK

BCLK

LRCLK

AGND

RA401

RA33

4

3

2

1

R449

OPEN

D402

C404

470p

33

OPEN

OPEN

OPEN

OPEN

GRN

D4

3

2

L-42WUM/1EGW

D3R3V

PP407

R408

ONMUTE

SDATA3

P400

OPEN

TPAG

5

6

7

8

C405

470p

33

D3R3V

D3R3V

D3R3V

D3R3V

GRN

D5

1

D401

D3R3V

C413

470p

PP426

R412

33

AP15V

D5V

BOOT

R441

0

BCLK

/RESET

/CS

ONMUTE

OT1-200121

FRAMINGHAM, MA 01701-9168

D5V

C407

0.1uZ

D5V

C406

0.1uZ

D5V

C408

0.1uZ

D5V

C409

0.1uZ

D6

D7

1

3

C414

470p

D400

D3R3V

2

L-42WUM/1EGW

D3R3V

PP427

R413

33

CN402B

87BFN-030R-3F

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

LRCLK

MCLK

(4)CPU(I2C)

ControlSpace

C415

470p

PP428

R414

33

R

R

Q402

2

1

SRCDIR3

/SDOE

SRCUL0

SRCUL2

CID3

CID1

DTC114EKA

PP437

C421

0.1uZ

DIRFLG1

H8P74

DIRFLG0

15

PP442

PP441

C419

22p

PP429

R416

330

3

Q401

2

1

PP434

C420

0.1uZ

432

6

C418

22p

PP430

R415

330

Q404

DTC114EKA

R419

10k

DTC114EKA

3

PP435

M400

S-80930ANMP

2

VDD

5

CD

GND

3

R400

R401

R402

R469

R468

R467

R466

987

RA402

RA10k

10

32

1

PP439

Q400

NC

OUT

33

33

33

33

R465

OPEN

R464

OPEN

R463

OPEN

R462

OPEN

D3R3V

1

4

1

10k

10k

10k

R428

10k

DTC114EKA

PP453

PP452

PP438

32

Q403

PP451

R418

10k

PP436

1

PP450

PP449

C423

12p

C424

12p

D3R3VD3R3V

32

PP448

R458

OPEN

R459

OPEN

R429

10k

49

NC

50

NC

51

P14

52

P15

53

____

P16

54

IRQ3

55

AN4

56

AN5

57

AN6

58

AN7

59

AN3

60

AN2

61

AN1

62

AN0

63

NC

64

NC

PP433

XTAL400

10.000MHZ

PP431

D3R3V

R460

OPEN

R461

OPEN

C426

0.1uZ

C438

0.1uZ

P

47NC48

NC

1NC2NC3

PP499

PP500

P

P

P

8

8

8

5

7

6

44

45

46

TXD

RXD

SCK3

AVCC4X25X16VCL7RES

___8TEST9VSS10OSC211OSC112VCC13P5014P5115NC16NC

C422

0.1uZ

D5V

PP501

PP502

P

P

8

8

4

3

16V10u

P

P

8

8

2

1

C437

P

8

0

35

36

___

P8037P8138P8239P8340P8441P8542P8643P87

NMI

PP432

C425

0.1uZ

18

17

16

15

14

13

12

11

P

P

P

8

8

8

7

5

6

M402

HD64F3664FP

33NC34

NC

NC

NC

P76

P75

P74

(P57)SDA

(P56)SCL

P12

P11

P10

P55

P54

P53

P52

NC

NC

R417

OPEN

C436

0.1uZ

R457

R456

M406

74VHC541

I0

Q0

I1

Q1

I2

Q2

I3

Q3

I4

Q4

I5

Q5

I6

Q6

I7

Q7

E2

E1

R430

10k

32

31

30

29

28

27

26

25

24

23

22

PP443

21

20

19

18

17

D3R3V

C427

16V10u

M404

TA48033F

1

IN

COM

3

33

R455

33

R454

PP503

2

PP504

3

4

5

6

7

8

9

19

1

PP444

PP445

DAN217

OUT

PP505

PP506

R432

2.2k

PP446

PP447

D404

3

2

D3R3V

1

2

C435

0.1uZ

33

33

D3R3V

R431

2.2k

/RSTSRC

/RSTDIR

/RSTDSP

D3R3V

R470

10k

DIRFLG1

H8P74

I2C1_SCL

SRCDIR1

/RSTSRC

/RSTDSP

PINCAP6

SDOUT0

SDOUT1

SDOUT2

SDOUT3

C434

16V10u

SDATA1

SDATA3

D3R3V

R433

OPEN

R434

0

EMU(KuC)

I2C1_SDA

SRCDIR2

SRCDIR0

/RSTDIR

PINCAP7

PINCAP5

R448

10k

R447

10k

R446

10k

SDATA0

SDATA2

/SDOE

CN401

OPEN

1 2

3

5 6

7 8

9

11 12

13

R444

33

D3R3V

4

10

14

C432

22p

RXD

TXD

A

BOOT

CN400

OPEN

5

4

3

2

1

D5V

PP454

DTC114EKA

B

DIRFLG0

/CPUCS

C

SRCUL1

SRCUL3

CID2

CID0

D

/EXTRES

D3R3V

E

F

G

SDOUT0

SDOUT1

SDOUT2

SDOUT3

AXR0[5]

AXR0[6]

AXR0[7]

AXR0[8]

H

ESP-88C/ESP-00 Processors

Dolby/DTS PCB Assy., Rev. B

Part Number 302210

Sheet 5 of 5

AuBit

Loading...

Loading...