BOE HV460WU2-200 Specification

PROPRIETARY NOTE

PROPRIETARY NOTE

PROPRIETARY NOTE

PROPRIETARY NOTE

THIS SPECIFICATION IS THE PROPERTY OF BOE DT AND SHALL NOT BE

REPRODUCED OR COPIED WITHOUT THE WRITTEN PERMISSION OF BOE DT

AND MUST BE RETURNED TO BOE DT UPON ITS REQUEST

SPEC. NUMBER

S8XX-XXXX

PRODUCT GROUP

TFT LCD

REV.

P0

ISSUE DATE

2012.02.15

PAGE

of 24

B20 10 - 8 00 2 -O (1/3)

A4(210 X 297)

TITLE:

TITLE:

TITLE:

TITLE:

A4(210 X 297)

BEIJING BOE DISPLAY T E CHNOLOGY

1

HV460WU2-200 Preliminary Product Specification

HV460WU2-200 Preliminary Product Specification

HV460WU2-200 Preliminary Product Specification

HV460WU2-200 Preliminary Product Specification

PRODUCT GROUP

REV ISSUE DATE

TFT LCD

P0 2012.02.15

SPEC. NUMBER

S8XX-XXXX

SPEC. TITLE

HV460WU2-200 Preliminary Product Specification

PAGE

of 24

A4(210 X 297)

REV. ECN NO. DESCRIPTION OF CHANGES DATE PREPARED

P0 - Initial Release 2012.02.15 Hongming Zhan

REVISION HISTORY

B20 10 - 8 00 2 -O (2/3)

2

A4(210 X 297) B20 10 - 8 00 2 -O (3/3)

PRODUCT GROUP

REV ISSUE DATE

TFT LCD

P0 2012.02.15

SPEC. NUMBER

S8XX-XXXX

SPEC. TITLE

HV460WU2-200 Preliminary Product Specification

PAGE

of 24

3

Contents

Contents

Contents

Contents

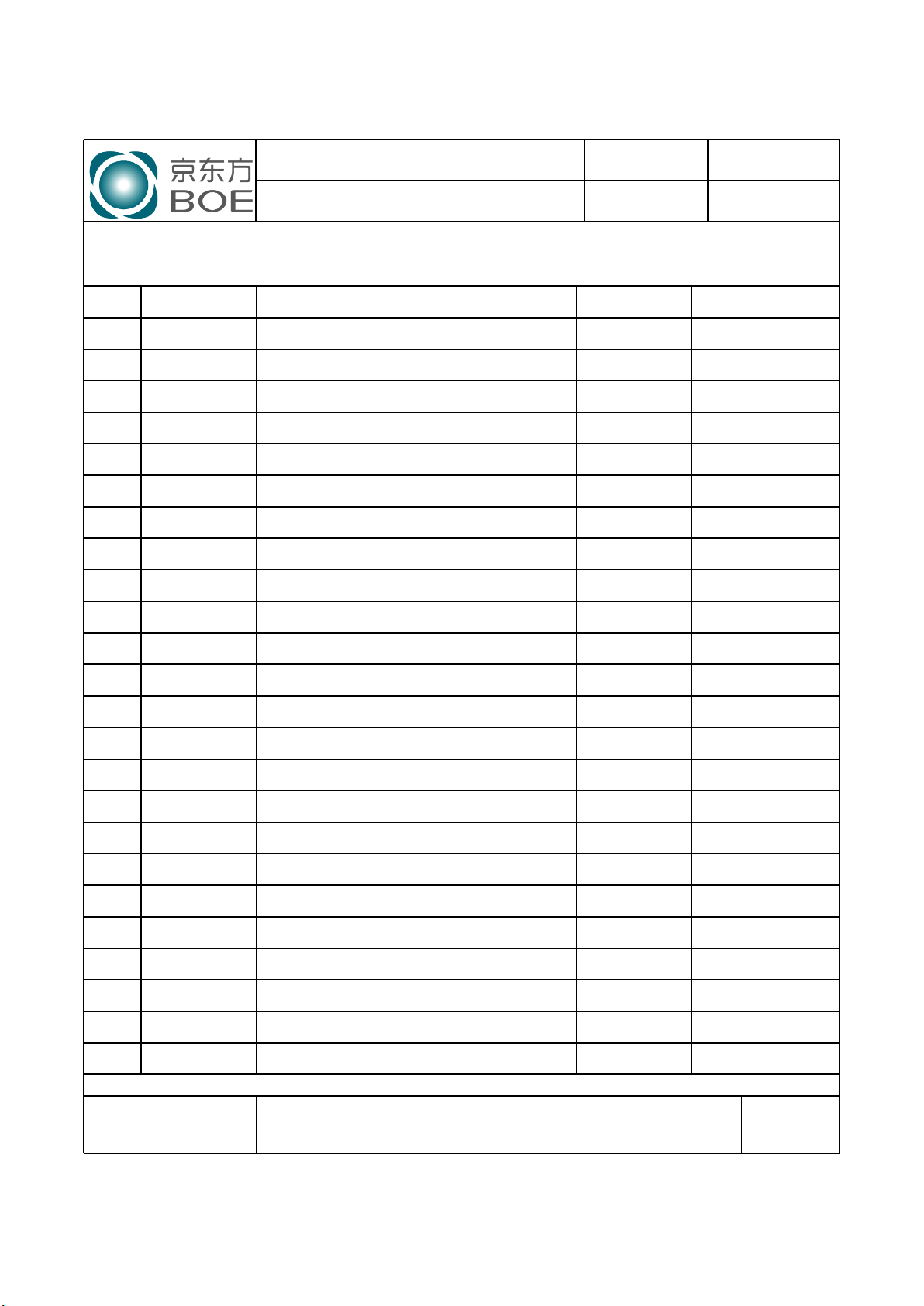

No ITEM Page

REVISIONS HISTORY 2

CONTENTS

3

1 GENERAL DESCRIPTION 4

1.1 Introduction

1.2 Features

1.3 Applications

1.4 General Specification

2 ABSOLUTE MAXIMUM RATINGS 6

3 ELECTRICAL SPECIFICATIONS

7

3.1 TFT LCD Open Cell

4 INTERFACE CONNECTION 8

4.1 Open Cell Input Signal & Power

4.2 LVDS Interface

5 SIGNAL TIMING SPECIFICATIONS 11

5.1 Timing Parameters

5.2 Signal Timing Waveform

5.3 Input Signals, Basic Display Colors & Cray Scale Of Colors

5.4 Power Sequence

6 OPTICAL SPECIFICATIONS 15

7 MECHANICAL CHARACTERISTICS 17

8 RELIABLITY 18

9 PRODUCT SERIAL NUMBER 19

10 PACKING INFORMATION

20

11 HANDING & CAUTIONS 22

12 APPENDIX 23

A4(210 X 297) B20 10 - 8 00 2 -O (3/3)

PRODUCT GROUP

REV ISSUE DATE

TFT LCD

P0 2012.02.15

SPEC. NUMBER

S8XX-XXXX

SPEC. TITLE

HV460WU2-200 Preliminary Product Specification

PAGE

of 24

4

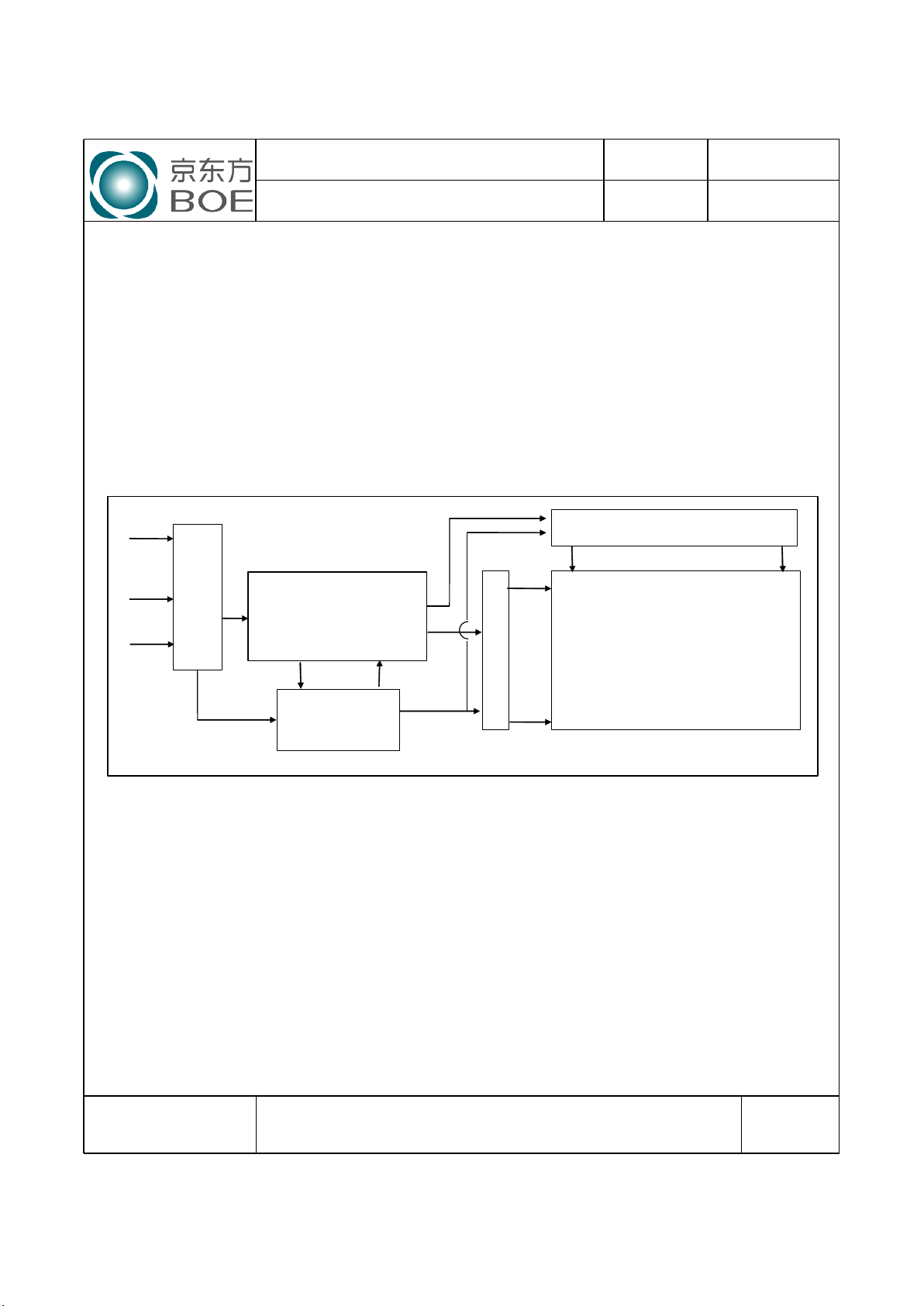

1.0 GENERAL DESCRIPTION

1.0 GENERAL DESCRIPTION

1.0 GENERAL DESCRIPTION

1.0 GENERAL DESCRIPTION

HV460WU2-200 is a color active matrix TFT LCD open cell using amorphous silicon TFT's

(Thin Film Transistors) as an active switching devices. This module has a 46.00 inch diago

nally measured active area with WUXGA resolutions (1920 horizontal by 1080 vertical pixe

l array). Each pixel is divided into RED, GREEN, BLUE dots which are arranged in vertical

stripe and this module can display 16.7M colors. The TFT-LCD panel used for this module

is adapted for a low reflection and higher color type.

CN1

CN1

CN1

CN1

(51pin)

(51pin)

(51pin)

(51pin)

LVDS

LVDS

LVDS

LVDS

2Ports

2Ports

2Ports

2Ports

LVDS_SEL

LVDS_SEL

LVDS_SEL

LVDS_SEL

Source Driver Circuit

Source Driver Circuit

Source Driver Circuit

Source Driver Circuit

TFT - LCD Panel

(1920 × RGB × 1080 pixels)

G1

G1

G1

G1

S1

S1

S1

S1 S1920

S1920

S1920

S1920

G1080

G1080

G1080

G1080

RGB(Mini-LVDS)

RGB(Mini-LVDS)

RGB(Mini-LVDS)

RGB(Mini-LVDS)

Timing Controller

Timing Controller

Timing Controller

Timing Controller

[LVDS Rx & Mini-LVDS

[LVDS Rx & Mini-LVDS

[LVDS Rx & Mini-LVDS

[LVDS Rx & Mini-LVDS

Tx integrated]

Tx integrated]

Tx integrated]

Tx integrated]

Gate Driver Circuit

Gate Driver Circuit

Gate Driver Circuit

Gate Driver Circuit

Power Circuit

Power Circuit

Power Circuit

Power Circuit

Block

Block

Block

Block

# 7

+

+

+

+ 12

12

12

12 .0V

.0V

.0V

.0V

VDD

VDD

VDD

VDD

1.2 Features

LVDS interface with 2 pixel / clock

High-speed response

Low color shift image quality

8-bit color depth, display 16.7M colors

High luminance and contrast ratio, low reflection and wide viewing angle

DE (Data Enable) only mode

ADS technology is applied for high display quality

RoHS compliant

1.1 Introduction

A4(210 X 297) B20 10 - 8 00 2 -O (3/3)

PRODUCT GROUP

REV ISSUE DATE

TFT LCD

P0 2012.02.15

SPEC. NUMBER

S8XX-XXXX

SPEC. TITLE

HV460WU2-200 Preliminary Product Specification

PAGE

of 24

5

Parameter

Parameter

Parameter

Parameter Specification

Specification

Specification

Specification Unit

Unit

Unit

Unit Remark

Remark

Remark

Remark

Active area 1018.08(H) × 572.67(V) mm

Number of pixels 1920(H) ×1080(V) pixels

Pixel pitch 176.75(H) ×RGB

×

530.25(V)

㎛

Pixel arrangement Pixels RGB Vertical stripe

Display colors 16.7M(8bits-true) colors

Display mode Transmission mode, Normally Black

Open Cell

Transmittance

6.3 (typ.) %

At center

point with

BOE BLU

Weight 2370 (Typ.) gram With T-con

Board

Power Consumption 9.0(Typ.) Watt

Surface Treatment Haze 13%, 3H, Anti -glare treatment (F

ront Polarizer)

Clear (Bottom Polarizer)

< Table 1. General Specifications >

1.3 Application

Home Alone Multimedia TFT-LCD TV

Display Terminals for Control System

Full High Definition TV(FHD TV)

AV application Products

1.4 General Specification

A4(210 X 297) B20 10 - 8 00 2 -O (3/3)

PRODUCT GROUP

REV ISSUE DATE

TFT LCD

P0 2012.02.15

SPEC. NUMBER

S8XX-XXXX

SPEC. TITLE

HV460WU2-200 Preliminary Product Specification

PAGE

of 24

6

The followings are maximum values which, if exceed, may cause faulty operation or

damage to the unit. The operational and non-operational maximum voltage and current

values are listed in Table 2.

Parameter

Parameter

Parameter

Parameter Symbol

Symbol

Symbol

Symbol Min.

Min.

Min.

Min. Max.

Max.

Max.

Max. Unit

Unit

Unit

Unit Remark

Remark

Remark

Remark

Power Supply Voltage VDD VSS-0.3 13.5 V Ta = 25

℃

Operating Temperature

T

OP

0 + 50

℃

Note 1

T

SUR

0 + 60

℃

Storage Temperature

T

ST

-20 + 60

℃

Operating Ambient Humidit

y

Hop 10 80 %RH

Storage Humidity Hst 10 80 %RH

< Table 2. Open Cell Electrical Specifications >

[VSS=GND=0V]

2.0 ABSOLUTE MAXIMUM RATINGS

2.0 ABSOLUTE MAXIMUM RATINGS

2.0 ABSOLUTE MAXIMUM RATINGS

2.0 ABSOLUTE MAXIMUM RATINGS

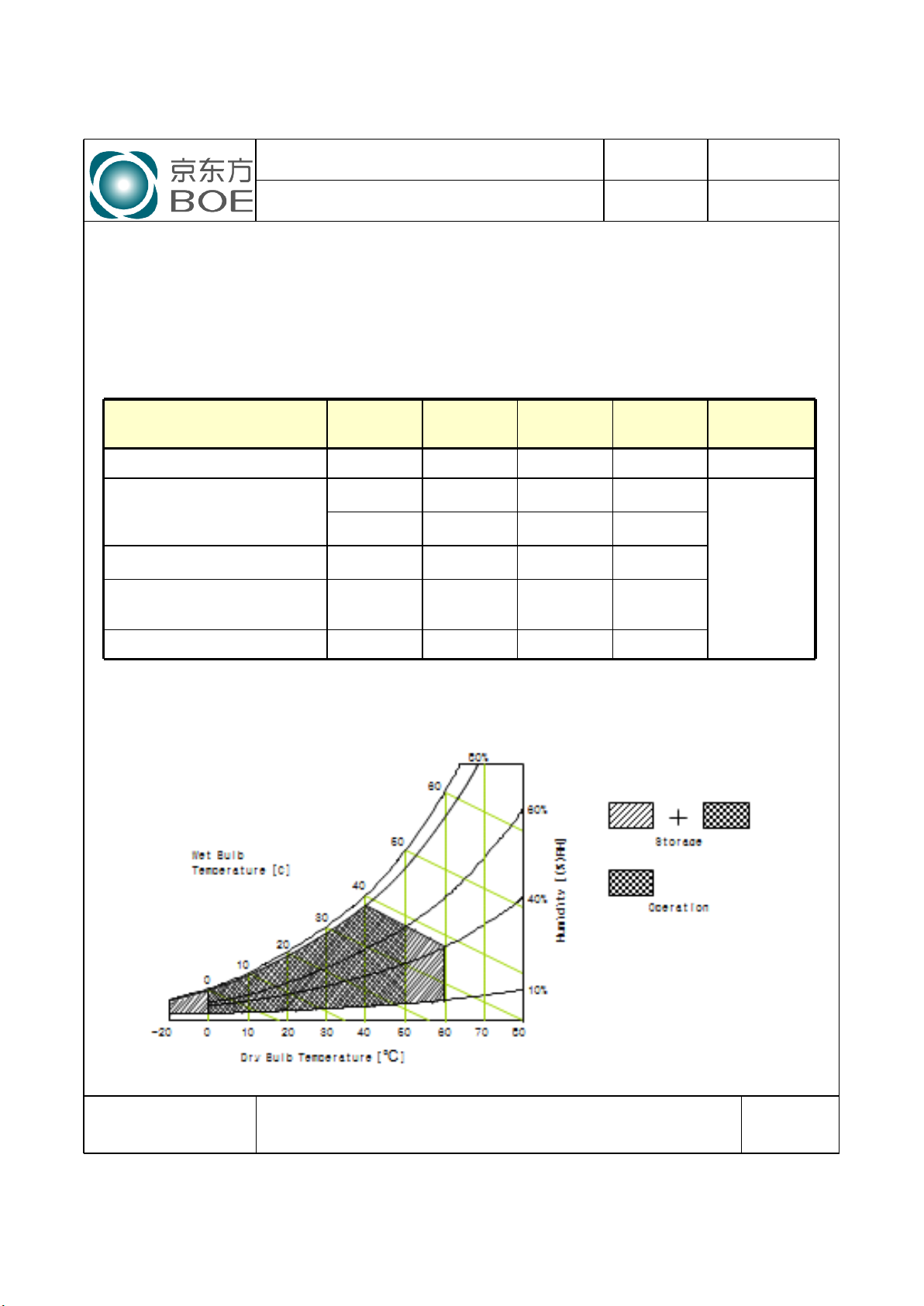

Note 1 : Temperature and relative humidity range are shown in the figure below.

Wet bulb temperature should be 39 ℃ max. and no condensation of water.

A4(210 X 297) B20 10 - 8 00 2 -O (3/3)

PRODUCT GROUP

REV ISSUE DATE

TFT LCD

P0 2012.02.15

SPEC. NUMBER

S8XX-XXXX

SPEC. TITLE

HV460WU2-200 Preliminary Product Specification

PAGE

of 24

7

[Ta =25 ± 2 ℃]

< Table 3. Open Cell Electrical Specifications >

Parameter

Parameter

Parameter

Parameter Symbol

Symbol

Symbol

Symbol

Values

Values

Values

Values

Unit

Unit

Unit

Unit Remark

Remark

Remark

Remark

Min

Min

Min

Min Typ

Typ

Typ

Typ Max

Max

Max

Max

Power Supply Input Voltage VDD 10.8 12 13.2 Vdc

Power Supply Ripple Voltage VRP 300 mV

Power Supply Current IDD - 750 850 m A

Note 1

Power Consumption PDD 9.0 10.2 Watt

Rush current IRUSH - - 3.0 A Note 2

LVDS

Interface

Differential Input High

Threshold Voltage

VLVTH +100 +300 mV

Differential Input Low

Threshold Voltage

VLVTL -300 -100 mV

Common Input Voltage VLVC 1.0 1.2 1.4 V

CMOS

Interface

Input High Threshold

Voltage

VIH 2.7 - 3.3 V

Input Low Threshold

Voltage

VIL 0 - 0.6 V

3.0 ELECTRICAL SPECIFICATIONS

3.0 ELECTRICAL SPECIFICATIONS

3.0 ELECTRICAL SPECIFICATIONS

3.0 ELECTRICAL SPECIFICATIONS

Note 1 : The supply voltage is measured and specified at the interface connector of LCM.

The current draw and power consumption specified is for VDD= 12 .0V,

Frame rate fV=60Hz and Clock frequency = 75.4MHz.

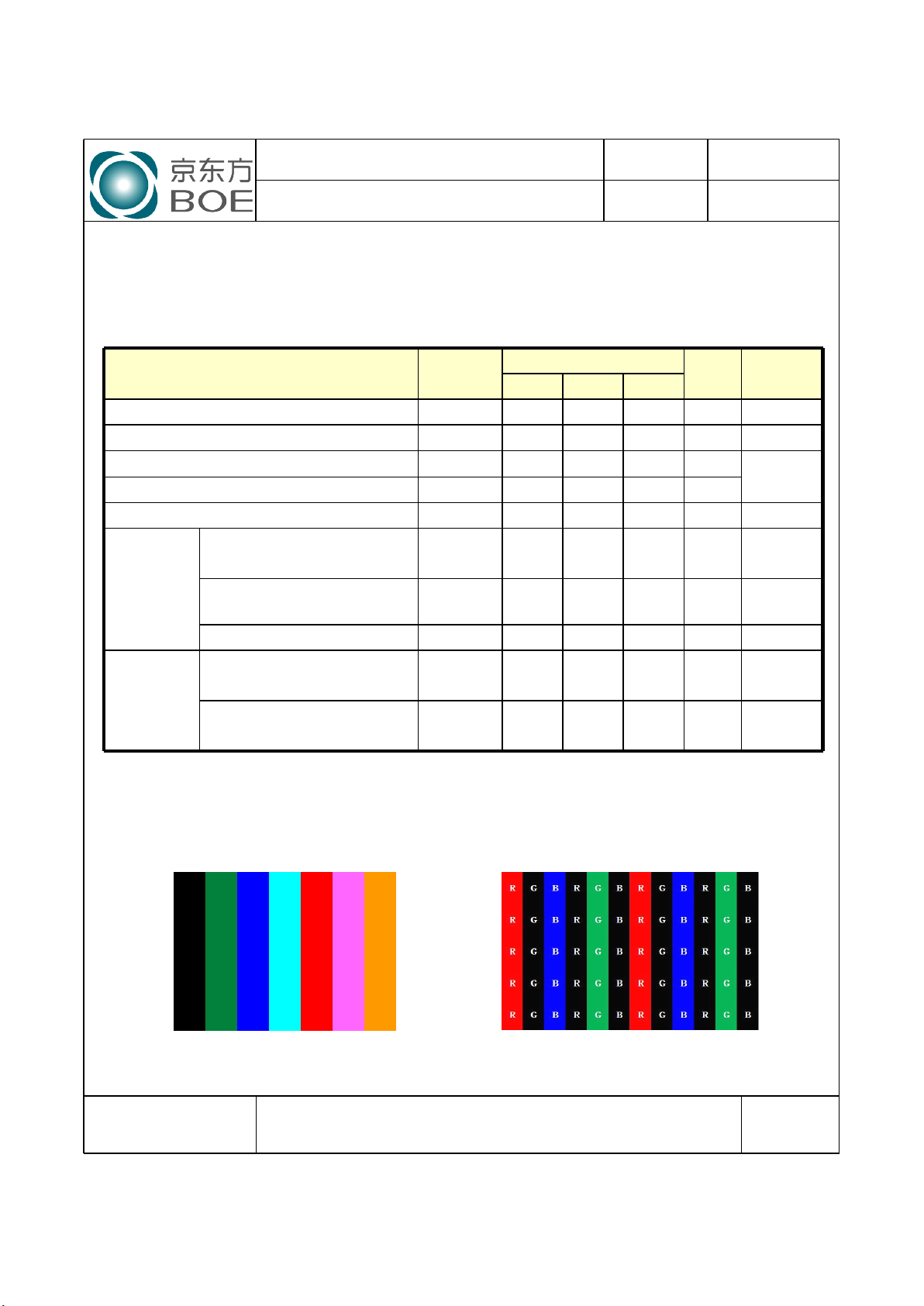

Test Pattern of power supply current

a) Typ : Color Test (L0/L255) b) Max : Vertical Subline (L0/L255)

Note 2 : The duration of rush current is about 2ms and rising time of Power Input is 1ms(min)

3.1 TFT LCD open cell

A4(210 X 297) B20 10 - 8 00 2 -O (3/3)

PRODUCT GROUP

REV ISSUE DATE

TFT LCD

P0 2012.02.15

SPEC. NUMBER

S8XX-XXXX

SPEC. TITLE

HV460WU2-200 Preliminary Product Specification

PAGE

of 24

8

4.0 INTERFACE CONNECTION

4.0 INTERFACE CONNECTION

4.0 INTERFACE CONNECTION

4.0 INTERFACE CONNECTION

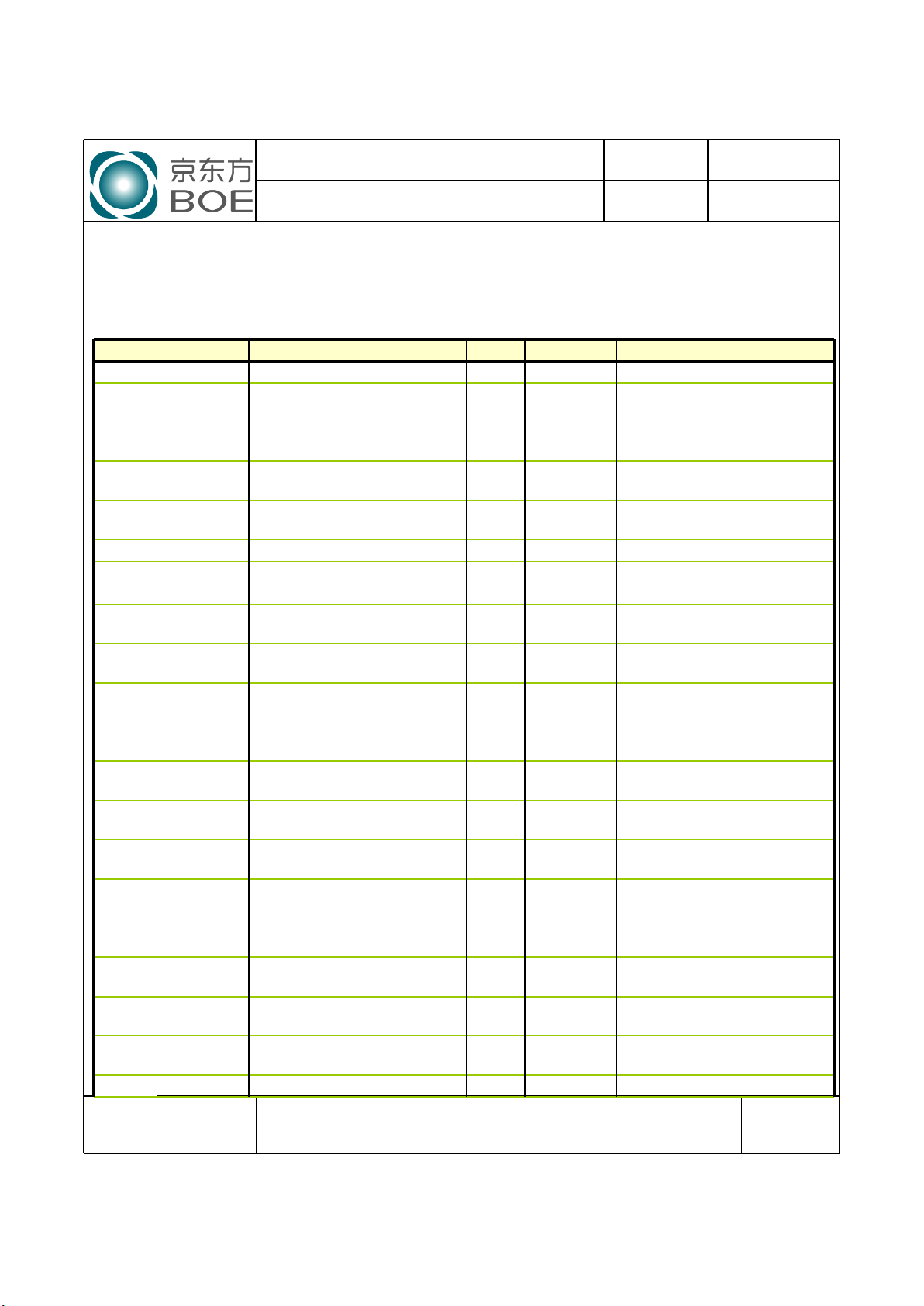

4.1 Module Input Signal & Power

- Connector : IS100-L30B-C23 (Manufactured by UJU) or Equivalent.

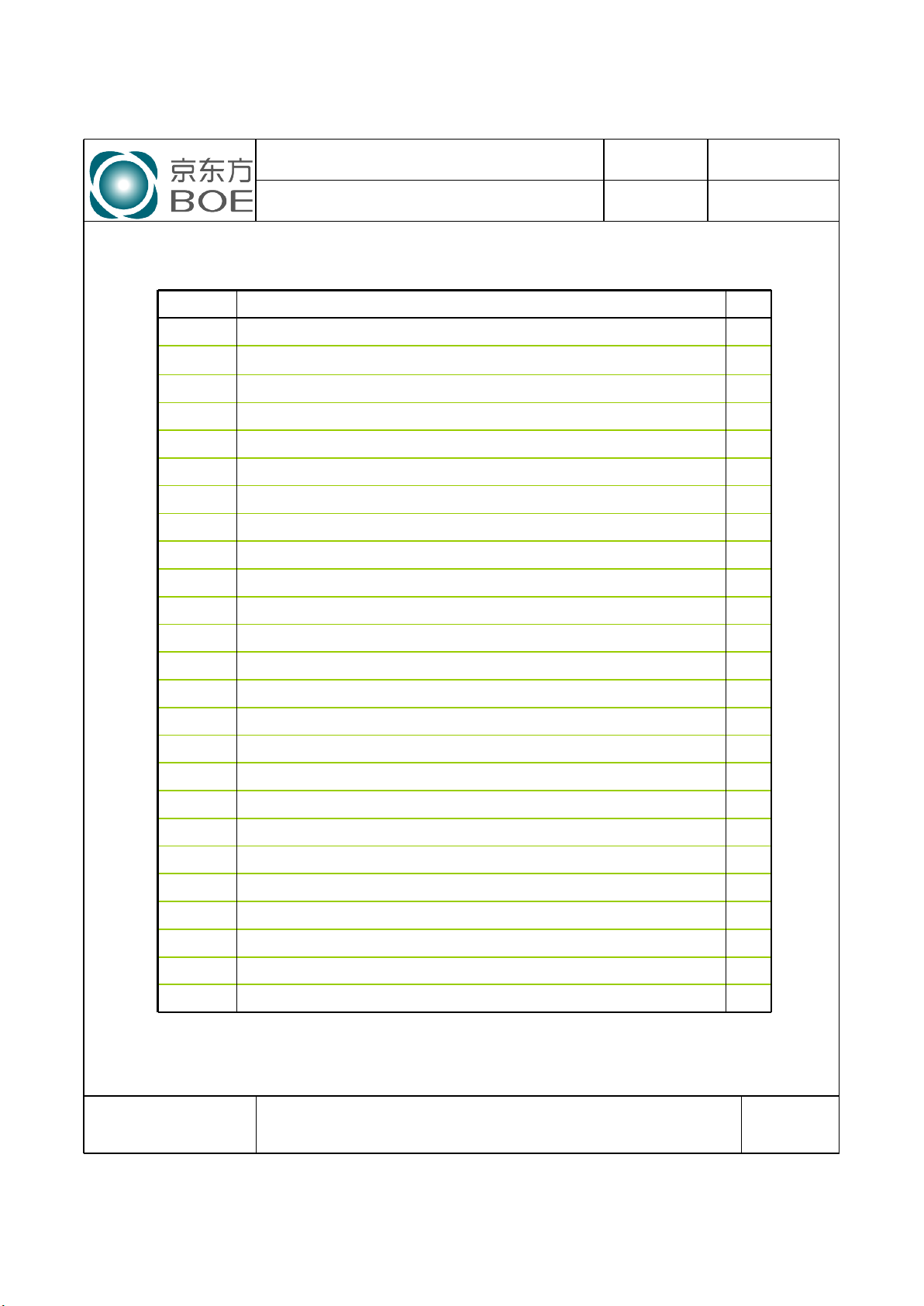

< Table 4. Open Cell Input Connector Pin Configuration >

Pin No

Pin No

Pin No

Pin No

Symbol

Symbol

Symbol

Symbol Description

Description

Description

Description

Pin No

Pin No

Pin No

Pin No

Symbol

Symbol

Symbol

Symbol Description

Description

Description

Description

1 NC No Connection 21 GND Ground

2 SDA I2C Data 22 CH1[3]-

First pixel negative LVDS differe

ntial data input. Pair3

3 SCL I2C Clock 23 CH1[3]+

First pixel positive LVDS differe

ntial data input. Pair3

4 NC Not Connected 24 CH1[4]-/NC

First pixel negative LVDS differe

ntial data input. Pair4

5 NC Not Connected 25 CH1[4]+/NC

First pixel positive LVDS differe

ntial data input. Pair4

6 NC Not Connected 26 NC Not Connected

7 SELLVDS

High : JEIDA

Low or Open:NS

27 NC Not Connected

8 NC Not Connected 28 CH2[0]-

Second pixel negative LVDS diff

erential data input. Pair0

9 NC Not Connected 29 CH2[0]+

Second pixel positive LVDS diff

erential data input. Pair0

10 NC Not Connected 30 CH2[1]-

Second pixel negative LVDS diff

erential data input. Pair1

11 GND Ground 31 CH2[1]+

Second pixel positive LVDS diff

erential data input. Pair1

12 CH1[0]-

First pixel negative LVDS differe

ntial data input. Pair0

32 CH2[2]-

Second pixel negative LVDS diff

erential data input. Pair2

13 CH1[0]+

First pixel positive LVDS differe

ntial data input. Pair0

33 CH2[2]+

Second pixel positive LVDS diff

erential data input. Pair2

14 CH1[1]-

First pixel negative LVDS differe

ntial data input. Pair1

34 GND Ground

15 CH1[1]+

First pixel positive LVDS differe

ntial data input. Pair1

35 CH2CLK- First pixel negative LVDS clock

16 CH1[2]-

First pixel negative LVDS differe

ntial data input. Pair2

36 CH2CLK+ First pixel positive LVDS clock

17 CH1[2]+

First pixel positive LVDS differe

ntial data input. Pair2

37 GND Ground

18 GND Ground 38 CH2[3]-

Second pixel negative LVDS diff

erential data input. Pair3

19 CH1CLK- First pixel negative LVDS clock 39 CH2[3]+

Second pixel positive LVDS diff

erential data input. Pair3

20 CH1CLK+ First pixel positive LVDS clock

Loading...

Loading...