Page 1

V772 CRT Monitor Service Guide

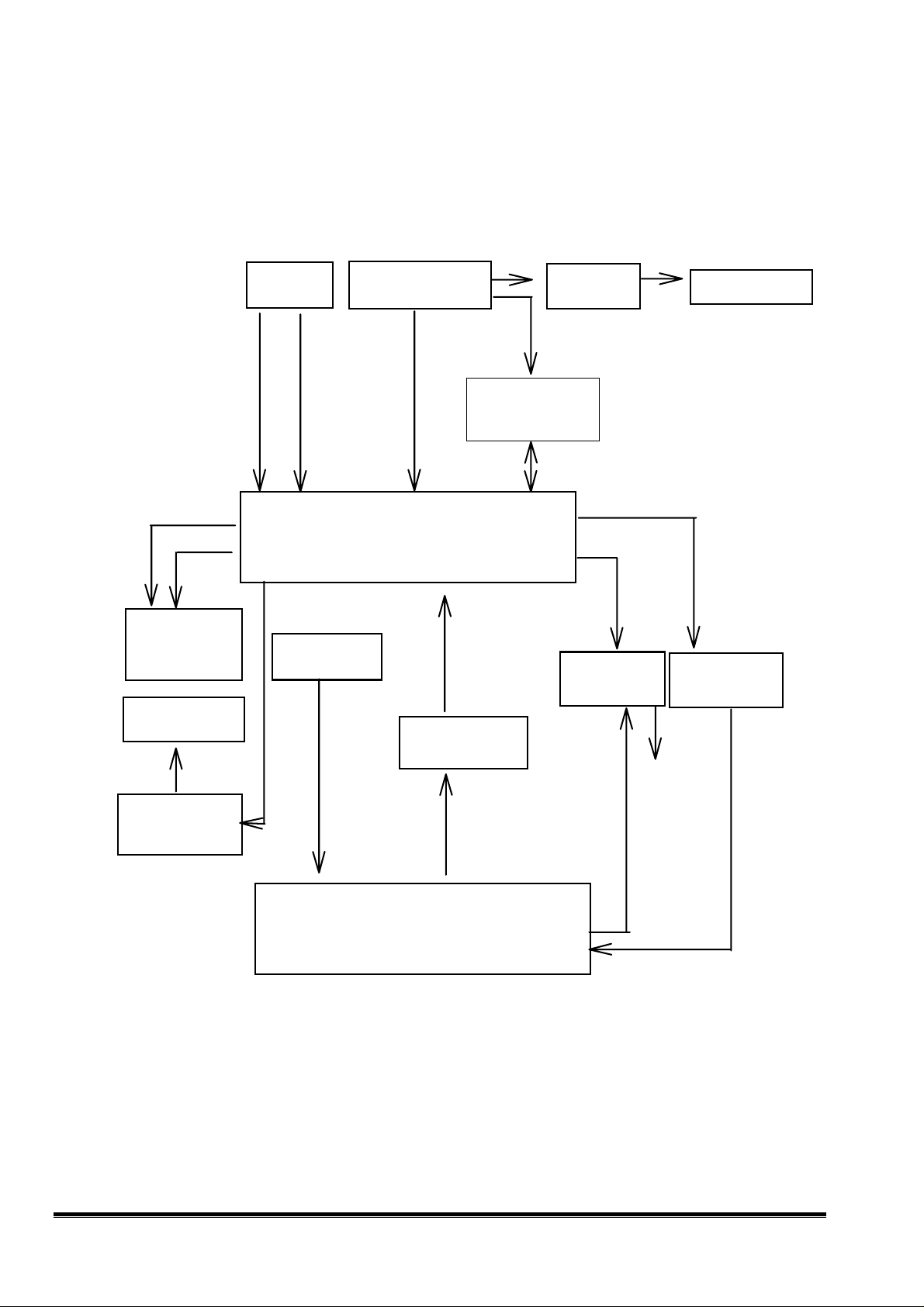

ACER V772 DEFLECTION CIRCUIT OPERATION THEORY

1. The Block Diagram of Deflection:

H-sync

V-sync

AutoSync Deflection

IC TDA4856

Digital

Controller

Controller

I2C BUS

Tilt

Circuit

Circuit Operation Theory

Rotation

Vertical

Deflection

Output

IC TDA4866

H-SIZE

Compensation

Dynamic

Regulation

Feedback

Step Up

for B+

Horizontal

Deflection Output

Circuit

Shut down

Circuit

G1 & Spot

Killer Circuit

Dynamic

Focus

G1

1

Confidential

Page 2

V772 CRT Monitor Service Guide

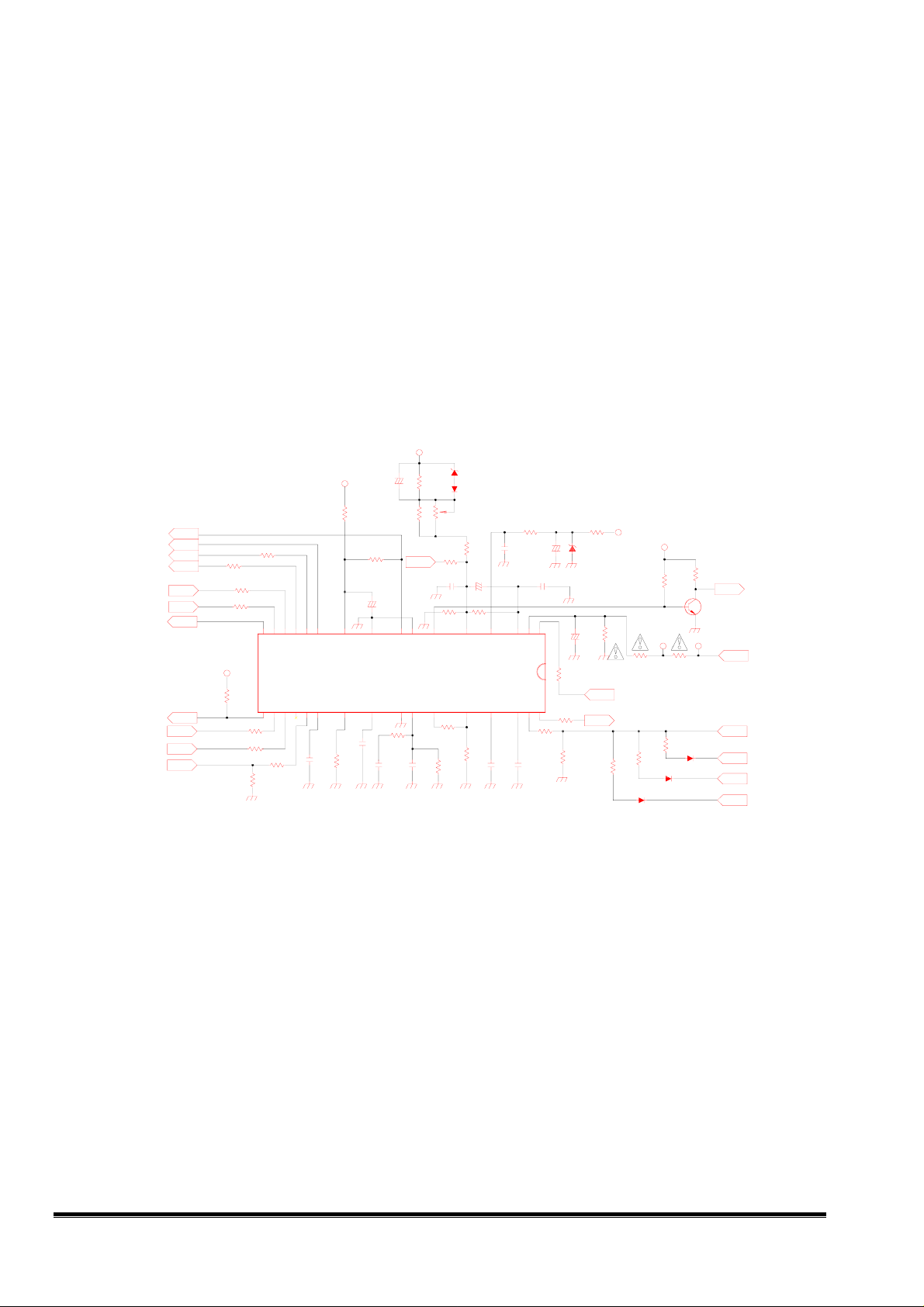

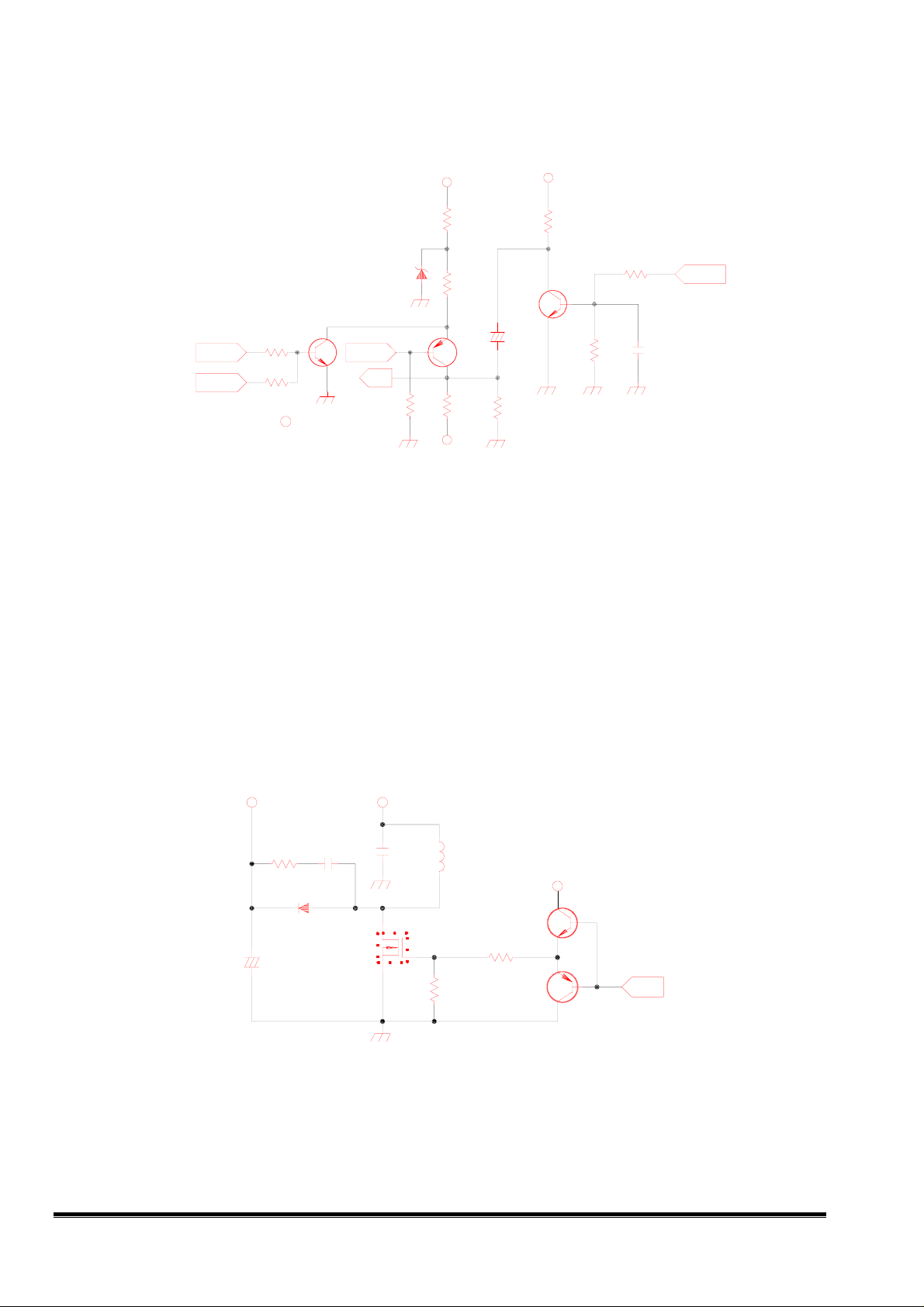

2. Autosync Deflection Controller (TDA4856)

Circuit Operation Theory

2.1 pin 1 is AFC feedback.

2.2 pin XRAY: if V XRAY > threshold (6.25V typical) switches the whole IC into protection mode.

2.3 pin 3,4,5,6,8 for B+ control function block.

2.4 pin 11(EWDRV) is a parabolic waveform used for pincushion correction

2.5 pin 16 generates video claming & blanking pulse.

2.6 pin 18,19 is I2C data.

2.7 pin 21 V-regulation.

2.8 the resistor from pin 28 (HREF) to ground determines the maximum oscillator frequency.

2.9 the resistor from pin 27 (HBUF) to pin 28 defines the frequency range.

2.10 pin 31 H-regulation.

2.11 pin 32 focus.

+48V

7

GND

HPLL1

26

8200P

100V

(PE)

R205

110K

HVADJ

(OPEN)

6

BDRV

HBUF

27

R214

1.27K

(1%)

VR201

R267

56K

C202

0.01U

100V

(PE)

R237

10K

R266

8.2M

ZD204

30V

D201

1N4148

JUMPER

R206

C222

(EL)

R208

5

BIN

HREF

28

R215

2.67K

(1%)

R257R238

+14V

+

R263

R235

1K

2.2K12K

ZD201

12V

R216

C204

+

15.8K

2.2U

(1%)

50V

(EL)

10K

HFLB

FOCUSFOCUS

R268

120K

R260

390K

C226C203

2200P

100U

100V

25V

(EL)

(PE)

1U

50V

+

1M

4

BSENS

HCAP

29

C210C208

0.01U

100V

(EPI)

3

BOP

HPLL2

30

C211C209

2200P

100V

(PE)

C227

0.1U

50V

(D)

2

XRAY

HSMOD

31

R220

JUMPER

1

HFLB

FOCUS

32

R261

(OPEN)

100K

(1%)

D207

1N4148

+14V

R221

10K

TP3 TP2

D206

(OPEN)

R222

4.7K

1/4W

R218R217

22.1K

(1%)

R262

(OPEN)

D208

(OPEN)

Q201

H945

PWM

+48V

HSMOD

SC2

SC1

SC0

HDRV

EWDRV

V2

V1

VBL

HBL

CLAMP

HULK

SCL

SDA

VSMOD

R270

10K

+14V

R264

100

(OPEN)

R201

100

R202

100

R258

R209

100

R210

100

R265

100

16

CLBL

HUNLOCK

17

R211

JUMPER

15

HSYNC

SCL

18

14

VSYNC

SDA

19

13

VOUT1

ASCOR

20

12

VOUT2

VSMOD

21

C206

0.1U

100V

(PE)

R236

10

1/2W

(FS)

11

EWDRV

VAGC

22

+14V

R212

22.1K

(1%)

C207

0.1U

100V

(PE)

10

VCC

VREF

23

R204

2.2K

1/4W

C201

+

47U

50V

(EL)

9

i.c.

VCAP

24

C205

2.2U

50V

(EL)

0.1U

100V

(PE)

+

R203

62K

8

HDRV

IC201

TDA4856

SGND

25

R213

3.3K

HV-ADJ

Fig 2 Autosync Deflection Controller circuit

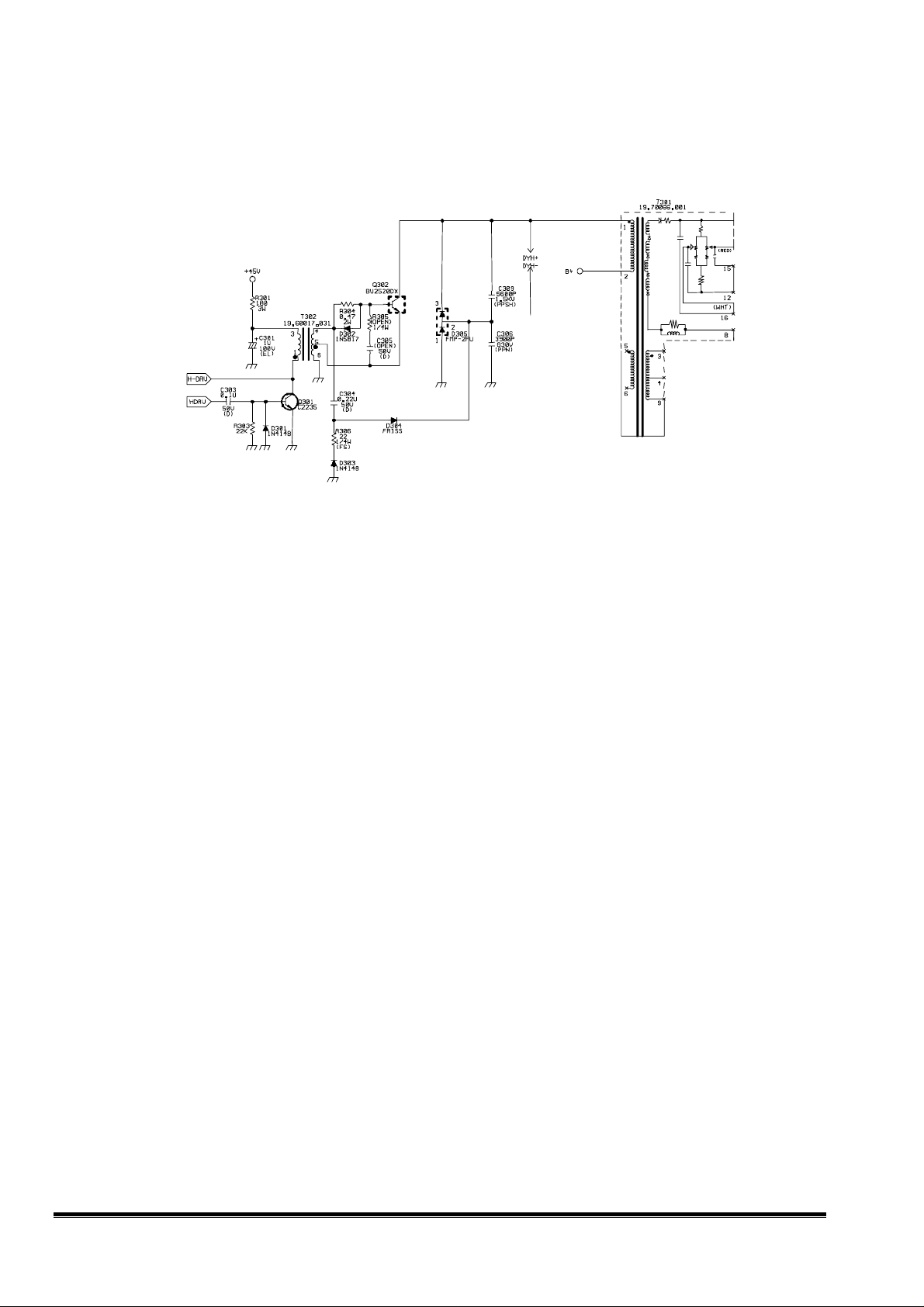

3. H-Driver & Output CKT:

3.1 HDRV signal comes from IC201 pin8, then goes into Q301, Q301 constitutes an inverting stage

and combines with T302 to drive Q302.

3.2 Q302, C306, C309, D305 constitute the H-output CKT with diode modulator mode.

3.3 Q324 & Q325 constitute a switch for lower frequency driver switching to cover the low h

HOT

fe

running under low frequency will occur poor-drive condition.

2

Confidential

Page 3

V772 CRT Monitor Service Guide

Circuit Operation Theory

Fig 3 HDRV & output circuit

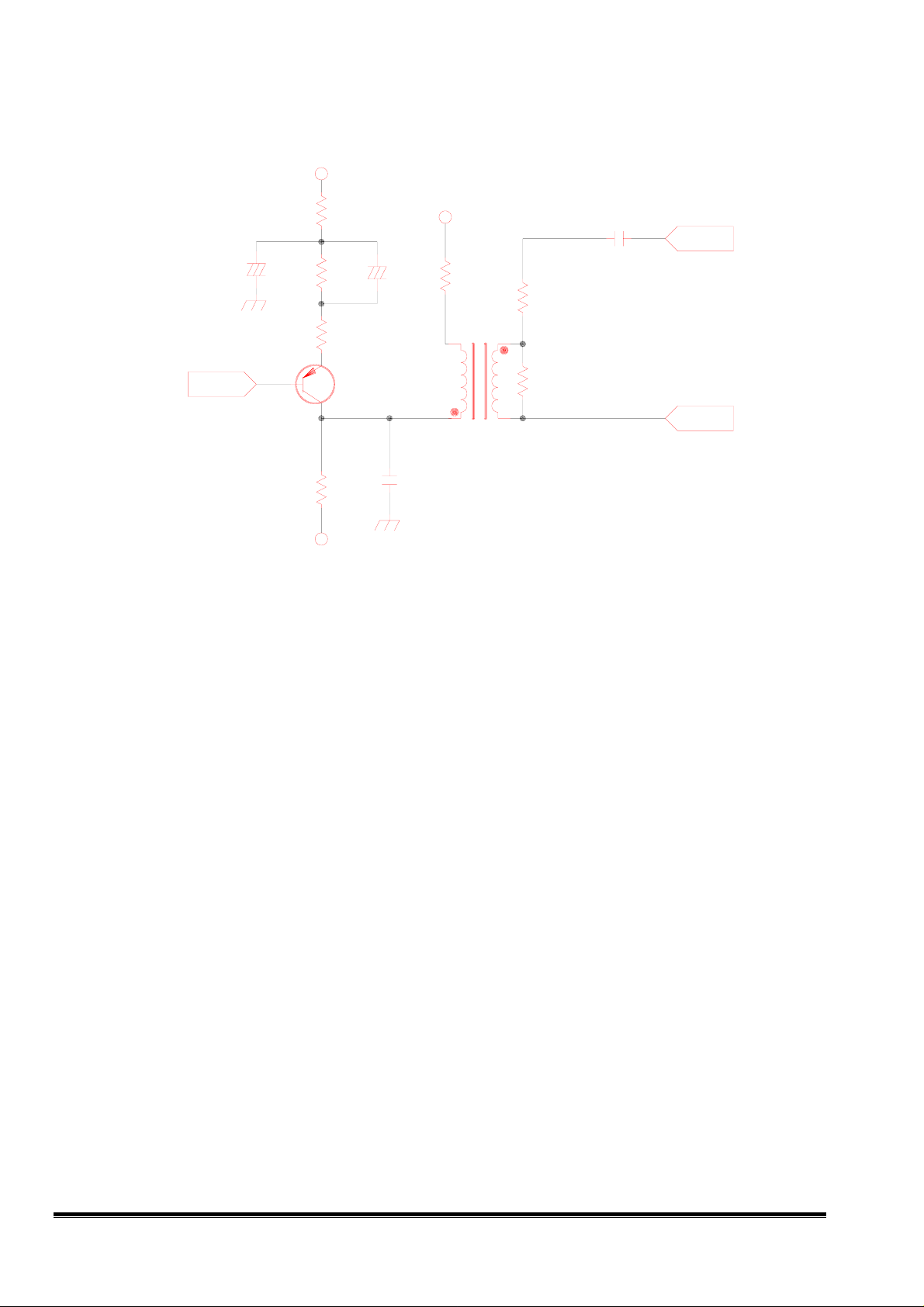

4. Dynamic focus CKT

According to the CRT spec

H dynamic focus Vpp = 300 V

V dynamic focus Vpp = 130 V

4-1 Vertical dynamic focus

The signal from IC201 (pin 32) is a vertical frequency parabolic waveform.

Q321: an inverting amplifier stage.

4-2 Horizontal dynamic focus:

The waveform of C313 (CS-2, CS-1) is a horizontal frequency parabolic waveform, and is amplified by

T304.

3

Confidential

Page 4

V772 CRT Monitor Service Guide

+14V

Circuit Operation Theory

C327

10U

50V

(EL)

19.20113.001

C328

470P

1KV

(D)

DAF

R373

150

1/2W

T304

3

4

C329

0.033U

R327

10

1W

(FS)

2

R379

1K

2W

1

400V

(MPE)

CS-2

CS-1

FOCUS

+

C346

22U

16V

(EL)

-190V

R391

1K

R351

68K

R352

3.9K

Q321

BF423

R353

560K

1/4W

+

Fig 4 Dynamic Focus circuit

5. Brightness & spot killer CKT.

5.1 G1 CKT

The bright control signal from UC controller is about 0 ~ 5V, when the voltage of bright control signal

decreases, the current flow through R241 increases and the voltage of G1 increases.

5.2 Blanking CKT

To avoid the disturbed picture display on the screen, we have to blank the monitor in the following

situations.

(1) when display mode is changed.

(2) when the monitor enter the power saving mode.

(3) blank the vertical retrace line

when the " blank" signal becomes "high" Q208 "ON" , Q203 "OFF".G1 voltage is about ( -190 *

R271/(R271+R241)) ≒ -184V. The signal which is IC201 (pin 16) is inverted and amplified by Q202,

and coupling to G1.During the vertical retrace interval , the G1 voltage will be drop down about 48V.

4

Confidential

Page 5

V772 CRT Monitor Service Guide

Circuit Operation Theory

+

C224

0.22U

250V

(EL)

R271

1/2W

+45V

R232

5.6K

1/2W

C223

0.01U

50V

(D)

CLAMP

R254

2.7K

Q202

H945

R239

6.8K

1M

BLANK

HULK

R255

10K

R256

10K

Q208

H945

BRITE

G1

ZD203

5.1V

R269

+6.5V

R231

100

1/4W

R240

3.3K

Q203

BF423

R241

100K

1K

1/2W

-190V

Fig5 Brightness & Spot killer circuit

6. BDRV and step-up CKT

6.1 The "BDRV" signal from TDA4856 pin6 is a square waveform. It is inverted and amplified by

Q201, Q311 and Q312 constitute a buffer stage.

6.2 Q325, L301, D318, C323 is step-up circuit B+ = 45 * ( T

on

+ T

off

) / T

off

.

+45VB+

C334

1000P

A

+

R333

10

1W

C323

4.7U

250V

(EL)

D318

UG4D

1KV

(D)

IRF630

Q325

C322

(OPEN)

100V

(PE) 19.40195.001

R371

10K

L301

900UH

R370

47

+14V

Q311

H945

Q312

A733

PWM

F

ig 6 BDRV & Step-up circuit

5

Confidential

Page 6

V772 CRT Monitor Service Guide

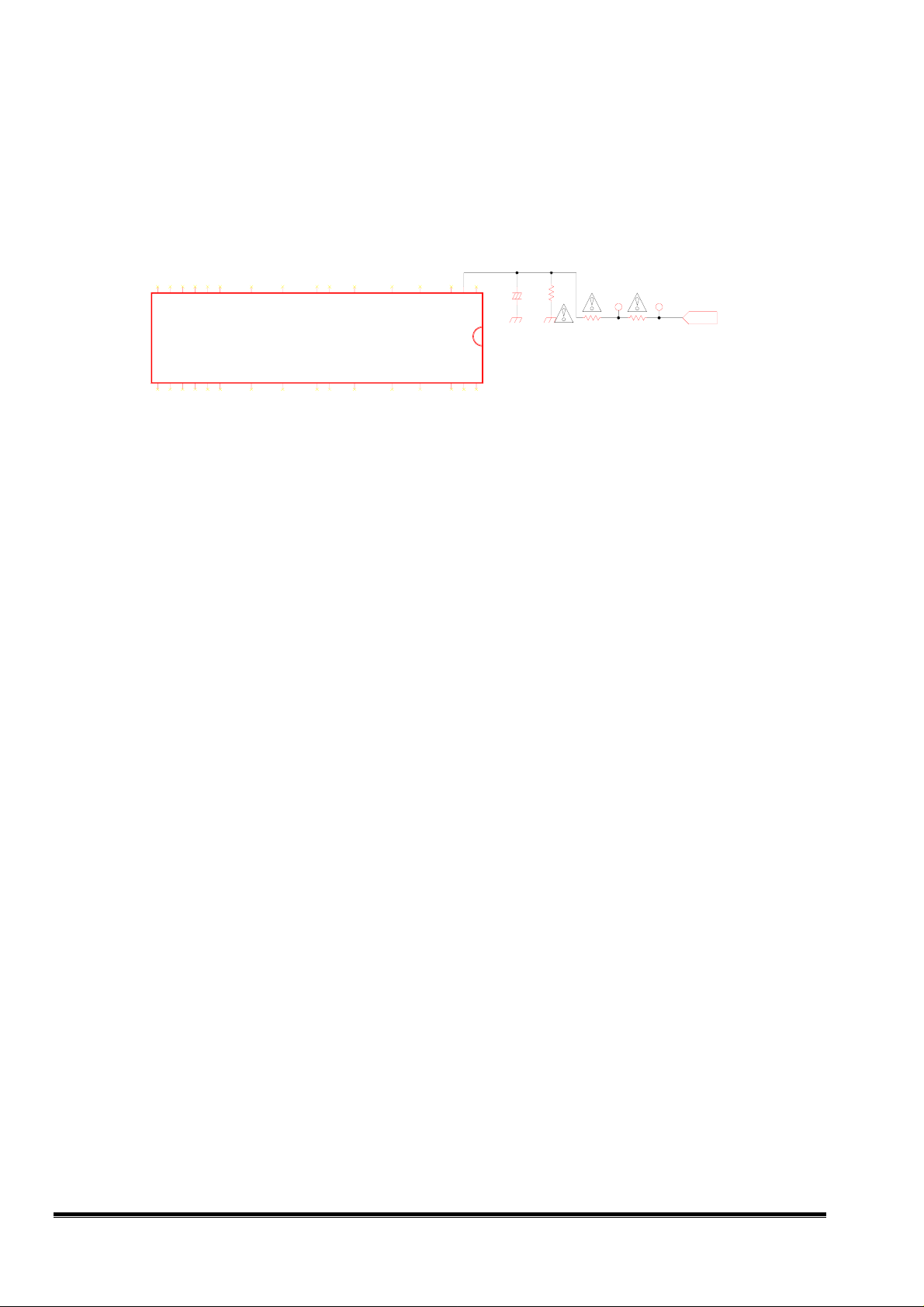

7. HV Shutdown Circuit

Circuit Operation Theory

The IC201 pin2 (XRAY) provides a voltage detector with a threshold. If the voltage at pin XRAY

exceeds this threshold (6.25v typical) the pins HDRV, BDRV, VOUT1 and VOUT2 are floating.

When anode voltage increases, the voltage at FBT (pin3) increases, the voltage at IC201 pin2 increases.

The shutdown voltage is about 28KV.

C204 R216

+

2.2U

16

15

CLBL

HSYNC

14

131211

VSYNC

VOUT1

VOUT2

10

VCC

EWDRV

9

i.c.

TDA4856

8

HDRV

IC201

7

GND

6

BDRV

5

BIN

4

BSENS

3

BOP

2

1

HFLB

XRAY

50V

(EL)

15.8K

(1%)

R217 R218

100K

(1%)

TP3 TP2

22.1K

(1%)

+48V

HUNLOCK

ASCOR

SCL

SDA

17

18

19

20

VAGC

VSMOD

21

22

VREF

23

VCAP

24

SGND

HPLL1

25

26

HBUF

27

HREF

28

HCAP

29

HPLL2

HSMOD

30

31

FOCUS

32

Fig 7 HV- shutdown CKT

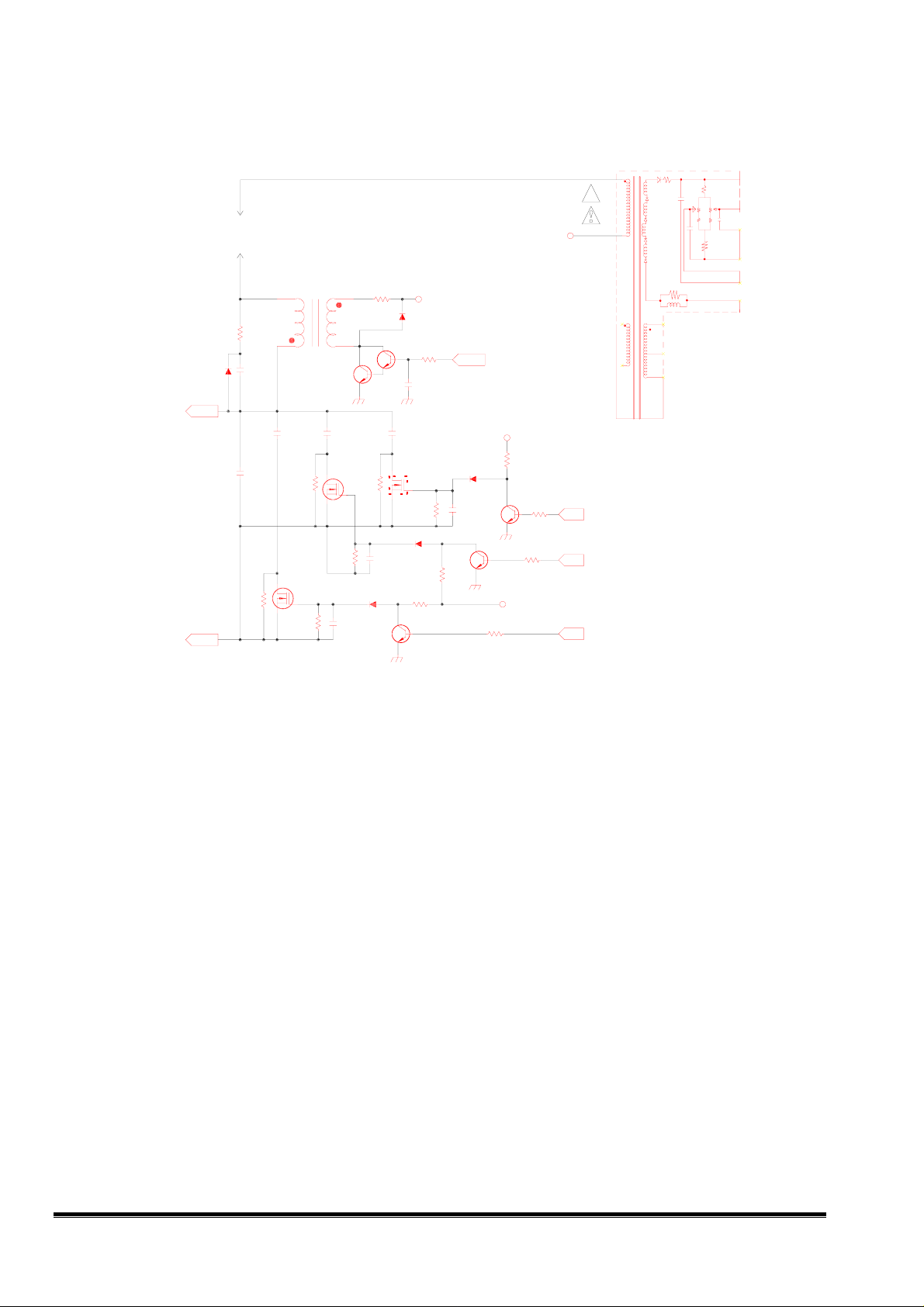

8.Horizontal linearity CKT

V772 Cs control truth table

Frequency range SC0 SC1 SC2 Cs Capacitor

Fh< 36K 0 0 0 C310+C311+C312+C313

36K<Fh<40K 0 0 1 C310+C311+C312

40K<Fh<51K 1 0 1 C310+C312

51K<Fh<62K 1 0 1 C310+C312

62K<Fh<72K 1 1 1 C310

6

Confidential

Page 7

V772 CRT Monitor Service Guide

D

DYH+

DYH-

L304

10UH

19.50051.051

54

0.15U

250V

R338

100K

1/4W

A

Q309

IRF630

A

R313

47K

D312

RGP10J

CS-2

CS-1

B

R309

220

2W

C321

560P

1KV

C310

0.3U

400V

(MPP)

R321

100K

1/4W

B

Q324

C2235

C312

0.33

250V

(MPP)

Q308

IRF630

R324

47K

C315

0.047U

50V

(D)

Circuit Operation Theory

T301

19.70066.001

1

*

(RED)

B+

A

2

10

2W

C317

50V

(D)

Q322

H945

(MPP)(MPP)

IRF640

C311C313

1.0U

250V

Q307

D322

1N4148

R319

10K

C330

(OPEN)

50V

(D)

A

R317

47K

D310

FR155

R326

4.7K

R312

4.7K

+6.5V

H-LIN

FR155

C316

0.047U

50V

(D)

Q304

H945

D309

Q303

H945

R311

47K

+14V

R316

4.7K

+14V

R315

R325

47K

47K

SC0

SC1

SC2

5

3

4

6

9

R322

32

R320

100K

1/4W

0.047U

D311

FR155

Q305

H945

15

12

(WHT)

16

8

Fig 8 Linear circuit

7

Confidential

Page 8

V772 CRT Monitor Service Guide

Circuit Operation Theory

9. ABL CIRCUIT

When the beam current is over the limited current, the ABL circuit will pull down the

voltage of the video preamp (pin 10) to reduce the gain of video amplifier.

T301

19.70066.001

1

(RED)

2

5

3

4

6

9

15

12

(WHT)

16

8

C324

1500P

100V

(PE)

R308

10K

1/2W

D306

1N4148

D307

1N4148

R310

1.5K

R314

6.8K

ABLADJ

ABL

Fig 9 ABL circuit

8

Confidential

Page 9

V772 CRT Monitor Service Guide

Circuit Operation Theory

10. TILT CKT

We can rotate raster clockwise or counterclockwise by changing the direction of the current flow

through the tilt coil.

When the voltage of MP202 (pin3) is larger than 8V, the current flows from Q205 to Tilt coil, other

wise, the current flows from tilt coil to Q206

Q205

H945

Q206

A733

+6.5V

(OPEN)

+

(EL)

R249

1/4W

TILT-COIL

C228

2.2U

50V

MP202

3P

1

2

3

TILT

+5V

R243

(OPEN)

R244

2.2K

+14V +14V

Q207

R247

2.2K

R246

10K

Q204

H945

R245

10K

C225

+

2.2U

50V

(EL)

H945

Q210

A733

Fig 10 TILT circuit

9

Confidential

Page 10

V772 CRT Monitor Service Guide

11. Vertical Output Circuit

This vertical driver IC circuit is a half bridge configuration

The signals from TDA4856 OSC IC to TDA4863AJ

IC202

TDA4863AJ

-8.5V

Circuit Operation Theory

+14V

C217

470U

16V

+

R253

180

1/4W

C220

0.1U

100V

(PE)

(EL)

R251

1.8K

180

1/4W

R228

V1

V2

C219 C218 C214

5600P

100V

(PE)

1K

R229

1K

5600P

100V

R250 R252

(PE)

1.8K

R225

1

1/2W

DYV+

DYV-

INP

7

INN

6

R224

5.6

1/4W

C216

0.1U

100V

(PE)

TR201

100

GND

V-OUT

5

VP3

VP2

3

4

2

+

100U

35V

(EL)

R226

270

C215

470U

16V

+

(EL)

Fig11 Vertical output circuit

VP1

1

D202

1N4003

ZD202

20V

R274

33K

R275

27K

R227

0.22

1/2W

(FS)

C213

+

1000U

25V

(EL)

(105C)

V+

10

Confidential

Page 11

V772 CRT Monitor Service Guide

Switching Power Supply Operation Theory

1. General Specification

Input Voltage: 90~264VAC (FULL RANGE)

Input Frequency: 47~63Hz

Output Requirement: Dc Output

+6V

+13V

+78V

+45V

-10V

2. Block Diagram

DEGAUSS

CIRCUIT

AC

INPUT

RFI

FILTER

RECTIFIER

&

FILTER

SWITCHING

ELEMENT

ISOLATION

TRANSFOR

-MER

Circuit Operation Theory

OUTPUT

RECTIFIER

AND

FILTER

OUTPUT

FEEDBACK

CONTROL

CIRCUIT

POWER

SAVING

CONTROL

3. Circuit Operation Theorem

3.1 RFI FILTER

FG

L

L602

34

R601

12

N

C601

0.47U

250V

(X)

C603

2200P

250V

(Y)

C602

2200P

250V

(Y)

L603

L604

This circuit designed to inhibit electric and magnetic interference for meet FCC, VDE, VCCI standard

requirements.

11

Confidential

Page 12

V772 CRT Monitor Service Guide

3.2 Rectifier and filter

L

AC INPUT

D602~D605

20D6 * 4

3

~

4

-+

1

Circuit Operation Theory

+

C612

220U

400V

(EL)

DC OUTPUT

~

2

N

When power switch is turn on, the AC voltage is Rectifier and filter by D603~D606, C612. The DC

output voltage will be 1.4*(ac input)

3.3 switching Element and isolation transformer

11

12

10

16

(SHORT)

13

FR701

(SHORT)

FR702

(SHORT)

15

18

FR704

C53

EGP30B

C608

47U

25V

(EL)

R604

C614

(OPEN)

D608

RGP10D

82K

2W

R608

20K

L607

(BEAD)

0.01U

C50

D610

UF4007

FS14SM-12

R611

1K

B61

C613

1KV

(D)

C51

UF4007

R607

0.15

2W

Q602

D614

*

L606

(BEAD)

L608

(BEAD)

C624

220P

T601

6

ZD601

(OPEN)

D613

(OPEN)

1

8

1KV

(D)

R619

470

2W

9

In a flyback converter operated in the discontinuous mode, the energy stored in the flyback

transformer(actually an inductor) must be zero at the beginning and end of each switching

period.

During the "ON" time, energy taken from the input is stored in the transformer when

12

Confidential

Page 13

V772 CRT Monitor Service Guide

Circuit Operation Theory

the switching transistor turn-off, this stored energy is all delivered to the output.

3.4 Output Rectifier and filter

The structure of each output is illustrated as below

T601

since the transformer T601 acts as a storing energy inductance, diode D1 and capacitor C1 are to

produce a dc output and additional L1, C2 to suppress high-frequency switching spikes.

D1 L1

+

C1

+

C2

13

Confidential

Page 14

V772 CRT Monitor Service Guide

3.5 Control circuit

Circuit Operation Theory

R613

36K

C615

2200P

50V

(PE)

R612

47

1N4004

R614

100K

C616

0.01U

100V

+

C617

4.7U

50V

(EL)

M603

D611

1N4148

D612

1N4148

C625

(OPEN)

8

4

C618

0.01U

50V

(D)

76

VCC OUT

VREF

IC601

UC3842

R/C

C619

0.022U

50V

(D)

R615

51K

R616

10K

ISSEN

IC603

MCR100-3 24V

A

R620

10K

R607

0.15

2W

R611

3

GNDFBCOMP

521

ZD602

R622

510

GK

C627

+

50V

(EL)

10U

+6.5VA

1K

*

*

C620

820P

50V

(D)

(PE)

ZD603

5.1V

4 1

M604

R738

82

1/2W

The current mode control IC UC3842 is used in the switching power supply which function of each

pin

described as follows.

pin 1 : Error amplifier output pin 5 : Ground

pin 2 : Error amplifier reverse input pin 6 : Output

pin 3 : Current sense pin 7 : VCC

pin 4 : OSC sawtooth pin 8 : Reference Voltage:5V

14

Confidential

Page 15

V772 CRT Monitor Service Guide

Circuit Operation Theory

When power is initially applied to the circuit, capacitor C626 charges through R624, R623, ZD601.

When the voltage across C607 reaches a level of 16V, IC601 is turn-on the +5Vdc will be

set up at pin8 then R613, C615 generate a fixed frequency sawtooth wave to pin4, at this time

MOSFET will be driver by pin6 with square wave the pulse width of square wave is decided by

pin2, pin3 is current feedback control, It will to sense MOSFET current. The D613, D612, R614,

C617 are soft start components to avoid the duty too large when power starts up.

3.6 Feedback circuit

This power supply is a primary feedback circuit. It used IC601 for voltage regulation

, The output voltage differential signal will be detected and sensed to the pin2 of UC3842 for

comparison then the duty cycle of MOSFET will be decided to control the output voltage.

R614

100K

+

D612

1N4148

D613

1N4148

C617

(EL)

ZD602

0.15

2W

R611

1K

24V

C620

820P

50V

(D)

1

(D)50V(OPEN)

8

4

C618

10U

50V

0.01U

57.6K

R616

50V

(D)

C609

76

VCC OUT

VREF

IC601

UC3842B

R/C

C619

0.022U

50V

(D)

R615

560K

(EL)

+

50V0.22U

VR601

*

2K

R618

*

(OPEN)

ISSEN

9.09K

3

GNDFBCOMP

521

R617

*

15

Confidential

Page 16

V772 CRT Monitor Service Guide

3.7 DEGAUSS CIRCUIT

Circuit Operation Theory

+12V

DEGAUSS

L610

TR602

2R9M

2P

C604

(OPEN)

250V

RL601

1

2

56

1

(Y)

L611

L604

180UH

3T

1N4148

Q740

H945

D740

R741

2.2K

43

L603

180UH

M602

2

B53

3T

This circuit has the function of auto degaussing and manual degaussing. When power supply is

switched ON it is auto degaussing stage. When user make the selection of the manual degaussing

function in OSD, the degaussing current will flow through coil to degauss the screen of monitor.

TR602 is a PTCR to control degaussing coil current

3.8 power saving control

Mode H-sync V-sync LED Power Rating

Normal Normal Normal Green

Stand-by None Normal Amber

Suspend Normal None Amber

Off None None Amber

100﹪

≦

5W

≦

5W

≦

5W

When both of the H-sync and V-sync are none, the power supply +14v output will be cut-off.

The power input will be under 5W.

When the H-sync or V-sync is none, the power supply +14v output will be cut-off. The power input

will be under 5W.

16

Confidential

Page 17

V772 CRT Monitor Service Guide

30. Video CKT

V772 VIDEO C.K.T. BLOCK DIAGRAM

Circuit Operation Theory

:

31. OSD Preamp CKT:

(a) AS shown in the block diagram:

The R/G/B signals will generate an enough amplitude of Vpp to show up on the

CRT screen after the amplification of two amplifiers. The first one, preamp CKT,

process the signal and mix up the OSD, and the second one does the power

amplification.

(b) OSD preamp IC101, LM1269, will output the R.G.B signals separated. The R.G, B

driver will control the gain of these three guns individually to approach the white

balance of CRT.

(c) The signal H-Blank is to let the output of LM1269 down to 0.2V while non-display

duration. Then the CRT driver CKT will generate a level higher than Black Level. (i.e.

SYNC TIP), therefore the video signal will be blanked in order to prevent the fold over

to occure while adjusting H-phase. Besides, the SYNC TIP is used for

the DC Restoration of cascode CKT.

(d) LM1269 is equipped with OSD mixer, when signal CUT is Low, the output of

LM1269 is video signal when signal CUT goes high, the output will be OSD signal.

17

Confidential

Page 18

V772 CRT Monitor Service Guide

Circuit Operation Theory

32. CRT DRIVER CKT:

Output stage adopts CRT driver LM2468 to amplify the signal which has been

recessed by LM1269 to a enough amplitude of Vpp, then display on the CRT. The IC

contains three high input impedance, wide band amplifiers which directly drive the

RGB cathodes of a CRT. The gain of each channel is internally set at -15 and can

drive CRT capacitive loads as well as resistive loads presented by other application

limited only by the package’s power dissipation.

33. DC Restore CKT:

(a) The video signal amplified by the output stage is coupled to CRT by way of AC

coupling. So DC restoration CKT is needed to do the white balance adjustment.

(b) This DC restoration circuit adopts SYNC TIP CLAMP, in the duration of

SYNC TIP the capacitor charges, and the capacitor discharge in the other time.

The Black Level is kept to the level of DC restoration set by UC.

34. ABL CKT: (Auto Brightness Limit)

ABL is a protection circuit. When the anode current goes higher than the setting

value of ABL circuit. ABL will pull down the voltage of contrast to limit the anode

current. This is helpful to protect CRT.

35. H-BLANK CKT:

Affair the collect pulse comes from FBT being shaped and inverted, it will be sent

to preamp CKT and used as the H-Blank.

36. Brightness, V-blank, change mode blank, spot killer CKT:

(a) About the cut off voltage , while the voltage, cathode to G1 , over the cut off ,

voltage, the picture will disappear, If cut off voltage of the CRT is

set at 110V and the black level of cathode is 60v, the picture won’t show,

the signals higher the black level once the G1 voltage is lower than-50v.

(b) As described above, we may using the voltage control G1 as the brightness

control. Generally the G1 control range is about 10~15V if the raster

brightness is form 0 to 0.8 ft-L.

(c) Similarly, we may overlap a negative pulse of vertical duration on the G1

voltage to prevent the vertical retrace line from showing on the picture , This

is to keep the voltage cathode to G1 over the cut off voltage during the

period of vertical retrace.

18

Confidential

Page 19

V772 CRT Monitor Service Guide

Circuit Operation Theory

(d) In order to avoid the picture occur transiently while change mode, pull

down the G1 voltage and let the voltage cathode to G1 over CUT OFF voltage.

This will make the picture blanking.

(e) While monitor turned off , the discharge speed of high voltage circuit is slow

since there is no deflection scan act on the electronic beam, a spot which will

destroy the phosphor of CRT. So the SPOT KILLER circuit will generate a

negative voltage higher than CUT OFF to the G1 to beam this is to protect

the CRT.

19

Confidential

Page 20

V772 CRT Monitor Service Guide

g

Circuit Operation Theory

ACER V772 MICROCONTROLLER CIRCUIT OPERATION THEORY

1.

Introduction:

This model, V772, will support powerful OSD function to help end user fine adjustment. The

Microcontroller circuit of the V772 can determine what mode it is by detecting the frequency of

horizontal and vertical synchronous and the polarity of horizontal synchronous, and provide DC

voltages to control the picture and save the adjusted value into the EEPROM by using the OSD,

"On Screen Display control", that means the user can get any information of the picture display or

adjust it and save the status values into the EEPROM by choosing and pressing the proper key

according to the indication of the OSD. In addition, user can press i-key to do auto-calibration.

2.

Block diagram :

The major parts of V772 Microcontroller circuit are MCU, EEPROM, OSD IC, and Auto

Calibration Module. The circuit block diagram is shown as below.

MCU

(MTV112)

Hsync

Vsync

H-polarity

EEPROM

Preset mode data,

User saved mode data.

Reset circuit

12MHz Crystal

circuit

Control Panel

5 keys input

i-key

Left,Right,Enter,Exit

Detecting the

input signals

of H,Vsync &

H-polarity.

Searching for

the same saved

mode timing

with the input

signals and

et the data.

Checking if the

valid key be pressed

and do key function.

(UART) External

adjustment

function

PWM

output

Degaussing

Blanking

SC0 - SC2

OSD IC

Display OSD

and output

PWM to video

circuit

To deflection

circuit

DCLK

DATA

AP3113

Calibration

PC

RS232

auto alignment

program

Auto

Module

HBNK

VBNK

RGB

Signal

20

Confidential

Page 21

V772 CRT Monitor Service Guide

3.MCU and the peripheral circuit operation theory:

3-1.MCU function:

The MCU is MTV112, it is an 87C51 with PWM output controlled microcontroller, after

power on, the reset circuit output a "High" to "Low" signal (>40mS) and the 12MHz crystal

oscillated circuit working, the MCU begin to manages the following functions,

(1) To detect mode and output proper SC0, SC1 and SC2 to deflection circuit.

(2) To check if there is the same saved mode in the EEPROM and get the data to transfer into

DC voltages by PWM output and RC filter circuits to control the picture, color, contrast

and brightness.

(3) To check if there is the valid key be pressed and do the key function.

(4) To memorize mode timings and any adjustable parameters of the picture into EEPROM.

(5) To output data to OSD IC for making an "on screen display control" menu.

(6) The inner registers and PWM output of MCU can be controlled by the external PC

alignment program.

(7) To calibrate the size, position, and geometry of the picture by pressing i-key. It will be

placed right size and position.

3-2.How to detect mode timing:

Only when the mode timing input is stable, we can adjust the picture and check the

horizontal and vertical sync frequency by the OSD menu, and the mode timing input mean the

horizontal sync signal and the vertical sync signal.

(1) The vertical sync frequency measurement:

We use the base timer, it can generate a count during a fixed time, this fixed time is

12/12MHz and we call it "Time base", so when the first vertical sync generated, we enable

the base timer, and the next vertical sync generated, we disable the base timer, and we only

need to calculate how many counts are during a vertical sync period. The formula is

Vertical sync frequency

= FV

= 1 / Vertical sync period

= 1 / [Counts * (Time base)]

==> Vertical sync frequency = 1000000 / Counts

(2) The horizontal sync frequency measurement:

We use the event counter for calculating how many counts are during a long fixed time,

because the vertical sync period is longer than the horizontal sync period, we can enable the

event counter when the first vertical sync generated and disable the event counter when the

next vertical sync generated, this time, we can get the horizontal sync counts during a vertical

sync period.

The formula is Horizontal sync frequency

= FH

= Horizontal sync counts / Vertical sync period

==> Horizontal sync frequency

= Horizontal sync Counts / Vertical sync period

Circuit Operation Theory

21

Confidential

Page 22

V772 CRT Monitor Service Guide

u

3-3.What are the valid key functions for user:

There are four keys on V772 control panel. They are "Left," "Right," "Enter," and "Exit."

There are used for OSD controlling. "Enter" for entering sub-menu of main menu, "Exit"

for escaping to main menu from sub-menu or leaving OSD menu, and "Left," "Right" for

adjusting the bar value.

Except the OSD basic key functions, the user can only press "Right" for brightness

adjustment, or "Left" for contrast adjustment.

3-4.How to memorize the timing and adjusted data:

The EEPROM of V772 is 24C08, it has 1024 bytes memory size and communicates with

MCU by two wires of I2C bus, one wire is "SCL," the other is "SDA".

The MCU send clock and data to EEPROM to do "Write" function and send clock and

receive data from EEPROM to do "Read" function by these two wires.

We define three parts of storage area. One is for the storage of the factory preset data,

another is for saving user adjusted data, the other is for common settings area where stored

the data of the OSD color temperature settings, contrast and brightness value.

3-5.How to display the OSD menu:

The OSD IC of V772 is AP3122 which is developed by vender, it receives the data of the

OSD fonts and attribute what we want to display on the screen from the MCU by 2 wires of

communication, and exports OSD window data and PWM volume to the VIDEO circuit, the

block diagram is shown as below,

MCU(MTV112)

OSD IC (AP3114)

SDA

(1)Send data to

RAM for OSD

SCL

Shift receiving

register and decoder.

fonts or

attribute.

(2)Send data to

Control

registers

for PWM ouput

Control

register

s

RAM

Fonts

generator

PWM

output

Circuit Operation Theory

Output to

the VIDEO circ

ROUT

GOUT

BOUT

FBKGC

VSYNC

HSYNC

(H-BLANK,HBNK)

3-6.How to execute the auto alignment function:

The MCU MTV112 supports the UART function, it has 2 I/O serious ports, one is the

receiver, the other is the transmitter, they are connected with an interface to PC and PC can

execute alignment program by RS232 communication to send the formatted data to the MCU

for adjusting any adjustable parameters of the picture and saving the adjusted values into

22

VCO circuit

Confidential

Page 23

V772 CRT Monitor Service Guide

EEPROM. By this way, we can get the products with the same quality and reduce the

manufacturing time.

Circuit Operation Theory

23

Confidential

Loading...

Loading...