Page 1

DLP PROJECTOR

SERVICE MANUAL

MODEL:PE8700

CAUTION

BEFORE SERVICING THE PROJECTOR,

READ THE SAFETY PRECAUTIONS IN THIS MANUAL.

Page 2

Contents

1. Safety Precautions 2

2. Servicing Precautions 2

3. Engineering Specification 3

4. Spare Parts List 23

5. Block Diagram 24

6. Packing Description 25

7. Appearance Description 26

8. Alignment Procedure 28

9. Trouble Shooting Guide 39

10. Factory OSD Operation 49

11. Firmware upgrade procedure 56

12. RS232 Codes 58

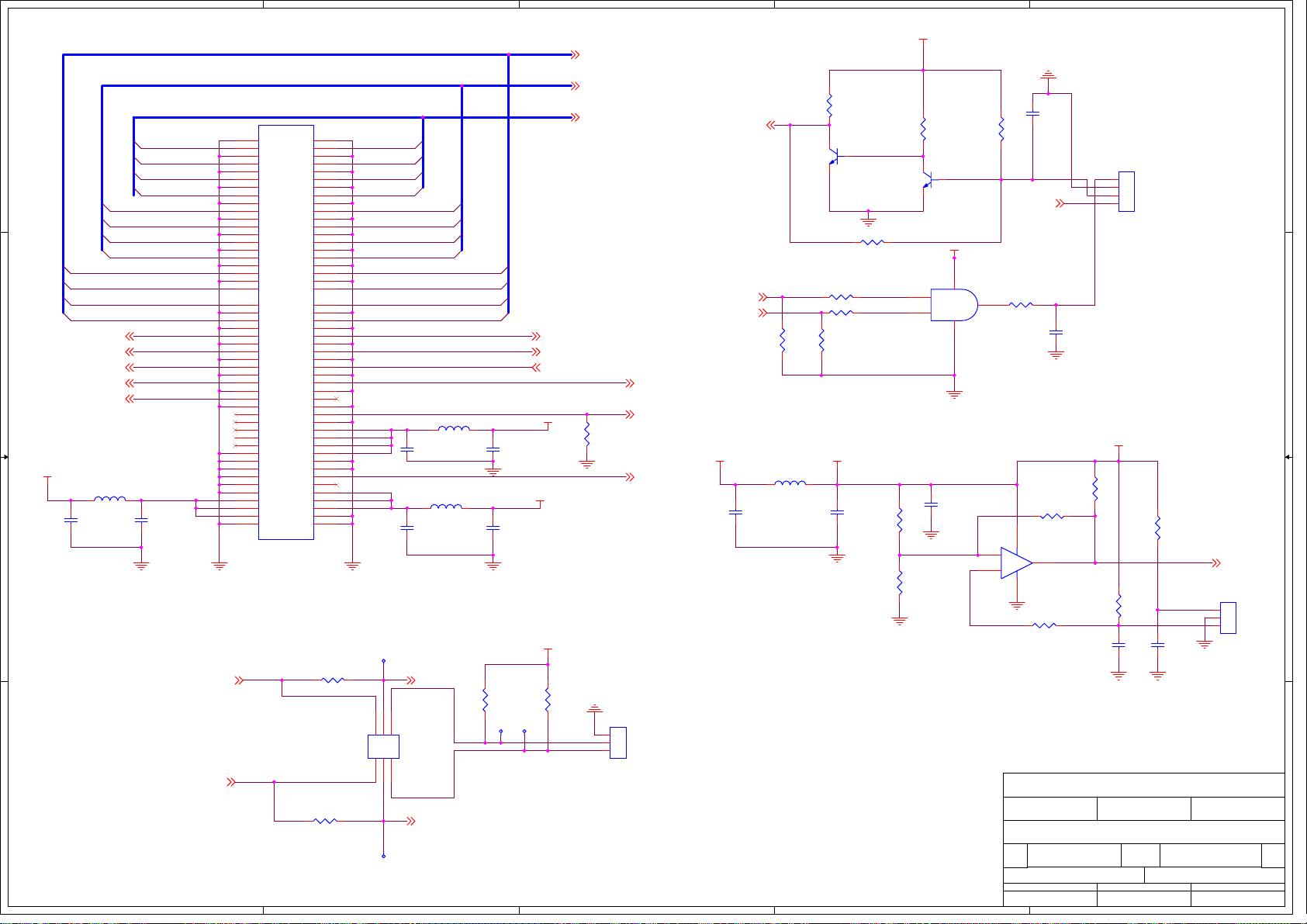

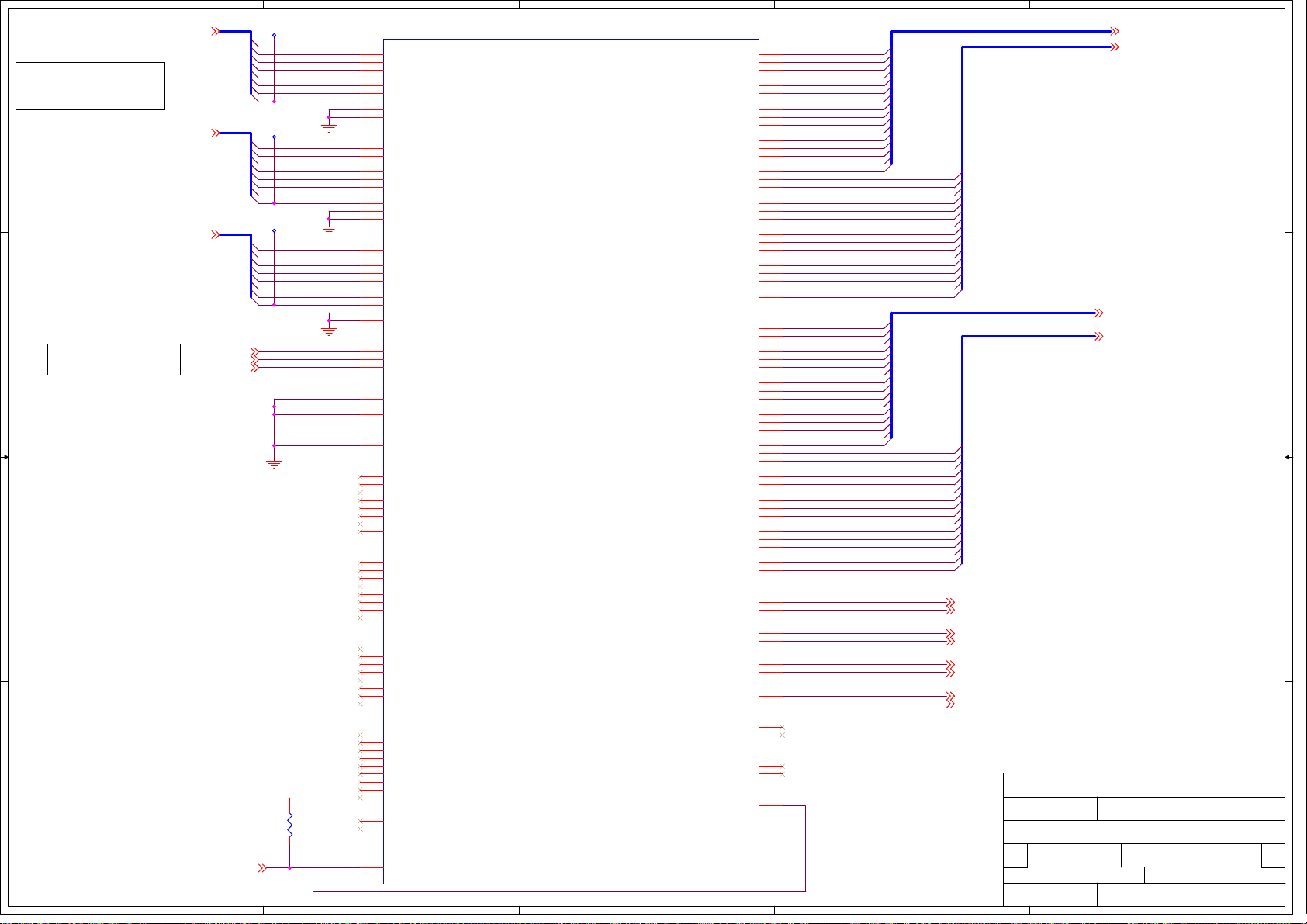

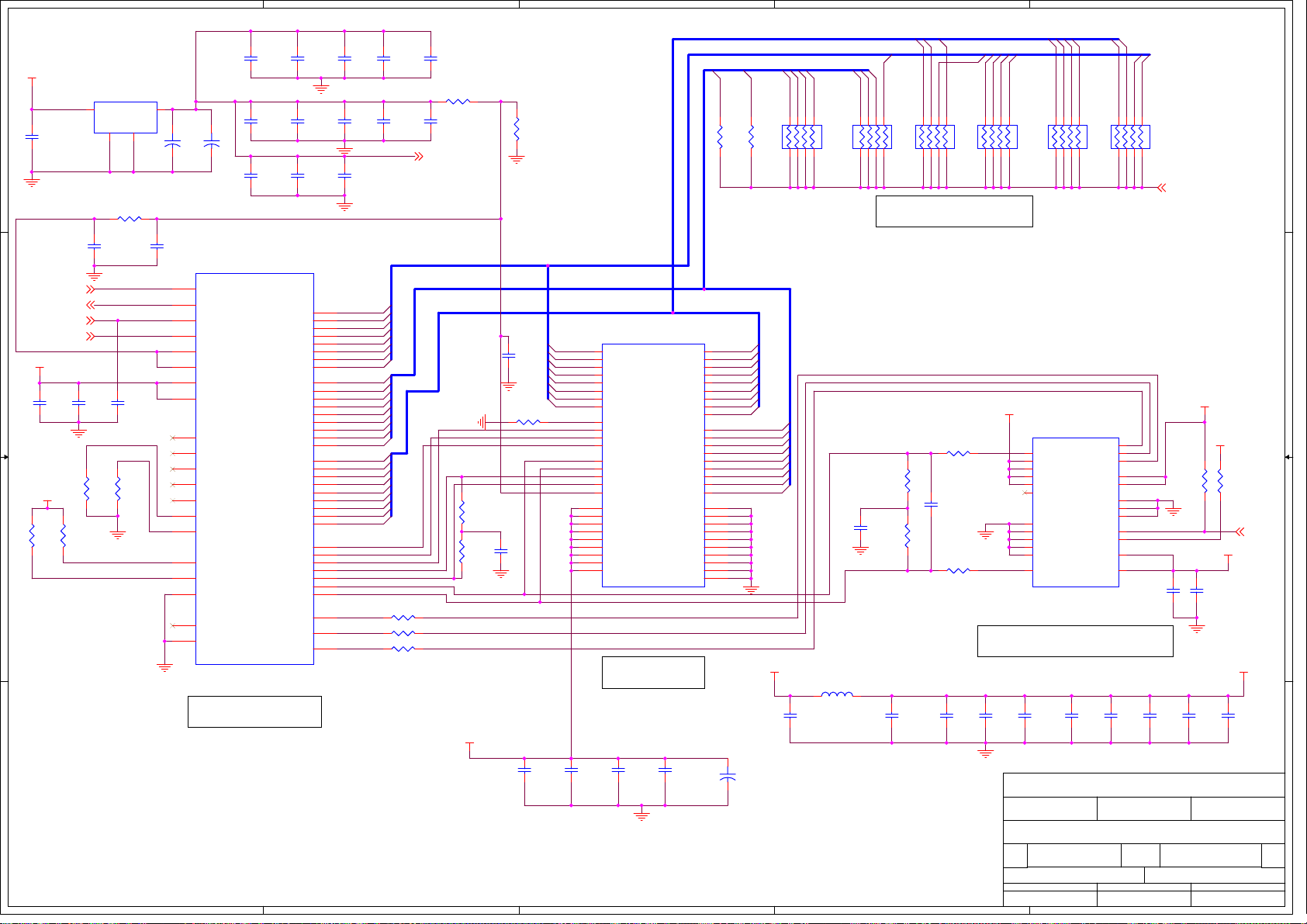

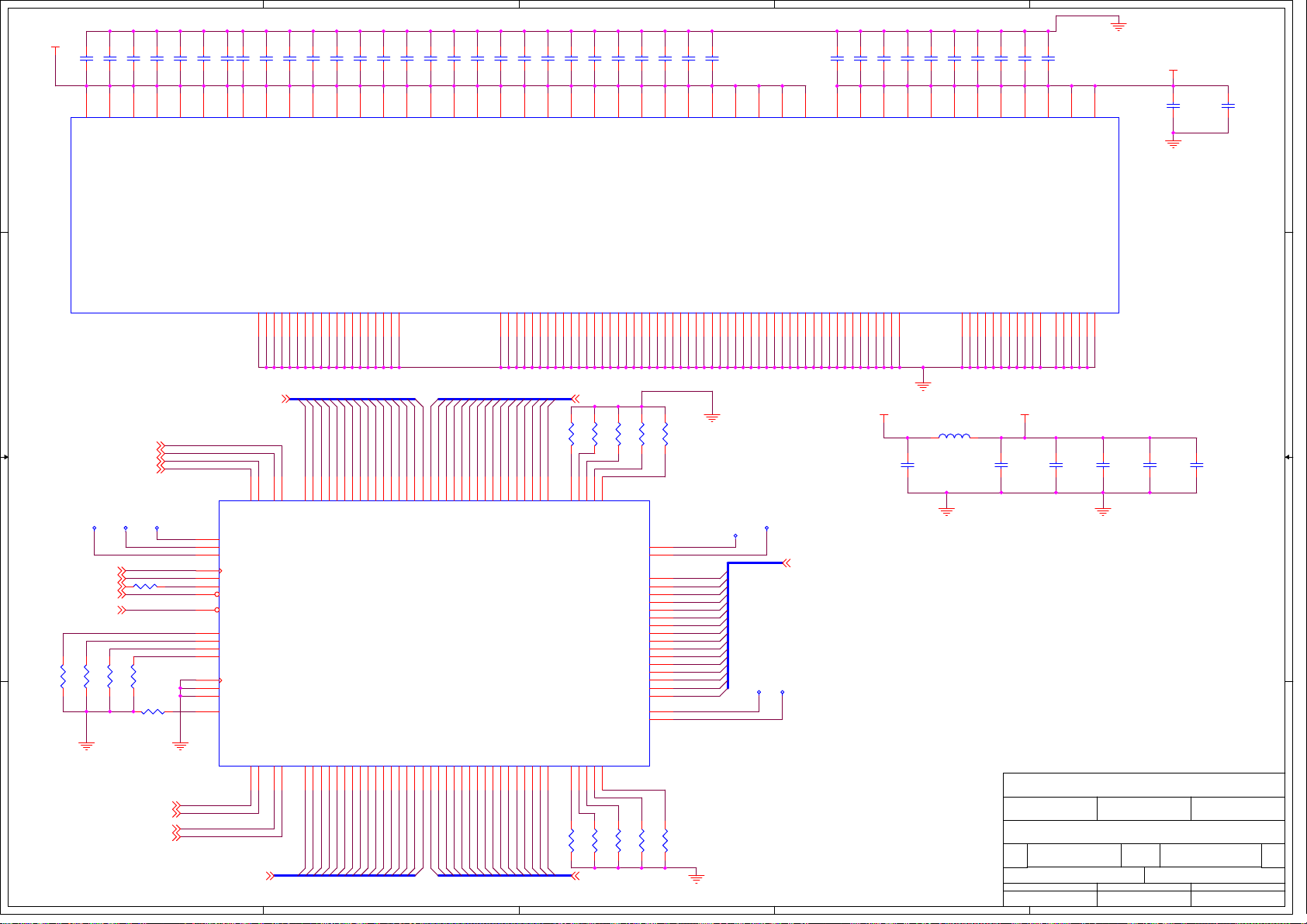

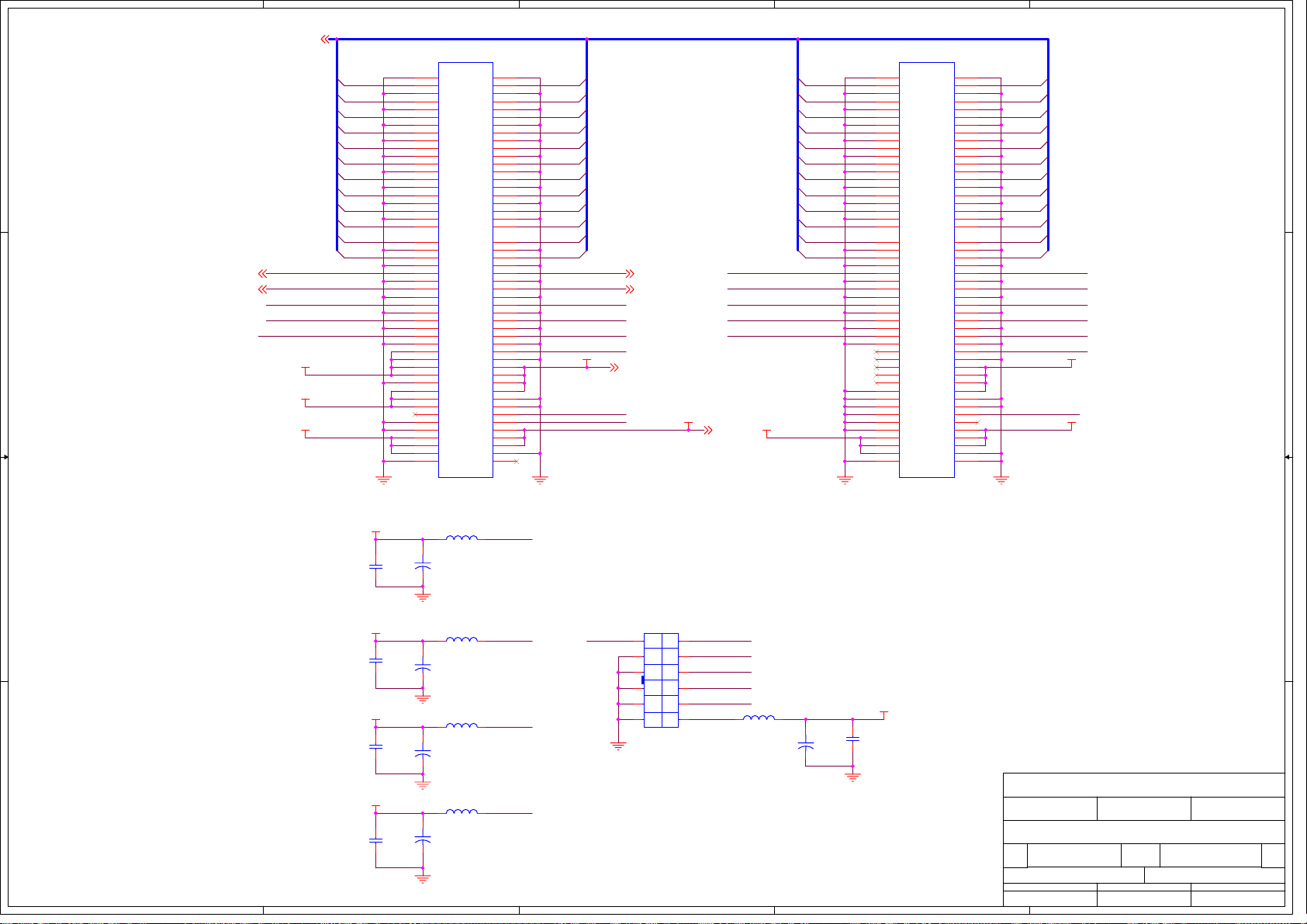

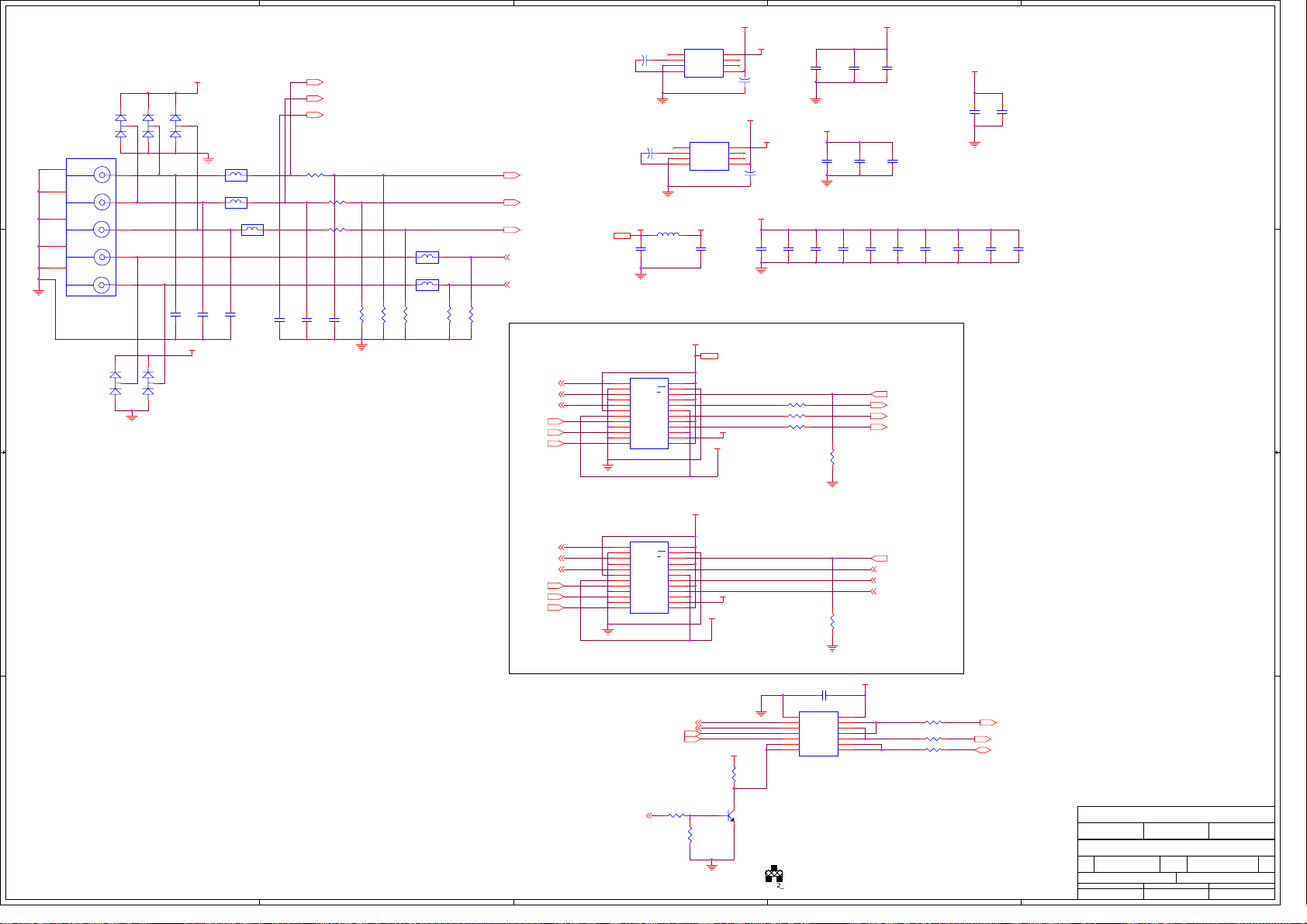

13. Schematics 69

1

Page 3

1. Safety Precautions

1. Be sure to read this manual before servicing and save it for future reference.

2. The lamp becomes extremely hot during operation. Allow the projector to cool for

approximately 45 minutes prior to removing the lamp assembly for replacement. Do not

operate lamps beyond the rated lamp life. Excessive operation of lamps beyond the

rated life could cause them to explode on rare occasions.

3. Never replace the lamp assembly or any electronic components unless the projector is

unplugged.

4. To reduce the risk of electric shock, do not disassemble this appliance. Take it to a

qualified technician when service or repair is required. Incorrect re-assembly can cause

electric shock when the appliance is subsequently used.

5. Do not place this product on an unstable cart, stand, or table. The product may fail,

sustaining serious damage.

2. Servicing Precautions

1. When replace the lamp, be sure to avoid burns your fingers because the lamp becomes

too hot.

2. Never touch the lamp bulb with a finger or anything else. Never drop it or give it a shock.

They may cause bursting of the bulb.

3. This projector is provided with a high voltage circuit for the lamp. Do not touch the

electric parts of power unit when turn on the projector.

4. Do not touch the exhaust fan during operation.

2

Page 4

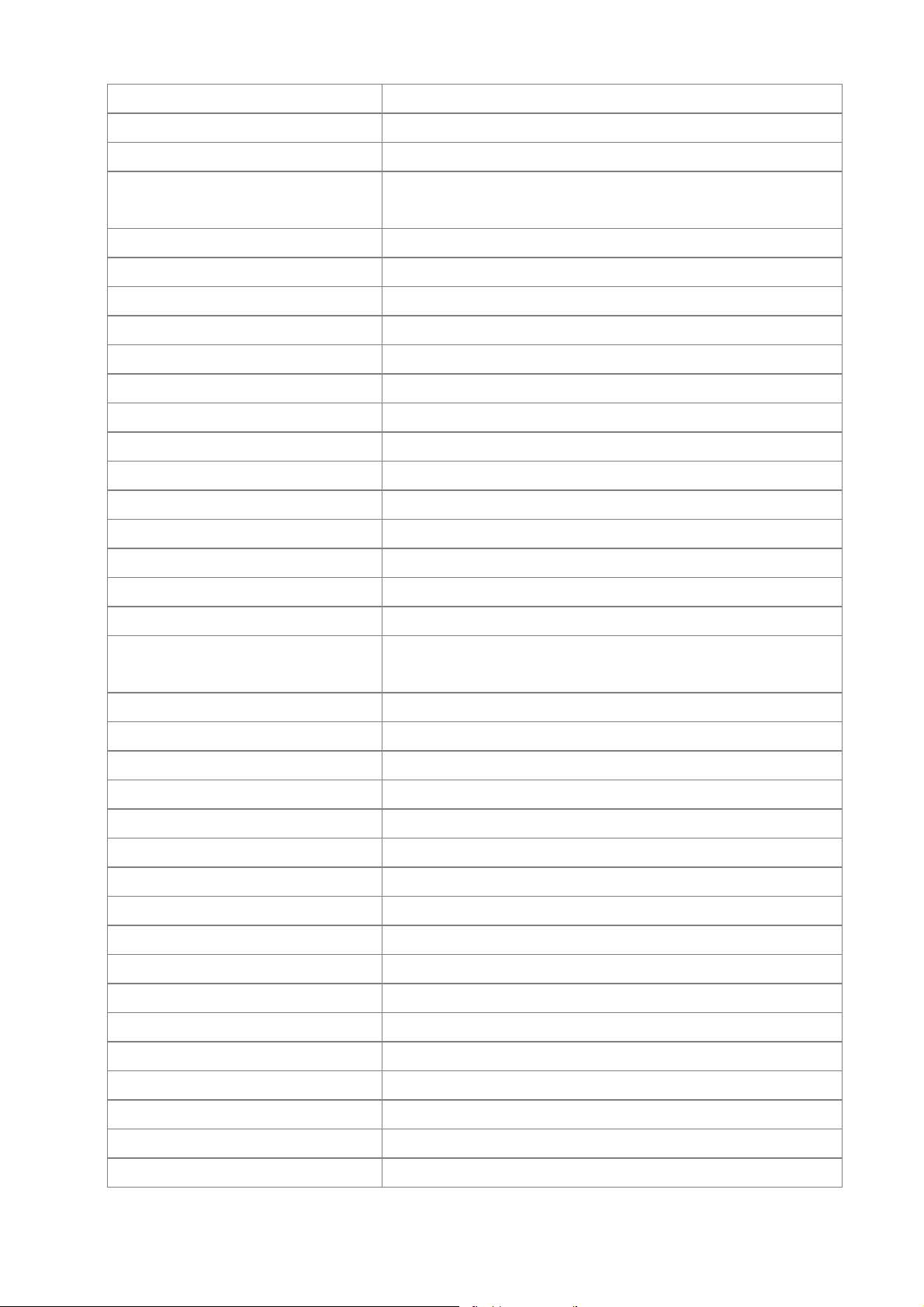

3. Engineering Specification

Superscripts indicate the method in Appendix B used for a given measurement, unless otherwise

noted.

1.0 Image Quality All tests must adhere to the assumptions in Appendix A

1.1 Brightness (In ‘optical test’ mode)

1.1.1 Typical 660 ANSI Lumens

1.1.2 Minimum 450 ANSI Lumens

1.2 Brightness Uniformity (In ‘optical test’ mode)

1.2.1 Typical 73 %

1.2.2 Minimum 60 %

1.3 Contrast Ratio (In ‘optical test’ mode)

1.3.1 Peak Contrast 1400:1 (Minimum)

1.4 Light Leakage

1.4.1 Blue Edge Procedure: Test @ distance 3m with 100% white pattern

Criteria: Color coordinateΔx,Δy≦0.015 (compared with the

center)

1.4.2 Light Leakage out of

Active Area

1.4.3 Reflective Edge Condition: distance 3m or image of 100” wide

1.4.4 Blemish / Dust Test Pattern: Blue 90 with linear de-gamma / Gray 6

1.5 Color All Color Measurements must adhere to the assumptions in

X Y

1.5.1 100% Gray (White) .274 ± .04 .318 ± .04

1.5.4 Red .647 ± .04 .341 ± .04

1.5.5 Green .304 ± .04 .566 ± .04

< 1 lux @ diagonal 60”

Test Pattern: without connecting any source to projector

Criteria: No horizontal and vertical lines outside of the image

Criteria: Follow HD2 DMD image quality specifications

Appendix A

TBD --PPR final

1.5.6 Blue .129 ± .04 .080 ± .04

1.6 Color Uniformity20 x y

1.6.1 100% Gray (White)

1.6.2.1 L1->L9 ±.04 ±.04

1.6.2.2 E10->E13 ±.04 ±.04

1.7 Mirror Defects / Dot Defects Dark pixels<=2, bright pixels =0 (See Appendix D)

1.8 Image Distortion Pincushion 1.0%

3

Page 5

Keystone 1.0%

1.9 Descriptive Image Quality There should be no streaks or jitter, good saturated colors, and

crisp resolution. Must adhere to Appendix E

1.10 Lateral Color 1 Pixel

1). 52” Diagonal for OPT test;

1.11 Screen Size for Testing

2). Distance 3.0m for Focus test. ( Tele @ the same Throw

Distance. )

Criteria: Pixel clear ( same as test chart )

2.0 Optical

2.1 Optical Structure Single Chip 0.8” 12° tilt DMD ( HD2 ) from Texas Instruments

(HD2 Front Projection Image Quality Specification described in

Appendix D)

2.2 Projection Lens Manual Zoom & Focus

2.2.2 F/#

2.8

2.2.3 Throw Ratio 100” Diagonal at 3m ( Wide )

2.2.4 Zoom Ratio 1.2 : 1

2.2.5 Focus and flare As following chart:

2.3 Lamp

2.3.1 Maker Ushio

2.3.2 Model NSH 210 MD

2.3.3 Type DC lamp

2.3.4 Lamp Wattage 210 watts

2.3.5 Lamp life 1000 Hours ( Typical )

2.4 Focus Distance 1.5 – 5m

2.5 Keystone Correction

2.5.1 Electronic ± 12°

2.6 Colors 24-bit color

2.7 Native Resolution

4

Page 6

2.7.1 PC Mode 1280 x 720 pixels

1280 x 720 pixels

2.7.2 Video Mode

3.0 Mechanical & Cosmetic

3.1 Dimensions 400L x 347W x 116H

3.2 Weight 16.7 lbs (7581 g)

3.3 Security Slot Kensington compatible slot 150N break away force

3.4 Feet 4 adjustable feet

3.5 Lamp Replace Position Front

4.0 Compatibility Supporting timing: see appendix E

4.1 RGB PC Compatible VGA, SVGA, XGA

4.2 Video Signal Composite, S-Video, Y/CB/CR

4.3 HDTV DTV Y/PB/PR , DTV RGBHV ,DTV DVI-I ( 480P, 1080i, 720P,

576P, 540P)

4.4 Image Inversion Mirror, Upside-down, Mirror Upside-down

4.5 Scaling Scaling from other resolutions to native by O-plus

chip

TM

scaling

4.6 Aspect ratio ANAMORPHIC, 4x3, LETTER BOX, VIRTUAL WIDE.

5.0 Interface Connectors

5.1 RGB Input DVI x 1 (include 5.2.5)

5.2 Video Input

5.2.1 Composite

RCA x 1

5.2.2 S-Video S-Video x 1

5.2.3 Component RCA x 3

5.2.4 Progressive component

BNC x 5

and DTV RGBHV

5.2.5 Digital Video DVI x 1 with HDCP

5.3 RS232C Input

Telephone jack

6.0 Electrical

6.1 RGB

6.1.1 Input

6.1.1.1 Amplitude 0.7 ± 0.1 VPP at 75Ω termination, positive bright

6.1.1.2 Input

75Ω

Impedance

6.1.1.3 Synch TTL compatible

6.1.2 Computer

Compatibility

The unit should be compatible with normal computer formats

ranging from VGA to XGA.

6.1.3 Video Compatibility Don’t use BUBUKAU DVD for test equipment.

5

Page 7

6.2 Control

6.2.1 IR Receivers

6.2.1.1 Location 2receiver, located on the front and rear of this projector

6.2.1.2 Range 8m ( front ) / 5m ( rear ) with 30 degree horizontal Angle and 15

degree vertical angle

7.0 Power Requirements

7.1 Power Supply VAC 100 – 240 Full range switch (50/60Hz), 3 Wire Grounded

7.2 Power Consumption 310W max.

7.3 Power Connector

8.0 Audible Noise Level

IEC

34 dB (

Max) @ 25℃ sea level

9.0 Thermal

9.1 Surface Metal

9.2 Surface Plastic

9.3 Exhaust Air

9.4 Screws, Terminals

60°C

65°C

80°C

70°C

10.0 Contamination

10.1 Prevention Optical system is closed

10.2 Dust in Optical Path No noticeable dust

11.0 Included Accessories

11.1 Cables Power Cord Set (US, UK, Euro) x 1, VGA Cable (1.8m) x 1,

Projector Common Cable x 1

11.2 Printed Matter User’s manual

11.3 Remote Control IR Remote x 1, AAA Batteries x 2

12.0 User Interface

12.0 Backlight

12.1 Operator Panel YES

12.2 Indicators Power Status LED, Lamp Status LED

12.3 Remote Control Front IR receiver , Rear IR receiver

12.4 Onscreen Menu Should be in 3 languages (English, French, Spanish )

12.8 User’s Manual Should be in 3 languages (English, French, Spanish )

13.0 Reliability

13.1 General Failure Def. See Appendix B

13.2 MTBF 20000 hours except for DMD chip , lamp , fans and color wheel.

14.0 Environmental

14.1 Operating 10 – 35°C, 20 – 90%RH, without condensation

14.2 Storage -10 – 70°C, 20 – 90%RH, without condensation

14.3 Altitude

14.4 Shock

NO

0 – 6000 feet above sea level, ambient 30 ℃

6

Page 8

14.4.1 Straight Drop 50mm

14.4.2 Tilt Over Should be able to fall over from tilting without taking any

damage. Must Adhere to Appendix B

14.5 Gas No corrosive, toxic, or combustible gas should be emitted

14.6 Electrostatic Discharge comply to the acceptance criteria as specified in EN

61000-4-2/1995

15.0 Regulatory UL, CE, FCC Class B. Must Adhere to Appendix B Section 10.0

15.1 Safety Requirements UL compliance: UL6500 (2th Version)

CSA compliance: E60065-00

TUV compliance: IEC60065:2001

CCC: GB8898; GB13837; GB17625.1: 1998

15.1 EMI Requirements 1. CE Mark compliance: EMC: 89/336/EEC

EN 55013:1990+A12 :1994+A13 :1996+A14 :1999

EN 61000-3-2:1995+A1 :1998+A2 :1998+A14 :2000

EN 61000-3-3:1995+A1 :2001

EN 55020:1994+A1 :1996+A12/A13/A14 :1999

IEC 61000-4-2/2001

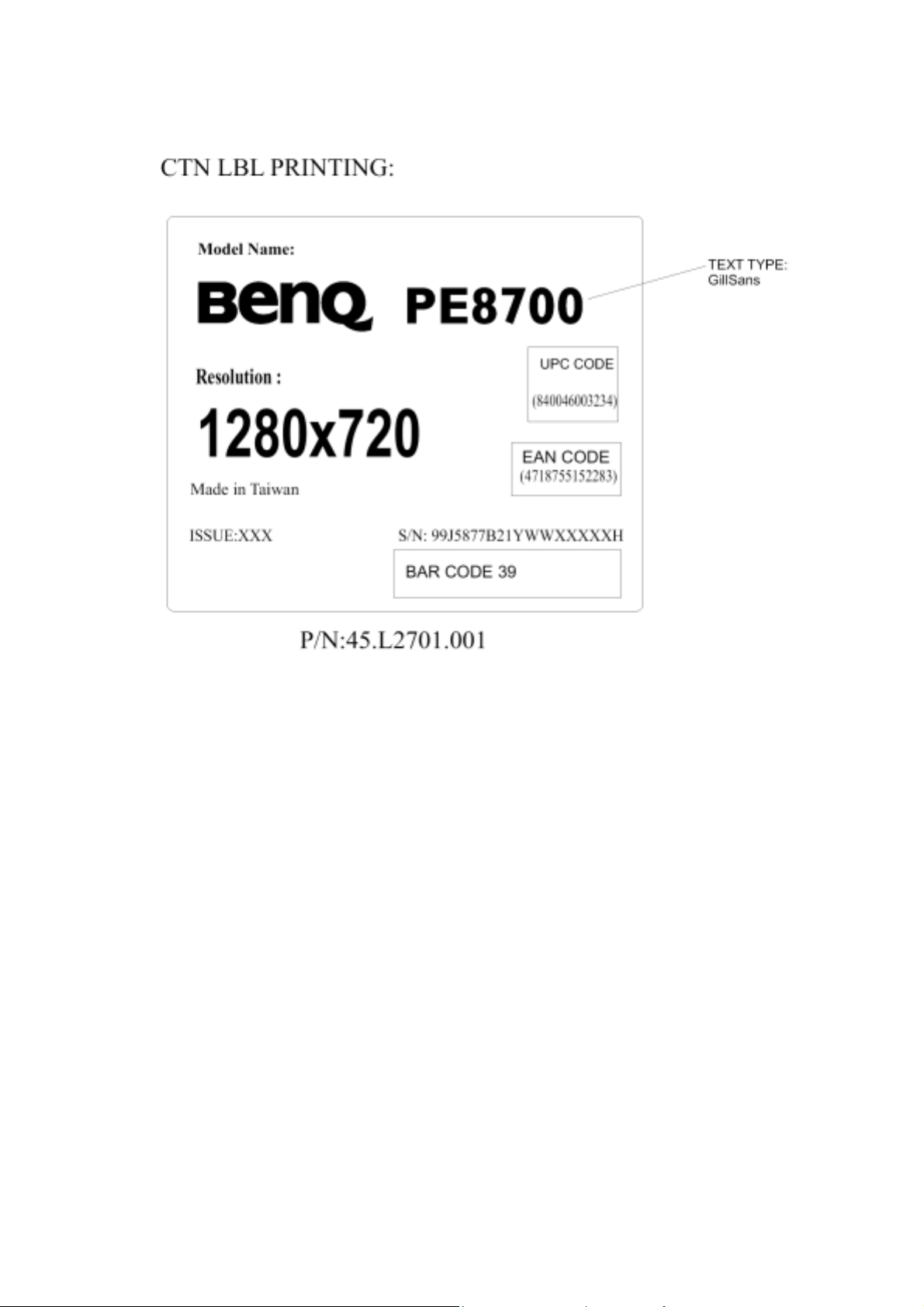

16.0 Packaging

16.1 Packaging Form Must adhere to attached file

16.1.1 Dimensions 537 x 520 x 260 mm

16.1.2 Weight TBD

16.1.3 Palletization 1140 x 1050 x 120 mm

16.1.4 Carton Labeling Must adhere to attached file

16.2 Vibration Must adhere to Appendix B

16.3 Drop Test Must adhere to Appendix B

IEC 61000-4-3/2001

IEC 61000-4-4/1995+A1:2000+A2:2001

2. FCC

FCC Part 15B

3. C-Tick

ASIN2S 1053:1996

4. VCCI

VCCI/2002(15

th

Edition)

7

Page 9

Appendix A Optical Measurement

This part of the Optical Test Instruction describes those measurements to be executed

during the production of the optical engines.

Content:

A1 BRIGHTNESS

A2 BRIGHTNESS UNIFORMITY

A3 BRIGHTNESS DIFFERENCE

A4 ANSI CONTRAST

A5 PEAK CONTRAST

A6 LIGHT LEAKAGE

A7 IMAGE DISTORTION

A8 THROW RATIO

A9 ZOOM RATIO

A10 FOCUS RANGE

A11 COLOR

A12 COLOR UNIFORMITY

A13 OPTICAL KEYSTONE (FIXED)

General requirements

1. The unit shall be allowed to stabilize without further adjustment for a

minimum of 10 minutes, at nominal ambient room temperature of 25°C,

before making measurements.

2. Measurements shall take place in a light proof room, where the only source of

illumination is the projector. Less than 1% of the light on the screen shall be

from any source other than the projector.

3. All measurements shall be made on flat screens that do not provide any

advantage to the performance of the unit

4. All measurements shall be made at standard color temperature setting, 100%

white image (per ANSI IT7.228-1997), except where noted

8

Page 10

Practical consideration

+++++++

1. When measuring contrast manually, operators should not wear white

clothing since light reflected from white clothing can influence the

measurement.

2. Unless otherwise specified the projection lens is set in the widest zoom

position since zoom function can influence the measurement.

3. Measurement should be performed with Minolta Chromameter, Model

CL-100, or equivalent.

A1. BRIGHTNESS

Unit: Lumen

Brightness: Default

Contrast: Default

W: width of projected image; H: height of projected image

A (Area) = W * H (in meters)

987654321

ANSI Lumens = )()(

+

LLLLLLLLL

2

mAlux

∗

9

1

W

3

1

W

6

1

H

6

1

H

3

9

Page 11

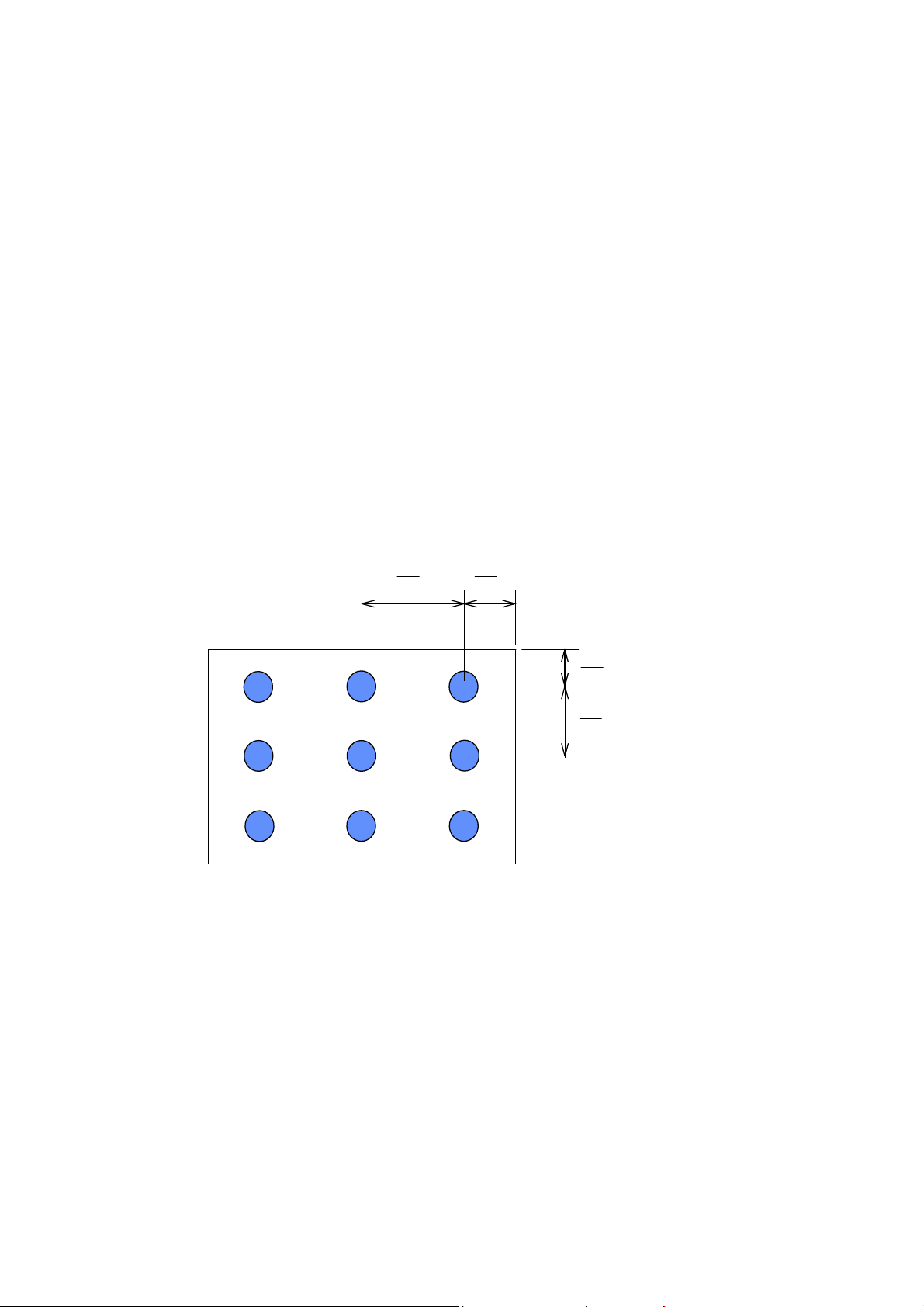

A2. BRIGHTNESS UNIFORMITY

Unit: %

Brightness: Default

Contrast: Default

Uniformity =

EEEEMIN

1/20w

)13,12,11,10(

987654321

LLLLLLLLL

++++++++

9

E10

L5

E12

E11

E13

A3. BRIGHTNESS DIFFERENCE

Unit: %

Brightness: Default

Contrast: Default

Brightness Difference=

−

1/20h

))13,12,11,10()13,12,11,10((

EEEEMINEEEEMAX

9

987654321

LLLLLLLLL

++++++++

A4. ANSI CONTRAST

Unit: Contrast : 1

Brightness: Default

Contrast: Default

Contrast Ratio shall be determined from illuminance values obtained from a

black-and-white ”chessboard” pattern consisting of 16 equal rectangles. The

white rectangles shall be at 100% gray and the black rectangles at 0% gray.

Illuminance measurements shall be made at the center of each of the rectangles.

Contrast Ratio = Average lux value of the white rectangles/Average lux value

of the black rectangles

10

Page 12

−

+

A5. PEAK CONTRAST

Unit: Contrast : 1

Brightness: Default

Contrast: Default

Contrast Ratio = Lux value at the center of a solid white screen/the lux value

of a solid black screen

A6. LIGHT LEAKAGE

Unit: Lux

Brightness: Default

Contrast: Default

Leakage = The maximum light leakage of a solid black screen outside the

projected image

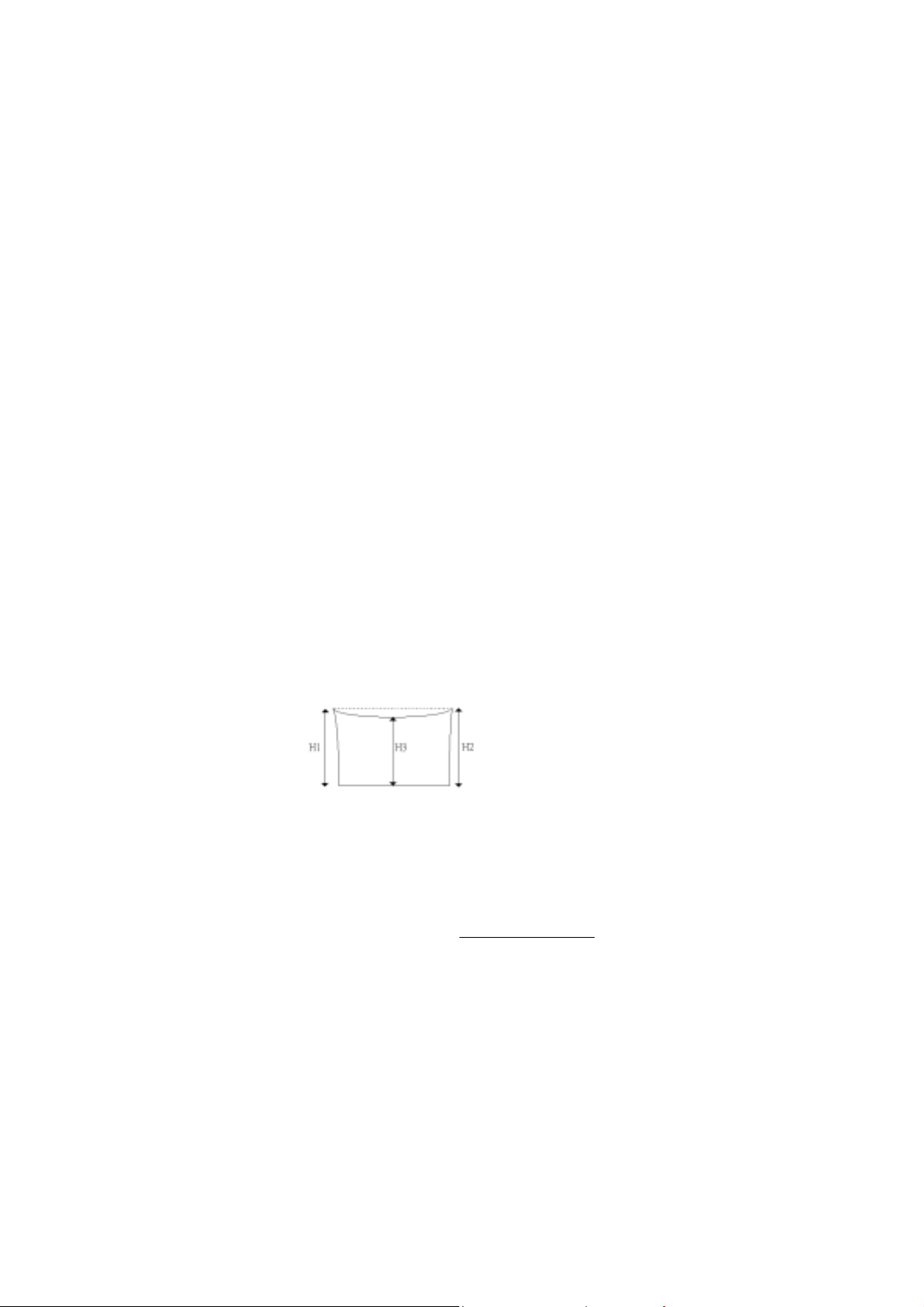

A7. IMAGE DISTORTION

Unit: %

Brightness: Default

Contrast: Default

Measurement procedure:

Measure the dimensions H1, H2 and H3, with H3 at the half image width, as

shown above for both zoom settings. For each the distortion is defined as:

3*221

distTV

=−

H

HHH

%100*

3*2

All should be within the absolute specification tolerance.

A8. THROW RATIO

Unit: Ratio : 1

Brightness: Default

Contrast: Default

Throw ratio = projection distance / the width of the projected image

11

Page 13

−

A9. ZOOM RATIO

Unit: Ratio : 1

Brightness: Default

Contrast: Default

Zoom ratio = maximum / minimum image diagonal size at a fixed projection

distance.

A10. FOCUS RANGE

Unit: m (Max~Min)

Brightness: Default

Contrast: Default

The minimum/maximum focus distance is the minimum/maximum projection

distance (front side projection lens and the image lane), expressed in meter,

at which the image is still at its best for focus.

A11. COLOR

Unit: x, y

Measurements at the center (except in the case of color uniformity

measurements) of a screen which is entirely of the color being measured and

at default brightness and contrast

settings.

A12. COLOR UNIFORMITY

Unit: x, y

Difference between any two points out of Lx and Ex should not exceed the

specification for the given color.

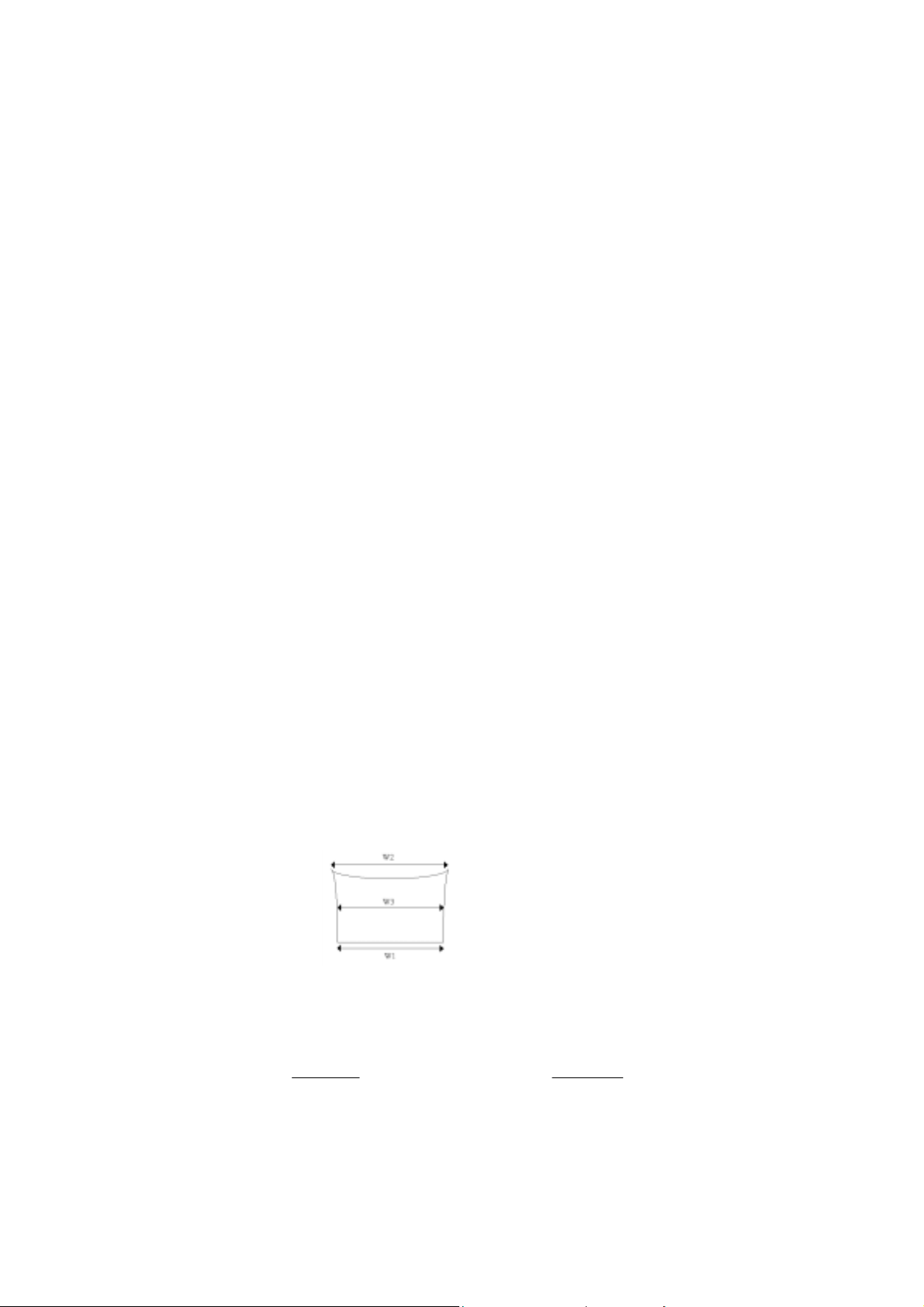

A13. OPTICAL KEYSTONE (FIXED)

Unit: %

Brightness: Default

Contrast: Default

Measure the dimensions W1, W2 and W3 at the half image height, as shown

above. The distortion is defined as:

WW

distTV

−

=− & %100*

%100*

distTV

=−

331W

WW

332W

12

Page 14

Appendix B Design Verification Test Procedure

1.Purpose

This standard establishes the environmental specification for projector related

products, which defines the level of product performance and reliability in the field. It is not

necessary the intent of these specification to simulate a typical user environment, but rather

to provide for a level of product robustness that when applied over a wide range of

manufacturing variability and environmental usage conditions.

2.Test Summary

Dynamic Testing Specification

Package Drop 76cm, 1 drop per orientation, all 6 primary surfaces, plus a selected

corners, and three selected edges, total of 10 drops

Package Vibration

Shock, non-operating 50g, 20ms half-sine, all primary axis, 1 shock per orientation, total of 3

Security Lock 150N break away force

Fragility

Atmospherics

Temperature/Humidity,

operating

Random , 0.01g2/Hz, 5~100Hz, all primary axis, 20 min per orientation,

total of 60min

Sine, 0.5g, 5~200Hz, 1 octave/min, 15 min dwell on each resonant

frequency, all primary axis, one sweep (30min minimum) per orientation,

total of 90+min

shocks

Shock, 50g, 20ms half-sine, all primary axis, 1 shock per orientation, total

of 3 shocks

Accelerate Life Test (operating), 65

Thermal shock(bare board), -65~125

Input Voltage, 90~264V

Input RGB signal, 0.7V±0.1

10~35oC/10~80RH, 48hr

o

C, 72hr

o

C, 48hr

Temperature/Humidity,

non-operating

Altitude, operation

Safety/EMC

UL/cUL

TUV Rheinland

Fcc/CE/C-Tick

-10~70oC/10~80RH, 48hr

0~6000ft@30oC, 4hr

13

Page 15

3.Definition

3.1 Failure Criteria:

The product is expected to perform to its full potential without loss of function,

performance, critical parametric changes, and other undesirable anomalies, over the

applied boundaries of this specification. The following product failure are not allowed within

the boundaries defined in this specification:

1.Failure including permanent damage, critical parametic changes (optical

performance defined in Appendix A), and latent defects.

2.Failure requiring operator intervention.

3.Failure violating external laws, regulatory agency standards, and government

directives.

4.Failure resulting in a safety, potential safety, issue.

3.2 EUT: Equipment under Test

3.3 Q: Peak Acceleration Response divided by acceleration input peak

4.Test Order

Atmospherics, Dynamic, and Safety test sets require separate units and can be

processed in parallel. EUT testing shall be performed serially within each set.

Set 1 (3 units) Set 2 (3 units) Set 3

Dynamics: Atmospherics: Safety/EMC:

Package Drop Temperature/Humidity, Operating EFT

Package Vibration Temperature/Humidity,

ESD

Non-operating

Shock Altitude, Operating EMI-Radiated

Bench Drop Aging EMI-Conducted

EMI-Susceptibility

14

Page 16

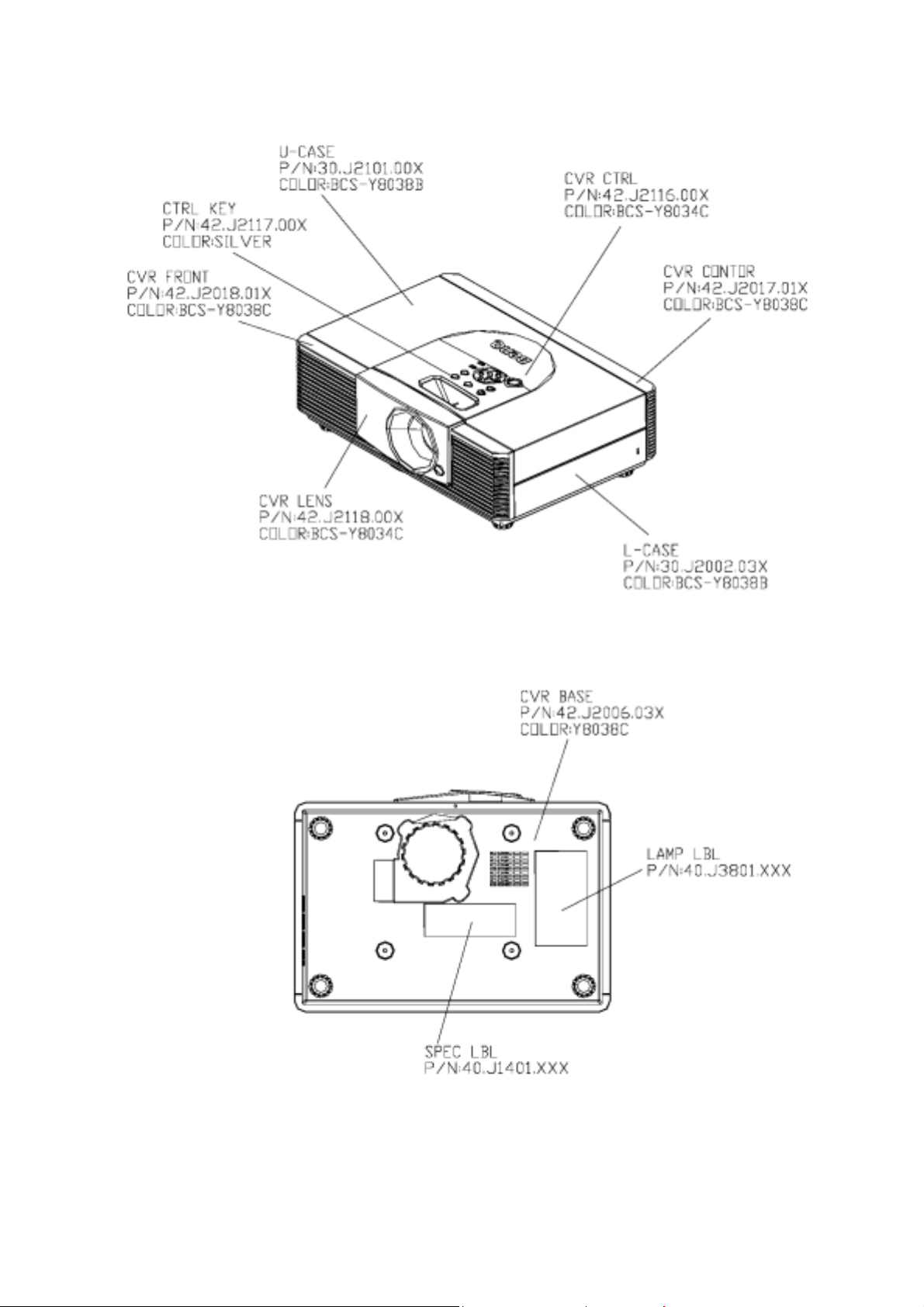

Appendix C Drawings and Attachments

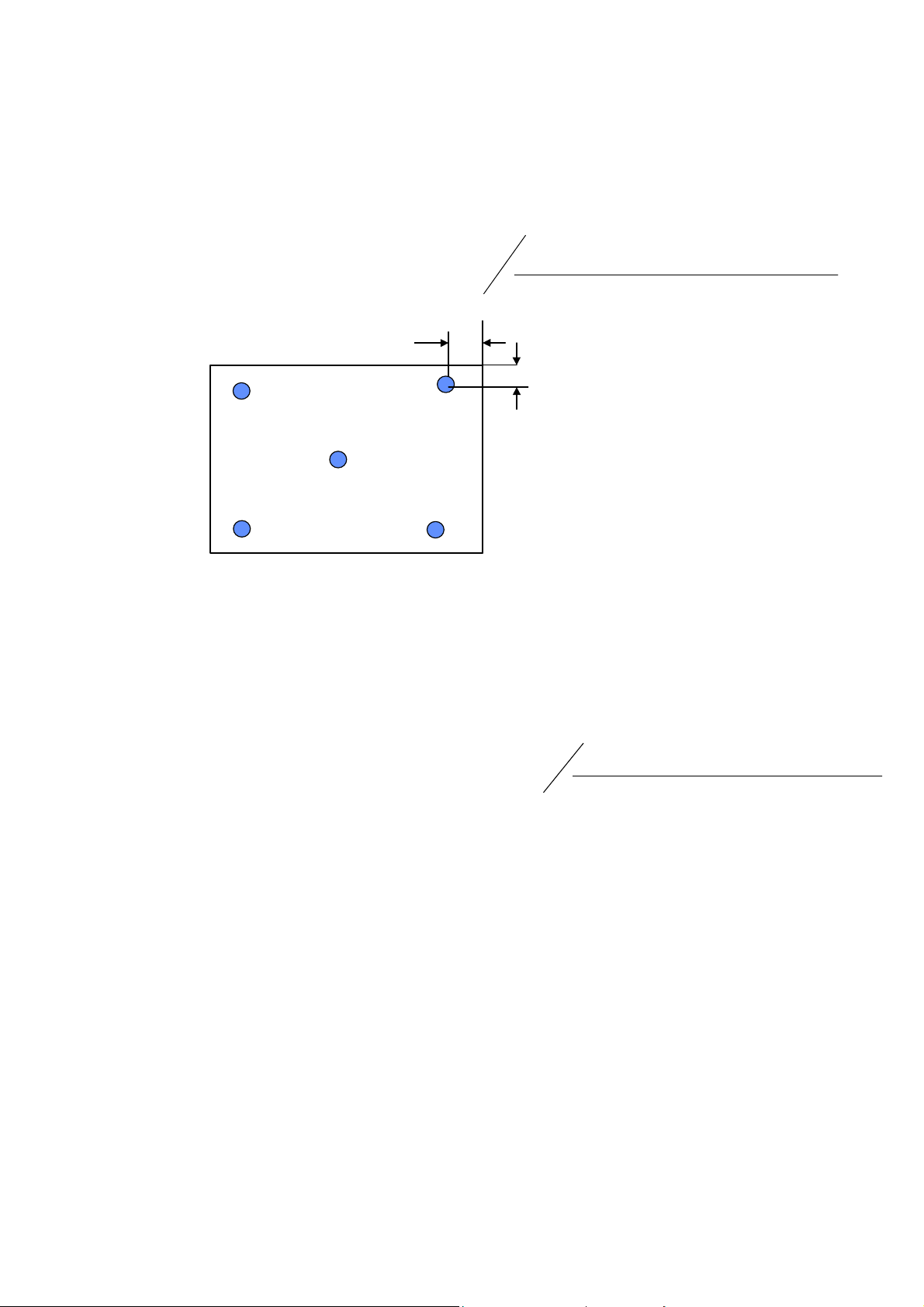

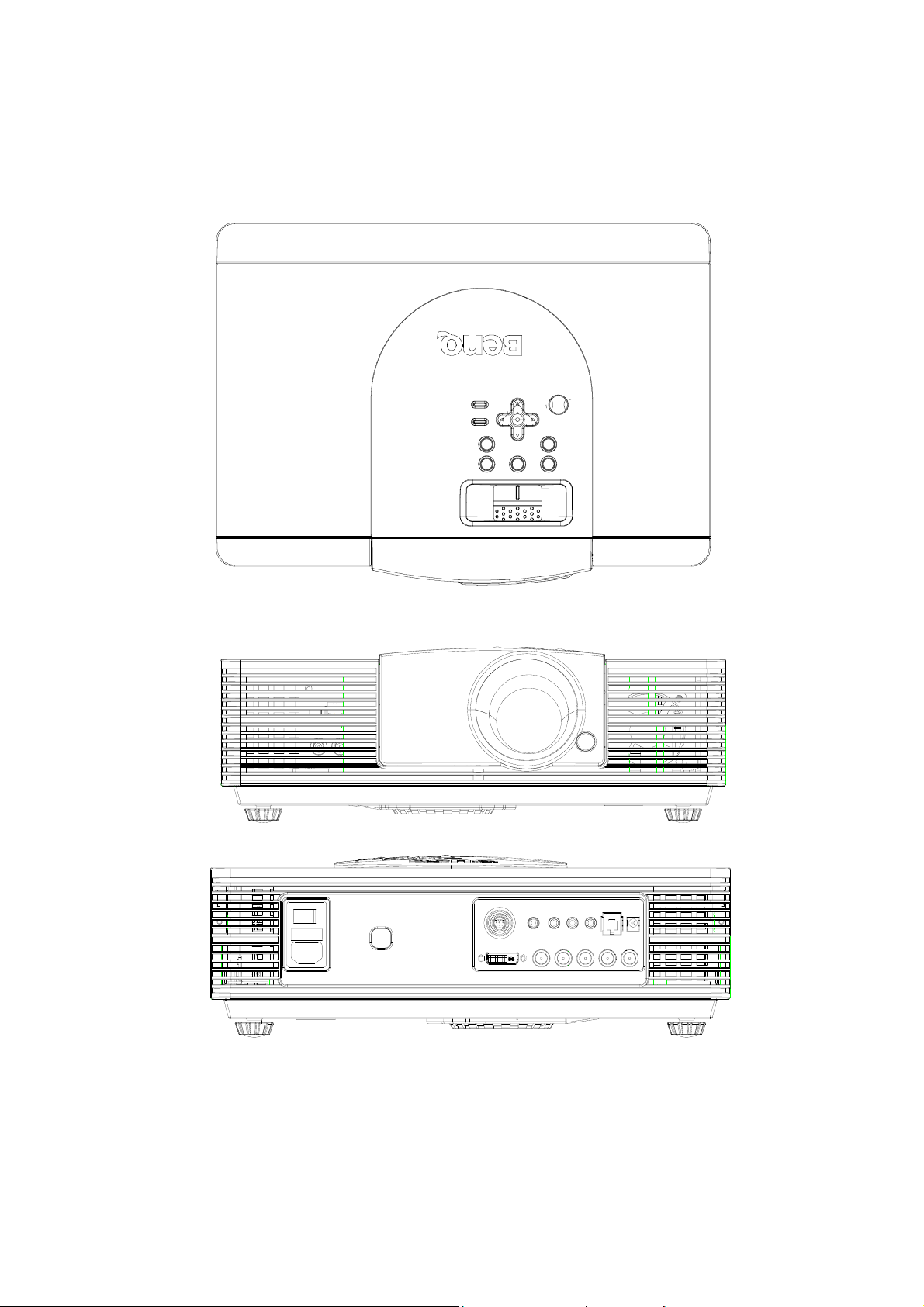

Drawing 1: Top view of BENQ PE8700 video projector

15

Page 17

16

Page 18

Appendix D HD2 Front Projection Image Quality Specification

1. SCOPE

This document specifies the image quality requirements applicable to the HD2 Component

Set for Front Projection image display. The HD2 Component Set provides digital imaging

functionality based on Digital Micromirror Device (DMD) technology.

2. DEFINITIONS

2.1 Blemish

A blemish is an obstruction (dark blemish), reflection, or refraction of light (light blemish)

that is visible, but out of focus in the projected image under specified conditions of

inspection (see Table 1). It is caused by a particle, scratch, or other artifact located in the

image illumination path.

2.2 Dark pixel

A dark pixel is a single pixel or mirror that is non-functional (stuck) in the OFF position.

2.3 Bright pixel

A bright pixel is a single pixel or mirror that is non-functional (stuck) in the ON position.

2.4 Unstable pixel

An unstable pixel is a single pixel or mirror that does not operate in sequence with

parameters loaded into memory. The unstable pixel appears to be flickering

asynchronously with the image.

2.5 Adjacent pixels

Adjacent pixels are defined as sharing a common border or common point.

2.6 Border defects

Border defects are bright blemishes (see 2.1) or bright pixel defects (see 2.3) in the

non-active area that may be visible in front projection mode.

2.7 Blue test screen

This screen is used to test for major dark blemishes and dark pixels. All areas of the screen

are colored at a specific blue level, based on MS Paint 0-255 RGB scale:

Major Dark Blemish

Blue Value 90

Red Value 0

Green Value 0

17

Page 19

2.8 Gray 6 test screen

This screen is used to test light blemishes and bright pixels. All areas of the screen are

colored at a specific gray level, based on MS Paint 0-255 RGB scale:

Major Light Blemish

Blue Value 6

Red Value 6

Green Value 6

2.9 Gray 10 test screen

This screen is used to test light blemishes and bright pixels. All areas of the screen are

colored at a specific gray level, based on MS Paint 0-255 RGB scale:

Major Light Blemish

Blue Value 10

Red Value 10

Green Value 10

2.10 White test screen

This screen is used to test light border blemishes and bright pixels. All areas of the active

area are colored at a specific gray level, based on MS Paint 0-255 RGB scale:

Major Dark Blemish

Blue Value 255

Red Value 255

Green Value 255

2.11 black test screen

This screen is used to test light border blemishes and bright pixels. All areas of the active

area are colored at a specific gray level, based on MS Paint 0-255 RGB scale:

Major Dark Blemish

Blue Value 0

Red Value 0

Green Value 0

18

Page 20

2.12 Red Ramp test screen

This screen is used to test light border blemishes and bright pixels. All areas of the active

area are colored at a specific gray level, based on MS Paint 0-255 RGB scale:

Major Dark Blemish

Blue Value 0

Red Value Start 0,end 255

Green Value 0

3. ACCEPTANCE REQUIREMENTS

3.1 Test Conditions (as tested in OEM projector)

· Projector degamma correction shall be linear. Using HD Control “Curtain” Mode is

equivalent.

· Image noise reduction algorithms “Blue Noise STM” and “Boundary Dispersion” shall be

set to “off”.

· Projector shall be used in front projection mode using a customer-specified screen, and

OEM optical system.

· The diagonal size of the projected image shall be 52 inches (132cm).

· The projected image shall be inspected from a 60 inches (1.52 meter) minimum viewing

distance.

· Projector will be properly focused on the DMD array as shown on the screen.

· Testing time is limited to 20seconds per screen.

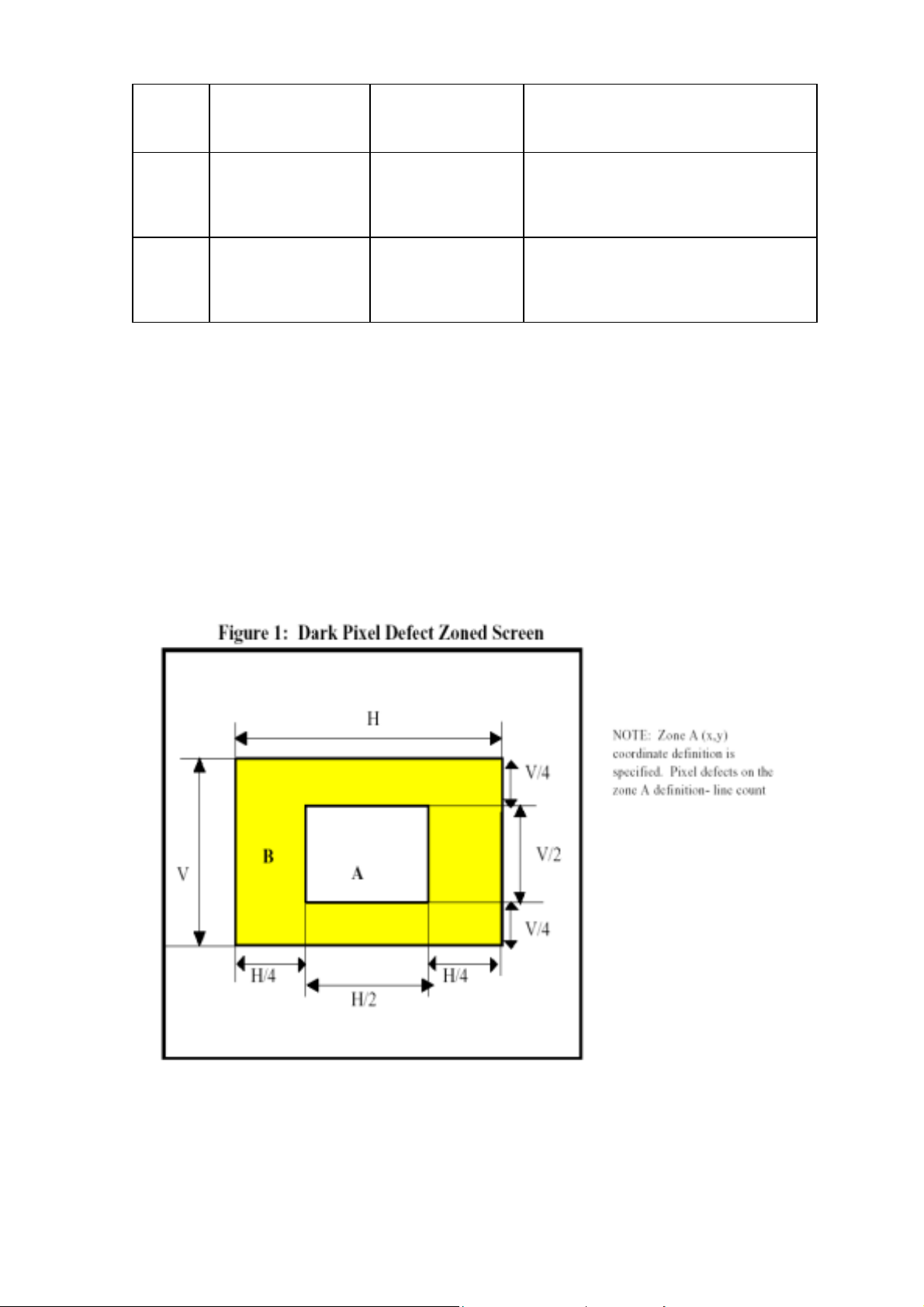

· Refer to Table 1 for acceptance criteria, in specified order:

TEST

ORDER

1 Major Dark Blemish Blue 90 No dark blemishes visible on Blue 90

2 Dark Pixel Blue 90

3 Border Defects Gray 10 No border defects visible

4 Major Light Blemish Gray 6 No light blemishes visible on Gray 6

TEST SCREEN ACCEPTANCE CRITERIA

0 dark pixels allowed in Zone A

Zoned Screen (see

below figure 1)

<=2 dark pixels allowed in Zone B

No adjacent dark pixels

19

Page 21

5 Light Pixel Gray 6 No light pixels visible on Gray 6

6 Minor Blemishes White or Black

7 Unstable Pixel Red Ramp

Screen(or any

other

TABLE 1. Image Quality Specification

Total of Dark and Light Blemishes ≦

4

(See Test 4 , 5)

No unstable pixels

Notes:

1. The acceptance basis for all cosmetic DMD defects will be the projected image tests

referenced in Table 1.

2. Projected blemish numbers include the shadow of the artifact in addititon to the artifact

itself.(Count=4)

4. The projected image shall not contain any blemish more than 15 cm long, measured on

a 1.32m diagonal screen.

20

Page 22

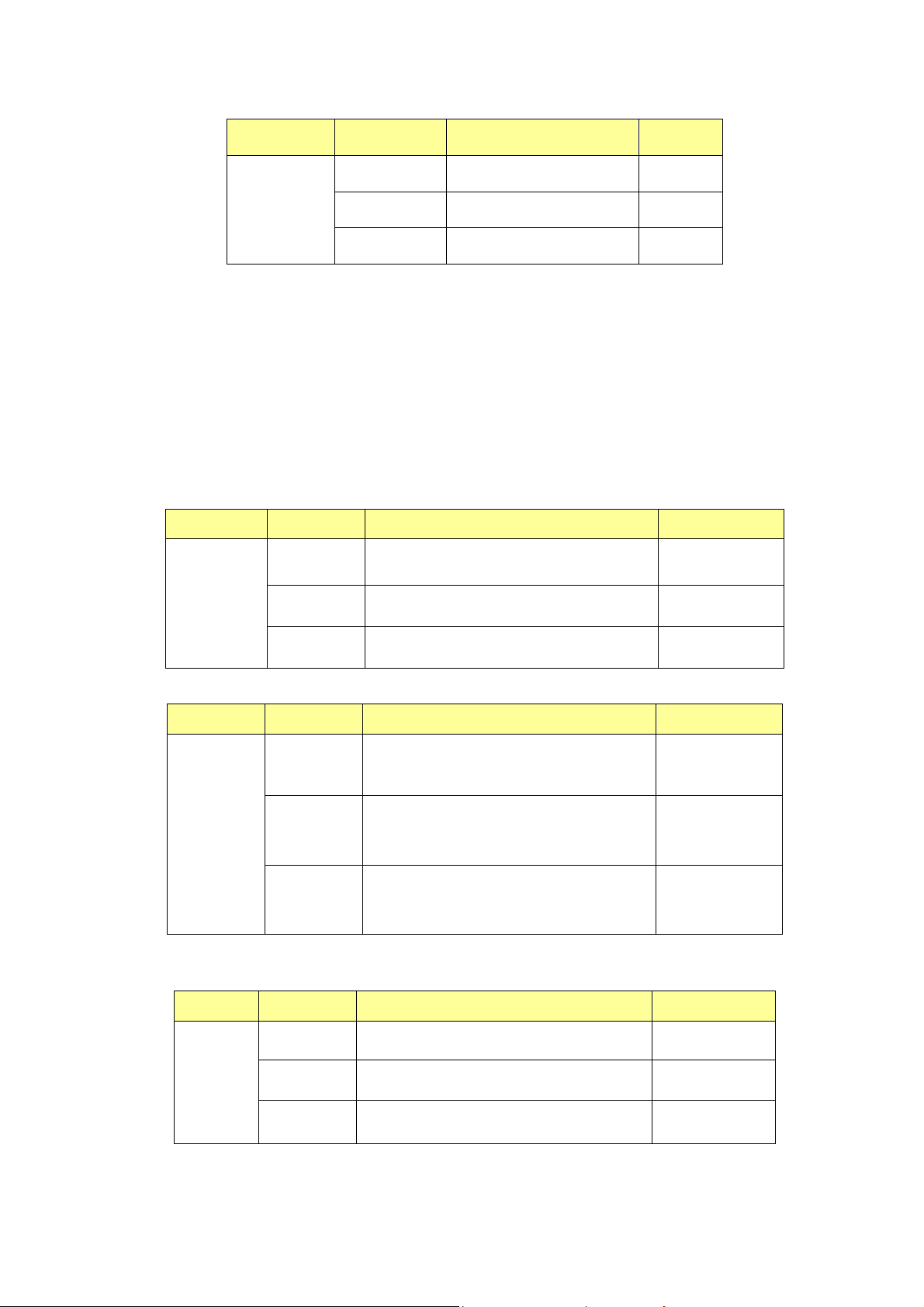

Appendix E Supporting Timings

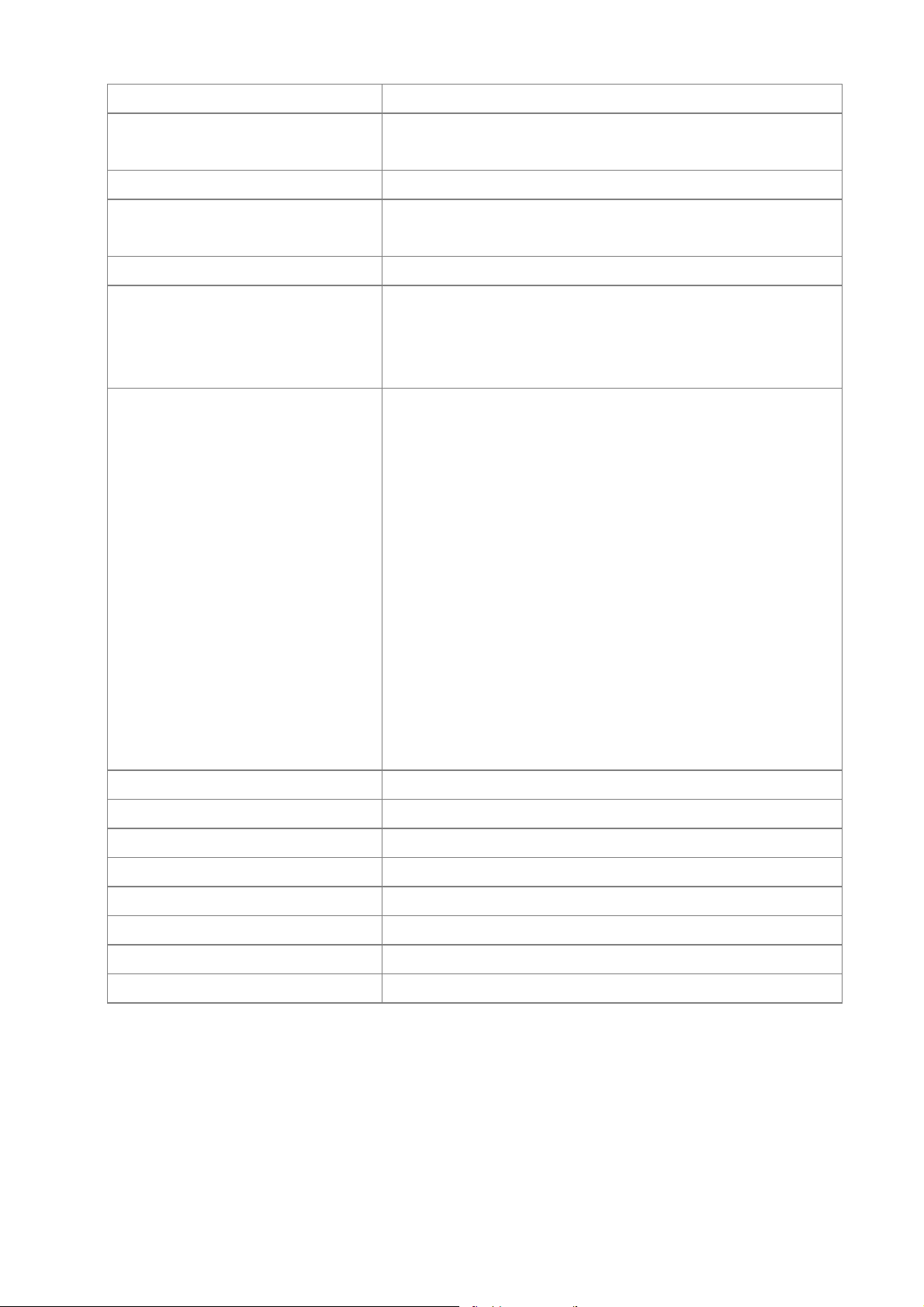

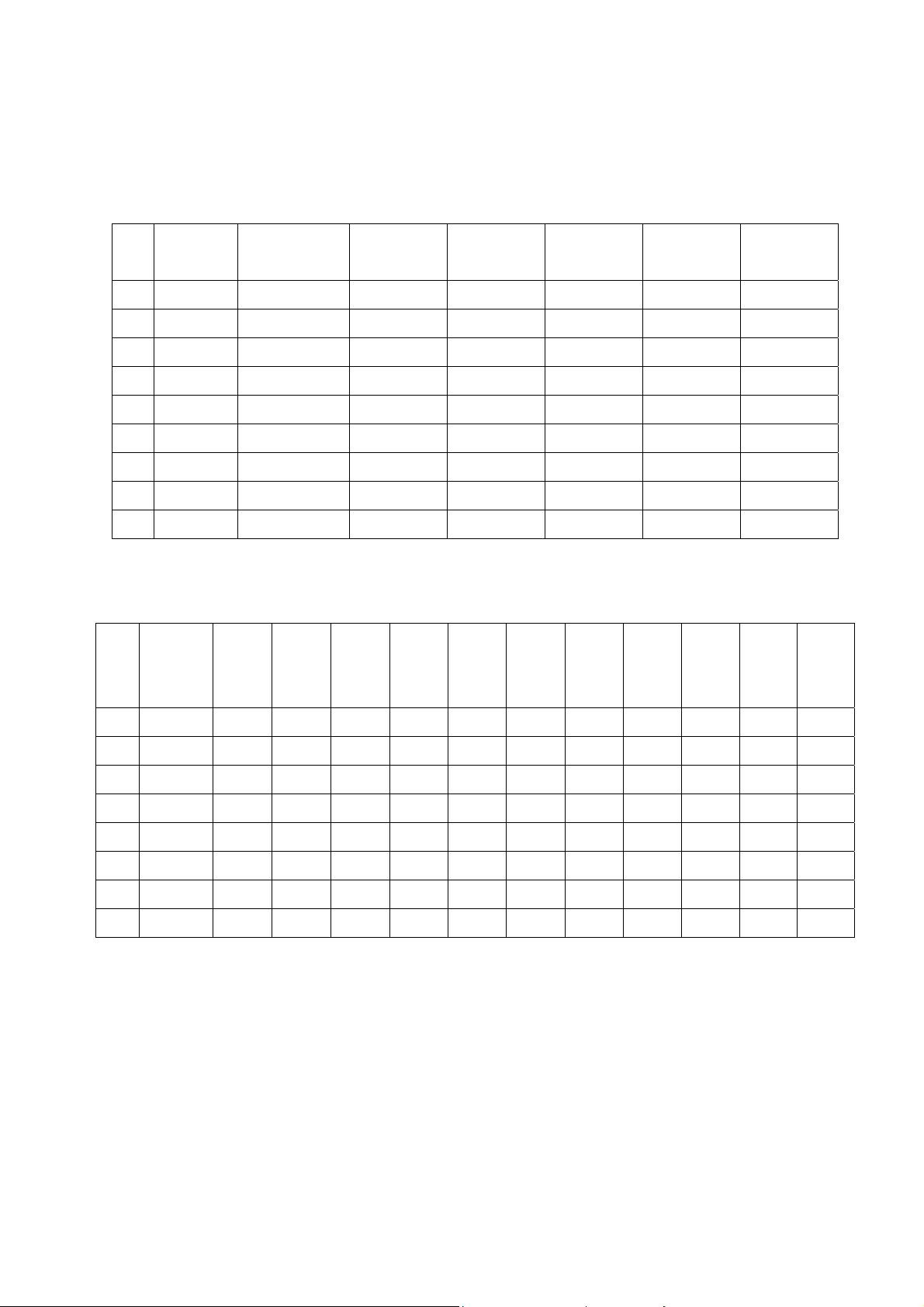

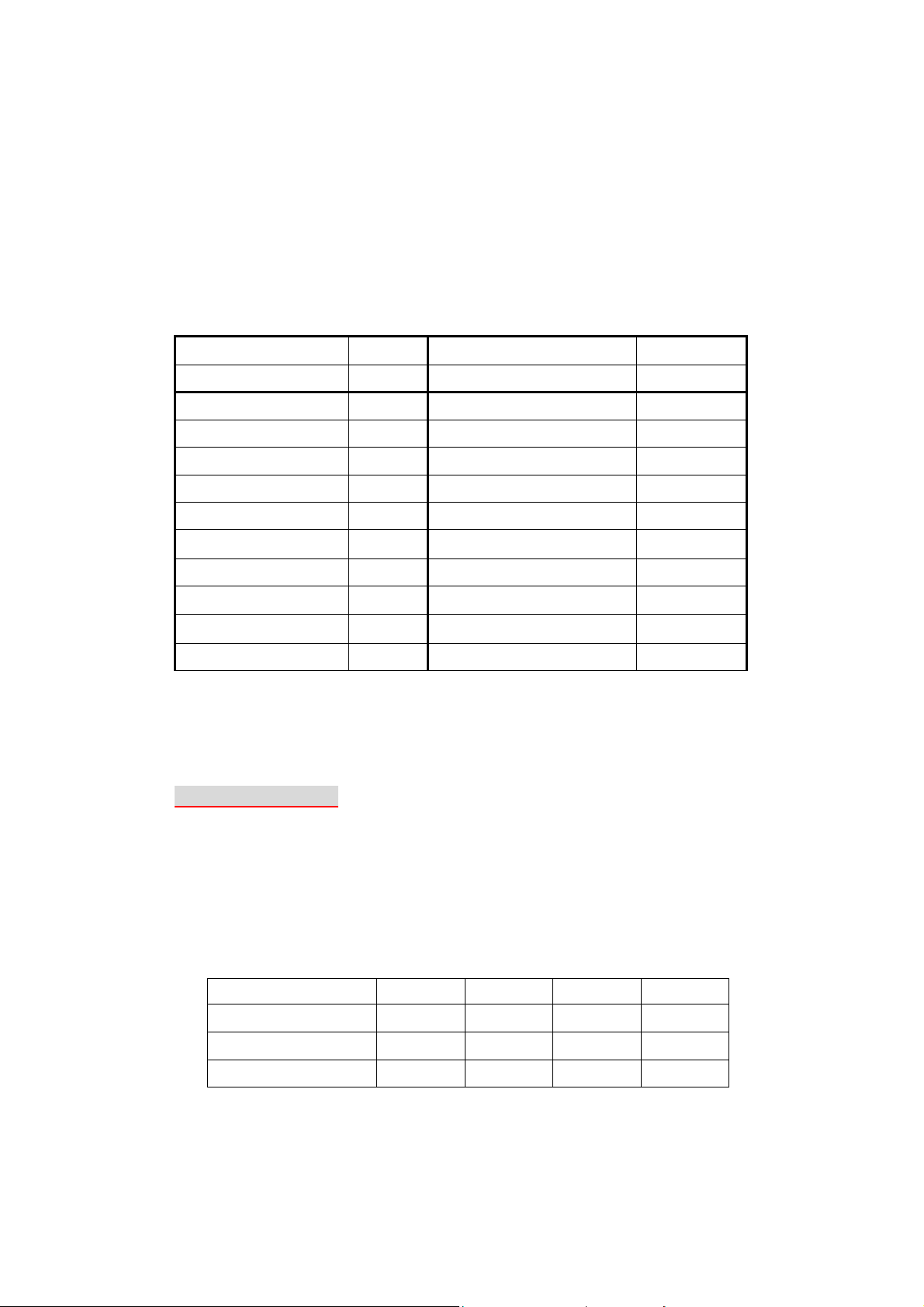

Table 1: Support Timings by DVI-I Input (Analog or Digital PC signals)

Resolution Vert. Freq

(Hz)

1 VGA 640 x 400 70.089 31.470 25.167 D/A -/+

2 VGA 640 x 480 59.590 31.470 25.167 D/A -/-

3 VGA 640 x 480 85.008 43.269 36.0 D/A -/-

4 SVGA 800 x 600 60.317 37.879 40.0 D/A +/+

5 SVGA 800 x 600 75.000 46.875 49.5 D/A +/+

6 SVGA 800 x 600 85.061 53.674 56.25 D/A +/+

7 XGA 1024 x 768 60.004 48.363 65.0 D/A -/-

8 XGA 1024 x 768 75.029 60.023 78.75 D/A +/+

9 XGA 1024 x 768 84.997 68.677 94.5 D/A +/+

Table 2: Support Timing by DVI-I Input

Index Format

name

Line

Rate

Pixel

Rate

Frame

Rate

Line

active

Hori. Freq

(kHz)

Line

total

Frame

active

Pixel freq

(MHz)

Frame

total

Digital (D)/

Analog (A)

H back

porch

H sync

width

Polarity

V back

porch

V sync

width

(kHz)

1 480p59 31.469 27 59.94 720 858 480 525 59 63 30 6

2 576p50 31.25 27 50 720 864 576 625 68 64 39 5

3 720p50 37.5 74.25 50 1280 1980 720 750 260 40 20 5

4 720p59 44.955 74.176 59.94 1280 1650 720 750 260 40 20 5

5 720p60 45 74.25 60 1280 1650 720 750 260 40 20 5

6 1080i25 28.125 74.25 25 1920 2640 1080 1125 148 44 15 5

7 1080i29 33.716 74.176 29.97 1920 2200 1080 1125 192 44 15 5

8 1080i30 33.75 74.25 30 1920 2200 1080 1125 192 44 15 5

(MHz)

(HZ)

(pixel)

(pixel)

(line)

(line)

(pixel)

(pixel)

(line)

(line)

21

Page 23

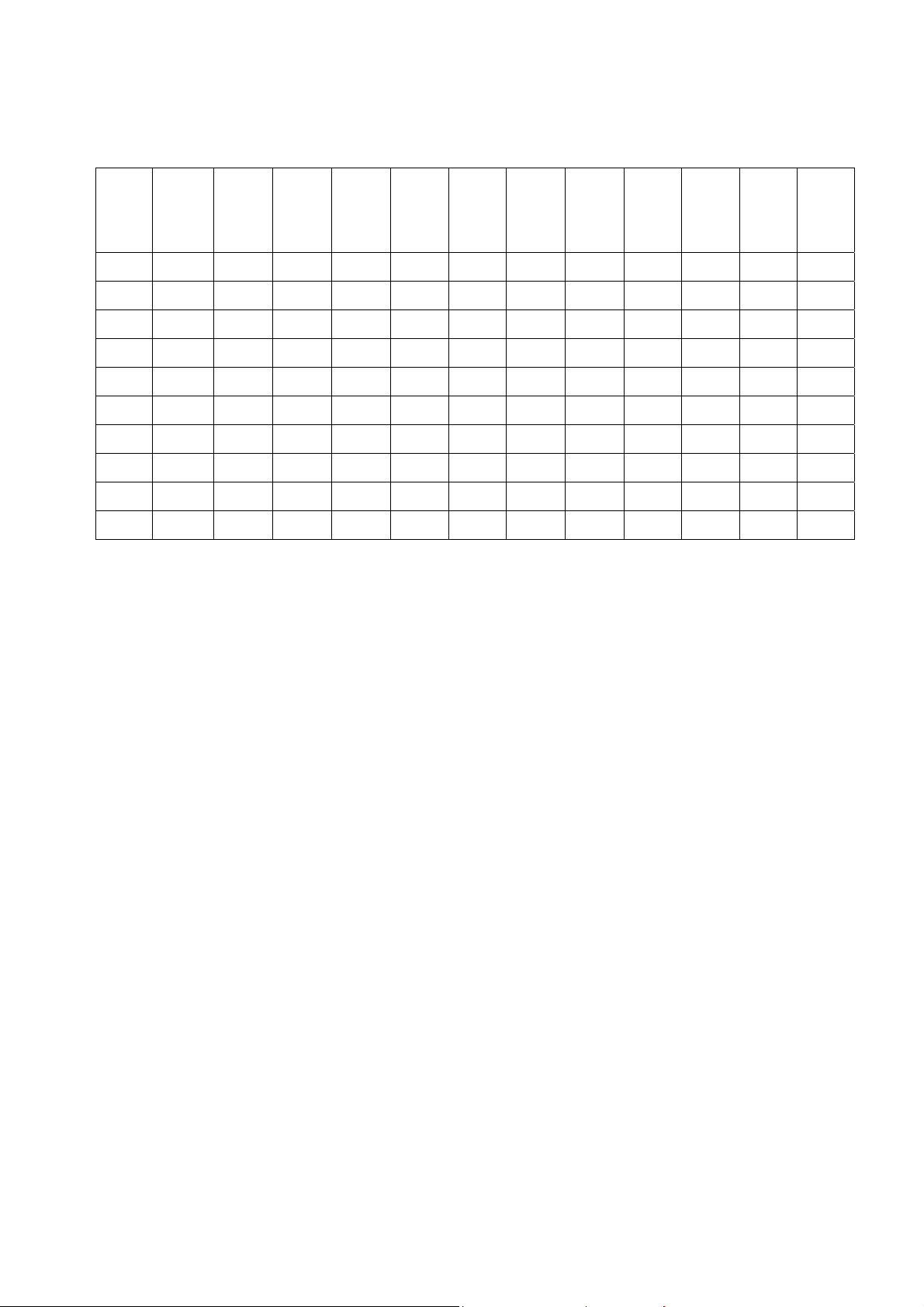

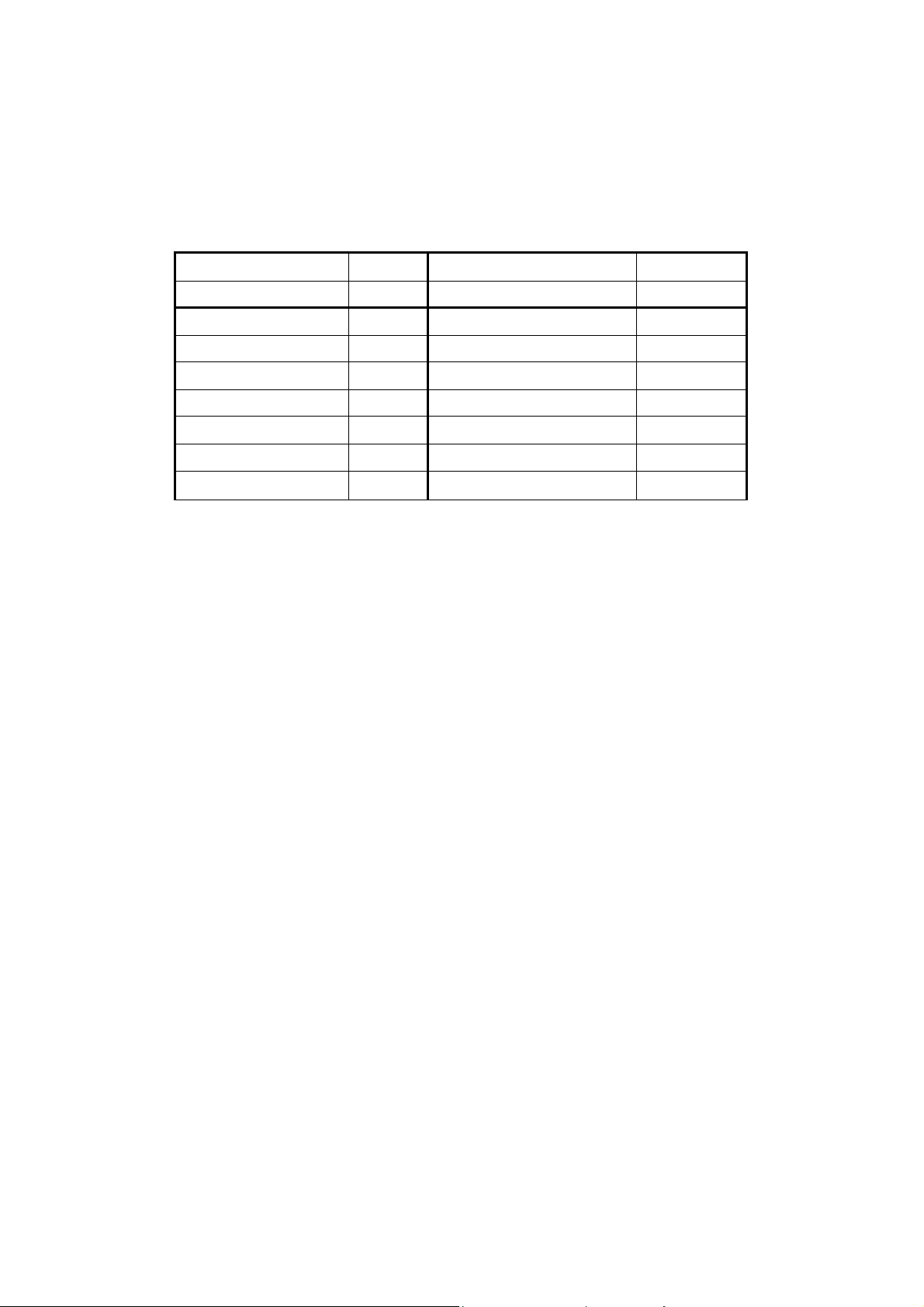

Table 3: EDTV and HDTV Timing supported by component (YPBPR) and RGBHV Input

Index Format

name

1 480i 15.734 13.5 59.94 720 858 480 525 59 63 30 6

2 576i 15.625 13.5 50 720 864 576 625 68 64 39 5

3 480p 31.469 27 59.94 720 858 480 525 59 63 30 6

4 576p 31.25 27 50 720 864 576 625 68 64 39 5

5 720p50 37.5 74.25 50 1280 1980 720 750 260 40 20 5

6 720p59 44.955 74.176 59.94 1280 1650 720 750 260 40 20 5

7 720p60 45 74.25 60 1280 1650 720 750 260 40 20 5

8 1080i25 28.125 74.25 25 1920 2640 1080 1125 148 44 15 5

9 1080i29 33.716 74.176 29.97 1920 2200 1080 1125 192 44 15 5

10 1080i30 33.75 74.25 30 1920 2200 1080 1125 192 44 15 5

Line

Rate

(kHz)

Pixel

Rate

(MHz)

Frame

Rate

(HZ)

Line

active

(pixel)

Line

total

(pixel)

Frame

active

(line)

Frame

total

(line)

H back

porch

(pixel)

H sync

width

(pixel)

V back

porch

(line)

V sync

width

(line)

22

Page 24

Chapter 4 Spare Parts List

Projector PE8700 99.J5877.B21

NO Parts NO Description

1 55.J2003.001 IR BD HT480W MI

2 55.J5801.011 PCBA MAIN/BD FOR BENQ

3 55.J5824.001 PCBA DMD BOTTOM/BD HT720G

4 55.J1313.001 PCB 1L SENSOR-B BD SL700 X MI

5 65.J2004.001 COLOR WHEEL SIX SEGMENT UNAXI

6 55.J5802.001 PCBA DMD/BD HT720G

7 65.J5801.001 ASSY LENS ZOOM HT720G PROT

8 71.00HD2.A00 IC MUSTANG DMD PREMIUM CLGA

9 65.J3403.001 ASSY BALLAST210W/USHIO DX660

10 55.J2006.010 PCBA KEYPAD/BD HT720G BENQ

11 55.J5817.001 PCBA TRANSLATION/BD HT720G

12 60.J2020.021 ASSY CVR BASE HT720W/BENQ

13 60.J2023.022 ASSY L/C HT720W/BENQ

14 60.J2037.011 ASSY CVR FRONT HT720W/BENQ

15 60.J2038.011 ASSY CVR BACK CONTOR HT720W

16 60.J2112.001 ASSY CVR LENS HT720W BENQ

17 55.J2013.001 PCBA THERMAL SENSOR/B HT480W

18 55.J2021.001 PCB FPC/BD FOR HT480W

19 55.J5810.011 PCBA CONNECTOR/BD FOR BENQ

20 55.J2005.001 PCBA POWER BD HT480W MI

21 55.J5811.001 PCBA PFC/BD HT720G

22 44.J2003.021 CTN AB 455X500X228 HT720G/BEN

23 47.J2008.001 CUSHION FRONT EPE HT480W

24 47.J5804.001 CUSHION REAR EPE HT720G BENQ

25 50.J2103.501 CABLE RGA/DVI-A (WHDDC) 1.8M

26 50.L2508.501 SIGNAL/C DUAL DVI-D/DVI-D 200

27 60.J2028.R01 ASSY AV CABLE RUNCO CL-500

28 98.J2032.B01 HT480W BENQ REMOTE CONTROL

29 60.J2104.CG1 ASSY CSD LAMP MODULE PE8700

23

Page 25

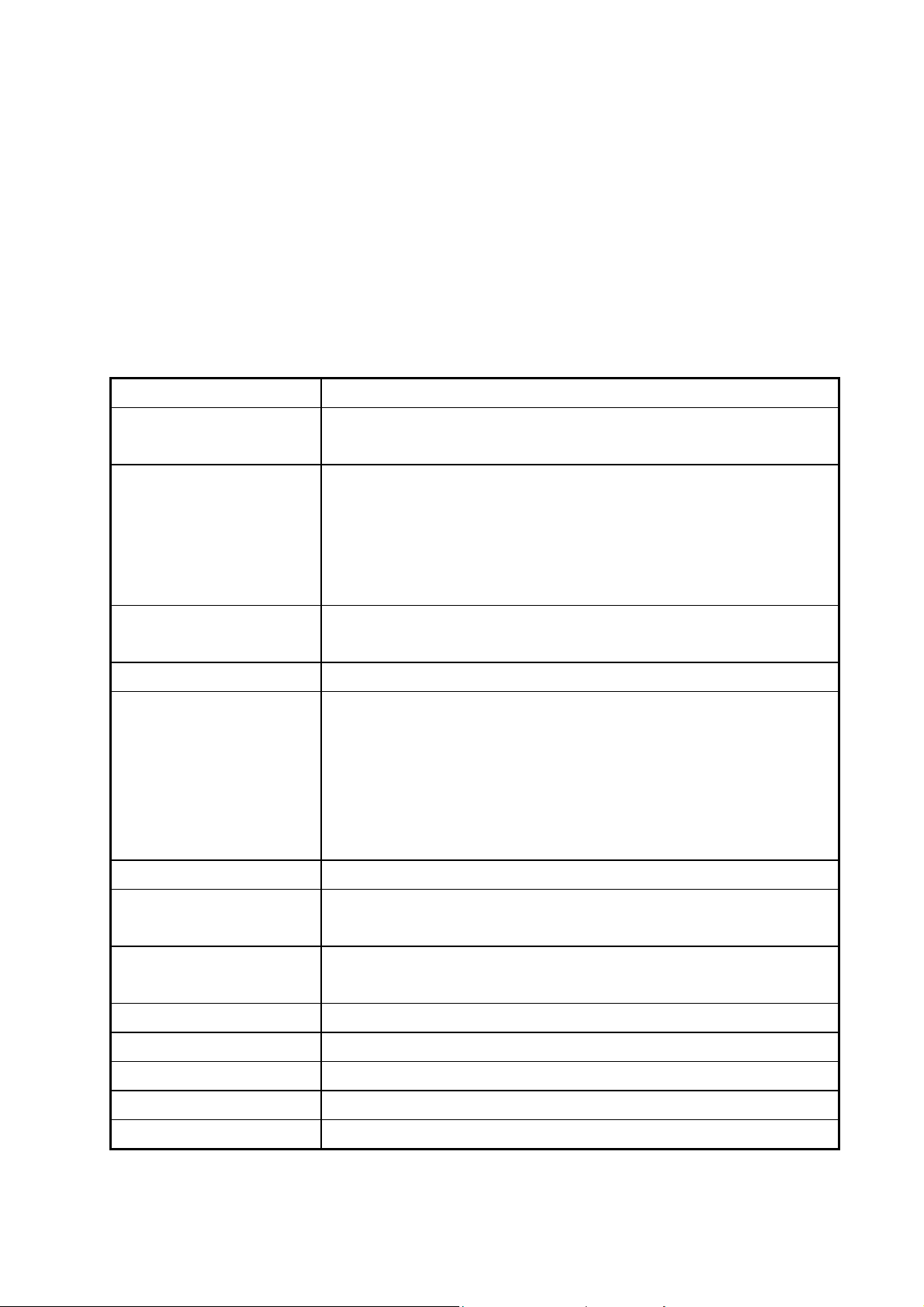

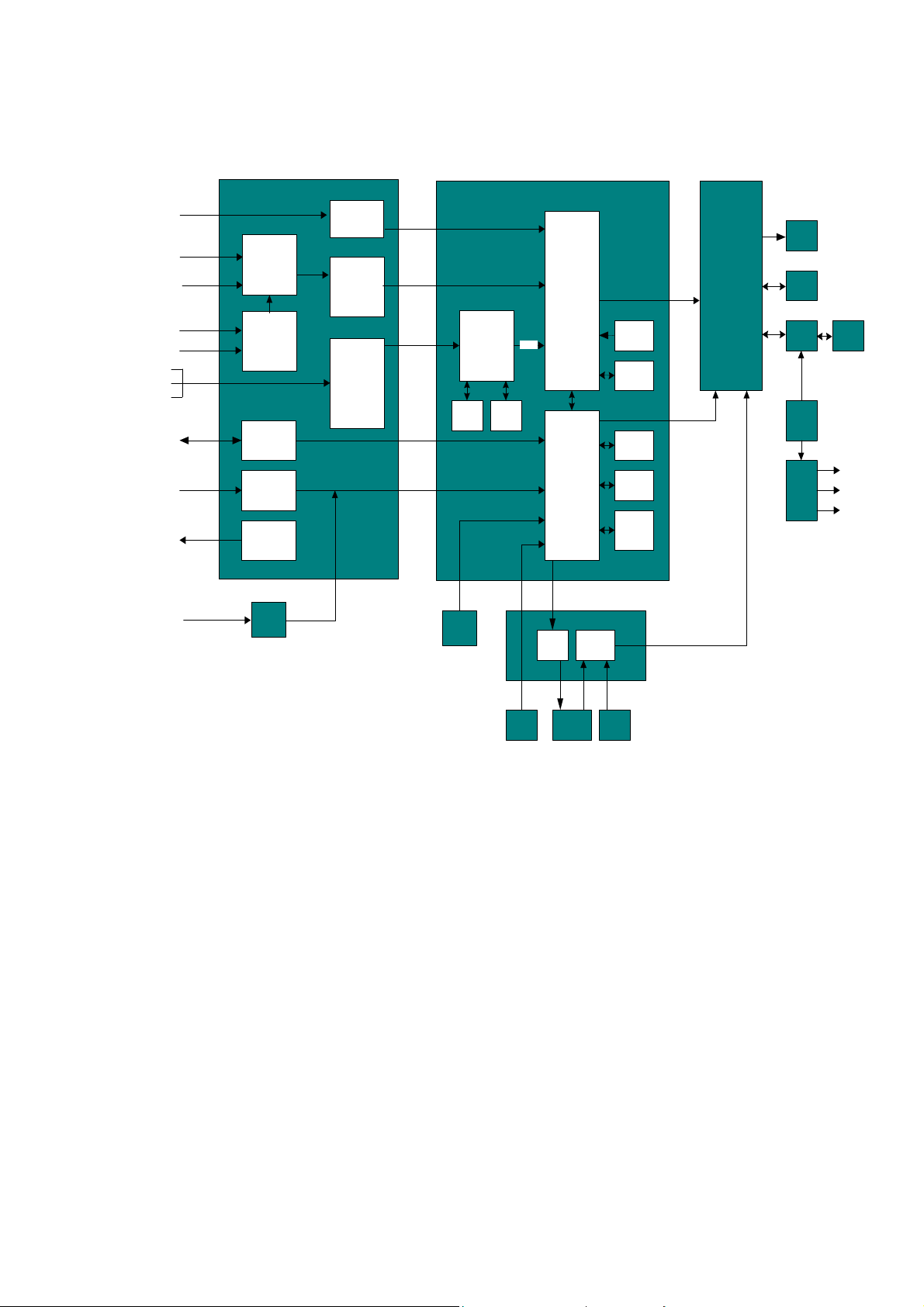

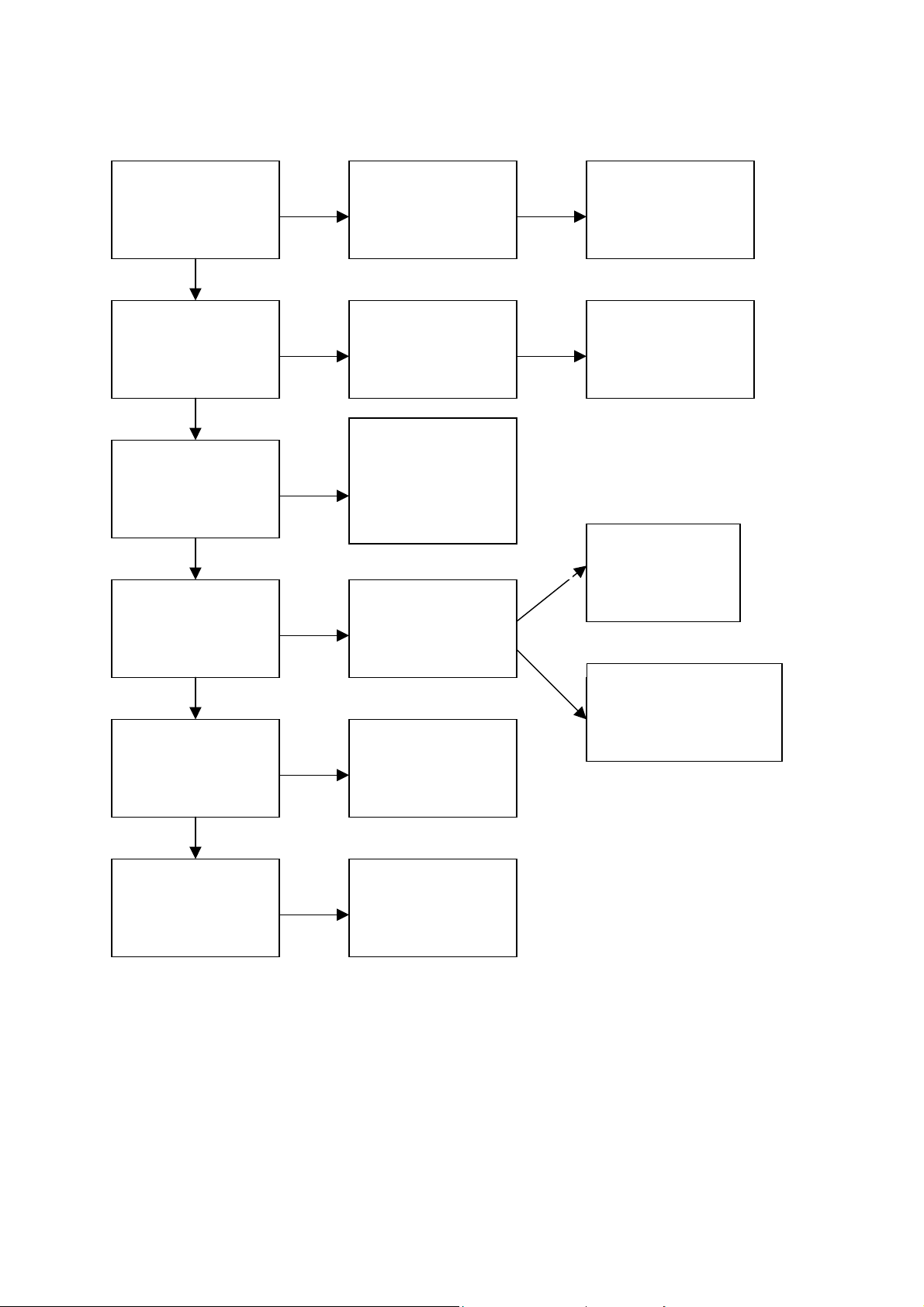

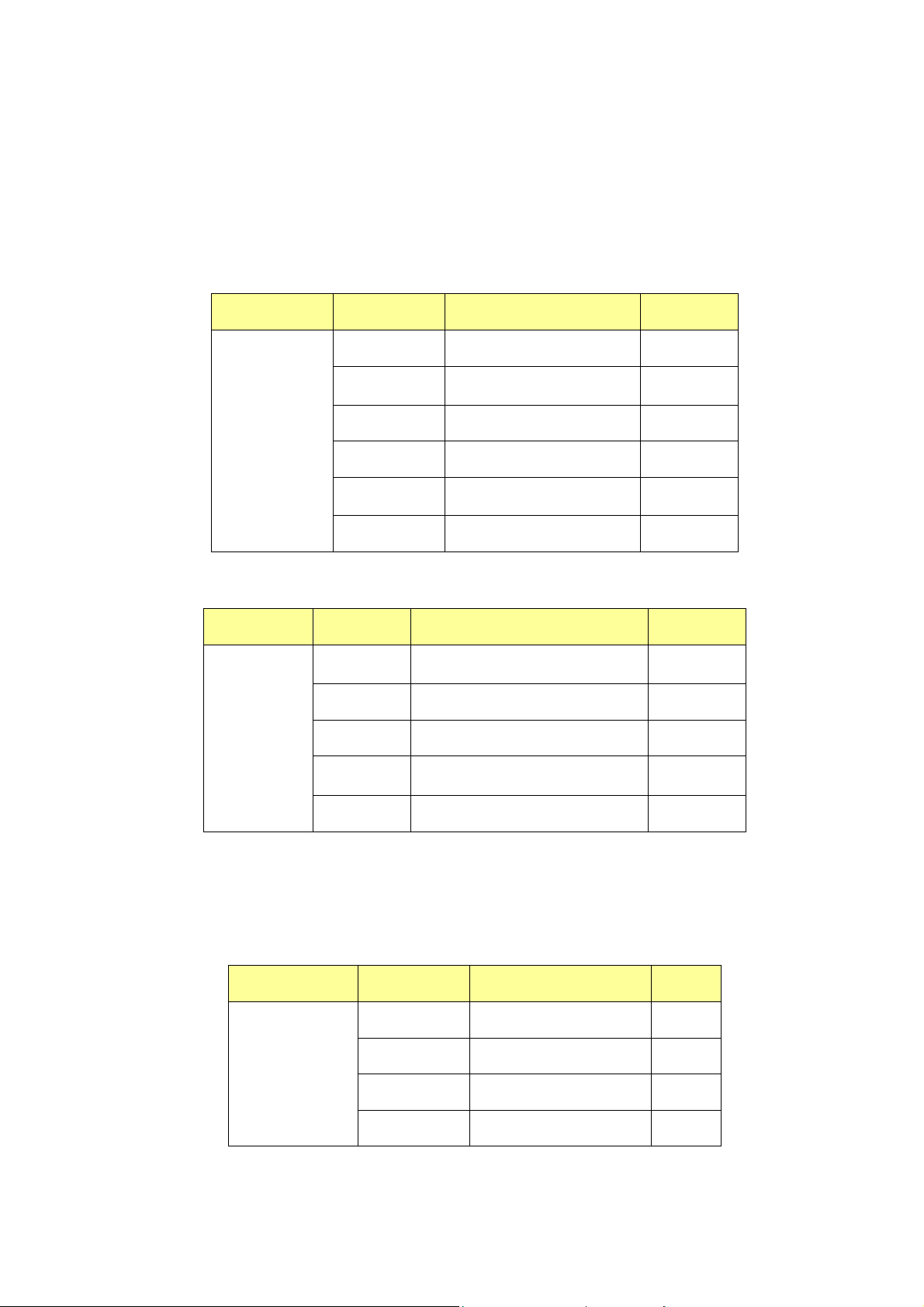

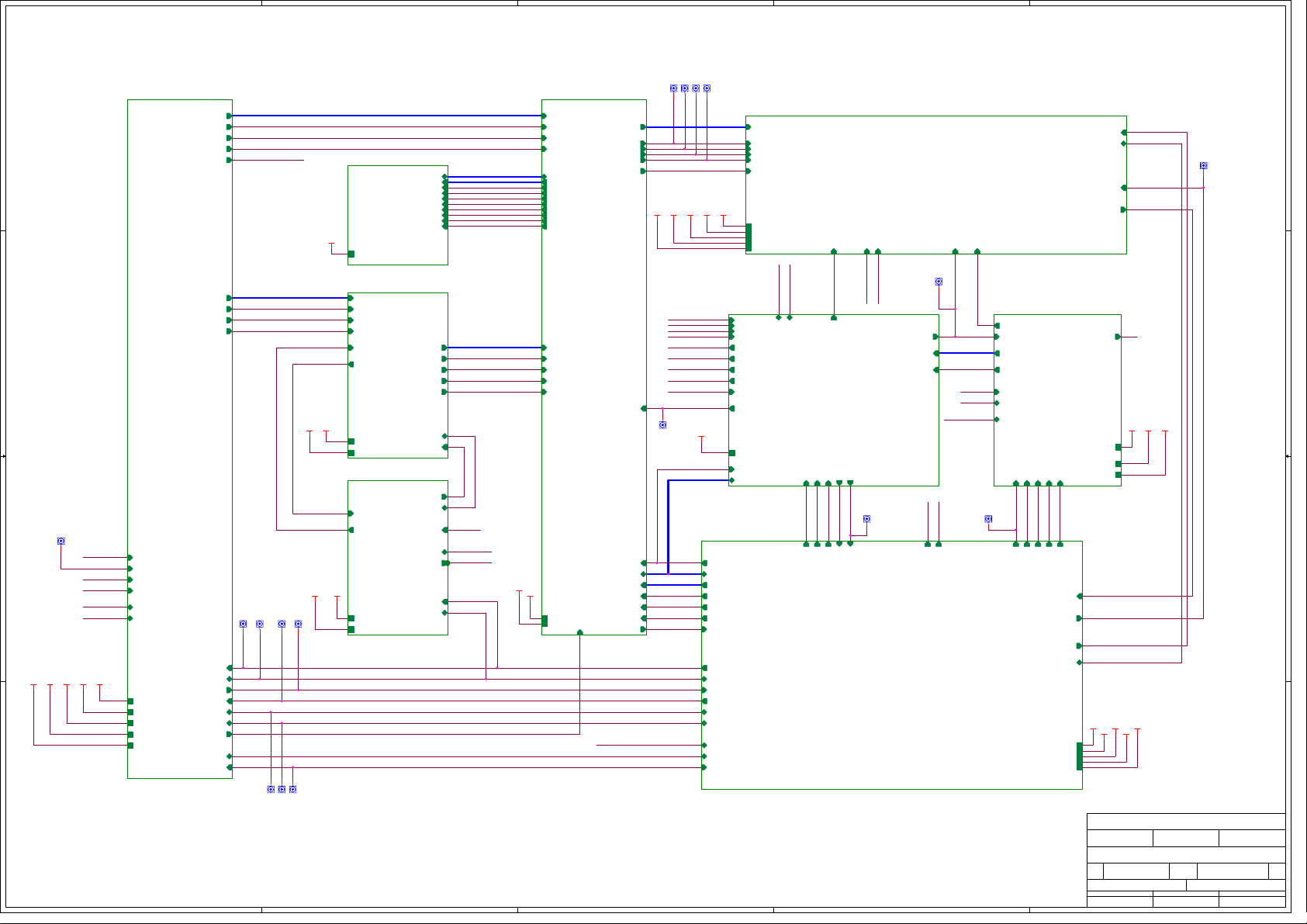

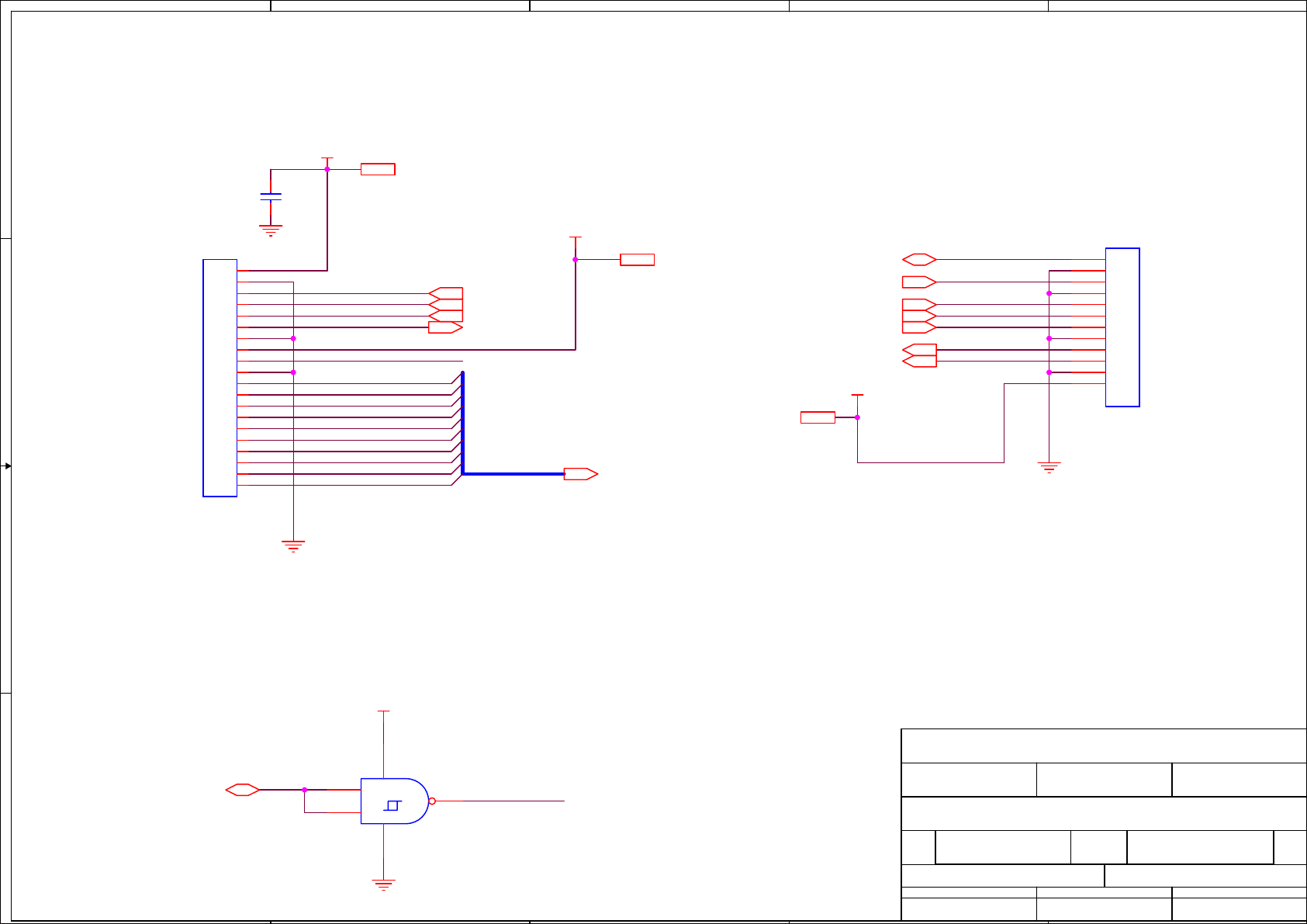

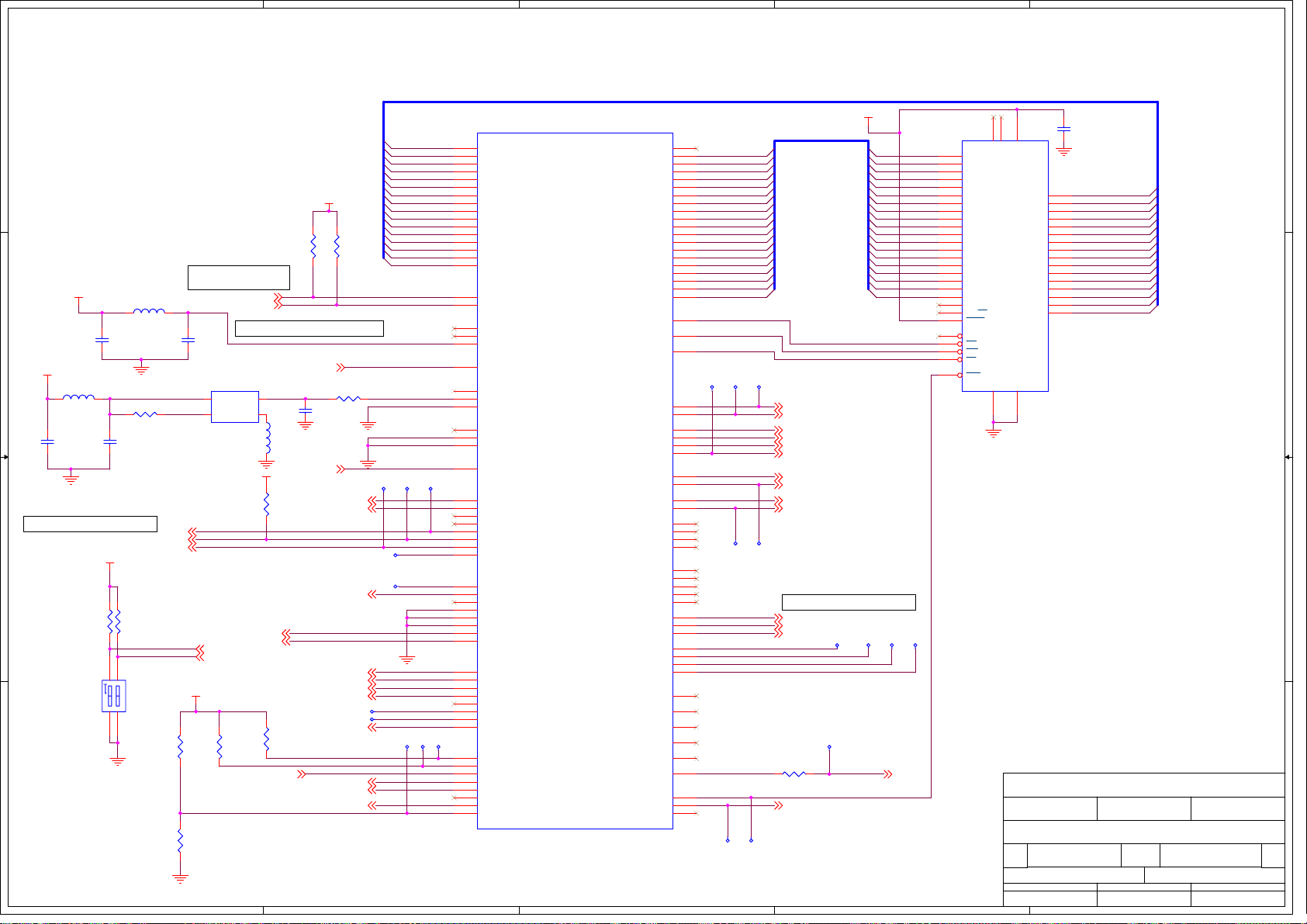

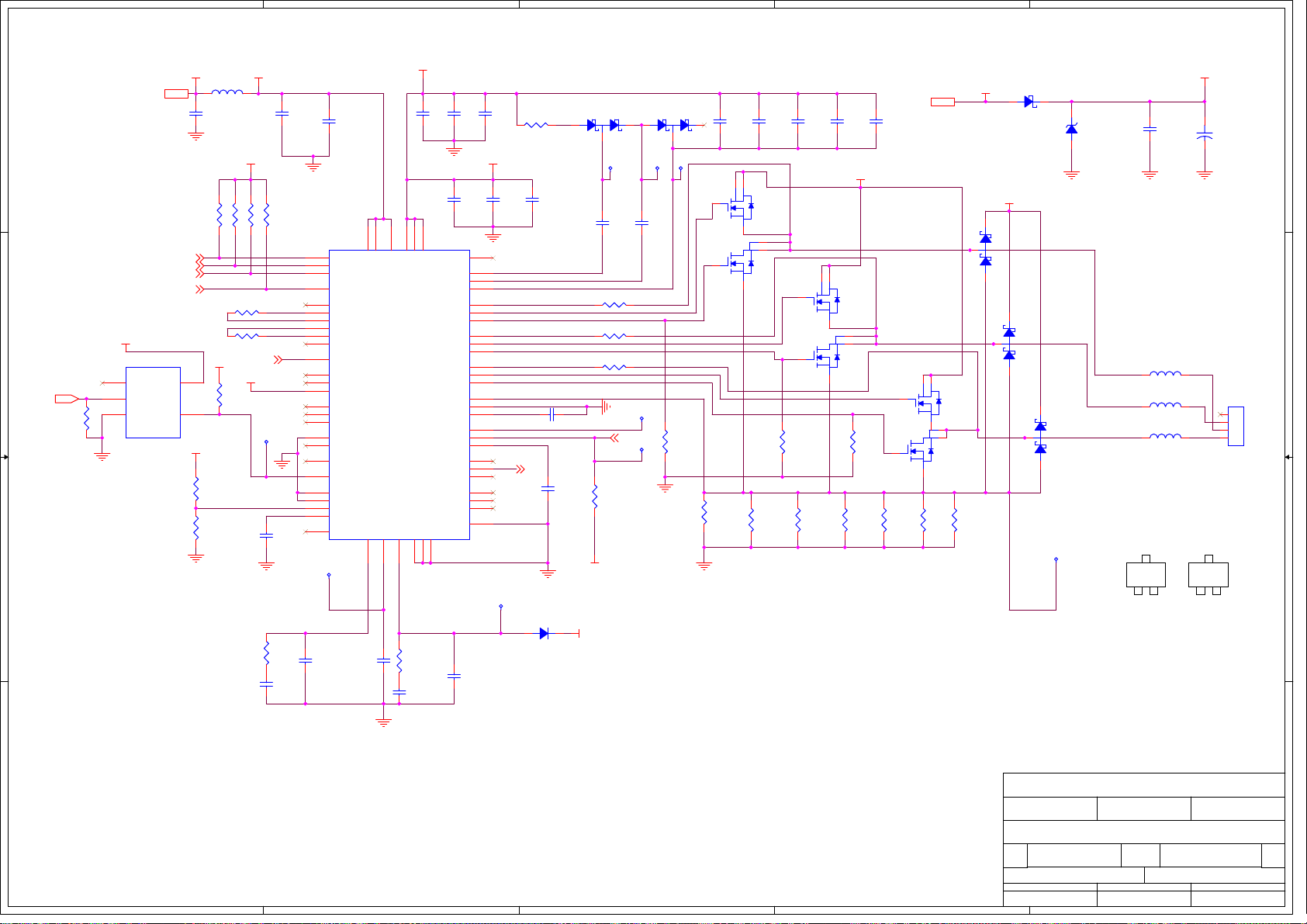

5. Black Diagram

RGB DVI

RGB PC

RGB/YPbPr

BNC

YCbCr

YPbPr

S-video

Video

YCbC r

RS232 RJ11

IR (TOP)

12V Trigger O/P

IR (fron t) IR Board

Conntctor Board Main Board

Sil169

(U17)

MUX

(U2,U3,U4)

IR Board

MUX

(U5)

RS232

Download

(U14)

IR

(U12)

12V

(Q2,Q3)

IR

Board

ADC AD9883

(U7)

Video Decoder

SAA7118

(U10)

SDRAM

(U3)

Keyboard

De-inter lace

SII504

(U2)

MCU503

(U4)

Video Port

Scaler

RM1-A

(U5)

CPU RDC8820

(U10)

Fan

Driver

(U1,U3)

Translatio n Board

Protec tion

Circuit

(U4)

Reset IC

(U18)

SDRAM

(U19,U20,

U21)

SRAM

(U9)

Frash

(U12)

RS232

Hardware

Monito r

(U14)

DMD Board

HD2

DMD

Color

Cheel

Blaster Lamp

400V

PFC

Board

Power

Board

3.3V

5V

12V

Therm al

Sensor

Fans

Therm al

Break

24

Page 26

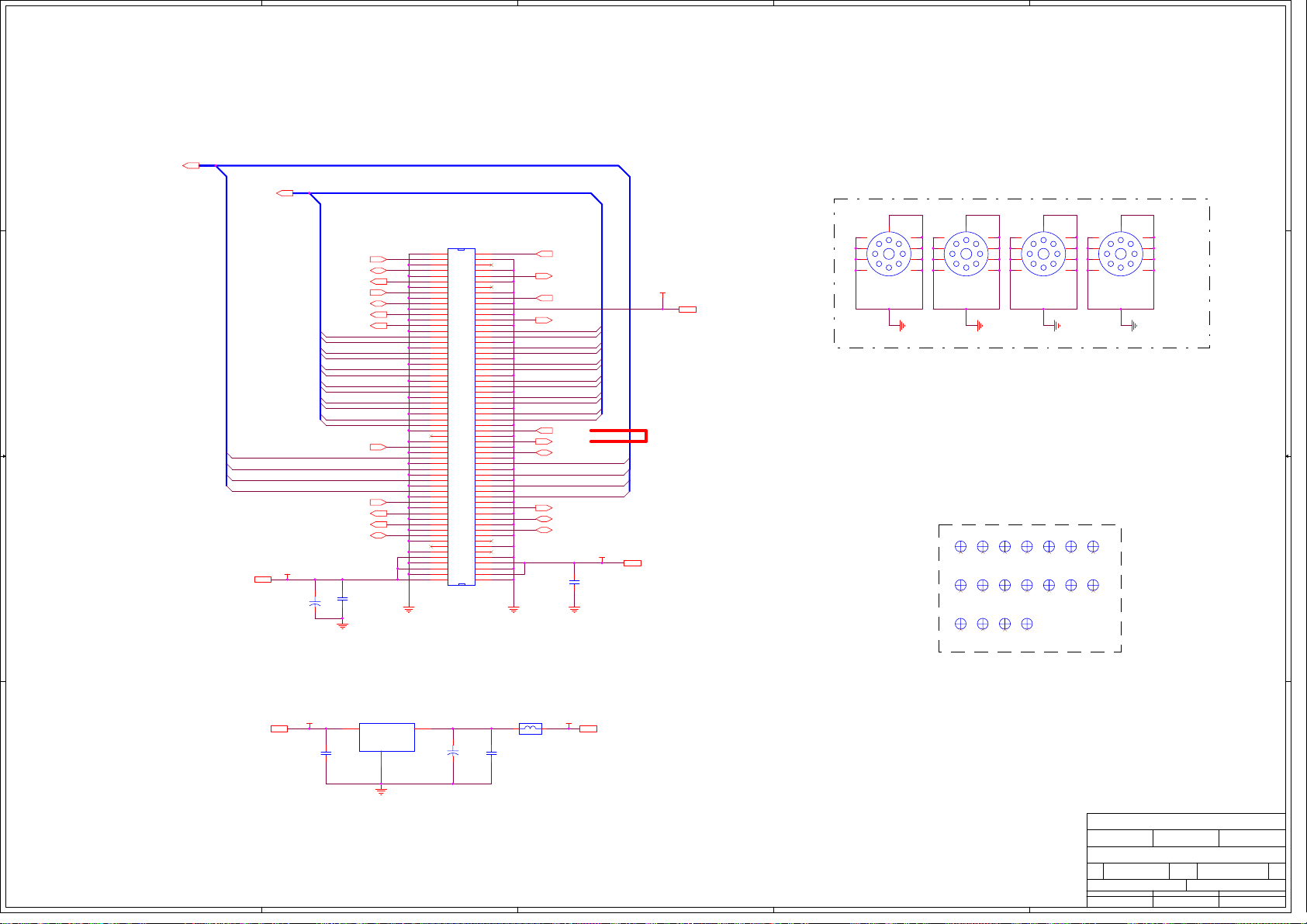

6. Packaging Description

25

Page 27

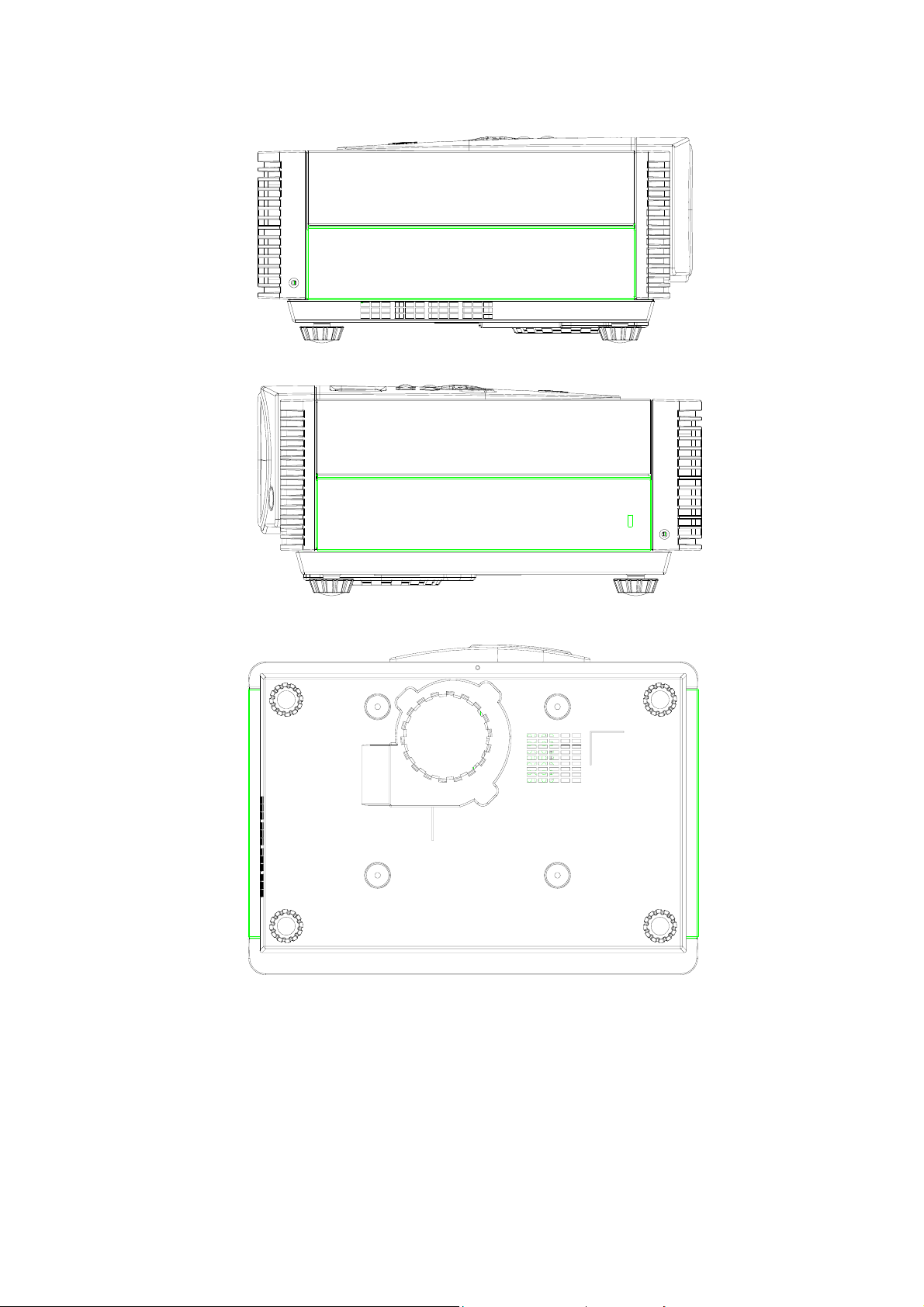

7. Appearance Description

26

Page 28

27

Page 29

8. Alignment Procedure

1. DMD Bias Voltage Alignment

Equipment:

- None

Procedure:

1. Watch DMD chip Label

2. Switch the DIP switch on DMD board according to the character on the DMD chip

B C D E

1 of SW H1 1 0 1 0

2 of SW H2 1 1 0 0

0: Left; 1:Right

2.Color Wheel Delay Alignment

Equipment:

- Battery Biased Silicon PIN Detector

- Oscilloscope

- Probe

OSD Default value used for color delay alignment

Item Value Item Value

USER>DVI-A> Factory>DLP>

Brightness 0 Brightness 0

Contrast 30 Contrast 49

Color 60 CW delay 20

Tint 15 User>Setup>Whit

Sharpness 0 Red Gamma 66

Filter 2 Green Gamma 66

Color Temp 0 Blue Gamma 66

R gain 512

G gain 512

B gain 512

R Offset 0

G Offset 0

B Offset 0

The default values let optical engine to get maximum contrast and brightness.

28

Page 30

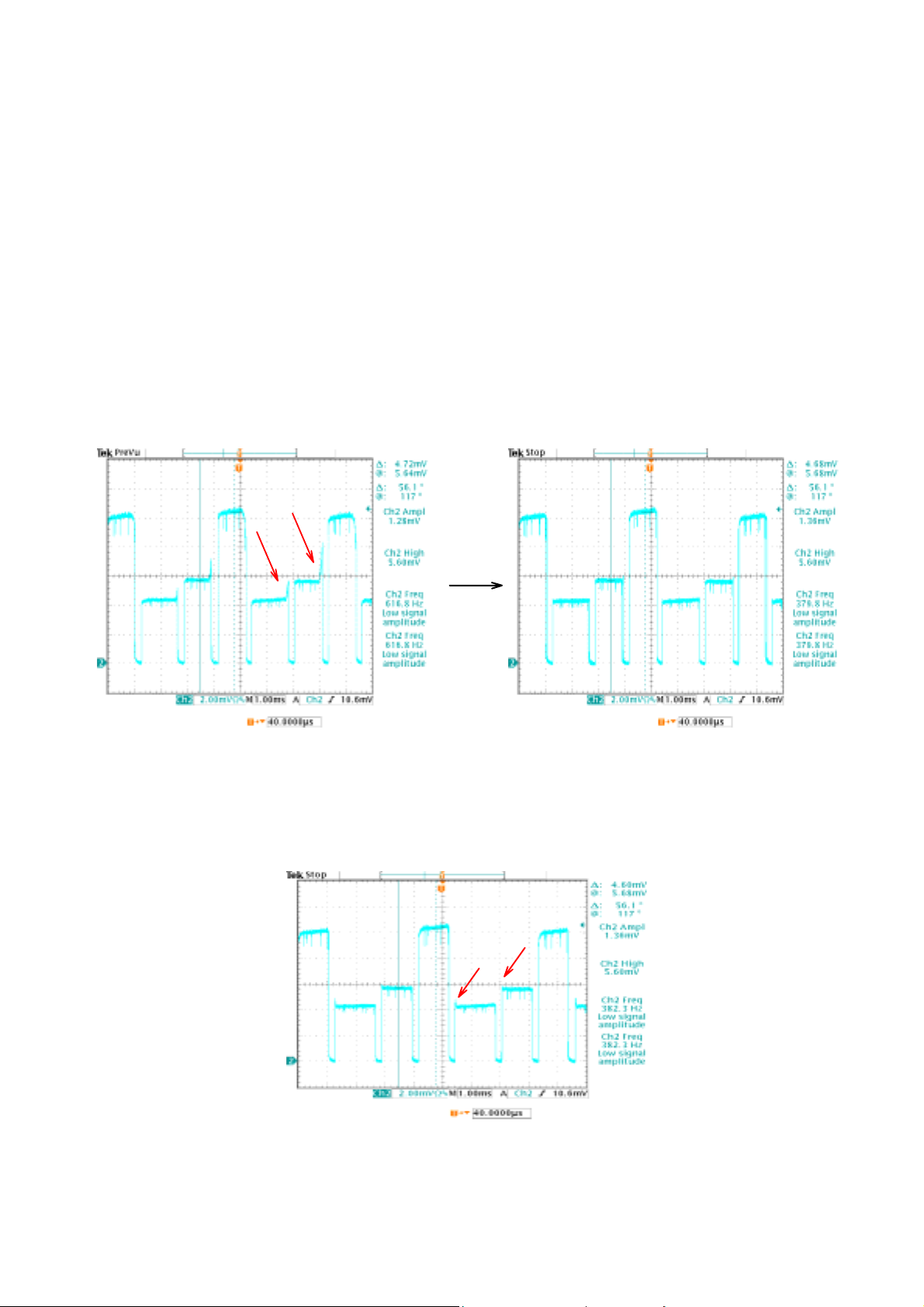

Procedure:

1. Probe impedance matches 50 ohm

2. Change Timing and pattern of pattern generator :

Timing : 800x600@60Hz (H:37.879Khz,V:60.317Hz)

pattern : full white

3. Adjust user & factory OSD values to default.

4. Open Factory OSD, and select color wheel delay item.

5. The image will become white.

6. Put the detector on the screen that white image was projected.

7. Watch the oscilloscope and notice the square waveform

8. Use the “” and “” key to increment or decrement the color wheel delay value

9. No matter the waveform is square or not, let the waveform was lagged first

Lag Exact

10. Then increment or decrement the value to let the waveform to be square

11. Do not adjust too much, let the signal get ahead, if it happens, go back to step 7 and do

it again.

Ahead

12. Select “Save Setting” at “Factory OSD>Factory>”.

29

Page 31

3. DVI-Analog Color Alignment Procedure

Default valve(User menu)

contrast color Sharpness

Video 17 23 3

S-Video 17 23 1

Comp 17 30 0

Comp-HD 17 30 3

RGBHV 17 30 3

DVI-I 17 30 1

The Gamma(RED ,GREEN,BLUE) is 66 for temperature 0,1,2,3,4.

Equipment:

- Pattern generator (Chroma 2250)

- Lux meter ( CL-100)

OSD Default value used for DVI-Analog color alignment

Item Value Item Value

USER>Picture> Factory>HDADJ>RG

Brightness 30 R offset 55

Contrast 17 G offset 63

Color 30 B offset 62

Tint 15 R Gain 89

Sharpness 1 G Gain 89

Filter 1 B Gain 89

Color Temp 2

Factory>DLP

Brightness 0

Contrast 49

User>Setup>White

Gamma Red, Green, 66

Gamma Red, Green, 0

30

Page 32

+

Procedure:

A. Black Level Adjustment: (DLP brightness)

1. Change pattern of pattern generator :

Pattern : Black (Gray 0)

2. Adjust DLP Brightness to let the black picture to just distinguish.

B. White Level Adjustment: (AD contrast---R,G,B gain)

1. Change pattern of pattern generator :

pattern : White (100% Gray)

2. Use Lux meter to measure the white level. Adjust the contrast value of AD9883 (RGB)

to let the light output to just max.

3. Change to 32-gray (0 ~ 100%) pattern. All steps must appear,

C. Offset adjustment at low brightness (AD R, G, B offset)

1. Change Timing and pattern of pattern generator :

pattern : 10% Gray

2. Set user color temp to 6500K.

3. Adjust AD9883 Red and Blue Offset to meet 6500K color spec.

D. Color Temperature at high brightness (Scalar Gamma R, G, B Gain)

1. Change Timing and pattern of pattern generator :

Timing : 800x600@60Hz (H:37.879Khz,V:60.317Hz)

Pattern : 80% gray

2 Color temperature spec: CIE 1976 u’, v’ chromaticity)

Color temperature

'

27

=

x

=

y

'

=

u

'

=

v

u

''

−

12

4

9

364818

vu

'

v

''

364818

+−

vu

x

3122

++−

yx

y

3122

++−

yx

5400°K 6500°K 7500°K

0.333 0.312 0.296

0.333 0.329 0.316

0.210 0.197 0.190

0.473 0.468 0.459

Deviation:

u’v’=

( vu ∆+∆

2

'

2

'

<=0.010 <=0.010 <=0.010

Color Temp 4 = color temp is the same as that of 6500K

31

Page 33

3 The variance of color coordinate via R,G,B gains:

x Y

R ↓ X ↓

G ↓

-

-

y ↓

B ↓ X ↑ y ↑

4. Adjust 6500K temperature color by changing Gamma-Rgain, Ggain, and Bgain.

5. Open Factory OSD and set the factory default value :

user>setup>white C0 C1(5400k C2(6500k C3(7500k

Gamma-Rgain 512 512 512 512

Gamma-Ggain 512 412 467 479

Gamma-Bgain 512 398 452 490

User the lux meter and adjust Gamma-Rgain, Gamma-Ggain, & Gamma-Bgain to

meet the spec.

6. Press “Save Graphics Color Temp” to save current setting into memory.

7. Select “Save Setting” at “Factory OSD>Factory>”.

8.Change pattern to 10% gray pattern and measure the color temp. If 6500K color spec is

not met, repeat all procedures in C and D.

9. Follow step 1 to 8 to adjust 5400K, 7500K color temperature.

10. For auto-alignment, use Command Y31/Y32/Y33 to save 5400K/6500K/7500K

temperature

11. For auto alignment, use Command to reset Temp4 color temp to 6500K

4. YPBPR Color Alignment

(A) YPbPr Component:

Equipment:

- Pattern generator (VG-828)

- Lux meter ( CL-100)

OSD Default value used for YPBPR color alignment

Item Value Item Value

USER>Picture>

Brightness 30

Contrast 17

Color 30

Tint 15

Sharpness 3 Brightness 60

Factory>HD ADJ>YPbPr>

32

Page 34

Filter 1 Contrast 76

Color Temp 2 Saturation 49

Pb offset 60

Pr offset 60

Procedure:

(a). PBPR Offset adjustment: (AD PB, PR Offset)

1. The variance of color coordinate via Pb offset and Pr offset:

x y

Pb offset ↓ x ↓ y ↓

Pb offset ↑ x ↑ y ↑

Pr offset ↓ x ↑ y ↓

Pr offset ↑ x ↓ y ↑

If we line the x and y, then the Pb offset is the shift action and the Pr offset is the

rotational action.

2. Connect power, YPbPr Video into projector.

3. Change Timing and pattern of pattern generator :

Timing : 480P(H:31.54 KHz,V:60.08 Hz)

pattern : 10gray Pattern

4. Turn on projector

5. Set user OSD values to default.

6. Enter factory mode.

7. Set Factory values to default.

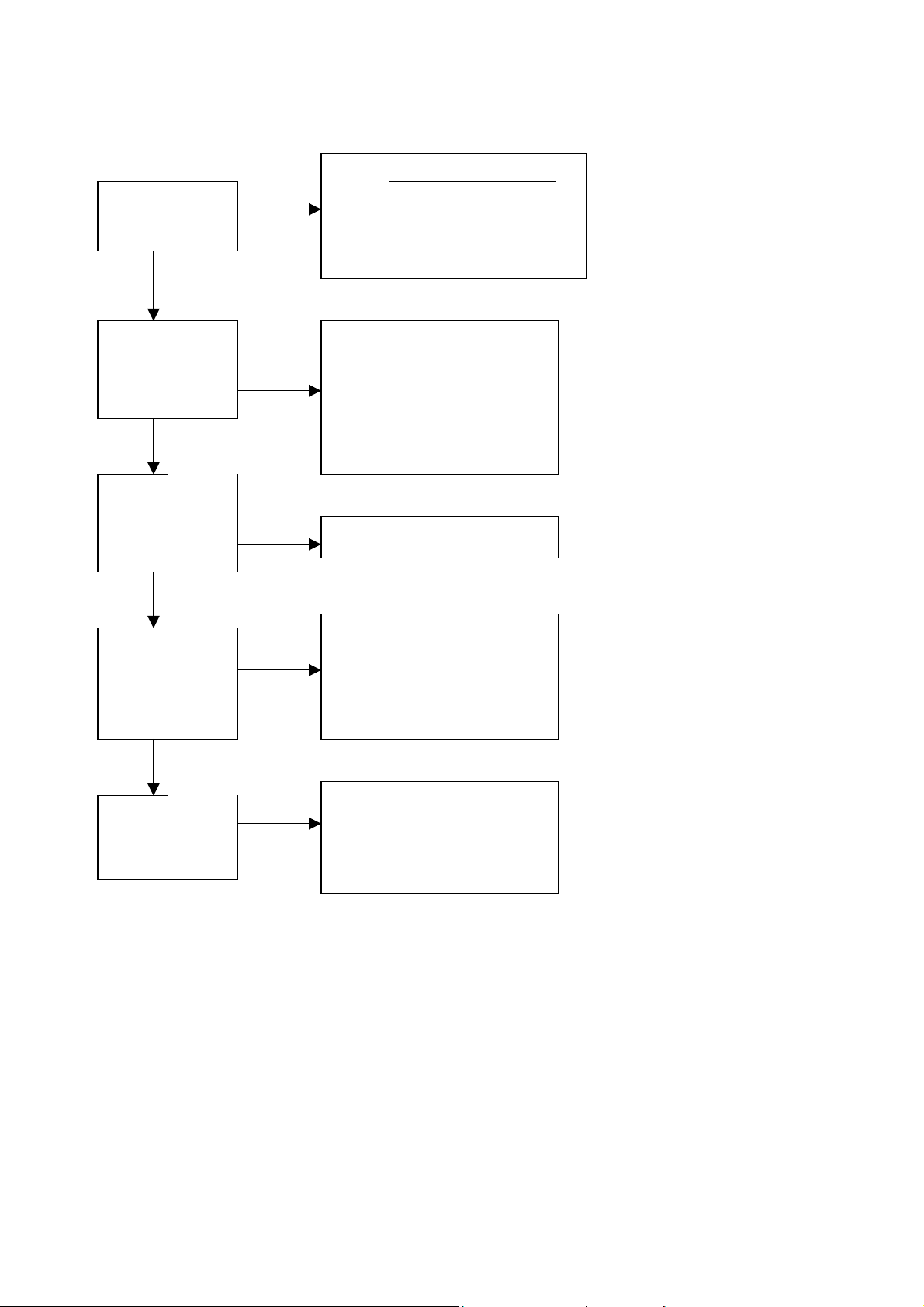

8. Follow the Pb, Pr offset adjustment flow chart to adjust color temperature to 6500K

b). Gray Level: (AD YPBPR Contrast, Brightness)

1. Change Timing and pattern of pattern generator :

Timing : 480P(H:31.54 KHz,V:60.08 Hz)

pattern : gray 32( or gray16 only for overscan)

2. Adjust the Brightness of AD9883 (RGB) to let the black level of the gray

32 to just distinguish. Use Lux meter to measure the white level of the gray 32. Adjust

the contrast value of AD9883 (RGB) to let the light output to just max.

3. Check the 32 levels of gray. All steps must appear,

33

Page 35

(c). Saturation Level: (Scalar)

1. Change Timing and pattern of pattern generator :

Timing : 480P(H:31.54 KHz,V:60.08 Hz)

pattern : 100% blue

2. Adjust saturation and use lux meter to measure to let the light output just max.

3. Select “Save Setting” at “Factory OSD>Factory>”.

Use L ux m ete r to

read the coordinate of

black and the value

note (x1,y1).

Case

x1>x0 & y1>y0

Decrease Pb offset

until x<=x0 or

A B C

Case x<=x0:

The value note (x2,y2).

Dy = y2 - y0.

Decrease Pb o ffset until the y

value <= y2 - 1/2Dy . Now, the

reading of the Lux meter =

(x3,y3) and x3 will < x0, y3 will

> y0.

Decrease Pr offset the x value

will increa se an d y v alue w ill

decrease to meet the sp ec.

y<=y0

Case y<=y0:

The value note (x2,y2).

Dx = x2 - x0.

Decrease Pb offset until the x

value <= x2 - 1/2Dx . Now, the

reading of the Lux m eter =

(x3,y3) an d x 3 w ill > x0 , y3 w ill

Increase P r offset th e x va lue w ill

decrease and y value will increase

to meet the spec.

< y0.

Increase Pb offset

Case x>=x0:

The value no te (x2,y2).

Dy = y0 - y2.

Increase Pb offset until the y

value >= y2 + 1/2Dy . Now, the

reading of the Lux meter =

(x3,y3) and x3 will > x0, y3 will

< y0.

Increase Pr offset the x value will

decrease a nd y v alu e w ill in creas e

to meet the spec.

Case

x1<x0 & y1<y0

until x>=x0 or

y>=y0

value >= x2 + 1/2Dx . Now, the

(x3,y3) and x3 will < x0, y3 will

Decrease Pr offset the x valu e

D

Case y>=y0:

The value note (x2,y2).

Dx = x0 - x2.

Increase Pb offset until the x

reading o f the L ux m ete r =

> y0.

will increa se an d y v alu e will

decrease to me et the sp ec.

Case

x1>x0 & y1<y0

Increase Pr offset until

x<=x0 or y>=y0

Case x<=x0: Case y>=y0:

BC

Case

x1<x0 & y1>y0

Decrease Pr offset

until x>=x0 or y<=y0

Case x>=x0: Case y>=y0:

DA

34

Page 36

Case x1>x0 & y1 > y0 :

y =.331

x =.291

x0 =.281 y0 =.311

x =.301

x0 =.281 y0 =.311

y =.321

dec. Pb

dec. Pb

Case x1<x0 & y1 < y0 :

x0 =.281 y0 =.311

x =.271

x0 =.281 y0 =.311

x =.261

inc. Pb

y =.291

dec. Pb

y =.301

x =.281 y =.321

x0 =.281 y0 =.311

x =.291 y =.311

x0 =.281 y0 =.311

x0 =.281 y0 =.311

x =.281

x0 =.281 y0 =.311

x =.271

y =.301

y =.311

dy=.01

1/2dy=0.005

dec. Pb

dx=.01

1/2dx=0.005

dec. Pb

dy=.01

1/2dx=0.005

inc. Pb

dx=.01

1/2dx=0.005

inc. Pb

y =.316

x0 =.281 y0 =.311

x =.276

x =.286

x0 =.281 y0 =.311

x =.286

x0 =.281 y0 =.311

x0 =.281 y0 =.311

x =.276

y =.306

y =.306

y =.316

dec. Pr

inc. Pr

inc. Pr

dec. Pr

x =.281 y =.311

x =.281 y =.311

x =.281 y =.311

x =.281 y =.311

Case x1>x0 & y1 < y0 :

x =.291

x0 =.281 y0 =.311

x =.301

x0 =.281 y0 =.311

inc. Pr

y =.291

inc. Pr

y =.301

Case x1<x0 & y1>y0

y =.331

y =.321

dec. Pr

dec. Pr

x0 =.281 y0 =.311

x =.271

x0 =.281 y0 =.311

x =.261

x =.281

x0 =.281 y0 =.311

y =.301

x =.291 y =.311

x0 =.281 y0 =.311

y =.321

x0 =.281 y0 =.311

x =.281

x0 =.281 y0 =.311

x =.271

y =.311

dy=.01

1/2dx=0.005

inc. Pb

dx=.01

1/2dx=0.005

dec. Pb

dy=.01

1/2dy=0.005

dec. Pb

dx=.01

1/2dx=0.005

inc. Pb

x =.286

x0 =.281 y0 =.311

x =.286

x0 =.281 y0 =.311

x0 =.281 y0 =.311

x =.276

x0 =.281 y0 =.311

x =.276

y =.306

y =.306

y =.316

y =.316

inc. Pr

inc. Pr

dec. Pr

dec. Pr

x =.281 y =.311

x =.281 y =.311

x =.281 y =.311

x =.281 y =.311

35

Page 37

V

V

5. TV Color Alignment Procedure

5.1 TV Color Temp Alignment

Equipment:

- Pattern generator (VG-828)

- Lux meter ( CL-100)

OSD Default value used for YCBCR color temp alignment

Item

alue Item

alue

USER>Picture>

Brightness 30

Contrast 17

Color 30

Tint 15

Factory>SD

Sharpness 0 Brightness 180

Filter 3 Contrast 92

Color Temp 2 Saturation 90

User>Setup>White

Gamma Red, Green, 66

Gamma Red, Green, 0

1. Connect the signal to YCBCR component connector, and change Timing and pattern of

pattern generator :

Timing : NTSC(H:15.73 KHz,V:29.96 Hz)

pattern : 80% Gray

2. Color temperature spec:

Color temp. 4 is the same as that of 6500K

3. The variance of color coordinate via R,G,B gains:

4. Adjust 5400K / 6500K / 7500K temperature color.

5. Open Factory OSD and set the factory default value :

User>setup>white C0 C1(5700k C2(6500k C3(9300k

Gamma-Rgain 512 512 512 512

Gamma-Ggain 512 416 467 490

Gamma-Bgain 512 408 460 508

36

Page 38

6. User the lux meter and adjust Gamma-Rgain, Gamma-Ggain, & Gamma-Bgain to meet

the spec.

7. Press “Save Color Temp. Videos > AS Color Temp 5400” to save into memory.

8. Repeat 6~7 to perform the 6500K and 7500K color temperature.

9. Select “Save Setting” at “Factory OSD>Factory>”.

10. For auto-alignment, use Command Y80/Y81/Y82 to save 5700K/6500K/9300K

temperature.

5.2 Gray Level for YCBCR Component

Procedure:

(a). Gray Level:

1. Connect power, YCbCr Video into projector.

2. Change Timing and pattern of pattern generator :

Timing : NTSC(H:15.73 KHz,V:29.96 Hz)

pattern : gray 32( or gray16 only for overscan)

3. Light on projector

4. Set user OSD values to default.

5. Enter factory mode.

6. Set Factory values to default.

7. Adjust the Brightness and Contrast to let the black level to just distinguish, and the

light output of white level to just max.

8. Check the 32 levels of gray. All steps must appear,

(b). Saturation Level:

9. Change Timing and pattern of pattern generator :

Timing : NTSC(H:15.73 KHz,V:29.96 Hz)

pattern : 100% blue

10. Adjust saturation and use the Lux meter to measure to let the light output just max.

11. Select “Save Setting” at “Factory OSD>Factory>”.

37

Page 39

5.3 Gray Level for Composite Video & S-Video

Equipment:

- Pattern generator (VG-828)

- Lux meter ( CL-100)

OSD Default value:

Item Value Item Value

USER>Picture>

Brightness 30

Factory>SD

Contrast 17 Brightness 158

Color 23 Contrast 75

Tint 15 Saturation 91

Sharpness 3 Hue 0

Filter 3

Color Temp 2

Procedure:

(a) Gray Level

1. Connect power, Composite video or S-Video, into projector.

2. Change Timing and pattern of pattern generator :

Timing : NTSC(H:15.73 KHz,V:29.96 Hz)

pattern : gray 32( or gray16 only for overscan)

3. Light on projector

4. Set user OSD values to default.

5. Enter factory mode.

6. Set Factory values to default.

7. Adjust the Brightness and Contrast to let the black level to just distinguish, and the light

output of white level to just max.

8. Check the 32 levels of gray. All steps must appear,

(b). Saturation Level:

9. Change Timing and pattern of pattern generator :

Timing : NTSC(H:15.73 KHz,V:29.96 Hz)

pattern : 100% blue

10. Adjust saturation and use lux meter to measure to let the light output just max.

11. Select “Save Setting” at “Factory OSD>Factory>”.

6. Additional Patterns used for color final check

(a). Pattern 1: 0 ~ 14% gray, 2% change per step, (For DVI-A, YPBPR inputs)

Criteria: All gray bars should have the same color. Brightness change should be linear.

(b) Pattern 2: 16-gray (0 ~ 100%), For all input sources

Criteria: All gray bars should have the same color. Brightness change should be linear.

38

Page 40

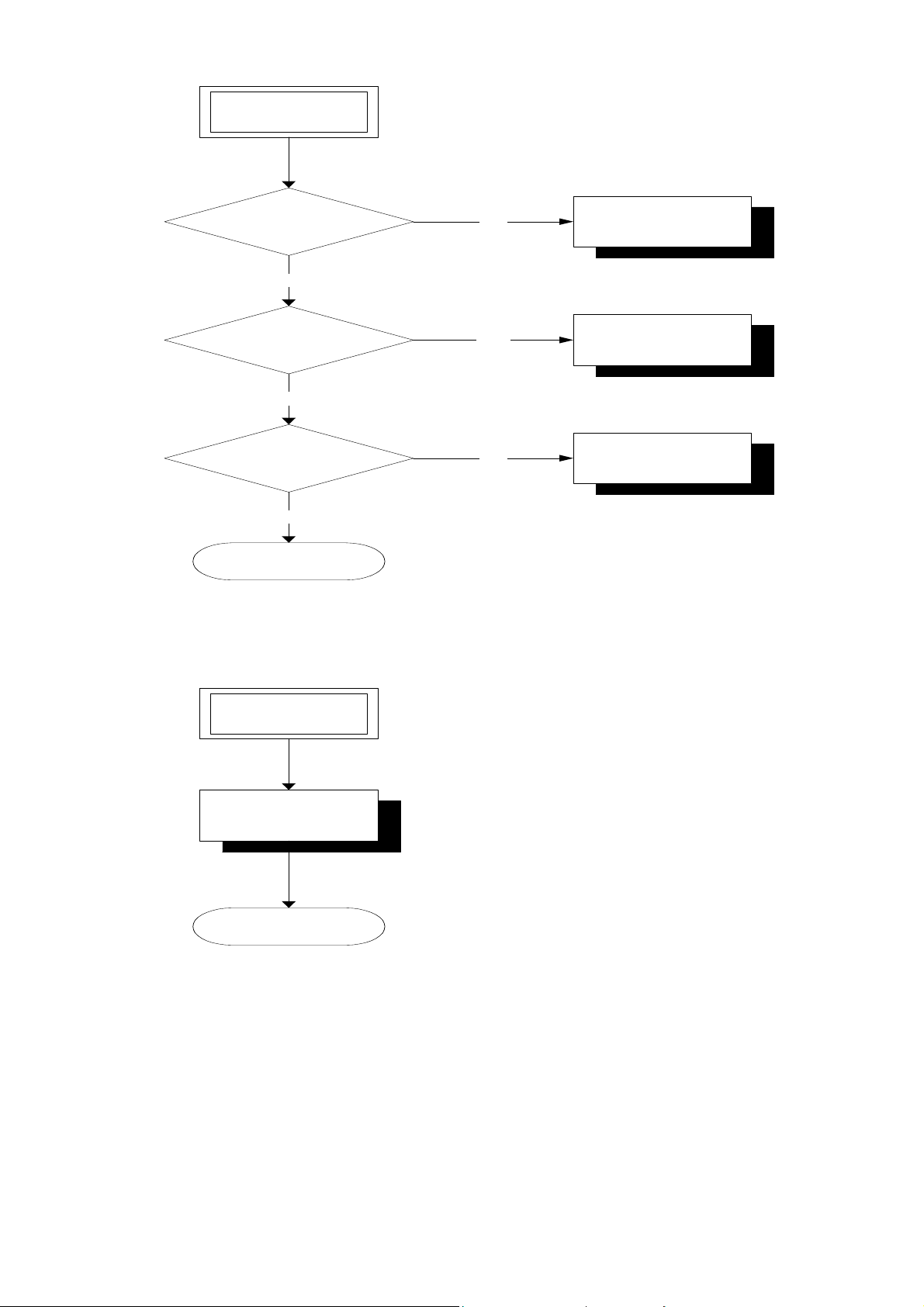

9. Trouble Shooting Guide

1. System trouble shooting :

Is LED light when

Main Power Switch

on?

n n

Check door luck

switch

1.Check +3Vs, +5Vs

2. Check power

Is Orange LED

active when remote

power on?

Is lamp turned on?

Does starting OSD

shows normally?

Does DVI-I signal

shows normally?

y

y

y

y

n

n

n

n

Are fans spinning?

Check DMD board

Check ballast

Check lamp

Does any stripe

shows on screen?

Check Connector

board and FPC

board

n

Check fans, wire and

Translation board

Check DMD board

y

Check DMD

socket

n

Check Main board, DMD

board

Does Video signal

shows normally?

y

n

Check Main board ,

FPC and Connector

board

39

Page 41

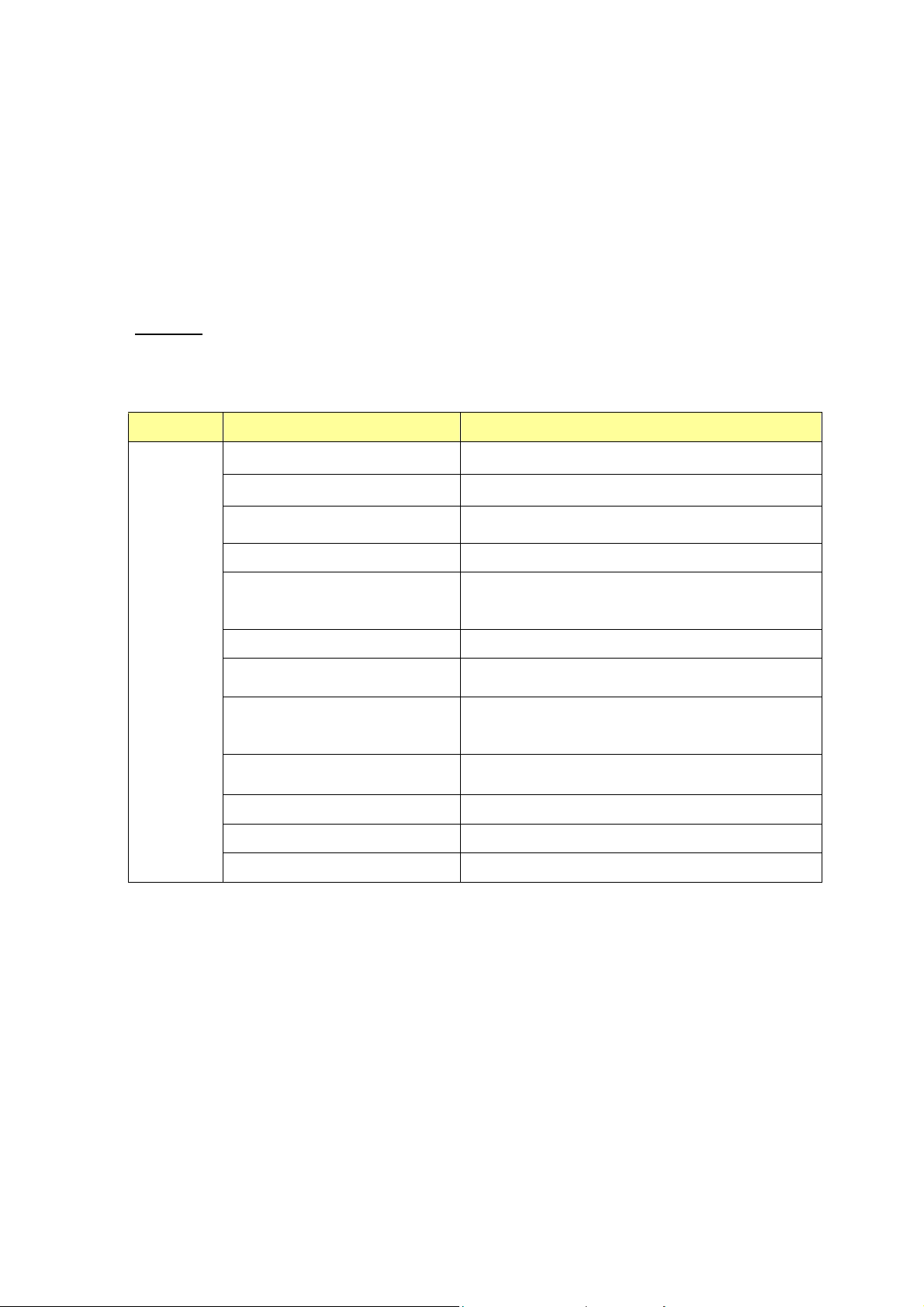

2. Main board trouble shooting:

Y

Y

Y

(1) Main:

REMOTE

POWERON

NO

ES

1. See CPU trouble shooting

U18, reset successful?

2. U17, RP25, RP24 OK?

3. CPU (U10) 56pin(IR) signal?

OSD ok?

When no valid

signal

OSD ok.

When input PC

signal

OSD ok.

When input

Video signal

NO

ES

NO

ES

NO

1. RP19,RP17,RP15,RP13

ok?

2. U19, U20 OK?

3. Check L8 with 100Mhz ok?

4. check L9 with 40Mhz ok?

1.check J2

1. RP1, RP2, RP3, RP4, R6

R3, R2, R4 ok? (SIL504

output)

2. check J2

Saving data in

EEPROM

YES

NO

1.Replace U6 (EEPROM)

2.check R36 R37(IIC pull high

resistors)

40

Page 42

Y

Y

Y

(2) SIL504 trouble shooting: (U4, U2)

X1, 20Mhz?

RESET

successful?

System IIC ok?

(U4 pin 15,14)

ES

SIL504 IIC ok?

(U4 pin 2, 3)

ES

DEINTDONE

Signal ok? (U4

pin21)

ES

No

No

No

No

1. check X1, C41, C42

2. check U17,RP25

1.Q2,Q3 ok? (level shift )

2. RP7 ok? ( IIC Pull high)

1. R10,R11ok? ( IIC Pull

high)

2. Replace U4

1. check SIL504 1.8V ok?

2. check U2, U3 ok?

41

Page 43

(3) CPU (U10) trouble shooting guide :

Check +3Vs

(pin92)

YES

Check X1

crystal

NO

1. Check C75, C76

2. replace X1

1. Check U9(SRAM), check CPU_LCS_N (pin 58) and

2. Check U12(Flash), check R68 and CPU_UCS_N (pin

YES

NO

RESET

Successful?

CPU_BHE_N is active?

57) is active?

YES

check U18, make sure U18

pin1 has delayed for certain

period of time ,from L go H.

42

Page 44

3. DMD board trouble shooting guide.

N

RESETZ And

POWERGOO

D?

Color wheel

Spinning?

Color wheel

Feedback (J3

pin3) ok?

Lamp light ok?

YES

YES

YES

O

NO

NO

NO

1. No RESETZ check main board and

translation board.

2. No POWERGOOD check main board

1. Check Color wheel and CW connector (J4)

2. CW power supply P12V of U13

1. Check CW sensor board and CW tag

2. Feedback 150Hz

1. Check J1 pin 1 (lampon) , normal status is

low

2. Check J1 pin 3(lamp light feedback) should

be low.

Normal Image

on screen ?

(32-Gray Pattern

in Factory mode

is

recommended)

YES

DMD pixels always on

Horizontal dark/bright lines

Check DMD socket.

Check C-spring

Check DMD B/D : DAD1000(U1) VCC (5V), VBIAS

(23 ~ 26V), VRST (-26V)

Vertical dark/bright lines

Check C-spring

Color missing

Check DMD socket.

43

Page 45

4. Connector board trouble shooting guide.

S-video is OK?

No

Composite is

No

OK?

Component is

No

OK?

Check L14,L17

Check U5

Check U10

Check L13

Check U5

Check U10

Check L15,L16,L18

Check U10

No

DVI- A is

OK?

DVI-D (HDCP)is

No

OK?

YPbPr is OK?

BNC-PC is OK?

No

No

J6 12V output?

Check L28,,L29,L31,L32,L33

Check U17

Check U18DDC

Check U17

Check L2,L3,L4

Check U2

Check U7

Check L2,L3,L4,L5,L6

Check U2,U3,U4

Check F1

Check Q2

Check L24

Check Q3

44

Page 46

RS232 is OK?

No

Check R61,R62

Check U14

Check main board

5. Power board trouble shooting guide.

Power BD Check.

Disconnect the wire

Fuse Broken ?

Yes

Proceed to "Prim ary

Circuit Check".

No

form b uttom b d . to

Short Pin12& P in9.

power bd.

No +3.3V Output.

Check + 3.3V-Fix exists ?

Yes

F704 Broken ?

Yes

Replace new fuse.

No

No

Check output

voltages.(1)+ 3.3V(2)

+1 2V (3 )+5 V (4)+ 5 V -

Fix(5)+3.3V-Fix.

Proceed to "No +3.3V-

Fix output".

Q 70 4 w o rk s no rm a lly ?

Yes

Check trace.

No

Check Q 702,Q703,

and O n/Off signal.

45

Page 47

N o +12V O utput

C heck 12V exists ?

Yes

Check Q703 works

norm ally ?(V ce<0.2V )

Yes

Check Q702 works

norm ally ?(V ce>10V )

Yes

C heck R 730 and

layout trace.

No +5V output.

C heck + 5V -F ix exist ?

No

No

No

No

Proceed to "N o 12V

Output".

Q 703 dam ages and

replace new

tran sistor.

Q 702 dam ages and

replace new

tran sistor.

Proceed to "No +5V -

Fix output".

Yes

Check Q701 works

norm ally ?(V ce<02V )

Yes

Check Q705 works

norm ally ?

Yes

C heck the trace of

+5V.

No

No

Q 701 dam ages and

replace new

tran sistor.

R eplace new P-

M O SFET.

46

Page 48

N o 12V output

o r N o + 5 V -F ix

output

C heck D 701 had been

inserted properly ?

Yes

C heck IC701 dam ages ?

No

C heck D 702 had been

inserted properly ?

Yes

Proceed to "Check

p rim a ry c irc uit" .

No

Yes

No

S o ld er it a g ain .

R eplace new IC 701.

S o ld er it a g ain .

No +3.3V-Fix

O utput

C heck IC705, IC602,

R 718, R 742, R 617,

Proceed to "Check

R616.

p rim a ry c irc uit" .

47

Page 49

Check primary

circ u it.

Fuse B roken ?

Yes

Yes

PinD & P inS of Q601

are shorted. Replace

new

R612,Q60 1,R611,ZD

602,IC601 and Fuse.

Check IC 601.

No

No

Proceed to "Check

IC601".

Check B D 651 dam ages ?Check Q601 dam ages ?

Yes

Inside diodes of

BD 601 are shorted.

Replace new bridge

diode.

No

Proceed to "Check

IC601".

Open R 612 an d inject

12V to Pin7 of

IC601.

Is the P W M w av efo rm o f

Pin6 of IC601 is correct ?

Yes

Replace ZD 601 and

IC603.

No

Replace IC601.

48

Page 50

10. Factory OSD Operation

There are 10 pages in this OSD, the ways to enter factory OSD are open user OSD, then

press power on button. If you have to return user OSD, open factory OSD and press power

on button again.

Go to \User OSD\Environment\lamp hours\minutes, then press Right, Left, Right, Left,

Enter in a row to switch to factory OSD.

1. Factory

This page is mostly for our factory to use.

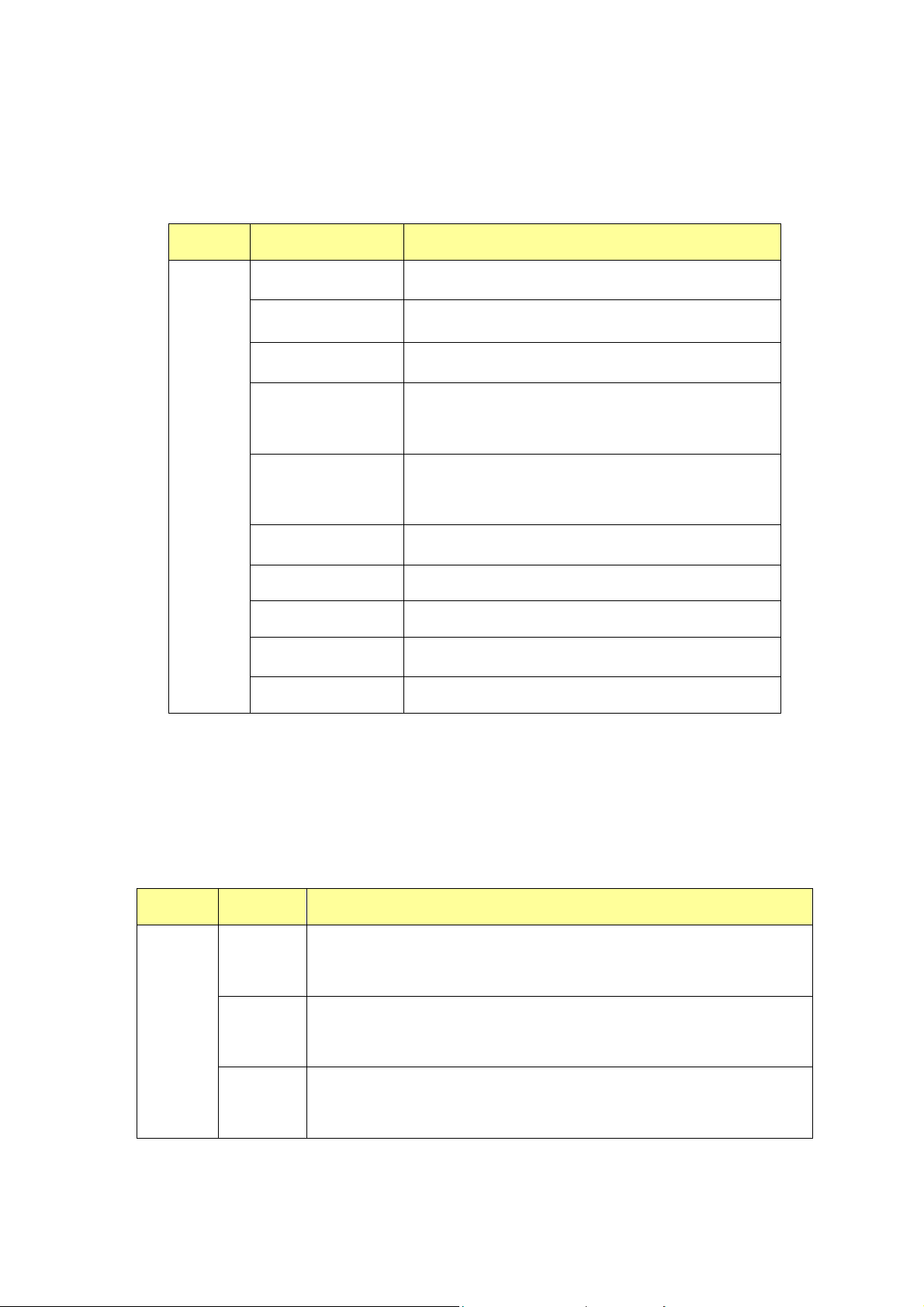

Page Items Comment

Return User OSD

Save Settings

Load Saved Settings

Load Factory Default Load factory default

Load All User Default

Burn In Mode Burn-In mode On/Off

Factory

Burn In Timer Setup hours Set burn-in hours

Burn In Timer Running hours &

minutes

RS232 Baudrate Set baudrate of RS2329600 or 115200

Quit Factory OSD and return user OSD

Save current settings of factory OSD to EEPROM

Load previous saved settings from EEPROM

Restore all settings of user

OSD and PC/HD timing parameters

Running hours of burn-in mode

OSD Timer OSD automatic off time

Usage Hour Record total usage hours of this projector

Software version Software version

49

Page 51

2. HD Adj

This page is the settings of A/D converter. There are 2 sections, one is for RGBHV format

signal (DVI-A input and RGB-HD input), the other is for YPbPr format signal

(Comp-HD input).

Page Items Comment Range

Red Offset A/D converter red offset 0~127

Green Offset A/D converter green offset 0~127

Blue Offset A/D converter blue offset 0~127

RGBHV format

Red Gain A/D converter red gain 0~255

Green Gain A/D converter green gain 0~255

Blue Gain A/D converter blue gain 0~255

Page Items Comment Range

Brightness A/D converter green offset 0~127

Contrast A/D converter green gain 0~255

YPbPr format

3. STD Adj

This page is the settings of video decoder. There are 2 sections, one is for Video and

S-Video input, the other is for component input.

Page Items Comment Range

Saturation A/D converter red and blue gain 0~255

Pb-Offset A/D converter blue offset 0~127

Pr-Offset A/D converter red offset 0~127

Brightness V/D brightness 0~255

Contrast V/D contrast -128~127

Video & S-Video

Saturation V/D saturation -128~127

Hue V/D hue -128~127

50

Page 52

Page Items Comment Range

Brightness V/D brightness 0~255

Component

Contrast V/D contrast -128~127

Saturation V/D saturation -128~127

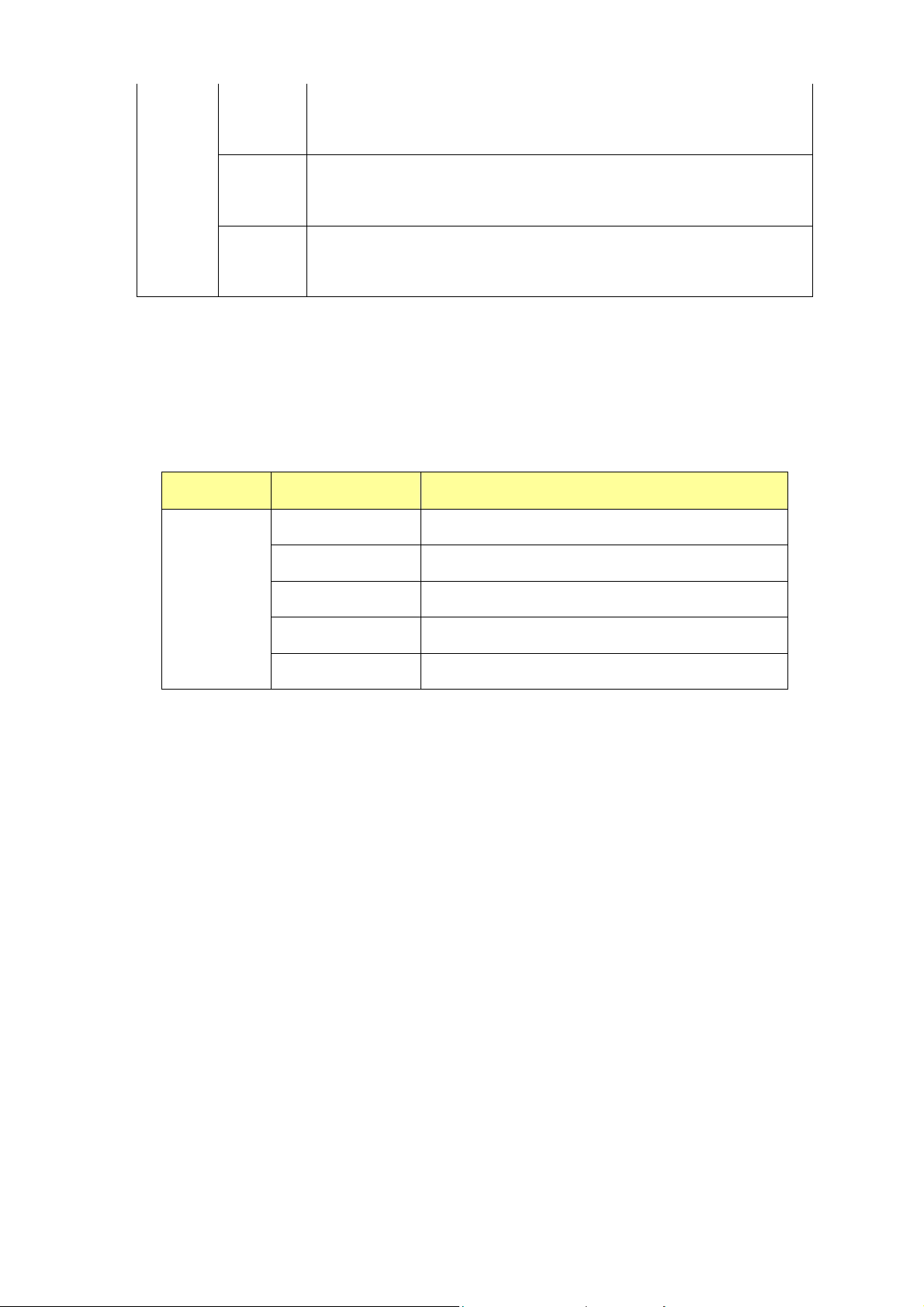

4. Color Balance

For color temperature settings, they are the combination of gamma gain and gamma

offset. This page allows operator to adjust gamma correction to fit the expected color

temperature, and save these settings as one of the color temperature settings. And this

page also provides the function to restore color temperature setting to default gamma

combination.

Page Items Comment Range

Red Adjust the shape of RM-1A gamma curve 0~128

Gamma

Green Adjust the shape of RM-1A gamma curve 0~128

Blue Adjust the shape of RM-1A gamma curve 0~128

Page Items Comment Range

Multiply gamma curve by a gain

1~512

(gain= settings/512)

Multiply gamma curve by a gain

1~512

(gain= settings/512)

Multiply gamma curve by a gain

1~512

(gain= settings/512)

Gamma Gain

Red

Green

Blue

Page Items Comment Range

Red Add an offset value to gamma curve 0~90

Gamma

Offset

Green Add an offset value to gamma curve 0~90

Blue Add an offset value to gamma curve 0~90

51

Page 53

Page Items Comment

Save Data Temp.

Page Items Comment

Save Video Temp.

Save gamma gain and gamm offset

as color temp 9300K

Save gamma gain and gamm offset

as color temp 6500K

Save gamma gain and gamm offset

as color temp 5700K

Restore combination

Save gamma gain and gamm offset as

color temp 9300K

Save gamma gain and gamm offset as

color temp 6500K

Save gamma gain and gamm offset as

For data input (Component >= 480p

signal, DVI-A, and DVI-D)

For data input (Component >= 480p

signal, DVI-A, and DVI-D)

For data input (Component >= 480p

signal, DVI-A, and DVI-D)

Restore default value of gamma

correction

For video input (Component < 480p

signal, Video, and S-Video)

For video input (Component < 480p

signal, Video, and S-Video)

For video input (Component < 480p

5. Filter Bypass

Page Items Comment

Filter Bypass

color temp 5700K

Restore combination

V-in

V-out On/Off status of RM-1A's video output filter

G-in On/Off status of RM-1A's graphics input filter

signal, Video, and S-Video)

Restore default value of gamma

correction

On/Off status of RM-1A's video input filter

52

Page 54

6. DLP

This page allows user to change DLP settings.

Page Items Comment Range

Brightness DLP brightness -64~64

Contrast DLP contrast 0~100

DLP

CW delay DLP color wheel delay 0~1023

Degamma

DLP degamma table 0~6

Table

7.Pattern1

This page allows user to call up DLP present curtains and RM-1A patterns.

Page Items Comment

Red Curtain

Green Curtain DLP present curtain. For CW delay measurement

Blue Curtain DLP present curtain. For CW delay measurement

Black Curtain DLP present curtain. For optical experiment.

Patterns 1

Color Bar RM-1A pattern. For checking gray scale.

DLP present curtain. For CW delay measurement

Checker Board RM-1A pattern. For optical contrast measurement.

13-Points RM-1A pattern. For optical experiment.

Reflective Edge RM-1A pattern. For optical light leakage experiment

53

Page 55

8.Pattern2

This page allows user to call up DLP DDP1010 series present patterns.

Page Items Comment

Patterns 2

Solid Field - Yellow

Solid Field - Cyan

Solid Field - Magenta

Horizontal Ramp

Vertical Ramp

Horizontal Lines

Diagonal Lines DLP DDP1010 present pattern. Monochrome pattern.

Vertical Lines DLP DDP1010 present pattern. Monochrome pattern.

Grid

Checker Board DLP DDP1010 present pattern. Monochrome pattern.

DLP DDP1010 present pattern. For checking color.

DLP DDP1010 present pattern. For checking color.

DLP DDP1010 present pattern. For checking color.

DLP DDP1010 present pattern. Monochrome pattern,

for checking gray scale.

DLP DDP1010 present pattern. Monochrome pattern,

for checking gray scale.

DLP DDP1010 present pattern. Monochrome pattern.

DLP DDP1010 present pattern. Monochrome pattern.

9.Pattern3

This page allows user to call up DLP DDP1010 series present patterns, the major goal

of this page is for DMD inspection.

Page Items Comment

DLP DDP1010 present pattern. For inspection of 'major dark blemish' and

Patterns 3

Blue 90

'dark pixel' on DMD chip.

DLP DDP1010 present pattern. For inspection of 'border defects' on DMD

Gray 10

chip.

DLP DDP1010 present pattern. For inspection of 'major light blemish' and

Gray 6

light pixel' on DMD chip.

54

Page 56

White Full

Black Full

Red Ramp

DLP DDP1010 present pattern. For inspection of 'minor blemishes' on

DMD chip.

DLP DDP1010 present pattern. For inspection of 'minor blemishes' on

DMD chip.

DLP DDP1010 present pattern. For inspection of 'unstable pixel' on DMD

chip.

10 . Test Mode

For different situation, we need different settings. Here we define 5 kinds of settings in

‘Picture Adjust’ page to fit some situations.

Page Items Comment

Optical Test High brightness, high contrast, high saturation

Test Mode

Middle Value All settings in the middle value

Play DVD Optimal settings for watching DVD

Color Wheel Delay Low brightness, high contrast, high saturation

Blue Filter Only 'blue' is left, for 'color' and 'tint' adjustment

55

Page 57

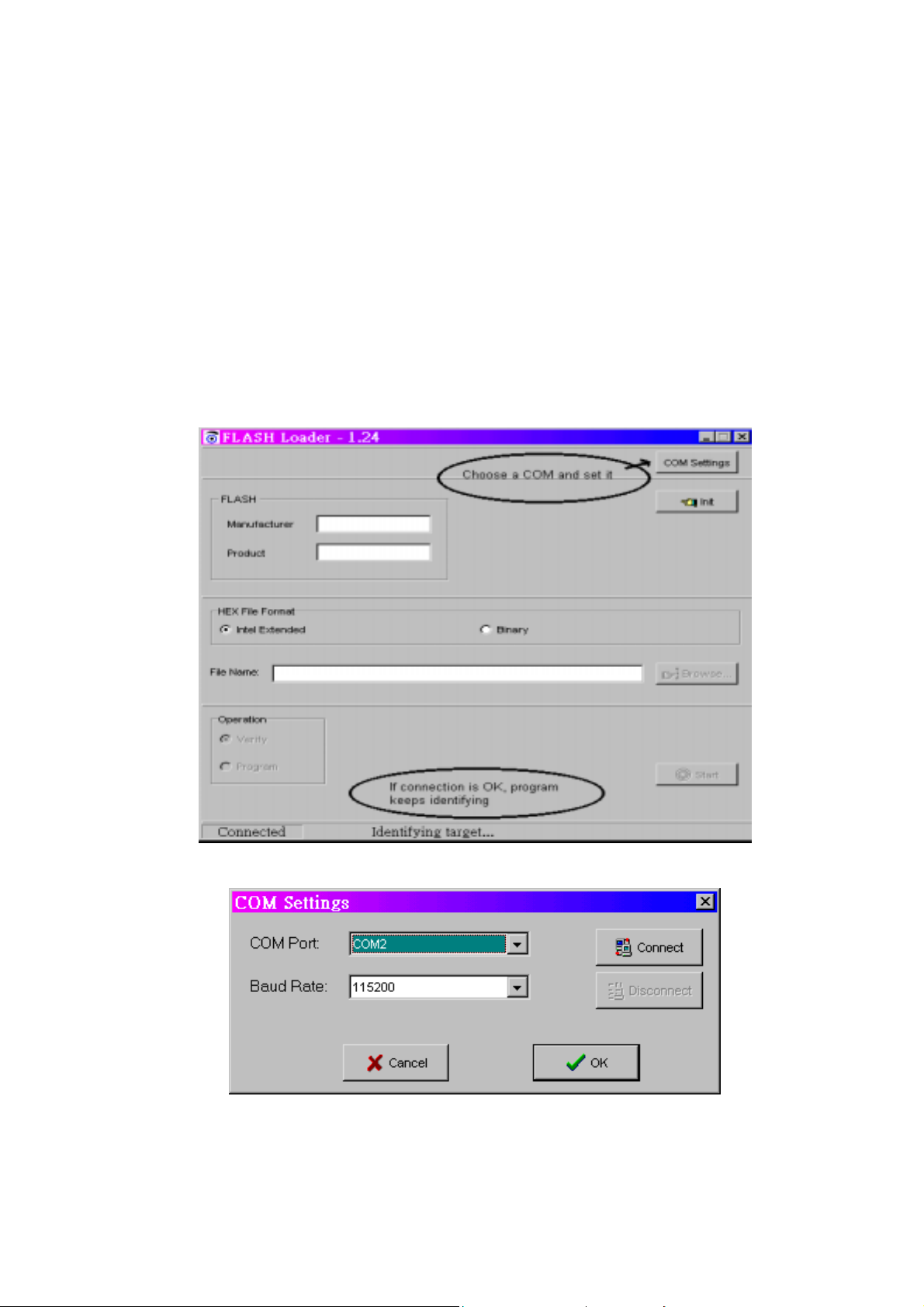

11. Firmware Upgrade Procedure

1. Connect specific download cable to RS232 (RJ-11) connector. Remember to turn the

AC switch off.

2. Execute the ‘Flash Loader’ program. If the ‘COM Settings’ item is ready, you can see

‘Identifying target…’ at the bottom of flash loader. If not, open ‘COM Settings’ item.

Choose the ‘COM Port’ you use, always set the baud rate 115200, then press ‘Connect’

and ‘OK’ button. The program returns to its main page, and ‘Connected’ and ‘Identifying

target’ are supposed to be displayed at the bottom of the flash loader.

56

Page 58

3. Turn the AC switch on. In 3 seconds, ‘flash loader’ will identify the flash ROM of this

unit. Choose ‘Hex File Format’ as ‘Intel Extended’, ‘Operation’ as ‘Program’, and

‘Browse’ the ‘File Name’. After that, press the ‘Start’ button. ‘Flash Loader’ starts to

load program to Flash ROM.

4. After download procedure finished, remove download cable and turn the AC switch off.

Then the user can operate this machine in normal condition.

5. The hex file to be loaded, the format of its name is

BenQ_PE8700_RM1A_Ver102_20030619.hex

I. II. III. IV. V.

I. Brand name

II. Model name

III. Scaler type

IV. Version of SW

V. Released date

57

Page 59

12. RS232 Codes

1. Set up peripherals

BenQ PE8700 provides an RJ-11 connector for RS232 serial communication control. The

user can use the ‘Hyper Terminal’ program of Microsoft Windows to control this unit.

To set the settings of serial port first is necessary. Choose which COM port you want

to connect, and set its settings as below:

Baud Rate: 115200 or 9600

Parity: None

Data bits: 8

Stop bits: 1

Flow Control: None

For baud rate setting, it depends on the settings in our \Factory OSD\FACTORY\RS232

BAUDRATE\ 9600 or 115200.

58

Page 60

After settling down, connect our specific RS232 cable and press the ‘call’ icon of ‘Hyper

Terminal’ program. After this, press ‘Enter’ key, if an ‘>’ symbol come up, that means the unit

is ready to accept commands for computer.

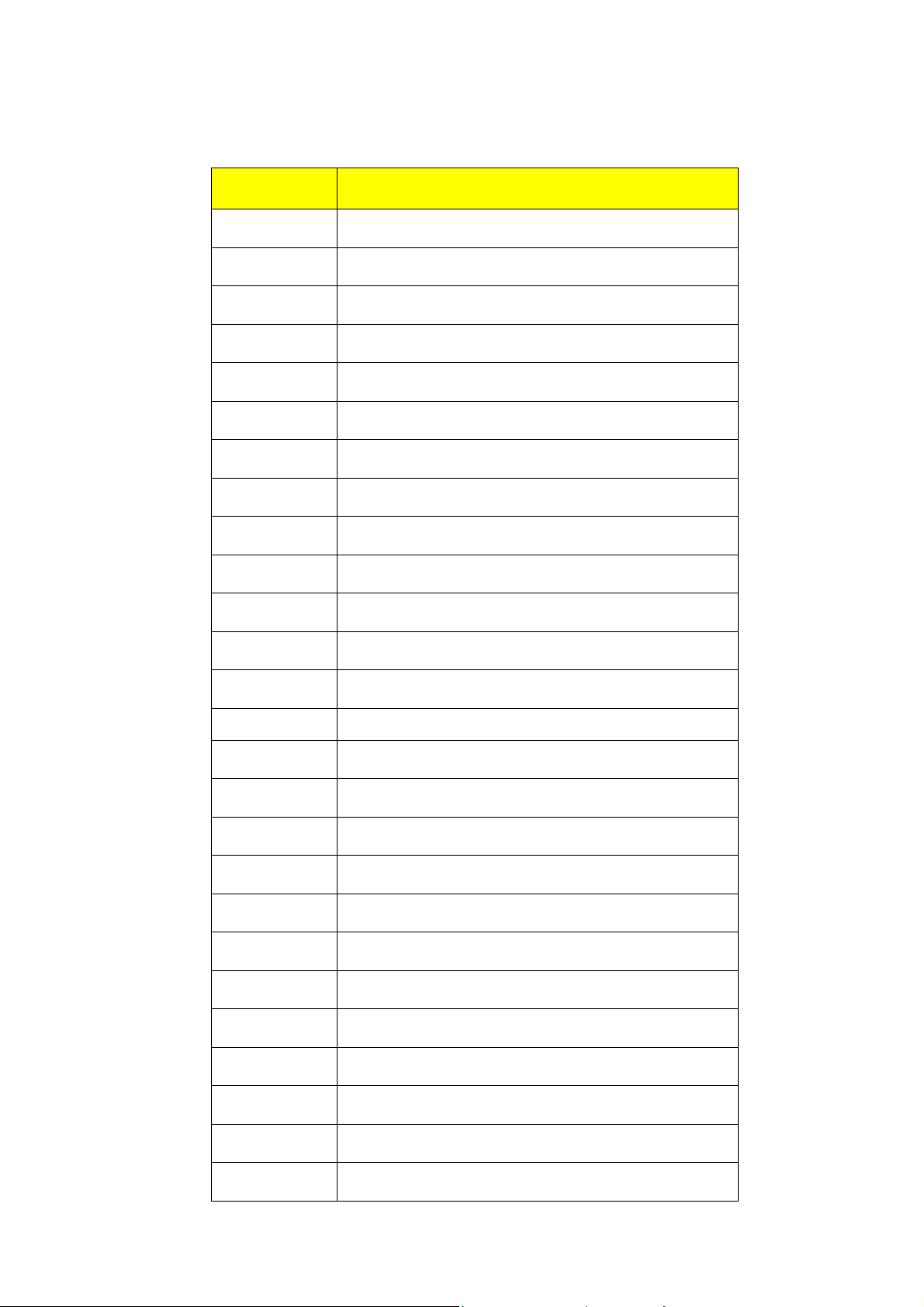

2. Commands list

There are 3 kinds of serial commands, X-group, Y-group and Z-group.

For X-group, these functions are public. Any end-user can control the unit by these

commands, as long as they set correct RS232 communication. Following table is the codes

list of X-group command.

59

Page 61

Code Function

X00 Must be Reversed , no function

X01 Power On

X02 Power Off

X03 Message On

X04 Message Off

X05 Lamp hours reset

X06 Load all user OSD default value

X07 Save current active source settings

X08 Change active OSD

X10 Menu

X11 Enter

X12 Exit

X13 Up(arrow key)

X14 Down(arrow key)

X15 Left(arrow key)

X16 Right(arrow key)

X20 Switch to Composite input

X21 Switch to S-Video input

X22 Switch to Component input

X23 Switch to Dsub_PC input

X24 Switch to YPbPr input

X25 Switch to BNC_PC input

X26 Switch to DVI input

X27 Switch to DVI_I input

X30 4:3 screen

X31 16:9 screen

X35 Aspect - Anamorphic

60

Page 62

X36 Aspect - Standard (4:3)

X37 Aspect - Letter box

X38 Aspect - Virtual wide

X39 Aspect - Through

X40 Load memory 1 settings

X41 Load memory 2 settings

X42 Load memory 3 settings

X43 Load 'optical test' mode settings

X44 Load 'middle' mode settings

X45 Load 'CW delay adjustment' mode settings

X46 Load default of current source

X47 Save memory 1 settings

X48 Save memory 2 settings

X49 Save memory 3 settings

X50 Scale up

X51 Scale down

X55 Switch active source

X56 Picture in picture display

X57 Picture by picture display

X60 Switch language 1

X61 Switch language 2

X62 Switch language 3

X63 Switch language 4

X64 Switch language 5

X65 Switch language 6

X66 Switch language 7

X67 Switch language 8

X85 PC input - auto

61

Page 63

X90 Image orientation - floor front

X91 Image orientation - ceiling front

X92 Image orientation - floor rear

X93 Image orientation - ceiling rear

X94 Back light board On

X95 Back light Board Off

X99 On line help

When an user sends a command, he must follow the command format in the list. After

he sends a command, program will acknowledge 2 pieces of information. This information,

we call it ‘ACK’ in the following content.

The format of first ACK is XnX

The length is 3, first and last characters are always be X. And the number ‘n’ is 0, 1 or

2. The explanation of n is

0: Right command format and function

1: Illegal format

2: Illegal function

So, if the user presses XA85, this one is wrong format, ACK will be X1X.

And if the user presses X98, because this function is not included in our command

table, ACK will be X2X.

For above situation, program sends the user an ACK, then waiting for a new

command.

If the user presses correct command, take an example, X35, first ACK, X0X will send

to the user. That tells the user it’s a right command. Then program starts to deal with this

command, and changes the aspect ratio to ‘anamorphic’ mode. When finish, the user will

receive 2nd ACK. The format is Xn_ccX

The length is 6. First and last characters are X, second character is the ACK, followed

by a ‘_’ character. ‘cc’ is the function number. So, in this case, the 2nd ACK is X0_35X. And

the user can continue to send next command.

For Y-group, this one is for our factory, not public. When our operators send

commands to the unit, the ACK format is identical as X-group, difference is only ‘Y’ instead

of ‘X’.

62

Page 64

Following is the list of Y-group:

Code Function

Y01 Save current factory settings

Y02 Load saved factory settings

Y03 Load factory default

Y04 Load all user default

Y05 Burn-In mode on

Y06 Burn-In mode off

Y07 Set RS232 baudrate as 9600

Y08 Set RS232 baudrate as 115200

Y10 Save as data color temperature 1

Y11 Save as data color temperature 2

Y12 Save as data color temperature 3

Y20 Save as video color temperature 1

Y21 Save as video color temperature 2

Y22 Save as video color temperature 3

Y30 Restore data color temperature to default

Y31 Restore video color temperature to default

Y32 Restore white balance settings to default

Y40 DMD -- Degamma table 0

Y41 DMD -- Degamma table 1

Y42 DMD -- Degamma table 2

Y43 DMD -- Degamma table 3

Y44 DMD -- Degamma table 4

63

Page 65

Y52 Red Curtain

Y53 Green Curtain

Y54 Blue Curtain

Y55 Black Curtain

Y57 Color Bar

Y58 Chess Board

Y59 Optical 13-point

Y60 Reflective Edge

Y61 Grid

Y62 Blue 90 Curtain

Y63 Gray 10 Curtain

Y64 Gray 6 Curtain

Y65 Full White Curtain

Y66 Full Black Curtain

Y67 Red Ramp Curtain

Y68 Gray 20 Curtain

Y70 Load 'optical test' mode settings

Y71 Load 'middle value' mode settings

Y72 Load 'Play DVD' mode settings

Y73 Load 'CW delay adjustment' mode settings

Y74 Load 'Blue filter' mode for color and tint adjustment

Y80 Load default for factory auto alignment procedure

Y81 Save corresponding settings after auto alignment

Y98 Display version

Y99 On line help

64

Page 66

Example:

1. Command = Y89893 (Enter)

ACK = Y1Y (Illegal format, wrong length)

2. Command = Y98 (Enter)

ACK = Y2Y (Illegal function)

3. Command = Y52 (Enter)

st

ACK = Y0Y

1

2nd ACK = Y0_52Y

For Z-group, this one is for ‘auto-alignment’ procedure in our factory. This one allows

engineers to read or write the unit settings without OSD operation, it will save time to set

the value. Following is the table of Z-group.

Code Function

Z001 Brightness adjustment

Z002 Contrast adjustment

Z003 Color adjustment

Z004 Sharpness adjustment

Z005 Tint adjustment

Z006 Color temperature adjustment

Z007 Filters adjustment

Z008 Independent color control - Red adjustment

Z009 Independent color control - Green adjustment

Z010 Independent color control - Blue adjustment

Z011 Independent color control - Yellow adjustment

Z012 DMD white peaking adjustment

Z020 Frequency adjustment

Z021 Phase adjustment

Z022 H - Position adjustment

Z023 V - Position adjustment

65

Page 67

Z030 Keystone adjustment

Z034 RGBHV input -- Red offset

Z035 RGBHV input -- Green offset

Z036 RGBHV input -- Blue offset

Z037 RGBHV input -- Red gain

Z038 RGBHV input -- Green gain

Z039 RGBHV input -- Blue gain

Z042 YPbPr input -- Brightness

Z043 YPbPr input -- Contrast

Z044 YPbPr input -- Saturation

Z045 YPbPr input -- Pb Offset

Z046 YPbPr input -- Pr Offset

Z050 CVBS & S-Video -- Brightness

Z051 CVBS & S-Video -- Contrast

Z052 CVBS & S-Video -- Saturation

Z053 CVBS & S-Video -- Hue

Z054 Component -- Brightness

Z055 Component -- Contrast

Z056 Component -- Saturation

Z060 Gamma--Index

Z061 Gamma--Red

Z062 Gamma--Green

Z063 Gamma--Blue

Z064 Gamma gain -- Red

Z065 Gamma gain -- Green

Z066 Gamma gain -- Blue

Z067 Gamma offset -- Red

Z068 Gamma offset -- Green

66

Page 68

Z069 Gamma offset -- Blue

Z070 DMD -- Brightness

Z071 DMD -- Contrast

Z072 DMD -- Color Wheel Delay

Z073 DMD -- Degamma table

Z080 Burn-in hours

Z099 On line help

The length of the command must be 11. The format, take an example, to read DMD

color wheel delay:

Z072RxxxxxZ, where

Byte 1: must be 'Z' or 'z'

Byte 2~4: function code

Byte 5: action, must be ‘r’ or ‘R’

Byte 6~10: Don’t care

Byte 11: must be 'Z' or 'z'

In contrast, if write DMD color wheel delay:

Z072W+0025Z, where

Byte 1: must be 'Z' or 'z'

Byte 2~4: function code

Byte 5: action, must be ‘w’ or ‘W’

Byte 6: sign byte, must be ‘-‘ or ‘+’

Byte 7~10: the value to be written

Byte 11: must be 'Z' or 'z'

67

Page 69

And the length of ACK must be 12, and format is

Z0_072+0025Z

Byte 1: Always ‘Z’

Byte 2: ACK

Byte 3: Always ‘_’

Byte 4~6: function code

Byte 7: sign byte, ‘+’ or ‘-‘

Byte 8~11: the current value after writing

Byte 12: Always ‘Z’

And ‘ACK’ value is

0: Right command and function

1: Illegal Format

2: Illegal Function

3: Illegal Action,

4: Illegal Adjusted Situation,

5. Written value is over up limit,

6. Written value is over down limit

If the ACK is 0, 5, 6, program will deal this command. If ACK = 5, program writes the legal

maximum value to the setting. If ACK = 6, writes the legal minimum value to the setting.

68

Page 70

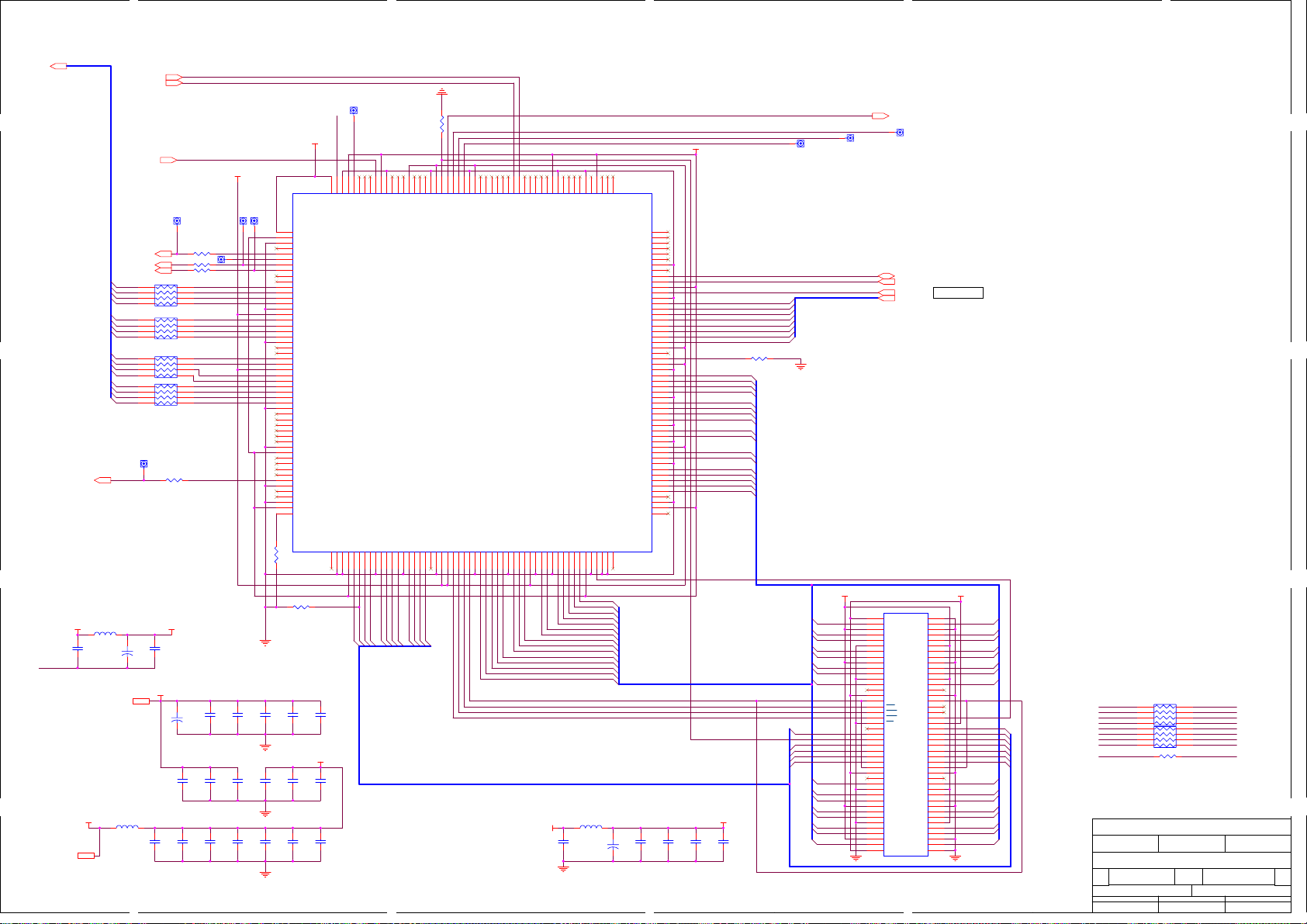

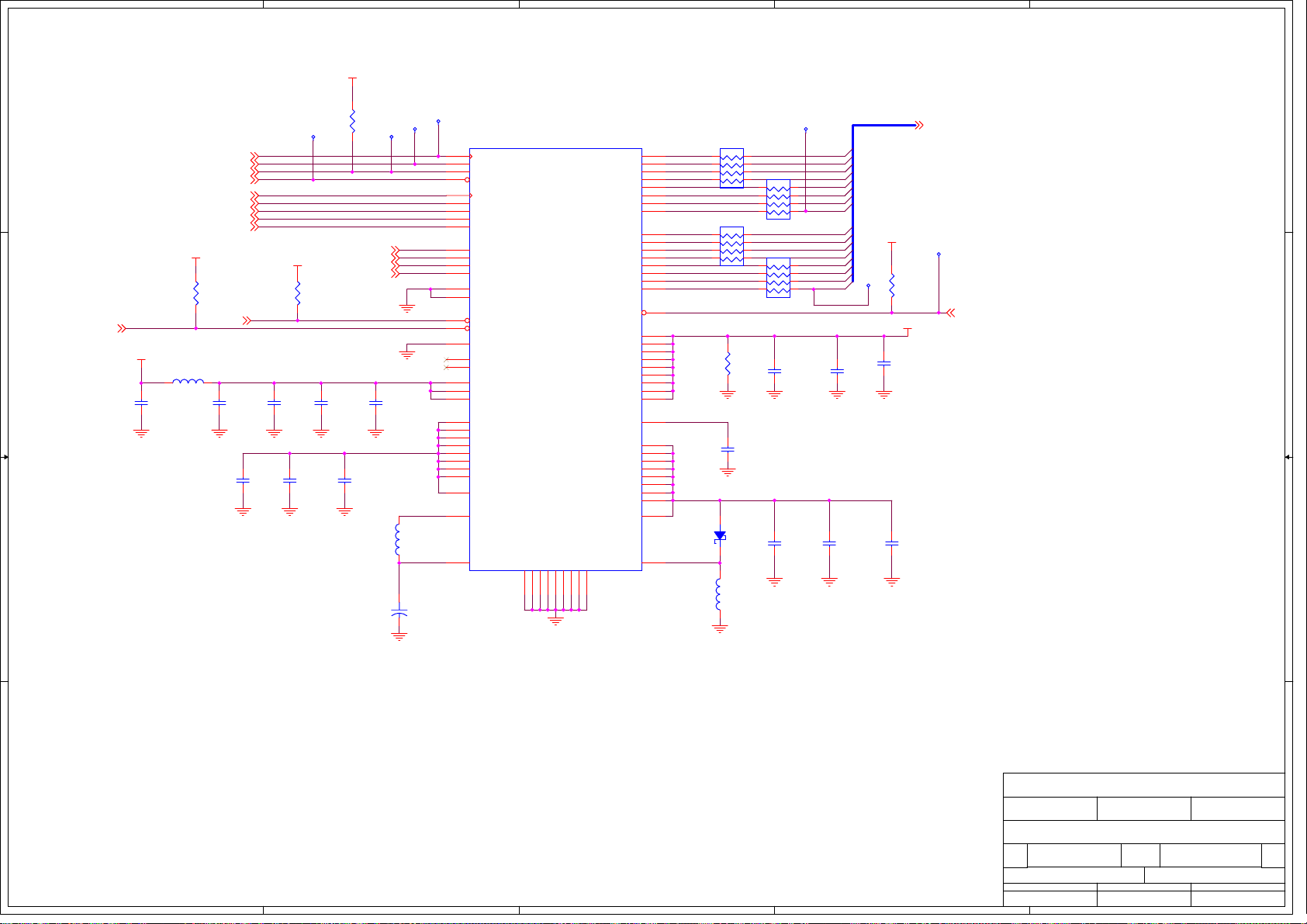

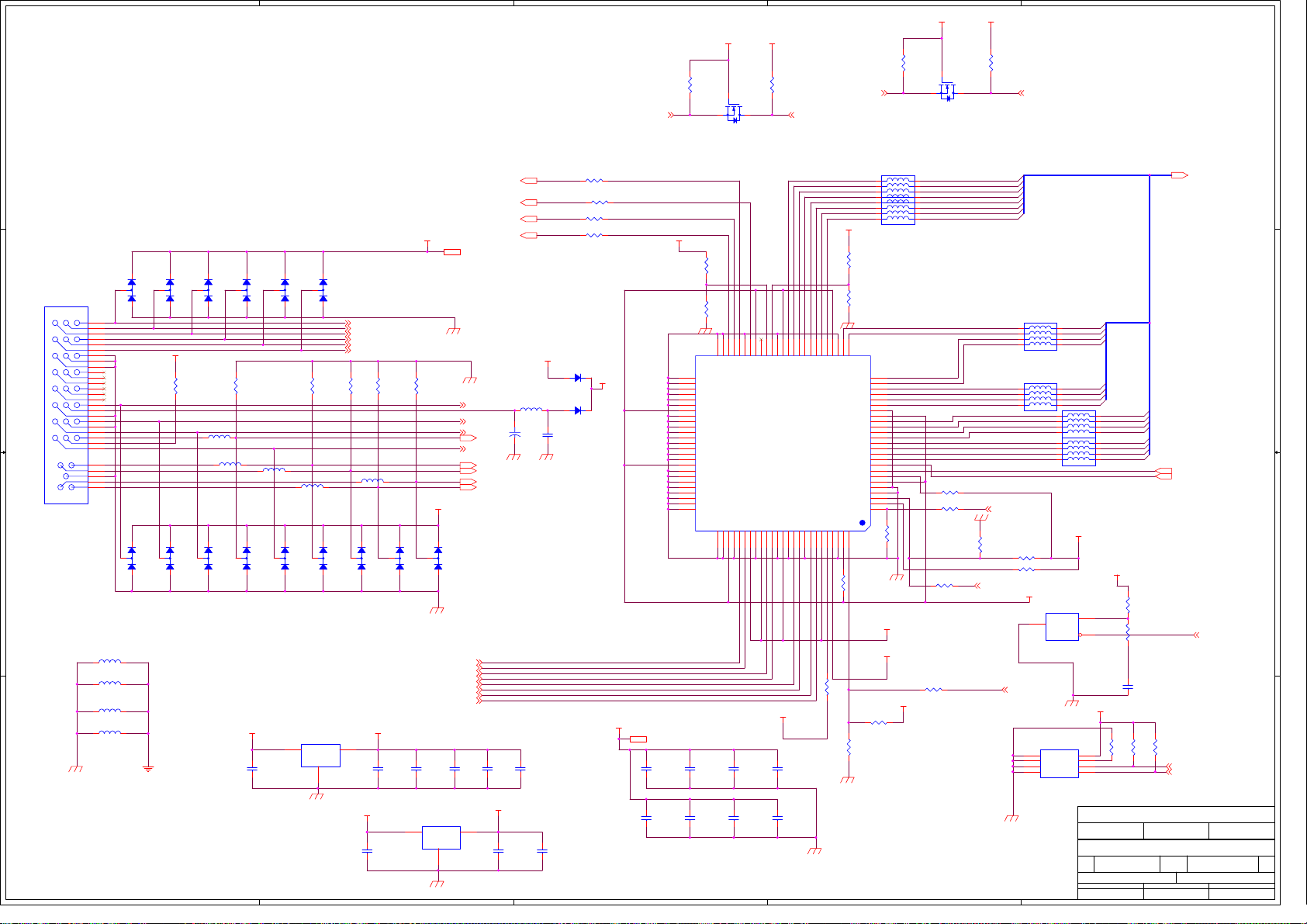

5

120-Pin B2B Connectors

D D

C C

TP7

E1

1

SII141_PDO

B B

A A

TRIGGER

RM1_RST_N

MUX_SEL

+12VA +3VA+5VA+5VS +1_8V

SPAREI

SPAREO

SII141_PDO

TRIGGER

RM1_RST_N

MUX_SEL

SPAREI

SPAREO

+3VA

+5VA

+12VA

+1_8V

+5VS

1_120Pin B2B Connectors

5

D_INA[0..23]

D_VSYNC

D_HSYNC

DIN_CLK

DVI_SCDT

DI_IN[2..9]

DI_27M_CLK

DI_VSYNC

DI_HSYNC

CPU_RXD0

CPU_TXD0

MUX_SEL_P

MUX_BUFFER

DVI_ACTDATA

MUX_SEL_Q

DVI_SCDT

+3VA

DI_IN[2..9]

DI_27M_CLK

DI_VSYNC

DI_HSYNC

+1_8V+3VA

DEINTDONE

RESET_DVDO

TP20

TP18

TP19

E1

E1

E1

1

1

1

SCL

SDA

IR

1

1

TP8

TP9

E1

E1

+5VA+3VA

TP17

E1

1

1

TP15

E1

D_INA[0..23]

D_VSYNC

D_HSYNC

DIN_CLK

+3VA

8_SDRAM 64MBit x 3

SDRAM 64MBit x 3

Sil503_Deinterlacer

DI_IN[2..9]

DI_27M_CLK

DI_VSYNC

DI_HSYNC

RESET_DVDO

DEINTDONE

+1_8V

+3VA

2_Sil504_Deinterlacer

MCU503 Controller

DEINTDONE

+5VA

+3VA

3_MCU503 Controller

4

4

MEM_DQ[0..79]

MEM_A[0..11]

MEM_RAS_N

MEM_CAS_N

MEM_BS

MEM_CLK

MEM_WE_N

MEM_CS_N

MEM_DQM_L

MEM_DQM_U

V_IN[0..15]

V_ACTIVE

V_VSYNC

V_HSYNC

VCLK

DI_SDA

DI_SCL

DI_SCL

DI_SDA

MCURESETRESET_DVDO

DMD_SDA

DMD_SCL

3

TP4

TP2

TP3

TP1

E1

E1

E1

E1

SCL

SDA

CPU_RXD0

CPU_TXD0

MUX_SEL_P

MUX_BUFFER

MUX_SEL_Q

IR

3

TP11

E1

CPU_A1

CPU_A2

CPU_A3

CPU_A4

MCURESET

TRIGGER

SII141_PDO

MUX_SEL

DVI_SCDT

RM1_RST_N

1

CPU_RD_N

CPU_D[0..7]

CPU_A[0..7]

RM1_WR_N

RM1CLKIN

RM1_CS_N

RM1_IRQ

1

1

+12VA +5VS+3VA +3VS+5VA

CPU_D[0..7]

1

1

OP_A[0..23]

OP_VSYNC

OP_HSYNC

OP_ENABLE

OCLK_OUT

OP_FIELD

+3VS

CPU_RD_N

CPU_FLASH_SRAM

CPU_RD_N

CPU_D[0..7]

CPU_A[0..7]

RM1_WR_N

RM1CLKIN

RM1_CS_N

RM1_IRQ

SCL

SDA

CPU_RXD0

CPU_TXD0

MUX_SEL_P

MUX_BUFFER

BACKLIGHT_CTRL

MUX_SEL_Q

IR

5_CPU_FLASH_SRAM

80 Pin Connector to DLP

OP_A[0..23]

OP_VSYNC

OP_HSYNC

OP_ENABLE

OCLK_OUT

OP_FIELD

+5VS

+3VS

+12VA

+5VA

+3VA

I/O

CPU_A1

CPU_A2

CPU_A3

CPU_A4

MCURESET

TRIGGER

SII141_PDO

MUX_SEL

DVI_SCDT

RM1_RST_N

+3VS

CPU_RD_N

CPU_D[0..7]

6_I/O

SPAREI

SPAREI

SPAREO

SPAREO

CPU_PCS0_N

CPU_WR_N

CPU_PCS0_N

CPU_WR_N

CPU_WR_N

CPU_PCS0_N

DLP_SPARE

DLP_SPARE

DLP_SPARE

RESETVCC

RESETVCC

WRITE_PROT

RESETVCC

RESET_N

WRITE_PROT

RESET_N

RESET_N

WRITE_PROT

RM1

D_INA[0..23]

D_VSYNC

D_HSYNC

DIN_CLK

MEM_DQ[0..79]

MEM_A[0..11]

MEM_RAS_N

MEM_CAS_N

MEM_BS

MEM_CLK

MEM_WE_N

MEM_CS_N

MEM_DQM_L

MEM_DQM_U

V_IN[0..15]

V_ACTIVE

V_VSYNC

V_HSYNC

V_CLK

DI_SCL

DI_SDA

MCURESET

DMD_SDA

DMD_SCL

SCL

SCL

SDA

SDA

DVI_ACTDATA

+1_8V

MEM_DQ[0..79]

MEM_A[0..11]

MEM_RAS_N

MEM_CAS_N

MEM_BS

MEM_CLK

MEM_WE_N

MEM_CS_N

MEM_DQM_L

MEM_DQM_U

V_IN[0..15]

V_ACTIVE

V_VSYNC

V_HSYNC

VCLK

+3VA

+3VA

+1_8V

4_RM1

DVI_ACTDATA

OP_A[0..23]

OP_VSYNC

OP_HSYNC

OP_ENABLE

OCLK_OUT

OP_FIELD

RM1_RST_N

CPU_RD_N

CPU_D[0..7]

CPU_A[0..7]

RM1_WR_N

RM1CLKIN

RM1_CS_N

RM1_IRQ

BACKLIGHT_CTRL

2

DLP

Connector/POWER

SYNCVALID

BALLAST_CTRL

TP6

E1

POWERON

POWERON

KEYPAD[0..9]

1

SYNCVALID

BALLAST_CTRL

SYNCVALID

BALLAST_CTRL

LAMP_PROTECT

BACKLIGHT_CTRL

SYNCVALID

BALLAST_CTRL

LAMP_PROTECT

TP16

E1

1

CPU

2

POWERON

DLP_RESETZ

KEYPAD[0..9]

SCL

SDA

DLP_RESETZ

TP13

E1

1

DLP_RESETZ

POWERON

KEYPAD[0..9]

LAMP_PROTECT

SCL

SDA

BACKLIGHT_CTRL

KEY_LED2

FAN_CTRL

KEY_LED2

FAN_CTRL

KEY_LED2

FAN_CTRL

DMD_SCL

DMD_SDA

POWER

LAMPLIT