Page 1

A

1 1

B

C

D

E

Compal Confidential

2 2

NTV00

LA-5661 Rev 0.4 Schematics

3 3

Intel PineView Processor/ Tiger point

2009-12-08 REV : 0.4

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2009/11/10 2010/11/10

2009/11/10 2010/11/10

2009/11/10 2010/11/10

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

NTV00 LA5661P M/B

NTV00 LA5661P M/B

NTV00 LA5661P M/B

1 35Tuesday, December 08, 2009

1 35Tuesday, December 08, 2009

1 35Tuesday, December 08, 2009

E

0.4

0.4

0.4

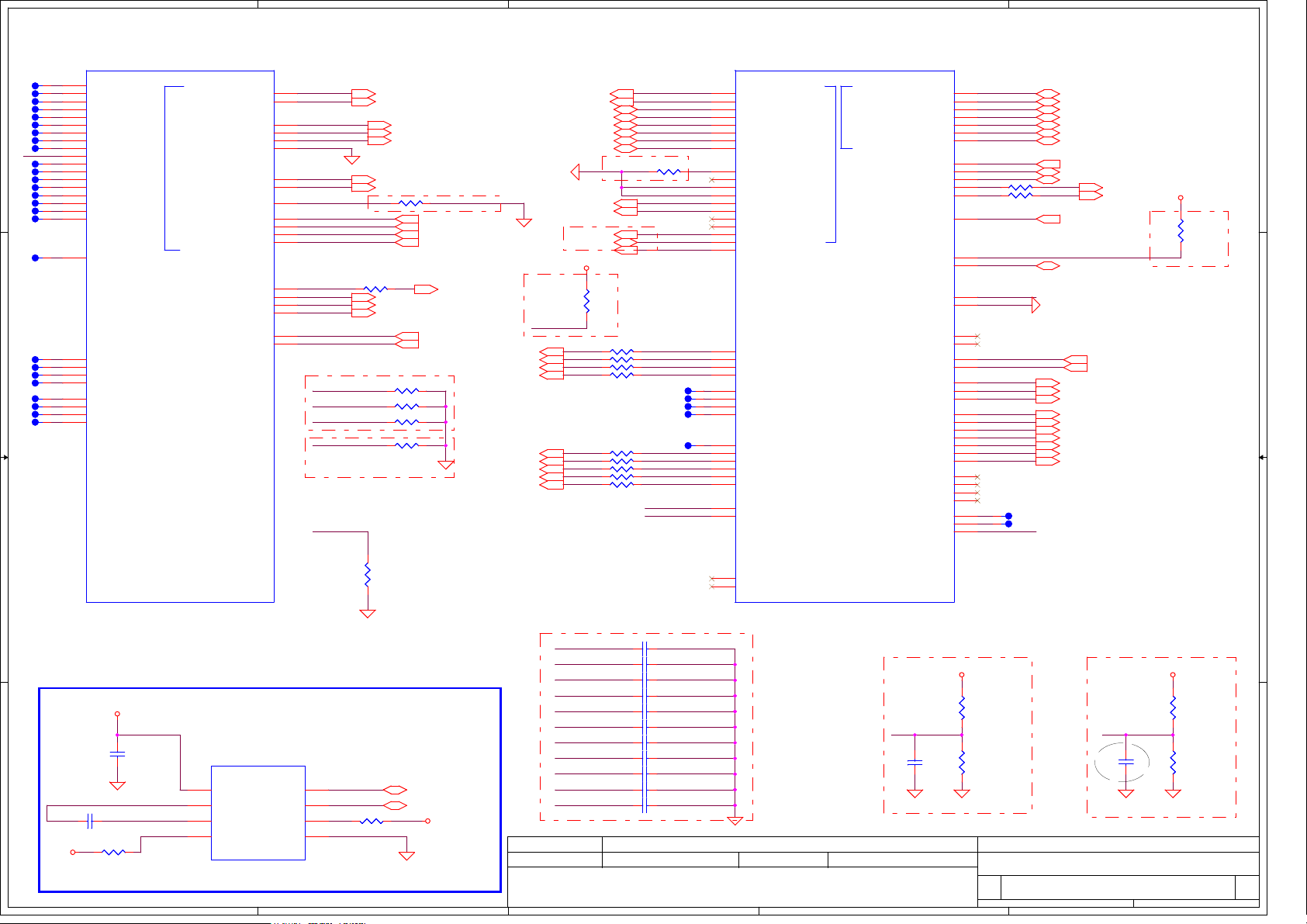

Page 2

A

Compal Confidential

B

C

D

E

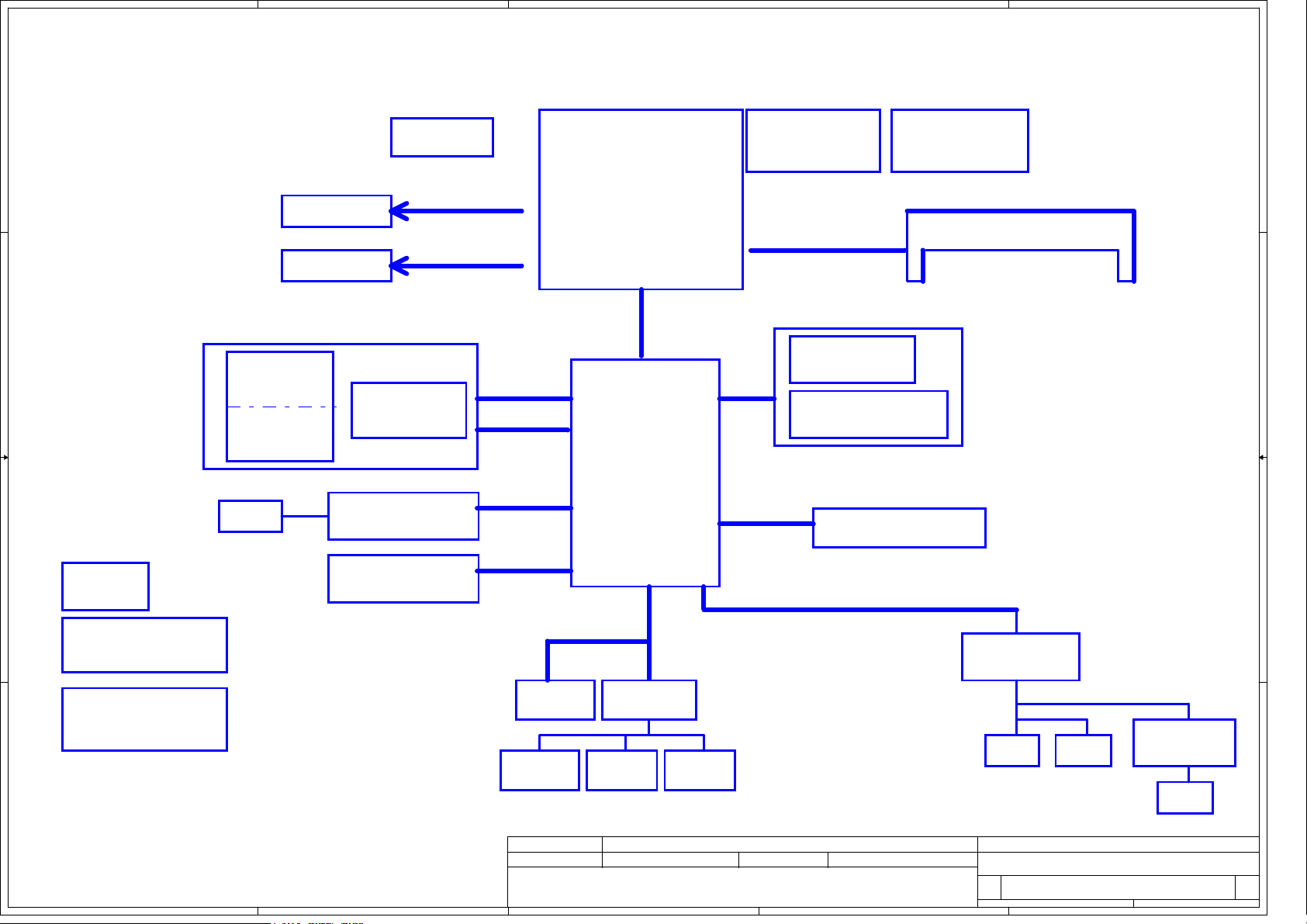

Model Name :

File Name :

1 1

2 2

3 3

RTC CKT.

page 13

NTV00

LA-5661P

PCIeMini Card

WiMax

USB port 6

page 15

PCIeMini Card

WLAN

RJ45

page 20

PCIe port 2

page 15

CRT Conn.

page 10

LCD Conn.

page 9

PCIeMini Card

3G

RTL8103EL 10/100M

Card Reader

RTS5159 2IN1

USB port 3

Fan Control

PCIe port 3

page 23

LVDS

ONE CHANNEL

USB port 5

page 15

page 20

page 21

DMI x 2

USB

5V 480MHz

PCIe 1x [2,4]

1.5V 2.5GHz(250MB/s)

PCIe 1x

1.5V 2.5GHz(250MB/s)

USB

5V 480MHz

Intel Pineview-M

(22x22mm)

page 4,5,6

Tiger Pointer

(17x17mm)

page 11,12,13,14

Thermal Sensor

EMC1402

Memory BUS(DDRII)

1.8V DDRII 667

USB Conn X3

USB port 0,1,4

USB

5V 480MHz

SATA port 0

5V 1.5GHz(150MB/s)

HD Audio

BT conn

USB port 2

3.3V 24.576MHz/48Mhz

page 5

page 16

page 17

SATA HDD

Clock Generator

SLG8SP556VTR

page 8

200pin DDRII-SO-DIMM

page 17

page 7

DC/DC Interface CKT.

3.3V 33 MHz

page 25

Power Circuit DC/DC

page 27~34

Debug Port

page 23

Touch Pad

page 24

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

ENE KB926 D3

Int.KBD

page 23

LPC BUS

page 22

SPI ROM

page 23

Compal Secret Data

Compal Secret Data

2009/11/10 2010/11/10

2009/11/10 2010/11/10

2009/11/10 2010/11/10

C

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

HDA Codec

ALC272-GR

page 18

AMP.

E

TPA6017

page 19

SPK CONN

page 19

2 35Friday, November 20, 2009

2 35Friday, November 20, 2009

2 35Friday, November 20, 2009

MIC CONN

page 18 page 18

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

HP CONN

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

NTV00 LA5661P M/B

NTV00 LA5661P M/B

NTV00 LA5661P M/B

0.4

0.4

0.4

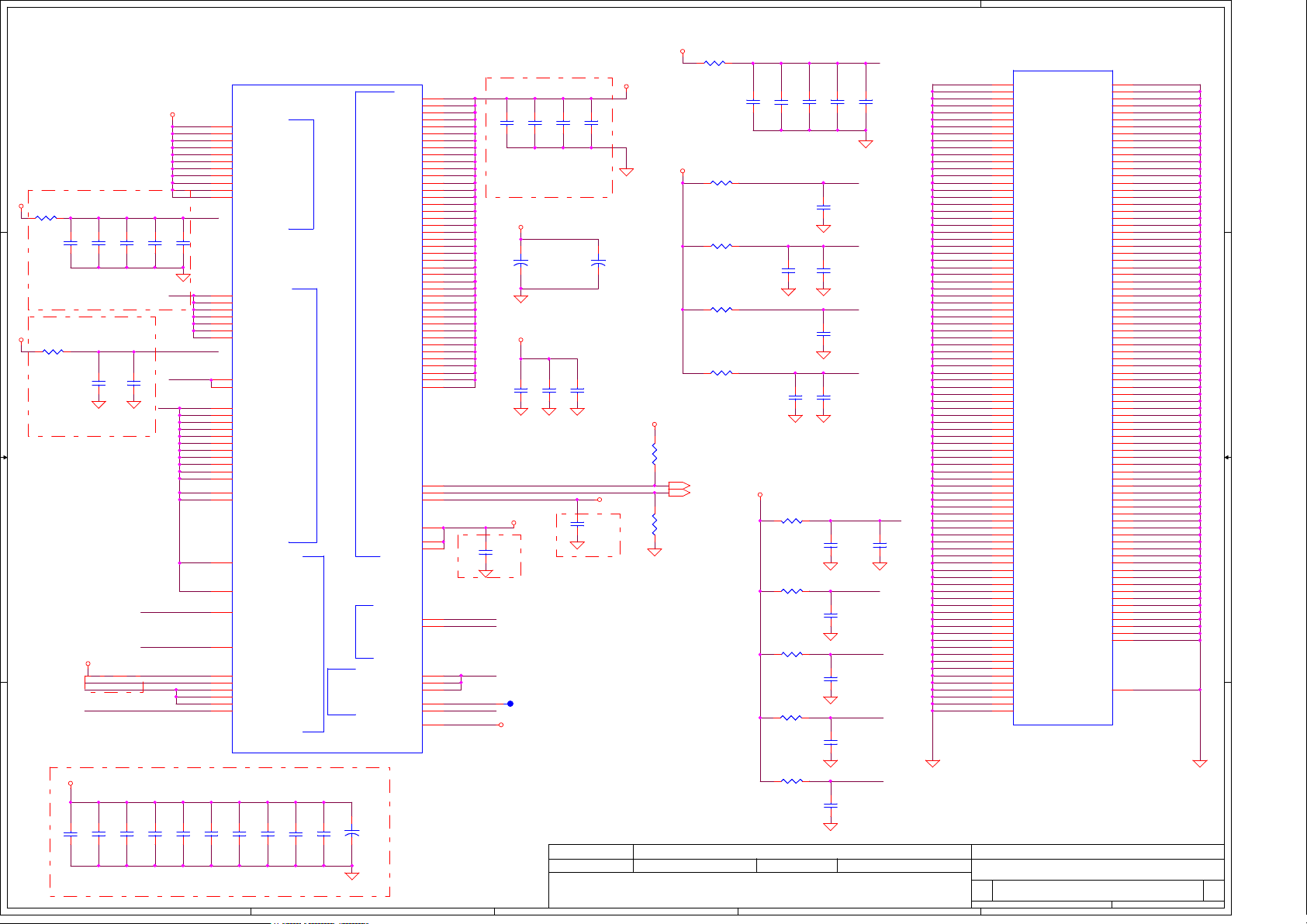

Page 3

A

B

C

D

E

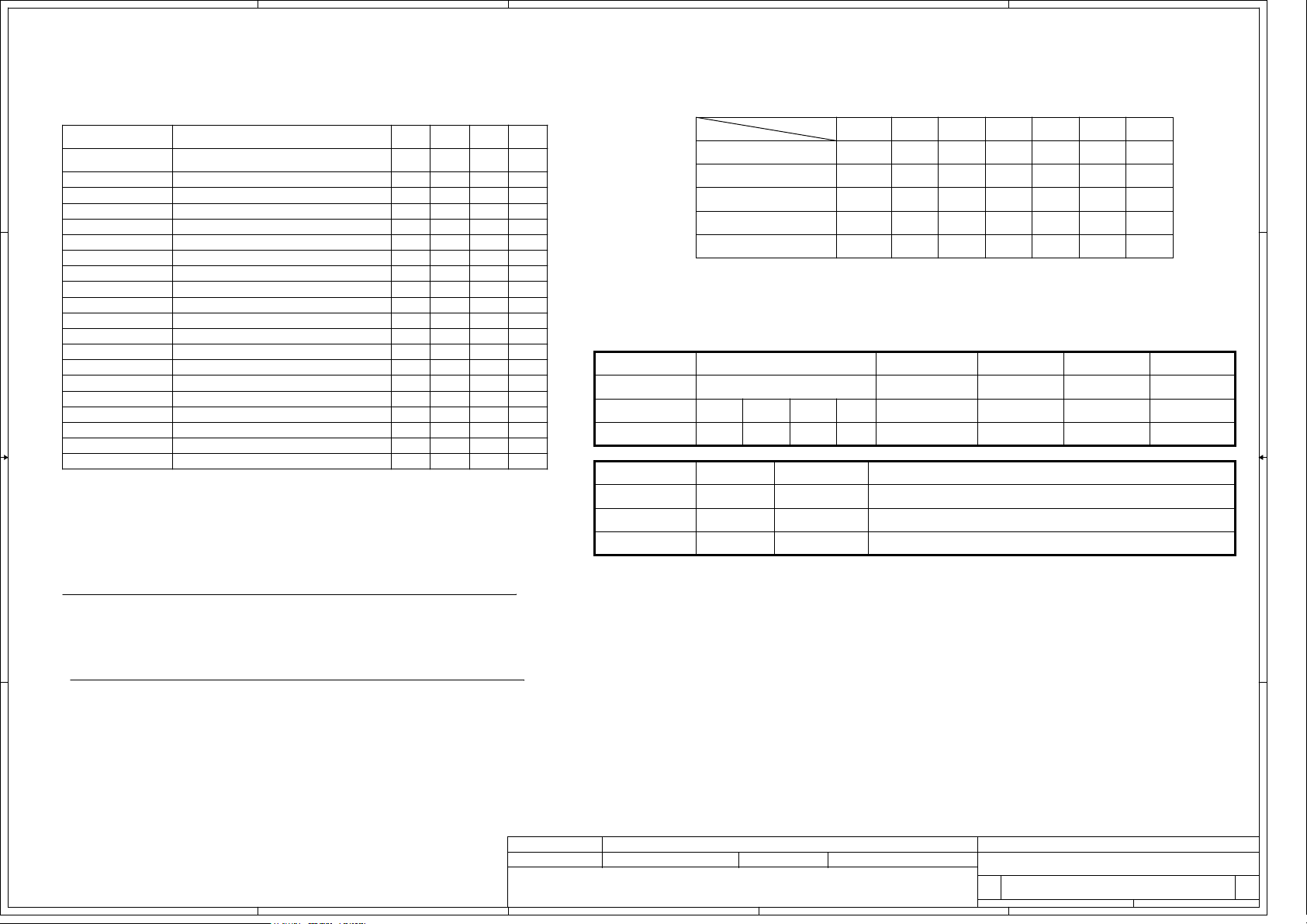

Voltage Rails

1 1

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF1.5V switched power rail

OFF

OFF

OFF

OFF

OFF

ON

OFF

OFF

OFFONOFF

ONON ONON

OFF

OFF

OFF

ON

OFF

OFF

OFF

ONON

OFF

G3

BTO Option Table

Function

description

explain

BTO

Power Plane

VIN

B+

+CPU_CORE

+0.89VS

+0.9VS

+1.05VS

Description

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

0.89VS GFX support voltage

0.9V switched power rail for DDR terminator

VCCP switched power rail

+1.5VS

+1.8V

+1.8VS

+3VALW

+3V_SB

1.8V power rail for DDR

1.8VS switched power rail

3.3V always on power rail

3.3V power rail for LAN

+3V_LAN 3.3V power rail for LAN

2 2

+RTCVCC RTC power

+3VS

+5VALW

+5V_SB

+5VS

+VSB

3.3V switched power rail

5V always on power rail

5V power rail for SB

5V switched power rail

VSB always on power rail

S1 S3 S5

ON ON ON

ON ON ON ON

ON

OFF

ON

OFF

ON

OFF OFF

ON

OFF OFF

ON

OFF

ON

ON

OFF OFF

ON

ON

ON

ON

ON ON

ON

OFF

ON

ON

ON

ON

ON

OFF OFF

ON

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

Mini PCI-E SLOT

Wi-Fi WiMax

WLAN@

SIGNAL

SLP_S3#

SLP_S4#

HIGH HIGH HIGH

HIGH

LOW

LOW LOW

LOWLOW

STAR

POWER SAVING

WIMAX@3G3G@ STAR@

SLP_S5#

HIGHHIGHHIGH

HIGH

HIGH

LOW

+VALW

ON

ON

ON

ON

ON

+V +VS Clock

ON

ON

ON

OFF

OFF

ON

OFF

OFF

OFF

ONON

LOW

OFF

OFF

OFF

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

description

explain

BTO

Function

3 3

EC SM Bus1 address

Device

Smart Battery

Address

EC SM Bus2 address

Device

EMC1402

Address

1001 010X b0001 011X b

Tiger point SM Bus address

Device

Clock Generator

(SLG8SP556VTR)

DDR DIMMA

4 4

A

Address

1101 001Xb

1010 000Xb

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2009/11/10 2010/11/10

2009/11/10 2010/11/10

2009/11/10 2010/11/10

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

NTV00 LA5661P M/B

NTV00 LA5661P M/B

NTV00 LA5661P M/B

3 35Monday, November 23, 2009

3 35Monday, November 23, 2009

3 35Monday, November 23, 2009

E

0.4

0.4

0.4

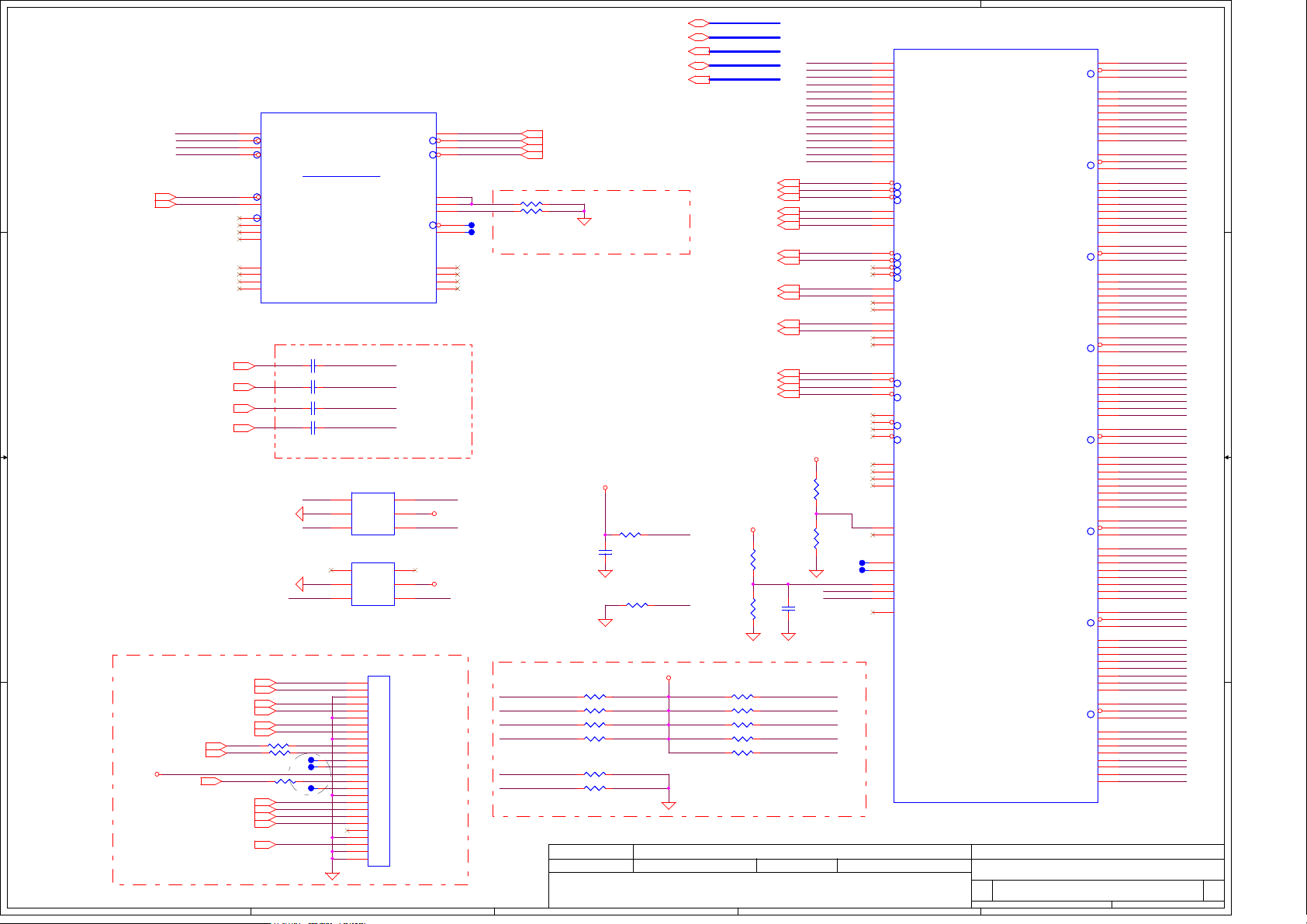

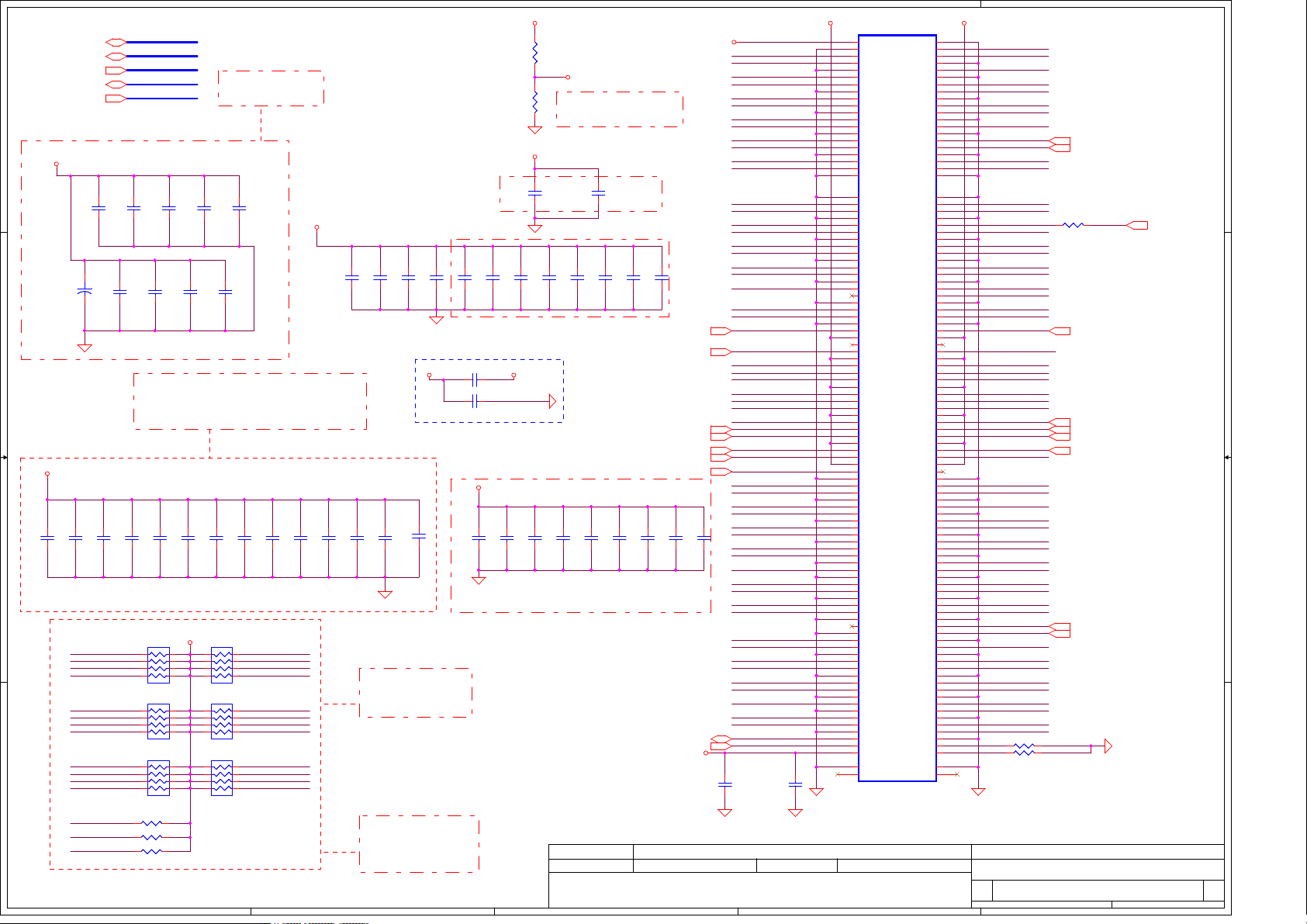

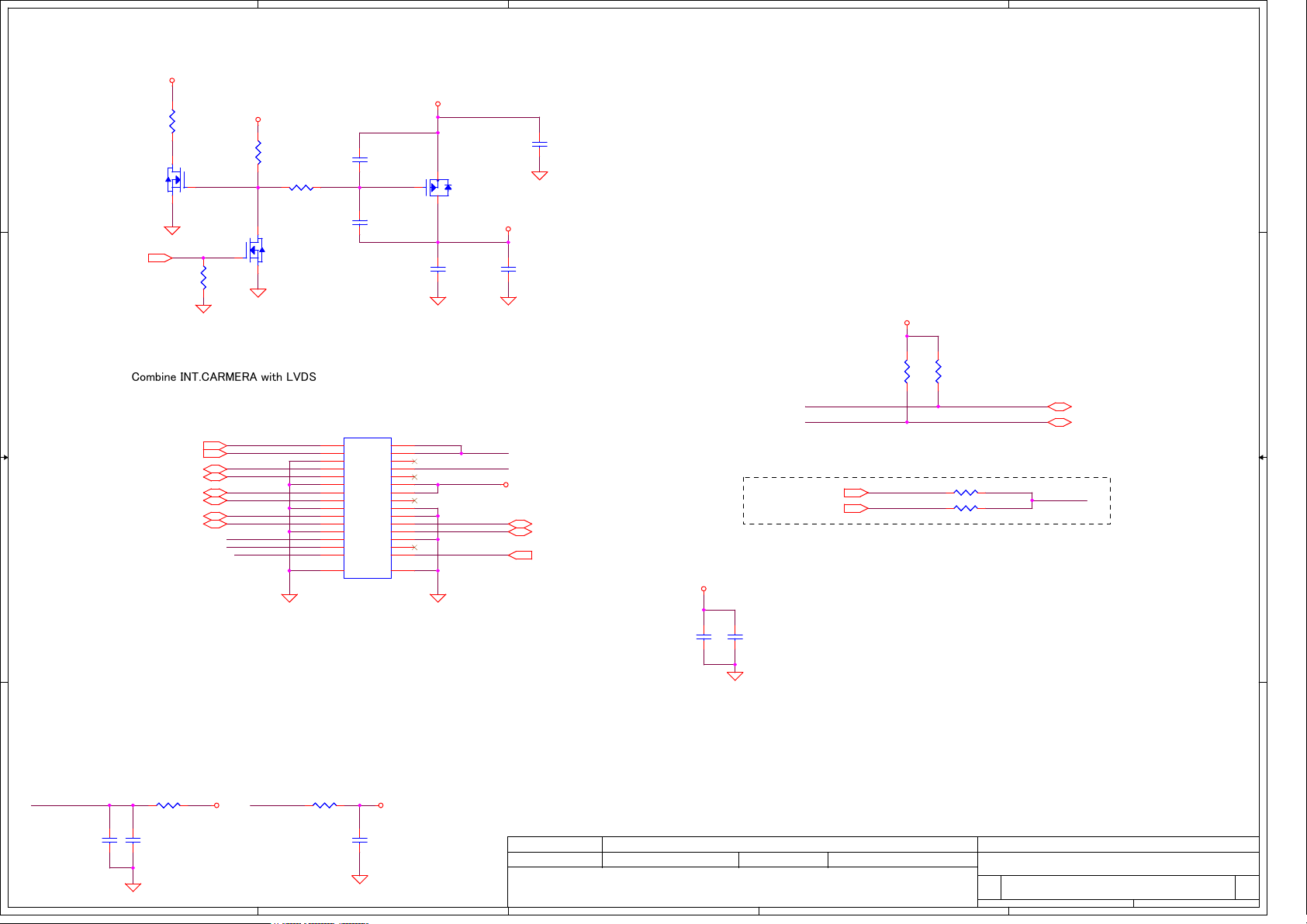

Page 4

5

PINEVIEW_M

C253

C253

1 2

C254

C254

1 2

C255

C255

1 2

C256

C256

1 2

XDP_TDI

XDP_TMS

XDP_TRST#

XDP_PREQ#

XDP_PRDY#

XDP_BPM#3

XDP_BPM#2

XDP_BPM#1

XDP_BPM#0

T52T52

T53T53

12

@

@

T54T54

XDP_TDO

XDP_TRST#

XDP_TDI

XDP_TMS

XDP_TCK

PINEVIEW_M

REV = 1.1

REV = 1.1

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

0.1U_0402_10V7K

U71A

D D

CLK_CPU_EXP#8

CLK_CPU_EXP8

C C

B B

+1.05VS

A A

5

DMI_RXP0_C

DMI_RXN0_C

DMI_RXP1_C

DMI_RXN1_C

H_PWRGD5,13

SLPIOVR13

PLTRST#5,13,15,20

DMI_RXP012

DMI_RXN012

DMI_RXP112

DMI_RXN112

XDP_PREQ#5

XDP_PRDY#5

XDP_BPM#35

XDP_BPM#25

XDP_BPM#15

XDP_BPM#05

XDP_TDO5

XDP_TRST#5

U71A

F3

DMI_RXP_0

F2

DMI_RXN_0

H4

DMI_RXP_1

G3

DMI_RXN_1

N7

EXP_CLKINN

N6

EXP_CLKINP

R10

EXP_TCLKINN

R9

EXP_TCLKINP

N10

RSVD

N9

RSVD

K2

RSVD

J1

RSVD

M4

RSVD

L3

RSVD

PINEVIEW-M_FCBGA8559

PINEVIEW-M_FCBGA8559

R354 1K_0402_5%@R354 1K_0402_5%@

1 2

R347 1K_0402_5%

R347 1K_0402_5%

1 2

@

@

PLTRST#

R348 1K_0402_5%

R348 1K_0402_5%

XDP_TDI5

XDP_TMS5

XDP_TCK5

4

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_RXP0_C

DMI_RXN0_C

DMI_RXP1_C

DMI_RXN1_C

DMI_TXN_1

EXP_RCOMPO

EXP_ICOMPI

EXP_RBIAS

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

1 OF 6

1 OF 6

DMI

DMI

Middle at CPU and SB

D15

D15

1

2

CM1293A-04SO_SOT23-6

CM1293A-04SO_SOT23-6

D16

D16

1

2

CM1293A-04SO_SOT23-6

CM1293A-04SO_SOT23-6

ACES_87151-24051

ACES_87151-24051

I/O1

REF1

REF2

I/O23I/O3

@

@

I/O1

REF1

REF2

I/O23I/O3

@

@

JP16

JP16

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

G1

26

G2

@

@

4

6

I/O4

5

XDP_PREQ#

4

6

I/O4

5

XDP_TCK

4

XDP_TDO

+3VS

+3VS

3

DDR_A_DQS#[0..7]7

DDR_A_D[0..63]7

DDR_A_DM[0..7]7

DDR_A_DQS[0..7]7

DDR_A_MA[0..14]7

G2

G1

H3

J2

L10

DMI_IRCOMP

L9

L8

N11

T38T38

P11

T39T39

K3

L2

M2

N2

XDP Reserve

XDP_TDI

XDP_TMS

XDP_TDO

XDP_PREQ#

XDP_TRST#

XDP_TCK

DMI_TXP0 12

DMI_TXN0 12

DMI_TXP1 12

DMI_TXN1 12

R369

R369

10K_0402_5%

10K_0402_5%

R370

10K_0402_5%

10K_0402_5%

DDR_REF

1

C50

C50

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

R277

R277

R274

R274

R282

R282

R288

R288

R289

R289

Deciphered Date

Deciphered Date

Deciphered Date

DDR_A_WE#

DDR_A_CAS#

DDR_A_RAS#

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_CS0#

DDR_CS1#

DDR_CKE0

DDR_CKE1

M_ODT0

M_ODT1

M_CLK_DDR0

M_CLK_DDR#0

M_CLK_DDR1

M_CLK_DDR#1

+1.8V

XDP_BPM#3

XDP_BPM#2

XDP_BPM#1

XDP_BPM#0

XDP_PRDY#

DDR_A_WE#7

DDR_A_CAS#7

R162

R162

R378

R378

49.9_0402_1%

49.9_0402_1%

750_0402_1%

750_0402_1%

Pull-down must be placed

within 500 mils from Pineview-M

+1.8V

DDR_RPU

R242

R242

1

80.6_0402_1%

80.6_0402_1%

C5

C5

0.01U_0402_16V7K

0.01U_0402_16V7K

R261

R261

R262

R262

R263

R263

R264

R264

R265

R265

R266

R266

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1 2

51_0402_5%

51_0402_5%

1 2

@

@

51_0402_5%

51_0402_5%

1 2

@

@

51_0402_5%

51_0402_5%

1 2

@

@

51_0402_5%

51_0402_5%

@

@

1 2

51_0402_5%

51_0402_5%

1 2

@

@

51_0402_5%

51_0402_5%

@

@

Issued Date

Issued Date

Issued Date

2

R245

R245

80.6_0402_1%

80.6_0402_1%

3

DDR_RPD

+1.05VS

2009/11/10 2010/11/10

2009/11/10 2010/11/10

2009/11/10 2010/11/10

DDR_A_RAS#7

DDR_A_BS07

DDR_A_BS17

DDR_A_BS27

DDR_CS0#7

DDR_CS1#7

DDR_CKE07

DDR_CKE17

M_ODT07

M_ODT17

M_CLK_DDR07

M_CLK_DDR#07

M_CLK_DDR17

M_CLK_DDR#17

+1.8V

12

R50

R50

1K_0402_1%

1K_0402_1%

12

R142

R142

1K_0402_1%

1K_0402_1%

51_0402_5%

51_0402_5%

@

@

51_0402_5%

51_0402_5%

@

@

51_0402_5%

51_0402_5%

@

@

51_0402_5%

51_0402_5%

@

@

51_0402_5%

51_0402_5%

@

@

Compal Secret Data

Compal Secret Data

Compal Secret Data

12

12

12

12

12

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

12

12

@R370

@

DDR_RPD

DDR_RPU

2

PINEVIEW_M

U71B

U71B

AH19

DDR_A_MA_0

AJ18

DDR_A_MA_1

AK18

DDR_A_MA_2

AK16

DDR_A_MA_3

AJ14

DDR_A_MA_4

AH14

DDR_A_MA_5

AK14

DDR_A_MA_6

AJ12

DDR_A_MA_7

AH13

DDR_A_MA_8

AK12

DDR_A_MA_9

AK20

DDR_A_MA_10

AH12

DDR_A_MA_11

AJ11

DDR_A_MA_12

AJ24

DDR_A_MA_13

AJ10

DDR_A_MA_14

AK22

DDR_A_WE#

AJ22

DDR_A_CAS#

AK21

DDR_A_RAS#

AJ20

DDR_A_BS_0

AH20

DDR_A_BS_1

AK11

DDR_A_BS_2

AH22

DDR_A_CS#_0

AK25

DDR_A_CS#_1

AJ21

DDR_A_CS#_2

AJ25

DDR_A_CS#_3

AH10

DDR_A_CKE_0

AH9

DDR_A_CKE_1

AK10

DDR_A_CKE_2

AJ8

DDR_A_CKE_3

AK24

DDR_A_ODT_0

AH26

DDR_A_ODT_1

AH24

DDR_A_ODT_2

AK27

DDR_A_ODT_3

AG15

DDR_A_CK_0

AF15

DDR_A_CK_0#

AD13

DDR_A_CK_1

AC13

DDR_A_CK_1#

AC15

DDR_A_CK_3

AD15

DDR_A_CK_3#

AF13

DDR_A_CK_4

AG13

DDR_A_CK_4#

AD17

RSVD

AC17

RSVD

AB15

RSVD

AB17

RSVD

AB4

RSVD

AK8

RSVD

AB11

T40T40

T41T41

RSVD_TP

AB13

RSVD_TP

AL28

DDR_VREF

AK28

DDR_RPD

AJ26

DDR_RPU

AK29

RSVD

PINEVIEW-M_FCBGA8559

PINEVIEW-M_FCBGA8559

2

PINEVIEW_M

REV = 1.1

REV = 1.1

DDR_A_DQS_0

DDR_A_DQS#_0

DDR_A_DM_0

DDR_A_DQ_0

DDR_A_DQ_1

DDR_A_DQ_2

DDR_A_DQ_3

DDR_A_DQ_4

DDR_A_DQ_5

DDR_A_DQ_6

DDR_A_DQ_7

DDR_A_DQS_1

DDR_A_DQS#_1

DDR_A_DM_1

DDR_A_DQ_8

DDR_A_DQ_9

DDR_A_DQ_10

DDR_A_DQ_11

DDR_A_DQ_12

DDR_A_DQ_13

DDR_A_DQ_14

DDR_A_DQ_15

DDR_A_DQS_2

DDR_A_DQS#_2

DDR_A_DM_2

DDR_A_DQ_16

DDR_A_DQ_17

DDR_A_DQ_18

DDR_A_DQ_19

DDR_A_DQ_20

DDR_A_DQ_21

DDR_A_DQ_22

DDR_A_DQ_23

DDR_A_DQS_3

DDR_A_DQS#_3

DDR_A_DM_3

DDR_A_DQ_24

DDR_A_DQ_25

DDR_A_DQ_26

DDR_A_DQ_27

DDR_A_DQ_28

DDR_A_DQ_29

DDR_A_DQ_30

DDR_A_DQ_31

DDR_A_DQS_4

DDR_A_DQS#_4

DDR_A_DM_4

DDR_A_DQ_32

DDR_A_DQ_33

DDR_A_DQ_34

DDR_A_DQ_35

DDR_A_DQ_36

DDR_A_DQ_37

DDR_A_DQ_38

DDR_A_DQ_39

DDR_A_DQS_5

DDR_A_DQS#_5

DDR_A_DM_5

DDR_A_DQ_40

DDR_A_DQ_41

DDR_A_DQ_42

DDR_A_DQ_43

DDR_A_DQ_44

DDR_A_DQ_45

DDR_A_DQ_46

DDR_A_DQ_47

DDR_A_DQS_6

DDR_A_DQS#_6

DDR_A

DDR_A

2 OF 6

2 OF 6

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

DDR_A_DM_6

DDR_A_DQ_48

DDR_A_DQ_49

DDR_A_DQ_50

DDR_A_DQ_51

DDR_A_DQ_52

DDR_A_DQ_53

DDR_A_DQ_54

DDR_A_DQ_55

DDR_A_DQS_7

DDR_A_DQS#_7

DDR_A_DM_7

DDR_A_DQ_56

DDR_A_DQ_57

DDR_A_DQ_58

DDR_A_DQ_59

DDR_A_DQ_60

DDR_A_DQ_61

DDR_A_DQ_62

DDR_A_DQ_63

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

NTV00 LA5661P M/B

NTV00 LA5661P M/B

NTV00 LA5661P M/B

1

AD3

AD2

AD4

AC4

AC1

AF4

AG2

AB2

AB3

AE2

AE3

AB8

AD7

AA9

AB6

AB7

AE5

AG5

AA5

AB5

AB9

AD6

AD8

AD10

AE8

AG8

AG7

AF10

AG11

AF7

AF8

AD11

AE10

AK5

AK3

AJ3

AH1

AJ2

AK6

AJ7

AF3

AH2

AL5

AJ6

AG22

AG21

AD19

AE19

AG19

AF22

AD22

AG17

AF19

AE21

AD21

AE26

AG27

AJ27

AE24

AG25

AD25

AD24

AC22

AG24

AD27

AE27

AE30

AF29

AF30

AG31

AG30

AD30

AD29

AJ30

AJ29

AE29

AD28

AB27

AA27

AB26

AA24

AB25

W24

W22

AB24

AB23

AA23

W27

Pineview(1/3)

Pineview(1/3)

Pineview(1/3)

1

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DM0

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DM1

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DM2

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DM3

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DM4

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DM5

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DM6

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_DQS7

DDR_A_DQS#7

DDR_A_DM7

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

4 35Tuesday, December 08, 2009

4 35Tuesday, December 08, 2009

4 35Tuesday, December 08, 2009

0.4

0.4

0.4

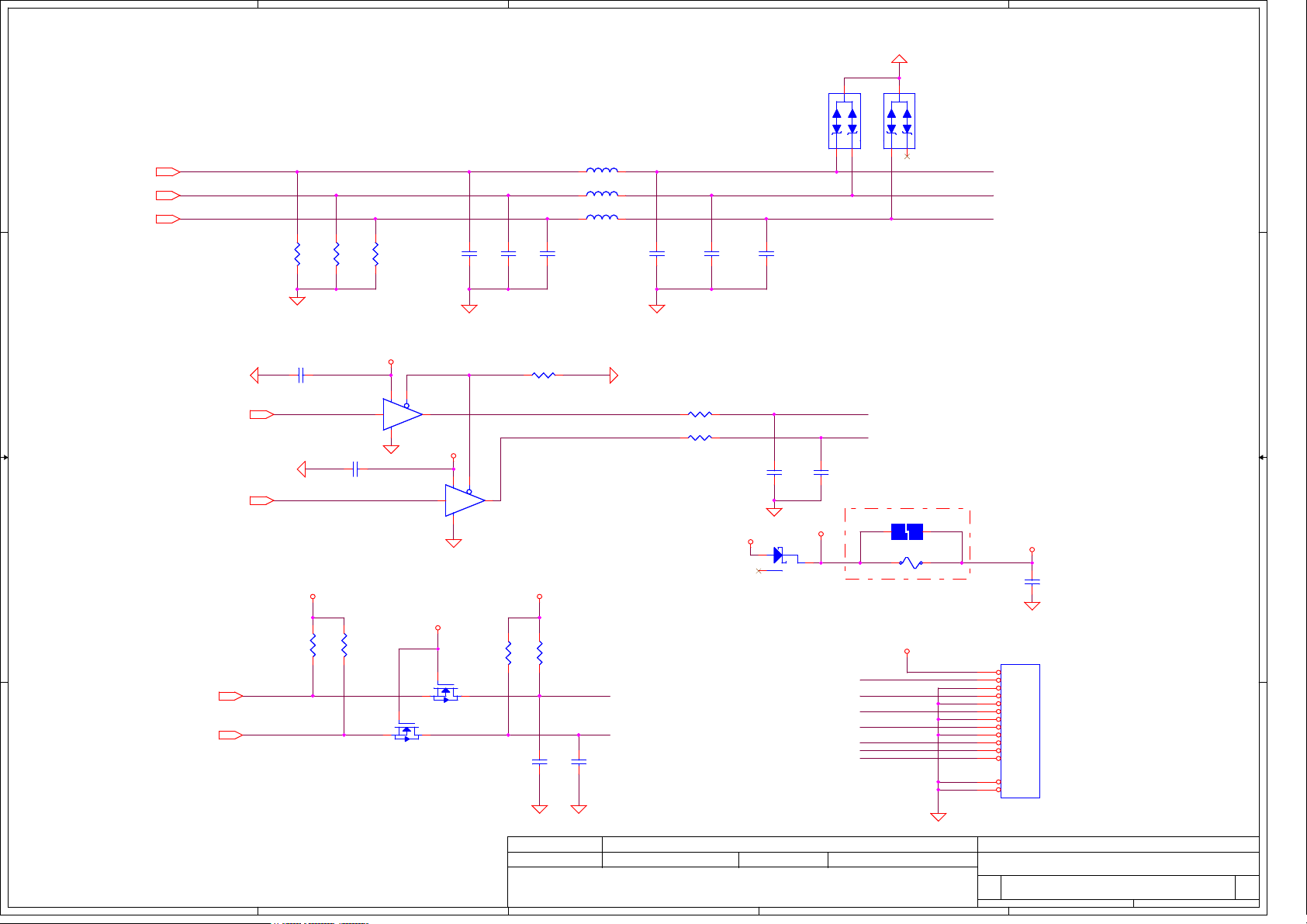

Page 5

5

PINEVIEW_M

U71C

U71C

D12

T2T2

T12T12

T3T3

T4T4

T13T13

D D

T5T5

T6T6

T7T7

T14T14

XDP_RSVD_9

T8T8

T15T15

T9T9

T16T16

T10T10

T17T17

T11T11

T28T28

T37T37

C C

T29T29

T30T30

T20T20

T21T21

T22T22

T23T23

T24T24

T25T25

C10

D10

B11

B10

B12

C11

AA7

AA6

AA21

W21

V21

A7

D6

C5

C7

C6

D8

B7

A9

D9

C8

B8

L11

R5

R6

T21

XDP_RSVD_00

XDP_RSVD_01

XDP_RSVD_02

XDP_RSVD_03

XDP_RSVD_04

XDP_RSVD_05

XDP_RSVD_06

XDP_RSVD_07

XDP_RSVD_08

XDP_RSVD_09

XDP_RSVD_10

XDP_RSVD_11

XDP_RSVD_12

XDP_RSVD_13

XDP_RSVD_14

XDP_RSVD_15

XDP_RSVD_16

XDP_RSVD_17

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

PINEVIEW_M

REV = 1.1

REV = 1.1

VGA

VGA

PM_EXTTS#_1/DPRSLPVR

MISC

MISC

CRT_HSYNC

CRT_VSYNC

CRT_RED

CRT_GREEN

CRT_BLUE

CRT_IRTN

CRT_DDC_DATA

CRT_DDC_CLK

DAC_IREF

REFCLKINP

REFCLKINN

REFSSCLKINP

REFSSCLKINN

PM_EXTTS#_0

PWROK

RSTIN#

HPL_CLKINN

HPL_CLKINP

M30

M29

GMCH_CRT_R

N31

GMCH_CRT_G

P30

GMCH_CRT_B

P29

N30

L31

L30

DAC_IREF

P28

CPU_DREFCLK

Y30

CPU_DREFCLK#

Y29

CPU_SSCDREFCLK

AA30

CPU_SSCDREFCLK#

AA31

PM_EXTTS#1

K29

PM_EXTTS#0

J30

PCH_POK

L5

PLTRST#

AA3

CLK_CPU_HPLCLK#

W8

CLK_CPU_HPLCLK

W9

To be placed <250 mils to U71 ball

GMCH_CRT_R

GMCH_CRT_G

GMCH_CRT_B

ENBKL

To be placed <500 mils to U71 ball

XDP_RSVD_9

4

GMCH_CRT_HSYNC 10

GMCH_CRT_VSYNC 10

GMCH_CRT_R 10

GMCH_CRT_G 10

GMCH_CRT_B 10

R376 be placed <500 mils to U71.P28

GMCH_CRT_DATA 10

GMCH_CRT_CLK 10

R376 665_0402_1%R376 665_0402_1%

0_0402_5%

0_0402_5%

R189

R189

PM_EXTTS#0 7

PCH_POK 13

PLTRST# 4,13,15,20

R307

R307

1 2

150_0402_1%

150_0402_1%

R254

R254

1 2

150_0402_1%

150_0402_1%

R255

R255

1 2

150_0402_1%

150_0402_1%

R34

R34

100K_0402_5%

100K_0402_5%

CPU_DREFCLK 8

CPU_DREFCLK# 8

CPU_SSCDREFCLK 8

CPU_SSCDREFCLK# 8

PM_DPRSLPVR 13

CLK_CPU_HPLCLK# 8

CLK_CPU_HPLCLK 8

R151 be placed U71.R22

Close to Processor pin

XDP_BPM#04

XDP_BPM#14

XDP_BPM#24

XDP_BPM#34

XDP_TDI4

XDP_TDO4

XDP_TCK4

XDP_TMS4

XDP_TRST#4

3

LVDS_ACLK#9

LVDS_ACLK9

LVDS_A0#9

LVDS_A09

LVDS_A1#9

LVDS_A19

LVDS_A2#9

LVDS_A29

2.37K_0402_1%

2.37K_0402_1%

ENBKL22

L_BKLTCTL9

Spacing(to other)>20 mil

LVDS_SCL9

LVDS_SDA9

GMCH_ENVDD9

+3VS

12

R133

R133

10K_0402_5%

10K_0402_5%

PM_EXTTS#0

R1930_0402_5%@R1930_0402_5%

R2210_0402_5%@R2210_0402_5%

@

R2090_0402_5%@R2090_0402_5%

@

@

R2140_0402_5%@R2140_0402_5%

@

R1900_0402_5%@R1900_0402_5%

@

R2060_0402_5%@R2060_0402_5%

R2070_0402_5%@R2070_0402_5%

@

@

R2110_0402_5%@R2110_0402_5%

@

R2120_0402_5%@R2120_0402_5%

@

R151

R151

ENBKL

L_BKLTCTL

T48T48

T49T49

T50T50

T51T51

T55T55

XDP_TDI_R

XDP_TDO_R

XDP_TCK_R

XDP_TMS_R

XDP_TRST#_R

H_THERMDA

H_THERMDC

L_IBG

U25

U26

R23

R24

N26

N27

R26

R27

R22

N22

N23

K25

K23

K24

H26

G11

E15

G13

F13

B18

B20

C20

B21

D14

D13

B14

C14

C16

D30

E30

J28

L27

L26

L23

G5

U71D

U71D

LA_CLKN

LA_CLKP

LA_DATAN_0

LA_DATAP_0

LA_DATAN_1

LA_DATAP_1

LA_DATAN_2

LA_DATAP_2

LIBG

LVBG

LVREFH

LVREFL

LBKLT_EN

LBKLT_CTL

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

BPM_1_0#

BPM_1_1#

BPM_1_2#

BPM_1_3#

BPM_2_0#/RSVD

BPM_2_1#/RSVD

BPM_2_2#/RSVD

BPM_2_3#/RSVD

RSVD

TDI

TDO

TCK

TMS

TRST#

THRMDA_1

THRMDC_1

PINEVIEW_M

PINEVIEW_M

LVDS

LVDS

REV = 1.1

REV = 1.1

ICH

ICH

CPU

CPU

2

THERMTRIP#

CPUPWRGOOD

SMI#

A20M#

FERR#

LINT0

LINT1

IGNNE#

STPCLK#

DPRSTP#

DPSLP#

INIT#

PRDY#

PREQ#

PROCHOT#

GTLREF

VSS

RSVD

RSVD

BCLKN

BCLKP

BSEL_0

BSEL_1

BSEL_2

VID_0

VID_1

VID_2

VID_3

VID_4

VID_5

VID_6

RSVD

RSVD

RSVD

RSVD

RSVD_TP

RSVD_TP

EXTBGREF

E7

H7

H6

F10

F11

E5

F8

G6

G10

G8

E11

F15

H_THERMTRIP#

E13

C18

W1

A13

H27

L6

E17

H10

J10

K5

H5

K6

H30

H29

H28

G30

G29

F29

E29

L7

D20

H13

D18

K9

D19

K7

H_SMI#

H_A20M#

H_FERR#

H_INTR

H_NMI

H_IGNNE#

H_STPCLK#

H_DPRSTP#

H_DPSLP#

H_INIT#

R2180_0402_5%@R2180_0402_5%

@

H_PROCHOT#

H_PWRGD

+H_GTL_REF

CLK_CPU_BCLK#

CLK_CPU_BCLK

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

CPU_VID6

T26T26

T27T27

H_EXTBGREF

R2240_0402_5% @ R2240_0402_5% @

H_SMI# 11

H_A20M# 11

H_FERR# 11

H_INTR 11

H_NMI 11

H_IGNNE# 11

H_STPCLK# 11

H_DPRSTP# 13

H_DPSLP# 13

H_INIT# 11

XDP_PRDY# 4

XDP_PREQ# 4

H_THERMTRIP# 11

H_PWRGD 4,13

CLK_CPU_BCLK# 8

CLK_CPU_BCLK 8

CPU_BSEL0 8

CPU_BSEL1 8

CPU_BSEL2 8

CPU_VID0 33

CPU_VID1 33

CPU_VID2 33

CPU_VID3 33

CPU_VID4 33

CPU_VID5 33

CPU_VID6 33

1

+1.05VS

R377

R377

68_0402_5%

68_0402_5%

Close to CPU

R150

B B

3 OF 6

PINEVIEW-M_FCBGA8559

PINEVIEW-M_FCBGA8559

3 OF 6

Pull down 1K to GND for Intel request

+3VS

1

C18

C18

2

0.1U_0402_16V4Z

A A

+3VS

0.1U_0402_16V4Z

C66

C66

1 2

2200P_0402_50V7K

2200P_0402_50V7K

1 2

R2 10K_0402_5%R2 10K_0402_5%

5

H_THERMDA

H_THERMDC

CPU_THERM#

CPU THERMAL SENSOR

U2

U2

GND

8

7

6

5

EC_SMB_CK2

EC_SMB_DA2

1

VDD

2

DP

3

DN

4

THERM#

EMC1402-1-ACZL-TR_MSOP8

EMC1402-1-ACZL-TR_MSOP8

Address:0100_1100 EMC1402-1

Address:0100_1101 EMC1402-2

SMCLK

SMDATA

ALERT#

R150

1K_0402_5%

1K_0402_5%

1 2

H_DPRSTP#

H_DPSLP#

H_PWRGD

H_A20M#

H_IGNNE#

H_INIT#

H_INTR

H_FERR#

H_NMI

EC_SMB_CK2 22

EC_SMB_DA2 22

12

R57 10K_0402_5%@R57 10K_0402_5%@

4

+3VS

H_SMI#

H_STPCLK#

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C416 220P_0402_50V7KC416 220P_0402_50V7K

1 2

C398 220P_0402_50V7KC398 220P_0402_50V7K

1 2

C514 220P_0402_50V7KC514 220P_0402_50V7K

1 2

C419 220P_0402_50V7KC419 220P_0402_50V7K

1 2

C441 220P_0402_50V7KC441 220P_0402_50V7K

1 2

C399 220P_0402_50V7KC399 220P_0402_50V7K

1 2

C414 220P_0402_50V7KC414 220P_0402_50V7K

1 2

C424 220P_0402_50V7KC424 220P_0402_50V7K

1 2

C445 220P_0402_50V7KC445 220P_0402_50V7K

1 2

C415 220P_0402_50V7KC415 220P_0402_50V7K

1 2

C447 220P_0402_50V7KC447 220P_0402_50V7K

1 2

2009/11/10 2010/11/10

2009/11/10 2010/11/10

2009/11/10 2010/11/10

3

C30

THRMDA_2/RSVD

D31

THRMDC_2/RSVD

PINEVIEW-M_FCBGA8559

PINEVIEW-M_FCBGA8559

ESD request

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

4 OF 6

4 OF 6

220P_0402_50V7K

220P_0402_50V7K

placed within 0.5"

of processor pin.

2

C23

C23

@

@

1

2

placed within 0.5" of processor

pin and 5 mils spacing

+1.05VS+1.05VS

R144

R144

1K_0402_1%

1K_0402_1%

R155

R155

2K_0402_1%

2K_0402_1%

H_EXTBGREF+H_GTL_REF

C24

C24

1U_0402_6.3V6K

1U_0402_6.3V6K

1

2

R244

R244

976_0402_1%

976_0402_1%

R156

R156

3.3K_0402_1%

3.3K_0402_1%

Add C24 for Ref board designReserve C23 for Ref board design

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Pineview(2/3)

Pineview(2/3)

Pineview(2/3)

NTV00 LA5661P M/B

NTV00 LA5661P M/B

NTV00 LA5661P M/B

5 35Tuesday, December 08, 2009

5 35Tuesday, December 08, 2009

5 35Tuesday, December 08, 2009

1

0.4

0.4

0.4

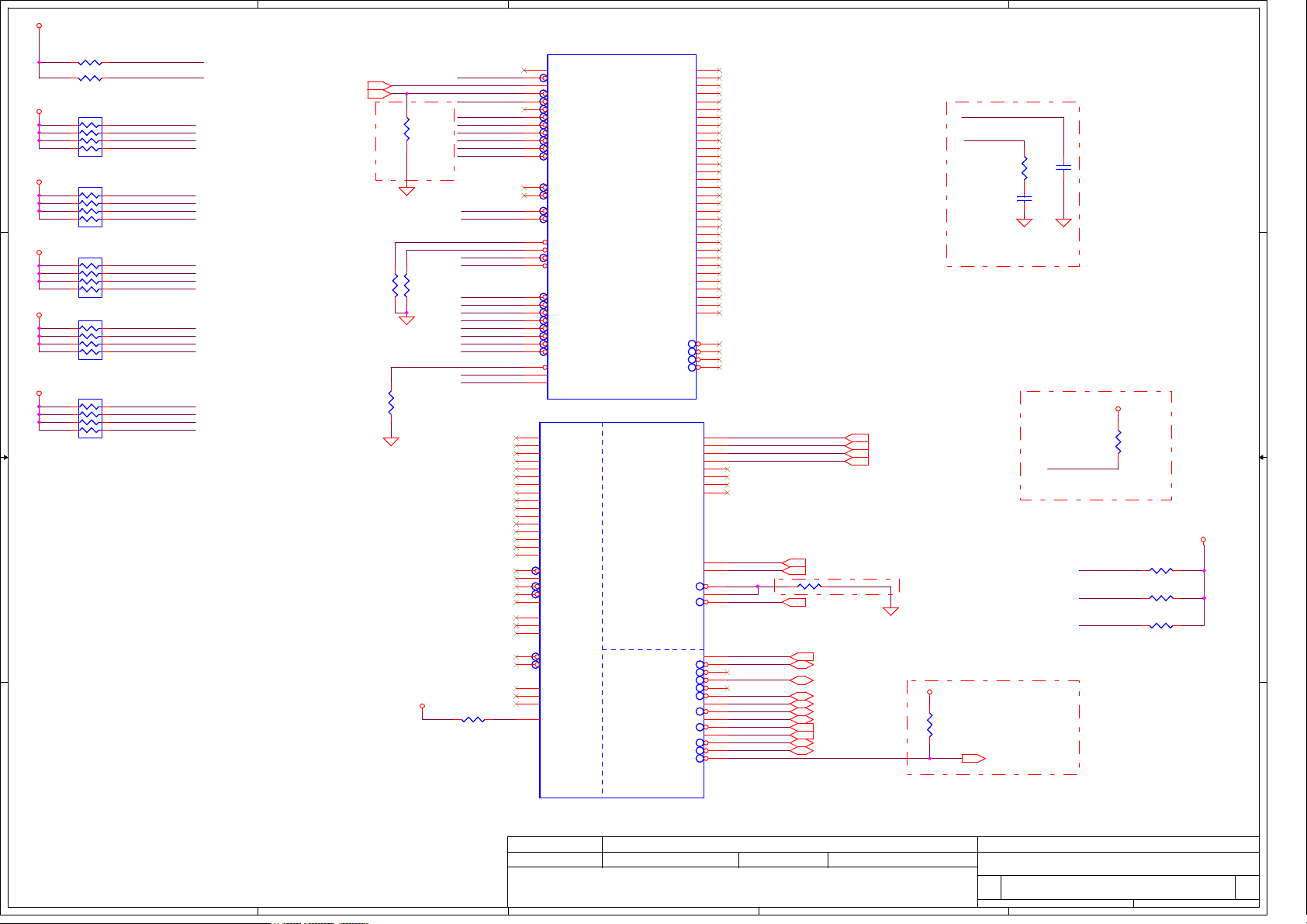

Page 6

5

U71E

U71E

+0.89VS

2

C22

C22

1

2.2U_0603_10V6K

2.2U_0603_10V6K

+VCC_SM

+VCCCK_DDR

270mA

@

@

+VCCCK_DDR

C128

C128

+VCCA_VCCD

1500mA

+VCCSFR_AB_DPL

180mA

+VCC_CRT_DAC

1

C76

C76

C70

C70

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

2640mA

+VCC_SM

2000mA

2

1

1

2

1U_0402_6.3V6K

1U_0402_6.3V6K

W14

W16

W18

W19

AK13

AK19

AK9

AL11

AL16

AL21

AL25

AK7

W10

W11

AA10

AA11

AA19

AC31

1

C75

C75

2

T13

VCCGFX

T14

VCCGFX

T16

VCCGFX

T18

VCCGFX

T19

VCCGFX

V13

VCCGFX

V19

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCCK_DDR

AL7

VCCCK_DDR

U10

VCCA_DDR

U5

VCCA_DDR

U6

VCCA_DDR

U7

VCCA_DDR

U8

VCCA_DDR

U9

VCCA_DDR

V2

VCCA_DDR

V3

VCCA_DDR

V4

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCACK_DDR

VCCACK_DDR

VCCD_AB_DPL

V11

VCCD_HMPLL

VCCSFR_AB_DPL

T30

VCCACRTDAC

T31

VCC_GIO

J31

VCCRING_EAST

C3

VCCRING_WEST

B2

VCCRING_WEST

C2

VCCRING_WEST

A21

VCC_LGI

PINEVIEW-M_FCBGA8559

PINEVIEW-M_FCBGA8559

1

C65

C65

2

1U_0402_6.3V6K

1U_0402_6.3V6K

C77

C77

1U_0402_6.3V6K

1U_0402_6.3V6K

D D

+1.8V

R3

R3

1 2

0_0603_5%

0_0603_5%

C332

C332

@

@

2.2U_0603_10V6K

2.2U_0603_10V6K

2.2U_0603_10V6K

2.2U_0603_10V6K

2

C19

C19

1

2.2U_0603_10V6K

2.2U_0603_10V6K

2

2

C21

C21

C20

C20

1

1

2.2U_0603_10V6K

2.2U_0603_10V6K

Please closed U71 ball

+1.8V

R11

R11

C C

1 2

0_0603_5%

0_0603_5%

22U_0603_6.3V_X5R

22U_0603_6.3V_X5R

1

C267

C267

0.1U_0402_10V6K

0.1U_0402_10V6K

2

1

2

Please closed U71 ball

B B

+3VS

10mA

+RING_EAST

+RING_WEST

190mA

+LGI_VID +DMI_HMPLL

60mA

+0.89VS

A A

1

2

C74

C74

1

1

C72

C72

C71

C71

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

2.2U_0603_10V6K

2.2U_0603_10V6K

5 OF 6

5 OF 6

PINEVIEW_M

PINEVIEW_M

REV = 1.1

REV = 1.1

GFX/MCH

GFX/MCH

DDR

DDR

EXP\CRT\PLL

EXP\CRT\PLL

2

1

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C51

C51

C15

C15

1

2

0.1U_0402_10V6K

0.1U_0402_10V6K

Close Chipset pin

5

POWER

POWER

DMI

DMI

VCCSFR_DMIHMPLL

1

+

+

C276

C276

330U_B2_2.5VM_R15M

330U_B2_2.5VM_R15M

2

10U_0805_6.3V4Z

10U_0805_6.3V4Z

CPU

CPU

LVDS

LVDS

4

VCCSENSE

VSSSENSE

VCCALVDS

VCCDLVDS

4

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCA

VCCP

VCCP

VCCP

VCCA_DMI

VCCA_DMI

VCCA_DMI

RSVD

VCCP

6040mA

1U_0402_6.3V6K

A23

A25

A27

B23

B24

B25

B26

B27

C24

C26

D23

D24

D26

D28

E22

E24

E27

F21

F22

F25

G19

G21

G24

H17

H19

H22

H24

J17

J19

J21

J22

K15

K17

K21

L14

L16

L19

L21

N14

N16

N19

N21

C29

B29

Y2

D4

B4

B3

80mA

1U_0402_6.3V6K

VCCSENSE

VSSSENSE

@

@

Please closed U71.D4

+VCC_ALVD

V30

+VCC_DLVD

W31

150mA

+VCC_DMI

T1

540mA

T2

T3

P2

AA1

180mA

E2

420mA

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

C428

C428

C429

C429

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

Please closed U71 ball

+CPU_CORE

2 x 330uF

1

+

+

C275

C275

330U_B2_2.5VM_R15M

330U_B2_2.5VM_R15M

2

+CPU_CORE

1

1

C269

C269

C268

C268

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

+1.05VS

1

C35

C35

0.1U_0402_10V6K

0.1U_0402_10V6K

2

+1.05VS

Please closed U71.Y2

T56T56

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

C427

C427

2

1

C270

C270

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C391

C391

0.01U_0402_16V7K

0.01U_0402_16V7K

2

Issued Date

Issued Date

Issued Date

3

+CPU_CORE

1

C250

C250

1U_0402_6.3V6K

1U_0402_6.3V6K

2

1

+

+

C278

C278

330U_D2_2.5VY_R6M

330U_D2_2.5VY_R6M

2

22U_0805_6.3V6M

22U_0805_6.3V6M

+1.5VS

3

+1.05VS

R12

R12

1 2

0_0603_5%

0_0603_5%

1

2

C36

C36

C33

C33

2

1

@

@

@

@

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

+1.05VS

R20

R20

1 2

0_0603_5%

0_0603_5%

R21

R21

1 2

0_0603_5%

0_0603_5%

C64

C64

R23

R23

1 2

0_0603_5%

0_0603_5%

R28

R28

1 2

0_0603_5%

0_0603_5%

+CPU_CORE

12

100_0402_1%

100_0402_1%

R32

R32

VCCSENSE 33

VSSSENSE 33

R31

R31

100_0402_1%

100_0402_1%

1 2

2009/11/10 2010/11/10

2009/11/10 2010/11/10

2009/11/10 2010/11/10

+1.8VS

R258

R258

1 2

0_0603_5%

0_0603_5%

1U_0402_6.3V6K

1U_0402_6.3V6K

R25

R25

1 2

0_0603_5%

0_0603_5%

1U_0402_6.3V6K

1U_0402_6.3V6K

R18

R18

1 2

0_0603_5%

0_0603_5%

1U_0402_6.3V6K

1U_0402_6.3V6K

R26

R26

1 2

0_0603_5%

0_0603_5%

22U_0805_6.3V6M

22U_0805_6.3V6M

R27

R27

1 2

0_0603_5%

0_0603_5%

1U_0402_6.3V6K

1U_0402_6.3V6K

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

C68

C68

1

2

C55

C55

22U_0603_6.3V_X5R

22U_0603_6.3V_X5R

1U_0402_6.3V6K

1U_0402_6.3V6K

1

2

C192

C192

C225

C225

C69

C69

C56

C56

C232

C232

1

C227

C227

2

+RING_EAST

1

C226

C226

2

+RING_WEST

1

C241

C241

2

@

@

1

C34

C34

2

+VCC_DMI

+VCC_DMI

1

C224

C224

2

1U_0402_6.3V6K

1U_0402_6.3V6K

+VCCA_VCCD

1

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

+LGI_VID

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

+VCCSFR_AB_DPL

1

1U_0402_6.3V6K

1U_0402_6.3V6K

2

+VCC_CRT_DAC+VCC_CRT_DAC

1

2

1

2

1

2

1

2

2

1

C223

C223

2

1U_0402_6.3V6K

1U_0402_6.3V6K

C189

C189

+DMI_HMPLL

+VCC_ALVD

+VCC_DLVD

2

1

PINEVIEW_M

PINEVIEW_M

U71F

U71F

REV = 1.1

REV = 1.1

A11

VSS

A16

VSS

A19

VSS

A29

RSVD_NCTF

A3

RSVD_NCTF

A30

RSVD_NCTF

A4

RSVD_NCTF

AA13

VSS

AA14

VSS

AA16

VSS

AA18

VSS

AA2

VSS

AA22

VSS

AA25

VSS

AA26

VSS

AA29

VSS

AA8

VSS

AB19

VSS

AB21

VSS

AB28

VSS

AB29

VSS

AB30

VSS

AC10

VSS

AC11

VSS

AC19

VSS

AC2

VSS

AC21

VSS

AC28

VSS

AC30

VSS

AD26

VSS

AD5

VSS

AE1

VSS

AE11

VSS

AE13

VSS

AE15

VSS

AE17

VSS

AE22

VSS

AE31

VSS

AF11

VSS

AF17

VSS

AF21

VSS

AF24

VSS

AF28

VSS

AG10

VSS

AG3

VSS

AH18

VSS

AH23

VSS

AH28

VSS

AH4

VSS

AH6

VSS

AH8

VSS

AJ1

RSVD_NCTF

AJ16

VSS

AJ31

RSVD_NCTF

AK1

RSVD_NCTF

AK2

RSVD_NCTF

AK23

VSS

AK30

RSVD_NCTF

AK31

RSVD_NCTF

AL13

VSS

AL19

VSS

AL2

RSVD_NCTF

AL23

VSS

AL29

RSVD_NCTF

1

2

AL3

RSVD_NCTF

AL30

RSVD_NCTF

AL9

VSS

B13

VSS

B16

VSS

B19

VSS

B22

VSS

B30

RSVD_NCTF

B31

RSVD_NCTF

B5

VSS

B9

VSS

C1

RSVD_NCTF

C12

VSS

C21

VSS

C22

VSS

C25

VSS

C31

RSVD_NCTF

D22

VSS

E1

RSVD_NCTF

E10

VSS

E19

VSS

E21

VSS

E25

VSS

E8

VSS

F17

VSS

F19

VSS

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

GND

GND

6 OF 6

6 OF 6

PINEVIEW-M_FCBGA8559

PINEVIEW-M_FCBGA8559

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Pineview(3/3)

Pineview(3/3)

Pineview(3/3)

NTV00 LA5661P M/B

NTV00 LA5661P M/B

NTV00 LA5661P M/B

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F24

F28

F4

G15

G17

G22

G27

G31

H11

H15

H2

H21

H25

H8

J11

J13

J15

J4

K11

K13

K19

K26

K27

K28

K30

K4

K8

L1

L13

L18

L22

L24

L25

L29

M28

M3

N1

N13

N18

N24

N25

N28

N4

N5

N8

P13

P14

P16

P18

P19

P21

P3

P4

R25

R7

R8

T11

U22

U23

U24

U27

V14

V16

V18

V28

V29

W13

W2

W23

W25

W26

W28

W30

W4

W5

W6

W7

Y28

Y3

Y4

T29

0.4

0.4

6 35Tuesday, December 08, 2009

6 35Tuesday, December 08, 2009

6 35Tuesday, December 08, 2009

1

0.4

Page 7

5

DDR_A_DQS#[0..7]4

DDR_A_D[0..63]4

DDR_A_DM[0..7]4

DDR_A_DQS[0..7]4

DDR_A_MA[0..14]4

D D

+1.8V

2

C362

C362

C364

C364

1

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

1

1

+

+

@

@

C358

C358

C363

C363

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

220U_B2_2.5VM_R35

220U_B2_2.5VM_R35

C C

+0.9VS

1

C84

C84

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

DDR_A_MA13

M_ODT0

DDR_CS0#

DDR_A_RAS#

DDR_A_MA1

DDR_A_MA3

DDR_A_MA10

DDR_A_BS0

DDR_A_WE#

DDR_A_CAS#

DDR_CS1#

M_ODT1

DDR_A_MA14

DDR_A_BS2

DDR_CKE0

1

C80

C80

C86

C86

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C82

C82

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

B B

A A

2

2

C366

C366

1

1

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

1

C365

C365

C367

C367

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

Layout Note:

Place one cap close to every 2 pullup

resistors terminated to +0.9VS

1

1

C98

C98

C101

C101

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+0.9VS

RP6

RP6

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

47_0804_8P4R_5%

RP2

RP2

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

47_0804_8P4R_5%

RP3

RP3

1 8

2 7

3 6

4 5

47_0804_8P4R_5%

47_0804_8P4R_5%

R163

R163

1 2

47_0402_5%

47_0402_5%

R72

R72

1 2

47_0402_5%

47_0402_5%

R73

R73

1 2

47_0402_5%

47_0402_5%

5

2

C368

C368

1

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

1

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C102

C102

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

47_0804_8P4R_5%

47_0804_8P4R_5%

47_0804_8P4R_5%

47_0804_8P4R_5%

47_0804_8P4R_5%

47_0804_8P4R_5%

C369

C369

0.1U_0402_16V4Z

0.1U_0402_16V4Z

Layout Note:

Place near JDDR1

2

C370

C370

1

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

1

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

2

RP5

RP5

RP4

RP4

RP1

RP1

1

1

C97

C97

C81

C81

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

DDR_A_BS1

18

DDR_A_MA2

27

DDR_A_MA0

36

DDR_A_MA4

45

DDR_A_MA6

18

DDR_A_MA7

27

DDR_A_MA11

36

DDR_CKE1

45

DDR_A_MA12

18

DDR_A_MA8

27

DDR_A_MA9

36

DDR_A_MA5

45

+1.8V

1

C99

C99

C96

C96

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

4

1

C579

C579

C567

C567

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

C85

C85

C83

C83

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

Layout Note:

Place these resistor

closely DIMMA,all

trace length<1000 mil

Layout Note:

Place these resistor

closely DIMMA,all

trace length

Max=1000 mil

4

Please closed SO-DIMM

1

1

2

1

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C26

C587

C587

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C454

C454

C26

C588

C588

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+1.8V

1

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

R53

R53

1K_0402_1%

1K_0402_1%

R54

R54

1K_0402_1%

1K_0402_1%

+DIMM_VREF

C90

C90

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

2

1 2

C88 0.1U_0402_16V4Z

C88 0.1U_0402_16V4Z

@

@

1 2

C87 0.1U_0402_16V4Z

C87 0.1U_0402_16V4Z

@

@

+1.8V

C589

C589

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C558

C558

C608

C608

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+1.5VS

1

1

C46

C46

C559

C559

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+DIMM_VREF

1

C343

C343

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C41

C41

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

3

1

C91

C91

@

@

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

2

1

C627

C627

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C547

C547

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

3

+DIMM_VREF

1

1

C541

C541

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

DDR_CKE04

DDR_A_BS24

DDR_A_WE#4 DDR_CS0# 4

DDR_A_CAS#4 M_ODT0 4

DDR_CS1#4

M_ODT14

1

1

C628

C628

C344

C344

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C542

C542

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

CLK_SMBDATA8,15

CLK_SMBCLK8,15

+3VS

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2009/11/10 2010/11/10

2009/11/10 2010/11/10

2009/11/10 2010/11/10

DDR_A_D0

DDR_A_D1

DDR_A_DQS#0

DDR_A_DQS0 DDR_A_D6

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_DM3

DDR_A_D26

DDR_A_D27

DDR_CKE0

DDR_A_BS2

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

DDR_A_MA10

DDR_A_BS0

DDR_A_WE#

DDR_A_CAS#

DDR_CS1#

M_ODT1

DDR_A_D32

DDR_A_D33

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_D34

1

DDR_A_D35

DDR_A_D40

2

DDR_A_D41

DDR_A_DM5

DDR_A_D42

DDR_A_D43

DDR_A_D48

DDR_A_D49

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

DDR_A_DM7

DDR_A_D58

DDR_A_D59

CLK_SMBDATA

CLK_SMBCLK

C371

C371

1

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

Compal Secret Data

Compal Secret Data

Compal Secret Data

1

C372

C372

2

Deciphered Date

Deciphered Date

Deciphered Date

+1.8V

12

12

Share +DIMM_VREF for

1.DDRII VREF

2.PineView DDR_VREF

20mils

1

2

1

C25

C25

C546

C546

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

C610

C610

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

+1.8V +1.8V

JDIM1

JDIM1

1

VREF

3

VSS

5

DQ0

7

DQ1

9

VSS

11

DQS0#

13

DQS0

15

VSS

17

DQ2

19

DQ3

21

VSS

23

DQ8

25

DQ9

27

VSS

29

DQS1#

31

DQS1

33

VSS

35

DQ10

37

DQ11

39

VSS

41

VSS

43

DQ16

45

DQ17

47

VSS

49

DQS2#

51

DQS2

53

VSS

55

DQ18

57

DQ19

59

VSS

61

DQ24

63

DQ25

65

VSS

67

DM3

69

NC

71

VSS

73

DQ26

75

DQ27

77

VSS

79

CKE0

81

VDD

83

NC

85

BA2

87

VDD

89

A12

91

A9

93

A8

95

VDD

97

A5

99

A3

101

A1

103

VDD

105

A10/AP

107

BA0

109

WE#

111

VDD

113

CAS#

115

NC/S1#

117

VDD

119

NC/ODT1

121

VSS

123

DQ32

125

DQ33

127

VSS

129

DQS4#

131

DQS4

133

VSS

135

DQ34

137

DQ35

139

VSS

141

DQ40

143

DQ41

145

VSS

147

DM5

149

VSS

151

DQ42

153

DQ43

155

VSS

157

DQ48

159

DQ49

161

VSS

163

NC,TEST

165

VSS

167

DQS6#

169

DQS6

171

VSS

173

DQ50

175

DQ51

177

VSS

179

DQ56

181

DQ57

183

VSS

185

DM7

187

VSS

189

DQ58

191

DQ59

193

VSS

195

SDA

197

SCL

199

VDDSPD

201

G1

203

GND

FOX_AS0A426-N4RN-7F

FOX_AS0A426-N4RN-7F

CONN@

CONN@

2

NC/CKE1

DIMMA

VSS

DQ4

DQ5

VSS

DM0

VSS

DQ6

DQ7

VSS

DQ12

DQ13

VSS

DM1

VSS

CK0

CK0#

VSS

DQ14

DQ15

VSS

VSS

DQ20

DQ21

VSS

DM2

VSS

DQ22

DQ23

VSS

DQ28

DQ29

VSS

DQS3#

DQS3

VSS

DQ30

DQ31

VSS

VDD

NC/A15

NC/A14

VDD

VDD

VDD

BA1

RAS#

VDD

ODT0

NC/A13

VDD

VSS

DQ36

DQ37

VSS

DM4

VSS

DQ38

DQ39

VSS

DQ44

DQ45

VSS

DQS5#

DQS5

VSS

DQ46

DQ47

VSS

DQ52

DQ53

VSS

CK1

CK1#

VSS

DM6

VSS

DQ54

DQ55

VSS

DQ60

DQ61

VSS

DQS7#

DQS7

VSS

DQ62

DQ63

VSS

SA0

SA1

GND

1

2

DDR_A_D4

4

DDR_A_D5

6

8

DDR_A_DM0

10

12

14

DDR_A_D7

16

18

DDR_A_D12

20

DDR_A_D13

22

24

DDR_A_DM1

26

28

M_CLK_DDR0

30

M_CLK_DDR#0

32

34

DDR_A_D14

36

DDR_A_D15

38

40

42

DDR_A_D20

44

DDR_A_D21

46

48

50

NC

A11

A7

A6

A4

A2

A0

S0#

NC

G2

DDR_A_DM2

52

54

DDR_A_D22

56

DDR_A_D23

58

60

DDR_A_D28

62

DDR_A_D29

64

66

DDR_A_DQS#3

68

DDR_A_DQS3

70

72

DDR_A_D30

74

DDR_A_D31

76

78

DDR_CKE1

80

82

84

DDR_A_MA14

86

88

DDR_A_MA11

90

DDR_A_MA7

92

DDR_A_MA6

94

96

DDR_A_MA4

98

DDR_A_MA2

100

DDR_A_MA0

102

104

DDR_A_BS1

106

DDR_A_RAS#

108

DDR_CS0#

110

112

M_ODT0

114

DDR_A_MA13

116

118

120

122

DDR_A_D36

124

DDR_A_D37

126

128

DDR_A_DM4

130

132

DDR_A_D38

134

DDR_A_D39

136

138

DDR_A_D44

140

DDR_A_D45

142

144

DDR_A_DQS#5

146

DDR_A_DQS5

148

150

DDR_A_D46

152

DDR_A_D47

154

156

DDR_A_D52

158

DDR_A_D53

160

162

M_CLK_DDR1

164

M_CLK_DDR#1

166

168

DDR_A_DM6

170

172

DDR_A_D54

174

DDR_A_D55

176

178

DDR_A_D60

180

DDR_A_D61

182

184

DDR_A_DQS#7

186

DDR_A_DQS7

188

190

DDR_A_D62

192

DDR_A_D63

194

196

R326 10K_0402_5%R326 10K_0402_5%

198

200

202

204

1 2

R325 10K_0402_5%R325 10K_0402_5%

1 2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

M_CLK_DDR0 4

M_CLK_DDR#0 4

R59

R59

1 2

0_0402_5%

0_0402_5%

DDR_CKE1 4

DDR_A_BS1 4

DDR_A_RAS# 4DDR_A_BS04

M_CLK_DDR1 4

M_CLK_DDR#1 4

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

DDRII-SODIMMA

DDRII-SODIMMA

DDRII-SODIMMA

NTV00 LA5661P M/B

NTV00 LA5661P M/B

NTV00 LA5661P M/B

7 35Tuesday, December 08, 2009

7 35Tuesday, December 08, 2009

7 35Tuesday, December 08, 2009

1

PM_EXTTS#0 5

0.4

0.4

0.4

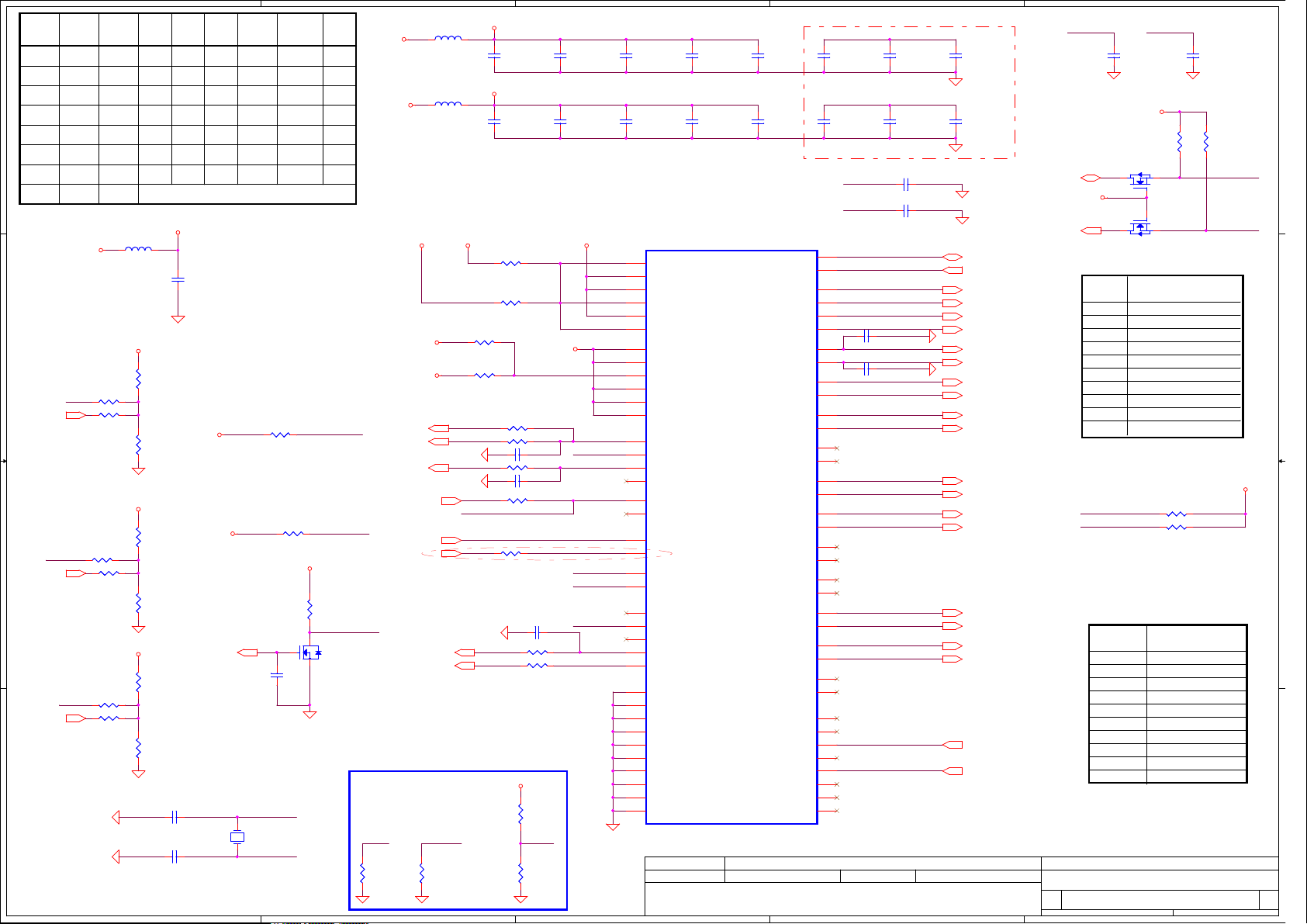

Page 8

5

PCI

SRC

CPU

CLKSEL1

0

FSA

CLKSEL0

MHz

266

MHz

1000

MHz

MHz

33.30

14.318 96.0 48.0

DOT_96

MHz

USB

MHz

FSC FSB REF

CLKSEL2

0 1000 133 33.31 14.318 96.0 48.0

0 1001 200 33.30 14.318 96.0 48.0

0 1001 166 33.31 14.318 96.0 48.0

D D

1 1000 333 33.30 14.318 96.0 48.0

1 1000 100 33.31 14.318 96.0 48.0

1 1001 400 33.30 14.318 96.0 48.0

1 1 1

+1.5VM_CK505

R19

R19

@

@

1 2

+1.5VS

FBMH1608HM601-T_0603

FBMH1608HM601-T_0603

@

@

C679

C679

R203

R203

2.2K_0402_5%

2.2K_0402_5%

1 2

R208

R208

0_0402_5%

0_0402_5%

R536

R536

1K_0402_5%

1K_0402_5%

1 2

R216

R216

0_0402_5%

0_0402_5%

R237

R237

10K_0402_5%

10K_0402_5%

1 2

R235

R235

0_0402_5%

0_0402_5%

+1.05VS

R222

R222

470_0402_5%

470_0402_5%

1 2

12

12

R205

@R205

@

1K_0402_5%

1K_0402_5%

+1.05VS

R213

R213

470_0402_5%

470_0402_5%

1 2

12

12

R215

@R215

@

0_0402_5%

0_0402_5%

+1.05VS

R234

R234

470_0402_5%

470_0402_5%

1 2

12

12

R236

@R236

@

0_0402_5%

0_0402_5%

C244 22P_0402_50V8JC244 22P_0402_50V8J

14.31818MHZ_16PF_DSX840GA

14.31818MHZ_16PF_DSX840GA

C243 22P_0402_50V8JC243 22P_0402_50V8J

C C

FSA

CPU_BSEL05

FSB

CPU_BSEL15

B B

FSC

CPU_BSEL25

A A

1

2

10U_0805_10V4Z

10U_0805_10V4Z

CLK_ENABLE#33

Reserved

+3VS

+3VS

100P_0402_50V8J

100P_0402_50V8J

Y1

Y1

R22

R22

C29

CLK_XTAL_IN

12

CLK_XTAL_OUT

1 2

R174

R174

10K_0402_5%

10K_0402_5%

@C29

@

H_STP_CPU#

10K_0402_5%

10K_0402_5%

H_STP_PCI#_R

1 2

10K_0402_5%

10K_0402_5%

+3VS

R435

@R435

@

1 2

13

D

D

Q31

@

Q31

2

@

2N7002_SOT23-3

2N7002_SOT23-3

G

G

S

S

For PCI2_TME:0=Overclocking of CPU and SRC allowed

(ICS only) 1=Overclocking of CPU and SRC NOT allowed

Routing the trace at least 10mil

5

4

+3VM_CK505

L15

+3VS

+1.05VS

L15

1 2

FBMH1608HM601-T_0603

FBMH1608HM601-T_0603

L14

L14

1 2

FBMH1608HM601-T_0603

FBMH1608HM601-T_0603

250 mA

1

C237

C237

10U_0805_10V4Z

10U_0805_10V4Z

2

+1.05VM_CK505

80 mA

1

C198

C198

10U_0805_10V4Z

10U_0805_10V4Z

2

1

2

1

2

SA000020K00 (Silego : SLG8SP556VTR )

+1.5VM_CK505 +3VM_CK505

+1.05VM_CK505

+1.5VM_CK505

CLK_48M_CR21

CLK_PCH_48M12

CLK_PCH_14M13

VGATE13,22,33

H_STP_CPU#13

H_STP_PCI#13

CLK_EN

CLK_PCI_LPC22

CLK_PCI_PCH11

For ITP_EN, 0 =SRC8/SRC8#; 1 = ITP/ITP#

For PCI4_SEL, 0 = Pin24/25 : DOT96 / DOT96#

Pin28/29 : LCDCLK / LCDCLK#

ITP_EN PCI2_TME

1 2

1 = Pin24/25 : SRC_0 / SRC_0#

Pin28/29 : 27M/27M_SS

PCI4_SEL

R228

R228

10K_0402_5%

10K_0402_5%

R231

R231

10K_0402_5%

10K_0402_5%

1 2

4

R16

R16

1 2

0_0603_5%

0_0603_5%

R15

@R15

@

1 2

0_0603_5%

0_0603_5%

R13

R13

1 2

0_0603_5%

0_0603_5%

R14

@R14

@

1 2

0_0603_5%

0_0603_5%

1 2

1 2

@

@

1 2

C233 33P_0402_50V8K

C233 33P_0402_50V8K

1 2

@

@

1 2

C242 33P_0402_50V8K

C242 33P_0402_50V8K

VGATE

1 2

R92 0_0402_5%R92 0_0402_5%

CLK_EN

R84 0_0402_5%@R84 0_0402_5%@

1 2

+3VM_1.5VM_R

+1.05VM_CK505

+1.05VM_1.5VM_R

R19622_0402_5% R19622_0402_5%

R20222_0402_5% R20222_0402_5%

R21733_0402_5% R21733_0402_5%

@

@

1 2

C677 33P_0402_50V8K

C677 33P_0402_50V8K

R21933_0402_5% R21933_0402_5%

1 2

R22033_0402_5% R22033_0402_5%

1 2

+3VS

R229

R229

10K_0402_5%

10K_0402_5%

1 2

@

@

R230

R230

10K_0402_5%

10K_0402_5%

1 2

C210

C210

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C214

C214

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+3VM_CK505

FSA

FSB

FSB

FSC

H_STP_CPU#

H_STP_PCI#_R

CLK_XTAL_IN

CLK_XTAL_OUT

PCI2_TME

PCI4_SEL

PCI4_SEL

ITP_ENITP_EN

3

1

C234

C234

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

1

C208

C208

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

55

6

12

72

19

27

66

31

62

52

23

38

20

2

7

8

1

11

53

54

5

4

13

14

15

16

17

18

3

22

26

69

30

34

59

42

73

3

1

C238

C238

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

1

C206

C206

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

U12

U12

VDD_SRC

VDD_REF

VDD_PCI

VDD_CPU

VDD_48

VDD_PLL3

VDD_CPU_IO

VDD_PLL3_IO

VDD_SRC_IO

VDD_SRC_IO

VDD_IO

VDD_SRC_IO

USB_0/FS_A

FS_B/TEST_MODE

REF_0/FS_C/TEST_

REF_1

CKPWRGD/PD#

NC

CPU_STOP#

PCI_STOP#

XTAL_IN

XTAL_OUT

PCI_1

PCI_2

PCI_3

PCI_4/SEL_LCDCL

PCIF_5/ITP_EN

VSS_PCI

VSS_REF

VSS_48

VSS_IO

VSS_CPU

VSS_PLL3

VSS_SRC

VSS_SRC

VSS_SRC

VSS

SLG8SP556VTR_QFN72_10X10

SLG8SP556VTR_QFN72_10X10

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Close to U12

+3VM_1.5VM_R

CPU_0

CPU_0#

CPU_1

CPU_1#

LCDCLK/27M

SRC_2

SRC_2#

SRC_3

SRC_3#

SRC_4

SRC_4#

SRC_6

SRC_6#

SRC_7

SRC_7#

SRC_9

SRC_9#

SRC_10

SRC_10#

SRC_11

SRC_11#

CLKREQ_3#

CLKREQ_4#