Page 1

321

4

D

1.0 INPUT& RT2011.sch

C3103-11.sch

C

B

2.0 DC_DC & G a m ma.sch

C3103-12.sch

3.0 PANE L.sch

C3103-13.sch

4.0 MCU. sch

C3103-14.sch

ECN.sch

ECN.sch

D

C

B

A

1 2 34

Title

B

Date: 31-Mar-20 05 Sheet of

File: F:\P- DV D\D L 31 03\C 3103R -1. DDB Drawn By:

DL3103 驱动板原理图

Number RevisionSize

15

A

Page 1 of 5 2005-3-31 10:16

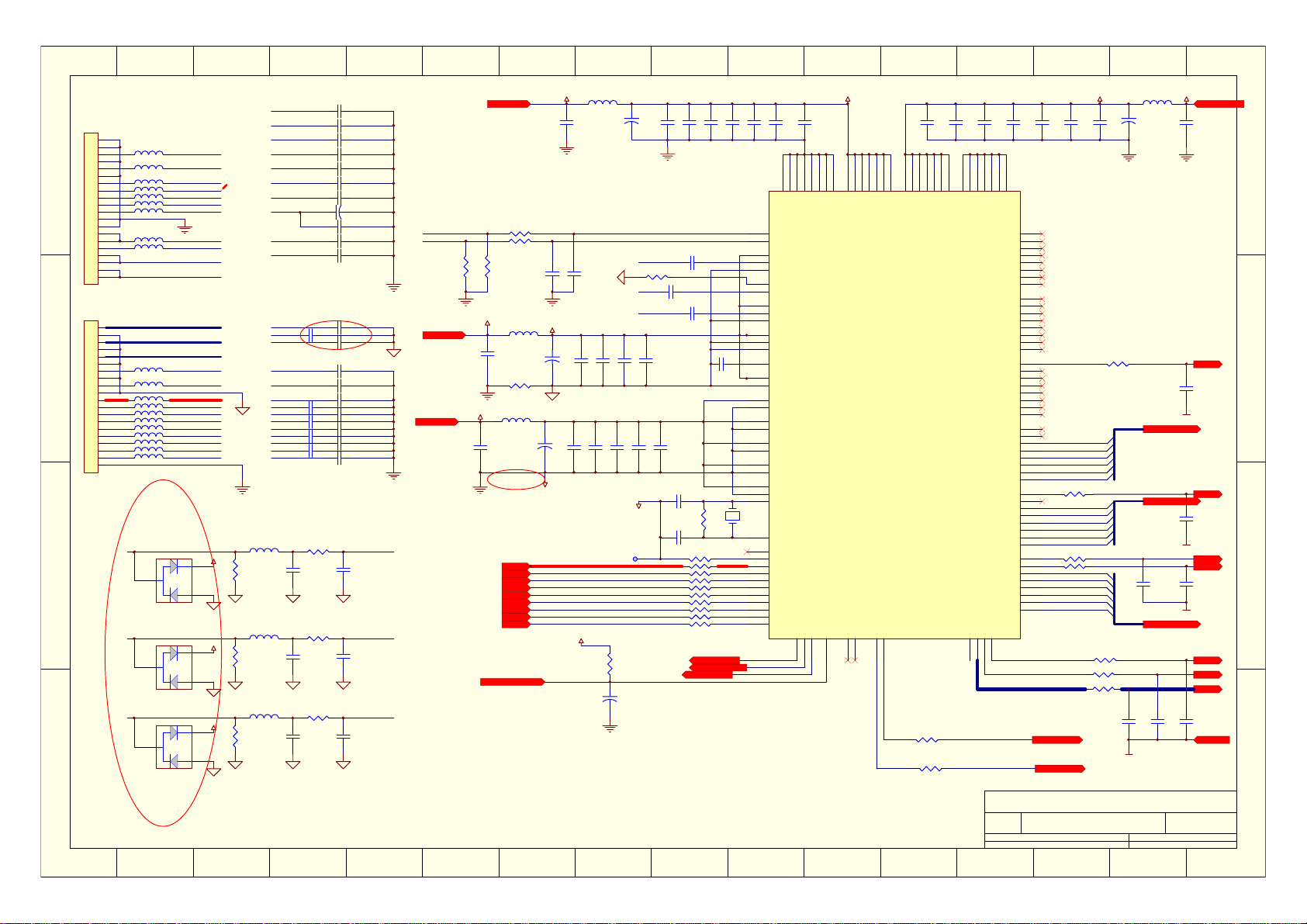

Page 2

151413121110987654321

FB109

3DVCC

FBSMT

1 2

1 2

C150

0.1uF

T47uF/16V

C151

0.1uF

C152

0.1uF

1 2

12

12

+

12

+

C111

C153

0.1uF

1 2

PLL_GND

1

R113

100K

C174

T10uF/16V

1 2

B

R105 1M-10M

C156 47nF

G

R

C155

0.1uF

1 2

C154

C157

0.1uF

0.1uF

1 2

1 2

1TP102

C112

C113

0.1uF

0.1uF

1 2

AHS

AVS

C158 47nF

C160 47nF

12

C167

22pF

C168

12

22pF

1

2

3

4 5

1

2

3

4 5

RTD_SCK

RTD_SDIO

RTD_SCS

C114

0.1uF

1 2

1 2

0.1uF

12

R117

1M

C115

0.1uF

1 2

C161

12

12R115 10k

12R116 100ohm

8RP101

7

6

33RP

8RP102

7

6

33RP

C116

0.1uF

1 2

101

103

94

93

92

96

95

99

98

97

90

91

88

89

100

87

78

77

79

82

84

83

85

86

75

76

73

Y101

24.576MHz

74

80

81

122

114

115

116

117

118

119

120

121

C117

0.1uF

1 2

GNDO9GNDO24GNDO37GNDO52GNDO65GNDO

AHS

AVS

ADC_B_ VDD

B

ADC_B_ GND

SOG

G

ADC_R_ VDD

R

ADC_R_ GND

ADC_VDD

ADC_GND1

ADC_GND0

ADC_REFIO

GUARD_VDD

GUARD_GND

DPLL_VDD

DPLL_GND

APLL1_ VDD

APLL1_ GND

APLL2_ VDD

APLL2_ GND

APLL3_ VDD

APLL3_ GND

PLL_GUARD_VDD

PLL_GUARD_GND

XI

XO

PLL_TEST1

PLL_TEST2

BCLK

B0

B1

B2

B3

B4

B5

B6

B7

1 2

R103

1K

3PVCC

1 2R101 33ohm

1 2R102 33ohm

R104

2K

1 2

3AVCC

C143

0.1uF

1 2

C142

0.1uF

1 2

PCB

3DVCC

FB127

FBSMT

R430

DNC

FB125

FBSMT

铜皮处理

ADC_VCC

12

12

+

C144

22uF/16V

PLL_GND

C145

22pF

1 2

12

+

C146

22uF/16V

1 2

C110

0.1uF

1 2

1 2

C147

12pF

C148

0.1uF

1 2

C149

0.1uF

C178 22pF

PANEL_PW

C179 22pF

J101

1

1

2

2

FB101 FBSMT

D

C

10

11

12

13

14

15

16

17

18

19

20

CON20

J102

10

11

12

13

14

15

16

17

18

19

20

CON20

4

4

5

5

6

6

7

7

8

8

9

9

10

11

12

13

14

15

16

17

18

19

20

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

11

12

13

14

15

16

17

18

19

20

FB102 FBSMT

FB103 FBSMT

FB104 FBSMT

FB105 FBSMT

FB106 FBSMT(DNS)

FB129 FBSMT

FB10 7 120 Ohm

FB108 FBSMT

FB114 FBSMT

FB115 FBSMT

FB116 FBSMT

FB117 FBSMT

FB118 FBSMT

FB119 FBSMT

FB120 FBSMT

FB121 FBSMT

FB122 FBSMT

FB123 FBSMT

FB124 FBSMT

3

3

PANEL_PW

RTD_RESET

N/P

RTD_SCK

RTD_SCS

RTD_SD IO

1R#

VCC

BL-SW

BL-GND

BL-9V

B/VGA

G/VGA

R/VGA

HSIN

VSIN

CKB

UV0

UV1

UV2

UV3

UV4

UV5

UV6

UV7

RTD_RESE T

N/P

RTD_SCK

RTD_SCS

RTD_SD IO

1R#

VCC

BL-SW

BL-9V

B/VGA

G/VGA

R/VGA

HSIN

VSIN

CKB

UV0

UV1

UV2

UV3

UV4

UV5

UV6

UV7

C102 22pF

C103 22pF

C104 22pF

C105 22pF(DNS)

C106 22pF

1 2C101 T100uF/16V

C107 0.1uF

C108 22pF

C109 0.1uF

C180 TVS

C180 TVS

C182 TVS

C135 22pF

C136 22pF

C137 22pF

C128 22pF

C138 22pF

C129 22pF

C139 22pF

C130 22pF

C140 22pF

C131 22pF

C141 22pF

HSIN

VSIN

3PVCC

3AVCC

input interfac e

L103

R112

100ohm

C163

5p

R111 100ohm

C164

5p

R124 100ohm

C172

5p

C165

22pF

C166

22pF

C173

22pF

B

CKB

UV0

UV1

UV2

UV3

UV4

UV5

UV6

G

R

UV7

RTD_RESET

RESET BY 8051

CKB

UV0

UV1

UV2

UV3

UV4

UV5

UV6

UV7

R3DVCC

L102

R108

75ohm

R109

75ohm

R123

75ohm

FEB_0603

L101

FEB_0603

FEB_0603

B/VGA

D101

B

3

BAT54S

D102

3

BAT54S

D103

3

A

BAT54S

3AVCC

2

2

3

1

1

G/VGA

3AVCC

2

2

3

1

1

R/VGA

3AVCC

2

2

3

1

1

R3DVCC 2.5DVCCR2.5 DVCC

C119

C120

C121

C118

0.1uF

0.1uF

1 2

102

105

124

GNDO

GNDO

106

VCCO10VCCO23VCCO38VCCO51VCCO66VCCO

123

VCCO

VCCK11VCCK26VCCK54VCCK71VCCK

0.1uF

1 2

1 2

126

109

39

VCCK

VCCK

GNDK12GNDK25GNDK53GNDK72GNDK

RTD201 1

PWM031PWM1/REF_CLK32DDC_SCL

SDI/SDO

SCLK

SCSB

RESET#

112

113

111

104

DDC_SDA

108

107

R126

100ohm

12

R127

100ohm

12

0.1uF

1 2

40

GNDK

DHS33DCLK34DVS60DEN

110

DBBLU0

DBBLU1

DBBLU2

DBBLU3

DBBLU4

DBBLU5

DBBLU6

DBBLU7

DBGRN0

DBGRN1

DBGRN2

DBGRN3

DBGRN4

DBGRN5

DBGRN6

DBGRN7

DBRED0

DBRED1

DBRED2

DBRED3

DBRED4

DBRED5

DBRED6

DBRED7

DABLU0

DABLU1

DABLU2

DABLU3

DABLU4

DABLU5

DABLU6

DABLU7

DAGRN0

DAGRN1

DAGRN2

DAGRN3

DAGRN4

DAGRN5

DAGRN6

DAGRN7

DARED0

DARED1

DARED2

DARED3

DARED4

DARED5

DARED6

DARED7

59

DDC_SDA

DDC_SCL

C122

0.1uF

1 2

125

GNDK

Title

A0

Date: 31-Mar-2005 Sheet of

File: F: \P- D V D \D L3103 \C3 103R- 1.D D B Drawn B y:

C123

0.1uF

1 2

127

128

1

2

3

4

5

6

7

8

13

14

15

16

17

18

19

20

21

22

27

28

29

30

35

36

41

42

43

44

45

46

47

48

49

50

55

56

57

58

61

62

63

64

67

68

69

70

Pin Na mes Visible

Pin Numbers Visible

Pin Nu mber s Visib le

TCON-1

TCON-0

TCON-ECLK

DDC_SDA

DDC_SCL

DL3103驱动板原理图

Number RevisionSize

C124

0.1uF

1 2

BOA0

BOA1

BOA2

BOA3

BOA4

BOA5

GOA0

GOA1

GOA2

GOA3

GOA4

GOA5

ROA0

ROA1

ROA2

ROA3

ROA4

ROA5

1 2R122 33ohm

1 2R121 33ohm

1 2R128 33ohm

12R118 33ohm

12R119 33ohm

12R120 33ohm

1 2

C125

0.1uF

12

+

C126

T47uF/10V

DGND

12R106 33ohm

STH

STV

CKH

C175

12pF

DGND

FB110

FBSMT

C169

20pF(DNS)

25

C176

20pF(DNS)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

DGND

BOA[0:5]

CPV

GOA[0:5]

DGND

POL

LD

DGND

ROA[0:5]

1 2

C127

0.1uF

OE

2.5DVCC

OE

C162

20pF(DNS)

CPV

C170

20pF(DNS)

POL

LD

C171

20pF(DNS)

STH

STV

CKH

C177

20pF(DNS)

DGND

16

D

C

B

A

Page 2 of 5 2005-3-31 10:16

Page 3

54321

6

FB201

3.3V

0ohm

D

C

B

A

C201

T47uF/10V

1 2 3 4 5 6

GNDP

C202

106

GNDP

FB203

0ohm

FB204

0ohm

R201

100K

C211

330pF

R202

10K

GNDP

C212

NC

GNDP

GNDP

GNDP

GNDP

1

2

3

R159 =

R239

7.2K IF AVDD 8.0 V;

100K_1%

6.8K IF AVDD 8.4V ;

6.2K IF AVDD 8.8V .

GNDP GNDP

1

2

3

4

VIN

VSS

ON/OFF

S-L2980

R240

U201A

COMP

FB

SD

PGND

ADP1610

U202A

VOUT

6.2k

8

SS

7

RT

6

IN

5

SW

C213

1uF_25V

C221

1uF_25V

C222

1uF_25V

5

4

NC

L201

4.7uH

R203

0ohm

R211

R212

NC

223

GNDP

GNDP

D202

2

2

3

3

1

1

BAT54S

AVDD

D204

1

1

3

3

2

2

BAT54S

D205

1

1

3

3

2

2

BAT54S

+8.7V

V1AVDD

R226

15K

VR201

GNDP

50K

2

1 3

R241

15K

C232

10uF

3.3V

D201

Vsw

SB07-03C

R213

330ohm

C224

2.2uF_25V

R227

510ohm

R204

619k

R125 =

549K IF AVDD 8.0 V;

590K IF AVDD 8.4V ;

619K IF AVDD 8.8V .

R214

100K_1%

C215

NC

D203

UDZ16B

UDZ10B

AVDD

GNDP

D206

3

4

C203

NC

C214

2.2uF_25V

C223

1uF_25V

GNDP

VADJ

FB202

120 Ohm

C204

22uF/16V

(Option:470uf )筿秆筿甧

GNDP

16V/1mA

2

R244

C216

2

2.2uF_25V

1

1

-10V/1mA

2

R245

C225

2

2.2uF_25V

1

1

25

U203A

+

1

-

AD8565

GNDP GNDP

C205

10uF

(Option:100uF )筿秆筿甧

GNDP

3.3V

C233

226/10V

8.8V/50mA

AVDDLCD_VDD V1

C206

0.1uF

VGH

VGL

VCOM

8.7V

V1

R205

100_1%

R206

10_1%

8.54V

V2

R207

510_1%

R216

20_1%

7.59V

V3

R217

100_1%

R218

300_1%

7.02V

V4

R219

620_1%

R220

100_1%

6.49V

V5

R229

3600_1%

5.4V

V6

R231

2000_1%

R232

20_1%

5.04V

V7

R233

500_1%

C207

0.1uF

GNDP

C208

0.1uF

GNDP

C218

0.1uF

GNDP

C217

0.1uF

GNDP

C226

0.1uF

GNDP

C227

0.1uF

GNDP

C228

0.1uF

GNDP

V8

Tit le

Orcad B

Date: 31-Mar-2005 Sheet of

File: F:\P-DVD\DL3103\C3103R-1.DDB Drawn By:

3.78V

V8

GNDP

GNDP

GNDP

GNDP

GNDP

GNDP

GNDP

C209

0.1uF

C210

0.1uF

C219

0.1uF

C220

0.1uF

C229

0.1uF

C230

0.1uF

C231

0.1uF

35

D

C

B

A

R208

2000_1%

R209

20_1%

3.43V

V9

R210

3600_1%

2.33V

V10

R222

620_1%

R223

100_1%

1.80V

V11

R224

300_1%

R225

100_1%

1.23V

V12

R234

510_1%

R235

20_1%

0.26V

V13

R236

100_1%

R237

10_1%

0.1V

V14

R238

15_1%

R243

20_1%

GNDP

DL3103

驱动板原理图

Number RevisionSize

Page 3 of 5 2005-3-31 10:16

Page 4

54321

6

D

C

B

J303

A

Option net

R304 0.1uF

LCD_VDD

LCD_VDD

STV

STV

STH

STH

1

1

2

2

3

3

1*3P 1.0MM HEAD E R

FB304 FBSMT

C310

0.1uF

BL-GND

BL-SW

BL-9V

C1

22uF/16V

STV_U

STH_R

C311

0.1uF

INV

EDGSL

U/D

R/L

R310

1K

POL

STV_D

OE

CPV

STV_U

EDGSL

LCD_VDD

V9

VGL

V2

VGH

V6

U/D

VCOM

AVDD

V14

V11

V8

V5

V3

RP301 33RP

1 8

2 7

3 6

4 5

R311 33ohm

R312 33ohm

RP302 33RP

1 8

2 7

3 6

4 5

R313 33ohm

R320 33ohm

R321 33ohm

RP303 33RP

1 8

2 7

3 6

4 5

R322 33ohm

R323 33ohm

ROA[0:5]

GOA[0:5]

STH_L

INV

STH_R

BOA[0:5]

V10

V12

V13

AVDD

V1

V4

V7

CKH

ROA5

ROA4

ROA3

ROA2

ROA1

ROA0

GOA5

GOA2

GOA1 G1

GOA0

LCD_VDD

LD

BOA5

BOA4

BOA3

BOA2

BOA1

BOA0

VCOM

SMD CONNECT (FFC Cable Type)2x30pin 2connectors

注:以下迹线尽可能做到等长!

POL

STV_D

OE

CPV

STV_U

GND

EDGSL

V9

VGL

V2

VGH

V6

U/D

VCOM

GND

AVDD

V14

V11

V8

V5

V3

GND

R5

R4

R3

R2

R1

R0

GND

GND

G3GOA3

G2

G0

STH_L

INV

GND

DCLK

STH_R

LD

B5

B4

B3

B2

B1

B0

R/L

V1

V4

V7

V10

V12

V13

AVDD

GND

VCOM

DGND

VCC

J301

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

C301

T47uF/10V

VCC

CON30

J302

1

G5

2

G4GOA4

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

V3.3

FB305

120 Ohm

CON30

C319

10uF

U301 AMC1117-ADJ

3

VIN

C302

C303

0.1uF

10uF

U302 AMC1117-ADJ

3

VIN

C313

C314

0.1uF

10uF

ADJ

1

ADJ

1

3

4

R324

1K

PANEL_PW

VOUT

TAB

VOUT

TAB

U303

RT9701

vin

ce

2

4

T47uF/10V

2

4

vout

vout

GND

2

BL-GND

1 2 3 4 56

V3.3

FB301

R305

2K

R306

3.3K

C304

C305

0.1uF

120 Ohm

FB302

120 Ohm

C306

10uF

C307

10uF

FB303

2.5DVCC

LCD_VDD

LCD_VDD

C317

10uF

120 Ohm

RTD 2.5DVCC

R314

1K

C316

C315

T100uF/6.3V

R315

1K

1

5

Title

Orcad B

Date: 31-Mar-2005 Sheet of

File: F:\P- D V D \ D L 3103 \C 3103R - 1. D D B Drawn By :

0.1uF

C320

T100uF/6.3V

DL3103驱动板原理图

Number RevisionSize

C321

0.1uF

3DVCC

C308

0.1uF

RTD 3DVCC

C309

D

3AVCC

0.1uF

RTD 3AVCC

3PVCC

C318

0.1uF

RTD 3PVCC

C

B

A

4

5

Page 4 of 5 2005-3-31 10:16

Page 5

321

4

D

C403

0.1uF

1 2

R431

1 2

1K

MCU_VCC

C404

10uF_16V

MCU_VCC

1 2

R428

47K

ALE/PROG_

35

12

DGND

MCU_VCC

12

12

12

12

R408

47k

12

R409

47k

R412

R410

R411

47k

15K

47K

R429

IR#

2

112

1 2R417 33ohm

1 2R418 33ohm

1 2R419 33ohm

1 2R420 33ohm

1 2R421 33ohm

1 2R422 33ohm

1 2R423 33ohm

PANEL_PW

IICSCL

IICSDA

RTD_RESET

RTD_SDIO

RTD_SCK

RTD_SCS

PANEL_PW

IICSCL

RTD_RESET

RTD_SDIO

RTD_SCK

RTD_SCS

36

33

MCU_VCC

32

PSEN_

31

P2.7

P2.6

P2.5

P2.4

P2.3

P2.2

P2.1

P2.0

EA_/VPP

R416

MCU_VCC

NC

R427

30

47K

29

28

27

26

25

24

N/P

DGND

12

+

RST

12

R407

1K

10

R432

2

P1.0

10K

3

P1.1

4

P1.2

5

P1.3

6

P1.4

7

P1.5

8

P1.6

9

P1.7

14

P3.2

15

P3.3

16

P3.4

17

P3.5

18

P3.6

19

P3.7

13

P3.1

11

P3.0

U402

8954

Y401

1 2

24M/crystal

R415 1M

1 2

C407

22pF

1 2

RST

44

VCC

XTAL220XTAL121VSS

C408

22pF

1 2

2

2

1

1

P0.043P0.142P0.241P0.340P0.439P0.538P0.637P0.7

P4.3

22

12

DGND

MCU_VCC

R402

R401

10k

10k

1 2

1 2

IICSDA

IICSCL IICSDA

C

8

5

6

4

U401

5DVCC

TEST

SDA

SCL

GND

IS24C16(SO-8)

7

3

A2

2

A1

1

A0

DGND

C401

0.1uF

1 2

3DVCC

FB402

120 Ohm

12

12

12

+

C402

R405

R406

T47uF/10V

47k

47k

DGND

BL-SW

J401

1*3P 1.0MM HEADER

RS232 and ISPFor Debug

DDC_SDA

1

1

DDC_SCL

2

2

3

3

DDC_SDA

DDC_SCL

B

D

C

B

A

Title

B

Date: 3 1-Mar-2005 Sheet of

1 2 3 4

File: F:\P-DVD\DL31 03\C31 03R-1. DDB Drawn By:

Number RevisionSize

DL3103驱动板原理图

55

A

Page 5 of 5 2005-3-31 10:16

Loading...

Loading...