AZMIC AZ100EP16FETR2, AZ100EP16FETR1, AZ100EP16FET, AZ100EP16FELR2, AZ100EP16FELR1 Datasheet

...

AZ100EP16FE

ECL/PECL High Speed VCSEL Driver with

Variable Output Swing or Limiting Amplifier

1630 S. STAPLEY DR., SUITE 125 • MESA, ARIZONA 85204 • USA • (480) 962-5881 • FAX (480) 890-2541

www.azmicrotek.com

ARIZONA MICROTEK, INC.

FEATURES

• Silicon-Germanium for High Speed

Operation

• <100ps Typical Rise/Fall Times

• Optimized for 0.622 to 2.5Gbps Fiber

Applications

• Available in a 3x3mm MLP Package

DESCRIPTION

The AZ100EP16FE is a Silicon–Germanium (SiGe) differential VCSEL driver with variable output swing or

limiting post amplifier. The 100EP16FE is optimized for OC-12,OC-24, OC-48, Ethernet, Sonnet, Fiber Channel or

related applications at data rates up to 2.5Gbps. An input controls the amplitude of the Q/Q¯ outputs, which allows

compensation for differing VCSEL characteristics.

The operational range of the 100EP16FE control input, V

CTRL

, is from V

REF

(full swing) to VCC (small swing).

For post amplifier applications, maximum swing is achieved by leaving the V

CTRL

pin open or by tying it to the

negative supply pin (V

EE

). Simple control of the output swing can be obtained by a variable resistor between the

V

REF

and VCC pins, with the wiper driving V

CTRL

. A typical application circuit is described in this Data Sheet.

The 100EP16FE also provides a V

REF

output which functions as a DC bias for input AC coupling to the device.

The V

REF

pin should be used only as a bias for the 100EP16FE as its current sink/source capability is limited. When

used, the V

REF

pin should be bypassed to ground via a 0.01µF capacitor.

The maximum DC output current should be kept below 16mA. Connecting each output (Q/Q¯) to V

EE

with a

180Ω resistor is typically used. The load is then AC coupled from the output. DC and AC symmetrical loading of

the Q/Q¯ outputs will provide the best output wave shape.

Under open input conditions for D/D¯, the Q/Q¯ outputs are not guaranteed.

NOTE: Specifications in ECL/PECL tables are valid when thermal equilibrium is established.

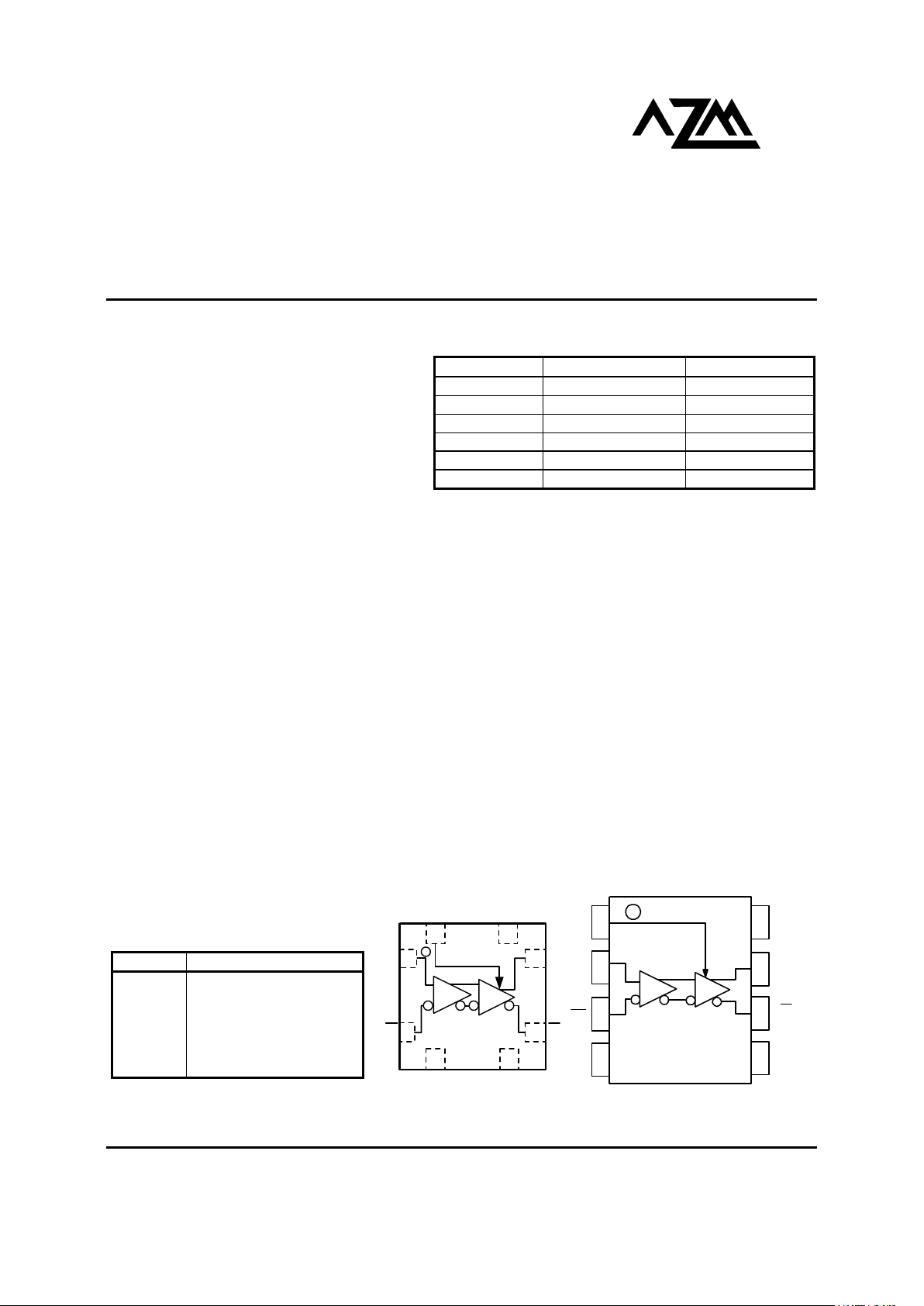

PACKAGE AVAILABILITY

PACKAGE PART NO. MARKING

MLP 8 AZ100EP16FEL AZM16D

MLP 8 T&R AZ100EP16FELR1 AZM16D

MLP 8 T&R AZ100EP16FELR2 AZM16D

TSSOP 8 AZ100EP16FET AZHP16FE

TSSOP 8 T&R AZ100EP16FETR1 AZHP16FE

TSSOP 8 T&R AZ100EP16FETR2 AZHP16FE

PIN DESCRIPTION

PIN FUNCTION

D, D¯ Data Inputs

V

CTRL

Output Swing Control

Q, Q¯ Data Outputs

V

REF

Reference Voltage Output

V

CC

Positive Supply

V

EE

Negative Supply

8

4

5

6

3

2

1

7

V

CC

D

V

EE

Q

Q

V

REF

D

V

CTRL

8

5

6

7

4

3

2

1

V

CC

D

V

EE

Q

Q

V

REF

D

V

CTRL

8 MLP (TOP VIEW) 8 TSSOP

AZ100EP16FE

March 2002 * REV - 4 www.azmicrotek.com

2

Absolute Maximum Ratings are those values beyond which device life may be impaired.

Symbol Characteristic Rating Unit

VCC PECL Power Supply (VEE = 0V) 0 to +4.5 Vdc

VI PECL Input Voltage (V

EE

= 0V) 0 to +4.5 Vdc

VEE ECL Power Supply (VCC = 0V) -4.5 to 0 Vdc

VI ECL Input Voltage (VCC = 0V) -4.5 to 0 Vdc

I

OUT

Output Current --- Continuous

--- Surge

22

44

mA

TA Operating Temperature Range -40 to +85

°C

T

STG

Storage Temperature Range -65 to +150

°C

100K ECL DC Characteristics (VEE = -3.0V to -3.6V, VCC = GND)

-40°C 0°C 25°C 85°C

Symbol Characteristic

Min Typ Max Min Typ Max Min Typ Max Min Typ Max

Unit

VOH Output HIGH Voltage1 -1095 -890 -1035 -870 -1000 -920 -840 -940 -760 mV

VOL

Output LOW Voltage

1

V

CTRL

= V

REF

-1935 -1745 -1905 -1715 -1885 -1790 -1695 -1830 -1640 mV

VOL

Output LOW Voltage

1

V

CTRL

= V

CC

-1140 -950 -1120 -930 -1100 -1005 -910 -1055 -865 mV

V

REF

Reference Voltage -1700 -1500 -1700 -1500 -1700 -1500 -1700 -1500 mV

IIH

Input HIGH Current

D, D¯

V

CTRL

80

400

80

400

80

400

80

400

µA

IIL

Input LOW Current 0.5 0.5 0.5 0.5

µA

IEE Power Supply Current 20 26 35 21 27 36 21 28 36 22 31 38 mA

1. Each output is terminated through a 180Ω resistor to VEE.

100K LVPECL DC Characteristics (VEE = GND, VCC = +3.3V)

-40°C 0°C 25°C 85°C

Symbol Characteristic

Min T

yp

Max Min T

yp

Max Min T

yp

Max Min T

yp

Max

Unit

VOH Output HIGH Voltage

1,2

2205 2410 2265 2430 2300 2380 2460 2360 2540 mV

VOL

Output LOW Voltage

2

V

CTRL

= V

REF

1365 1555 1395 1585 1415 1510 1605 1470 1660 mV

VOL

Output LOW Voltage

2

V

CTRL

= V

CC

2160 2350 2180 2370 2200 2295 2390 2245 2435 mV

V

REF

Reference Voltage 1600 1800 1600 1800 1600 1800 1600 1800 mV

IIH

Input HIGH Current

D, D¯

V

CTRL

80

400

80

400

80

400

80

400

µA

IIL

Input LOW Current 0.5 0.5 0.5 0.5

µA

IEE Power Supply Current 20 26 35 21 27 36 21 28 36 22 31 38 mA

1. For supply voltages other that 3.3V, use the ECL table values and ADD supply voltage value.

2. Each output is terminated through a 180Ω resistor to V

EE

.

AC Characteristics (V

EE

= -3.0 to -3.6V, VCC = GND, V

CTRL=VREF

or VEE = GND, VCC = +3.0V to +3.6V, V

CTRL=VREF

)

-40°C 0°C 25°C 85°C

Symbol Characteristic

Min Typ Max Min Typ Max Min Typ Max Min Typ Max

Unit

f

max

Maximum Toggle

Frequency

5

>6 >6 >6 >6 GHz

t

PLH

/ t

PHL

Input to Output

Delay

(Diff)

(SE)

100 150

155

240 100 150

155

240 100 150

155

240 120 170

175

280

ps

t

SKEW

Duty Cycle Skew

1

(Diff) 4 20 4 15 4 15 4 15 ps

Vpp Minimum Input Swing2 150 150 150 150 mV

V

CMR

Common Mode Range3

V

EE

+

2.0

V

CC

V

EE

+

2.0

V

CC

V

EE

+

2.0

V

CC

V

EE

+

2.0

V

CC

V

Av Small Signal Gain4 28 dB

tr / tf

Output Rise/Fall Times Q

(20% - 80%)

130 130 130 130 ps

1. Duty cycle skew is the difference between a t

PLH

and t

PHL

propagation delay through a device.

2. V

PP

is the minimum peak-to-peak differential input swing for which AC parameters are guaranteed.

3. The V

CMR

range is referenced to the most positive side of the differential input signal. Normal operation is obtained if the HIGH level falls within the

specified range and the peak-to-peak voltage lies between V

PP

(min) and 1V. The lower end of the V

CMR

range varies 1:1 with VEE and is equal to VEE + 2V.

4. Differential input, differential output. 180Ω to VEE on Q/Q¯ outputs with 50Ω AC coupled load.

5. See Figure 2.

AZ100EP16FE

March 2002 * REV - 4 www.azmicrotek.com

3

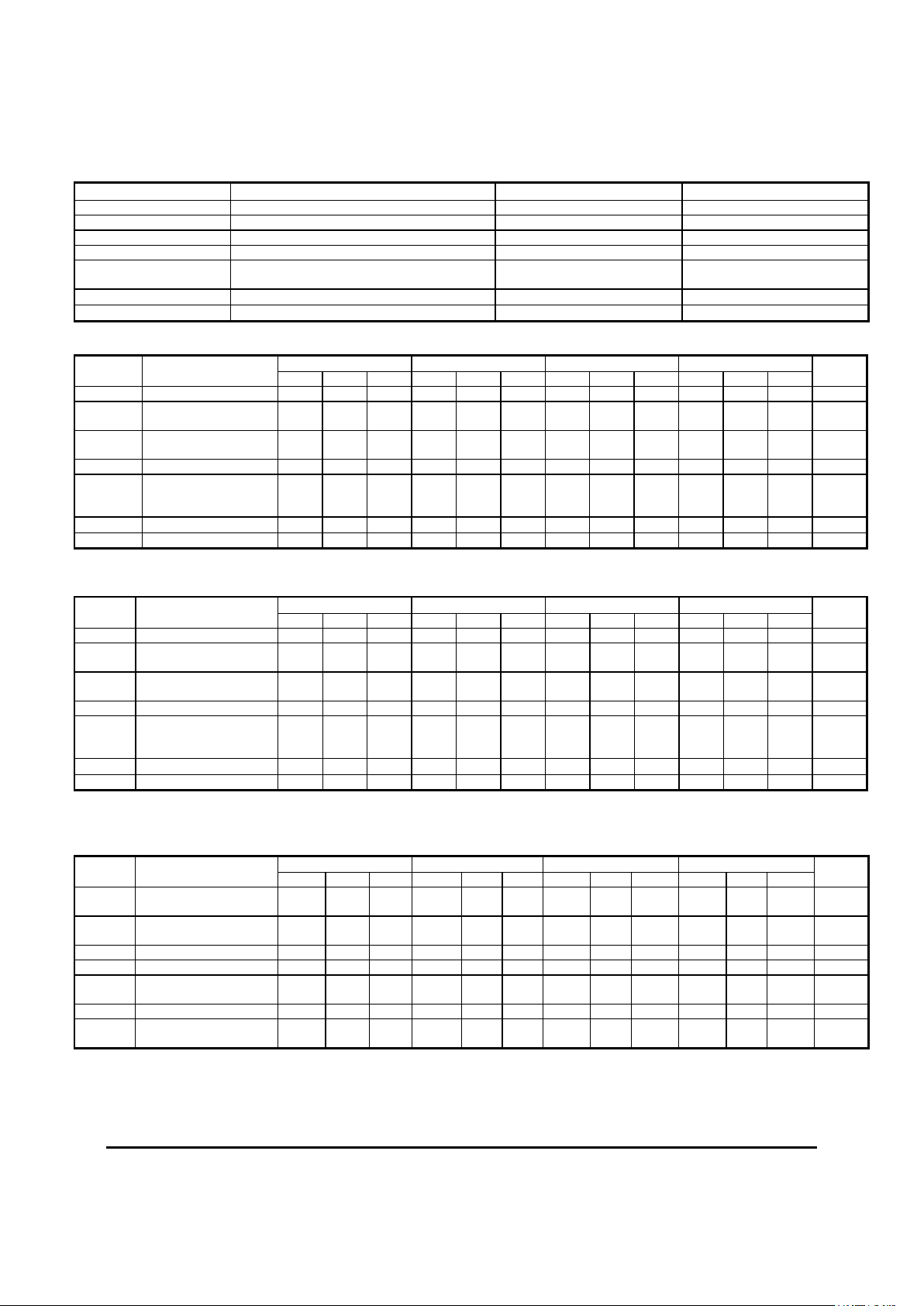

50 50180

- 3.3V

180

5K

8

5

6

7

4

3

2

1

V

CC

D

V

EE

Q

Q

V

REF

D

V

CTRL

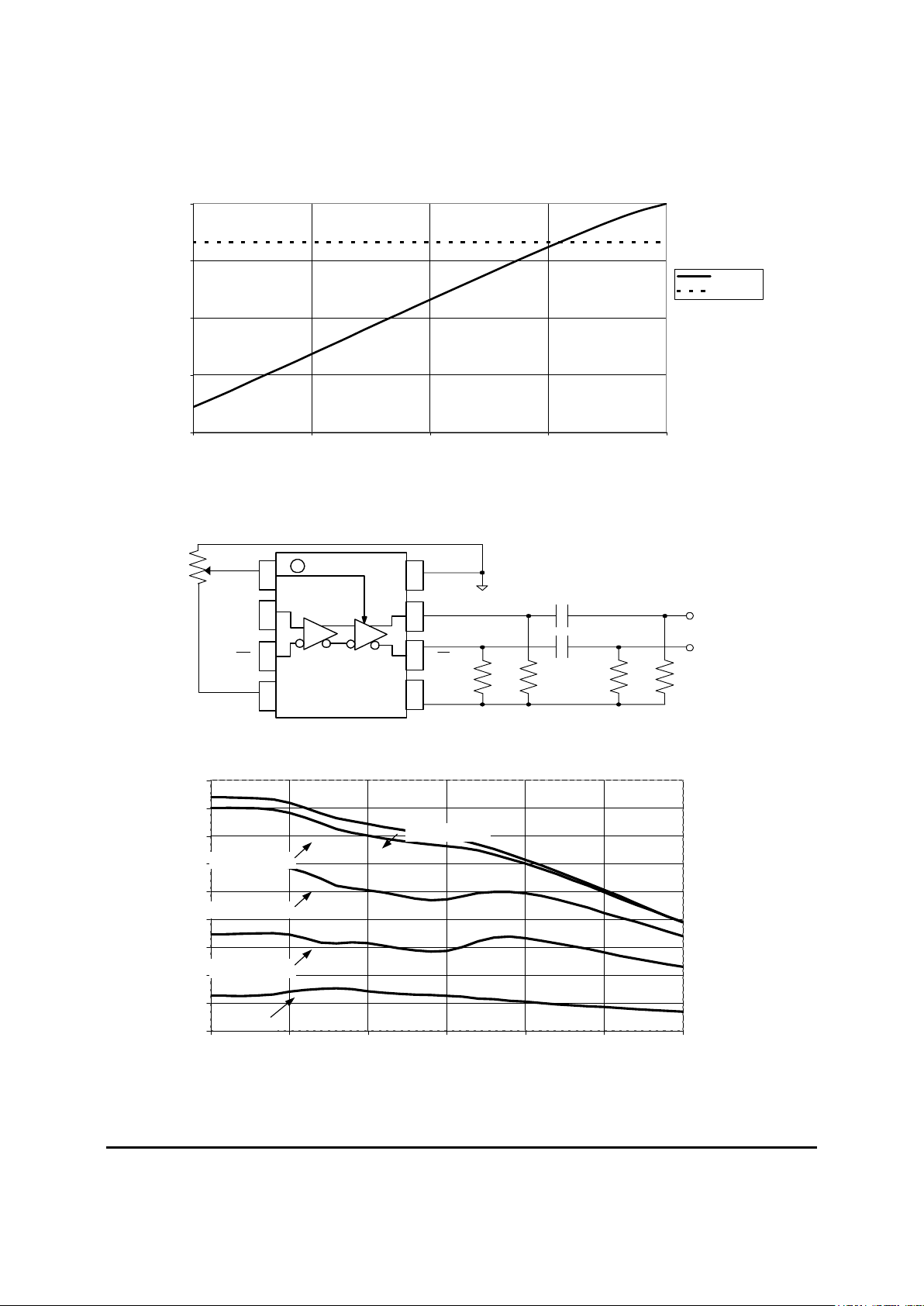

Figure 2: Large Signal Performance*

0

100

200

300

400

500

600

700

800

900

0 1000 2000 3000 4000 5000 6000

FREQUENCY (MHz)

V

OUTpp

(mV)

V

CTRL=VCC

V

CTRL=VCC

-2.0V

V

CTRL=VCC

-1.5V

V

CTRL=VCC

-1.0V

V

CTRL=VCC

-0.5V

Typical AZ100EP16FE Voltage Output Swing at +25C, VEE Nom

(see Figure 1)

1.240 V (100K ECL)

0

25

50

75

100

0.0 0.4 0.8 1.2 1.6

V

CTRL

(V)

V

SWING

(% pk-pk differential)

%OUT

100K ECL

Figure 1: Typical Application

*Measured using a 750mV differential input source at 50% duty cycle.

Loading...

Loading...