Page 1

Page 1 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Features

Microsoft Azure Sphere SoC based module

solution for advanced end-to-end IOT security

Based on MediaTek MT3620AN Wi-Fi SoC

- 1x 500MHz Arm Cortex A7 application

processor with 4MB SRAM

- 2x 200MHz Arm Cortex M4F cores,

each with 64KB SRAM

- 4MB embedded RAM (shared)

- 16MB QSPI flash memory

- Dual-band 2.4/5GHz 802.11 a/b/g/n Wi-Fi

Module I/O peripheral support

- 3x ISU interfaces, pre-configured for

UART, SPI, I2C

- ADC/GPIO: 3x 12-bit ADC inputs (or GPIOs)

- PWM/GPIO: 9x PWM outputs

(or up to 24 GPIOs)

- RTC (requires VBAT supply)

- Programming & recovery interface

Microsoft Visual Studio IDE for accelerated

application software development & debug

OTA authentication & updates (device lifetime)

Dimensions: 33mm x 22mm x 3.5mm

Onboard dual-band 2.4/5GHz chip antenna

- (Pulse W3006)

Operating temperature:

- -35C to +85°C

(Note: For industrial temperature range,

please use the U.FL version module)

Certifications:

- FCC, IC, CE, MIC, RoHS (pending)

Note: Microsoft Azure Sphere OS support for

some MT3620 features is still being added

Applications

IoT edge devices

Smart home appliances / security

Smart retail

Remote access

Building automation

Factory automation

For more info on Azure Sphere MT3620 modules,

visit: http://avnet.me/mt3620-modules

To purchase an Azure Sphere MT3620 Starter Kit

visit: http://avnet.me/mt3620-kit

AES-MS-MT3620-M-G

Azure Sphere

MT3620 module

(with chip antenna)

Page 2

Page 2 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

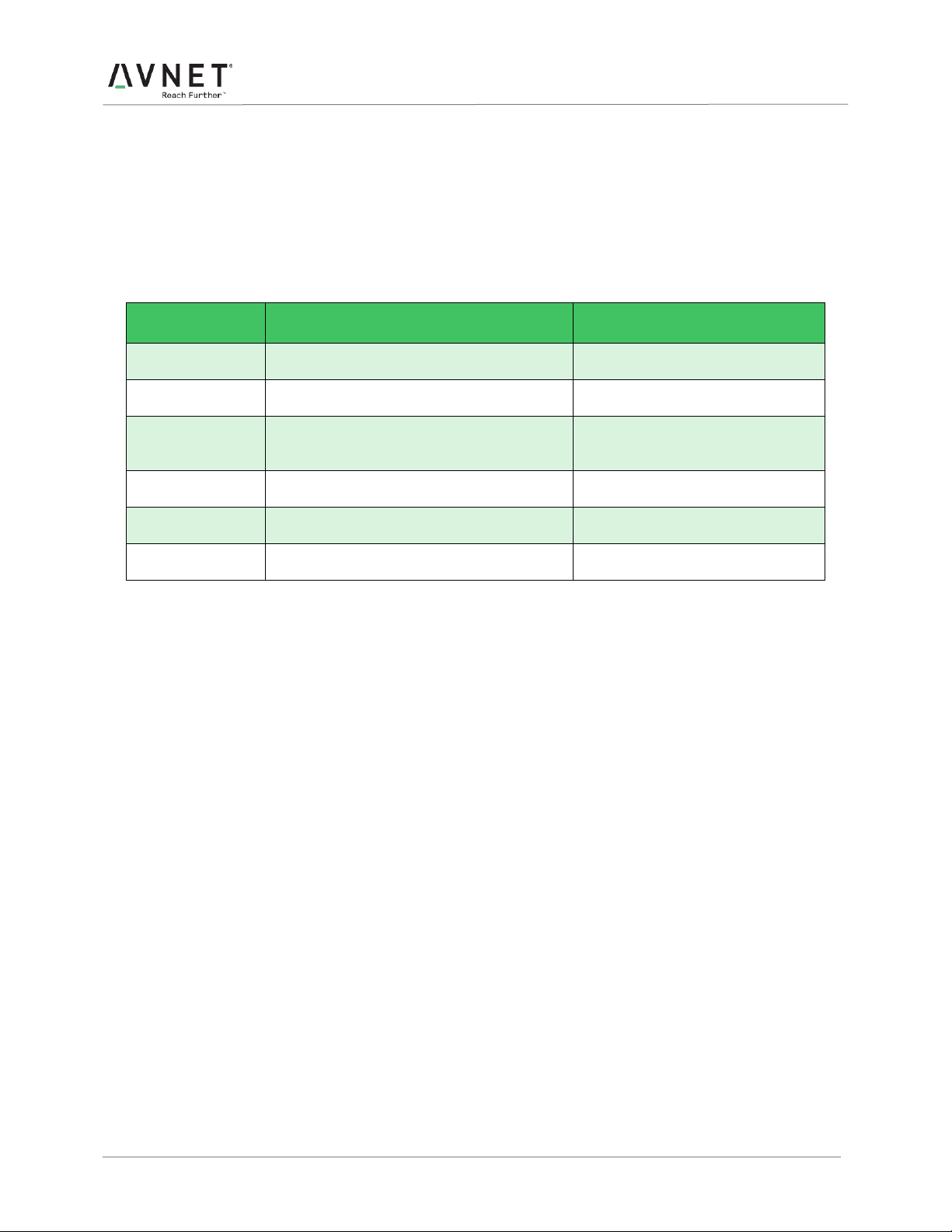

Version

Date

Comment

1.0

05/07/2019

Initial release, new document scope, photos, pinout detail and content

1.1

05/07/2019

Added FCC Module Statement (USA)

1.2

05/16/2019

Updated OEM instructions

Part Number

Description

AES-MS-MT3620-M-G

Azure Sphere MT3620 Module (chip antenna)

Product Page: http://avnet.me/mt3620-modules

AES-MS-MT3620-SK-G

Azure Sphere MT3620 Starter Kit

Product Page: http://avnet.me/mt3620-kit

Document Control

Document Version: 1.0

Document Date: 05/07/2019

Document Author: Peter Fenn

Document Classification: Public

Document Distribution: Public

Version History

Ordering Information

Page 3

Page 3 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Table of Contents

Features ...................................................................................................................... 1

Applications ................................................................................................................. 1

Document Control ....................................................................................................... 2

Ordering Information ................................................................................................... 2

Overview ..................................................................................................................... 6

Module Block Diagram ................................................................................................ 7

Module Application Development and Programming .................................................. 8

Development Computer Software Installation ...................................................................................... 8

Module Interfaces with the Development Computer ............................................................................ 8

Module Integration onto an OEM Board ...................................................................... 9

Module Power Interfaces ..................................................................................................................... 9

Wi-Fi Network Settings ......................................................................................................................... 9

Wi-Fi Subsystem ................................................................................................................................ 10

Wi-Fi Antenna ..................................................................................................................................... 10

A7 Application Processor ................................................................................................................... 10

M4F IO Processors ............................................................................................................................ 10

Flash Memory ..................................................................................................................................... 10

Pluton Security Subsystem ................................................................................................................ 10

Real Time Clock (RTC) ...................................................................................................................... 10

Peripheral Serial Interfaces ................................................................................................................ 10

Other I/O Interfaces ............................................................................................................................ 10

MT3620 Bootstrap Pins ...................................................................................................................... 11

Module Placement and Ground plane requirements ......................................................................... 12

Module Pinout Locations .................................................................................................................... 13

Module Pinout Table .......................................................................................................................... 14

Electrical Specifications ............................................................................................ 16

Absolute Maximum Ratings ............................................................................................................... 16

Recommended Operating Conditions ................................................................................................ 16

DC Characteristics ............................................................................................................................. 16

Current Consumption ......................................................................................................................... 17

RF Characteristics .................................................................................................... 18

Wi-Fi 2.4GHz Band RF Receiver Specifications ................................................................................ 18

Wi-Fi 2.4GHz Band RF Transmitter Specifications ............................................................................ 20

Wi-Fi 5GHz Band RF Receiver Specifications ................................................................................... 21

Wi-Fi 5GHz Band RF Transmitter Specifications ............................................................................... 22

Page 4

Page 4 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Wi-Fi RF Receiver Blocking Specifications ........................................................................................ 23

Mechanical Specifications ......................................................................................... 24

Module Dimension Details ................................................................................................................. 24

Tape and Reel Packaging .................................................................................................................. 25

Soldering and Cleaning Recommendations .............................................................. 26

Optimum Soldering Reflow Profile ..................................................................................................... 26

Cleaning ............................................................................................................................................. 26

Certifications and Compliance .................................................................................. 27

RoHS Compliance .............................................................................................................................. 27

Regulatory Compliance ...................................................................................................................... 27

FCC and ISED Regulatory Notices (USA and Canada) .................................................................... 27

Modification statement ................................................................................................................... 27

Interference statement ................................................................................................................... 27

RF Radiation Exposure Statement ................................................................................................. 27

FCC Class B Digital Device Notice (USA) ..................................................................................... 28

FCC Module Statement (USA) ....................................................................................................... 28

CAN ICES-003 (B) ......................................................................................................................... 28

Labeling Requirements for the OEM Host Board ........................................................................... 28

29

FCC Requirements for User Manual of the OEM Host Board: ...................................................... 29

IC Requirements for User Manual of the OEM Host Board: .......................................................... 30

FCC Host 15B and 15C Compliance Statement (USA) ................................................................. 30

CE Statement (Europe) ...................................................................................................................... 30

CE Labeling Requirements (Europe) ............................................................................................. 30

OEM Instructions ................................................................................................................................ 31

Shipping, Handling and Storage ............................................................................... 31

Shipping ............................................................................................................................................. 31

Handling ............................................................................................................................................. 31

Moisture Sensitivity (MSL) ................................................................................................................. 31

Storage ............................................................................................................................................... 32

Contact Information ................................................................................................... 32

Legal Information ................................................................ ................................ ...... 33

Limitations .......................................................................................................................................... 33

Avnet Module License and Product Warranty .................................................................................... 33

Appendix-A: Programming Adaptor Footprint ........................................................... 35

Page 5

Page 5 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Table of Figures

Figure 1 – Simplified MT3620 SoC Block Diagram ........................................................................................... 6

Figure 2 – AES-MS-MT3620-M-G Module Block Diagram ............................................................................... 7

Figure 3 – Module with dual-band Chip Antenna ............................................................................................ 10

Figure 4 – OEM board Footprint for AES-MS-MT3620-M-G Module .............................................................. 12

Figure 5 – AES-MS-MT3620-M-G Module Pinout .......................................................................................... 13

Figure 6 – AES-MS-MT3620-M-G Module Mechanical Details ...................................................................... 24

Figure 7 – Tape and Reel Details ................................................................................................................... 25

Figure 8 – Recommended Soldering Profile for Lead-Free Solder ................................................................. 26

Figure 9 – Module Pinout to Recommended Service & Debug Interface Connector ..................................... 36

Page 6

Page 6 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

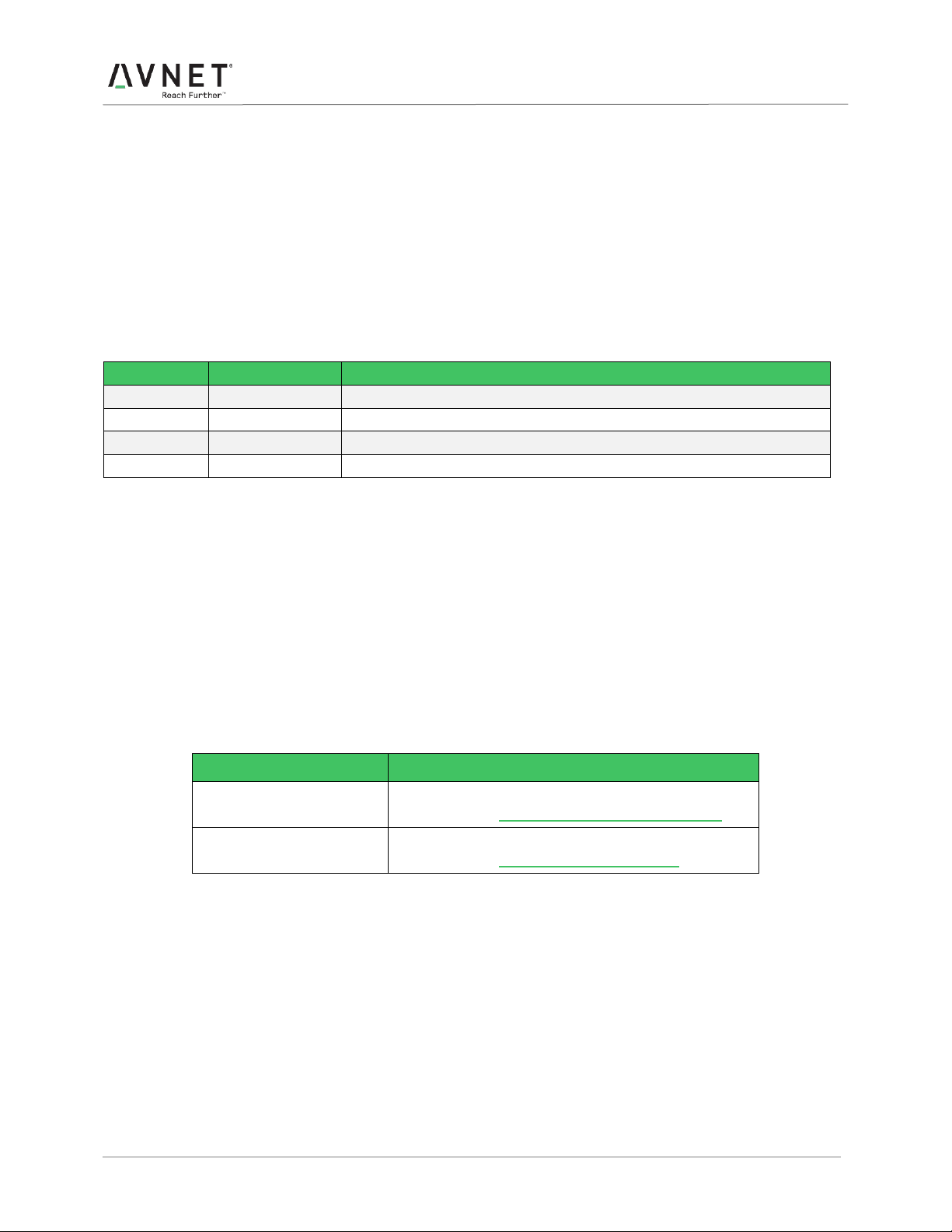

Overview

The AES-MS-MT3620-M-G is a small form-factor, tri-core Wi-Fi SoC module, intended for use as a secure

Wi-Fi client, in internet-connected IoT applications. Avnet’s production-ready, certified module comes fitted

with a single dual-band chip antenna, for cost-optimized application in 2.4 GHz or 5GHz Wi-Fi networks

Based on the MediaTek MT3620AN SoC, this is a new class of connected SoC IoT device that facilitates

“end-to-end security”. User applications can target it’s 500 MHz ARM Cortex-A7 core as well as two general

purpose 200 MHz ARM Cortex-M4F I/O subsystem cores designed to support real-time requirements. The

on-chip peripherals (GPIO, UART, I2C, SPI, I2S, PWM and ADC) can be mapped to any of these three

user-accessible processor cores.

Figure 1 – Simplified MT3620 SoC Block Diagram

Further differentiators of the MT3620 device are its built-in Pluton security subsystem (with dedicated CM4F

core) for secure boot and secure system operation, its dual-band 802.11 a/b/g/n Wi-Fi connectivity, as well

as integration of on-chip PMU, RTC plus FLASH and SRAM memory. Wi-Fi based OTA firmware and user

application updates (using certificate-based authentication) are hosted by Microsoft for the device lifetime

The Cortex-A7 application processor runs Microsoft’s Azure Sphere Secure OS. Custom user applications

are developed in C using Microsoft’s Visual Studio IDE, which includes user-friendly debugging features

such as single-step execution, breakpoints and watch-points (supported via a dedicated service UART)

The module allows easy design migration and end-product enhancements. By integrating all necessary

support and RF front end circuitry onto a small 33 mm x 22 mm module, Avnet has reduced the design time

for implementing Sphere-based solutions. Developers can leverage the module’s wireless regulatory

certifications (pending) for their end product, saving considerable certification costs and testing time.

The Avnet Azure Sphere MT3620 chip module has a 33mm x 22mm form-factor, with 66 pad castellated

“stamp-hole” footprints. It has an on board chip antenna (Pulse W3006) with a 26MHz crystal oscillator.

Microsoft Visual Studio IDE is used for software development of applications that target this Azure Sphere

MT3620 Module. Instructions for installing this Integrated Development Environment, as well as it’s Azure

Sphere SDK companion application and necessary drivers, are detailed (with examples) in the User Guide

for Avnet’s Azure MT3620 Sphere Starter Kit

Page 7

Page 7 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Online authentication and firmware updates are supported for the MT3620 device lifetime.

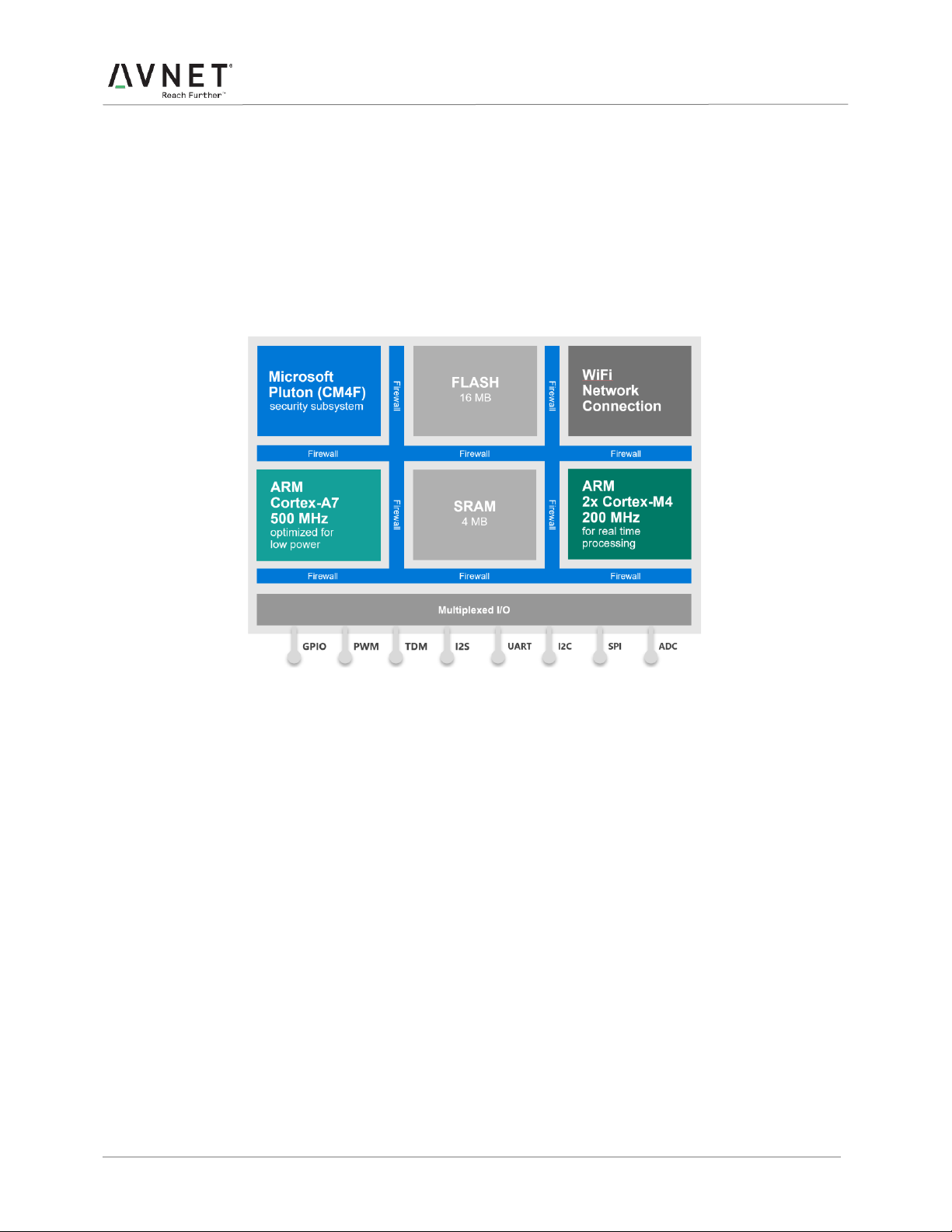

Module Block Diagram

Figure 2 – AES-MS-MT3620-M-G Module Block Diagram

Page 8

Page 8 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Module Application Development and Programming

Development Computer Software Installation

In depth instructions are provided at the Microsoft Getting started with Azure Sphere webpage:

https://aka.ms/AzureSphereSDK

Microsoft’s Getting Started with Azure Sphere page details the download & install of two software items:

1) Azure Sphere SDK Preview for Visual Studio from the Visual Studio Marketplace

2) Visual Studio 2017 version 15.7 or later (free Community edition is sufficient)

as well as USB driver installation for a wired interface between a development computer and the module

Microsoft’s Azure Sphere SDK provides the following:

The azsphere command-line utility for managing devices, images, and deployments

Libraries for application development

Visual Studio extensions to support Azure Sphere development, debug and flash programming

Microsoft’s Visual Studio IDE provides a sophisticated development environment for editing, building and

debugging custom embedded C applications (a GCC cross-compiler and GDB debugger provide the

underlying build and debug tools)

For application development targeting this module, it is recommended that hardware and software

prototyping be done using the Avnet Azure Sphere MT3620 Starter Kit http://avnet.me/mt3620-kit )

Module Interfaces with the Development Computer

The module is designed to support up to four wired interfaces with the development computer.

Three 4-wire UART interfaces (SERVICE, RECOVERY and DEBUG) dedicated for connection with

the host development computer are pinned-out, each with hardware flow-control.

A 3-wire SWD interface is also pinned-out

RESET and RECOVERY (via DEBUG_RTS during boot) signals determine the module operating

mode

Page 9

Page 9 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Interface Pins

Description

Notes

3V3

Main input voltage to the module.

3.3V (+/- 10%)

Powered by an external PMU

or DC/DC convertor

3V3_RTC

Real Time Clock power input to module

Powered by external battery,

or connect this to the 3V3 rail

VREF_ADC

Reference voltage for on-chip A/D

convertor

Powered by external reference

voltage, or connect to the

MT3620 2.5V LDO output

EXT_PMU_EN

MT3630 output to enable / disable

external PMU or DC/DC convertor

May be left unconnected

PMU_EN

MT3630 input to enable / disable the

internal PMU

May be left unconnected

WAKEUP

MT3630 input to wake-up the A7

processor from power-saving sleep mode

May be left unconnected

Module Integration onto an OEM Board

Module Power Interfaces

To power this module, the OEM board must be able to supply a maximum of 2.5 Watts at 3.3V.

Prior to power-up of the module, the following interfaces need to be attended to:

Wi-Fi Network Settings

For Wi-Fi connected user applications, the module’s Wi-Fi network settings need to be configured by one of

the following methods:

a) In the application software (using #define statements), OEM factory-programmed into the module

b) Via a companion nRF52840 BLE device integrated onto the OEM’s end-product board

c) Via the SERVICE UART interface with a Windows-10 development computer running the

azsphere command-line utility (See Appendix-A detail of the suggested PCB footprint to support

temporary attachment of an FTDI FT4232HQ based USB to serial adaptor)

Upon power-up and connection to the designated Wi-Fi network, the module will communicate with the

Microsoft Azure Sphere Security Service, which authenticates and manages one or more of the following

downloads/uploads with the module:

Push of Azure Sphere OS firmware updates to the module

Deployment of custom application software to the module

Reporting of Sphere OS and application versions plus error information to the Azure Sphere Server

The Microsoft Azure Sphere Security Service will also authenticate data transfers between the custom user

application executing on the module and Microsoft Azure (or other) cloud services

Page 10

Page 10 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Figure 3 – Module with

dual-band Chip Antenna

Wi-Fi Subsystem

Dual-band 2.4/5GHz 802.11 a/b/g/n Wi-Fi (20 MHz channels only)

Has an N968 Andes 32bit MCU

Uses an external 26 MHz crystal oscillator on the module

Has an integrated 5GHz Balun

Uses external 2.4GHz Balun and Diplexer devices on the module

Wi-Fi Antenna

The module is fitted with an on-board dual-band

chip antenna for 2.4GHz and 5GHz operation

(Pulse Electronics antenna p/n: W3006)

An inline switched RF probe connector

is provided to facilitated RF conducted measurements

A7 Application Processor

1x 500MHz Arm Cortex A7 application processor

core, with 4MB SRAM (shared)

M4F IO Processors

2x 200MHz Arm Cortex M4F IO processor cores,

each with 64KB SRAM

The module pins-out the IO0_TXD and IO1_TXD pins from their dedicated UARTs

SWD interface based debug and programming of M4F IO MCU cores may at later date be enabled

Flash Memory

16MB 100MHz (on-die) QSPI flash memory

Pluton Security Subsystem

1x Cortex M4F MCU, dedicated RAM, ROM and GP timers, system control outputs

Real Time Clock (RTC)

Low-power RTC with timer/time of day control over system power (32KHz crystal oscillator)

Peripheral Serial Interfaces

Three ISU serial interfaces are pinned-out. Their accessible pins are limited to that needed for support of:

ISU0: UART, max rate=3Mbps (4-wire)

ISU1: SPI , max rate=40 MHz (5-wire)

ISU2: I2C , max rate=1MHz (2-wire)

Other I/O Interfaces

All pinned-out I/O pins (including ISU interfaces listed above) can be individually configured as GPIO pins.

A subset of these can be configured as:

PWM outputs

ADC inputs

EXT INT inputs

Page 11

Page 11 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

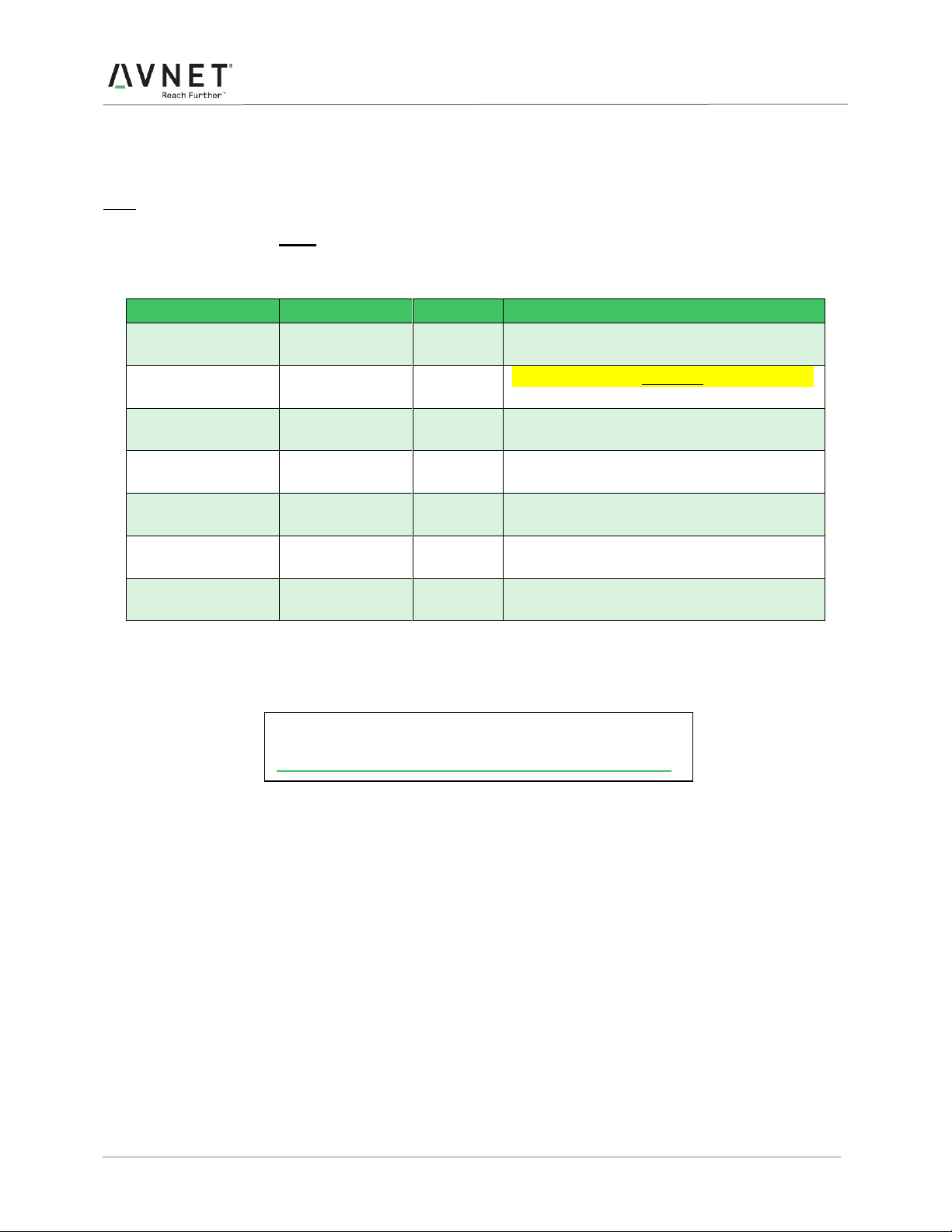

Function

Pin Name

Strapping

Recommendation

Normal/Test mode

DEBUG_TXD

Pull-Down

Pull-down resistor is on module

Mode = Normal

Recovery mode

DEBUG_RTS

Pull-Down

Pull-down resistor required on OEM board!

Controlled via PC interface, - if present

RTC mode

RECOVERY_TXD

Pull-Up

Pull-up resistor is on module

RTC oscillator = 32 kHz crystal

26MHz

IO0_RTS

Pull-Up

MT3620 internal pull-up on module

Oscillator frequency = 26 MHz

26MHz

IO0_TXD

Pull-Down

Pull-down resistor is on module

Oscillator frequency = 26 MHz

N9 JTAG

IO1_TXD

Pull-Down

Pull-down resistor is on module

N9 JTAG = OFF

A7 JTAG

RECOVERY_RTS

Pull-Down

Pull-down resistor is on module

A7 JTAG = OFF

See the MT3620 Product Brief at the Mediatek webpage

for more detail on the MT3620AN SoC device…

https://www.mediatek.com/products/azureSphere/mt3620

MT3620 Bootstrap Pins

Note! Six of the seven bootstrap pins are already strapped on the module.

The DEBUG_RTS signal must however be strapped on the OEM board with a 2K2 pull-down resistor, to

ensure that RECOVERY mode remains disabled (This signal gets driven high to select RECOVERY via an

FTDI device based interface with the development computer when a Debug-Programmer cable is attached)

Page 12

Page 12 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Module Placement and Ground plane requirements

For optimum antenna performance the Ground plane of the OEM board (on which the module is fitted)

needs to be maximized

The GND pads in the antenna area of the module must be connected to this Ground plane

Placement of the module should be 6 mm or more from any corner of the OEM carrier board

A PCB cutout is recommended in the host carrier board beneath the chip antenna (17mm x 7mm)

Figure 4 – OEM board Footprint for AES-MS-MT3620-M-G Module

Page 13

Page 13 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Module Pinout Locations

Figure 5 – AES-MS-MT3620-M-G Module Pinout

Page 14

Page 14 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Module

Pad

MT3620

Pad

MT3620

Net Name

I/O

Pin Function

Pre-Assigned

Starter Kit Function=BLUE

1 GND

GND

2

2,3

3V3

Power

3

2,3

3V3

Power

4

GND

5

13

GPIO0_PWM0

I/O

GPIO / INT in / PWM out

PWM CLICK1

6

14

GPIO1_PWM1

I/O

GPIO / INT in / PWM out

PWM CLICK2

7

15

GPIO2_PWM2

I/O

GPIO / INT in / PWM out

INT_CLICK

8

17

GPIO4_PWM4

I/O

GPIO / INT in / PWM out

GPIO4_LED_APP

9

18

GPIO5_PWM5

I/O

GPIO / INT in / PWM out

GPIO5_LED_WIFI

10

19

GPIO6_PWM6

I/O

GPIO / INT in / PWM out

INT_LSM6DSO

11

21

GPIO8_PWM8

I/O

GPIO / INT in / PWM out

GPIO8_LED_USER_RED

12

22

GPIO9_PWM9

I/O

GPIO / INT in / PWM out

GPIO9_LED_USER_GRN

13

25

GPIO10_PWM10

I/O

GPIO / INT in / PWM out

GPIO10_LED_USER_BLU

14

27

GPIO12

I/O

GPIO / INT in

GPIO12_SW_A

15

28

GPIO13

I/O

GPIO / INT in

GPIO13_SW_B

16

31

GPIO16

I/O

GPIO / INT in

RST CLICK1

17

32

GPIO17

I/O

GPIO / INT in

RST CLICK2

18

39

GPIO26_SCLK0_TXD0

I/O

GPIO / ISU0

UART TXD

19

40

GPIO27_MOSI0_RTS0_SCL0

I/O

GPIO / ISU0

UART RTS / I2C0

20

42

GPIO28_MISO0_RXD0_SDA0

I/O

GPIO / ISU0

UART RXD / I2C0

21

43

GPIO29_CSA0_CTS0

I/O

GPIO / ISU0

UART CTS

22

46

GPIO31_SCLK1_TXD1

I/O

GPIO / ISU1

SPI SCLK / UART1

23

47

GPIO32_MOSI1_RTS1_SCL1

I/O

GPIO / ISU1

SPI MOSI / UART1 / I2C1

24

48

GPIO33_MISO1_RXD1_SDA1

I/O

GPIO / ISU1

SPI MISO / UART1 / I2C1

25

49

GPIO34_CSA1_CTS1

I/O

GPIO / ISU1

SPI CS #1 / UART1

26

50

GPIO35_CSB1

I/O

GPIO / ISU1

SPI CS #2

27

52

GPIO37_MOSI2_RTS2_SCL2

I/O

GPIO / ISU2

I2C

28

53

GPIO38_MISO2_RXD2_SDA2

I/O

GPIO / ISU2

I2C

29

58

GPIO41_ADC0

I/O

GPIO / ADC in

AMBIENT LIGHT SENSOR

30

59

GPIO42_ADC1

I/O

GPIO / ADC in

AN CLICK1

31

60

GPIO43_ADC2

I/O

GPIO / ADC in

AN CLICK2

32

66

VOUT_2V5

AO

33

67

VREF_ADC

AI min 1.8V, max 2.5V

34

81

PMU_EN

I pull-up on module

35

70

WAKEUP

I

Ext. Wakeup Input

pull-up on module

36

69

EXT_PMU_EN

O

Ext. 3V3 regulator enable

37

GND

GND

Module Pinout Table

Page 15

Page 15 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Module

Pad

MT3620

Pad

MT3620

Net Name

I/O

Pin Function

Pre-Assigned

Starter Kit

Function=BLUE

38

GND

GND

39

71

3V3_RTC

Power

min 2.50 V, max 3.63V

40

GND

GND

41

GND

GND

42

88,89

3V3

Power

43

88,89

3V3

Power

44

94

DEBUG_RXD

I

Debug UART

DEBUG_RXD

45

96

DEBUG_RTS

O

Debug UART

(pulled-down / FTDI controlled

strapping state on Starter Kit)

DEBUG_RTS

46

95

DEBUG_TXD

O

Debug UART

(pulled-down on module)

DEBUG_TXD

47

97

DEBUG_CTS

I

Debug UART

DEBUG_CTS

48

98

SWD_DIO

I/O

CM4F SWD

SWD_DIO

49

99

SWD_CLK

I

CM4F SWD

SWD_CLK

50

100

SWO

O

CM4F SWD

SWO

51

125

SYSRST_N

I SYSRST_N

52

127

SERVICE_TXD

O

Service UART

SERVICE_TXD

53

129

SERVICE_RXD

I

Service UART

SERVICE_RXD

54

128

SERVICE_RTS

O

Service UART

SERVICE_RTS

55

130

SERVICE_CTS

I

Service UART

SERVICE_CTS

56

134

RECOVERY_RXD

I

Recovery UART

RECOVERY_RXD

57

135

RECOVERY_TXD

O

Recovery UART

(PU on module)

RECOVERY_TXD

58

136

RECOVERY_RTS

O

Recovery UART

(pulled-down on module)

RECOVERY_RTS

59

137

RECOVERY_CTS

I

Recovery UART

RECOVERY_CTS

60

139

IO0_GPIO86/IO0_TXD

O

IO0_GPIO / IO0_TXD

(pulled-down on module)

IO0_TXD

61

143

IO1_GPIO90/IO1_TXD

O

IO1_GPIO / IO1_TXD

(pulled-down on module)

IO1_TXD

62 - 66

GND

GND

GND pour

67

PADGND

GND

Thermal pad for MT3620

Module Pinout Table (continued)

Note! Azure Sphere OS support for some MT3620 features is still to be released by Microsoft.

eg. GPIO, UART, I2C and SPI peripherals are now supported, but support for the ARM Cortex-M4F cores,

ADC and PWM and functions is at this time still pending.

Page 16

Page 16 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Symbol

Parameter

Max

Unit

3V3

3.3V Supply Voltage

-0.3 to 3.63

V

T

STG

Storage Temperature

-40 to +125

°C

V

ESD

ESD protection (human body model)

2000

V

Symbol

Rating

Min

Typ

Max

Unit

3V3

3.3V supply

2.97

3.3

3.63

V

3V3_RTC

RTC supply

2.5

3.3

3.63

V

T

AMBIENT

Ambient Temperature

-35

-

+85

°C

Symbol

Parameter

Conditions

Min

Max

Unit

V

IL

Input Low Voltage

LVTTL

-0.28

0.8

V

V

IH

Input High Voltage

2.0

3.63

V

V

OL

Output Low Voltage

|IOL| = 4 to 16 mA

-0.28

0.4

V

VOH

Output High Voltage

|IOH| = 4 to 16 mA

2.4

VDD33+0.33

V

RPU

Input Pull-Up Resistance

PU=high, PD=low

40

190

kΩ

RPD

Input Pull-Down Resistance

PU=low, PD=high

40

190

kΩ

Electrical Specifications

Note! The electrical characteristics documented here are for the MT3620AN SoC device only, as defined in

the Mediatek MT3620AN Datasheet and Product Brief documents

Absolute Maximum Ratings

Recommended Operating Conditions

DC Characteristics

Page 17

Page 17 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Power mode

Description

Details

Typical

current

consumption

Hardware

wake-up

latency

Subsystem

Power

State

RTC mode

Only RTC

domain is on.

Memory is not

retained.

Requires a cold

boot to resume

Pluton CM4 subsystem

Off

0.01mA or

0.02mA (*1)

24ms

(crystal and

PLL lock,

PMU time

CA7 subsystem

Off

CM4F I/O subsystems

Off

Wi-Fi subsystem

Off

Buses/peripherals

Off

Worst case

power

consumption

no Wi-Fi

All subsystems

apart from

Wi-Fi running

at full speed

Pluton CM4 subsystem

On

220mA

Worst case

380mA (*2)

N/A, 650us

WiFi

subsystem

resume

latency

CA7 subsystem

On

IO 0/1 CM4

subsystems

On

Wi-Fi subsystem

Light sleep

Buses/peripherals (*3)

On

Worst case

power

consumption

with Wi-Fi

(*2)

All subsystems

running at full

speed, Wi-Fi

very active

Pluton CM4 subsystem

On

520mA (*4)

Worst case

750mA (*2)

N/A

CA7 subsystem

On

IO 0/1 CM4

subsystems

On

Wi-Fi subsystem

On

Buses/peripherals (*3)

On

RF (A or G Band)

On

Flash (*5)

On

Current Consumption

Note *1: 0.01mA/0.02mA with/without external 3.3v source PMIC control switch respectively.

Note *2: The current values are measured under typical case (TT silicon and 25C/1.15V) and

the TDP (max thermal design power) includes simulation worst case condition

(TT/125C/1.15V/MC99 ,MC99 is PTPX power simulation library).

Note *3: It depends on how busy the peripherals are and how they are configured.

Note *4: This data is based on 100% Wi-Fi transmission on the 5GHz band at 14dBm.

Note *5: It depends on the I/O loading and flash power consumption.

Page 18

Page 18 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Parameter

Description

Performance

Min

Typical

Max

Unit

Main

Aux

Frequency range

Center channel frequency

2412

2484

MHz

RX sensitivity

DBPSF, 1 Mbps DSSS

-

-94.6

-97.1

-90.0

dBm

DQPSF, 2 Mbps DSSS

-

-91.6

-94.1

-87.0

dBm

DQPSF, 5.5 Mbps CCK

-

-89.6

-92.1

-85.0

dBm

DQPSF, 11 Mbps CCK

-

-86.6

-89.1

-82.0

dBm

BPSK rate 1/2, 6 Mbps OFDM

-

-91.6

-94.1

-87.0

dBm

BPSK rate 3/4, 9 Mbps OFDM

-

-89.3

-91.8

-86.0

dBm

QPSK rate 1/2, 12 Mbps OFDM

-

-88.5

-91.0

-84.0

dBm

QPSK rate 3/4, 18 Mbps OFDM

-

-86.1

-88.6

-82.0

dBm

16QAM rate 1/2, 24 Mbps OFDM

-

-82.8

-85.3

-81.0

dBm

16QAM rate 3/4, 36 Mbps OFDM

-

-79.4

-81.9

-78.0

dBm

64QAM rate 1/2, 48 Mbps OFDM

-

-75.2

-77.7

-73.0

dBm

64QAM rate 3/4, 54 Mbps OFDM

-

-73.9

-76.4

-71.0

dBm

RX sensitivity

BW=20MHz, Mixed mode

800ns guard interval, Non-STBC

MCS 0, BPSK rate 1/2

-

-90.9

-93.4

-87.0

dBm

Maximum Receive Level

MCS 1, QPSK rate 1/2

-

-87.7

-90.2

-86.0

dBm

MCS 2, QPSK rate 3/4

-

-85.3

-87.8

-84.0

dBm

MCS 3, 16QAM rate 1/2

-

-82.3

-84.8

-81.0

dBm

MCS 4, 16QAM rate 3/4

-

-78.8

-81.3

-77.0

dBm

MCS 5, 64QAM rate 2/3

-

-74.4

-76.9

-74.0

dBm

MCS 6, 64QAM rate 3/4

-

-73.0

-75.5

-71.0

dBm

MCS 7, 64QAM rate 5/6

-

-71.8

-74.3

-69.0

dBm

1 Mbps DSSS

-20

-10

-

dBm

11 Mbps CCK

-20

-10

-

dBm

6 Mbps OFDM

-20

-10

-

dBm

54 Mbps OFDM

-20

-10

-

dBm

HT20 MCS0

-20

-10

-

dBm

HT20 MCS7

-20

-20

-

dBm

RF Characteristics

Wi-Fi 2.4GHz Band RF Receiver Specifications

The specification in table below is measured at the antenna port, which includes the front-end loss.

Page 19

Page 19 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Parameter

Description

Performance

Min

Typical

Max

Unit

Main

Aux

Receive adjacent channel

rejection

BPSK rate 1/2, 6 Mbps OFDM

16

34

-

dBm

BPSK rate 3/4, 9 Mbps OFDM

15

31

-

dBm

QPSK rate 1/2, 12 Mbps OFDM

13

30

-

dBm

QPSK rate 3/4, 18 Mbps OFDM

11

27

-

dBm

16QAM rate 1/2, 24 Mbps

OFDM

8

25

-

dBm

16QAM rate 3/4, 36 Mbps

OFDM

4

23

-

dBm

64QAM rate 1/2, 48 Mbps

OFDM

0

22

-

dBm

64QAM rate 3/4, 54 Mbps

OFDM

-1

22

-

dBm

MCS 0, BPSK rate 1/2

16

33

-

dBm

MCS 1, QPSK rate 1/2

13

29

-

dBm

MCS 2, QPSK rate 3/4

11

26

-

dBm

MCS 3, 16QAM rate 1/2

8

24

-

dBm

MCS 4, 16QAM rate 3/4

4

20

-

dBm

MCS 5, 64QAM rate 2/3

0

18

-

dBm

MCS 6, 64QAM rate 3/4

-1

17

-

dBm

MCS 7, 64QAM rate 5/6

-2

15

-

dBm

Receiver residual PER

All rates, -50dBm input power

- - 0.005

%

Wi-Fi 2.4GHz Band RF Receiver Specifications (continued)

Page 20

Page 20 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Parameter

Description

Performance

Min

Typical

Max

Unit

Frequency range

Center channel frequency

2412

-

2484

MHz

Output power with

spectral mask and EVM

compliance

1 Mbps DSSS

- x

16(1)

-

dBm

11 Mbps CCK

-

16(1)

-

dBm

6 Mbps OFDM

-

16(1)

-

dBm

54 Mbps OFDM

-

16(1)

-

dBm

HT20 MCS 0

-

16(1)

-

dBm

HT20 MCS 7

-

16(1)

-

dBm

Output power with

spectral mask and EVM

compliance

(at -40◦C and 85◦C)

1 Mbps DSSS

-

15(1)

-

dBm

11 Mbps CCK

-

15(1)

-

dBm

6 Mbps OFDM

-

15(1)

-

dBm

54 Mbps OFDM

-

15(1)

-

dBm

HT20 MCS 0

-

15(1)

-

dBm

HT20 MCS 7

-

15(1)

-

dBm

TX EVM

1 Mbps DSSS

-

-

-10

dB

11 Mbps CCK

-

-

-10

dB

6 Mbps OFDM

-

-

-5

dB

54 Mbps OFDM

-

-

-25

dB

HT20 MCS 0

-

-

-5

dB

HT20 MCS 7

-

-

-28

dB

Output power

variation(2)

TSSI closed-loop control across all

temperature range

and channels and VSWR ≦ 1.5:1.

-1.5

-

1.5

dB

Carrier suppression

-

- - -30

dBc

Harmonic output

power

2nd Harmonic

-

-45

-43

dBm/MHz

3rd Harmonic

-

-45

-43

dBm/MHz

Wi-Fi 2.4GHz Band RF Transmitter Specifications

The specification in table below is measured at the antenna port, which includes the front-end loss.

Note 1: Low power PA.

Note 2: VDD33 voltage is within ±5% of typical value.

Page 21

Page 21 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Parameter

Description

Performance

Min

Typical

Max

Unit

Main

Aux

Frequency range

Center channel frequency

5180

- 5825

MHz

RX sensitivity

BPSK rate 1/2, 6 Mbps OFDM

-

-90.0

-91.5

-86.0

dBm

BPSK rate 3/4, 9 Mbps OFDM

-

-87.7

-89.2

-85.0

dBm

QPSK rate 1/2, 12 Mbps OFDM

-

-87.0

-88.5

-83.0

dBm

QPSK rate 3/4, 18 Mbps OFDM

-

-84.5

-86.0

-81.0

dBm

16QAM rate 1/2, 24 Mbps OFDM

-

-81.3

-82.8

-75.0

dBm

16QAM rate 3/4, 36 Mbps OFDM

-

-78.0

-79.5

-72.0

dBm

64QAM rate 1/2, 48 Mbps OFDM

-

-73.6

-75.1

-70.0

dBm

64QAM rate 3/4, 54 Mbps OFDM

-

-72.2

-73.7

-68.0

dBm

RX sensitivity

BW=20MHz HT

Mixed mode

800ns guard interval

non-STBC

MCS 0, BPSK rate 1/2

-

-89.3

-90.8

-86.0

dBm

MCS 1, QPSK rate 1/2

-

-86.3

-87.8

-84.0

dBm

MCS 2, QPSK rate 3/4

-

-83.8

-85.3

-82.0

dBm

MCS 3, 16QAM rate 1/2

-

-80.8

-82.3

-76.0

dBm

MCS 4, 16QAM rate 3/4

-

-77.3

-78.8

-74.0

dBm

MCS 5, 64QAM rate 2/3

-

-72.8

-74.3

-72.0

dBm

MCS 6, 64QAM rate 3/4

-

-71.4

-72.9

-70.0

dBm

MCS 7, 64QAM rate 5/6

-

-70.2

-71.7

-66.0

dBm

Maximum receive level

6 Mbps OFDM

-30

-10

-

dBm

54 Mbps OFDM

-30

-20

-

dBm

MCS0

-30

-15

-

dBm

MCS7

-30

-20

-

dBm

Receive adjacent

channel rejection

BPSK rate 1/2, 6 Mbps OFDM

16

24

-

dBm

BPSK rate 3/4, 9 Mbps OFDM

15

23

-

dBm

QPSK rate 1/2, 12 Mbps OFDM

13

21

-

dBm

QPSK rate 3/4, 18 Mbps OFDM

11

19

-

dBm

16QAM rate 1/2, 24 Mbps OFDM

8

15

-

dBm

16QAM rate 3/4, 36 Mbps OFDM

4

10

-

dBm

64QAM rate 1/2, 48 Mbps OFDM

0 5 -

dBm

64QAM rate 3/4, 54 Mbps OFDM

-1 3 -

dBm

MCS 0, BPSK rate 1/2

16

24

-

dBm

MCS 1, QPSK rate 1/2

13

21

-

dBm

MCS 2, QPSK rate 3/4

11

19

-

dBm

MCS 3, 16QAM rate 1/2

8

16

-

dBm

Wi-Fi 5GHz Band RF Receiver Specifications

Specifications in the table below are measured at the antenna port, which includes the front-end loss.

Page 22

Page 22 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Parameter

Description

Performance

Min

Typical

Max

Unit

Main

Aux

MCS 4, 16QAM rate 3/4

4

12

-

dBm

MCS 5, 64QAM rate 2/3

0

7

-

dBm

MCS 6, 64QAM rate 3/4

-1

5

-

dBm

Receiver residual PER

MCS 7, 64QAM rate 5/6

-2

3

-

dBm

Parameter

Description

Performance

Min

Typical

Max

Unit

Frequency range

Center channel frequency

5180

-

5825

MHz

Output power with

spectral mask and

EVM

compliance

6 Mbps OFDM

-

14(1)

-

dBm

54 Mbps OFDM

-

14(1)

-

dBm

HT20 MCS 0

-

14(1)

-

dBm

HT20 MCS 7

-

14(1)

-

dBm

Output power with

spectral mask and

EVM

compliance (at -40◦C

and 85◦C)

6 Mbps OFDM

-

13(1)

-

dBm

54 Mbps OFDM

-

13(1)

-

dBm

HT20 MCS 0

-

13(1)

-

dBm

HT20 MCS 7

-

13(1)

-

dBm

TX EVM

6 Mbps OFDM

-

-

-5

dB

54 Mbps OFDM

-

-

-25

dB

HT20 MCS 0

-

-

-5

dB

HT20 MCS 7

-

-

-28

dB

Output power

variation(2)

TSSI closed-loop control across all

temperature range

and channels and VSWR ≦ 1.5:1.

-1.5

-

1.5

dB

Carrier suppression

- - -30

dBc

Harmonic output

power

2nd Harmonic

-

-45

-43

dBm/MHz

3rd Harmonic

-

-45

-43

dBm/MHz

Wi-Fi 2.4GHz Band RF Receiver Specifications (continued)

Wi-Fi 5GHz Band RF Transmitter Specifications

The specification in table below is measured at the antenna port, which includes the front-end loss.

Note 1: Low power PA

Note2: VDD33 voltage is within ±5% of typical value.

Page 23

Page 23 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Parameter

Description

Performance

Min

Typical

Max

Unit

Receiver in-band blocking(1)

CW and BT interferers

2.4 GHz CW and BT interfering signal

@ ±20MHz offset

-47

-

-

dBm

2.4 GHz CW and BT interfering signal

@ ±25MHz offset

-40

-

-

dBm

5 GHz CW interfering signal

@ ±20MHz offset

-35

-

-

dBm

Receiver out-band

blocking(1)

CW interferer

25 ≤ f < 2300 MHz

-28

-

-

dBm

2300 ≤ f < 2395 MHz

-40

-

-

dBm

2483.5 < f ≤ 2583.5 MHz

-45

-

-

dBm

Receiver out-band blocking(1)

CDMA, GSM, DCS and

PCS interferers(2)

CDMA UL: 824 – 849 MHz

-20

-

-

dBm

CDMA DL: 869 – 894 MHz

-10

-

-

dBm

GSM UL: 880 – 915 MHz

-10

-

-

dBm

GSM DL: 925 – 960 MHz

-10

-

-

dBm

DCS UL: 1710 – 1785 MHz

-13

-

-

dBm

DCS DL: 1805 – 1880 MHz

-20

-

-

dBm

PCS UL: 1850 – 1910 MHz

-20

-

-

dBm

PCS DL: 1930 – 1990 MHz

-20

-

-

dBm

Receiver out-band blocking(1)

WiFi interferers

5G receiver only, interfering signal:

2400 < f ≤ 2483.5 MHz

-20

-

-

dBm

2G receiver only, interfering signal:

5125 < f ≤ 5850 MHz

-20

-

-

dBm

Wi-Fi RF Receiver Blocking Specifications

The specifications in table below are measured at the antenna port, which includes the front-end loss.

Note 1: The desired signal's strength is 3 dB above the Maximum RX sensitivity. PER ≤ 10%.

Note 2: Except harmonic mixing.

Page 24

Page 24 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Mechanical Specifications

Module Dimension Details

Figure 6 – AES-MS-MT3620-M-G Module Mechanical Details

Page 25

Page 25 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Tape and Reel Packaging

AES-MS-MT3620 Azure Sphere Modules are available in tape and reel packaging at quantities of 600 units.

The reel dimensions are 13 inches (reel diameter) x 56 mm (tape-width).

The 56 mm tape-width conforms to the Electronic Components Association Standard EIA-481-D.

Figure 7 – Tape and Reel Details

Page 26

Page 26 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Soldering and Cleaning Recommendations

Optimum Soldering Reflow Profile

Figure 8 – Recommended Soldering Profile for Lead-Free Solder

Solder joint quality between the AES-MS-MT3620 Azure Sphere Module’s surface mount pads and

their bonding with the host board should meet the appropriate IPC Specification.

(See IPC-A-610-D Acceptability of Electronic Assemblies, section 8.2.1 “Bottom Only Terminations”)

It is recommended that only a single reflow soldering process be permitted for the host board

Any attempts at reworking the module will invalidate warrantee coverage and regulatory certifications

Cleaning

Cleaning of the populated module is not recommended!

Residuals under the module cannot be easily removed by any cleaning process

(Water / Solvents / Ultrasonic)

Page 27

Page 27 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Region

Regulatory Body

Status

United States

FCC

2AF62-AVT3620U (Pending)

2AF62-AVT3620C (Pending)

Canada

ISED (IC)

21571-AVT3620U (Pending)

21571-AVT3620C (Pending)

Europe

CE

EN 60950-1, EN 300 328, EN 301 489 (Pending)

Japan

MIC

Still to be submitted

All

RoHS

Compliant

Certifications and Compliance

RoHS Compliance

AES-MS-MT3620 Azure Sphere Modules are lead-free and RoHS compliant.

Regulatory Compliance

FCC, IC and CE certifications are currently pending

(Once the certification process has been concluded, this note will be removed from the datasheet)

AES-MS-MT3620 Azure Sphere Module certification applies to operation in various regulatory domains.

This section outlines certification information specific to the following countries and regions:

Should regulatory certification be required in a specific country or region not already covered, please contact

your local Avnet sales office or create a support request at http://avnet.me/mt3620-forums

FCC and ISED Regulatory Notices (USA and Canada)

Modification statement

Avnet has not approved any changes or modifications to this device by the user.

Any changes or modifications could void the user's authority to operate the equipment!

Interference statement

This device complies with Part 15 of the FCC Rules and Industry Canada's license-exempt RSS standards.

Operation is subject to the following two conditions: (1) this device may not cause interference, and (2) this

device must accept any interference, including interference that may cause undesired operation of the device.

RF Radiation Exposure Statement

This equipment complies with FCC and ISED radiation exposure limits set forth for an uncontrolled

environment. The antenna should be installed and operated with minimum distance of 20 cm between the

radiator and your body. This transmitter must not be co-located or operating in conjunction with any other

antenna or transmitter.

Page 28

Page 28 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant

to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful

interference in a residential installation. This equipment generates, uses and can radiate radio frequency

energy and, if not installed and used in accordance with the instructions, may cause harmful interference

to radio communications. However, there is no guarantee that interference will not occur in a particular

installation. If this equipment does cause harmful interference to radio or television reception, which can

be determined by turning the equipment off and on, the user is encouraged to try to correct the

interference by one of the following measures:

▪ Reorient or relocate the receiving antenna.

▪ Increase the separation between the equipment and receiver.

▪ Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.

▪ Consult the dealer or an experienced radio/TV technician for help.

FCC Class B Digital Device Notice (USA)

FCC Module Statement (USA)

The single-modular transmitter is a self-contained, physically delineated, component for which compliance

can be demonstrated independent of the host operating conditions, and which complies with all eight

requirements of § 15.212(a)(1) as summarized below.

1) The radio elements have the radio frequency circuitry shielded.

2) The module has buffered modulation/data inputs to ensure that the device will comply with Part 15

requirements with any type of input signal.

3) The module contains power supply regulation on the module.

4) The module contains a permanently attached antenna.

5) The module demonstrates compliance in a stand-alone configuration.

6) The module is labelled with its permanently affixed FCC ID label

7) The module complies with all specific rules applicable to the transmitter, including all the conditions

provided in the integration instructions by the grantee.

8) The module complies with RF exposure requirements.

CAN ICES-003 (B)

This Class B digital apparatus complies with Canadian standard ICES-003.

Labeling Requirements for the OEM Host Board

The host device shall be properly labelled to identify the modules within the host device. The certification label

of the module shall be clearly visible at all times when installed in the host device, otherwise the host device

must be labelled to display the FCC ID and IC of the module, preceded by the words "Contains transmitter

module", or the word "Contains", or similar wording expressing the same meaning, as follows:

Contains FCC ID: 2AF62-AVT3620C

Contains IC: 21571-AVT3620C

Page 29

Page 29 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

“WARNING: To satisfy FCC RF exposure requirements for mobile transmitting devices, a separation

distance of 20cm or more should be maintained between the antenna of this device and persons during

operation. To ensure compliance, operations at closer distances than this are not recommended”

This device complies with Part 15 of the FCC Rules.

Operation is subject to the following two conditions:

(1) This device may not cause harmful interference, and

(2) This device must accept any interference received, including interference that may cause

undesired operation.

This equipment has been tested and found to comply with the limits for a Class B digital device,

pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection

against harmful interference in a residential installation. This equipment generates, uses and can

radiate radio frequency energy and, if not installed and used in accordance with the instructions, may

cause harmful interference to radio communications. However, there is no guarantee that

interference will not occur in a particular installation. If this equipment does cause harmful

interference to radio or television reception, which can be determined by turning the equipment off

and on, the user is encouraged to try to correct the interference by one of the following measures:

▪ Reorient or relocate the receiving antenna.

▪ Increase the separation between the equipment and receiver.

▪ Connect the equipment into an outlet on a circuit different from that to which the receiver is

connected.

▪ Consult the dealer or an experienced radio/TV technician for help.

This device complies with Part 15 of the FCC Rules.

Operation is subject to the following two conditions:

(1) This device may not cause harmful interference, and

(2) This device must accept any interference received,

including interference that may cause undesired operation.

FCC Requirements for User Manual of the OEM Host Board:

The OEM integrator may not provide any information to the end user on how to install or remove this RF

module or change RF related parameters in the user manual of the end product.

The following statement must be included as a CAUTION statement in manuals for the OEM products, to

alert users of FCC RF exposure compliance:

The user manual for the final end product should include the following statement:

Page 30

Page 30 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Certification

Standard

Report Number

Test Lab

Safety

EN 60950-1:2006, A11:2009,

A1:2010, A12:2011, A2:2013

Pending

F2 Labs,

Middlefield OH, USA

EMF

EN 62311:2008

EN 62479:2010

Pending

F2 Labs,

Middlefield OH, USA

EMC

EN 301 489-1 V1.9.2

EN 301 489-17 V2.2.1

Pending

F2 Labs,

Middlefield OH, USA

Radio

EN 300 328 V1.9.1

Pending

F2 Labs,

Middlefield OH, USA

Industry Canada Statements

This Device complies with Industry Canada License-exempt RSS standard(s). Operation is subject to

the following two conditions: (1) this device may not cause interference, and (2) this device must accept

any interference, including interference that may cause undesired operation of the device.

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts

de licence. L'exploitation est autorisée aux deux onditions suivantes: (1) l'appareil ne doit pas produire

de brouillage, et (2) l'utilisateur de l'appa-reil doit accepter tout brouillage radioélectrique subi, meme si

le brouillage est susceptible d'en com-promettre le fonctionnement.

IC Requirements for User Manual of the OEM Host Board:

The user manual for the final end product shall display the following Industry Canada notices in a

conspicuous location:

FCC Host 15B and 15C Compliance Statement (USA)

The OEM integrator is responsible for testing their end-product for any additional compliance requirements

needed with this module installed (eg. digital device emissions, PC peripheral requirements, etc).

Additionally, investigative measurements and spot checking are strongly recommended to verify that full

system compliance is maintained when the module is integrated, in accordance with the "Host Product

Testing Guidance" in FCC's KDB 996369 D04 Module Integration Guide V01

CE Statement (Europe)

Avnet AES-MS-MT3620 Azure Sphere Modules have been tested and certified for use in the European Union.

Summary of European Compliance Tests:

When integrating this module into an end product, the OEM has responsibility to verify compliance of the final

product to the EU standards.

A Declaration of Conformity (DOC) must be issued and kept on file as described in Annex II of the Radio and

Telecommunications Terminal Equipment (R&TTE) Directive.

CE Labeling Requirements (Europe)

The ‘CE’ mark must be placed on the OEM product per the labelling requirements of the R&TTE Directive.

Page 31

Page 31 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

OEM Instructions

This module is certified for installation into OEM end-products under the following conditions:

1) The intended use of this AES-MS-MT3620-M-G module is for indoor locations. If the end product

using this module is able to operate in the band 5150-5250 MHz within Canada, it is only allowed to

be used indoors (to reduce potential harmful interference to co-channel mobile satellite systems)

The label of the end product in this case must include the text “For indoor use only”

2) It’s intended use is as a Wi-Fi client only (not a Wi-Fi access point or used in point-to-point mode)

3) The AES-MS-MT3620-M-G module is for (OEM) installation only.

The requirement for software security of UNII devices, is fully met by Microsoft Azure Sphere's advanced

security. Software updates require certificate-based authentication using hardware-based root of trust.

The device is set to “AllComplete” to permanently disable any access to any RF-related software changes.

https://docs.microsoft.com/en-us/azure-sphere/hardware/factory-floor-tasks#set-the-device-manufacturingstate-to-manufacturing-complete

Shipping, Handling and Storage

Shipping

Bulk orders of Avnet AES-MS-MT3620 Azure Sphere Modules are delivered in reels of 600.

(See detail under the section on Tape & Reel Packaging)

Handling

AES-MS-MT3620 Azure Sphere Modules contain sensitive electronic circuitry that require proper ESD

protection when handling. Failure to follow these ESD procedures may result in permanent damage to the

module.

The module should not be subjected to excessive mechanical shock.

Moisture Sensitivity (MSL)

Modules that have been exposed to moisture and environmental conditions exceeding the prescribed

packaging and storage conditions detailed in J-STD-020 (eg. not continuously in a sealed bag with a

desiccant pack) MUST be baked before mounting! (Failure to meet the packaging and storage conditions

described, will result in irreparable damage to modules during solder reflow soldering).

For devices that are packaged in a Moisture Barrier Bag with a desiccant pack and HIC (Humidity Indicator

Card), the HIC card should be referenced and J-STD-033 consulted to determine if baking is required prior

to reflow soldering.

In cases where baking is required, refer to J-STD-033 for details of the bake procedure.

“Broken reel” module quantities (under 600 units) typically require baking before reflow soldering

Page 32

Page 32 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Region

Organization

Email

Address & Phone

North America

Avnet Americas

eval.kits@avnet.com

AVNET - Americas

2211 South 47th Street

Phoenix, AZ 85034

USA

Phone: 1-800-585-1602

Europe

Avnet Silica

Microsoft@silica.com

Avnet Silica

Gruber Str. 60c

85586 Poing, Germany

Phone: +49-8121-77702

Storage

Per J-STD-033, the shelf life of devices in a Moisture Barrier Bag is 12 months at <40ºC and <90% room

humidity (RH).

Do not store in salty air or an environment where there is a high concentration of corrosive gas, such as Cl2,

H2S, NH3, SO2, or NOX.

Do not store in direct sunlight.

Contact Information

For further details, contact your local Avnet representative or e-mail us at:

Page 33

Page 33 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

Legal Information

Limitations

This product is not intended for use in safety-critical applications (such as life support or automotive) where

a failure of the Avnet product could be expected to cause severe personal injury or death.

Please refer to the final section of this document for additional restrictions to Avnet’s legal liability

Avnet Module License and Product Warranty

THIS AVNET MODULE (OR “PRODUCT”) AND ANY SUPPORTING DOCUMENTATION IS SUBJECT TO THIS

LICENSE AGREEMENT. USE OF THIS PRODUCT OR DOCUMENTATION SIGNIFIES ACCEPTANCE OF THE

TERMS AND CONDITIONS OF THIS LICENSE.

THE TERMS OF THIS LICENSE AGREEMENT ARE IN ADDITION TO THE AVNET CUSTOMER TERMS AND

CONDITIONS, WHICH CAN BE VIEWED AT www.em.avnet.com

THE TERMS OF THIS LICENSE AGREEMENT WILL CONTROL IN THE EVENT OF A CONFLICT

1. Limited License. Avnet grants You, the Customer, (“You” “Your” or “Customer”) a limited, non-exclusive, non-

transferable, license to: (a) use the Product for Your own internal testing, evaluation and design efforts at a single

Customer site; (c) make, use and sell the Product in a single production unit. No other rights are granted and

Avnet and any other Product licensor reserves all rights not specifically granted in this License Agreement. Except

as expressly permitted in this License, neither the Module, Documentation, nor any portion may be reverse

engineered, disassembled, decompiled, sold, donated, shared, leased, assigned, sublicensed or otherwise

transferred by Customer. The term of this License is in effect until terminated. Customer may terminate this

license at any time by destroying the Product and all copies of the Product Documentation.

2. Changes. Avnet may make changes to the Product or Product Documentation at any time without notice. Avnet

makes no commitment to update or upgrade the Product or Product Documentation and Avnet reserves the right

to discontinue the Product or Product Documentation at any time without notice.

3. Product Documentation. Product Documentation is provided by Avnet on an “AS-IS” basis and does not form

a part of the properties of the Product. All Product Documentation is subject to change without notice. Avnet

makes no representation as to the accuracy or completeness of the Product Documentation, and DISCLAIMS ALL

REPRESENTATIONS, WARRANTIES AND LIABILITIES UNDER ANY THEORY WITH RESPECT TO

PRODUCT INFORMATION.

4. Limited Product Warranty. AVNET WARRANTS THAT AT THE TIME OF DELIVERY, THE PRODUCTS

SHALL MEET THE SPECIFICATIONS STATED IN AVNET DOCUMENTATION FOR SIXTY (60) DAYS FROM

DELIVERY OF PRODUCTS. IF THE CUSTOMER CAN PROVIDE PROOF THAT THE QUALIFIED AVNET

PRODUCT WAS PURCHASED FOR THE PURPOSE OF AND DEPLOYED AS A COMPONENT IN THE

CUSTOMER’S COMMERCIALLY AVAILABLE PRODUCT THE WARRANTY WILL BE EXTENDED TO TWELVE

(12) MONTHS FROM THE DATE OF PURCHASE. TO THE EXTENT PERMITTED BY LAW, AVNET MAKES NO

OTHER WARRANTY, EXPRESS OR IMPLIED, SUCH AS WARRANTY OF MERCHANTABILITY, FITNESS FOR

PURPOSE OR NON-INFRINGEMENT. YOUR SOLE AND EXCLUSIVE REMEDY FOR BREACH OF AVNET’S

WARRANTY IS, AT AVNET’S CHOICE: (I) REPAIR THE PRODUCTS; (ii) REPLACE THE PRODUCTS AT NO

COST TO YOU; OR (iii) REFUND YOU THE PURCHASE PRICE OF PRODUCTS.

5. LIMITATIONS OF LIABILITY. CUSTOMER SHALL NOT BE ENTITLED TO AND AVNET WILL NOT BE

LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES OF ANY KIND OR

NATURE, INCLUDING, WITHOUT LIMITATION, BUSINESS INTERRUPTION COSTS, LOSS OF PROFIT OR

REVENUE, LOSS OF DATA, PROMOTIONAL OR MANUFACTURING EXPENSES, OVERHEAD, COSTS OR

EXPENSES ASSOCIATED WITH WARRANTY OR INTELLECTUAL PROPERTY INFRINGEMENT CLAIMS,

INJURY TO REPUTATION OR LOSS OF CUSTOMERS, EVEN IF AVNET HAS BEEN ADVISED OF THE

POSSIBILITY OF SUCH DAMAGES. THE PRODUCTS AND DOCUMENTATION ARE NOT DESIGNED,

AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN MEDICAL, MILITARY, AIR CRAFT, SPACE

Page 34

Page 34 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

OR LIFE SUPPORT EQUIPMENT NOR IN APPLICATIONS WHERE FAILURE OR MALFUNCTION OF THE

PRODUCTS CAN REASONABLY BE EXPECTED TO RESULT IN A PERSONAL INJURY, DEATH OR SEVERE

PROPERTY OR ENVIRONMENTAL DAMAGE. INCLUSION OR USE OF PRODUCTS IN SUCH EQUIPMENT

OR APPLICATIONS, WITHOUT PRIOR AUTHORIZATION IN WRITING OF AVNET, IS NOT PERMITTED AND

IS AT CUSTOMER’S OWN RISK. CUSTOMER AGREES TO FULLY INDEMNIFY AVNET FOR

ANY DAMAGES RESULTING FROM SUCH INCLUSION OR USE.

6. LIMITATION OF DAMAGES. CUSTOMER’S RECOVERY FROM AVNET FOR ANY CLAIM SHALL NOT

EXCEED CUSTOMER’S PURCHASE PRICE FOR THE PRODUCT GIVING RISE TO SUCH CLAIM

IRRESPECTIVE OF THE NATURE OF THE CLAIM, WHETHER IN CONTRACT, TORT, WARRANTY, OR

OTHERWISE.

7. INDEMNIFICATION. AVNET SHALL NOT BE LIABLE FOR AND CUSTOMER SHALL INDEMNIFY, DEFEND

AND HOLD AVNET HARMLESS FROM ANY CLAIMS BASED ON AVNET’S COMPLIANCE WITH

CUSTOMER’S DESIGNS, SPECIFICATIONS OR IN¬STRUCTIONS, OR MODIFICATION OF ANY PRODUCT

BY PARTIES OTHER THAN AVNET, OR USE IN COMBINATION WITH OTHER PRODUCTS.

8. U.S. Government Restricted Rights. The Product and Product Documentation are provided with

“RESTRICTED RIGHTS.” If the Product and Product Documentation and related technology or documentation are

provided to or made available to the United States Government, any use, duplication, or disclosure by the United

States Government is subject to restrictions applicable to proprietary commercial computer software as set forth in

FAR 52.227-14 and DFAR 252.227-7013, et seq., its successor and other applicable laws and regulations. Use of

the Product by the United States Government constitutes acknowledgment of the proprietary rights of Avnet and

any third parties. No other governments are authorized to use the Product without written agreement of Avnet and

applicable third parties.

9. Ownership. Licensee acknowledges and agrees that Avnet or Avnet’s licensors are the sole and exclusive

owner of all Intellectual Property Rights in the Licensed Materials, and Licensee shall acquire no right, title, or

interest in the Licensed Materials, other than any rights expressly granted in this Agreement.

10. Intellectual Property. All trademarks, service marks, logos, slogans, domain names and trade names

(collectively “Marks”) are the properties of their respective owners. Avnet disclaims any proprietary interest in

Marks other than its own. Avnet and AV design logos are registered trademarks and service marks of Avnet, Inc.

Avnet’s Marks may be used only with the prior written permission of Avnet, Inc.

11. General. The terms and conditions set forth in the License Agreement or at www.em.avnet.com will apply

notwithstanding any conflicting, contrary or additional terms and conditions in any purchase order, sales

acknowledgement confirmation or other document. If there is any conflict, the terms of this License Agreement will

control. This License may not be assigned by Customer, by operation of law, merger or otherwise, without the

prior written consent of Avnet and any attempted or purported assignment shall be void. Licensee understands

that portions of the Licensed Materials may have been licensed to Avnet from third parties and that such third

parties are intended beneficiaries of the provisions of this Agreement. In the event any of the provisions of this

Agreement are for any reason determined to be void or unenforceable, the remaining provisions will remain in full

effect. This constitutes the entire agreement between the parties with respect to the use of this Product, and

supersedes all prior or contemporaneous understandings or agreements, written or oral, regarding such subject

matter. No waiver or modification is effective unless agreed to in writing and signed by authorized representatives

of both parties. The obligations, rights, terms and conditions shall be binding on the parties and their respective

successors and assigns. The License Agreement is governed by and construed in accordance with the laws of the

State of Arizona excluding any law or principle, which would apply the law of any other jurisdiction. The United

Nations Convention for the International Sale of Goods shall not apply.

Copyright © 2019, Avnet, Inc. All rights reserved. Published by Avnet Electronics Marketing, a group of Avnet,

Inc. Avnet, Inc. disclaims any proprietary interest or right in any trademarks, service marks, logos, domain names,

company names, brands, product names, or other form of intellectual property other than its own. AVNET and the

AV logos are registered trademarks of Avnet, Inc.

Page 35

Page 35 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

#

Use Case

MT3620 Interface

1

Wi-Fi network settings are missing

or incorrectly configured

SERVICE UART

(4 pins)

2

A7 DEBUG UART access is

required

DEBUG UART

(2 of 4 pins)

3

M4 IO0 and IO1 TXD output are

needed (eg. for debug of M4 code)

M4F IO0 and IO1 TXD pins

(2 pins)

Appendix-A: Programming Adaptor Footprint

A key aspect of the operation of the MT3620 device are the Over-the-Air (OTA) updates of the Azure Sphere

OS firmware and the application software. There are however specific use cases where wired device

interfaces are needed (see table below). It is therefore recommended that a 10-pin connector footprint be

added to the OEM host board to interface with the module signals tabled below:

Notes:

1) There is currently a need to facilitate the configuration of the Wi-Fi network settings via the

SERVICE UART interface (the need for this will be reduced when Microsoft at later date adds

support for configuration of Wi-Fi settings via Wi-Fi A/P mode)

2) Once Wi-Fi has been configured, the Sphere OS can be “recovered” to latest version OTA via Wi-Fi

3) Access to the DEBUG UART output (of the A7 core) provides valued log-file status information that

can prove useful during software development debugging.

4) Access to the M4 TXD outputs can likewise provide status information to the software developer

To support these interfaces, an FTDI-based USB to serial adaptor is to be available for purchase from

Avnet, with 2x5 pin header connectors to support two different footprint options on the OEM host board:

a) “Tag-Connect” connector-less footprint (2x5 pads, 1.27mm pitch)

http://www.tag-connect.com/TC2050-IDC or

b) Dual-row header pins (2x5 pins, 1.27mm pitch)

Page 36

Page 36 of 36

May 16, 2019

Data Sheet and User Manual

AES-MS-MT3620-M-G Module

Data Sheet and User Manual

#

MT3620

Net Name

Module

Pad

I/O

#

MT3620

Net Name

Module

Pad

I/O

1

GND

63

- 2 GND

62

- 3 IO0_TXD

60

O 4 SERVICE_CTS

55

I 5 SERVICE_RTS

54

O 6 SERVICE_RXD

53

I 7 SERVICE_TXD

52

O 8 SYSRST_N

51

I 9 DEBUG_TXD

46

O

10

DEBUG_RTS

45

O

The pinout of the 2x5 pin footprint chosen for inclusion on the OEM board, should be as tabled below:

DEBUG_RTS is driven high by the PC during SYSRST_N of the MT3620 to initiate Sphere OS RECOVERY

The corresponding pads of these UART interfaces are located on same edge of the module for easy routing

to the selected 2x5 pin connector footprint on the OEM host board

Figure 9 – Module Pinout to Recommended Service & Debug Interface Connector