AUSTN AS5SS256K18DQ-9-XT, AS5SS256K18DQ-9-IT, AS5SS256K18DQ-8-XT, AS5SS256K18DQ-8-IT, AS5SS256K18DQ-10-XT Datasheet

...

AS5SS256K18

Rev. 2.0 12/00

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

1

SSRAM

AS5SS256K18

Austin Semiconductor, Inc.

FEA TURES

• Fast access times: 8, 10, and 15ns

• Fast clock speed: 113, 100, and 66 MHz

• Fast clock and OE\ access times

• Single +3.3V +0.3V/-0.165V power supply (VDD)

• SNOOZE MODE for reduced-power standby

• Common data inputs and data outputs

• Individual BYTE WRTIE control and GLOBAL WRITE

• Three chip enables for simple depth expansion and address

pipelining

• Clock-controlled and registered addresses, data I/Os and

control signals

• Interally self-timed WRITE cycle

• Burst control pin (interleaved or linear burst)

• Automatic power-down

• Low capacitive bus loading

• Operating Temperature Ranges:

- Military -55oC to +125oC

- Industrial -40oC to +85oC

OPTIONS MARKING

• Timing

7.5ns/8ns/113 MHz -8 *

8.5ns/10ns/100 MHz -9

10ns/15ns/66 MHz -1 0

• Packages

100-pin TQFP DQ No. 1001

• Operating Temperature Ranges:

- Military -55oC to +125oCIT

- Industrial -45oC to +85oCXT

*available as IT only.

256K x 18 SSRAM

Synchronous Burst SRAM,

Flow-Through

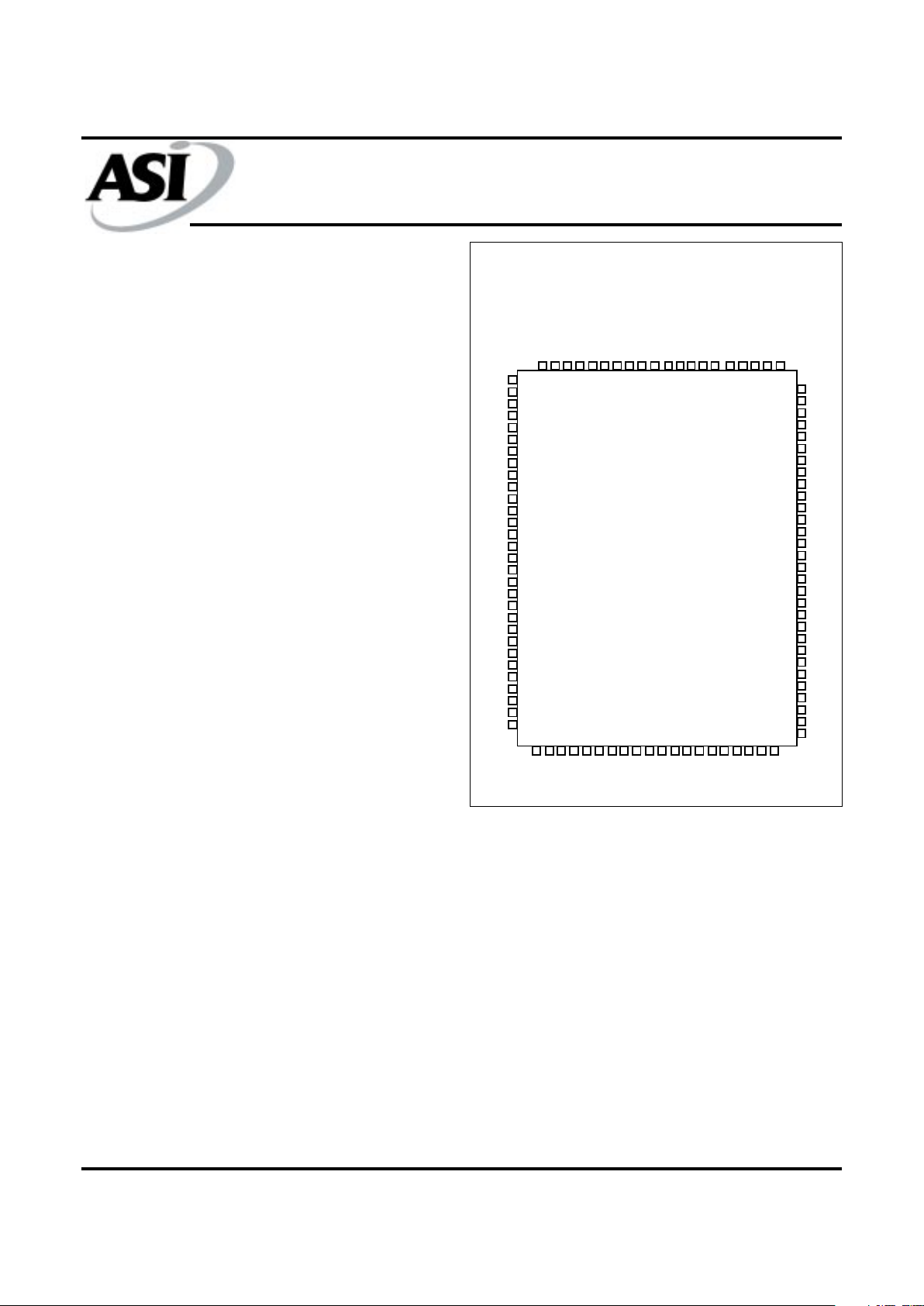

PIN ASSIGNMENT

(Top View)

100-pin TQFP

For more products and information

please visit our web site at

www.austinsemiconductor .com

SA

SA

CE\

CE2

NC

NC

bwB\

BWa\

CE2\

V

DD

V

SS

CLK

GW\

BWE\

OE\

ADSC\

ADSP\

ADV\

SA

SA

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81

NC

NC

NC

VDDQ

V

SS

NC

NC

DQb

DQb

V

SS

VDDQ

DQb

DQb

V

SS

V

DD

NC

V

SS

DQb

DQb

VDDQ

V

SS

DQb

DQb

DQPb

NC

V

SS

VDDQ

NC

NC

NC

SA

NC

NC

VDDQ

V

SS

NC

DQPa

DQa

DQa

V

SS

VDDQ

DQa

DQa

V

SS

NC

V

DD

ZZ

DQa

DQa

VDDQ

V

SS

DQa

DQa

NC

NC

V

SS

VDDQ

NC

NC

NC

MODE

SA

SA

SA

SA

SA1

SA0

DNU

DNU

V

SS

V

DD

NF**

NF**

SA

SA

SA

SA

SA

SA

SA

GENERAL DESCRIPTION

The Austin Semiconductor, Inc. Synchronous Burst SRAM family

employs high-speed, low power CMOS designs that are fabricated using an advanced CMOS process.

ASI’s 4Mb Synchronous Burst SRAMs integrate a 256K x 18, SRAM

core with advanced synchronous peripheral circuitry and a 2-bit burst

counter. All synchronous inputs pass through registers controlled by a

positive-edge-triggered single clock input (CLK). The synchronous

inputs include all addresses, all data inputs, active LOW chip enable

(CE\), two additional chip enables for easy depth expansion (CE2\,

CE2), burst control inputs (ADSC\, ADSP\, ADV\), byte write enables

(BWx\) and global write (GW\).

Asynchronous inputs include the output enable (OE\), clock (CLK)

and snooze enable (ZZ). There is also a burst mode input (MODE) that

selects between interleaved and linear burst modes. The data-out (Q),

enabled by OE\, is also asynchronous. WRITE cycles can be from one

to two bytes wide, as controlled by the write control inputs.

Burst operation can be initiated with either address status processor

(ADSP\) or address status controller (ADSC\) inputs. Subsequent burst

addresses can be internally generated as controlled by the burst advance input (ADV\).

Address and write control are registered on-chip to simplify WRITE

cycles. This allows self-timed WRITE cycles. Individual byte enables

allow individual bytes to be written. During WRITE cycles on this x18

device BW a\ controls DQa pins and DQPa; BWb\ controls DQb pins

and DQPb. GW\ LOW causes all bytes to be written. Parity bits are

available on this device.

ASI’s 4Mb Synchronous Burst SRAMs operate from a +3.3V V

DD

power supply, and all inputs and outputs are TTL-compatible. The device is ideally suited for 486, Pentium®, and PowerPC systems and

those systems that benefit from a wide synchronous data bus.

**pins 42,43 reserved for future address expansion for 8Mb, 16Mb densities.

AS5SS256K18

Rev. 2.0 12/00

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

2

SSRAM

AS5SS256K18

Austin Semiconductor, Inc.

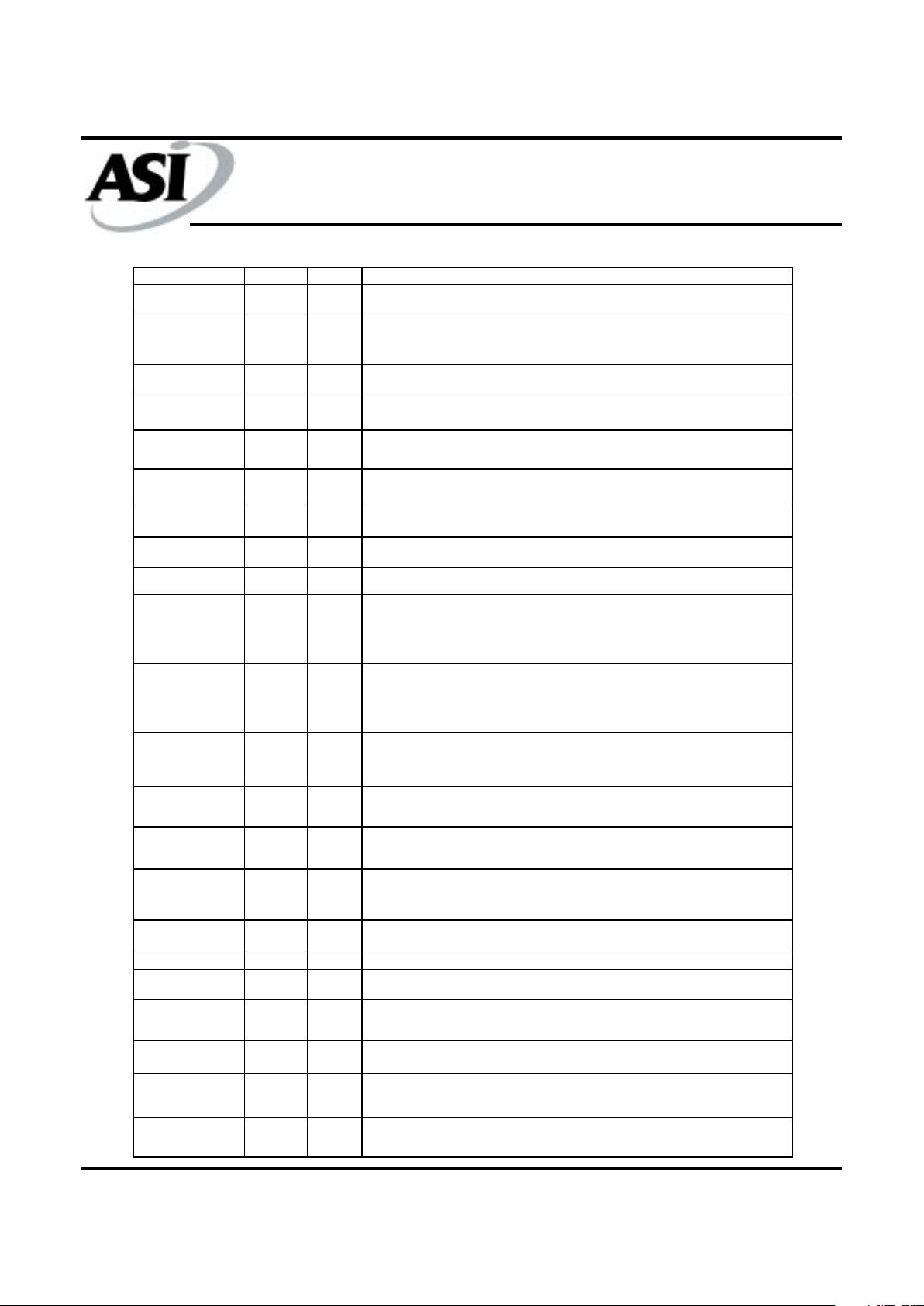

PIN DESCRIPTIONS

PIN NUMBERS SYM TYPE DESCRIPTION

37, 36, 32-35, 44-50,

80-82, 99, 100

SA0, SA1, SA Input Synchronous Address Inputs: These inputs are registered and must meet the setup and

hold times around the rising edge of CLK.

93, 94 BWa\

BWb\

Input Synchronous Byte Write Enables: These active LOW inputs allow individual bytes to be

written and must meet the setup and hold times around the rising edge of CLK. A byte

write enables is LOW for a WRITE cycle and HIGH for a READ cycle. BWa\ controls DQa

pins and DQPa; BWb\ controls DQb pins and DQPb.

87 BWE\ Input Byte Write Enable: This active LOW input permits BYTE WRITE operations and must meet

the setup and hold times around the rising edge of CLK.

88 GW\ Input Global Write: This active LOW input allows a full 18-bit WRITE to occur independent of the

BWE\ and BWx\ lines and must meet the setup and hold times around the rising edge of

CLK.

89 CLK Input Clock: This signal registers the addresses, data, chip enables, byte write enables and burst

control inputs on its rising edge. All synchronous inputs must meet setup and hold times

around the clock’s risin

g

edge.

98 CE\ Input Synchronous Chip Enable: This active LOW input is used to enable the device and

Conditions the internal use of ADSP\. CE\ is sampled only when a new external address is

loaded.

92 CE2\ Input Synchronous Chip Enable: This active LOW input is used to enable the device and is

sampled only when a new external address is loaded.

97 CE2 Input Synchronous Chip Enable: This active HIGH input is used to enable the device and is

sampled only when a new external address is loaded.

86 OE\ Input Output Enable: This active LOW, asynchronous input enables the data I/O output drivers.

83 ADV\ Input Synchronous Address Advance: This active LOW input is used to advance the internal

burst counter, controlling burst access after the external address is loaded. A HIGH on this

pin effectively causes wait states to be generated (no address advance). To ensure use of

correct address during WRITE cycle, ADV\ must be HIGH at the rising edge of the first

clock after an ADSP\ cycle is initiated.

84 ADSP\ Input Synchronous Address Status Processor: This active LOW input interrupts any ongoing

burst, causing a new external address to be registered. A READ is performed using the

new address, independent of the byte write enables and ADSC\, but dependent upon CE\,

CE2, and CE2\. ADSP\ is ignored if CE\ is HIGH. Power-down state is entered if CE2 if

LOW or CE2\ is HIGH.

85 ADSC\ Input Synchronous Address Status Controller: This active LOW input interrupts any ongoing

burst, causing a new external address to be registered. A READ or WRITE is performed

using the new address if CE\ is LOW. ADSC\ is also used to place the chip into powerdown state when CE\ is HIGH.

31 MODE Input Mode: This input selects the burst sequence. A LOW on this pin selects LINEAR BURST. A

NC or HIGH on this pin selects INTERLEAVED BURST. Do not alter input state while

device is operating.

64 ZZ Input Snooze Enable: This active HIGH, asynchronous input causes the device to enter a low-

power standby mode in which all data in the memory array is retained. When ZZ is active,

all other inputs are ignored.

(a) 58, 59, 62, 63, 68,

69, 72, 73

(b) 8, 9, 12,13, 18, 19,

22

,

23

DQa

DQb

Input/

Output

SRAM Data I/Os: Byte "a" is DQa pins; Byte "b" is DQb pins. Input data must meet setup

and hold times around the rising edge of CLK.

74, 24 NC/DQPa

NC/DQPb

NC/ I/O No Connect/Parity Data I/Os: Byte "a" is DQPa pins; Byte "b" is DQPb pins.

15, 41,65, 91 VDD Supply Power Supply: See DC Electrical Characteristics and Operating Conditions for range.

4, 11, 20, 27, 54, 61,

70, 77

VDDQ Supply Isolated Output Buffer Supply: See DC Electrical Characterics and Operating Conditions for

range.

5, 10, 14, 17, 21, 26,

40, 55, 60, 67 71, 76,

90

VSS Supply Ground: GND

38, 39 DNU --- Do Not Use: These signals may either be unconnected or wired to GND to improve

package heat dissipation.

1-3, 6, 7, 16,25, 28-30,

51-53, 56,57, 66, 75,

78, 79, 95, 96

NC ----- No Connect: These signals are not internally connected and may be connected to ground to

improve package heat dissipation.

42, 43 NF No Function: These pins are internally connected to the die and will have the capacitance of

input pins. It is allowable to leave these pins unconnected or driven by signals.

AS5SS256K18

Rev. 2.0 12/00

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

3

SSRAM

AS5SS256K18

Austin Semiconductor, Inc.

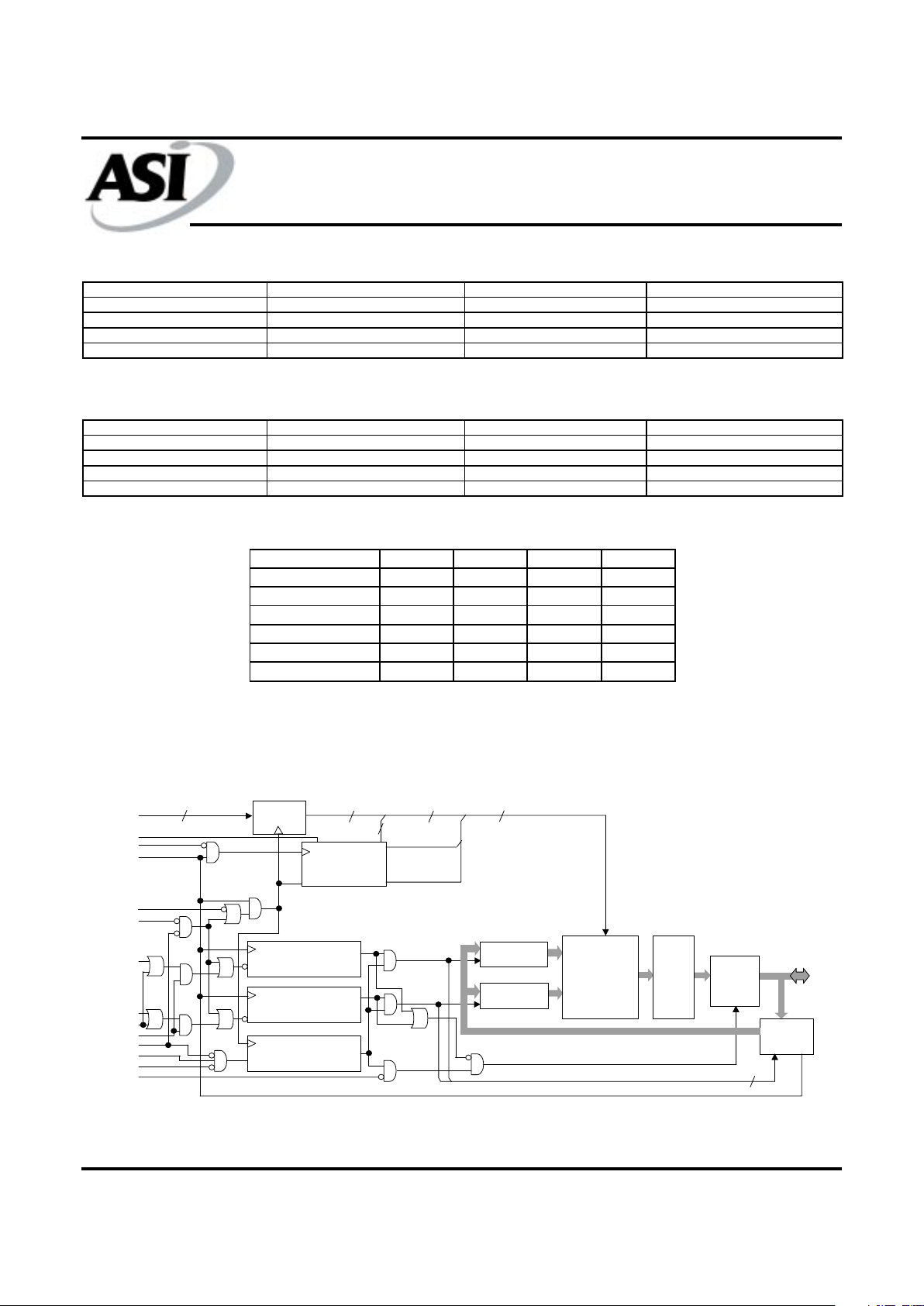

INTERLEAVED BURST ADDRESS TABLE (MODE=NC OR HIGH)

LINEAR BURST ADDRESS TABLE (MODE=LOW)

FUNCTIONAL BLOCK DIAGRAM

NOTE: The Functional Block Diagram illustrates simplified device operation. See T ruth T able, pin descriptions and timing

diagrams for detailed information.

18 18 16 18

SA0, SA1, SA

MODE

ADV\

CLK

ADSC\

ADSP\

BWb\

BWa\

BWE\

GW\

CE\

CE2

CE2\

OE\ 2

ADDRESS

REGISTER

BINARY

COUNTER AND

LOGIC

BYTE "b"

WRITE REGISTER

BYTE "a"

WRITE REGISTER

ENABLE

REGISTER

CLR

Q1

Q0

SA1'

SA0'

INPUT

REGISTERS

OUTPUT

BUFFERS

SENSE

AMPS

256K x 9 x 2

MEMORY

ARRAY

9

9

BYTE "b"

WRITE DRIVER

BYTE "a"

WRITE DRIVER

9

9

18

18

18

18

DQs

DQPa

DQPb

2

SA0-SA1

FIRST ADDRESS (EXTERNAL) SECOND ADDRESS (INTERNAL) THIRD ADDRESS (INTERNAL) FOURTH ADDRESS (INTERNAL)

X…X00 X…X01 X…X10 X…X11

X…X01 X…X00 X…X11 X…X10

X…X10 X…X11 X…X00 X…X01

X…X11 X…X10 X…X01 X…X00

FIRST ADDRESS (EXTERNAL) SECOND ADDRESS (INTERNAL) THIRD ADDRESS (INTERNAL) FOURTH ADDRESS (INTERNAL)

X…X00 X…X01 X…X10 X…X11

X…X01 X…X10 X…X11 X…X00

X…X10 X…X11 X…X00 X…X01

X…X11 X…X00 X…X01 X…X10

PARTIAL TRUTH TABLE FOR WRITE COMMANDS

FUNCTION GW\ BWE\ BWa\ BWb\

READ H H X X

READ H L H H

WRITE Byte "a" H L L H

WRITE Byte "b" H L H L

WRITE All Bytes H L L L

WRITE All Bytes L X X X

NOTE: Using BWE\ and BWa\ through BWb\, any one or more bytes may be

written.

AS5SS256K18

Rev. 2.0 12/00

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

4

SSRAM

AS5SS256K18

Austin Semiconductor, Inc.

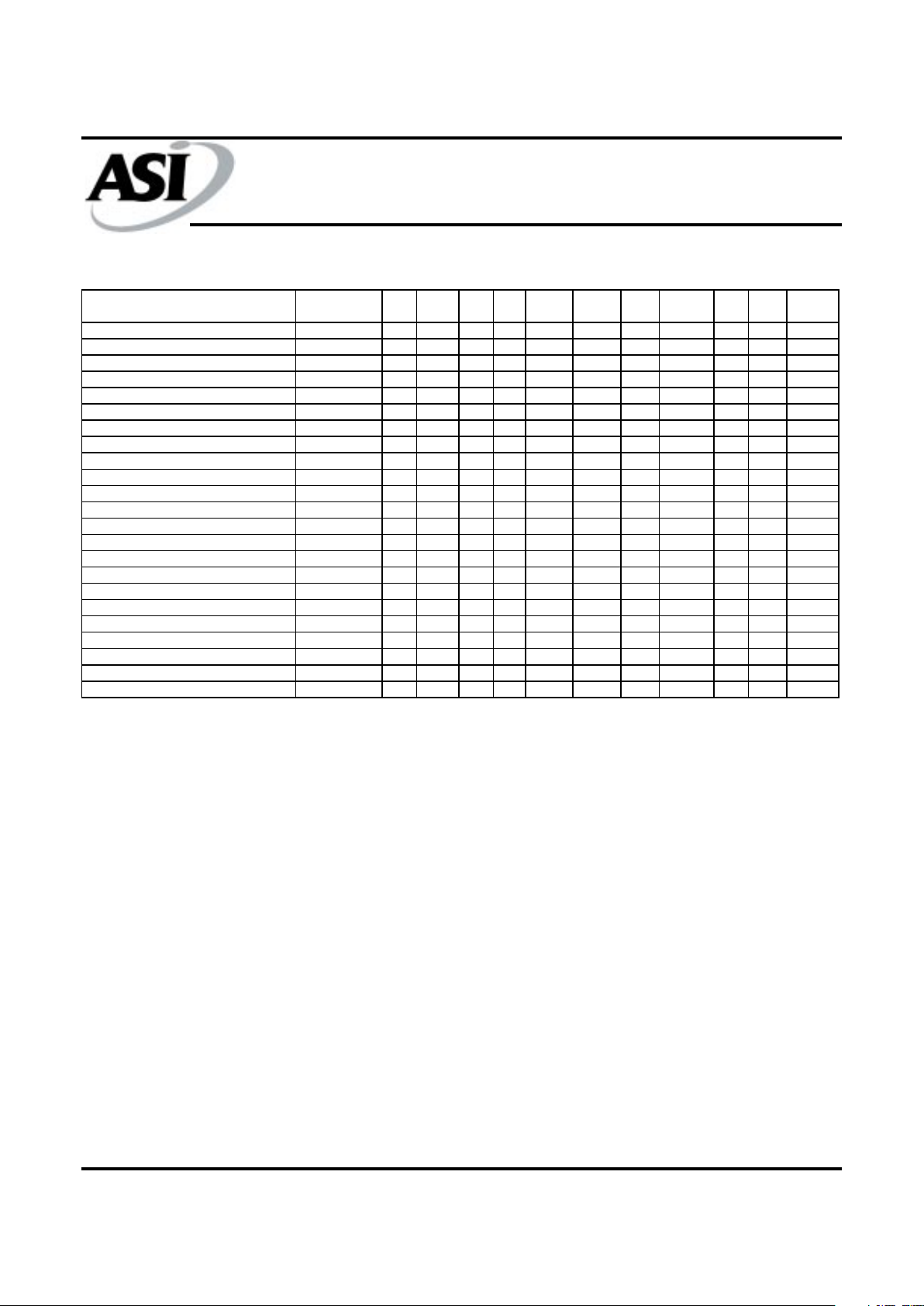

TRUTH TABLE

NOTES: 1. X means “Don’t Care.” \ means active LOW . H means logic HIGH. L means logic LOW.

2. For WRITE\, L means any one or more byte write enable signals (BWa\, BWb\) and BWE\ are LOW or GW\ is LOW. WRITE\ = H for all BWx\,

BWE\, GW\ HIGH.

3. BWa\ enables WRITEs to DQas and DQPa. BWb\ enables WRITEs to DQbs and DQPb.

4. All inputs except OE\ and ZZ must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

5. Wait states are inserted by suspending burst.

6. For a WRITE operation following a READ operation, OE\ must be HIGH before the input data setup time and held HIGH throughout the input

data hold time.

7. This device contains circuitry that will ensure the outputs will be in High-Z during power-up.

8. ADSP\ LOW always initiates an internal READ at the L-H edge of CLK. A WRITE is performed by setting one or more byte write enable signals

and BWE\ LOW or GW\ LOW for the subsequent L-H edge of CLK. Refer to WRITE timing diagram for clarification.

OPERATION

ADDRESS

USED

CE\ CE2\ CE2 ZZ ADSP\ ADSC\ ADV\ WRITE\ OE\ CLK DQ

DESELECT Cycle, Power-Down NONE H X X L X L X X X L-H High-Z

DESELECT Cycle, Power-Down NONE L X L L L X X X X L-H High-Z

DESELECT Cycle, Power-Down NONE L H X L L X X X X L-H High-Z

DESELECT Cycle, Power-Down NONE L X L L H L X X X L-H High-Z

DESELECT Cycle, Power-Down NONE L H X L H L X X X L-H High-Z

SNOOZE MODE, Power-Down NONE X X X H X X X X X X High-Z

READ Cycle, Begin Burst EXTERNAL L L H L L X X X L L-H Q

READ Cycle, Begin Burst EXTERNAL L L H L L X X X H L-H High-Z

WRITE Cycle, Begin Burst EXTERNAL L L H L H L X L X L-H D

READ Cycle, Begin Burst EXTERNAL L L H L H L X H L L-H Q

READ Cycle, Begin Burst EXTERNAL L L H L H L X H H L-H High-Z

READ Cycle, Continue Burst NEXT X X X L H H L H L L-H Q

READ Cycle, Continue Burst NEXT X X X L H H L H H L-H High-Z

READ Cycle, Continue Burst NEXT H X X L X H L H L L-H Q

READ Cycle, Continue Burst NEXT H X X L X H L H H L-H High-Z

WRITE Cycle, Continue Burst NEXT X X X L H H L L X L-H D

WRITE Cycle, Continue Burst NEXT H X X L X H L L X L-H D

READ Cycle, Suspend Burst CURRENT X X X L H H H H L L-H Q

READ Cycle, Suspend Burst CURRENT X X X L H H H H H L-H High-Z

READ Cycle, Suspend Burst CURRENT H X X L X H H H L L-H Q

READ Cycle, Suspend Burst CURRENT H X X L X H H H H L-H High-Z

WRITE Cycle, Suspend Burst CURRENT X X X L H H H L X L-H D

WRITE Cycle, Suspend Burst CURRENT H X X L X H H L X L-H D

Loading...

Loading...