AUSTN AS5C1008DJ-25-XT, AS5C1008DJ-25-IT, AS5C1008DJ-20-XT, AS5C1008DJ-20-IT, AS5C1008DJ-15-XT Datasheet

...

Austin Semiconductor, Inc.

SRAM

AS5C1008

128K x 8 SRAM

RUGGEDIZED PLASTIC

HIGH SPEED SRAM

FEATURES

• Access times of 15, 20 and 25 ns

• Fast output enable (t

• Low active power

• Low standby power

• Fully static operation, no clock or refresh required

• TTL Compatible Inputs and Outputs

• Single +5V power supply

• Package in Industry-standard 32-pin SOJ

OPTIONS MARKING

• Timing

15ns access -15

20ns access -20

25ns access -25

• Package

Plastic SOJ* DJ No. 905

) for cache applications

AOE

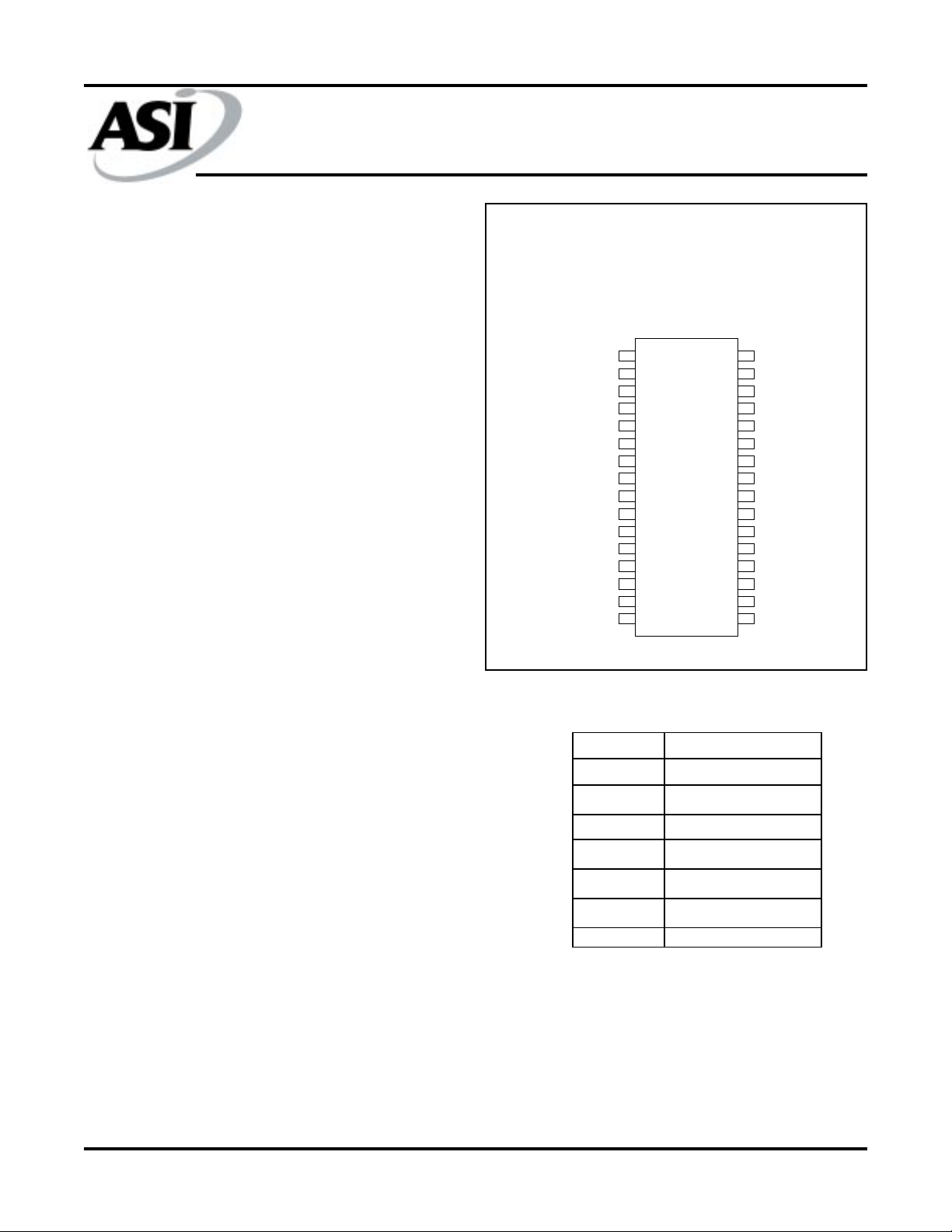

PIN ASSIGNMENT

(T op View)

32-Pin Plastic SOJ (DJ)

NC

A6

A5

A4

A3

A2

A1

A0

A16

A15

A14

A13

I/O0

I/O1

I/02

Vss

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

Vcc

A7

CE

WE\

A8

A9

A10

A11

OE\

A12

CE\

I/O7

I/O6

I/O5

I/O4

I/O3

2

1

• Operating T emperature Ranges

-Military (-55oC to +125oC) XT

-Industrial (-40oC to +85oC) IT

GENERAL DESCRIPTION

The ASI AS5C1008 is a high speed, low power, 128K by

8-bit ruggedized plastic (COTS) CMOS Static RAM. It is fabricated using high performance, CMOS technology . This highly

reliable process coupled with innovative circuit design techniques, yields access times as fast as 15ns (Max) over the

military and industrial temperature ranges.

When Chip Enable (CE\) is HIGH, the device assumes a

standby mode at which the power dissipation can be reduced

down to 125mW (max) at CMOS input levels.

Easy memory expansion is provided by using asserted LOW

CE\ and asserted HIGH CE2, and asserted LOW write enable

(WE\) controls both writing and reading of the memory.

TheAS5C1008 is pin-compatible with other 128K x 8

SRAM's in the SOJ package.

*For ceramic versions of this product, please see the

MT5C1008 datasheet.

AS5C1008

Rev. 3.5 1/01

PIN FUNCTIONS

A0 - A16 Address Inputs

WE\ Write Enable

CE\

, CE

1

Chip Enable

2

OE\ Output Enable

I/O0 - I/O

V

CC

V

SS

Data Inputs/Outputs

7

Power

Ground

NC No Connection

For more products and information

please visit our web site at

www.austinsemiconductor .com

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

1

Austin Semiconductor, Inc.

SRAM

AS5C1008

ABSOLUTE MAXIMUM RA TINGS*

Vcc Supply Relative to GND...................................-0.5V to +7.0V

Voltage on any pin Relative to GND.........-0.5V to Vcc +7.0V

Storage T emperature ............................................-65°C to +150°C

Ambient Temperature with Power Applied........-55oC to +125oC

Short Circuit Output Current.................................................260oC

Power Dissipation...................................................................1.0W

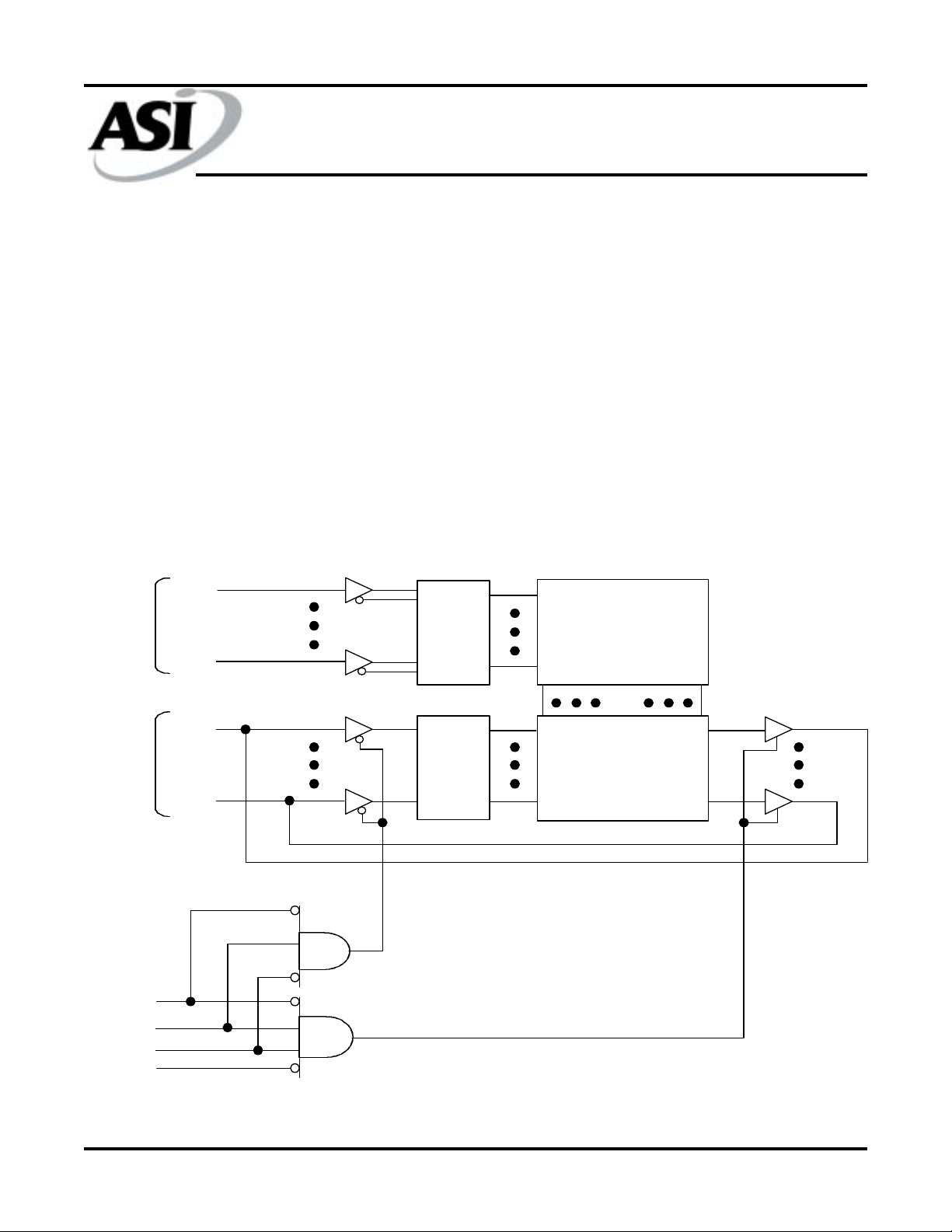

FUNCTIONAL BLOCK DIA GRAM

A0

Address

A16

Decoder

*Stresses greater than those listed under "Absolute Maximum

Ratings" may cause permanent damage to the device. This is

a stress rating only and functional operation of the device at

these or any other conditions above those indicated in the

operation section of this specification is not implied. Exposure

to absolute maximum rating conditions for extended periods

may affect reliability .

Memory Matrix

Data

CE\

CE

WE\

OE\

AS5C1008

Rev. 3.5 1/01

I/O0

Input Data

Control

I/O7

1

2

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

2

Column I/O

SRAM

AS5C1008

Austin Semiconductor, Inc.

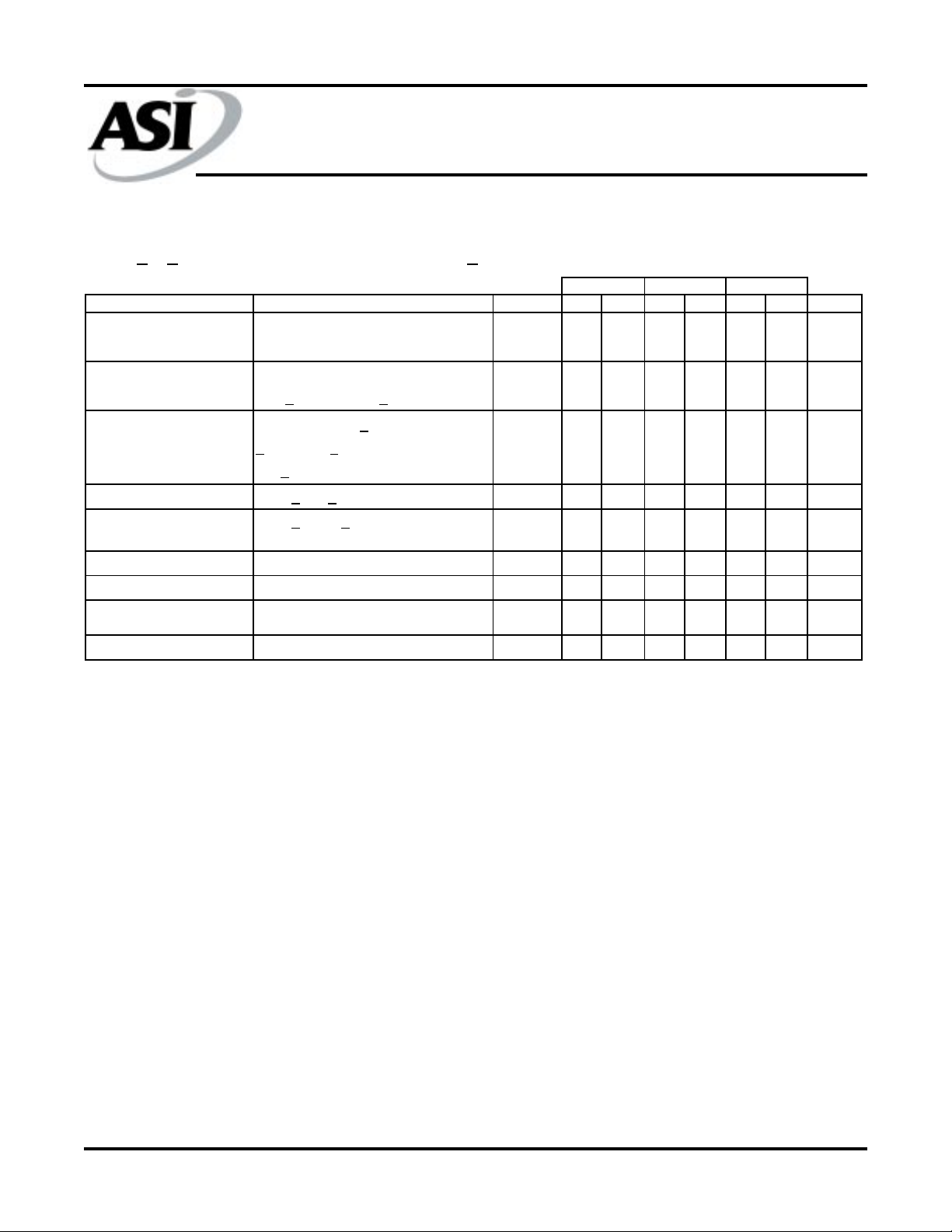

ELECTRICAL CHARACTERISTICS AND RECOMMENDED DC OPERATING CONDITIONS

(-55oC<TA<+125oC or -40oC to +85oC; Vcc = 5V+10%)

-15 -20 -25

PARAMETER CONDITIONS SYMBOL MIN MAX MIN MAX MIN MAX UNITS

Dynamic Operating

Current

TTL Standby Current TTL Inputs

CMOS Standby Current CMOS Inputs

Input Leakage Current

Output Leakage Current

Output High Voltage

Output Low Voltage

Input High Voltage V

Input Low Voltage

Vcc=MAX, I

CE

= VIL and CE2 = VIH, f = fmax

1

Vcc=MAX, V

CE\

> VIH and CE2 > VIL, f = fmax

1

Vcc=MAX, CE\

< 0.2V, VIN > Vcc -0.2V and

V

< 0.2V, f = 0

IN

GND <

VIN < Vcc I

GND <

V

Output Disabled

Vcc = MIN, I

Vcc = MIN, I

= 0mA,

OUT

= VIH or VIL,

IN

> Vcc -0.2V, or CE

1

< Vcc

OUT

= -4.0 mA V

OH

= 8.0 mA V

OL

I

CC1

I

SB1

2

I

SB2

LI

I

LO

OH

OL

IH

V

IL

180 150 140 mA

90 75 70 mA

10 10 10 mA

-10 10 -10 10 -10 10 µA

-10 10 -10 10 -10 10 µA

2.4 2.4 2.4 V

0.4 0.4 0.4 V

Vcc

2.2

+0.5

-0.5 0.8 -0.5 0.8 -0.5 0.8 V

2.2

Vcc

+0.5

2.2

Vcc

+0.5

V

PIN DESCRIPTIONS

A0 - A16: Address Inputs

These 17 address inputs select one of the 131,072 8-bit words in

the RAM.

CE\1: Chip Enable 1 Input

CE\1 is asserted LOW to read from or write to the device. If Chip

Enable 1 is deasserted, the device is deselected and is in standby

power mode. The I/O pins will be in the high-impedance state

when the device is deselected.

CE2: Chip Enable 2 Input

CE2 is asserted HIGH to read from or write to the device. If Chip

Enable 2 is deasserted, the device is deselected and is in standby

power mode. The I/O pins will be in the high-impedance state

when the device is deselected.

AS5C1008

Rev. 3.5 1/01

OE\: Output Enable Input

The Output Enable Input is asserted LOW. If asserted LOW

while CE\1 is asserted (LOW) and CE2 is asserted (HIGH) and

WE\ is deasserted (HIGH), data from the SRAM will be present

on the I/O pins. The I/O pins will be in the high-impedance

state when OE\ is deasserted.

WE\: Write Enable Input

The Write Enable input is asserted LOW and controls read and

write operations. When CE\1 and WE\ are both asserted (LOW)

and CE2 is asserted (HIGH) input data present on the I/O pins

will be written into the selected memory location.

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

3

Loading...

Loading...