Page 1

Document Version: 6

Date: 2004/7/5

Product Functional Specification

17 inch WXGA+ Color TFT LCD Module

Model Name: B170PW02 V.0

() Preliminary Specification

( ) Final Specification

www.jxlcd.com

www.jxlcd.com

Note: This Specification is subject to change without notice.

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 1/1

Page 2

Contents

1.0 Handling Precautions ..........................................................................................................................4

2.0 General Description...............................................................................................................................5

2.1 Display Characteristics..................................................................................................................................................... 5

2.2 Functional Block Diagram................................................................................................................................................ 6

3.0 Absolute Maximum Ratings..................................................................................................................7

4.0 Optical Characteristics..........................................................................................................................8

5.0 Signal Interface ....................................................................................................................................12

5.1 Connectors......................................................................................................................................................................12

5.2 Signal Pin........................................................................................................................................................................ 12

5.3 Signal Description .......................................................................................................................................................... 14

5.4 Signal Electrical Characteristics..................................................................................................................................... 15

5.5 Signal for Lamp connector ............................................................................................................................................. 15

6.0 Pixel Format Image..............................................................................................................................16

7.0 Parameter guide line for CCFL Inverter...........................................................................................16

8.0 Interface Timings.................................................................................................................................17

8.1 Timing Characteristics.................................................................................................................................................... 17

8.2 Timing Definition...........................................................................................................................................................18

9.0 Power Consumption............................................................................................................................. 19

10. Power ON/OFF Sequence.................................................................................................................... 20

11.0 Reliability /Safety Requirement........................................................................................................21

11.1 Reliability Test Conditions...........................................................................................................................................21

11.2 Safety............................................................................................................................................................................21

12.0 Packing dimension........................................................................................................................... 22

13.0 Mechanical Characteristics..............................................................................................................23

13.1 LCM Outline dimension (Front View)....................................................................................................................... 23

13.2 LCM Outline Dimension (Rear View) ......................................................................................................................... 24

13.3 Screw Hole Depth and Center Position........................................................................................................................ 25

14. Shipping Label Format........................................................................................................................ 26

www.jxlcd.com

www.jxlcd.com

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 2/2

Page 3

II Record of Revision

Version and Date Page Old description New Description Remark

V1. 2004/3/3 All First Release NA

V2. 2004/3/10 17 NA Add note 6 Update

V3. 2004/3/23 17

V4. 2004/5/13 16 CCFL DP-1 CCFL DP-1 Update

17 Tim ing Ch ar ac ter is ti cs Timing Ch ara ct er is tic s Update

18 Tim ing De fi nit io n Timing De fin iti on Update

19 Pow er Co ns ump ti on Power C on su mpt io n Update

24 LCM dr aw ing (R ea r V iew ) LCM dra wi ng (R ear Vi ew ) Update

V5. 2004/6/29 23 LCM drawing (Front View) LCM drawing (Front View) Update

V.6 2004/7/5 8 N/A Add viewing angle min value Add

Clock frequency and Horizontal Section Clock frequency and Horizontal Section

Update

www.jxlcd.com

www.jxlcd.com

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 3/3

Page 4

1.0 Handling Precautions

1) Do not press or scratch the surface harder than a HB pencil lead because the polarizers are very fragile

and could be easily damaged.

2) Be sure to turn off power supply when inserting or disconnecting from input connector.

3) Wipe off water droplets or oil immediately. Long contact with the droplets may cause discoloration or

spots.

4) When the panel surface is soiled, wipe it with absorbent cotton or other soft cloth.

5) Since the panel is made of glass, it may break or crack if dropped or bumped on hard surface.

6) Protect the module from static electricity and insure proper grounding when handling. Static electricity

may cause damage to the CMOS Gate Array IC.

7) Do not disassemble the module.

8) Do not press the reflector sheet at the back of the module.

9) Avoid damaging the TFT module. Do not press the center of the CCFL Reflector when it was taken out

from the packing container. Instead, press at the edge of the CCFL Reflector softly.

10) Do not rotate or tilt the signal interface connector of the TFT module when you insert or remove other

connector into the signal interface connector.

11) Do not twist or bend the TFT module when installation of the TFT module into an enclosure (Notebook

PC Bezel, for example). It should be taken into consideration that no bending/twisting forces are applied

to the TFT module from outside when designing the enclosure. Otherwise the TFT module may be

damaged.

12) Cold cathode fluorescent lamp in LCD contains a small amount of mercury. Please follow local regulations for

disposal.

13) The LCD module contains a small amount of material that has no flammability grade, so it should be supplied

by power complied with requirements of limited power source (2.11, IEC60950 or UL1950).

14) The CCFL in the LCD module is supplied with Limited Current Circuit (2.4, IEC60950 or UL 60950). Do not

connect the CCFL in Hazardous Voltage Circuit.

www.jxlcd.com

www.jxlcd.com

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 4/4

Page 5

2.0 General Description

This specification applies to the 17 inch Color TFT/LCD Module B170PW02

This module is designed for a display unit of notebook style personal computer.

The screen format is intended to support the WXGA +(1440(H) x 900(V)) screen and 262k colors (RGB 6-bits

data driver).

All input signals are LVDS interface compatible.

This module does not contain an inverter card for backlight.

22..11 DDiissppllaayy CChhaarraacctteerriissttiiccss

The following items are characteristics summary on the table under 25 ℃ condition:

ITEMS Unit SPECIFICATIONS

Screen Diagonal [mm] 17.0”

Active Area [mm] 367.20(H) x 229.50(V)

Pixels H x V 1440 (x3) x 900

Pixel Pitch [mm] 0..255(per one triad) x 0.255

Pixel Arrangement R.G.B. Vertical Stripe

Display Mode Normally White

Typical White Luminance(CCFL=6.0mA) [cd/m2] 385 Typ.(5 points average)

Contrast Ratio 350 : 1 Min ,400:1 Typ

Response Time [msec] 16 Typ.

Nominal Input Voltage VDD [Volt] +3.3 Typ.

Typical Power Consumption

(VDD line + VCFL line)

Weight [Grams] 1100g max. (w/o Inverter)

Physical Size [mm] 382.2(W) x 246.8(H) x 10.0(upper) max.

Electrical Interface 2 channel LVDS (4pair/1 channel)

Surface treatment Glare, low reflection

Support Color Native 262K colors ( RGB 6-bit data driver )

Temperature Range

Operating

Storage (Shipping)

www.jxlcd.com

www.jxlcd.com

[Watt] 13 Watt (w/o Inverter, All black pattern)@LCM

circuit 3.3 Watt(typ.),B/L input 9.8 Watt (typ.)

/8.6(lower) max

o

[

C]

o

[

C]

0 to +50

-20 to +60

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 5/5

Page 6

p

)

22..22 FFuunnccttiioonnaall BBlloocckk DDiiaaggrraamm

The following diagram shows the functional block of the 17 inches Color TFT/LCD Module:

(4 pairs LVDS )

Odd_RxIN0

Odd_RxIN1

Odd_RxIN2

Odd_RxCLKIN

Even_RxIN0

Even_RxIN1

Even_RxIN2

Even_RxCLKIN

VDD

GND

Mating Housing JAE FI-X30H

Mating ContactFI-XC3-1-15000

LCD DRIVE

CARD

JAE FI-XB30S-HF10 or compatible

LCD

Cont ro lle r

DC-DC

Converter

Ref circuit

Y-Driver

X-Driver

TFT A RRAY/CELL

1440(R/G/B) x 3

Bac kligh t U n it

Lam

Connector(2pin

JST BHSR-02VS-1

Mating Type SM02B-BHSS-1-TB

www.jxlcd.com

www.jxlcd.com

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 6/6

Page 7

3.0 Absolute Maximum Ratings

Absolute maximum ratings of the module is as following:

Item Symbol Min Max Unit Conditions

Logic/LCD Drive Voltage VDD -0.3 +4.0 [Volt]

Input Voltage of Signal Vin -0.3 VDD+0.3 [Volt]

CCFL Current ICFL - 7 [mA] rms

CCFL Ignition Voltage Vs - 1160(25oC) Vrms Note 1

Operating Temperature TOP 0 +50 [oC] Note 2

Operating Humidity HOP 5 95 [%RH] Note 2

Storage Temperature TST -20 +60 [oC] Note 2

Storage Humidity HST 5 95 [%RH] Note 2

Vibration 1.5 10-500 [G Hz]

Shock 180 , 2 [G ms] Half sine wave

Note 1 : Duration = 50msec

Note 2 : Maximum Wet-Bulb should be 39℃ and No condensation.

Wet bulb temperature chart

Twb=39°C

www.jxlcd.com

www.jxlcd.com

Operating Range

Storage Range

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 7/7

Page 8

4.0 Optical Characteristics

The optical characteristics are measured under stable conditions as follows under 25℃ condition:

Item

White Luminance

CCFL 6.0mA

Viewing Angle

Uniformity 5 Points 1.2

Uniformity 13 Points 1.5

CR: Contrast Ratio 350 400 - 6

Cross talk % 4 4

Response Time

Color / Chromaticity

Coordinates

(CIE 1931)

Unit

[cd/m2] 5 points average

[degree]

[degree]

[degree]

[degree]

[msec] Rising - 12 17

[msec] Falling - 4 8

[msec] Raising + Falling 16 25

Horizontal (Right)

CR = 10 (Left)

Vertical (Upper)

CR = 10 (Lower)

Red x 0.580 0.610 0.640

Red y 0.310 0.340 0.370

Green x 0.285 0.315 0.345

Green y 0.520 0.550 0.580

Blue x 0.115 0.145 0.175

Blue y 0.085 0.115 0.145

White x 0.290 0.320 0.350

White y

Note 1: Definition of 5 ,13 points position & white uniformity:

White uniformity is defined as the following with five/thirteen measurements (1~13).

Conditions Min. Typ. Max. Note

355 385 - 1,2,3

60

60

50

50

70

70

60

60

-

-

-

-

0.300 0.330 0.360

2,7

1

5

2,7

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 8/8

www.jxlcd.com

www.jxlcd.com

10mm

10mm

10mm

6

9

11

720 1080 360

7

1

5

3

12

2

4

10mm

8

10

13

10mm

225

450

675

Maximum Brightness of five (1,2,3,4,5) points

δ

=

W5

Minimum Brightness of five (1,2,3,4,5) points

Maximum Brightness of thirteen points

δ

=

W13

Minimum Brightness of thirteen points

Page 9

Note 2: Measurement method

The LCD module should be stabilized at given temperature for 30 minutes to avoid abrupt temperature change

during measuring. In order to stabilize the luminance, the measurement should be executed after lighting Backlight

for 30 minutes in a stable, windless and dark room.

Photodetector

(BM-5A,BM-7 or equivalent)

Field=2°

www.jxlcd.com

LCD Panel

www.jxlcd.com

Center of the screen

Note 3: Definition of Average Luminance of White (Y

Measure the luminance of gray level 63 at 5 points,Y

L (x) is corresponding to the luminance of the point X at Figure in Note (1).

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 9/9

):

L

= [L (1)+ L (2)+ L (3)+ L (4)+ L (5)] / 5

L

50 cm

TFT-LCD Module

Page 10

g

Note 4: Definition of Cross Talk (CT)

CT = | YB – YA | / YA × 100 (%)

Where

Y

A = Luminance of measured location without gray level 0 pattern (cd/m2)

YB = Luminance of measured location with gray level 0 pattern (cd/m2)

Note 5: Definition of response time:

The output signals of BM-7 or equivalent are measured when the input signals are changed from “Black” to

“White” (falling time) and from “White” to “Black” (rising time), respectively. The response time interval between the

10% and 90% of amplitudes. Refer to figure as below.

www.jxlcd.com

www.jxlcd.com

"Black"

100%

S

i

90%

g

n

a

l

(

R

e

l

a

t

i

v

e

v

a

l

u

10%

e

)

0%

Tr

Tf

"White""White"

Note 6. Definition of contrast ratio:

Contrast ratio is calculated with the following formula.

Contrast ratio (CR)=

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 10/10

Brightness on the “White” state

Bri

htness on the “Black” state

Page 11

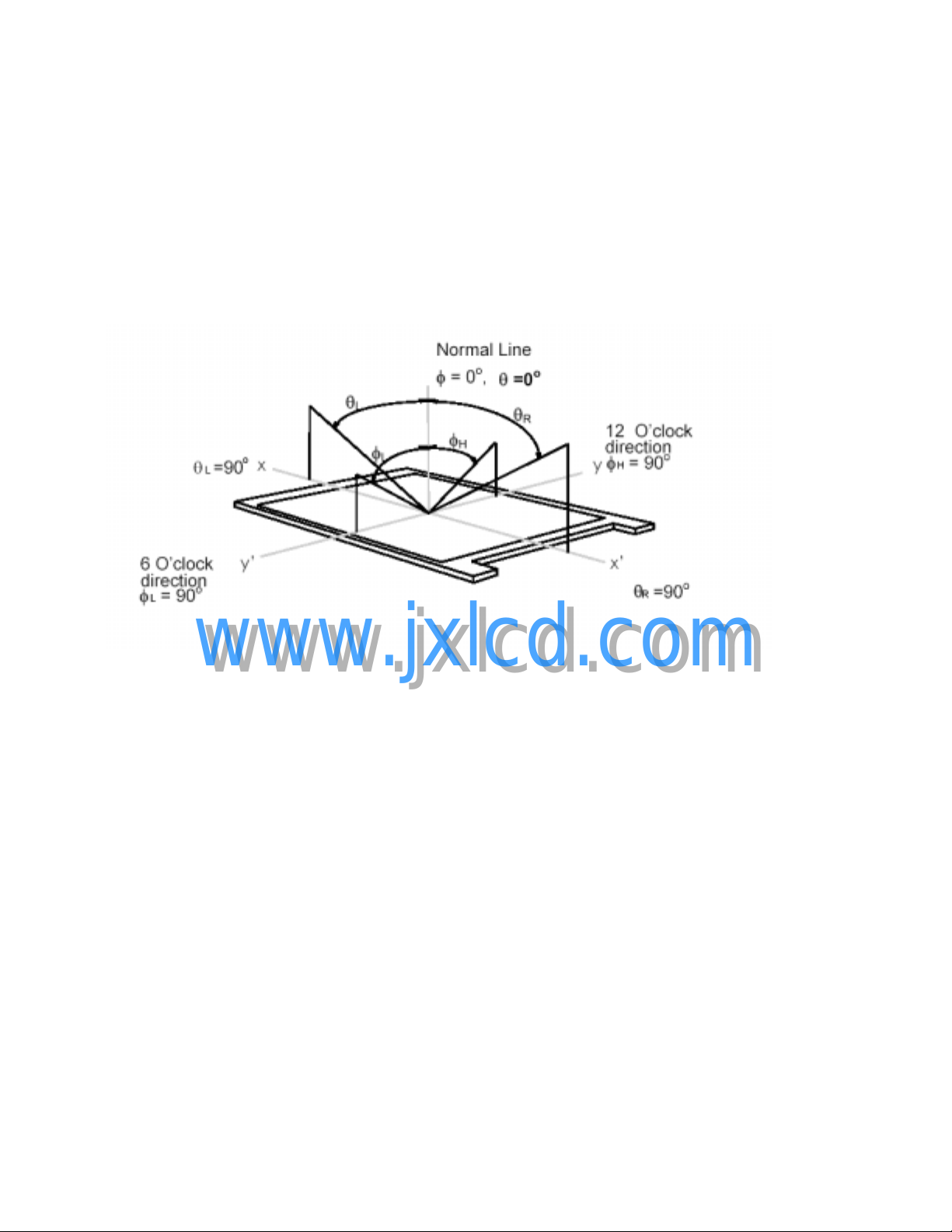

Note 7. Definition of viewing angle

Viewing angle is the measurement of contrast ratio ≧10, at the screen center, over a 180° horizontal and

180° vertical range (off-normal viewing angles). The 180° viewing angle range is broken down as follows; 90°

(θ) horizontal left and right and 90° (Φ) vertical, high (up) and low (down). The measurement direction is

typically perpendicular to the display surface with the screen rotated about its center to develop the desired

measurement viewing angle.

www.jxlcd.com

www.jxlcd.com

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 11/11

Page 12

y

5.0 Signal Interface

55..11 CCoonnnneeccttoorrss

Physical interface is described as for the connector on module.

These connectors are capable of accommodating the following signals and will be following components.

Connector Name / Designation

Manufacturer

Type / Part Number

Mating Housing/Part Number

Mating Contact/Part Number

Connector Name / Designation

Manufacturer

Type / Part Number

Mating Type / Part Number

55..22 SSiiggnnaall PPiinn

(1).Input signal interface

Pin no S

1 GND Ground

www.jxlcd.com

For Signal Connector

JAE or compatible

FI-XB30S-HF10 or compatible

FI-X30H

FI-XC3-1-15000

For Lamp Connector

JST

BHSR-02VS-1

SM02B-BHSS-1-TB

mbol Function Etc.

www.jxlcd.com

2 VDD Power supply ,3.3 V (typical)

3 VDD Power supply ,3.3 V (typical)

4 V

5 NC Reserved for supplier test

6 CLK

7 Data

8 Odd_RxIN0- -LVDS differential data input

9 Odd_RxIN0+ +LVDS differential data input

10 GND Ground

11 Odd_RxIN1- -LVDS differential data input

12 Odd_RxIN1+ +LVDS differential data input

13 GND Ground

14 Odd_RxIN2- -LVDS differential data input

15 Odd_RxIN2+ +LVDS differential data input

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 12/12

DDC 3.3V power

EDID

DDC Clock

EDID

DDC data

EDID

Page 13

16 GND Ground

17 Odd_RxCLKIN- -LVDS differential clock input

18 Odd_RxCLKIN+ +LVDS differential clock input

19 GND Ground

20 Even_RxIN0- -LVDS differential data input

21 Even_RxIN0+ +LVDS differential data input

22 GND Ground

23 Even_RxIN1- -LVDS differential data input

24 Even_RxIN1+ +LVDS differential data input

25 GND Ground

26 Even_RxIN2- -LVDS differential data input

27 Even_RxIN2+ +LVDS differential data input

28 GND Ground

29 Even_RxCLKIN- -LVDS differential clock input

30 Even_RxCLKIN+ +LVDS differential clock input

(2) LVDS channel interface data mapping diagram

ODD pair( 1st pixel input)

CK

DIN1

DIN2

DIN3

Even pair(2nd pixel input)

CK

DIN1

DIN2

www.jxlcd.com

www.jxlcd.com

G0 R5 R4 R3 R2 R1 R0

B1 B0 G5 G4 G3 G2 G1

DE VS HS B5 B4 B3 B2

G0 R5 R4 R3 R2 R1 R0

B1 B0 G5 G4 G3 G2 G1

DIN3

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 13/13

DE VS HS B5 B4 B3 B2

Page 14

55..33 SSiiggnnaall DDeessccrriippttiioonn

The module uses a LVDS receiver embedded in AUO’s ASIC. LVDS is a differential signal technology for LCD

interface and high-speed data transfer device.

Signal Name Description

V

+3.3V EDID Power

EDID

CLK

DATA

Odd_RxIN0-, Odd_RxIN0+

Even_RxIN0-, Even_RxIN0+

Odd_RxIN1-, Odd_RxIN1+

Even_RxIN1-, Even_RxIN1+

Odd_RxIN2-, Odd_RxIN2+

Even_RxIN2-, Even_RxIN2+

Odd_RxCLKIN,Odd_RxCLKIN0+

Even_RxCLKIN-,

Even_RxCLKIN0+

VDD +3.3V Power Supply

GND Ground

Note: Input signals shall be in low status when VDD is off.

Internal circuit of LVDS inputs are as following.

Signal Name Description

+RED5

+RED4

+RED3

+RED2

+RED1

+RED0

+GREEN 5

+GREEN 4

+GREEN 3

+GREEN 2

+GREEN 1

+GREEN 0

+BLUE 5

+BLUE 4

+BLUE 3

+BLUE 2

+BLUE 1

+BLUE 0

-DTCLK

DSPTMG

VSYNC

HSYNC

EDID Clock Input

EDID

EDID Data Input

EDID

Red Data 5 (MSB)

Red Data 4

Red Data 3

Red Data 2

Red Data 1

Red Data 0 (LSB)

Red-pixel Data

www.jxlcd.com

www.jxlcd.com

Green Data 5 (MSB)

Green Data 4

Green Data 3

Green Data 2

Green Data 1

Green Data 0 (LSB)

Green-pixel Data

Blue Data 5 (MSB)

Blue Data 4

Blue Data 3

Blue Data 2

Blue Data 1

Blue Data 0 (LSB)

Blue-pixel Data

Data Clock

Display Timing

Vertical Sync

Horizontal Sync

LVDS differential data input (Red0-Red5, Green0)

LVDS differential data input (Green1-Green5, Blue0-Blue1)

LVDS differential data input (Blue2-Blue5, Hsync, Vsync, DSPTMG)

LVDS differential clock input

Red-pixel Data

Each red pixel's brightness data consists of these 6 bits

pixel data.

Green-pixel Data

Each green pixel's brightness data consists of these 6 bits

pixel data.

Blue-pixel Data

Each blue pixel's brightness data consists of these 6 bits

pixel data.

The typical frequency is 48.2 MHz. The signal is used to

strobe the pixel data and DSPTMG signals. All pixel data

shall be valid at the falling edge when the DSPTMG signal

is high.

This signal is strobed at the falling edge of

-DTCLK. When the signal is high, the pixel data shall be

valid to be displayed.

The signal is synchronized to -DTCLK .

The signal is synchronized to -DTCLK .

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 14/14

Page 15

Note: Output signals from any system shall be low or Hi-Z state when VDD is off.

55..44 SSiiggnnaall EElleeccttrriiccaall CChhaarraacctteerriissttiiccss

Input signals shall be in low status when VDD is off.

It is recommended to refer the specifications of SN75LVDS86DGG (Texas Instruments) in detail.

Signal electrical characteristics are as follows;

Parameter Condition Min Max Unit

Vth

Vtl

Differential Input High

Voltage(Vcm=+1.2V)

Differential Input Low

Voltage(Vcm=+1.2V)

55..55 SSiiggnnaall ffoorr LLaammpp ccoonnnneeccttoorr

Pin # Signal Name

1 Lamp High Voltage

2 Lamp Low Voltage

www.jxlcd.com

www.jxlcd.com

-100

100

[mV]

[mV]

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 15/15

Page 16

6.0 Pixel Format Image

Following figure shows the relationship of the input signals and LCD pixel format.

1

2

1439 1440

1st Line

900th Line

R G B R G B

R G B R G B

R G B R G B

R G B R G B

7.0 Parameter guide line for CCFL Inverter

www.jxlcd.com

www.jxlcd.com

Parameter

White Luminance

5 points average

CCFL current(ICFL) 6.0 7.0 [mA] rms

CCFL Frequency(FCFL) 45 50 80 [KHz]

CCFL Ignition Voltage(Vs)

CCFL Voltage (Reference)

(VCFL)

CCFL Power consumption

(PCFL)

Note 1: DP-1 are AUO recommended Design Points.

*1 All of characteristics listed are measured under the condition using the AUO Test inverter.

*2 In case of using an inverter other than listed, it is recommended to check the inverter carefully. Sometimes,

interfering noise stripes appear on the screen, and substandard luminance or flicker at low power may happen.

*3 In designing an inverter, it is suggested to check safety circuit ver carefully. Impedance of CCFL, for instance,

becomes more than 1 [M ohm] when CCFL is damaged.

Min DP-1 Max Units Condition

350

775 815 940 [Volt] rms

385

9.8

1500 [Volt] rms

[cd/m

[Watt]

2

]

(Ta=25

(Ta=25

Note 2

(Ta=25

Note 3

(Ta= 0

Note 4

(Ta=25

Note 5

(Ta=25

Note 5, 6

℃)

℃)

℃)

℃)

℃)

℃)

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 16/16

Page 17

*4 Generally, CCFL has some amount of delay time after applying start-up voltage. It is recommended to keep

on applying start-up voltage for 1 [Sec] until discharge.

*5 The CCFL inverter operating frequency must be carefully chosen so that no interfering noise stripes on the

screen were induced.

*6 Reducing CCFL current increases CCFL discharge voltage and generally increases CCFL discharge

frequency. So all the parameters of an inverter should be carefully designed so as not to produce too much

leakage current from high-voltage output of the inverter.

Note 2: It should be employed the inverter, which has “Duty Dimming”, if ICCFL is less than 4mA.

Note 3: The CCFL inverter operating frequency should be carefully determined to avoid interference between

inverter and TFT LCD.

Note 4: The inverter open voltage should be designed larger than the lamp starting voltage at T=0

backlight may be blinking for a moment after turning on or not be able to turn on. The open voltage should

be measured after ballast capacitor. If an inverter has shutdown function it should keep its open voltage. for

longer than 1 second even if lamp connector is open.

Note 5: Calculator value for reference (ICFL×VCFL=PCFL)

Note 6: This model has 2 CCFL lamps.

o

C, otherwise

8.0 Interface Timings

88..11 TTiimmiinngg CChhaarraacctteerriissttiiccss

Parameter Symbol Min. Typ. Max. Unit Condition

Clock frequency 1/ T

Period

www.jxlcd.com

www.jxlcd.com

Horizontal

Section

Front Porch

Vertical

Section

Active

Blanking

Hsync Width

Back Porch

Period

Active

Blanking

Vsync Width

Back Porch

Front Porch

CLOCK

T

H

T

HD

THB - 160 -

T

HSW

T

- 112

HSB

T

HSF

T

V

T

VD

TVB - 12 -

T

VSW

T

- 6

VSB

T

VSF

20 48.2 85 MHz LVDS 2 channel input

- 880 -

720 720 720

T

- 16 -

-

- 32

- 912 -

900 900 900

- 3 -

- 3

-

-

-

CLOCK

T

HD

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 17/17

Page 18

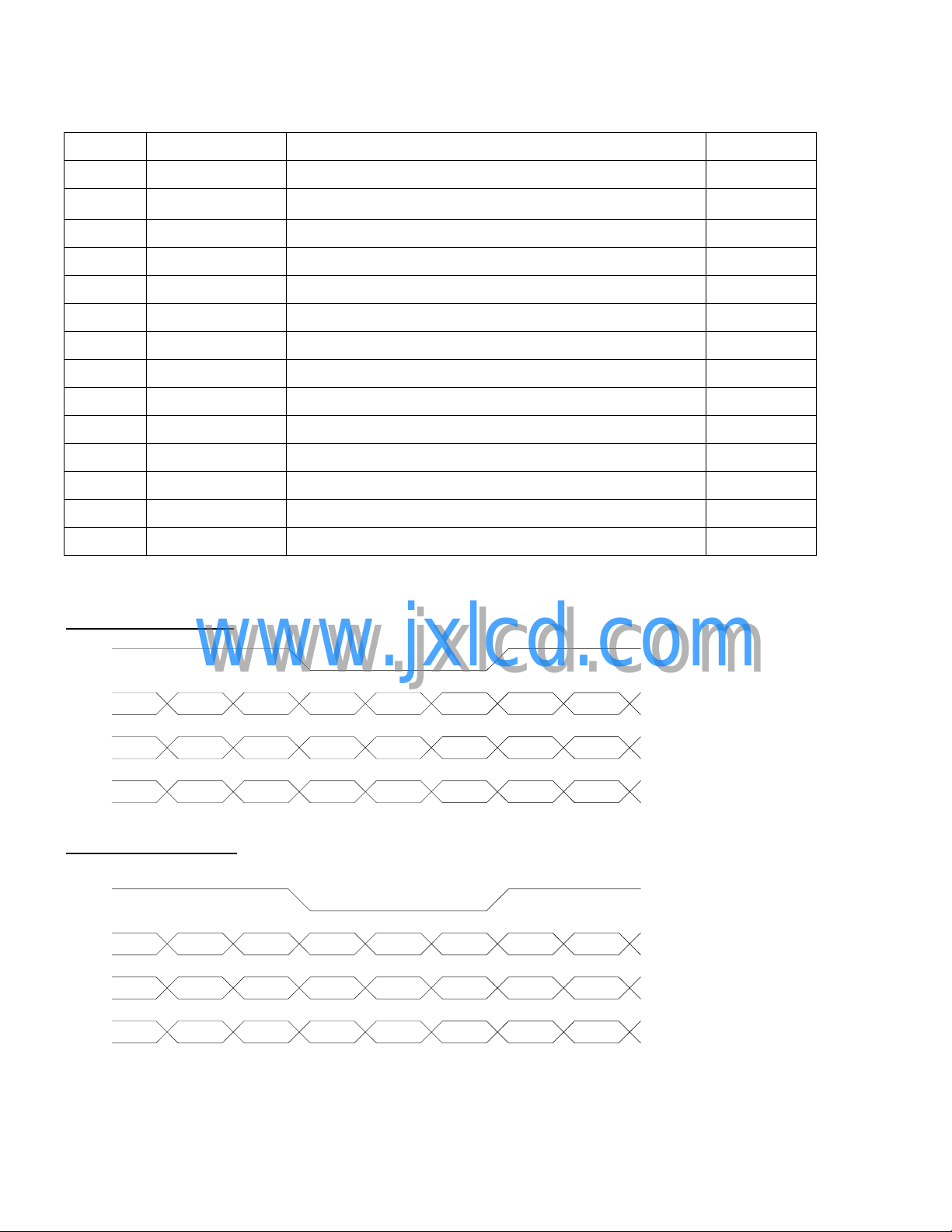

88..22 TTiimmiinngg DDeeffiinniittiioonn

www.jxlcd.com

www.jxlcd.com

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 18/18

Page 19

9.0 Power Consumption

Input power specifications are as follows;

Symbol Parameter Min Typ Max Units Condition

Module

VDD Logic/LCD Drive

PDD VDD Power 2.15 [Watt] All White pattern

PDD Max VDD Power max 3.3 [Watt] All BLACK pattern

IDD IDD Current 630 mA All White pattern

IDD Max IDD Current max 1000 mA All BLACK pattern

VDDrp Allowable

VDDns Allowable

Lamp

ICFL CCFL current 3.0 6.0 7.0 [mA]

VCFL CCFL Voltage

PCFL CCFL Power

Total Power

Consumption

3.0 3.3 3.6 [Volt] Load Capacitance 20uF

Voltage

100 [mV]

Logic/LCD Drive

Ripple Voltage

100 [mV]

Logic/LCD Drive

Ripple Noise

(Reference)

www.jxlcd.com

www.jxlcd.com

consumption

13.1 Watt typ (w/o Inverter, All black pattern)@LCM circuit 3.3 Watt(typ.),B/L input 9.8

Watt(typ.)

785

9.8

p-p

p-p

rms

[Volt]

rms

[Watt]

(Ta=25

(Ta=25

(Ta=25

℃)

℃)

℃)

Note : VDD=3.3V

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 19/19

Page 20

10. Power ON/OFF Sequence

VDD power and lamp on/off sequence is as follows. Interface signals are also shown in the chart. Signals

from any system shall be Hi-Z state or low level when VDD is off.

Sequence of Power-on/off and signal-on/off

Power Supply VDD

LVDS Interface

Backlight On

Apply the lamp voltage within the LCD operating range. When the backlight turns on before the

LCD operation or the LCD turns off before the backlight turns off, the display may momentarily

become abnormal.

0.1VDD

www.jxlcd.com

www.jxlcd.com

T1

0.9VDD

T2

T5

0.9VDD

T6

T3

0.1VDD

≦T1≦10ms

1ms

≦T2≦50ms

6ms

≦T3<50ms

0ms

400ms

200ms

200ms

≦T4

≦T5

≦T6

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 20/20

Page 21

11.0 Reliability /Safety Requirement

1111..11 RReelliiaabbiilliittyy TTeesstt CCoonnddiittiioonnss

Items Required Condition

Temperature Humidity Bias

High Temperature Operation

Low Temperature Operation

Continuous Life

On/Off Test ON/30 sec. OFF/30sec., 30,000 cycles

Hot Storage

Cold Storage

Thermal Shock Test

Hot Start Test

Cold Start Test

Shock Test (Non-Operating)

Vibration Test (Non-Operating)

ESD

Altitude Test

Maximum Side Mount Torque 2.5kgf.cm .

CCFL Life : 10,000 hours minimum

MTBF(Excluding the CCFL) : 30,000 hours with a confidence level 90%

www.jxlcd.com

www.jxlcd.com

40

℃/90%,300Hr

50

℃/Dry,300Hr

0

℃,500Hr

25

℃ ,2000 hours

60

℃/40% RH ,240 hours

-20

℃/50% RH ,240 hours

-20

℃/30 min ,60℃/30 min 100cycles

50

℃/1 Hr min. power on/off per 5 minutes, 5 times

0

℃/1 Hr min. power on/off per 5 minutes, 5 times

180G, 2ms, Half-sine wave

Sinusoidal vibration, 1.5G zero-to-peak, 10 to 500 Hz,

0.5 octave/minute; 0.5hr in each of three mutually

perpendicular axes.

Contact : operation

Air : operation

10000 ft / operation / 8Hr

30000ft / non-operation / 24r

±

8KV / non-operation ±10KV

±15KV / non-operation ±20KV

1111..22 SSaaffeettyy

UL 60950

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 21/21

Page 22

12.0 Packing dimension

14.1" Panel

17” panel 17” panel * 10 pcs

ESD Bag

www.jxlcd.com

www.jxlcd.com

For

For

17”

14"

use

use

mark

mark

Paper pad

Cushion

Top

14.1" Panel * 20 pcs

Cushion

side

Carton

"H" taping close

Carton

label

position

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 22/22

Page 23

13.0 Mechanical Characteristics

1133..11 LLCCMM OOuuttlliinnee ddiimmeennssiioonn ((FFrroonntt VViieeww))

www.jxlcd.com

www.jxlcd.com

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 23/23

Page 24

1133..22 LLCCMM OOuuttlliinnee DDiimmeennssiioonn ((RReeaarr VViieeww))

www.jxlcd.com

www.jxlcd.com

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 24/24

Page 25

1133..33 SSccrreeww HHoollee DDeepptthh aanndd CCeenntteerr PPoossiittiioonn

Screw hole minimum depth, from side surface =2.5 mm (See drawing)

Screw hole center location, from front surface = 4.2

Screw maximum length = 2.3 mm (See drawing)

Screw Torque: Maximum2.5 kgzf-cm

± 0.3mm (See drawing)

4.2 + 0.3

10.0 (Max)

www.jxlcd.com

www.jxlcd.com

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 25/25

Page 26

14. Shipping Label Format

23mm

www.jxlcd.com

www.jxlcd.com

Model name

83mm

Hardware

Week code

Firmware

Manufacturing area

Control

code

Model name

83mm

23mm

Hardware

(C) Copyright AU Optronics

Sep., 2003 All Rights Reserved. B170PW02 V0 Spec Ver.6

No Reproduction and Redistribution Allowed. 26/26

Week code

Firmware

Manufacturing area

Control

code

Loading...

Loading...