AUO T645HW05 V0 Specification

T645HW05 V0 Product Specification

Rev. 1.0

Model Name: T645HW05 V0

Issue Date : 2011/05/19

( )Preliminary Specifications

(****)Final Specifications

© Copyright AUO Optronics Corp. 2010 All Rights Reserved. Page 1 / 33

T645HW05 V0 Product Specification

Rev. 1.0

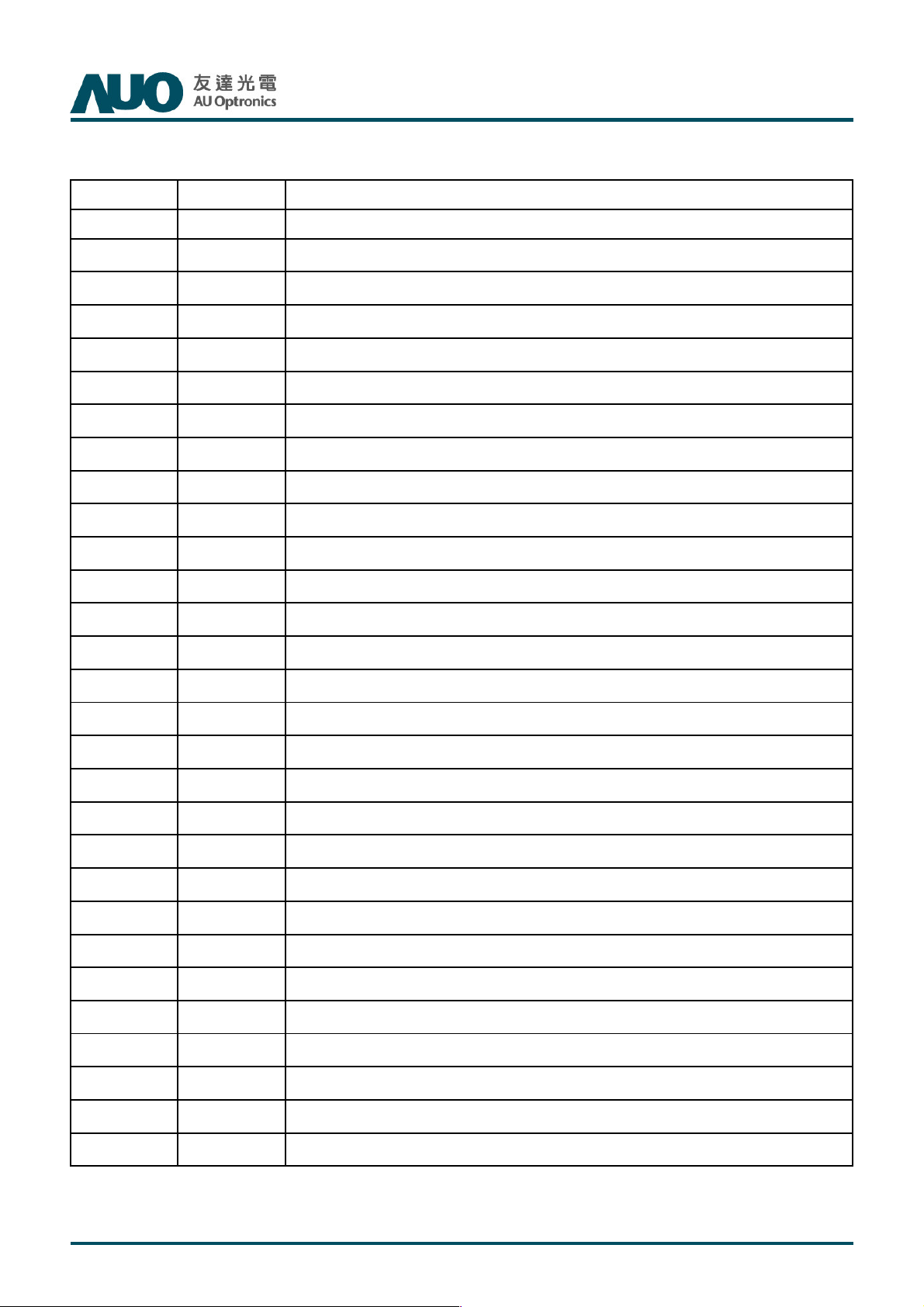

Contents

No

CONTENTS

RECORD OF REVISIONS

1 GENERAL DESCRIPTION

2 ABSOLUTE MAXIMUM RATINGS

3 ELECTRICAL SPECIFICATION

3-1 ELECTRIACL CHARACTERISTICS

3-2 INTERFACE CONNECTIONS

3-3 SIGNAL TIMING SPECIFICATION

3-4 SIGNAL TIMING WAVEFORM

3-5 COLOR INPUT DATA REFERENCE

3-6 POWER SEQUENCE

3-7 BACKLIGHT SPECIFICATION

4 OPTICAL SPECIFICATION

5 MECHANICAL CHARACTERISTICS

6 RELIABILITY TEST ITEMS

7 INTERNATIONAL STANDARD

7-1 SAFETY

7-2 EMC

8 PACKING

8-1 DEFINITION OF LABEL

8-2 PACKING METHODS

8-3 PALLET AND SHIPMENT INFORMATION

9 PRECAUTION

9-1 MOUNTING PRECAUTIONS

9-2 OPERATING PRECAUTIONS

9-3 ELECTROSTATIC DISCHARGE CONTROL

9-4 PRECAUTIONS FOR STRONG LIGHT EXPOSURE

9-5 STORAGE

9-6 HANDLING PRECAUTIONS FOR PROTECT FILM

© Copyright AUO Optronics Corp. 2010 All Rights Reserved. Page 2 / 33

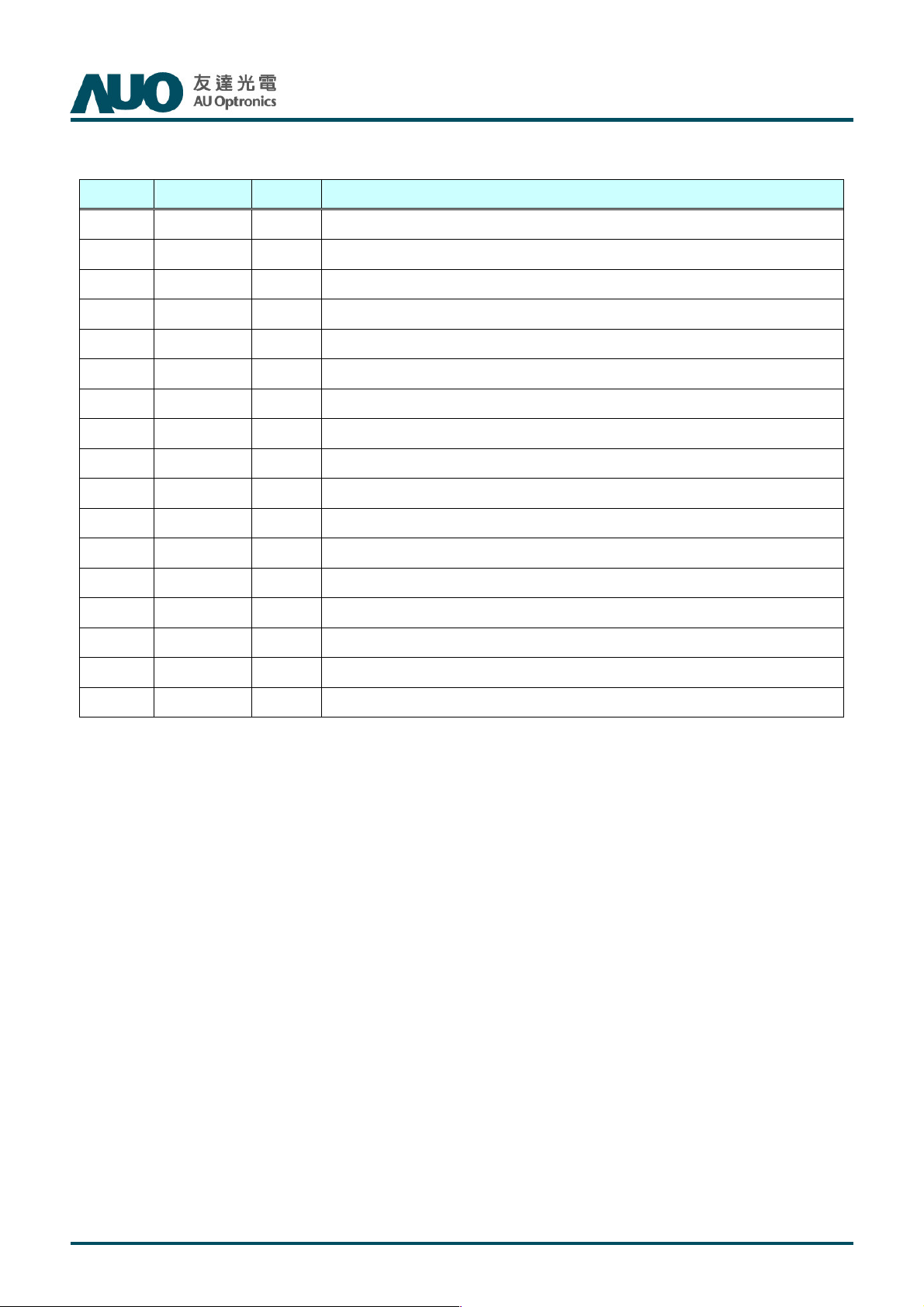

Record of Revision

T645HW05 V0 Product Specification

Rev. 1.0

Version

1.0 2010/11/19

1.1 2011/5/19 Update power consumption.

Date Page Description

First release

© Copyright AUO Optronics Corp. 2010 All Rights Reserved. Page 3 / 33

T645HW05 V0 Product Specification

Rev. 1.0

1. General Description

This specification applies to the 64.5 inch Color TFT-LCD Module T645HW05 V0. This LCD module has a TFT

active matrix type liquid crystal panel 1920 x 1080 pixels, and diagonal size of 64.5 inch. This module supports

1920 x 1080 mode. Each pixel is divided into Red, Green and Blue sub-pixels or dots which are arranged in vertical

stripes. Gray scale or the brightness of the sub-pixel color is determined with a 10-bit gray scale signal for each

dot.

The T645HW05 V0 has been designed to apply the 10-bit 4 channel LVDS interface method. It is intended to

support displays where high brightness, wide viewing angle, high color saturation, and high color depth are very

important.

* General Information

Items Specification Unit Note

Active Screen Size 64.53 inch

Display Area 1428.48 (H) x 803.52 (V) mm

Outline Dimension 1508.0(H) x 878.0(V) x 12.8(D) mm

Driver Element a-Si TFT active matrix

Display Colors 10 bit, 1.07B Colors

Number of Pixels 1920 x 1080 Pixel

Pixel Pitch 0.744 mm

Pixel Arrangement RGB vertical stripe

Display Operation Mode Normally Black

Surface Treatment HC, 3H

Best Viewing Distance 2.4 M

© Copyright AUO Optronics Corp. 2010 All Rights Reserved. Page 4 / 33

T645HW05 V0 Product Specification

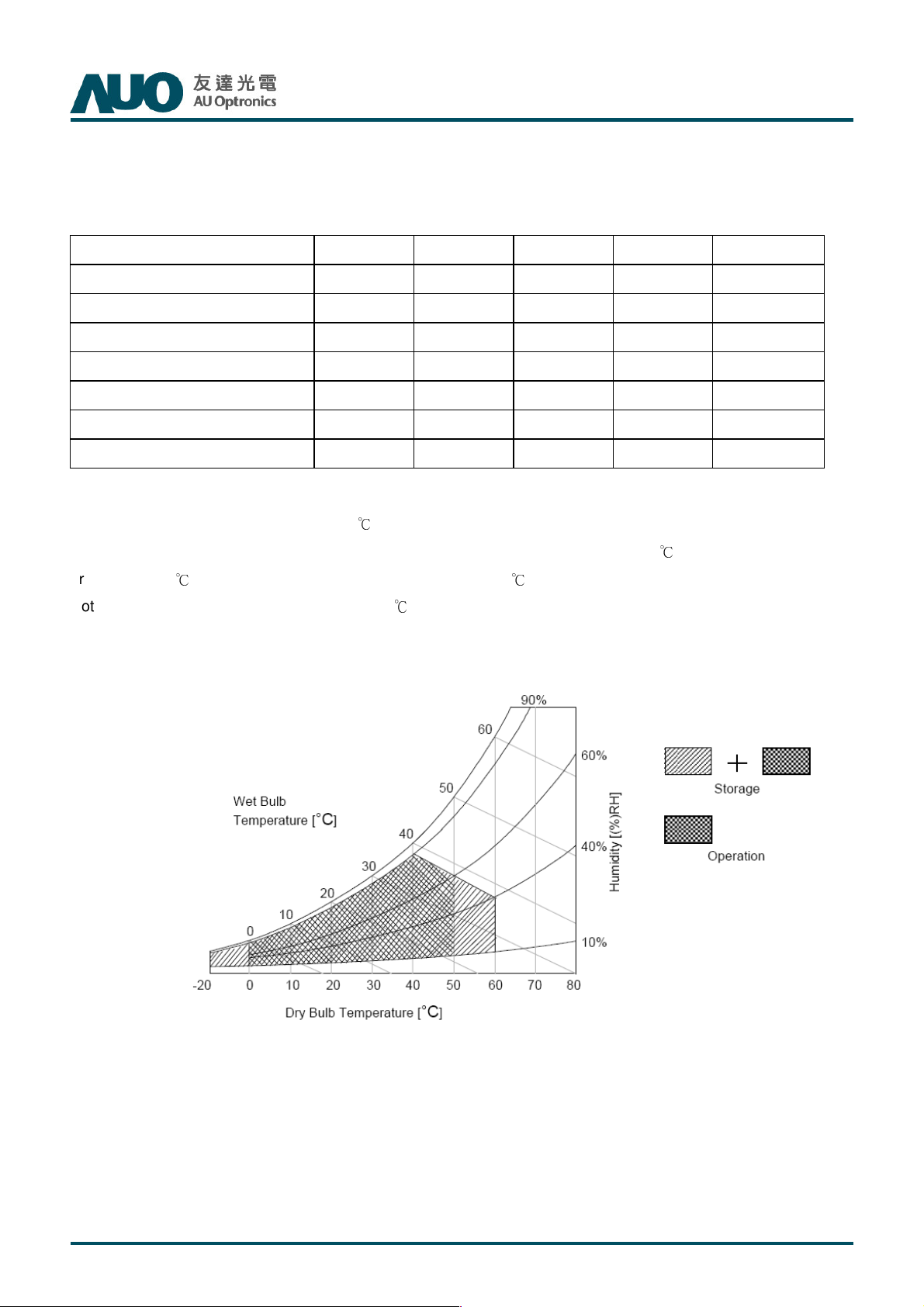

2. Absolute Maximum Ratings

The followings are maximum values which, if exceeded, may cause faulty operation or damage to the unit

Item Symbol Min Max Unit Conditions

Logic/LCD Drive Voltage VDD -0.3 14 [Volt] Note 1

Input Voltage of Signal Vin -0.3 4 [Volt] Note 1

Operating Temperature TOP 0 +50 [oC] Note 2

Operating Humidity HOP 10 90 [%RH] Note 2

Storage Temperature TST -20 +60 [oC] Note 2

Storage Humidity HST 10 90 [%RH] Note 2

Panel Surface Temperature PST - 65 [oC] Note 3

Note 1: Duration:50 msec.

Note 2 : Maximum Wet-Bulb should be 39 and No condensation.℃

Rev. 1.0

The relative humidity must not exceed 90% non-condensing at temperatures of 40 or less. At temperatures

greater than 40 , the wet bulb temperature must not exceed 39 .

Note 3: Surface temperature is measured at 50℃ Dry condition

℃ ℃

℃

© Copyright AUO Optronics Corp. 2010 All Rights Reserved. Page 5 / 33

s

µ

T645HW05 V0 Product Specification

Rev. 1.0

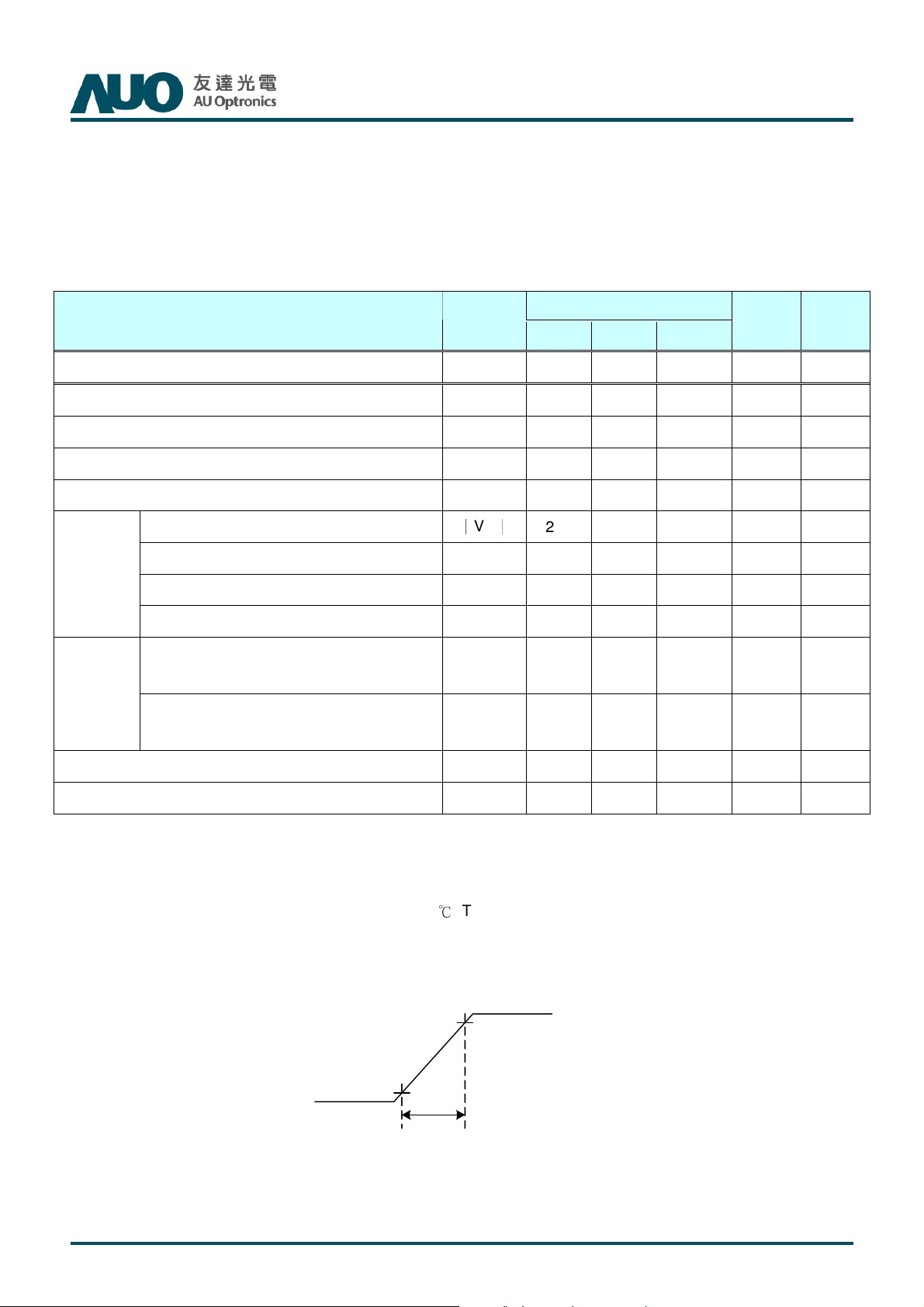

3. Electrical Specification

The T645HW05 V0 requires two power inputs. One is employed to power the LCD electronics and to drive the TFT

array and liquid crystal. The second input for BLU is to power inverter.

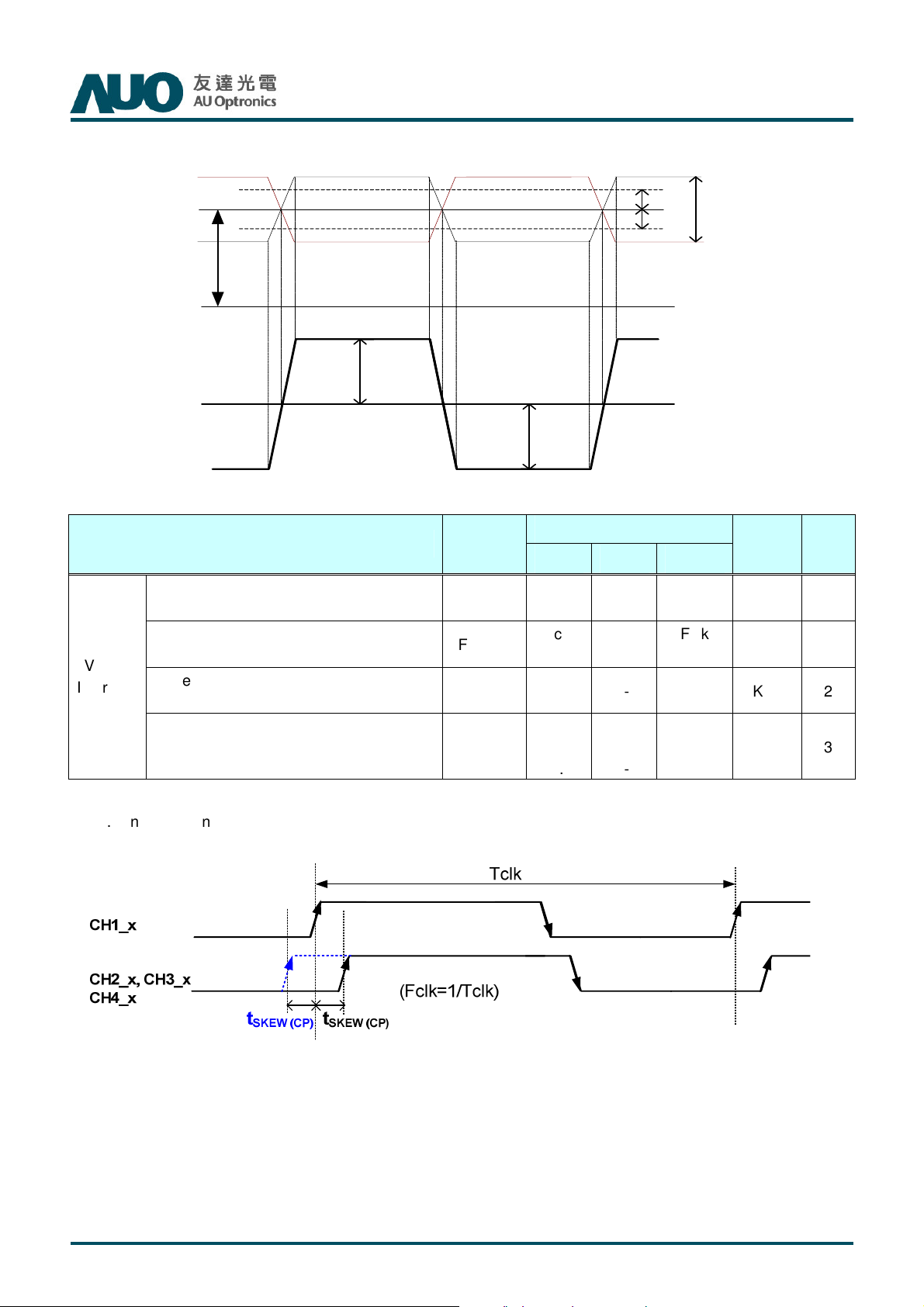

3.1 Electrical Characteristics

Parameter Symbol

Unit Note

Min. Typ. Max

LCD

Power Supply Input Voltage VDD 10.8 12.0 13.2 VDC 1

Power Supply Input Current IDD 0.6 1.2 1.8 A 2

Power Consumption PC -- 14.4 21.6 Watt 2

Value

Inrush Current I

Input Differential Voltage

LVDS

Interface

Differential Input High Threshold Voltage VTH +100 -- +300 4 4

Differential Input Low Threshold Voltage VTL -300 -- -100 4 4

Input Common Mode Voltage V

-- -- 7 A 3

RUSH

∣

V

∣

ID

1.10 1.25 1.40 VDC 4

ICM

200 400 600 mVDC 4

VIH

CMOS

Interface

Input High Threshold Voltage

(High)

VIL

Input Low Threshold Voltage

2.7 -- 3.3 VDC --

0 -- 0.6 VDC --

(Low)

Backlight Power Consumption PBL -- 192 205 Watt --

Life Time 30,000

-- Hours

--

Note :

1. The ripple voltage should be controlled under 10% of VCC

2. V

= 12.0V, Fv = 120Hz, F

DD

= 82MHz , 25 ℃, Test Pattern : White Pattern

CLK

>> refer to “Section:3.3 Signal Timing Specification, Typical timing”

3. Measurement condition : Rising time = 400us

VVVV

DD

DD

DDDD

GND

GND

GNDGND

10%

400

400

400400

90%

© Copyright AUO Optronics Corp. 2010 All Rights Reserved. Page 6 / 33

T645HW05 V0 Product Specification

Rev. 1.0

4. V

= 1.25V

ICM

L V D S -

V

IC M

L V D S +

G N D

0 V

|VID|

|VID|

V

T H

|VID|

V

T L

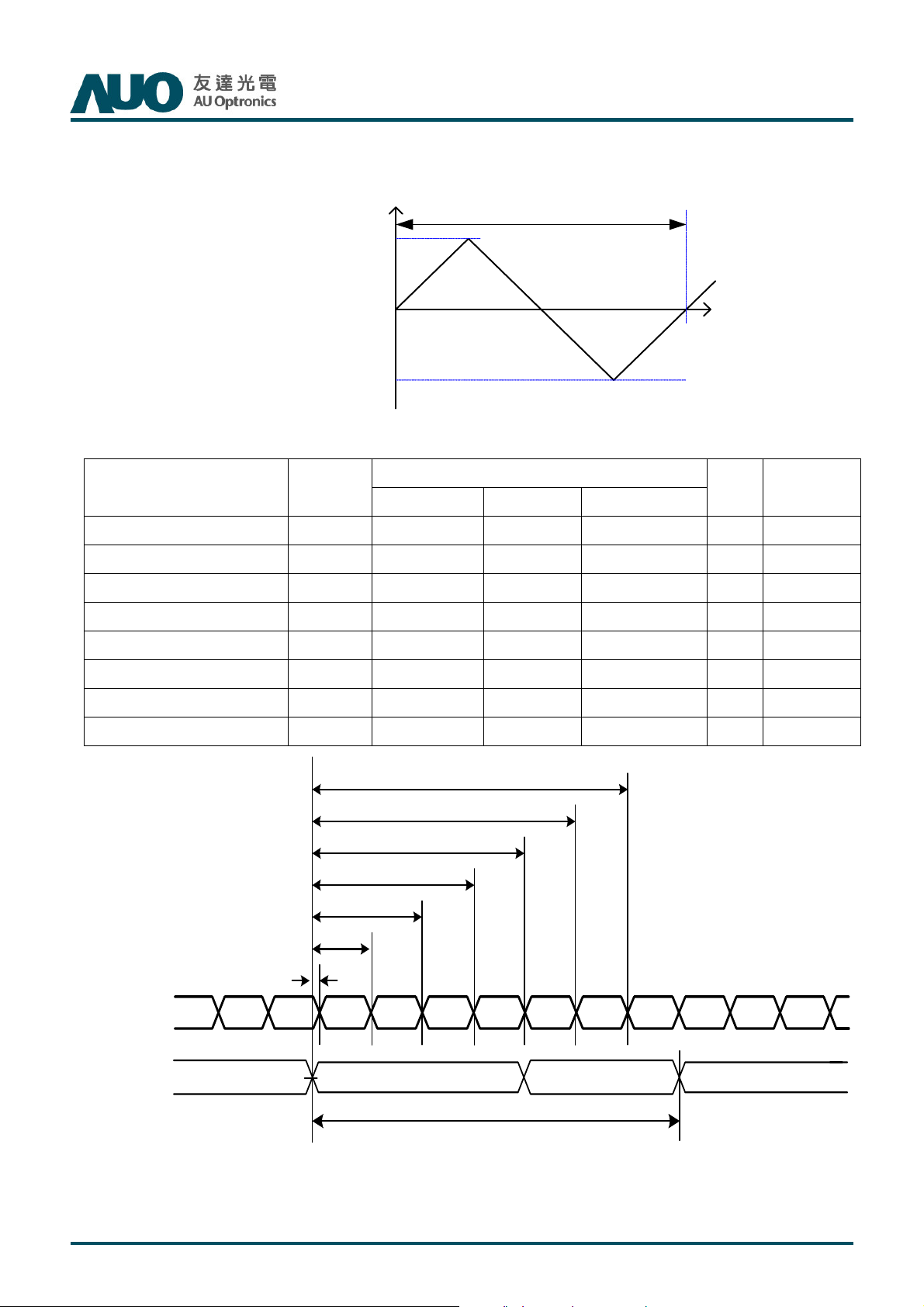

3.2 AC Electrical Characteristics

Parameter Symbol

Input Channel Pair Skew Margin t

Receiver Clock : Spread Spectrum

LVDS

Interface

Modulation range

Receiver Clock : Spread Spectrum

Modulation frequency

Receiver Data Input Margin

Fclk = 85 MHz

Fclk = 65 MHz

1. Input Channel Pair Skew Margin

SKEW (CP)

Fclk_ss

Fss

tRMG

Value

Min. Typ. Max

-500 -- +500 ps 1

Fclk

-3%

30

-0.4

-0.5

--

--

--

--

Fclk

+3%

200

0.4

0.5

Unit Note

MHz

2

KHz

2

ns

3

Note: x = 0, 1, 2, 3, 4

© Copyright AUO Optronics Corp. 2010 All Rights Reserved. Page 7 / 33

T645HW05 V0 Product Specification

2. LVDS Receiver Clock SSCG (Spread spectrum clock generator) is defined as below figures

1111////FFFF

SS

SS

SSSS

Fclk

Fclk____ss

FclkFclk

3. Receiver Data Input Margin

ss((((max

ssss

Fclk

Fclk

FclkFclk

Fclk

Fclk____ss

FclkFclk

ss((((min

ssss

max))))

maxmax

min))))

minmin

Rev. 1.0

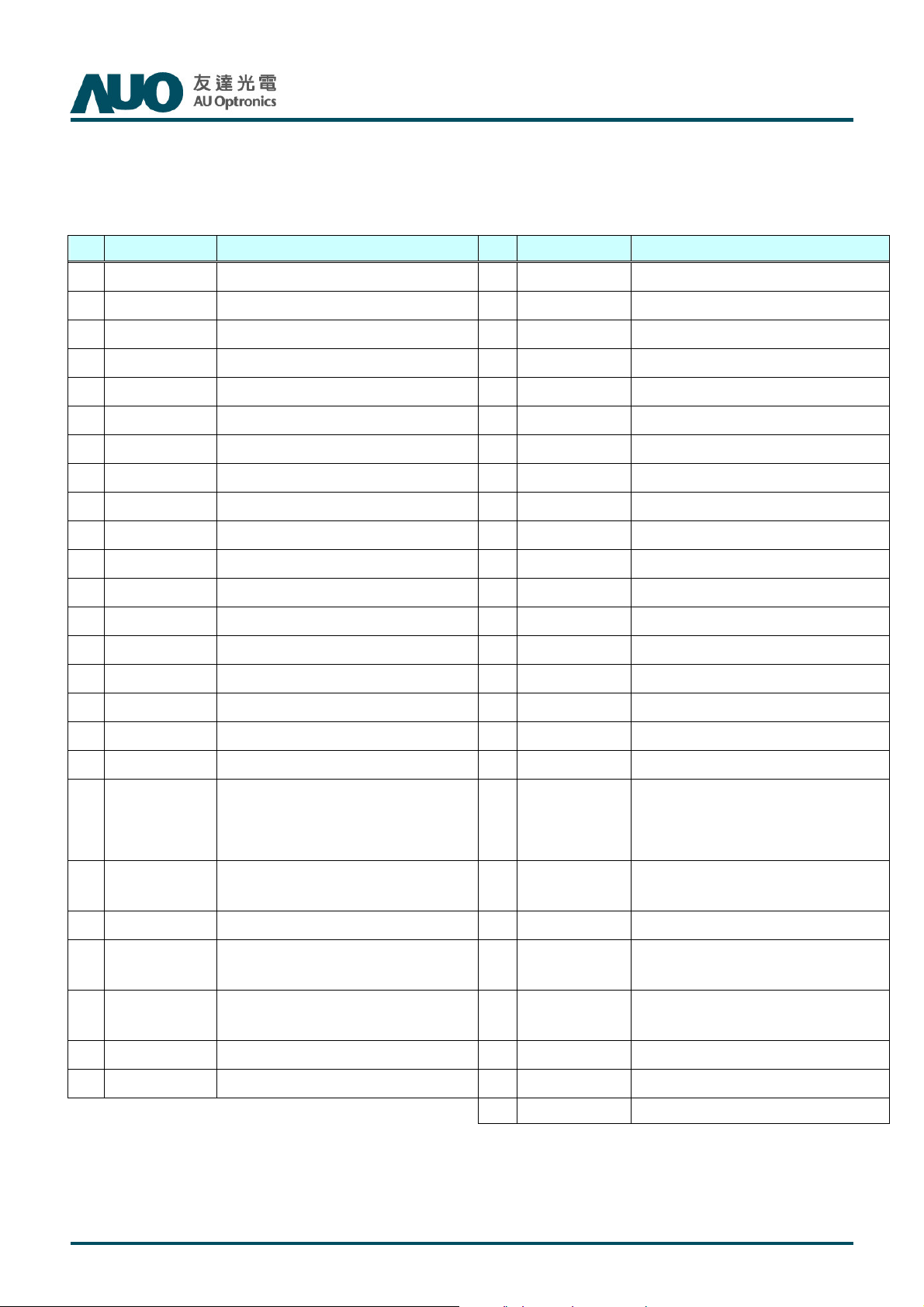

Parameter Symbol

Min Type Max

Input Clock Frequency Fclk Fclk (min) -- Fclk (max) MHz

Input Data Position0 tRIP1 -|tRMG| 0 |tRMG| ns

Input Data Position1 tRIP0 T/7-|tRMG| T/7 T/7+|tRMG| ns

Input Data Position2 tRIP6 2T/7-|tRMG|

Input Data Position3 tRIP5 3T/7-|tRMG|

Input Data Position4 tRIP4 4T/7-|tRMG|

Input Data Position5 tRIP3 5T/7-|tRMG|

Input Data Position6 tRIP2 6T/7-|tRMG|

Rating

Unit

2T/7 2T/7+|tRMG| ns

3T/7 3T/7+|tRMG| ns

4T/7 4T/7+|tRMG| ns

5T/7 5T/7+|tRMG| ns

6T/7 6T/7+|tRMG| ns

tRIP2

tRIP3

tRIP4

tRIP5

tRIP6

Note

T=1/Fclk

tRIP0

tRIP1

LVDS-Rx

Input Data

Rx1 Rx0 Rx6 Rx5 Rx4 Rx3 Rx2 Rx1 Rx0 Rx6Rx2Rx3

LVDS-Rx

VVVV

=

= 0000VVVV

= =

diff

diff

Input Clock

diff diff

1/Fclk=T

© Copyright AUO Optronics Corp. 2010 All Rights Reserved. Page 8 / 33

3.3 Interface Connections

LCD connector: FI-RE51S-HF (Manufactured by JAE)

Mating connector: FI-RE51S-HL (Manufactured by JAE)

T645HW05 V0 Product Specification

Rev. 1.0

PIN

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Symbol Description PIN

VDD Power Supply, +12V DC Regulated 26

VDD Power Supply, +12V DC Regulated 27

VDD Power Supply, +12V DC Regulated 28

VDD Power Supply, +12V DC Regulated 29

VDD Power Supply, +12V DC Regulated 30

GND Ground 31

GND Ground 32

GND Ground 33

GND Ground 34

CH2_0-

CH2_0+

CH2_1-

CH2_1+

CH2_2-

CH2_2+

LVDS Channel 2, Signal 0- 35

LVDS Channel 2, Signal 0+ 36

LVDS Channel 2, Signal 1- 37

LVDS Channel 2, Signal 1+ 38

LVDS Channel 2, Signal 2- 39

LVDS Channel 2, Signal 2+ 40

Symbol Description

CH4_0+

CH4_1-

CH4_1+

CH4_2-

CH4_2+

GND

CH4_CLK-

CH4_CLK+

GND

CH4_3-

CH4_3+

CH4_4-

CH4_4+

GND Ground

Reverse AUO Internal Use Only

LVDS Channel 4, Signal 0+

LVDS Channel 4, Signal 1-

LVDS Channel 4, Signal 1+

LVDS Channel 4, Signal 2-

LVDS Channel 4, Signal 2+

Ground

LVDS Channel 4, Clock -

LVDS Channel 4, Clock +

Ground

LVDS Channel 4, Signal 3-

LVDS Channel 4, Signal 3+

LVDS Channel 4, Signal 4-

LVDS Channel 4, Signal 4+

16

17

18

19

20

21

22

23

24

25

GND

CH2_CLK-

CH2_CLK+

GND

CH2_3-

CH2_3+

CH2_4-

CH2_4+

GND

CH4_0-

Ground 41

LVDS Channel 2, Clock - 42

LVDS Channel 2, Clock + 43

Ground 44

LVDS Channel 2, Signal 3- 45 LVDS_SEL

LVDS Channel 2, Signal 3+ 46

LVDS Channel 2, Signal 4- 47

LVDS Channel 2, Signal 4+ 48

Ground 49

LVDS Channel 4, Signal 0- 50

51

Reverse AUO Internal Use Only

Reverse AUO Internal Use Only

Reverse AUO Internal Use Only

HDR_IN

Reverse AUO Internal Use Only

3D_SEL

BITSEL

Reverse AUO Internal Use Only

Reverse AUO Internal Use Only

Reverse AUO Internal Use Only

HDR Function ON/OFF Selection

. Open / Low: HDR Function Disable

. High: HDR Function Enable

Open/High(3.3V) for NS,

Low(GND) for JEIDA

Open/High(3.3V) for 2D,

Low(GND) for 3D

Open/High(3.3V) for 10bit,

Low(GND) for 8bit

© Copyright AUO Optronics Corp. 2010 All Rights Reserved. Page 9 / 33

LCD connector: FI-RE41S-HF (Manufactured by JAE)

Mating connector: FI-RE41S-HL (Manufactured by JAE)

T645HW05 V0 Product Specification

Rev. 1.0

PIN Symbol Description PIN

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

VDD Power Supply, +12V DC Regulated 21

VDD Power Supply, +12V DC Regulated 22

V

DD

V

DD

V

DD

GND Ground 26

GND Ground 27

GND Ground 28

GND Ground 29

CH1_0-

CH1_0+

CH1_1-

CH1_1+

CH1_2-

CH1_2+

Power Supply, +12V DC Regulated 23

Power Supply, +12V DC Regulated 24

Power Supply, +12V DC Regulated 25

LVDS Channel 1, Signal 0- 30

LVDS Channel 1, Signal 0+ 31

LVDS Channel 1, Signal 1- 32

LVDS Channel 1, Signal 1+ 33

LVDS Channel 1, Signal 2- 34

LVDS Channel 1, Signal 2+ 35

Symbol Description

CH1_3+

CH1_4-

CH1_4+

GND

CH3_0-

CH3_0+

CH3_1-

CH3_1+

CH3_2-

CH3_2+

GND

CH3_CLK-

CH3_CLK+

GND

CH3_3-

LVDS Channel 1, Signal 3+

LVDS Channel 1, Signal 4-

LVDS Channel 1, Signal 4+

Ground

LVDS Channel 3, Signal 0-

LVDS Channel 3, Signal 0+

LVDS Channel 3, Signal 1-

LVDS Channel 3, Signal 1+

LVDS Channel 3, Signal 2-

LVDS Channel 3, Signal 2+

Ground

LVDS Channel 3, Clock -

LVDS Channel 3, Clock +

Ground

LVDS Channel 3, Signal 3-

16

17

18

19

20

GND

CH1_CLK-

CH1_CLK+

GND

CH1_3-

Ground 36

LVDS Channel 1, Clock - 37

LVDS Channel 1, Clock + 38

Ground 39

LVDS Channel 1, Signal 3- 40

41

CH3_3+

CH3_4-

CH3_4+

GND Ground

NC No Connect

NC No Connect

LVDS Channel 3, Signal 3+

LVDS Channel 3, Signal 4-

LVDS Channel 3, Signal 4+

Note 1: All GND (ground) pins should be connected together and should also be

connected to the LCD’s metal frame.

Note 2: All VDD (power input) pins should be connected together.

Note 3: All Reserved pins should be open without voltage input.

Note 4: All NC pins should be open without voltage input

Note 5: Signal should be sent as following sequence: 1st line: right eye, 2nd line: left eye

(T-con on upper side)

© Copyright AUO Optronics Corp. 2010 All Rights Reserved. Page 10 / 33

Loading...

Loading...