Page 1

DCBA

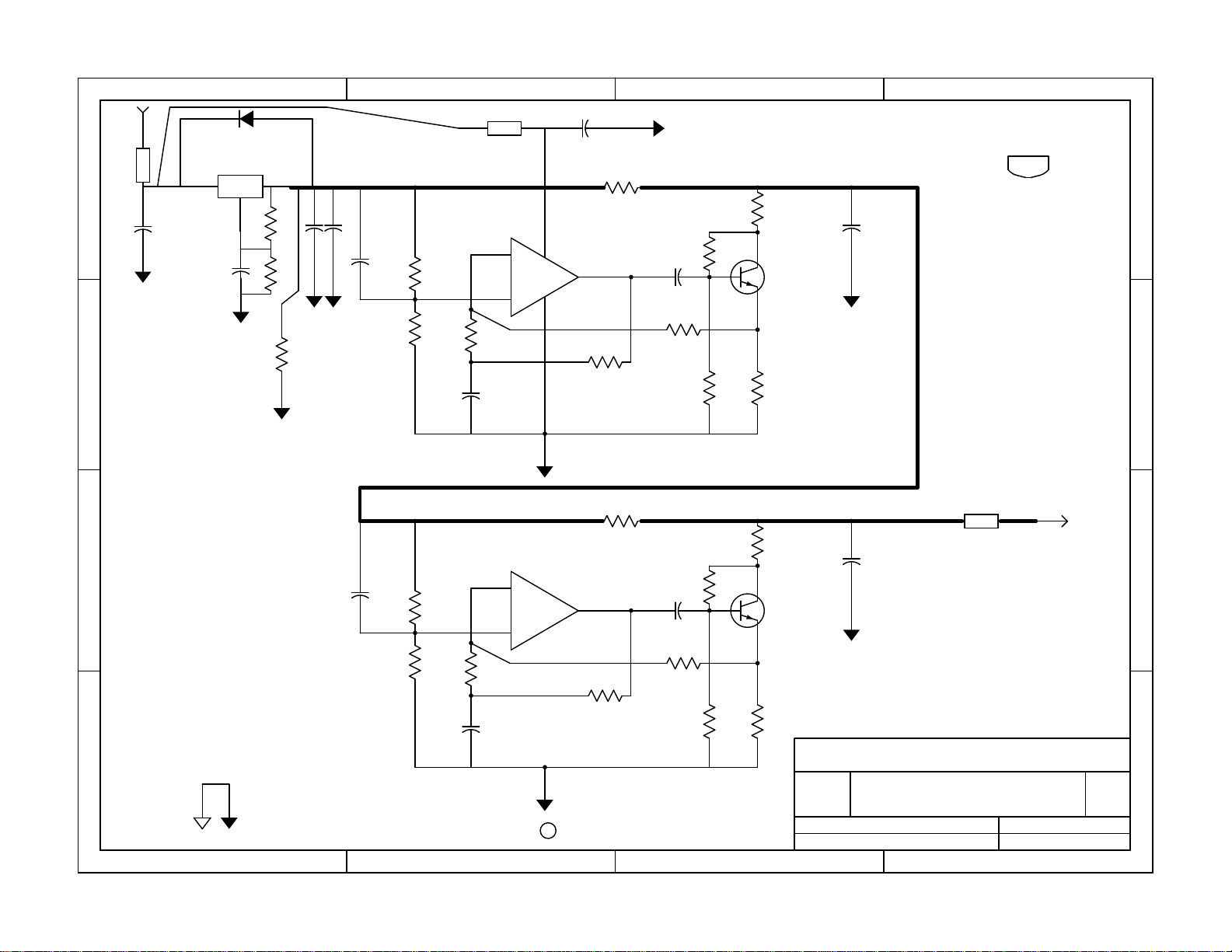

LM2950

TXP

TXN

0.1uF

U4

3

VO

C2

C10

330 uF

17

16

18

TP1

26

25

TP2

21

S7 LED3

S3 U2p15

S3 U2p3 & JP12

Title

Size

A

Date

Filename

1

VI

G

2

C4

out

VDD

R2

300/1watt

S2 R10

S2 R11

R12

S2 X2p5

S2 X2p8

S2 R13

c

Copyright 2003 Audio Crafters Guild

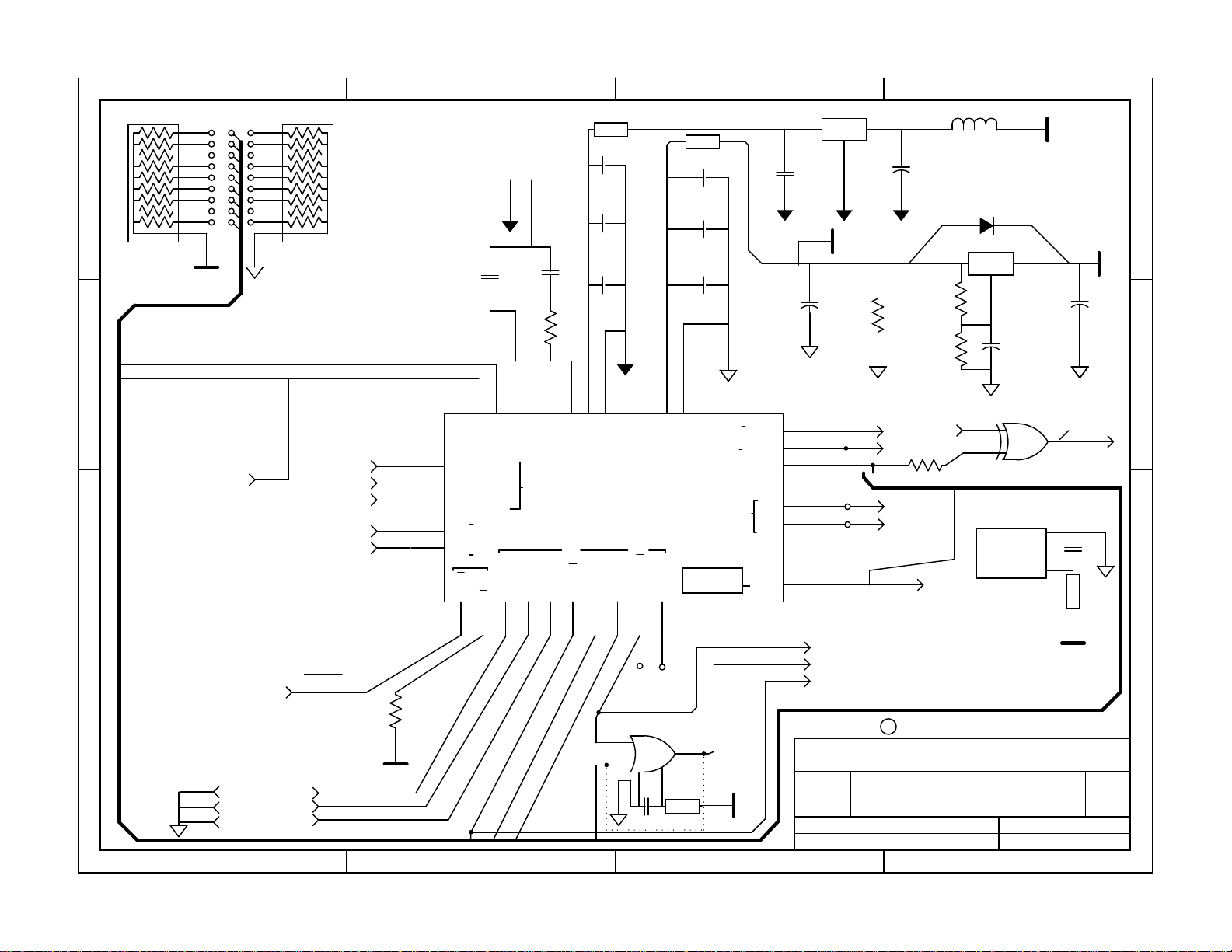

XD0 DIR, AJR Filter, Upsampler

ACG 2001.9.1

9 April 2003

XD0.S01

47k

1

RP1

JP1-JP9

10

9

8

7

6

5

4

3

2

1

VDD

47k

10

9

8

7

6

5

4

3

2

1

RP2

CFILT

CRIP

0.0022 uF

RFILT

2

12

13

14

5

4

ILRCK(TCBLD)

ISCLK(PRO/C)

SDIN(MUTE)

RXN

RXP

S2 R76

S2 R5

S2 R7

Master Clock Out

S2 R8

S2 X1p5

S2 X1p8

3

HWCONFIGBUS/9

Misc.

R

S

T

9

1

0

R

M

C

K

AES3 IN

H

/

S

2

4

1

1

R

E

R

R

Serial In

S

/

D

D

F

F

A

C

C

E

0

1

S

2

2

0

0.047 uF

3k

8

F

I

L

T

U

/

E

M

P

H

2

7

3

C1

10

C5

10

C7

0.1

6

V

A

+

Control

C

O

P

Y

FB1

7

A

G

N

D

CS8420

O

R

I

G

1

GNDANALOG

U1

V

/

A

U

T

D

C

I

B

O

L

2

1

8

9

2

3

V

D

+

1

5

FB8

C3

10

C6

10

C8

0.1

2

2

D

G

N

D

Serial Out

Output Master

Clock Generator

GNDDIGITAL

OLRCK

OSCLK

SDOUT

AES3 Out

OMCK

VIDEO

ERROR

RESET

S7 U20p7

R4

47k

4

VDD

(S3) CONFIG2

(S3) CONFIG0

(S3) CONFIG1

To U1 pin 11

NC7S32

1

U5

2

G

3

TP4

C77

V

5

TP5

4

FB9

VDD

600 ohms

39uF

2

1k

10.5k

polarity

S7

L1

D1

IN4004

U8

VO

A

R1

R3

2

1

NC7S86M5

SOT23

VI

1

39 uF

7486

U3:A

U3:B

Drawn by

3

C11

4

3

5

VEE

C9

3

C70

VDD

1

330 uF

S2 R12

0.1

FB10

RevNumber

2.1

NPT

ofSheet

1

in

VDD

2

3

4

8

A B C D

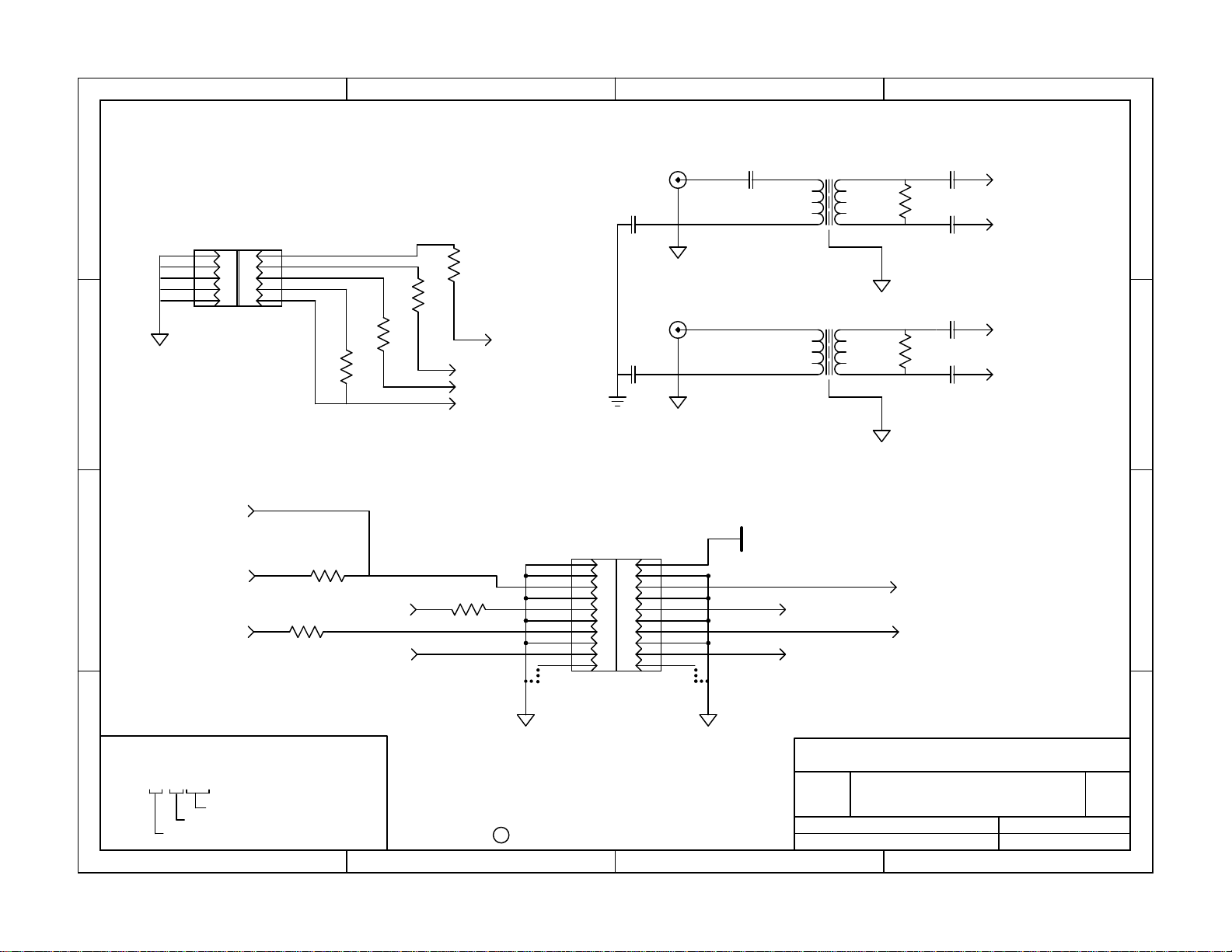

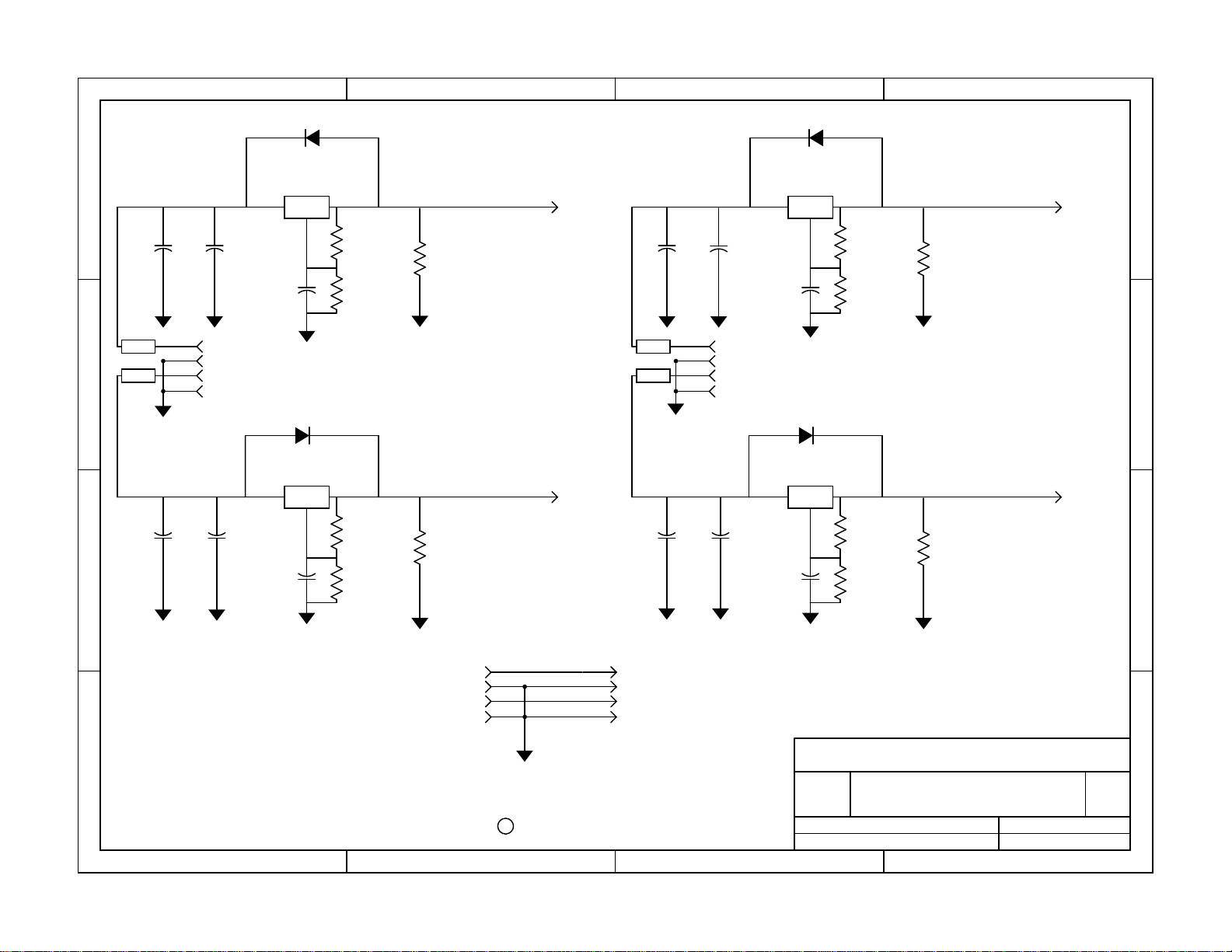

Page 2

DCBA

J1

SPDIF IN

1

1 = Clock Out in Syncro Mode

2-4 I2S Inputs

5-6 Mode Jumper

2

I2SIN:2

10

9

8

7

6

1

2

3

4

5

R8

75

R7

R5

75

R76

75

75

J2

SPDIF OUT

S1 U1p10

Optional RF bypass to chassis

S1 U1p12

S1 U1p13

S1 U1p14

C76

0.1 uF

S1

4

S2

SC937

S1

S2

SC937

R6

R9

C72

C73

C74

75 75

C75

0.01 uF

S1 U1p4

S1 U1p5

S1 U1p26

S1 U1p25

1

2

X1

P1

5

P2

X2

8

2

SH

P1

P2

SH

1

3

Sheet In/Out label scheme

4

S1 U1p14

Sheet number

S7 OSC2p3

S7 OSC1p3

S1 U1p21

S1 U1p16

Pin number if applicaple

Device number or signal name

256 Fs

256 Fs

64 Fs

R11

R13

75

S1 U1p17

S1 U1p18

Fs

Data

R10

Expansion Port

J6

J5

1

2

3

4

5

6

7

8

9

10

For normal operation

install jumpers

3 to 3

5 to 5

7 to 7

9 to 9

Ground jumpers to pins 10 may

be cut if spare I/O pins are needed.

c

Copyright 2003 Audio Crafters Guild

1

2

3

4

5

6

7

8

9

10

VDD

S3 R17

S3 R15

S3 R16

S3 R18

Title

XD0 Digital I/O Connections

Size

A

Date

Filename

9 April 2003

ACG 2001.9.1

XD0.S02

A B C D

Drawn by

3

4

RevNumber

2.1

NPT

2

8

ofSheet

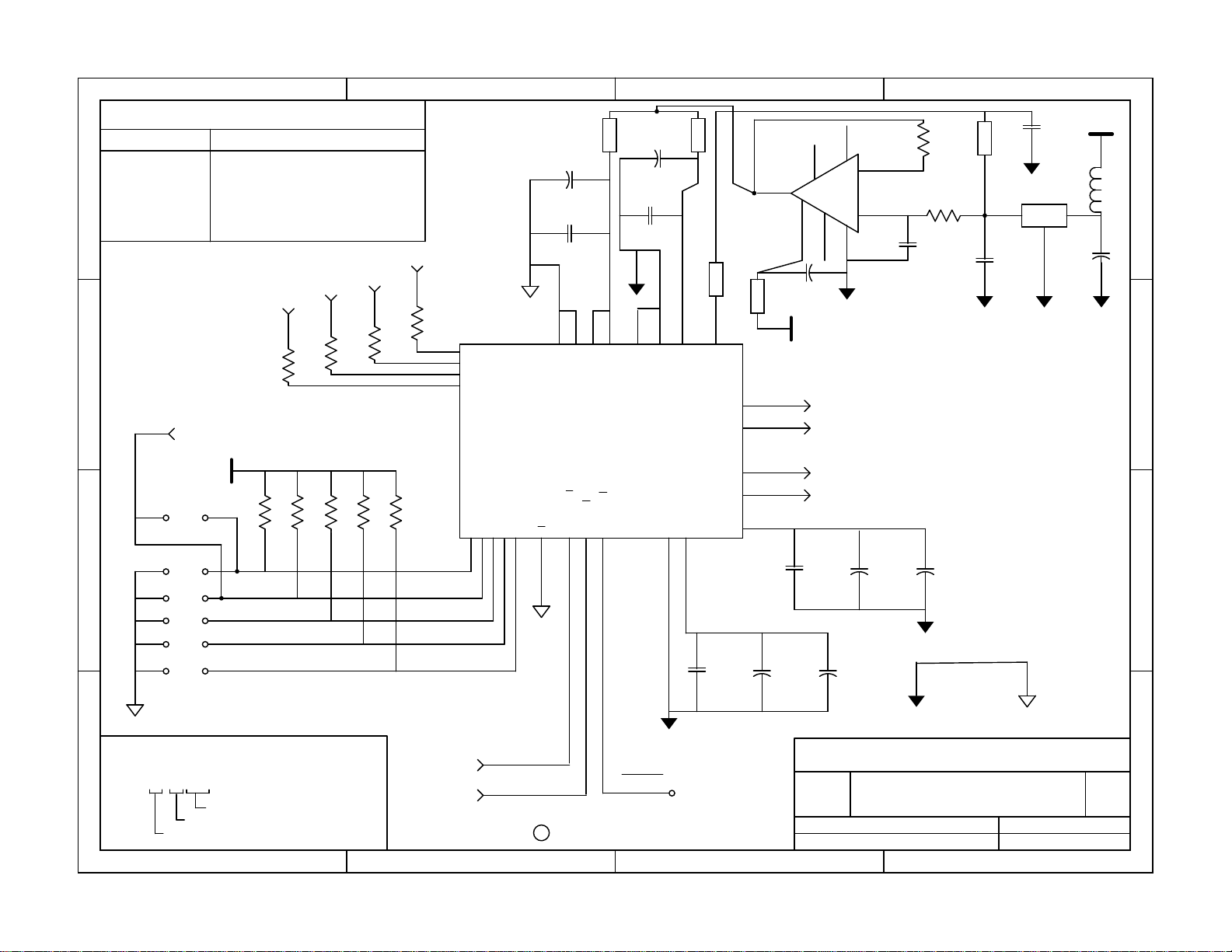

Page 3

DAC Sample Rate Configurations & Emphasis

2

I S modes

44k no emph.

1

44k w/emph.

96k *

192k *

* Emphasis not available for 96k & 192k rates.

M4 M3 M2 M1 M0

0 1 1 0 1

0 0 1 0 1

1 1 1 0 1

1 1 0 0 1

S2 R12

2

R18

S1 U1p3

VDD

10k

JP12

10k

JP13

3

JP14

JP15

JP16

RP5

S2 R13

75

10k

R17

75

10k

S2 R11

R16

10k

75

S2 R10

R15

DCBA

VEE

FB2

C13

FB11

C14

10 uF

10 uF

C15

U6

6

V+

C16

0.1 uF

0.1 uF

FB13

2

1

9

75

12

LRCK

11

SCLK

10

MCLK

13

SDATA

6

D

V

D

G

D

G

N

N

D

D

2

7

8

V

D

8

1

A

A

G

G

N

N

D

D

U2

CS4396

or

2

2

8

V

V

A

R

+

E

F

AOUTLAOUTL+

CS4397 or

CS43122

R

M

E

M

C

M

M

M

4

2

3

2

3

/

M

M

0

H

1

4

5

1

1

6

4

U

S

U

T

E

T

E

T

E

C

1

1

1

5

7

AOUTRAOUTR+

F

F

I

I

L

L

T

T

CMOUT

-

+

2

2

6

7

FB12

24

23

19

20

25

330 uF

C20

VEE

C21

1

NC

8

NC

2

-

AD811

NC

7

S4 FB4 OR S8 FB102

S4 FB6 OR S8 FB103

S4 FB5 OR S8 FB100

S4 FB7 OR S8 FB101

0.1 uF

3

+

V-

5

4

C22

R80

C17

10 uF

C23

1k

R14

100k

1

FB3

3

0.1uF

10 uF

C12

U7

LM2950

VO

C18

1

L2

1

1

VI

G

2

C19

600 ohms

39uF

2

3

JP17

Sheet In/Out label scheme

4

S1 U1p14

Sheet number

Pin number if applicaple

Device number or signal name

S7 U20p7

S1 U5p4

C24

MUTEC

c

Copyright 2003 Audio Crafters Guild

0.1 uF

C25

10 uF

Title

Size

Date

Filename

C26

10 uF

XD0 CS4396/7/122 DAC Stage

A

9 April 2003

ACG 2001.9.1

XD0.S03

A B C D

GNDDIGITALGNDANALOG

Drawn by

4

RevNumber

2.1

NPT

3

8

ofSheet

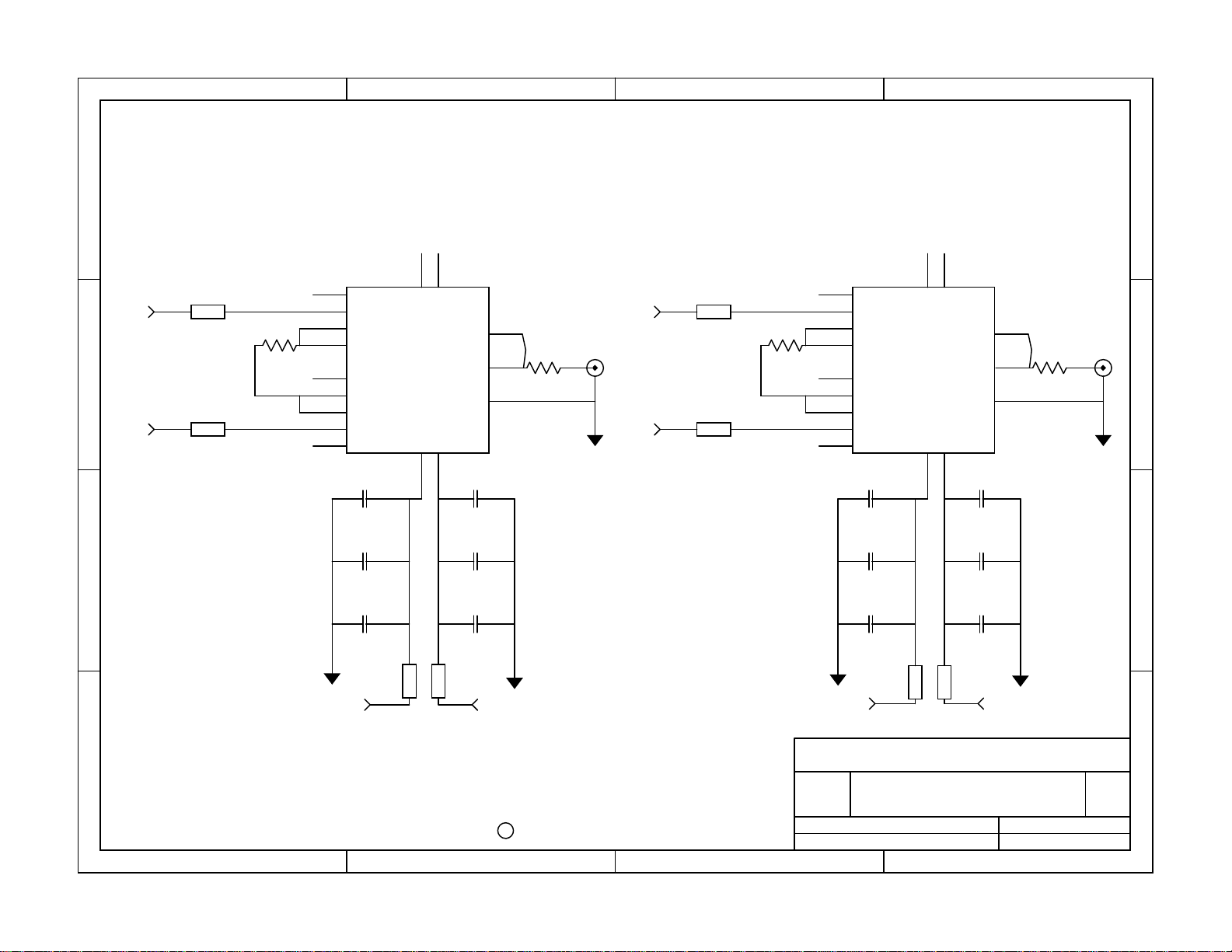

Page 4

DCBA

1

2

3

S3 U2p24

S3 U2p23

Left

4

3

12

G DRIVE

16

INPUT

15

FB4

RG1

open

FB6 FB7

13

14

6

2

1

5

GAIN SENSE

RG

G=100

+RG

+GAIN SENSE

+INPUT

+G DRIVE

C29

0.033uF

C31 C32

+

10 uF BG

N

N

U

U

L

L

L

L

U9

INA103

V

+9V

SENSE

OUPUT

8

REF

C27

11

R24

10

75

7

0.033uF

C33

10 uF BG 10 uF BG

+

C37

+

10 uF BG

+

S3 U2p19

FB5

LEFTOUT_J5

S3 U2p20

RG2

open

12

G DRIVE

16

INPUT

15

GAIN SENSE

13

RG

14

G=100

6

+RG

2

+GAIN SENSE

1

+INPUT

5

+G DRIVE

C30

0.033uF

10 uF BG

C36C35

10 uF BG

+

+

Right

3

N

U

L

L

U10

INA103

V

+

9

4

N

U

L

L

SENSE

OUPUT

V

8

C28

0.033uF

C34

C38

10 uF BG10 uF BG

REF

1

11

R25

10

75

7

++

RIGHTOUT_J6

2

3

FB14

4

FB15

S6U18p3S6U16p2

c

Copyright 2003 Audio Crafters Guild

S6U17p2 S6U19p3

Title

XD0 Analog Stage

FB16

FB17

Size

A

Date

Filename

9 April 2003

ACG 2001.9.1

Drawn by

XD0.S04

4

RevNumber

2.1

NPT

4

8

ofSheet

A B C D

Page 5

DCBA

Vee

FB19

D6

U11

1

FB18

330 uF

C40

3

C79

VI

39 uF

2

VO

A

1

R19

R20

1k

10.5k

C78

C41

330 uF

39 uF

C43

R29

R31

10k

10k

R32

1k

2

-

3

+

R21

2

300/1watt

330 uF

C45

C39

330 uF

8

LM833M

4

0.05

U13:A

1

R33

47k

R26

C44

330 uF

R30

300k

R28

R34

4300

B

470

R27

C

2N4401

E

R35

220

U12

15

330 uF

C42

TO92

C B E

* * *

2N4401

Top View

1

2

3

4

GNDDIGITAL GNDANALOG

A B C D

C47

39 uF

R39

R41

10k

10k

1k

R42

330 uF

6

5

C49

R36

FB20

VAOSC

0.05

220

R37

C46

-

+

U13:B

7

LM833M

C48

330 uF

R38

4300

B

C

2N4401

E

U15

330 uF

3

R40

R43

300k

47k

470

R4415R45

Title

XD0 Clock Twin Shunt Regulator

4

RevNumber

2.1

NPT

ofSheet

c

Copyright 2003 Audio Crafters Guild

Size

A

Date

Filename

9 April 2003

ACG 2001.9.1

Drawn by

XD0.S05 5 8

Page 6

DCBA

D3

U17

3

VI

A

C55

39 uF

J9

Right Power

D5

U19

2

VI

A

C61

39 uF

2

VO

1

1k

R47

S4U10

1

R49

R51R57

10.5k

300/1watt

DK# P10298 $0.58/10

2

3

VO

1

1k

R53

R55

300/1watt

10.5k

S4U10

3

3

C54

D2

U16

VI

A

39 uF

2

VO

1

R46

1k

S4U9

R48

300/1watt

10.5k

+15v Analog

1

330 uF

C50

330 uF

C51

FB22

+VA1

GND

J8

2

FB23

-VA1

GND

Left Power

FB24

FB25

+15v Analog

C52

330 uF

-15v Analog-15v Analog

330 uF

+VA2

GND

-VA2

GND

C53

D4

U18

2

VI

C56

330 uF

3

330 uF

C57

C60

39 uF

3

VO

A

1

R52

1k

R54

R56 R50

10.5k

300/1watt

S4U9

C58

C59

330 uF

330 uF

4

note: Output caps required for regulator stability

shown on analog stage sheet #4.

A B C D

DIR & DAC Regulator Input

Vee

GND

J7

Vdd

GND

Power In From External Supply

c

Copyright 2003 Audio Crafters Guild

S1L1, S2L2, S5U11

S1U4p2

S1U8p3, S7RP4

S1C11, S1R3

Title

XD0 Power Regulators

Size

A

9 April 2003

Date

Filename

ACG 2001.9.1

Drawn by

NPT

ofSheet

RevNumber

2.1

4

86XD0.S06

Page 7

DCBA

2

4

J12

5

6

7

8

4

3

2

1

Reset

VCC

U20

MAX707

PFI

CHARGE

560

RP4

RESET

RESET

G

N

D

3

MR

PFO

VDD

8

7

1

5

RESET

1

2

3

Master Clock

1

OSC1

1

2

INH

GND

OUT

VCC

C62

0.1

C80

10 uF

C63

2

2

1

GND

INH

0.1

VCC

OUT

OSC2

3

3

4

4

3

Master Clock

FB21

Master Clock

J10

GNDDIGITAL

S2 R13 & S3 R17

VAOSC

S2 R13 & S3 R17

VDD

VDD

FSY

FSX

INVERT

MUTE/RESET

SYNCRO

RP3

87654321

S1U3p2

10k

S1U3p2

S1U1p3

S3U2p3

S3U2p15

S1U5p4

S1U1p19

VD+ NC

1M

R58

R59

130k

V battery

J11 mounts LED1-7

LED1

LED2

LED3

FsX

FsY

Invert

LED4

Emphasis

LED5

Error/Reset

LED6

Video

LED7

Syncro/Spare

Sheet In/Out label scheme

4

S1 U1p14

Sheet number

Title

XD0 Clock, Control, & Reset

Size

A

Date

Filename

9 April 2003

ACG 2001.9.1

XD0.S07

Pin number if applicaple

Device number or signal name

Control And Status

c

Copyright 2003 Audio Crafters Guild

A B C D

Drawn by

RevNumber

2.1

NPT

7 8

ofSheet

4

Page 8

DCBA

C101

C102

0.22 uF

B+

1

RIGHTOUT

R108

1M

2

Optional Volume Control & Filter

S3 U2p19

1

S3 U2p20

2

LUACOLD

10k

CFILT100

CFILT101

LUAHOT

0.001 uF

to 0.0001 uF

C

C

W

LATTN100

W

DACT 10k

C

W

10k

Repeat for right channel using

RUACOLD, RUAHOT, CFILT102, CFILT103,

and RATTN101.

S3 U2p19

S3 U2p20

Left

0.22 uF

C100

1M

R100

1M

R101

R102

50k

R103

50k

9

1

R104

50k

7

SHIELD

2

6

V100

Alt. Rk = 375ohms.

8

3

4

heaters

5

R107

R106

200

220 uF

200

Right

S3 U2p24

3

S3 U2p23

4

c

Copyright 2003 Audio Crafters Guild

A B C D

0.22 uF

C103

1M

R110

1M

R111

R112

50k

R113

50k

9

1

R114

50k

7

SHIELD

2

R115

50k

6

V101

3

8

4

heaters

5

R116

200

R117

220 uF

200

C104

C105

0.22 uF

B+

LEFTOUT

R118

1M

R119

50

RELAY101:B

R105

50k

Broskie Follower

Title

XD0 Tubed Analog Stage

Size

A

Date

Filename

10 March 2003

ACG 2001.9.1

XD0.S08

Drawn by

RELAY100:B

R109

50

RevNumber

NPT

8

ofSheet

3

4

1.5

9

Page 9

1

B

C

2

E

3

4

1.5

RevNumber

NPT

ofSheet

8 9XD0.S09

1k

C

DCBA

D100

D101

L2

R120

L2

E

Drawn by

B

U101

1N4004

L1

L1

2N3904

ACG 2001.9.1

RIGHTOUT

10 March 2003

SizeADate

FB107

C113

10 uF

Filename

RESET NC

RESET8RESET

VCC

2

7MR1

U100

MUTEIN

OPTIONAL

5

PFO

GND

MAX707

PFI

4

UNMUTE

3

C114

Right

3

LFO

U104

LIN

4

3 1

2

LMO

LGND

5

13

4 2

WM8816

MUTEB8DATA

CSB

9

6

JP101

LEFTOUT

24

XD0 Tubed Analog Stage II

Relay Control & Vol Control Option

15

CCLK

10

RMO

RGND

12

14

13

RFO

DGN

DVD

AGN

AVD

RIN

1

1

D

7

D

1

6

D

1

D

0.1

0.1

Title

C112

C111

FB106

2 4

1 3

RIGHTIN

DCI/O

1 32

U102

1

5V

3

LFO

U103

2

LMO

WM8816

B+

1M

R121

130k

R122

C107

MUTEB8DATA

CSB

LGND

LIN

39 uF

3

Parts below dashed line optional for volume control.

5

4

9

6

CCLK

10

15

RMO

RGND

12

14

13

RFO

DGN

DVD

AGN

AVD

RIN

1

1

D

D

D

D

0.1

7

1

6

1

0.1

C109

C108

FB105

Copyright 2003 Audio Crafters Guild

c

FB104

VO

2

G

VI

1

C106

Left

39 uF

2

JP100

2 4

1 3

LEFTIN

3

C110

A B C D

10 uF

4

Page 10

B+

3

4

1.5

RevNumber

NPT

9

ofSheet

8

1M

2

RELAY100:B

50

R109

1

RIGHTOUT

R108

DCBA

C101

220 uF

6

50k

R104

Left

0.22 uF

200

R106

7

50k

R102

C100

S3 U2p19

C102

8

0.22 uF

heaters

4

V100

SHIELD

9

1M

R100

5

1

1M

R101

S3 U2p20

3

2

R103

200

R107

Alt. Rk = 375ohms.

50k

B+

R105

50k

C104

220 uF

200

R116

LEFTOUT

C105

0.22 uF

4

8

heaters

5

R118

1M

3

ACG 2001.9.1

Broskie Follower

XD0 Tubed Analog Stage

Title

SizeADate

RELAY101:B

200

R117

Drawn by

XD0.S08

10 March 2003

Filename

50

R119

W

CCW

LATTN100

C

W

DACT 10k

to 0.0001 uF

0.001 uF

10k

LUACOLD

Optional Volume Control & Filter

S3 U2p19

CFILT101

CFILT100

1

10k

LUAHOT

S3 U2p20

6

50k

R114

R112

C103

0.22 uF

and RATTN101.

RUACOLD, RUAHOT, CFILT102, CFILT103,

Repeat for right channel using

Right

S3 U2p24

2

V101

7

SHIELD

9

50k

1M

R110

1

1M

R111

2

R113

50k

R115

50k

A B C D

S3 U2p23

3

4

Copyright 2003 Audio Crafters Guild

c

Page 11

1

RESET

2

3

4

2.1

RevNumber

NPT

ofSheet

7 8

DCBA

5MR1

7

8

8

Emphasis

LED4

S1U1p3

4

S3U2p3

VDD

123

Error/Reset

LED5

S3U2p15

RP4

LED6

S1U5p4

XD0 Clock, Control, & Reset

Title

Video

Syncro/Spare

LED7

S1U1p19

RESET

Reset

VCC

2

VD+ NC

RESET

U20

PFO

GND

MAX707

PFI

4

1M

R58

3

130k

R59

J12

V battery

CHARGE

LED1

J11 mounts LED1-7

FsX

FsY

LED2

560

567

Invert

LED3

S1U3p2

Drawn by

ACG 2001.9.1

XD0.S07

9 April 2003

SizeADate

Filename

10k

87654321

S1U3p2

S2 R13 & S3 R17

Master Clock

3

VCC4OUT

OSC1

Master Clock

GND2INH

1

0.1

C62

1

VAOSC

FB21

C80

10 uF

C63

S2 R13 & S3 R17

4

0.1

OUT3VCC

INH1GND

2

2

Master Clock

OSC2

RP3

VDD

VDD

J10

FSY

FSX

INVERT

3

MUTE/RESET

SYNCRO

GNDDIGITAL

Copyright 2003 Audio Crafters Guild

Control And Status

S1 U1p14

Sheet In/Out label scheme

c

Pin number if applicaple

A B C D

Device number or signal name

Sheet number

4

Page 12

1

2

3

4

2.1

RevNumber

NPT

86XD0.S06

ofSheet

S4U10

DK# P10298 $0.58/10

DCBA

300/1watt

R49

2

U17

VO

VI

3

D3

+15v Analog

1k

R47

1

A

C53

C52

10.5k

R51R57

39 uF

C55

330 uF

Right Power

J9

GND

-VA2

+VA2

GND

330 uF

FB24

FB25

S4U10

D5

U19

-15v Analog-15v Analog

Drawn by

300/1watt

R55

1k

3

10.5k

R53

VO

1

A

VI

2

39 uF

C61

Title

ACG 2001.9.1

XD0 Power Regulators

9 April 2003

SizeADate

Filename

330 uF

C59

330 uF

C58

S1C11, S1R3

S1U4p2

S1U8p3, S7RP4

S1L1, S2L2, S5U11

S4U9

2

U16

VO

VI

3

D2

+15v Analog

1

S4U9

Copyright 2003 Audio Crafters Guild

c

DIR & DAC Regulator Input

GND

GND

Vdd

Vee

300/1watt

R48

1k

10.5k

3

R46

VO

1

A

39 uF

C54

Left Power

J8

D4

U18

1

A

VI

2

C51

GND

GND

+VA1

330 uF

-VA1

C50

330 uF

FB22

FB23

2

1k

R52

300/1watt

R54

10.5k

R56 R50

39 uF

C60

C57

330 uF

C56

330 uF

3

J7

Power In From External Supply

A B C D

shown on analog stage sheet #4.

note: Output caps required for regulator stability

4

Page 13

1

* * *

TO92

C B E

2N4401

DCBA

Top View

2

VAOSC

3

4

2.1

RevNumber

ofSheet

NPT

Drawn by

FB20

ACG 2001.9.1

XD0.S05 5 8

C42

C46

C39

FB19

R26

330 uF

0.05

220

R27

330 uF

C

U13:A

8

-

2

U12

4300

R28

C44

1

2N4401

E

B

330 uF

LM833M

+

3

10k

R29

R30

4

300k

R33

1k

R32

10k

R31

47k

15

R35

470

R34

C45

330 uF

R36

0.05

220

R37

330 uF

U15

C

4300

R38

C48

7

U13:B

-

6

2N4401

E

B

330 uF

LM833M

+

5

10k

R39

R40

300k

R43

1k

R42

10k

R41

47k

XD0 Clock Twin Shunt Regulator

Title

9 April 2003

SizeADate

Filename

15

R45

470

R44

Copyright 2003 Audio Crafters Guild

c

C49

330 uF

Vee

D6

U11

2

VO

A

VI

3

FB18

1

C78

C41

1k

1

R19

C40

39 uF

330 uF

C43

330 uF

10.5k

R20

39 uF

C79

R21

2

300/1watt

39 uF

3

C47

A B C D

GNDDIGITAL GNDANALOG

4

Page 14

1

2

RIGHTOUT_J6

75

R25

10

OUPUT

U10

7

REF

INA103

C28

0.033uF

8

V

9

V

+

NUL

NUL

11

SENSE

L

L

DCBA

4

Right

3

3

++

C34

+

C38

10 uF BG10 uF BG

+

FB17

FB16

4

8

2.1

RevNumber

NPT

ofSheet

4

Drawn by

ACG 2001.9.1

XD0.S04

Left

12

4

3

G DRIVE

INPUT16GAIN SENSE

15RG13

RG2

FB5

S3 U2p19

11

SENSE

NUL

L

NUL

L

+RG

G=10014+GAIN SENSE

6

2

1

open

S3 U2p20

LEFTOUT_J5

75

R24

10

7

REF

OUPUT

U9

INA103

+G DRIVE

+INPUT

5

V

V

+

10 uF BG

+

10 uF BG 10 uF BG

C36C35

C37

10 uF BG

+

S6U17p2 S6U19p3

S6U18p3S6U16p2

FB15

XD0 Analog Stage

Title

9 April 2003

SizeADate

Copyright 2003 Audio Crafters Guild

c

Filename

C30

0.033uF

C27

8

9

C33

0.033uF

FB14

+

+

G DRIVE

16

12

INPUT

15

RG13GAIN SENSE

RG1

G=10014+RG

open

+GAIN SENSE

2

6

+INPUT

1

+G DRIVE

5

C29

C31 C32

0.033uF

10 uF BG

10 uF BG

A B C D

FB4

S3 U2p24

1

2

FB6 FB7

S3 U2p23

3

4

Page 15

1

39uF

600 ohms

L2

VEE

1

C12

DCBA

1

U7

LM2950

3

VI

VO

FB3

C19

2

G

C18

0.1uF

2

3

GNDDIGITALGNDANALOG

4

2.1

RevNumber

8

NPT

ofSheet

3

Drawn by

10 uF

1k

R80

1

R14

1

100k

C17

2

3

-

NC

8

NC

AD811

U6

6

4

+

V-

5

NC

7

V+

330 uF

C20

VEE

FB12

S4 FB6 OR S8 FB103

S4 FB4 OR S8 FB102

23

24

S4 FB7 OR S8 FB101

S4 FB5 OR S8 FB100

19

25

20

C23

10 uF

C22

0.1 uF

C21

10 uF

C26

10 uF

C25

ACG 2001.9.1

XD0.S03

XD0 CS4396/7/122 DAC Stage

Title

9 April 2003

SizeADate

Filename

FB11

C13

FB2

C14

10 uF

C15

10 uF

C16

0.1 uF

0.1 uF

FB13

S2 R10

S2 R11

S2 R13

2

8

2

2

1

8

2

1

8

7

9

6

75

R15

S2 R12

12

75

VRE

VA+

AGN

AGN

V

D

V

D

DGN

DGN

SCLK

LRCK

11

R16

75

MCLK

10

R17

75

R18

F

D

D

D

D

SDATA

13

AOUTL-

U2

AOUTL+

or

CS4396

AOUTR-

AOUTR+

FILT+

FILT-

MUTEC

RESET

CS43122

CS4397 or

10k

10k

10k

RP5

10k

10k

MUT

C/H

CMOUT

E

M

0

M

1

M

2

M

3

M

4

0.1 uF

2

7

2

6

1

7

1

5

1

1

6

5

1

4

4

3

2

C24

MUTEC

S1 U5p4

S7 U20p7

Copyright 2003 Audio Crafters Guild

c

0 1 1 0 1

0 0 1 0 1

1 1 1 0 1

M4 M3 M2 M1 M0

2

44k no emph.

I S modes

DAC Sample Rate Configurations & Emphasis

1 1 0 0 1

96k *

192k *

44k w/emph.

* Emphasis not available for 96k & 192k rates.

1

VDD

Pin number if applicaple

S1 U1p3

JP13

JP14

JP15

JP16

JP12

2

3

JP17

S1 U1p14

Sheet In/Out label scheme

4

A B C D

Device number or signal name

Sheet number

Page 16

1

2

3

4

2.1

RevNumber

NPT

8

ofSheet

2

S1 U1p25

S1 U1p4

DCBA

C72

S1 U1p5

C73

R6

SH

P2

P1

8

5

X1

S1

2

1

4

S2

SC937

C76

0.1 uF

J1

SPDIF IN

S1 U1p26

C74

P1

X2

S1

J2

SPDIF OUT

C75

75 75

0.01 uF

R9

P2

SH

S2

SC937

Optional RF bypass to chassis

VDD

J6

S3 R17

S3 R15

S3 R16

S3 R18

10

987654321

XD0 Digital I/O Connections

Title

Drawn by

ACG 2001.9.1

XD0.S02

9 April 2003

SizeADate

Filename

J5

Expansion Port

123456789

install jumpers

For normal operation

10

3 to 3

7 to 7

5 to 5

be cut if spare I/O pins are needed.

Ground jumpers to pins 10 may

9 to 9

75

R76

75

R5

54321

I2SIN:2

987

6

10

5-6 Mode Jumper

2-4 I2S Inputs

1 = Clock Out in Syncro Mode

1

S1 U1p10

S1 U1p12

75

R7

75

R8

S1 U1p13

S1 U1p14

2

256 Fs

S7 OSC2p3

S7 OSC1p3

R13

256 Fs

S1 U1p21

3

R10

Fs

75

Data

S1 U1p17

R11

64 Fs

S1 U1p16

S1 U1p18

Copyright 2003 Audio Crafters Guild

c

Pin number if applicaple

S1 U1p14

Sheet In/Out label scheme

A B C D

Device number or signal name

Sheet number

4

Page 17

DCBA

L1

LM2950

U4

600 ohms

1

VI

G

VO

3

FB8

FB1

VEE

C1

2

C3

1

39uF

C4

C2

10

D1

IN4004

0.1uF

10

C6

C5

10

in

U8

10

3

VI

VO

2

out

VDD

VDD

A

C8

C7

C9

1

R1

1k

R2

C10

0.1

0.1

0.047 uF

CFILT

CRIP

0.0022 uF

330 uF

C11

R3

300/1watt

330 uF

3k

RFILT

2

39 uF

10.5k

GNDDIGITAL

2

2

2

3

GNDANALOG

7

6

8

1

1

1

0

S2 R12

3

4

7486

2

polarity

S7

S2 R10

17

OLRCK

DGN

VD+

AGN

VA+

FIL

RER

RMC

U3:A

NC7S86M5

1

R12

S2 R11

18

16

SDOUT

OSCLK

Serial Out

D

D

T

R

K

ILRCK(TCBLD)12RXN

13

3

S2 X2p8

S2 X2p5

TP1

25

26

TXP

TXN

AES3 Out

U1

CS8420

Serial In

SDIN(MUTE)

ISCLK(PRO/C)

5

14

3

0.1

C70

5

U3:B

SOT23

TP2

21

Output Master

TCB

V/AUDIO

ORI

COP

Control

U/EMP

DFC

DFC

S/AES

H/S

AES3 IN

RST

Misc.

RXP

4

FB10

S2 R13

OMCK

Clock Generator

L

G

Y

H

1

0

1

1

2

1

3

2

2

2

2

9

VIDEO

5

9

8

7

0

4

VDD

S3 U2p15

S3 U2p3 & JP12

S7 LED3

ERROR

4

2.1

RevNumber

NPT

Drawn by

Copyright 2003 Audio Crafters Guild

c

Title

4

TP5

TP4

U5

NC7S32

1

47k

ACG 2001.9.1

XD0 DIR, AJR Filter, Upsampler

V

G

2

9 April 2003

SizeADate

VDD

FB9

5

C77

3

To U1 pin 11

8

ofSheet

1

XD0.S01

Filename

47k

987654321

10

JP1-JP9

1098765432

47k

S2 R5

S2 R7

S2 R8

Master Clock Out

S2 X1p5

S2 X1p8

R4

RESET

VDD

RP2

S7 U20p7

1

1

RP1

VDD

S2 R76

HWCONFIGBUS/9

2

3

(S3) CONFIG1

(S3) CONFIG0

(S3) CONFIG2

4

A B C D

Page 18

DCI/O

1 32

1N4004

DCBA

D100

D101

1

39 uF

1

C106

U102

VI

G

5V

3

VO

C107

B+

R121

R122

1M

130k

2

39 uF

2

4

C114

VCC

U100

MAX707

PFI

RESET

RESET

G

N

D

8

RESET NC

7

1

MR

PFO

3

MUTEIN

5

OPTIONAL

UNMUTE

L1

L1

2N3904

2

Left

2 4

JP100

LEFTIN

1 3

3

Parts below dashed line optional for volume control.

4

5

6

8

9

10

12

13

FB104

LIN

LGND

CSB

MUTEB

DATA

CCLK

RGND

RIN

0.1

U103

WM8816

A

A

G

V

N

D

D

D

1

1

6

D

D

G

V

N

D

D

D

7

0.1

1

1

LFO

LMO

RMO

RFO

3

2

13

24

15

14

LEFTOUT

2 4

RIGHTIN

1 3

Right

JP101

4

5

6

8

9

10

12

13

FB106

LIN

LGND

CSB

MUTEB

DATA

CCLK

RGND

RIN

0.1

U104

WM8816

A

A

G

V

N

D

D

D

1

1

6

3

LFO

2

LMO

RMO

RFO

D

D

G

V

N

D

D

D

1

7

1

3 1

4 2

RIGHTOUT

15

14

0.1

U101

B

L2

L2

R120

C

E

1k

1

C

B

E

2

3

Relay Control & Vol Control Option

C108

4

10 uF

C110

FB105

c

Copyright 2003 Audio Crafters Guild

C109

10 uF

C113

C111

FB107

C112

Title

XD0 Tubed Analog Stage II

Size

ACG 2001.9.1

Date

A

10 March 2003

Filename

Drawn by

4

RevNumber

1.5

NPT

8 9XD0.S09

ofSheet

A B C D

Loading...

Loading...