ATMEL ATV750L-25SI, ATV750L-25SC, ATV750L-25PI, ATV750L-25PC, ATV750L-25NM-883 Datasheet

...

Features

•

Third Generation Programmable Logic Structure

– High-Density Replacement fo r Discrete Logic

•

High-Speed — Plus a New, Low-Power Version

•

Increased Logic Flexibility

– 42 Inputs and 20 Sum Terms

•

Flexible Output Logic

– 20 Flip-Flops - 10 Extra

– All Can Be Individually Buried or 10 Output Directly

– Each has Individual Asynchronous Reset and Clock Terms

•

Multiple Feedback Paths Provide for Buried State Machines

and I/O Bus Compatibility

•

Proven and Reliable High-Speed CMOS EPROM Process

– 2000V ESD Protection

– 200 mA Latchup Immunity

•

Reprogrammable

– Tested 100% for Programmability

•

24-pin, 300-mil Dual-In-line and 28-Lead Surface Mount Packages

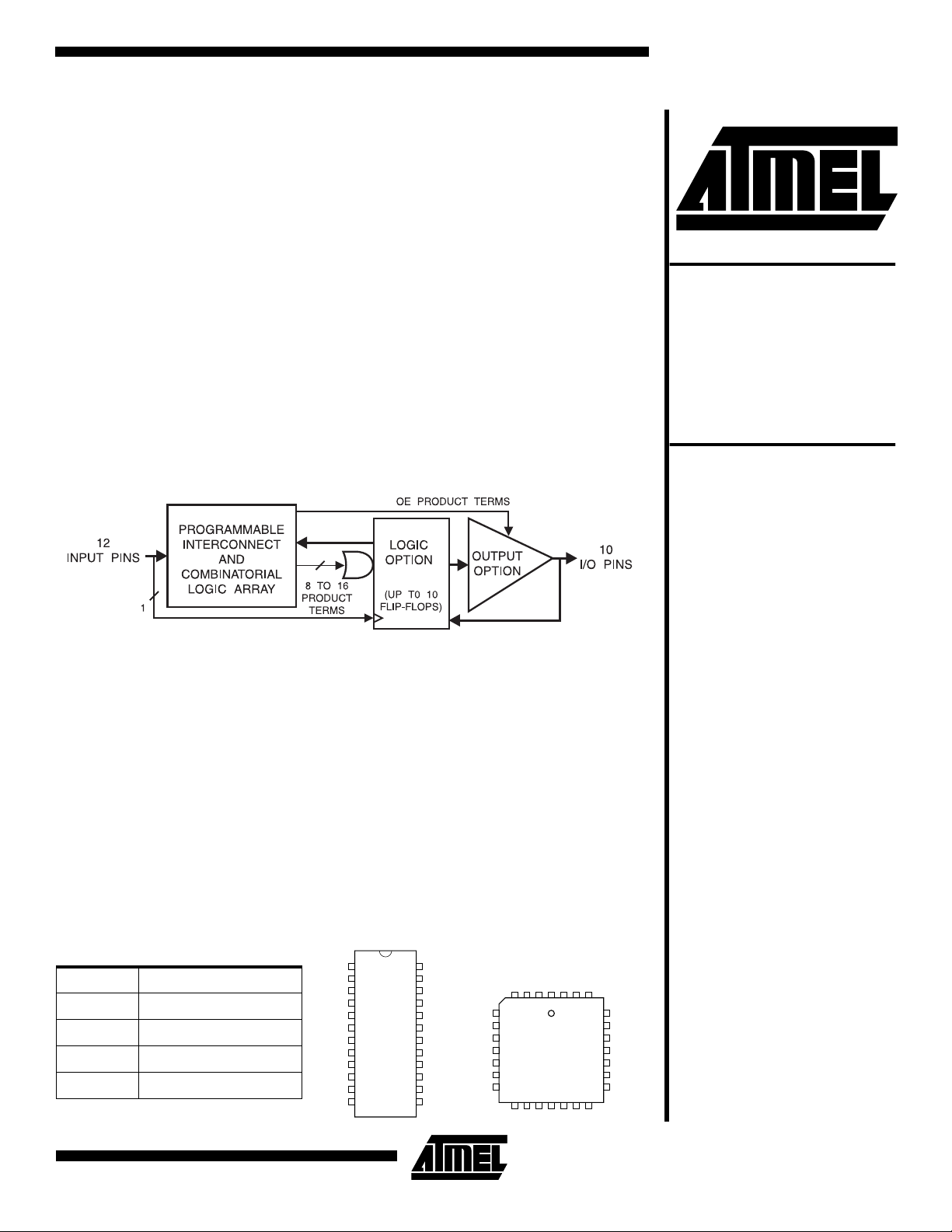

Logic Diagram

High Density UV

Erasable

Programmable

Logic Device

ATV750

ATV750L

Description

The ATV750( L) is 10 0% mor e powe rful tha n mos t other progr ammab le logi c dev ices

in 24-pin packages. Increased product terms, sum terms, and flip-flops translate into

more usable gates.

Each of the AT V750(L) ’s t wenty- two lo gic pins can be us ed as an inpu t. Ten o f th ese

can be used as input, output, o r bi-di rectio nal I/O pins. A ll twen ty flip- flops c an be fe d

back into the array independently. This flexibility allows burying all of the sum terms

and flip-flops.

There are 171 product terms available. A variable format is used to assign between

four and eight produc t terms per sum term. There a re two sum term s per output, providing added flexibility.

(continued)

Pin Configurations

Pin Name Function

IN Logic Inputs

I/O Bidirectional Buffers

* No Internal Connection

VCC +5V Supply

GND

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

DIP/SOIC

1

2

3

4

5

6

7

8

9

10

11

12

24

VCC

23

I/O

22

I/O

21

I/O

20

I/O

19

I/O

18

I/O

17

I/O

16

I/O

15

I/O

14

I/O

13

IN

5

IN

6

IN

7

IN

8

*

9

IN

10

IN

11

IN

PLCC/LCC

(Top View)

INININ*VCC

432

12131415161718

IN

IN

GND

1

*

I/O

282726

IN

I/O

I/O

I/O

25

I/O

24

I/O

23

*

22

I/O

21

I/O

20

I/O

19

I/O

Rev. 0024E–05/98

1

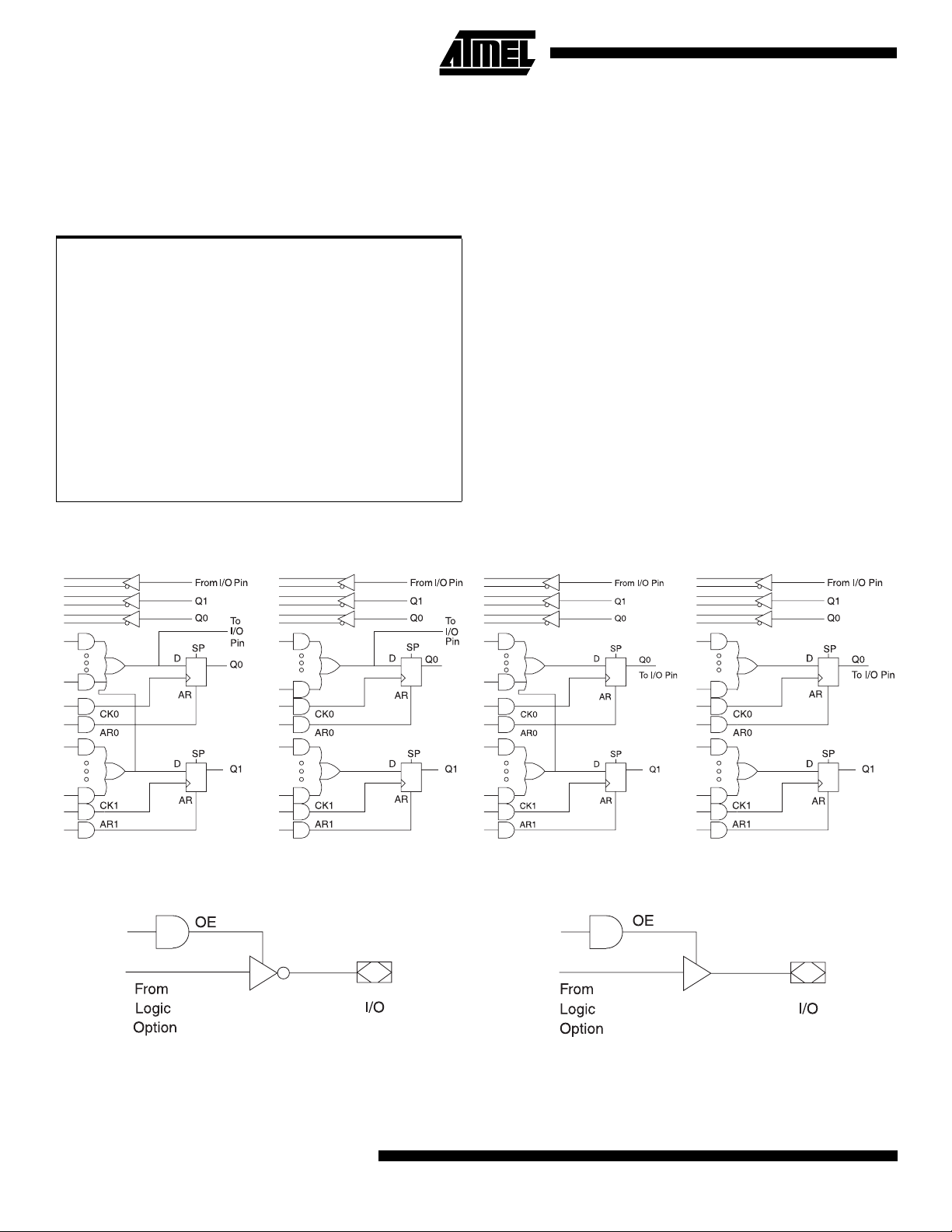

The ATV750(L) has more flip-flops available than other

PLDs in this density range. Complex state machines are

easily implemented.

Product terms are avai lable providing asynchronous

one clock term are pro vided per flip-f lop, with one ena ble

term per output. On e product ter m provides a gl obal synchronous preset. Register preload simplifies testing. The

device has an internal power up clear function.

resets, flip-flop clocks, and output enables. One reset and

Absolute Maximum Ratings

Temperature Under Bias...............................-55°C to + 125°C

Storage Temperature.................................... -65°C to + 150°C

Voltage on Any Pin with

Respect to Ground .........................................-2.0V to +7.0V

Voltage on Input Pins

with Respect to Ground

During Programming.....................................-2.0V to +14.0V

Programming Voltage with

Respect to Ground .......................................-2.0V to +14.0V

Integrated UV Erase Dose..............................7258 W.sec/cm

(1)

(1)

(1)

2

*NOTICE: Stresses beyond those listed under “Absolute

Maximum Ratings” may cause permanent damage to the dev ice . This is a s tress rating only an d

functional oper ation of the devi ce at t hes e o r any

other conditions beyond those indicated in the

operational sections of this specification is not

implied. Exposure to absolute maximum rating

conditions f or e xtended periods ma y af fect de vice

reliability .

Note: 1. Minimum voltage is -0.6V DC, which may under-

shoot to -2.0V for pulses of less than 20 ns. Maximum output pin voltage is Vcc + 0.75V DC,

which may overshoot to 7.0V for pulses of less

than 20 ns.

Logic Options

Combined Terms Separate Terms Combined Terms Separate Terms

Output Options

2

ATV750/L

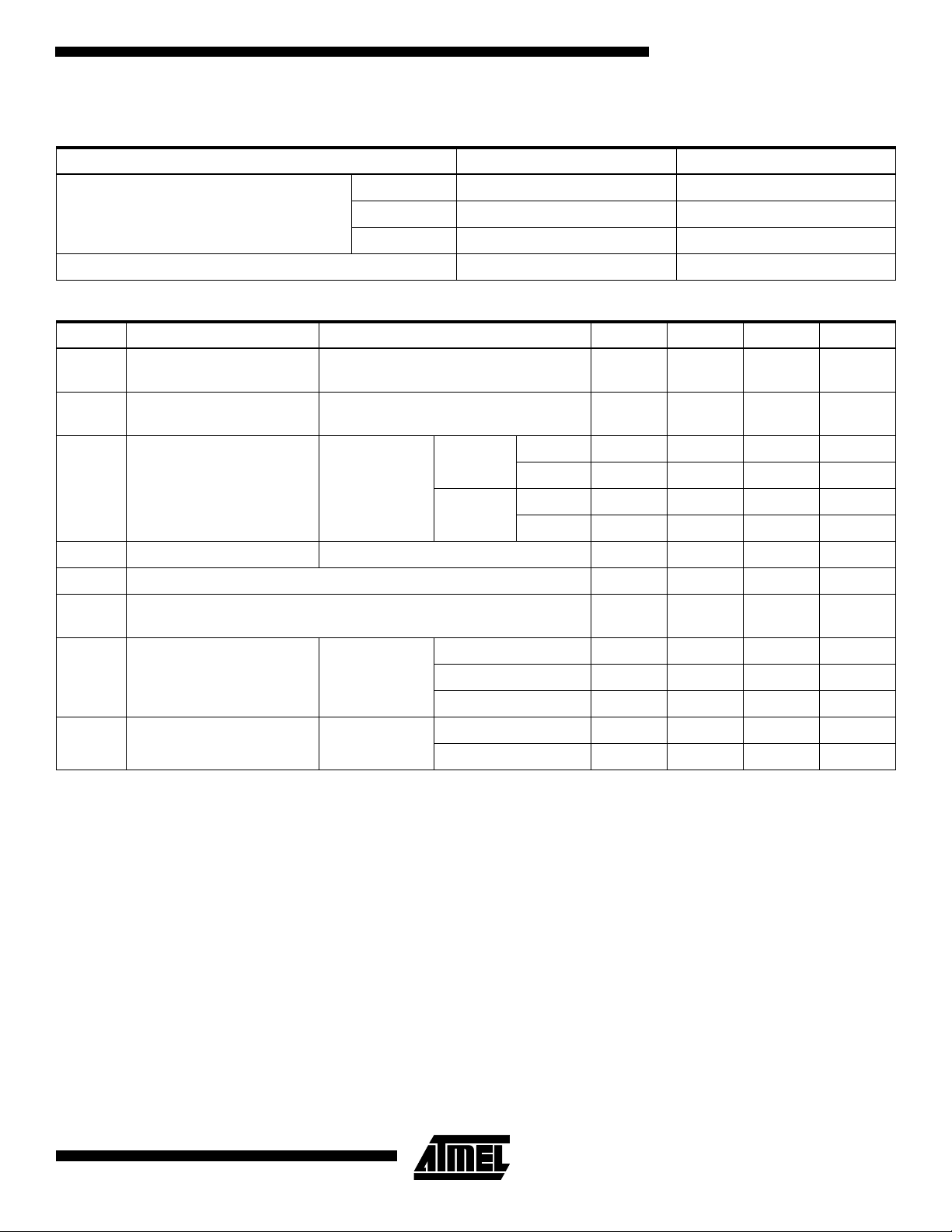

DC and AC Operating Conditions

Com. 0°C - 70°C 0°C - 70°C

ATV750/L

ATV750-20 ATV750/750L-25

Operating Temperature (Case)

Ind. -40°C - 85°C -40°C - 85°C

Mil. -55°C - 125°C -55°C - 125°C

V

Power Supply 5V ± 10% 5V ± 10%

CC

DC Characteristics

Symbol Parameter Condition Min Typ Max Units

I

LI

I

LO

Input Load

Current

Output Leakage

Current

VIN = -0.1V to VCC + 1V

= -0.1V to VCC + 0.1V

V

OUT

Com. 120 mA

= MAX,

V

I

CC

Po wer Supply

Current

CC

= GND ,

V

IN

Outputs Open

ATV750

Ind.,Mil. 140 mA

Com. 1.0 1 2 mA

ATV750L

Ind.,Mil. 1.0 15 mA

(1)

I

OS

V

IL

V

IH

V

OL

V

OH

Output Short Circuit Current V

= 0.5V -120 mA

OUT

Input Low Voltage -0.6 0.8 V

Input High Voltage

Output Low Voltage

Output High Voltage

VIN = VIH or VIL,

V

= MIN

CC

= VIH or VIL,

V

IN

V

= MIN

CC

= 12 mA Com.,Ind. 0.5 V

I

OL

IOL = 8 mA Mil. 0.5 V

I

= 24 mA, Com. 1.0 V

OL

I

= -100 µAV

OH

IOH = -4.0 mA 2.4 V

2.0 V

- 0.3 V

CC

Note: 1. Not more than one output at a time should be shorted. Duration of short circuit test should not exceed 30 sec.

10 µA

10 µA

+

CC

0.75

V

3

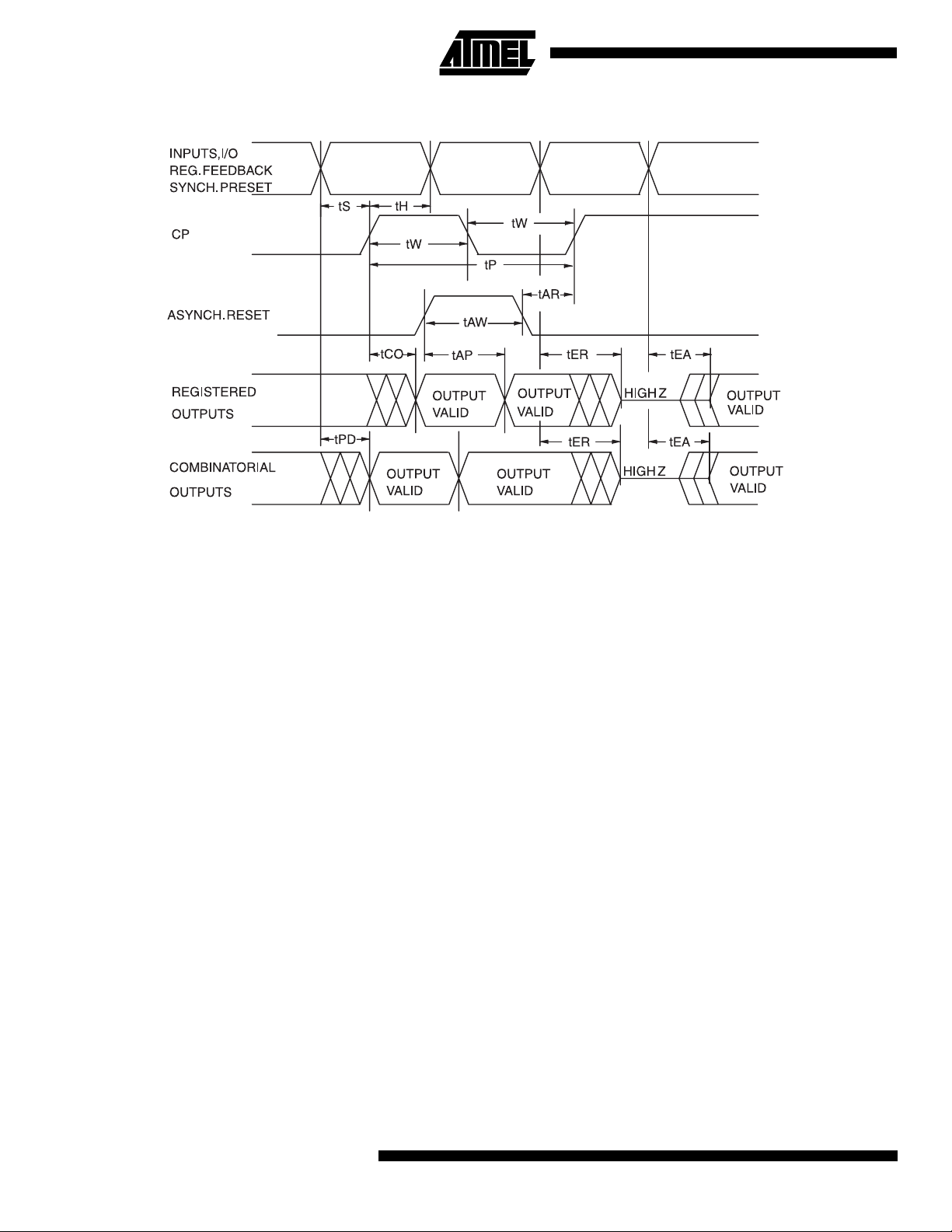

AC Waveforms

Note: 1. Timing measurement reference is 1.5V. Input AC driving levels are 0.0V and 3.0V, unless otherwise specified.

(1)

4

ATV750/L

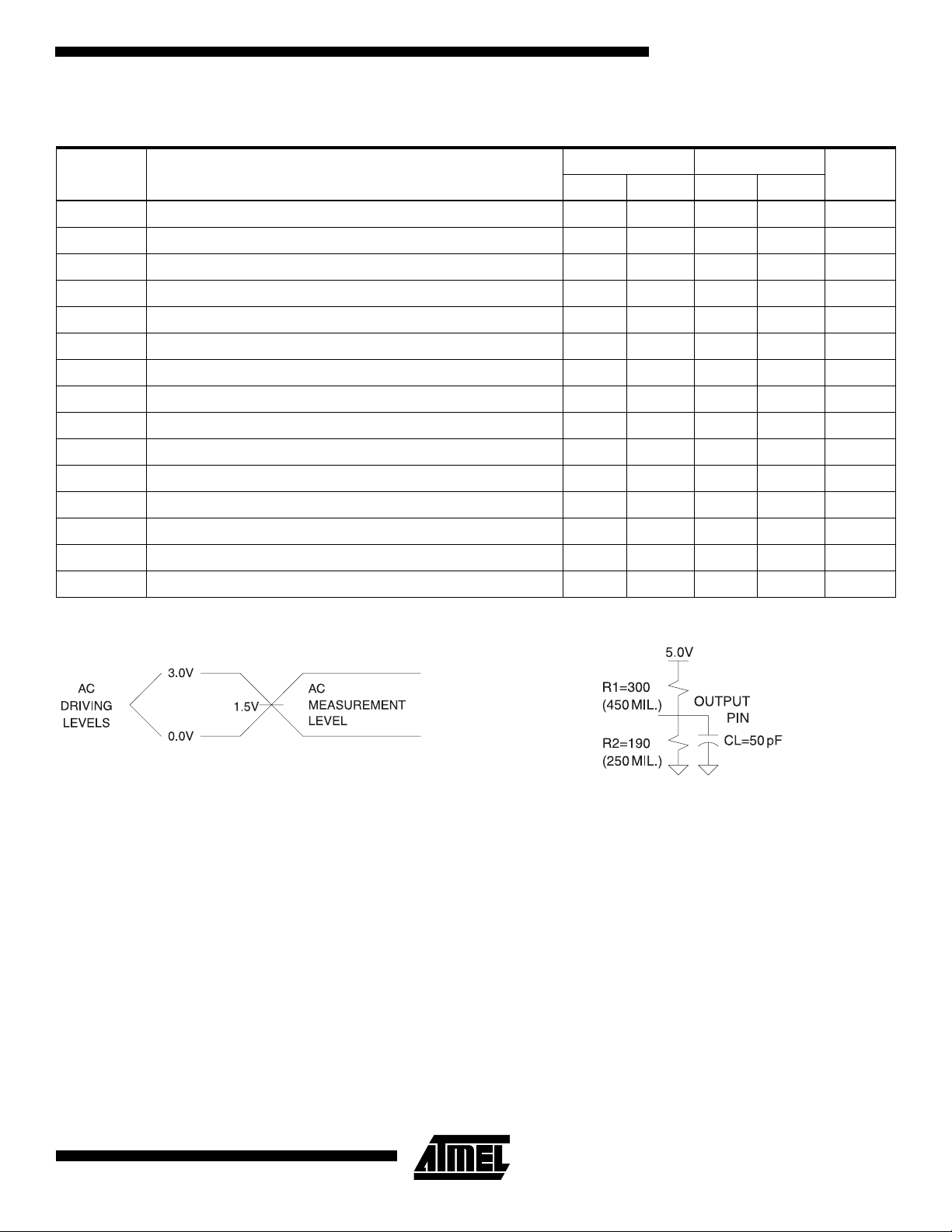

AC Characteristics

Symbol Parameter

t

PD

t

EA

t

ER

t

CO

t

CF

t

S

t

SF

t

H

t

P

t

W

F

MAX

t

AW

t

AR

t

AP

t

SP

Input or Feedback to Non-Registered Output 20 25 ns

Input to Output Enable 20 25 ns

Input to Output Disable 20 25 ns

Clock to Output 20 22 ns

Clock to Feedback 5 10 5 10 ns

Input Setup Time 10 12 ns

Feedback Setup Time 5 7 ns

Hold Time 5 5 ns

Clock Period 18 22 ns

Clock Width 8 10 ns

Maximum Frequency 55 45 MHz

Asynchronous Reset Width 15 20 ns

Asynchronous Reset Recovery Ti me 15 20 ns

Asynchronous Reset to Registered Output Reset 20 25 ns

Setup Time, Synchronous Preset 12 15 ns

ATV750/L

ATV750-20 ATV750/750L-25

UnitsMin Max Min Max

Input Test Waveforms and

Measurement Levels

tR, tF < 5 ns (10% to 90%)

Output Test Loads

5

Loading...

Loading...