ATMEL ATF16V8B User Manual

查询ATF16V8B供应商

Features

•

Industry Standard Architecture

– Emulates Many 20-Pin PALs

– Low Cost Easy-to-Use Software Tools

•

High-Speed Electrically Erasable Programmable Logic Devices

– 7.5 ns Maximum Pin-to-Pin Delay

•

Several Power Saving Options

Device ICC, Stand-By ICC, Active

ATF16V8B 50 mA 55 mA

ATF16V8BQ 35 mA 40 mA

ATF16V8BQL 5 mA 20 mA

®

HighPerf ormance

•

CMOS and TTL Compatible Inputs and Outputs

– Input and I/O Pull-Up Resistors

•

Advanced Flash Technology

– Reprogrammable

– 100% Tested

•

High Reliability CMOS Process

– 20 Year Data Retention

– 100 Erase/Write Cycles

– 2,000V ESD Protection

– 200 mA Latchup Immunity

•

Commercial, and Industrial Temperature Ranges

•

Dual-in-Line and Surface Mount Packages in Standard Pinouts

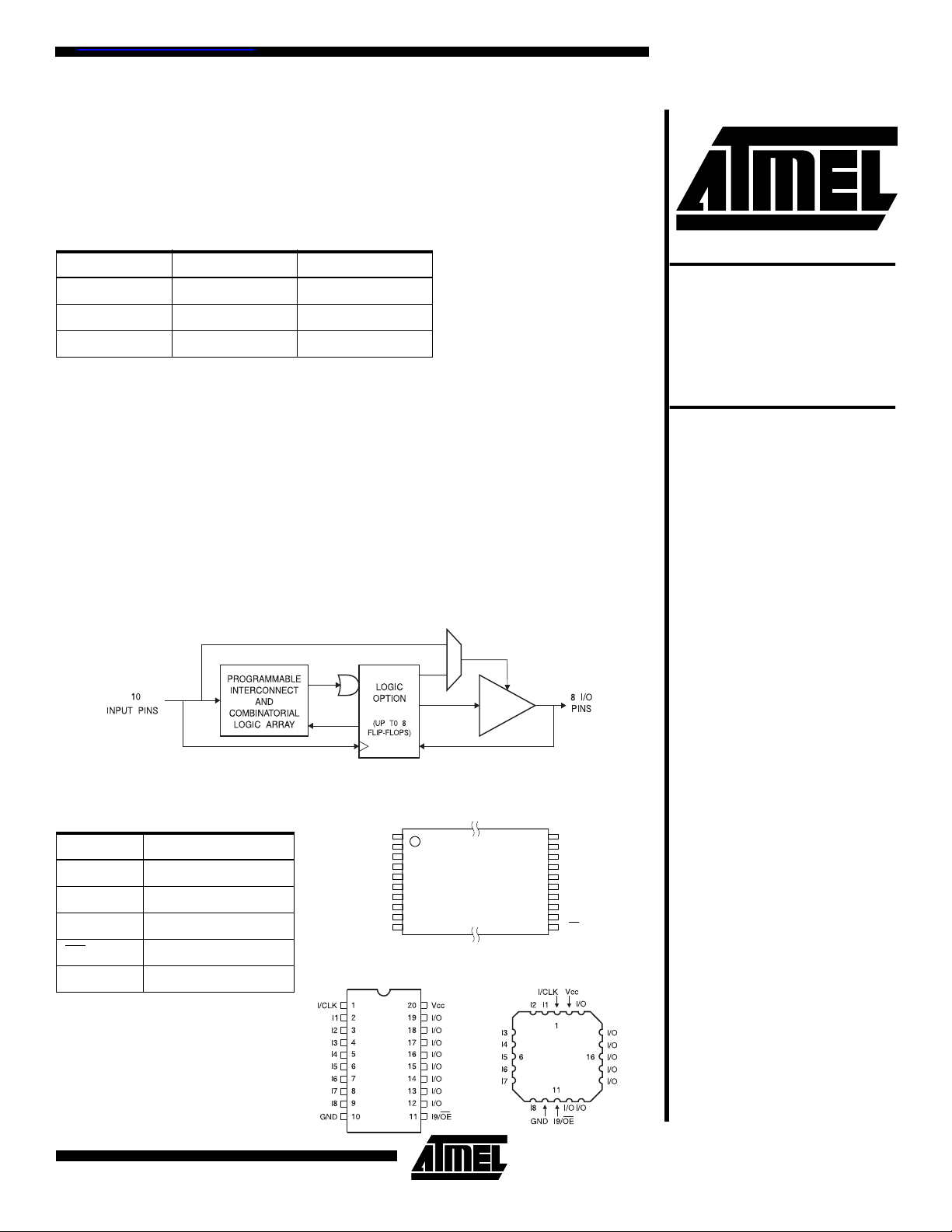

Block Diagram

TSSOP Top View

Pin Configurations

1

I/CLK

2

Pin Name Function

CLK Clock

I Logic Inputs

I/O Bidirectional Buffers

OE

V

CC

Output Enable

+5 V Supply

I1

3

I2

4

I3

5

I4

6

I5

7

I6

8

I7

9

I8

10

GND

DIP/SOIC PLCC Top View

Flash PLD

ATF16V8B

20

VCC

19

I/O

18

I/O

17

I/O

16

I/O

15

I/O

14

I/O

13

I/O

12

I/O

11

I9/OE

Rev. 0364E–07/98

1

Description

The ATF16V8B is a high performance CMOS (Elec trically

Erasable) Programmable Logic Device (PLD) which utilizes

Atmel’s proven electrically erasable Flash memory technology. Speeds down to 7 .5 ns a re o ffered. Al l s peed rang es

are specified over the full 5V ± 10% range for industrial

temperature ranges, and 5V ± 5% for commercial temperature ranges.

Several low power options allow selection of the best solution for various types of power-limited applications. Each of

Absolute Maximum Ratings*

Temperature Under Bias.................................-55oC to +125oC

o

Storage Temperature......................................-65

Voltage on Any Pin with

Respect to Ground .......................................-2.0 V to +7.0 V

Voltage on Input Pins

with Respect to Ground

During Programming...................................-2.0 V to +14.0 V

Programming Voltage with

Respect to Ground .....................................-2.0 V to +14.0 V

C to +150oC

(1)

(1)

(1)

these options significantly reduces total system power and

enhances system reliability.

The ATF16V8Bs incorporate a superset of the generic

architectures, wh ich allows direct repl acemen t of the 16R8

family and most 20-pin combinatorial PLDs. Eight outputs

are each allocated eight pr oduct terms. Three different

modes of operation, configured automatically with software, allow highly complex logic functions to be realized.

*NOTICE: Stresses beyond those listed under “Absolute

Maximum Ratings” may cause permanent damage to the dev ice . This is a s tress rating only an d

functional oper ation of the de vi ce at these or any

other conditions beyond those indicated in the

operational sections of this specification is not

implied. Exposure to absolute maximum rating

conditions f or e xtended periods ma y af fect de vice

reliability .

Note: 1. Minimum voltage is -0.6V DC, which may under-

shoot to -2.0V for pulses of less than 20 ns. Maximum output pin voltage is V

which may overshoot to 7.0V for pulses of less

than 20 ns.

+ 0.75V DC,

CC

DC and AC Operating Conditions

Commercial Industrial

Operating Temperature (Case) 0

V

Power Supply 5V ± 5% 5V ± 10%

CC

2

ATF16V8B

o

C - 70oC-40

o

C - 85oC

ATF16V8B

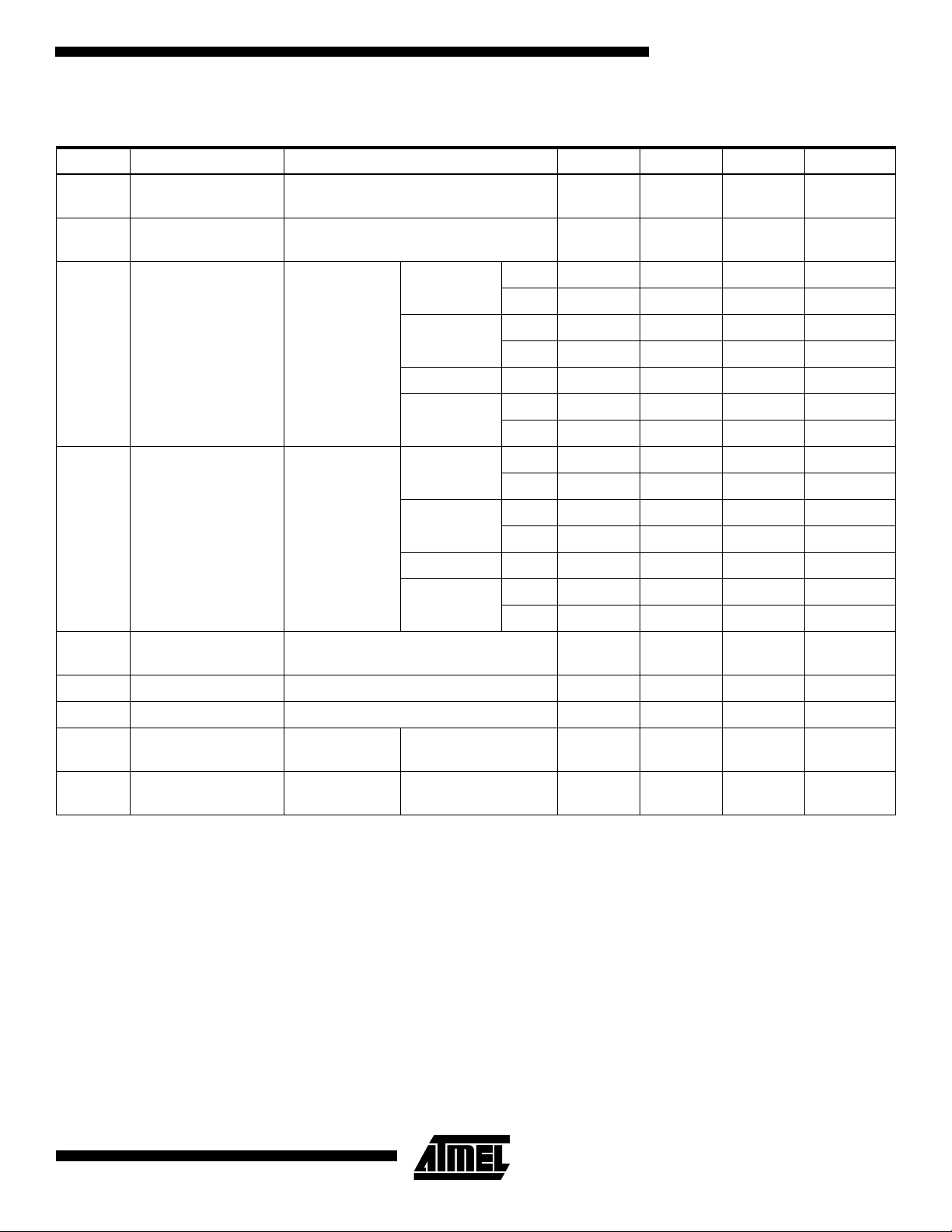

DC Characteristics

Symbol Parameter Condition Min Typ Max Units

I

IL

Input or I/O Low

Leakage Current

≤ VIL(MAX) -35 -100 µA

0 ≤ V

IN

I

I

I

I

IH

CC

CC2

OS

Input or I/O High

Leakage Current

3.5 ≤ VIN ≤ V

CC

10 µA

Com. 55 85 mA

B-7, -10

Ind. 55 95 mA

Com. 50 75 mA

Ind. 50 80 mA

Power Supply

Current, Standby

= MAX,

V

CC

= MAX,

V

IN

Outputs Open

B-15, -25

BQ-10 Com. 35 55 mA

Com. 5 10 mA

BQL-15, -25

Ind. 5 15 mA

Com. 60 90 mA

B-7, -10

Ind. 60 100 mA

Com. 55 85 mA

Ind. 55 95 mA

Clocked Power

Supply Current

V

= MAX,

CC

Outputs Open,

f=15 MHz

B-15, -25

BQ-10 Com. 40 55 mA

Com. 20 35 mA

BQL-15, -25

Ind. 20 40 mA

(1)

Output Short

Circuit Current

= 0.5 V -130 mA

V

OUT

V

IL

V

IH

V

OL

V

OH

Input Low Voltage -0.5 0.8 V

Input High Voltage 2.0 VCC+0.75 V

Output High Voltage

Output High Voltage

V

IN=VIH

V

CC

V

IN=VIH

V

CC

or VIL,

=MIN

or VIL,

=MIN

I

= -24 mA

OL

Com., Ind.

= -4.0 mA 2.4 V

I

OH

0.5 V

Note: 1. Not more than one output at a time should be shorted. Duration of short circuit test should not exceed 30 sec.

3

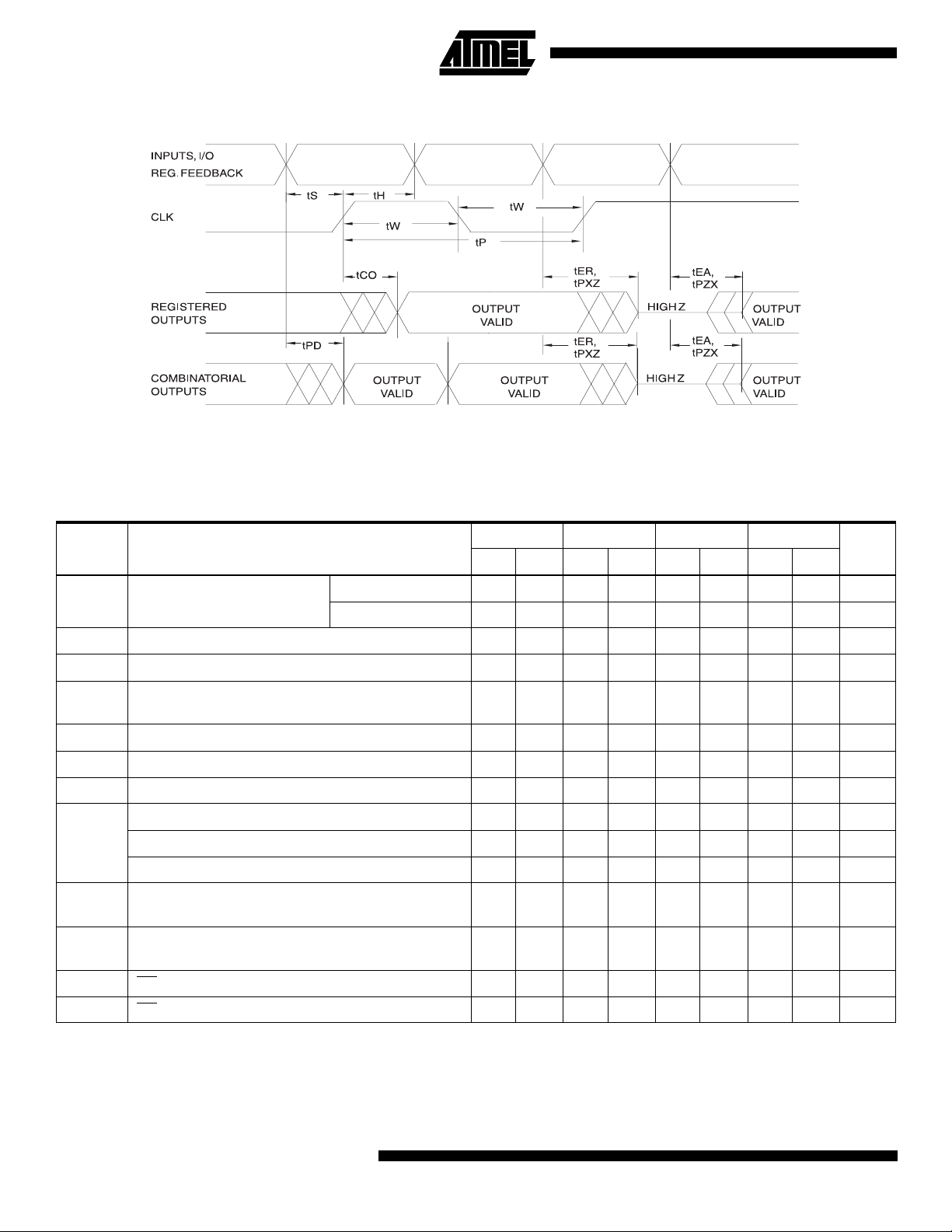

AC Waveforms

(1)

Note: 1. Timing measurement reference is 1.5V. Input AC driving levels are 0.0V 3.0V, unless otherwise specified.

AC Characteristics

Symbol Parameter

t

PD

t

CF

t

CO

t

S

t

H

t

P

t

W

F

MAX

t

EA

t

ER

Input or Feedback to

Non-Registered Output

Clock to Feedback 3 6 8 10 ns

Clock to Output 2527210212ns

Input or Feedback

Setup Time

Hold Time 0000ns

Clock Period 8 121624 ns

Clock Width 4 6 8 12 ns

External Feedback 1/(tS+tCO) 100 68 45 37 MHz

Internal Feedback 1/(t

No Feedback 1/(t

Input to Output Enable —

Product Term

Input to Output Disable —

Product Term

(1)

(2)

-7

8 outputs switching 3 7.5 3 10 3 15 3 25 ns

1 output switching 7 ns

5 7.5 12 15 ns

+ tCF) 125 74 50 40 MHz

S

) 125 83 62 41 MHz

P

3 9 3 10 3 15 3 20 ns

2 9 2 10 2 15 2 20 ns

-10 -15 -25

UnitsMin Max Min Max Min Max Min Max

t

t

PZX

PXZ

OE pin to Output Enable 2 6 2 10 2 15 2 20 ns

OE pin to Output Disable 1.5 6 1.5 10 1.5 15 1.5 20 ns

Notes: 1. See ordering information for valid part numbers and speed grades.

2. Recommend ATF16V8C -7.

4

ATF16V8B

ATF16V8B

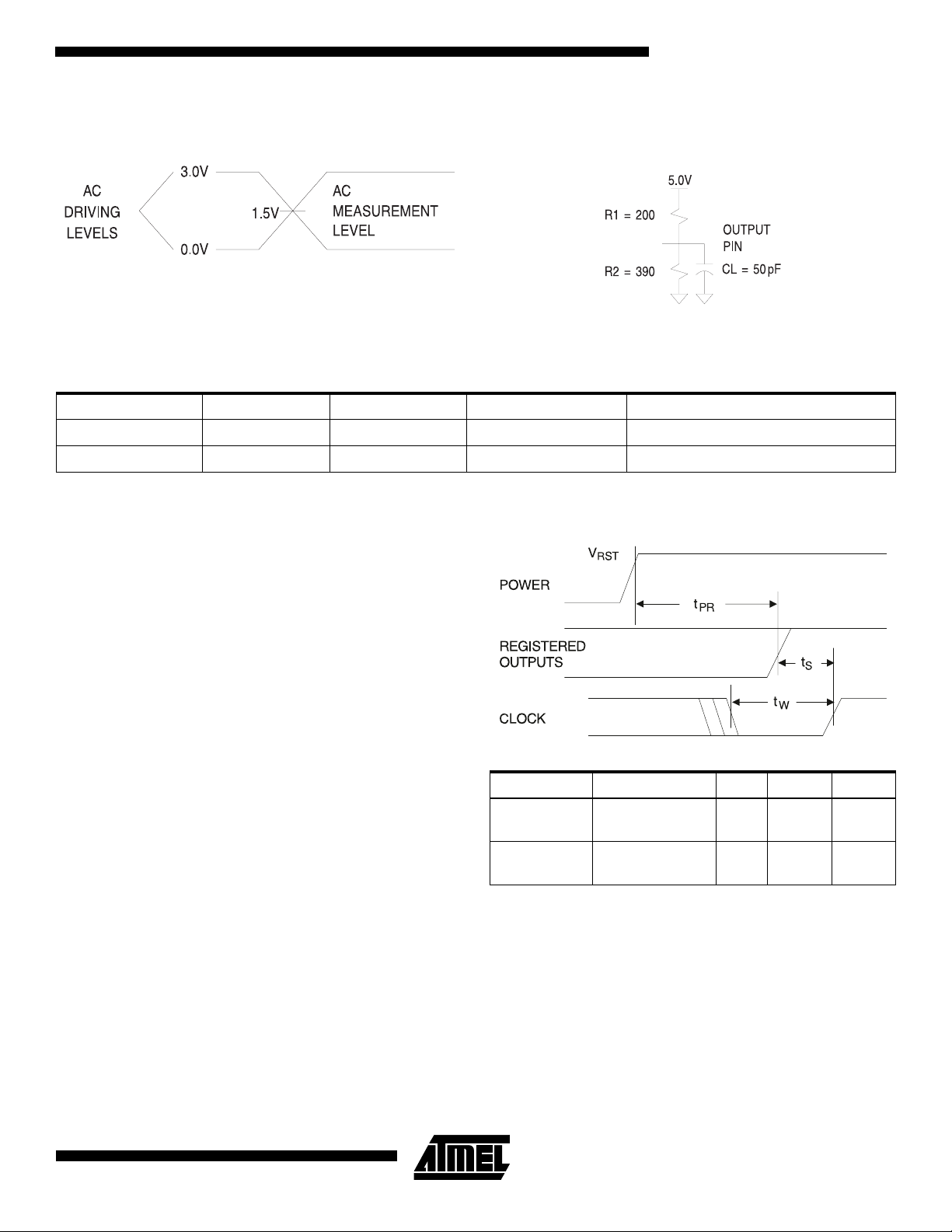

Input Test Waveforms and

Measurement Levels:

Output Test Loads:

Commercial

tR, tF < 5 ns (10% to 90%)

Pin Capacitance

f = 1 MHz, T = 25°C

C

IN

C

OUT

Note: 1. Typical values for nominal supply voltage. This parameter is only sampled and is not 100% tested.

(1)

T yp Max Units Conditions

58 pFV

68 pFV

= 0 V

IN

OUT

= 0 V

Power Up Reset

The registers in the ATF16V8 Bs are design ed to reset dur ing power up. At a point delayed slightly from V

, all registers will be re set to th e low st ate. As a r esult,

V

RST

the registered output state will always be high on power-up.

This feature is critical for state machine initialization. How-

ever, due to the asynchronous nature of reset and the

uncertainty of h ow V

actually rises in the sys tem, the fo l-

CC

lowing conditions are required:

1) The V

rise must be monotonic,

CC

2) After reset occurs, all input and feedback setup times

must be met before driving the clock pin high, and

3) The clock must remain stable during t

PR

.

Preload of Registered Outputs

The ATF16V8B’s registers are provided with circuitry to

allow loading of each register with either a high or a low.

This feature will simplify testing since an y state can be

forced into the registers to control test seq uencing. A

JEDEC file with preload is generated whe n a source fil e

with vectors is compiled. Once downloaded, the JEDEC file

preload sequence will be done automatically by most of the

approved programmers after the programming.

crossing

CC

Parameter Description Typ Max Units

t

PR

V

RST

Power-Up

Reset Time

Power-Up

Reset Voltage

Security Fuse Usage

A single fuse is provided to prevent unauthoriz ed copying

of the ATF16V8B fuse patterns. Once programmed, fuse

verify and preload are inhibited. However, the 64-bit User

Signature remains accessible.

The security fuse should be programmed last, as its effect

is immediate.

600 1,000 ns

3.8 4.5 V

5

Electronic Signature Word

There are 64 bits of programmable memory that are always

available to the user, even if the device is secured. These

bits can be used for user-specific data.

Programming/Erasing

Programming/erasing is performed using standard PLD

programmers. See

and Software Suppor

ming.

CMOS PLD Programming Hardware

t for information on software/program-

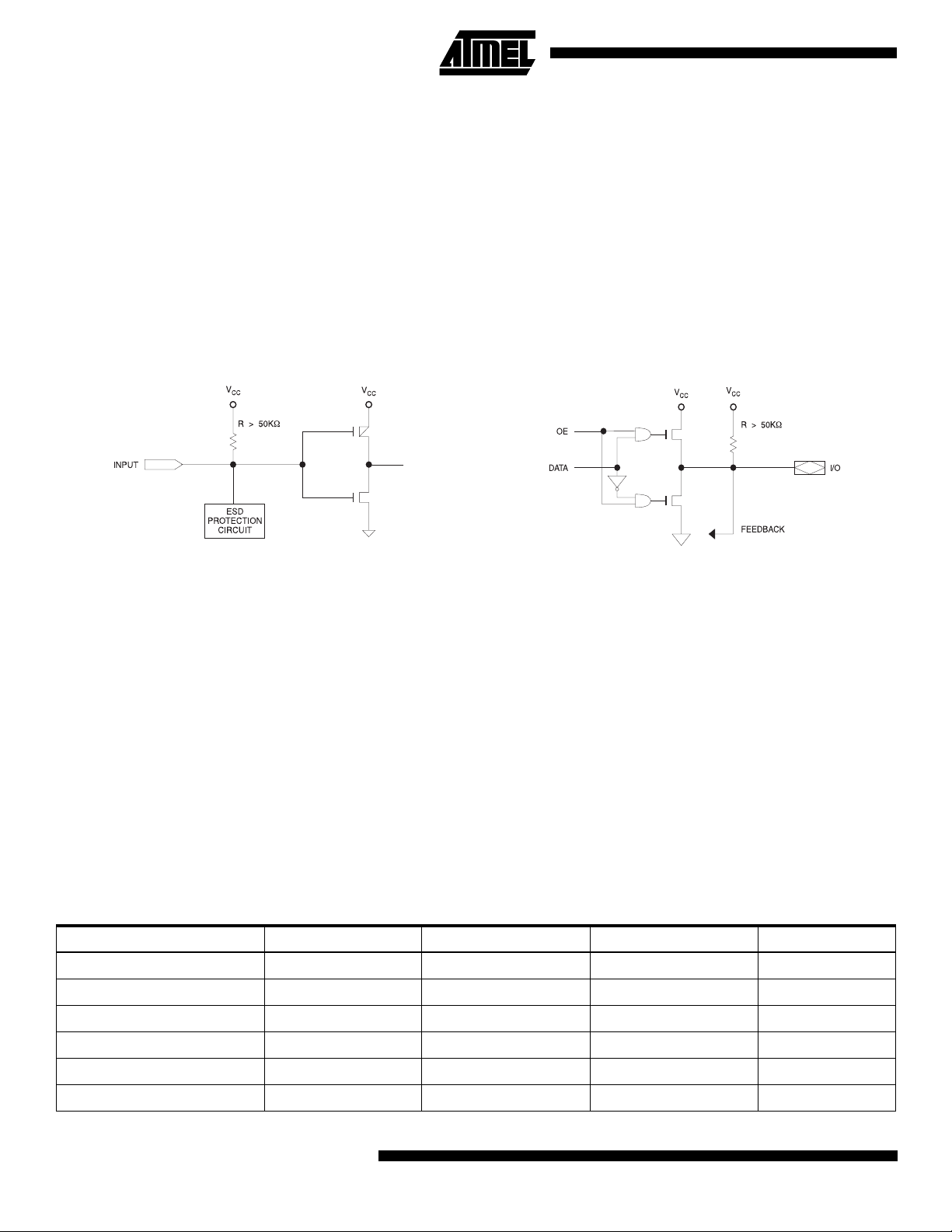

Input and I/O Pull-Ups

All ATF16V8B family members have internal input and I/O

pull-up resistors. Therefore, whenever inputs or I/Os are

not being driven externally, they will float to V

ensures that all lo gic array inputs are at kn own states.

These are relatively weak active pull-ups that can easily be

overdriven by TTL-compatible dr ivers (see input and I/O

diagrams below).

Input Diagram I/O Diagram

CC

. This

Functional Logic Diagram Description

The Logic Option and Fu nctional Diagrams des cribe the

ATF16V8B architec ture. Eig ht confi gurable ma crocell s can

be configured as a registered output, combinatorial I/O,

combinatorial output, or dedicated input.

The ATF16V8B can b e conf igured in one o f three di fferen t

modes. Each mode makes the ATF16V8B look like a different device. Most PLD compilers can choose the right

mode automatically. The user can also force the selection

by supplying the compiler with a mode selection. The determining factors would be the usage of register versus combinatorial ou tputs and ded icated output s versus outpu ts

with output enable control.

The ATF16V8B universal architect ure can be pro grammed

to emulate many 20-pin PAL devi ces. The se architectu ral

Compiler Mode Selection

Registered Complex Simple Auto Select

ABEL, Atmel-ABEL

CUPL

LOG/iC

OrCAD-PLD

PLDesigner

Tango-PLD

Note: 1. Only applicable for version 3.4 or lower.

P16V8R P16V8C P16V8AS P16V8

G16V8MS G16V8MA G16V8AS G16V8

GAL16V8_R

“Registered” “Com plex” “Simple” GAL16V8A

P16V8R P16V8C P16V8C P16V8A

G16V8R G16V8C G16V8AS G16V8

(1)

GAL16V8_C7

subsets can be found in ea ch of the con figurat ion modes

described in the foll owing pages . The user can downl oad

the listed sub set device JEDEC progr amming fi le to the

PLD programmer, and the ATF16 V8B c an be c onfi gu red to

act like the chosen device. Check with your programmer

manufacturer for this capability.

Unused product terms a re automatic ally disabled by the

compiler to decrease power consumption. A Security Fuse,

when programmed, protects the c ontent of the ATF16V8B .

Eight bytes (64 fuses) of User Signature are accessible to

the user for purposes such as storing project name, part

number, revision, or date. The User Signature is accessible

regardless of the state of the Security Fuse.

(1)

GAL16V8_C8

(1)

GAL16V8

6

ATF16V8B

Loading...

Loading...