ATMEL ATF1504AS-15JI84, ATF1504AS-15JI68, ATF1504AS-15JI44, ATF1504AS-15JC84, ATF1504AS-15JC68 Datasheet

...

1

Features

•

High Density, High Performance Electrically Erasable Complex Programmable Logic

Device

– 64 Macrocells

– 5 Product Terms per Macrocell, Expandable up to 40 per Macrocell

– 44, 68, 84, 100 pins

– 7 ns Maximum Pin-to-Pin Delay

– Registered Operation Up To 100 MHz

– Enhanced Routing Resources

•

In-System Programmabi lity (ISP) via JTAG

•

Flexible Logic Macrocell

– D/T/Latch Configurable Flip Flops

– Global and Individual Register Control Signals

– Global and Individual Output Enable

– Programmable Output Slew Rate

– Programmable Output Open Collector Option

– Maximum Logic utilization by burying a register within a COM output

•

Advanced Power Management Features

– Automatic 100

µµµµ

A Stand-By for “Z” Version

– Pin-Controlled 4 mA Stand-By Mode (Typical)

– Programmable Pin-Keeper Inputs and I/Os

– Reduced-Power Feature Per Macrocell

•

Available in Commercial and Industrial Temperature Ranges

•

Available in 44-, 68-, and 84-pin PLCC; 44- and 100-pin TQFP; and 100-pin PQFP

•

Advanced EE Technology

– 100% Tested

– Completely Reprogrammable

– 100 Program/Erase Cyc le s

– 20 Year Data Retention

– 2000V ESD Protection

– 200 mA Latch-Up Immunity

•

JTAG Boundary-Scan Testing to IEEE Std. 1149.1-1990 and 1149.1a-1993 Supported

•

PCI-compliant

•

3.3 or 5.0V I/O pins

•

Security Fuse Feature

Enhanced Features

•

Improved Connectivity (Additional Feedback Routing, Alternate Input Routing)

•

Output Enable Product Terms

•

D - Latch Mode

•

Combinatorial Output with Registered Feedback within any Macrocell

•

Three Global Clock Pins

•

ITD (Input Transition Detection) Circuits on Global Clocks, Inputs and I/O

•

Fast Registered Input from Product Term

•

Programmable “Pin-Keeper” Option

•

VCC Power-Up Reset Option

•

Pull-Up Option on JTAG Pins TMS and TDI

•

Advanced Power Management Features

– Edge Controlled Power Down “L”

– Individual Macrocell Power Option

– Disable ITD on Global Clocks, Inputs and I/O

Description

The ATF1504AS is a high performance, high density Complex Programmable Logic

Device (CPLD) which utilizes Atmel’s proven electrically erasable memory technology.

With 64 logic ma crocel ls and up to 68 inputs, i t easily integrat es logic fr om sever al

HighPerformance

EE CPLD

ATF1504AS

ATF1504ASZ

Rev. 0950D–07/98

(continued)

ATF1504AS(Z)

2

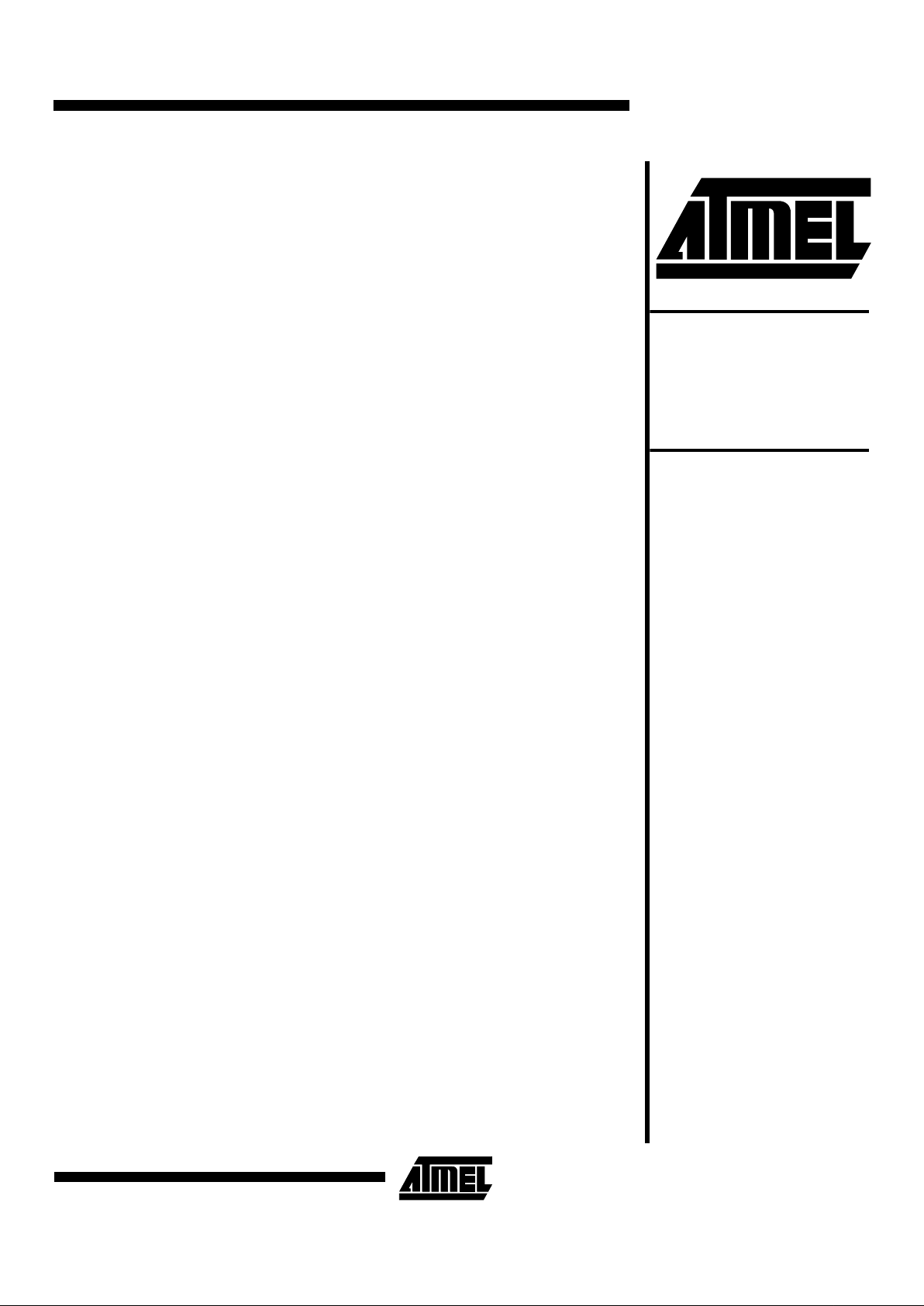

44-Lead PLCC

Top View

7

8

9

10

11

12

13

14

15

16

17

39

38

37

36

35

34

33

32

31

30

29

TDI/I/O

I/O

I/O

GND

PD1/I/O

I/O

I/O/TMS

I/O

VCC

I/O

I/O

I/O

I/O/TDO

I/O

I/O

VCC

I/O

I/O

I/O/TCK

I/O

GND

I/O

65432

1

4443424140

1819202122232425262728

I/O

I/O

I/O

I/O

GND

VCC

I/O

PD2/I/O

I/O

I/O

I/O

I/O

I/O

I/O

VCC

GCK2/OE2/I

GCLR/I

OE1/I

GCK1/I

GND

I/O/GCLK3

I/O

68-Lead PLCC

Top View

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

I/O

VCC

I/O/TD1

I/O

I/O

I/O

GND

I/O/PD1

I/O

I/O/TMS

I/O

VCC

I/O

I/O

I/O

I/O

GND

I/O

I/O

GND

I/O/TDO

I/O

I/O

I/O

VCC

I/O

I/O

I/O/TCK

I/O

GND

I/O

I/O

I/O

I/O

987654321

68676665646362

61

2728293031323334353637383940414243

I/O

I/O

I/O

I/O

VCC

I/O

I/O

GND

VCC

I/O

I/O/PD2

GND

I/O

I/O

I/O

I/O

VCC

I/O

I/O

I/O

GND

I/O

I/O

VCC

I/OE2/GCK2

GCLR/I

OE1/I

I/GCK1

GND

I/GCK3

I/O

VCC

I/O/TCK

I/O

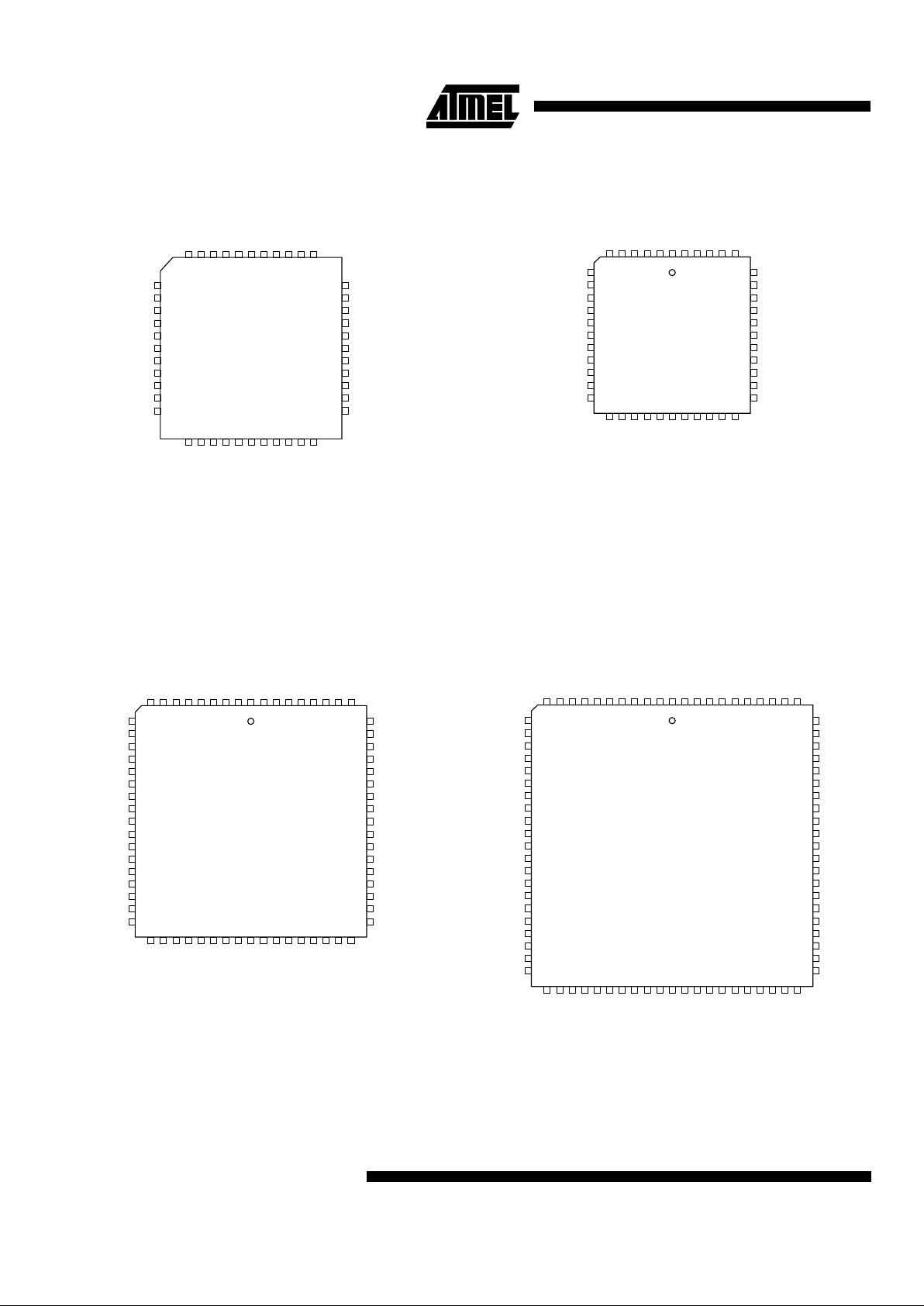

84-Lead PLCC

Top View

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

I/O

VCC

I/O/TDI

I/O

I/O

I/O

I/O

GND

I/O/PD1

I/O

I/O

I/O/TMS

I/O

I/O

VCC

I/O

I/O

I/O

I/O

I/O

GND

I/O

I/O

GND

I/O/TDO

I/O

I/O

I/O

I/O

VCC

I/O

I/O

I/O

I/O/TCK

I/O

I/O

GND

I/O

I/O

I/O

I/O

I/O

11

10

987654321

848382818079787776

75

333435363738394041424344454647484950515253

I/O

I/O

I/O

I/O

I/O

VCC

I/O

I/O

I/O

GND

VCC

I/O

I/O

I/O/PD2

GND

I/O

I/O

I/O

I/O

I/O

VCC

I/O

I/O

I/O

I/O

GND

I/O

I/O

I/O

VCC

I/OE2/GCK2

I/GCLR

I/OE1

I/GCK1

GND

I/GCK3

I/O

I/O

VCC

1/O

I/O

I/O

44-Lead TQFP

Top View

1

2

3

4

5

6

7

8

9

10

11

33

32

31

30

29

28

27

26

25

24

23

I/O/TDI

I/O

I/O

GND

PD1/I/O

I/O

TMS/I/O

I/O

VCC

I/O

I/O

I/O

I/O/TDO

I/O

I/O

VCC

I/O

I/O

I/O/TCK

I/O

GND

I/O

4443424140393837363534

1213141516171819202122

I/O

I/O

I/O

I/O

GND

VCC

I/O

I/O/PD2

I/O

I/O

I/O

I/O

I/O

I/O

VCC

I/OE2/GCK2

GCLR/I

I/OE1

GCK1/I

GND

GCK3

I/O

ATF1504AS(Z)

3

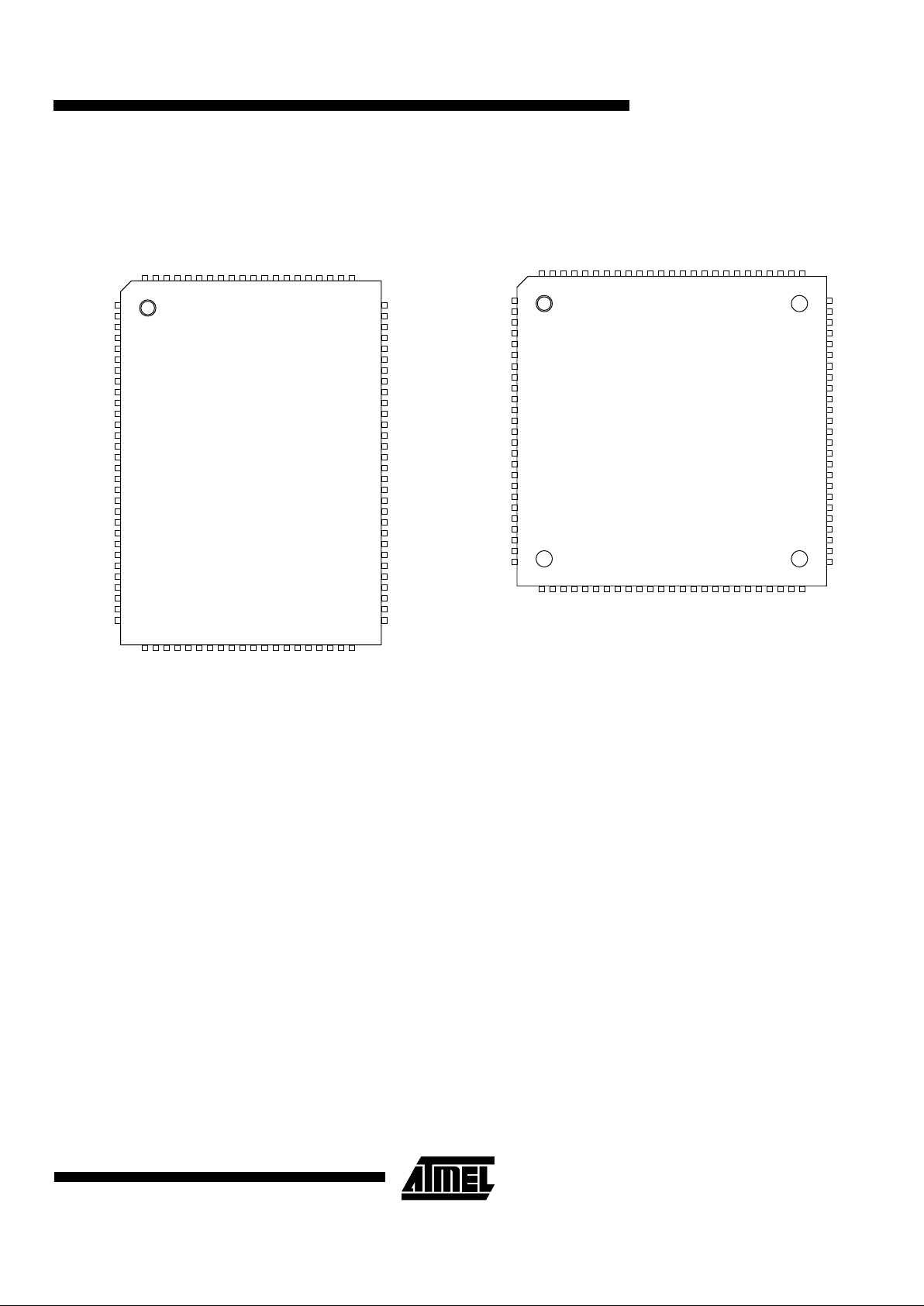

100-Lead PQFP

Top View

100-Lead TQFP

Top View

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

NC

NC

I/O

I/O

VCCIO

I/O/TDI

NC

I/O

NC

I/O

I/O

I/O

GND

I/O/PD1

I/O

I/O

I/O/TMS

I/O

I/O

VCCIO

I/O

I/O

I/O

NC

I/O

NC

I/O

GND

NC

NC

NC

NC

I/O

I/O

GND

I/O/TDO

NC

I/O

NC

I/O

I/O

I/O

VCCIO

I/O

I/O

I/O

I/O/TCK

I/O

I/O

GND

I/O

I/O

I/O

NC

I/O

NC

I/O

VCCIO

NC

NC

100

99989796959493929190898887868584838281

31323334353637383940414243444546474849

50

I/O

I/O

I/O

I/O

I/O

VCCIO

I/O

I/O

I/O

GND

VCCINT

I/O

I/O

I/O/PD2

GND

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

GND

I/O

I/O

I/O

VCCINT

INPUT/OE2/GCLK2

INPUT/GCLR

INPUT/OE1

INPUT/GCLK1

GND

I/O/GCLK3

I/O

I/O

VCCIO

I/O

I/O

I/O

NC

NC

VCCIO

I/O/TDI

NC

I/O

NC

I/O

I/O

I/O

GND

I/O/PD1

I/O

I/O

I/O/TMS

I/O

I/O

VCCIO

I/O

I/O

I/O

NC

I/O

NC

I/O

I/O

GND

I/O/TDO

NC

I/O

NC

I/O

I/O

I/O

VCCIO

I/O

I/O

I/O

I/O/TCK

I/O

I/O

GND

I/O

I/O

I/O

NC

I/O

NC

I/O

VCCIO

GND

NC

NC

I/O

I/O

I/O

I/O

I/O

VCCIO

I/O

I/O

I/O

GND

VCCINT

I/O

I/O

I/O/PD2

GND

I/O

I/O

I/O

I/O

I/O

NC

NC

I/O

I/O

I/O

I/O

I/O

GND

I/O

I/O

I/O

VCCINT

INPUT/OE2/GCLK2

INPUT/GCLR

INPUT/OE1

INPUT/GCLK1

GND

I/O/GCLK3

I/O

I/O

VCCIO

I/O

I/O

I/ONCNC

I/O

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

100

9998979695949392919089888786858483828180797877

76

26272829303132333435363738394041424344454647484950

ATF1504ASZ

4

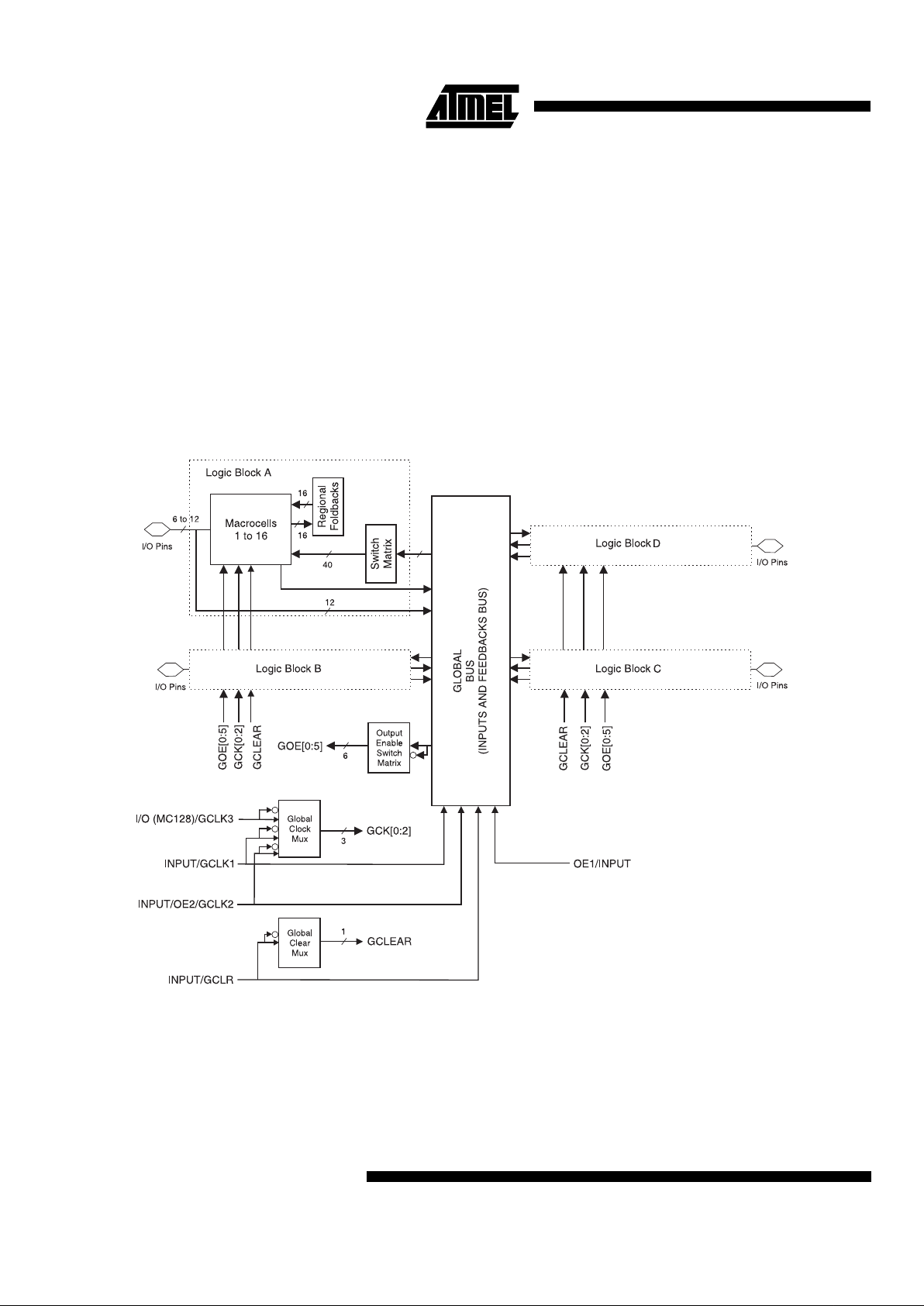

TTL, SSI, MSI, LSI and classic PLDs. The ATF1504AS’s

enhanced routing switch matrices increase usable gate

count, and the odds of successful pin-locked design modifications.

The ATF1504AS has up to 68 bi-directional I/O pins and 4

dedicated input pins, depending on the type of device package selected. Each dedicated pin can also serve as a global control signal; re gister clock, regi ster reset or output

enable. Each of th ese contro l signals can be selec ted for

use individually within each macrocell.

Each of the 64 macrocells g enerates a buried feedba ck,

which goes to the g lobal bus. E ach inpu t and I/ O pin al so

feeds into the global bu s. The sw itch matr ix in each logic

block then selects 40 individual signals from the global bus.

Each macrocell also generates a foldback logic term, which

goes to a regional bus . Casc ade logi c betwee n macroc ells

in the ATF1504AS allows f ast, effi cient ge neratio n of complex logic functions. The ATF1504AS contains four such

logic chains, each capable of creating sum term logic with a

fan in of up to 40 product terms.

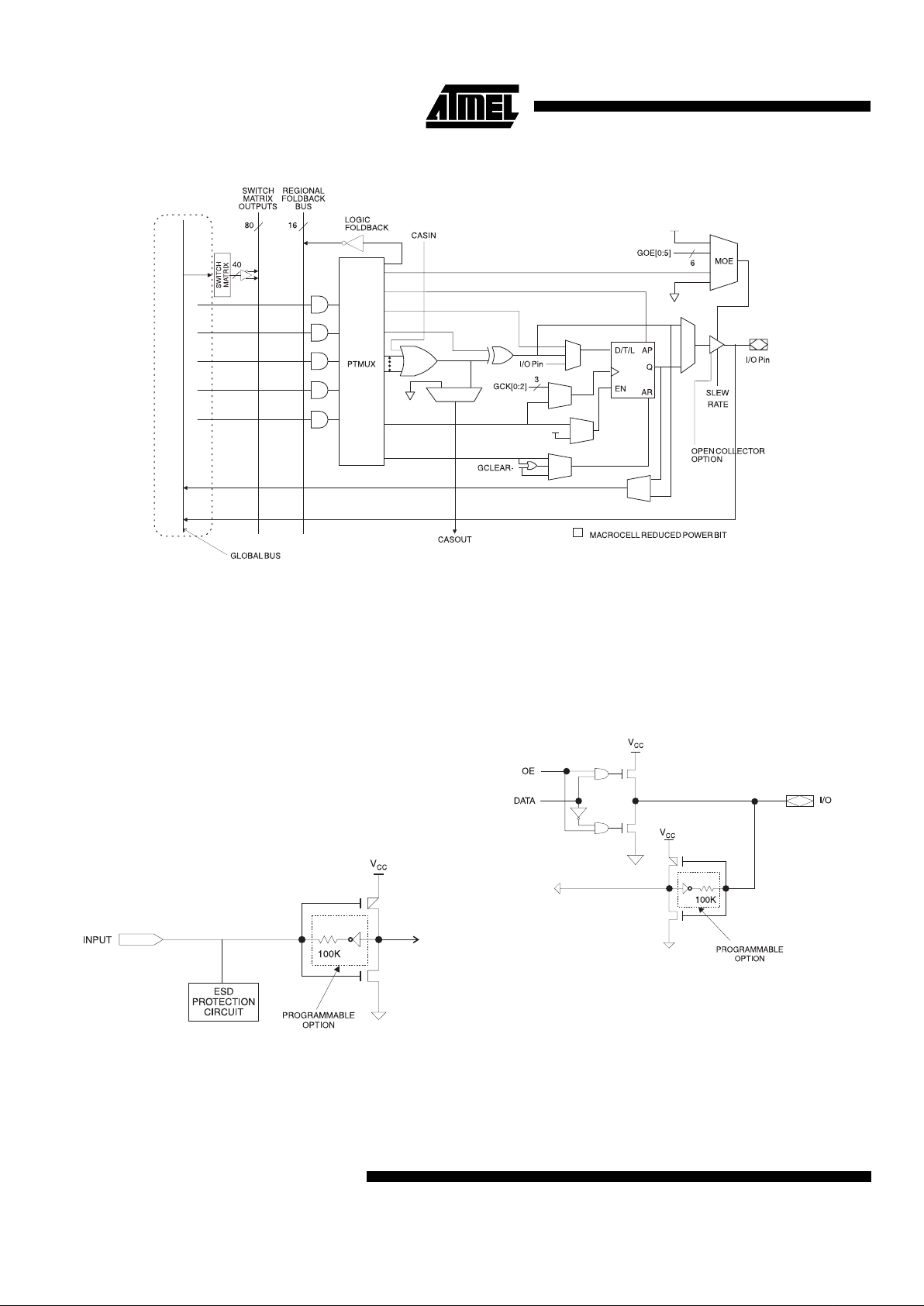

The ATF1504AS macrocell shown in Figure 1, is flexible

enough to support highly complex lo gic f unc ti ons operating

at high speed . The macroc ell cons ists of five sections:

product terms and product term select multiplexer;

OR/XOR/CASCADE logic; a flip-flop; output sel ect and

enable; and logic array inputs.

Block Diagram

Unused product terms are automatical ly disabled by the

compiler to decrease power consumption. A Security Fuse,

when programmed, protects the contents of the

ATF1504AS. Two bytes (16-bits) of User Signature are

accessible to the us er for purpos es such as storing pr oject

name, part number, revisi on or dat e. The Us er Signat ur e is

accessible regardless of the state of the Security Fuse.

The ATF1504AS device is an In-System Programmable

(ISP) device. It us es the industry stan dard 4-pin JTAG

interface (IEEE Std. 1149.1), and is fully compliant with

JTAG’s Boundary Scan Description Language (BSDL). ISP

allows the device to b e programmed with out removing it

from the printed circuit board. In addition to simplifying the

manufacturing flow, ISP also allows design modifications to

be made in the field via software.

ATF1504ASZ

5

Product Terms and Select MUX

Each ATF1504AS macrocell has five product terms. Each

product term recei ves as its inputs all si gna ls fr om both the

global bus and regional bus.

The product term selec t multi plexer (PTMU X) allo cates the

five product terms as needed to the macrocel l logic gates

and control signals. The PTMUX programming is determined by the design compiler, wh ich selec ts the opti mum

macrocell configuration.

OR/XOR/CASCADE Logic

The ATF1504AS’s logic structure is designed to efficiently

support all types of logic. Within a single macrocell, all the

product terms can be routed to the OR gate, creating a 5input AND/OR sum term. With the addition of the CASIN

from neighboring macrocells, this can be expanded to as

many as 40 product terms with a very small additional

delay.

The macrocell’s XOR gate allows efficient implementation

of compare and arithmetic fun ctions. O ne inpu t to the XOR

comes from the OR sum term. The other XOR input can be

a product term or a fixed high or low level. For combinatorial outputs, the fix ed level inpu t allows polar ity selec tion.

For registered func tions, the fixe d levels all ow DeMorgan

minimization of product terms. The XOR gate is also used

to emulate T- and JK-type flip-flops.

Flip Flop

The ATF1504AS’s flip flop has very flexible data and control functions. The data input can come from either the XOR

gate, from a separate product term or directly from the I/O

pin. Selectin g the se parate p roduc t term al lows cr eatio n of

a buried registered feedback within a combinatorial output

macrocell. (This feature is automatically implemented by

the fitter softwa re). In add ition to D, T, J K and SR op eration, the flip flop can also be configured as a flow-through

latch. In this mode, data passes through when the clock is

high and is latched when the clock is low.

The clock itself can eit her be on e of the Glo bal CLK Sig nal

GCK[0 : 2] or an indi vidual product term. T he flip flop

changes state on the clock’s rising edge. When the GCK

signal is used as the clock, one of the macrocell product

terms can be se lecte d as a clock e nable. W hen the clock

enable function is active and the enable signal (product

term) is low, all clock edges are ignored. The flip flop’s

asynchronous reset signal (AR) can be either the Global

Clear (GCLEAR), a product term, or always off. AR can

also be a logic OR of GCLEAR with a product term. The

asynchronous pres et (AP ) can be a pr odu ct ter m or alway s

off.

Output Select and Enable

The ATF1504AS macrocell output can be selected as registered or combinatorial. The buried feedback signal can be

either combinatorial or registered signal regardless of

whether the output is combinatorial or registered.

The output enable multiplexer (MOE) controls the output

enable signals. Any buf fer can be pe rmanen tly enabled for

simple output operation. Buffers can als o be permanently

disabled to allow use of the pin as an input. In thi s configu ration all the macroce ll reso urces are still avai lable, in cluding the buried feedback, expa nder and CASCADE log ic.

The output enable for each macrocell can be selected as

either of the two dedicated OE input pins as an I/O pin configured as an input, or as an individual product term.

Global Bus/Switch Matrix

The global bus contains all input and I/O pin signals as well

as the buried feedback si gnal from all 64 macroc ells. The

Switch Matrix in each Logic Block receives as its inputs all

signals from the global bus. Under s oftware control, up to

40 of these signals can be selected as inputs to the Logic

Block.

Foldback Bus

Each macrocell also generat es a foldback product term.

This signal goes to the regional bus and is available to 4

macrocells. The foldback is an inverse polarity of one of the

macrocell’s product terms. The 4 foldback terms in each

region allows generation of high fan-in sum terms (up to 9

product terms) with a small additional delay.

ATF1504ASZ

6

Figure 1.

ATF1504AS Macrocell

Programmable Pin-Keeper Option for

Inputs and I/Os

The ATF1504AS offers the op tion o f pro grammin g all inpu t

and I/O pins so that pin keeper c ircuits can be utilized .

When any pin is driven high or low and then subsequently

left floating, it will stay at that previous high or low level .

This circuitry prevent s unused input and I/O lines from

floating to inter mediat e volt age leve ls, whic h cause unn ecessary power consumption and system noise. The keeper

circuits eliminate the need for external pull-up resistors and

eliminate their DC power consumption.

Input Diagram

Speed/Power Management

The ATF1504AS has several built-in speed and power

management features. The ATF1504AS contains circuitry

that automatically puts the device into a low power stand-

by mode when no logic trans itions are oc curring. T his not

only reduces power consumption during inactive periods,

but also prov ides a p roportion al power s avings for most

applications running at system sp eeds bel ow 50 MHz. This

feature may be selected as a design option.

I/O Diagram

To further reduce power, each ATF1504AS macrocell has

a Reduced Power bit feat ure. Th is fe ature allows individual

macrocells to be c onfigur ed for maxi mum pow er sav ings.

This feature may be selected as a design option.

All ATF1504ASs also have an opti onal po wer do wn m ode.

In this mode, current d rops to below 10 m A. When t he

power down option is selected, either PD1 or PD2 pins (or

both) can be used to power down the part. The power down

option is selecte d in the de sign so urce file . When enabled,

ATF1504ASZ

7

the device goes into power down when either PD1 or PD2

is high. In the power down mo de, all internal logic signa ls

are latched and held, as are any enabled outputs.

All pin transitions are ignored until the PD pin is brought

low. When the power down feature is enabled, the PD1 or

PD2 pin cannot be used as a logic input or output. However, the pin’s macroc ell m ay st ill be used to gener ate bur ied foldback and cascade logic signals.

All Power-Down AC Ch aracteristic parameters are computed from external input or I/O pins, with Reduced Power

Bit turned on. For mac rocells in reduced- power mode

(Reduced power bit turned on), the reduced power adder,

tRPA, must be added to the AC param eters, whic h include

the data paths t

LAD

, t

LAC

, tIC, t

ACL

, t

ACH

and t

SEXP

.

The ATF1504AS macrocell also has an option whereby the

power can be reduced on a per macrocell basis. By

enabling this power down option, macrocells that are not

used in an application can be turned down thereby reducing the overall power consumption of the device.

Each output als o ha s i ndi vi dua l s lew rate control. This m a y

be used to reduce system noise by s lowing down outputs

that do not need to operate at maximum speed. Outputs

default to slow switching , and may be speci fied as fast

switching in the design file.

Design Software Support

ATF1504AS des igns are su pported by s everal thir d party

tools. Automated fitters allow logic synthesis using a variety

of high level description languages and formats.

Power Up Reset

The ATF1504AS has a power-up reset option at two different voltage trip levels when the device is being powered

down. Within the fitter, or during a conversion, if the

“power-reset” option is turned “on” (which is the default

option), the trip levels during power up or power down is at

2.8V. The user can change this default option from “on” to

“off” (within the fitter or specify it as a switch during conversion). When th is is done, the volt age trip level duri ng

power-down changes from 2.8V to 0.7V. This is to ensure a

robust operating environment.

The registers in the A TF1504 AS ar e d es igned to reset during power up. At a point delayed slightl y from V

CC

crossing

Vrst, all registers will be reset to the low state. The output

state will depend on the polarity of the buffer.

This feature is critical for state machine initialization. However, due to the asynchronous nature of reset and the

uncertainty of how V

CC

actually rises in the sy stem, the fol -

lowing conditions are required:

1. The V

CC

rise must be monotonic,

2. After reset occurs, all input and feedback setup

times must be met before driving the clock pinhigh, and,

3. The clock must remain stable during T

D

.

Security Fuse Usage

A single fuse is provided to preven t unauthorized copy ing

of the ATF1504AS fuse patterns. Once programmed, fuse

verify is inhibited. However, the 16-bit User Signature

remains accessible.

Programming

ATF1504AS devices are In-System Programmable (ISP)

devices utilizing the 4-pin JTAG protocol. This capability

eliminates package h andling normally requir ed fo r p ro gram

and facilitates rapid design iterations and field changes.

Atmel provides ISP hardware and softwar e to allow programming of the ATF1504AS via the PC. ISP is perfo rmed

by using either a downlo ad cab le, or a compar able b oard

tester or a simple microprocessor interface.

To facilitate ISP programmi ng by the Automated Test

Equipment (ATE) vendors. Serial Vector Format (SV F) file s

can be created by Atmel provided Software utilities.

ATF1504AS devices can also be programmed using standard 3rd party programmers. With 3rd party programmer

the JTAG ISP port can be disabled thereby allowing 4 additional I/O pins to be used for logic.

Contact your local Atmel representatives or Atmel PLD

applications for details.

ISP Programming Protection

The ATF1504AS has a special feature which locks the

device and pr events the in puts a nd I/O from d riving if the

programming process is interrupted due to any reason. The

inputs and I/O default to high-Z state during such a c ondition. In addition the pin keep er op tion pres erves the forme r

state during device programming.

All ATF1504AS devices ar e initially shipped in the erased

state thereby making them ready to use for ISP.

Note: For more information refer to the “Designing for In-Sys-

tem Programmability with Atmel CPLDs” application

note.

Loading...

Loading...