ATMEL ATA6662-TAQY, ATA6662, AT86RF212 Datasheet

Features

• Fully Integrated 800/900 MHz-Band Transceiver

- European ISM Band from 863 to 870 MHz

- North American ISM Band from 902 to 928 MHz

• Direct Sequence Spread Spectrum with Different Modulation and Data Rates

- BPSK with 20 and 40 kbit/s (compliant to IEEE 802.15.4-2006)

- O-QPSK with 100 and 250 kbit/s (compliant to IEEE 802.15.4-2006)

- O-QPSK with 200, 400, 500, and 1000 kbit/s PSDU Data Rate

• Flexible Combination of Frequency Bands and Data Rates

• Industry Leading Link Budget

- Receiver Sensitivity up to -110 dBm

- Programmable TX Output Power up to +10 dBm

• Low Power Supply Voltage from 1.8 V to 3.6 V

- Internal Voltage Regulators and Battery Monitor

• Low Current Consumption

- SLEEP = 0.2 µA

- TRX_OFF = 0.4 mA

- RX_ON = 9 mA

- TX_ACTIVE = 19 mA (at P

• Digital Interface

- Registers, Frame Buffer, and AES Accessible through SPI

- Clock Output with Configurable Rate

• Radio Transceiver Features

- Adjustable Receiver Sensitivity

- Integrated TX/RX Switch, LNA, and PLL Loop Filter

- Fast Settling PLL Supporting Frequency Hopping

- Automatic VCO and Filter Calibration

- Integrated 16 MHz Crystal Oscillator

- 128 byte FIFO for Transmit/Receive

• IEEE 802.15.4-2006 Hardware Support

- FCS Computation and Check

- Clear Channel Assessment

- Received Signal Strength Indicator, Energy Detection, and Link Quality

Indication

• MAC Hardware Accelerator

- Automatic Acknowledgement, CSMA-CA, and Retransmission

- Automatic Frame Filtering

• AES 128 bit Hardware Accelerator (ECB and CBC modes)

• Extended Feature Set Hardware Support

- True Random Number Generation for Security Applications

- TX/RX Indication (External RF Front End Control)

- MAC based Antenna Diversity

• Optimized for Low BoM Cost and Ease of Production

- Low External Component Count: Antenna, Reference Crystal, and Bypass

Capacitors

- Excellent ESD Robustness

• Industrial Temperature Range from -40°C to +85°C

• 32-pin Low-profile Lead-free Plastic QFN Package, 5.0 x 5.0 x 0.9 mm

• Compliant to IEEE 802.15.4-2003 and IEEE 802.15.4-2006, ETSI EN 300 220-1,

and FCC 47 CFR Section 15.247

= 5 dBm)

TX

3

AT86RF212

Low Power

800/900 MHz

Transceiver for

IEEE 802.15.4-

TM

2006, Zigbee

,

and ISM

Applications

PRELIMINARY

8168A-AVR-06/08

Disclaimer

1 Overview

Values contained in this datasheet are based on simulations and characterization of

other transceivers manufactured on a similar process technology. Final values will be

available after the device is characterized.

The AT86RF212 is a low-power, low-voltage 800/900 MHz transceiver specially

designed for low-cost IEEE 802.15.4, ZigBee

For the sub-1 GHz bands, it supports low data rates (20 and 40 kbit/s) of the IEEE

802.15.4-2003 standard [2] and provides optional data rates (100 and 250 kbit/s) using

O-QPSK, according to IEEE 802.15.4-2006 [1]. Furthermore, proprietary High Data

Rates Modes up to 1000 kbit/s can be employed.

The AT86RF212 is a true SPI-to-antenna solution. RF-critical components except the

antenna, crystal, and de-coupling capacitors are integrated on-chip. MAC and AES

hardware accelerators improve overall system power efficiency and timing.

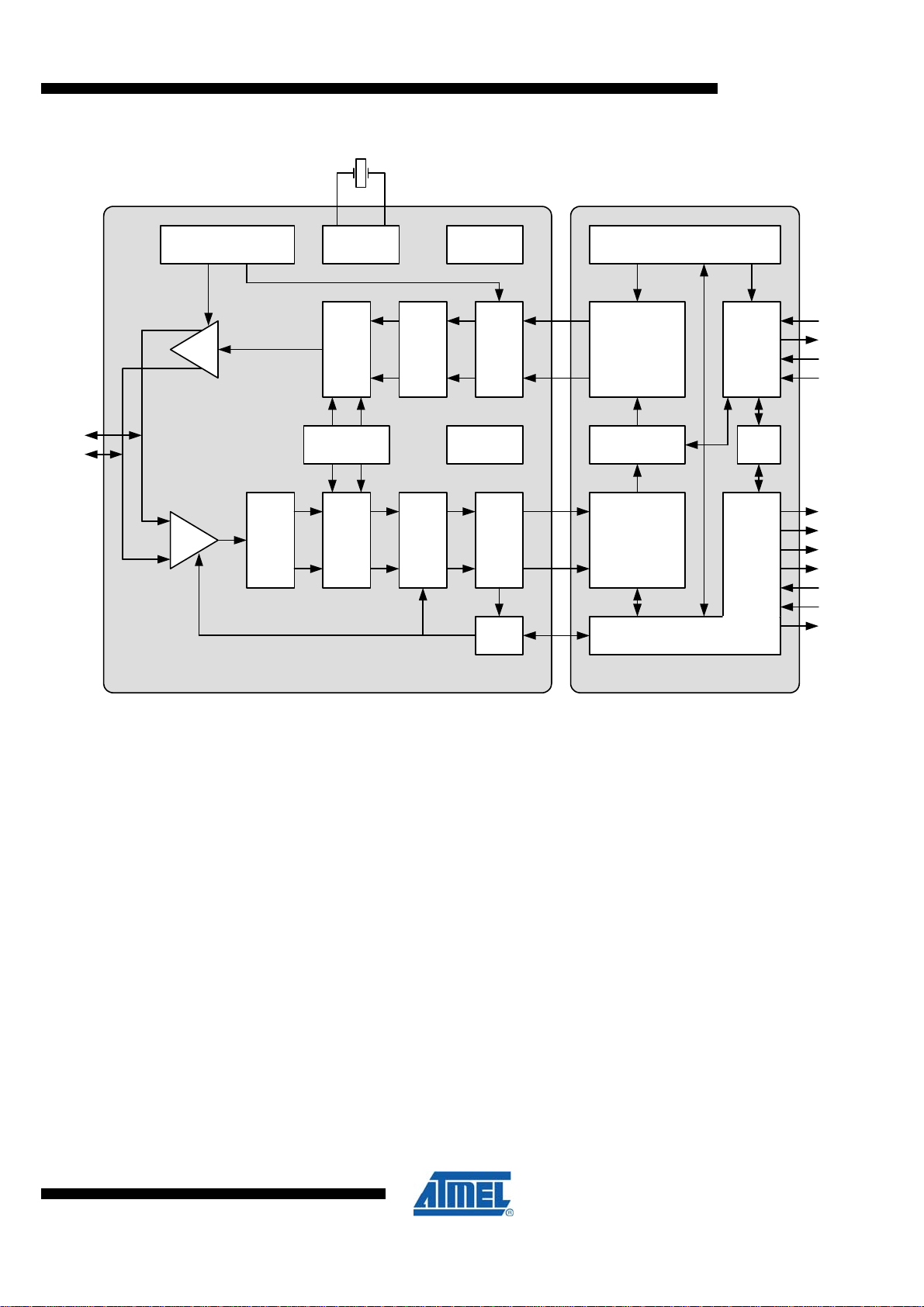

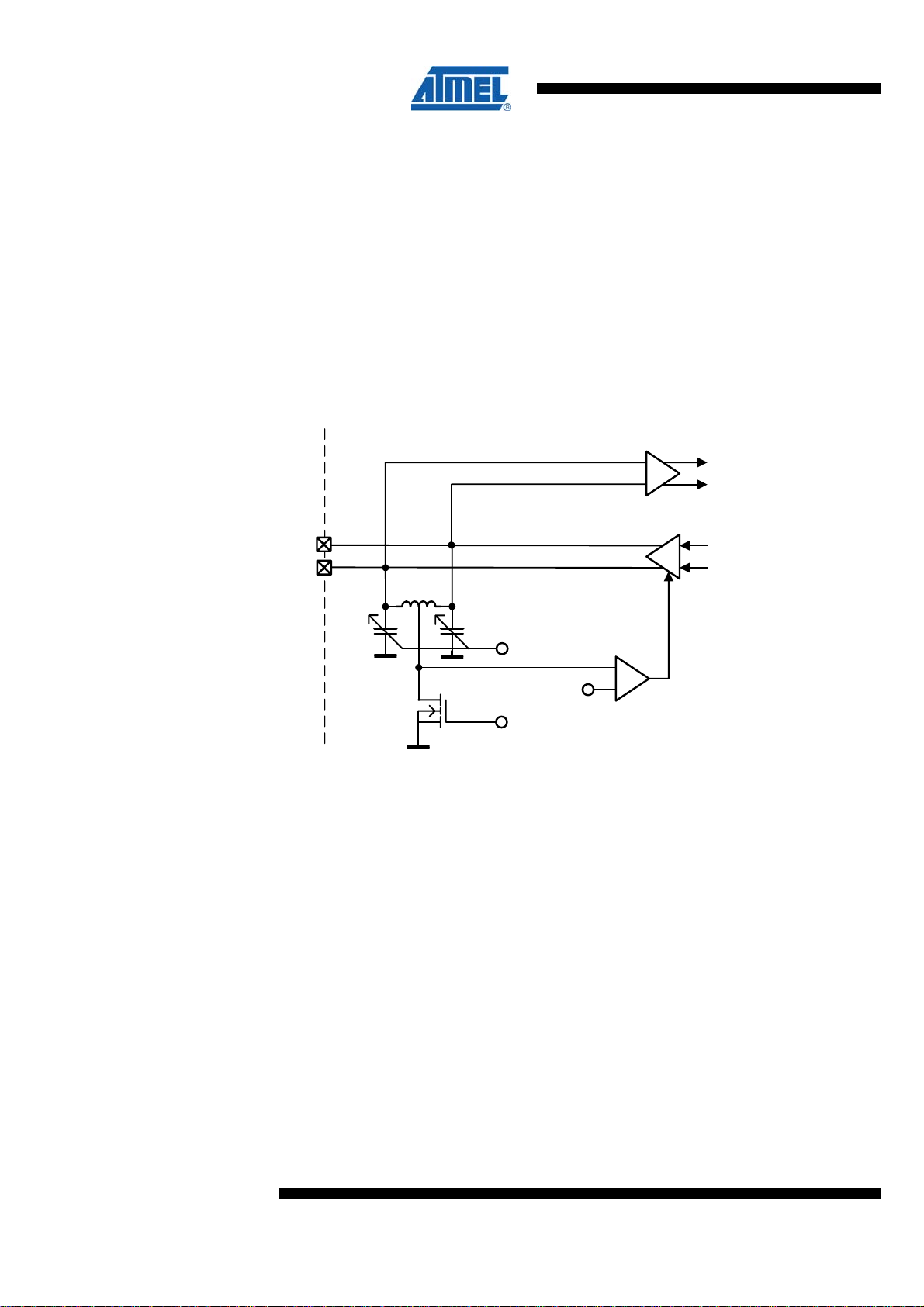

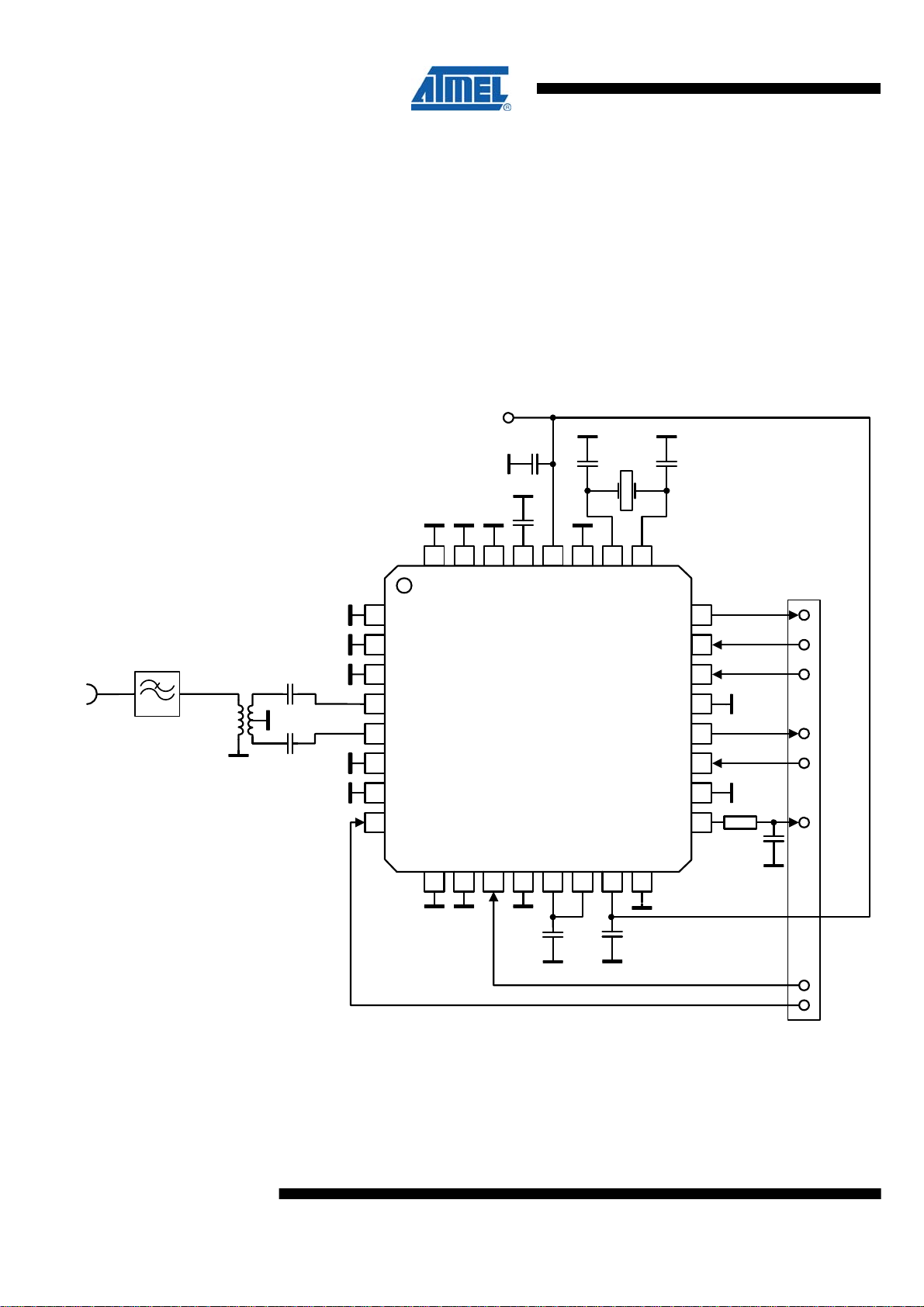

1.1 General Circuit Description

The AT86RF212 single-chip RF transceiver provides a complete radio interface

between the antenna and the microcontroller. It comprises the analog radio part, digital

modulation and demodulation including time and frequency synchronization, as well as

data buffering. The number of external components is minimized so that only the

antenna, a filter (at high output power levels), the crystal, and four bypass capacitors

are required. The bidirectional differential antenna pins are used in common for RX and

TX, i.e. no external antenna switch is needed. Control of an external power amplifier is

supported by two digital control signals (differential operation). The transceiver block

diagram is shown in

Figure 1-1.

TM

, and high data rate ISM applications.

2

AT86RF212

8168A-AVR-06/08

Figure 1-1. AT86RF212 Block Diagram

AT86RF212

RFP

RFN

LNA

TX Power

XTAL1

XOSC

Mixer LPF DAC PA

Frequency

Synthesis

PPF BPF ADC

Mixer

XTAL2

Voltage

Regulator

FTN,

BATMON

AGC

Configuration Registers

TX BBP

TRX Buffer

RX BBP

Control Logic

SPI

(Slave)

AES

/SEL

MISO

MOSI

SCLK

IRQ

CLKM

DIG1

DIG2

/RST

SLP_TR

DIG3/4

Analog Domain Digital Domain

The receiver path is based on a low-IF architecture. After channel filtering and downconversion the low-IF signal is sampled and applied to the digital signal processing part.

Communication between transmitter and receiver is based on direct sequence spread

spectrum with different modulation schemes and spreading codes. The AT86RF212

supports the IEEE 802.15.4-2006 standard mandatory BPSK modulation and optional

O-QPSK modulation in the 800 and 900 MHz band. For applications not necessarily

targeting IEEE compliant networks the radio transceiver supports proprietary High Data

Rate Modes based on O-QPSK.

A single 128 byte TRX buffer stores receive or transmit data.

The AT86RF212 features hardware supported 128 bit security operation. The

standalone AES encryption/decryption engine can be accessed in parallel to all PHY

operational modes. Configuration of the AT86RF212, reading, and writing of data

memory as well as the AES hardware engine are controlled by the SPI interface and

additional control signals.

On-chip low-dropout voltage regulators provide the analog and digital 1.8 V power

supply. Control registers retain their settings in SLEEP mode when the regulators are

turned off. The RX and TX signal processing paths are highly integrated and optimized

for low power consumption.

8168A-AVR-06/08

3

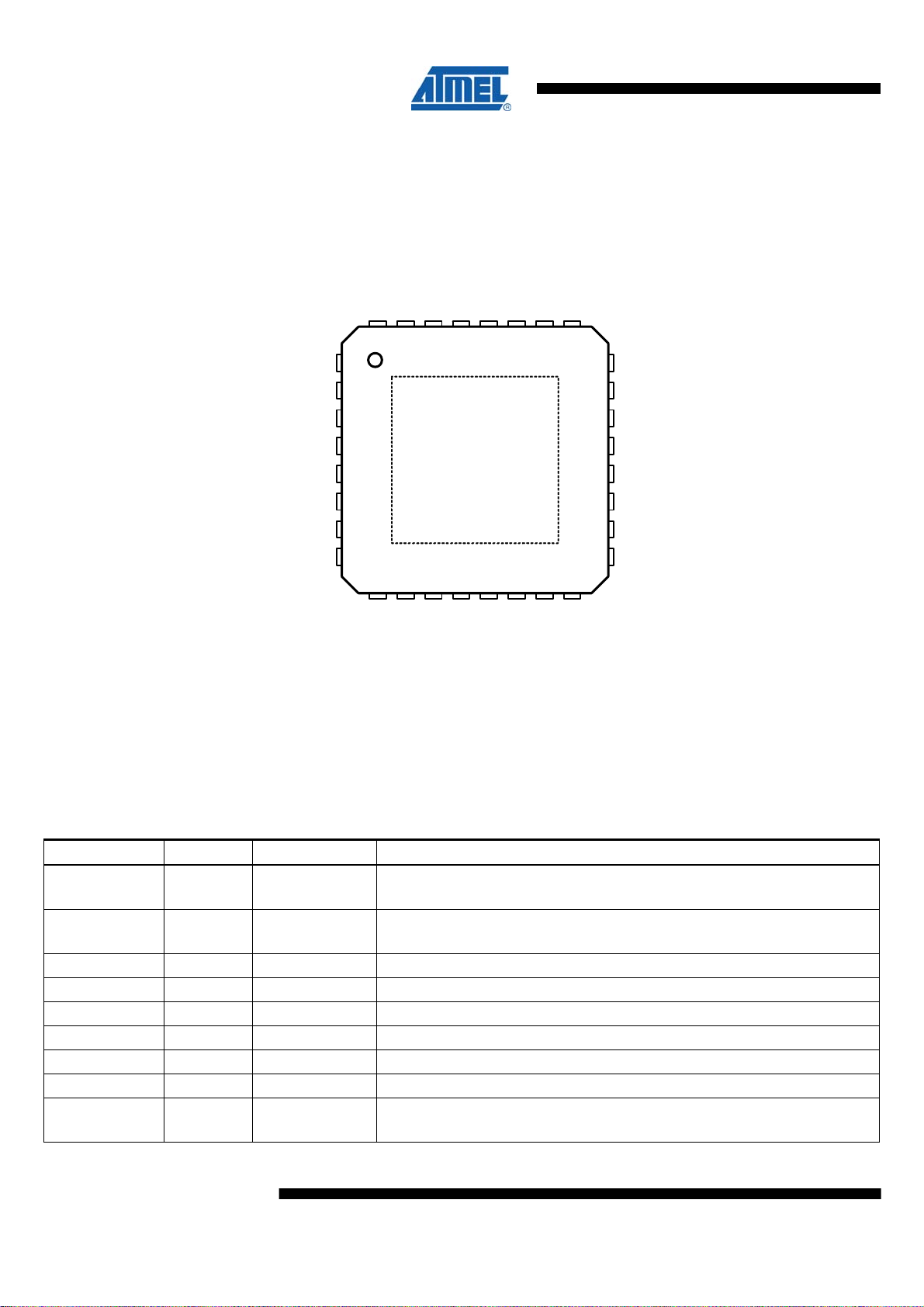

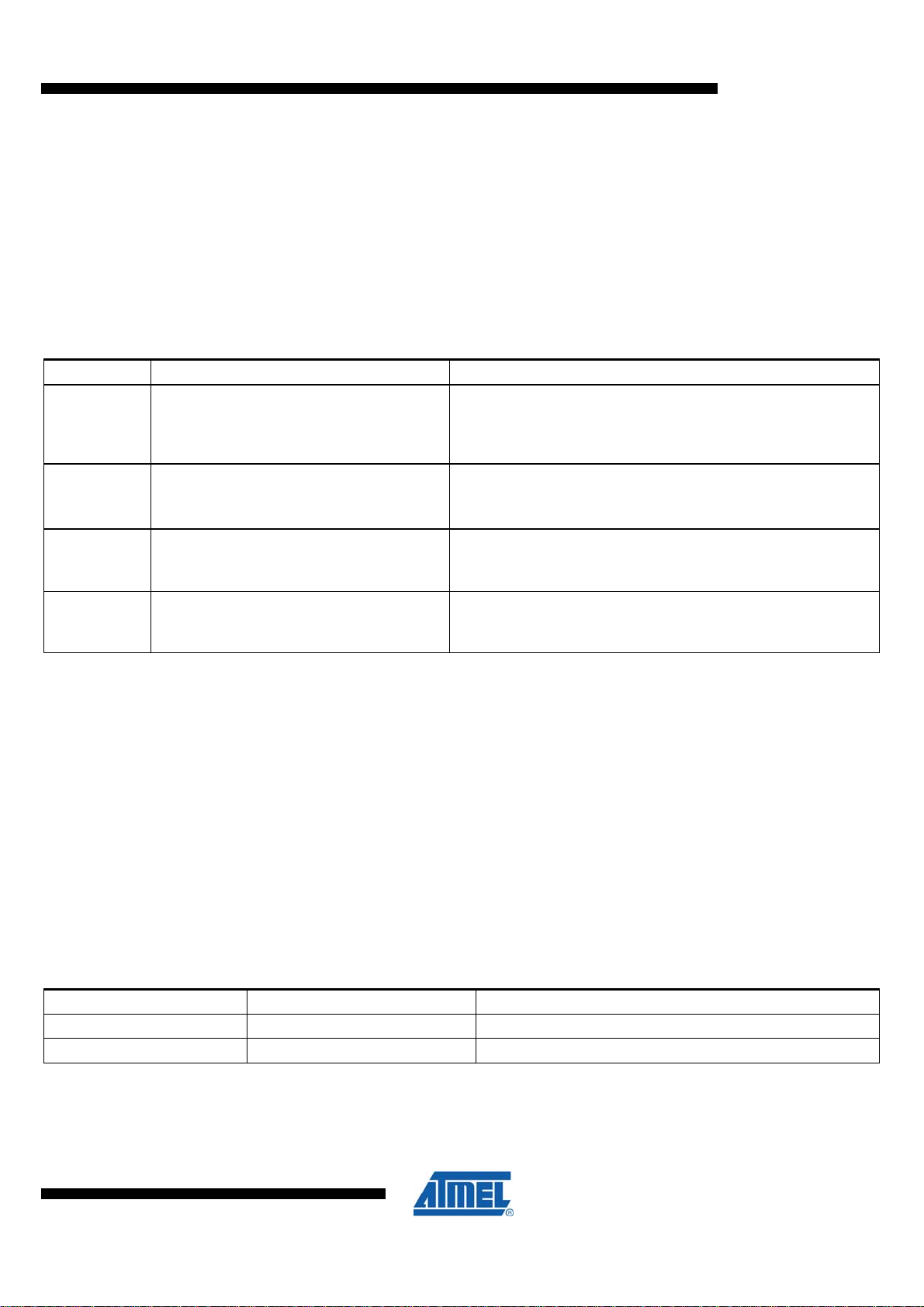

2 Pin Configuration

2.1 Pin-out Diagram

Figure 2-1. AT86RF212 Pin-out Diagram

AVSS

EVDD

AVDD

AVSS

AVSS

AVSS

32

31 30 29 28 27 26 25

DIG3

DIG4

AVSS

1

2

3

AVSS

exposed paddle

XTAL2

XTAL1

24

23

22

IRQ

/SEL

MOSI

RFP

RFN

AVSS

DVSS

/RST

4

5

6

7

8

9 10111213141516

DIG1

Note: The exposed paddle is electrically connected to the die inside the package. It shall be

soldered to the board to ensure electrical and thermal contact and good mechanical

stability.

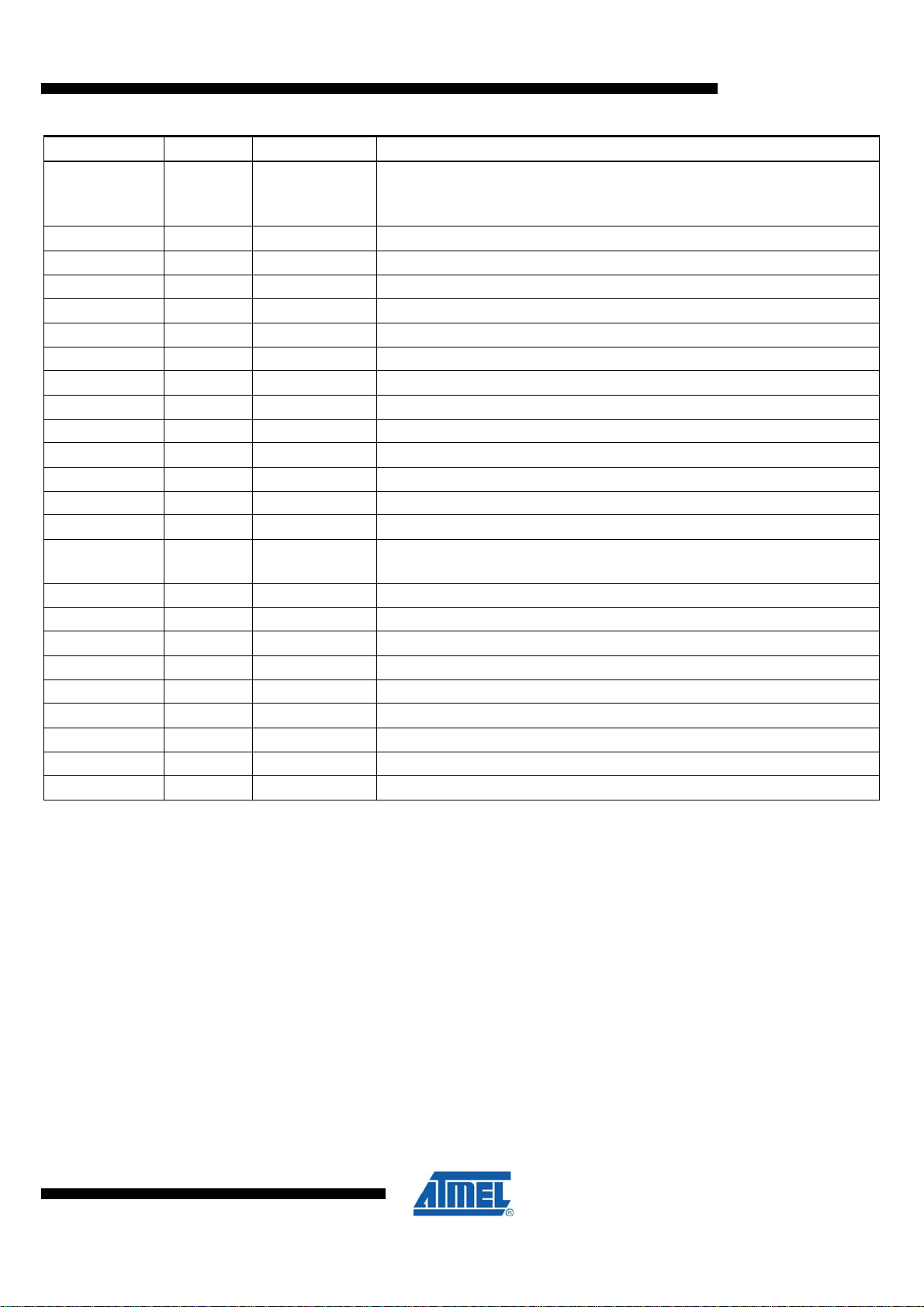

2.2 Pin Description

Table 2-1. Pin Description

Pins Name Type Description

1 DIG3 Digital output RX/TX Indication, see section 9.4;

if disabled, internally pulled to AVSS

2 DIG4 Digital output RX/TX Indication (DIG3 inverted), see section 9.4;

if disabled, internally pulled to AVSS

3 AVSS Ground Ground for RF signals

4 RFP RF I/O Differential RF signal

5 RFN RF I/O Differential RF signal

6 AVSS Ground Ground for RF signals

7 DVSS Ground Digital ground

8 /RST Digital input Chip reset; active low

9 DIG1 Digital output Antenna Diversity RF switch control, see section 9.3;

if disabled, internally pulled to DVSS

AT86RF212

DIG2

SLP_TR

DVSS

DVDD

DVDD

21

20

19

18

17

DVSS

DEVDD

DVSS

MISO

SCLK

DVSS

CLKM

4

AT86RF212

8168A-AVR-06/08

AT86RF212

Pins Name Type Description

10 DIG2 Digital output 1. Antenna Diversity RF switch control (DIG1 inverted), see section 9.3

2. Signal IRQ_2 (RX_START) for RX Frame Time Stamping, see section 9.5

If disabled, internally pulled to DVSS

11 SLP_TR Digital input Controls sleep, transmit start, receive states; active high, see section 4.6

12 DVSS Ground Digital ground

13 DVDD Analog Regulated 1.8 V internal supply voltage; digital domain, see section 7.5

14 DVDD Analog Regulated 1.8 V internal supply voltage; digital domain, see section 7.5

15 DEVDD Supply External supply voltage; digital domain

16 DVSS Ground Digital ground

17 CLKM Digital output Master clock signal output; low if disabled, see section 7.7

18 DVSS Ground Digital ground

19 SCLK Digital input SPI clock

20 MISO Digital output SPI data output (master input slave output)

21 DVSS Ground Digital ground

22 MOSI Digital input SPI data input (master output slave input)

23 /SEL Digital input SPI select, active low

24 IRQ Digital output 1. Interrupt request signal; active high or active low, see section 4.7

2. Buffer-level mode indicator; active high

25 XTAL2 Analog Crystal pin, see sections 2.2.1.3 and 7.7

26 XTAL1 Analog Crystal pin or external clock supply, see section 2.2.1.3 and 7.7

27 AVSS Ground Analog ground

28 EVDD Supply External supply voltage, analog domain

29 AVDD Analog Regulated 1.8 V internal supply voltage; analog domain, see section 7.5

30 AVSS Ground Analog ground

31 AVSS Ground Analog ground

32 AVSS Ground Analog ground

Paddle AVSS Ground Analog ground; exposed paddle of QFN package

2.2.1 Analog and RF Pins

2.2.1.1 Supply and Ground Pins

8168A-AVR-06/08

EVDD, DEVDD

EVDD and DEVDD are analog and digital supply voltage pins of the AT86RF212 radio

transceiver.

AVDD, DVDD

AVDD and DVDD are outputs of the internal voltage regulators and require bypass

capacitors for stable operation. The voltage regulators are controlled independently by

the radio transceivers state machine and are activated depending on the current radio

transceiver state. The voltage regulators can be configured for external supply. For

details refer to section

7.5.

AVSS, DVSS

AVSS and DVSS are analog and digital ground pins respectively.

5

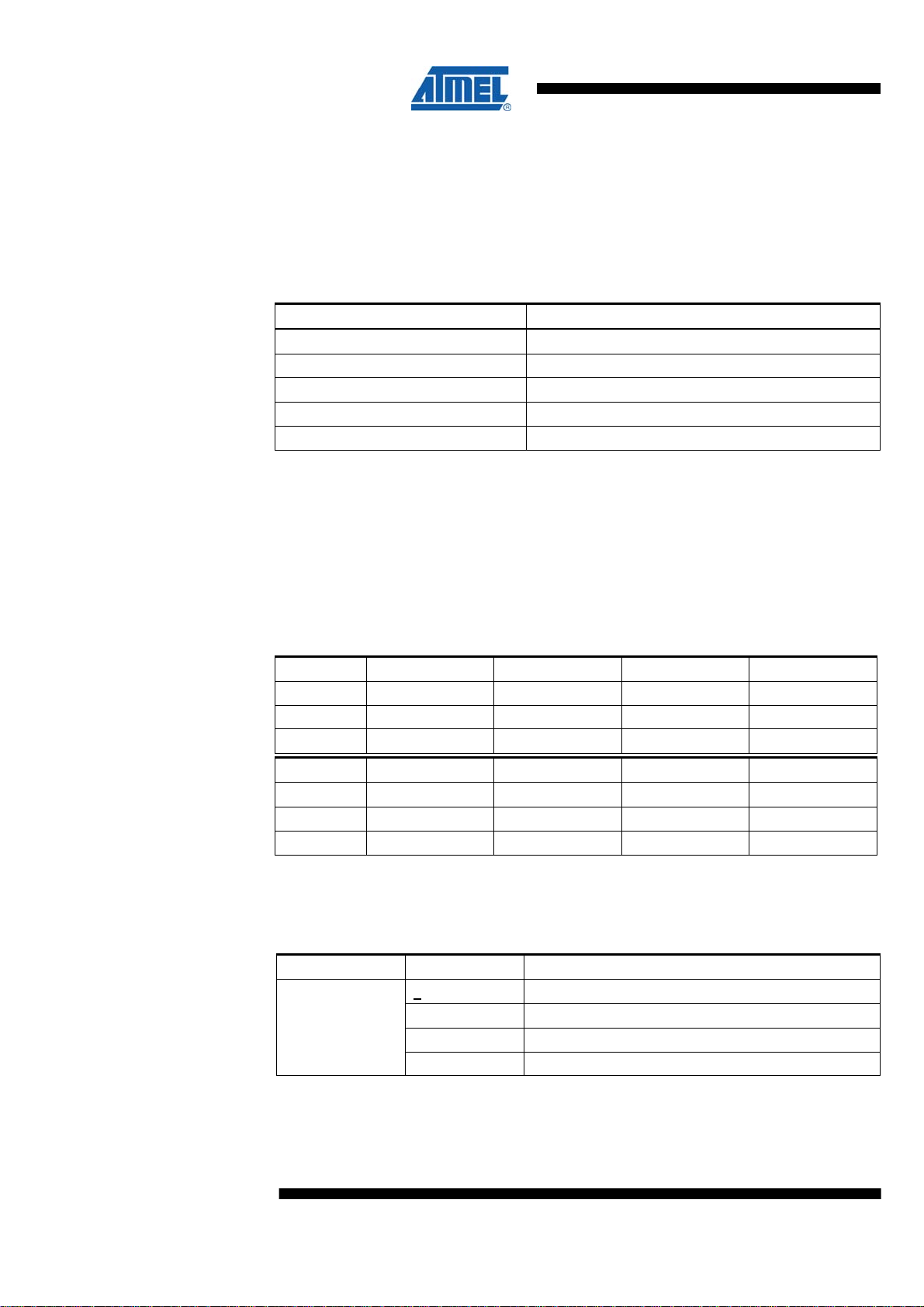

2.2.1.2 RF Pins

RFN, RFP

A differential RF port (RFP/RFN) provides common-mode rejection to suppress the

switching noise of the internal digital signal processing blocks. At board-level, the

differential RF layout ensures high receiver sensitivity by reducing spurious emissions

originated from other digital ICs such as a microcontroller.

The RF port is designed for a 100 Ω differential load. A DC path between the RF pins is

allowed. A DC path to ground or supply voltage is not allowed. Therefore when

connecting a RF-load providing a DC path to the power supply or ground, AC-coupling

is required as indicated in

Table 2-2.

A simplified schematic of the RF front end is shown in

Figure 2-2. Simplified RF Front-end Schematic

AT86RF212PCB

RFP

RFN

MC

0.9V

M0

RF port DC values depend on the operating state, refer to section

when the analog front-end is disabled (see section

ground, preventing a floating voltage larger than 1.8 V, which is not allowed for the

internal circuitry.

RXTX

CM

Feedback

Figure 2-2.

LNA

PA

5.1.2.3), the RF pins are pulled to

RX

TX

5. In TRX_OFF state,

6

AT86RF212

In transmit mode, a control loop provides a common-mode voltage of 0.9 V. Transistor

M0 is off, allowing the PA to set the common-mode voltage. The common-mode

capacitance at each pin to ground shall be < 100 pF to ensure the stability of this

common-mode feedback loop.

In receive mode, the RF port provides a low-impedance path to ground when transistor

M0, see

across the on-chip inductor can be measured at the RF pins.

Matching control (MC) is implemented by an adjustable capacitances to ground at each

RF pin as shown in

by setting a 4-bit control word (register 0x19, RF_CTRL_1).

Figure 2-2, pulls the inductor center tap to ground. A DC voltage drop of 20 mV

Figure 2-2. The input capacitance can be changed within 15 steps

8168A-AVR-06/08

2.2.1.3 Crystal Oscillator Pins

XTAL1, XTAL2

The pin XTAL1 is the input of the reference oscillator amplifier (XOSC), XTAL2 the

output. A detailed description of the crystal oscillator setup and the related

XTAL1/XTAL2 pin configuration can be found in section

When using an external clock reference signal, XTAL1 shall be used as input pin. For

further details refer to section

7.7.3.

2.2.1.4 Analog Pin Summary

Table 2-2. Analog Pin Behavior – DC values

Pin Values and Conditions Comments

RFP/RFN VDC = 0.9 V (BUSY_TX)

VDC = 20 mV (receive states)

DC = 0 mV (otherwise)

V

XTAL1/XTAL2 VDC = 0.9 V at both pins

CPAR = 3 pF

≤ 1.0 Vpp

V

AC

V

DVDD

AVDD

DC = 1.8 V (all states, except P_ON, SLEEP,

and RESET)

DC = 0 mV (otherwise)

V

V

DC = 1.8 V (all states, except P_ON, SLEEP,

RESET, and TRX_OFF)

DC = 0 mV (otherwise)

V

DC level at pins RFP/RFN for various transceiver states

AC-coupling is required if an antenna with a DC path to ground is

used. Serial capacitance and capacitance of each pin to ground

must be < 100 pF.

DC level at pins XTAL1/XTAL2 for various transceiver states

Parasitic capacitance (C

additional load capacitance to the crystal.

DC level at pin DVDD for various transceiver states

Supply pins (voltage regulator output) for the digital 1.8 V voltage

domain. The outputs shall be bypassed by 1 µF.

DC level at pin AVDD for various transceiver states

Supply pin (voltage regulator output) for the analog 1.8 V voltage

domain. The outputs shall be bypassed by 1 µF.

AT86RF212

7.7.

) of the pins must be considered as

par

2.2.2 Digital Pins

The AT86RF212 provides a digital microcontroller interface. The interface comprises a

slave SPI (/SEL, SCLK, MOSI and MISO) and additional control signals (CLKM, IRQ,

SLP_TR, /RST and DIG2). The microcontroller interface is described in detail in chapter

4.

Additional digital output signals DIG1 … DIG4 are provided to control external blocks,

i.e. for Antenna Diversity RF switch control or as an RX/TX Indicator, see sections

9.4, respectively. After reset, these pins are connected to digital ground

and

(DIG1/DIG2) or analog ground (DIG3/DIG4).

2.2.2.1 Driver Strength Settings

The driver strength of all digital output pins (MISO, IRQ, DIG1, …, DIG4) and CLKM pin

can be configured using register 0x03 (TRX_CTRL_0), see

Table 2-3.

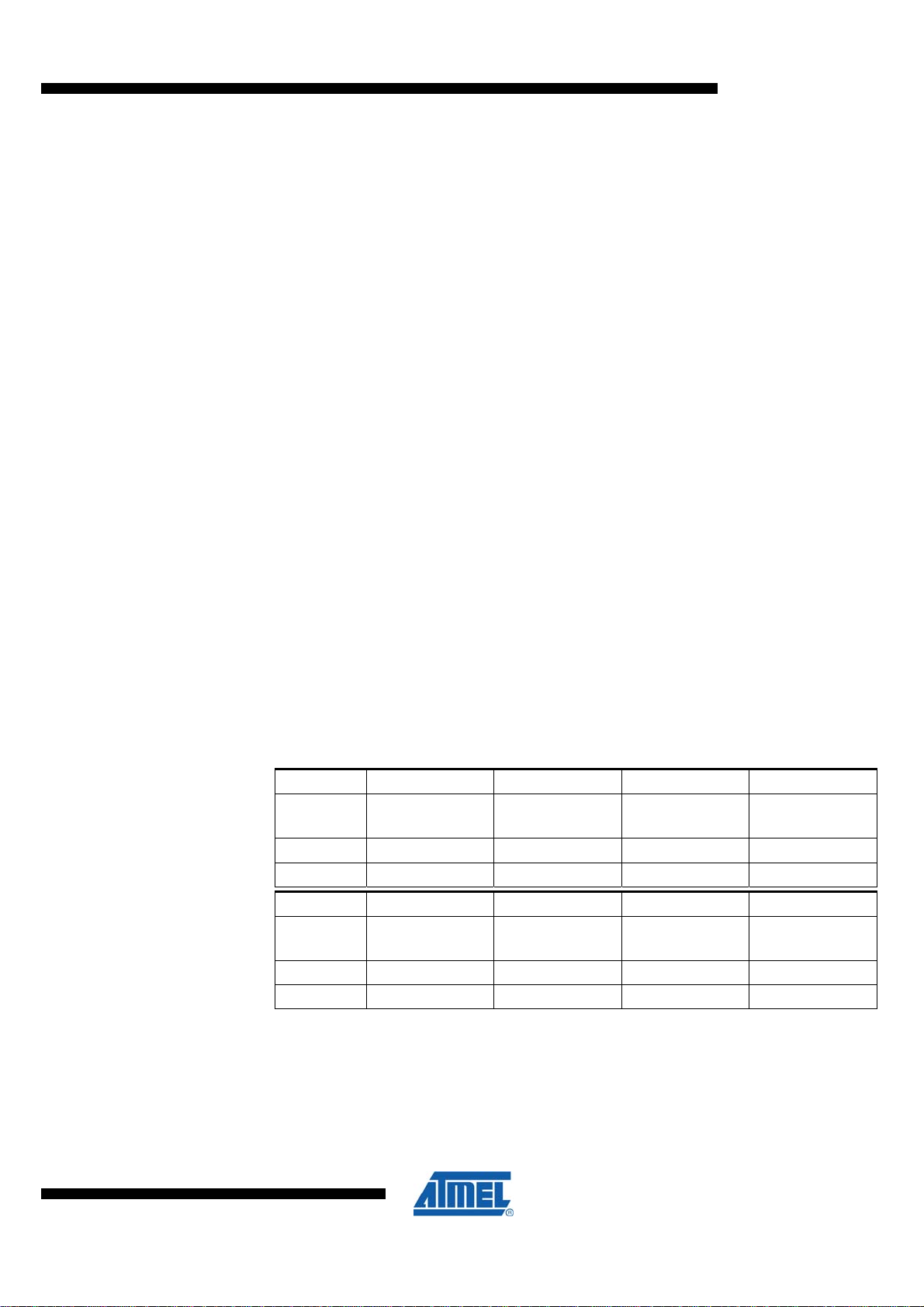

Table 2-3. Digital Output Driver Configuration

Pin Default Driver Strength Comment

MISO, IRQ, DIG1, …, DIG4 2 mA Adjustable to 2 mA, 4 mA, 6 mA, and 8 mA

CLKM 4 mA Adjustable to 2 mA, 4 mA, 6 mA, and 8 mA

The capacitive load should be as small as possible and not larger than 50 pF when

using the 2 mA minimum driver strength setting. Generally, the output driver strength

9.3

8168A-AVR-06/08

7

should be adjusted to the lowest possible value in order to keep the current

=

consumption and the emission of digital signal harmonics low.

2.2.2.2 Pull-up and Pull-down Configuration

Pulling resistors are internally connected to all digital input pins in radio transceiver

state P_ON, see section

configuration.

Table 2-4. Pull-up / Pull-Down Configuration of Digital Input Pins in P_ON State

In all other states including RESET, no pull-up or pull-down resistors are connected to

any of the digital input pins.

5.1.2.1. Table 2-4 summarizes the pull-up and pull-down

Pins H

/RST H

/SEL H

SCLK L

MOSI L

SLP_TR L

pull-up, L =ˆ pull-down

ˆ

2.2.2.3 Register Description

Register 0x03 (TRX_CTRL_0):

The TRX_CTRL_0 register controls the drive current of the digital output pads and the

CLKM clock rate.

Table 2-5. Register 0x03 (TRX_CTRL_0)

Bit 7 6 5 4

Name PAD_IO PAD_IO PAD_IO_CLKM PAD_IO_CLKM

Read/Write R/W R/W R/W R/W

Reset Value 0 0 0 1

Bit 3 2 1 0

Name CLKM_SHA_SEL CLK_CTRL CLKM_CTRL CLKM_CTRL

Read/Write R/W R/W R/W R/W

Reset Value 1 0 0 1

• Bit 7:6 – PAD_IO

These register bits set the output driver current of digital output pads, except CLKM.

Table 2-6. Digital Output Driver Strength

Register Bits Value Description

(1)

0

PAD_IO

Note: 1. Underlined values indicate reset settings.

2 mA

1 4 mA

2 6 mA

3 8 mA

8

AT86RF212

8168A-AVR-06/08

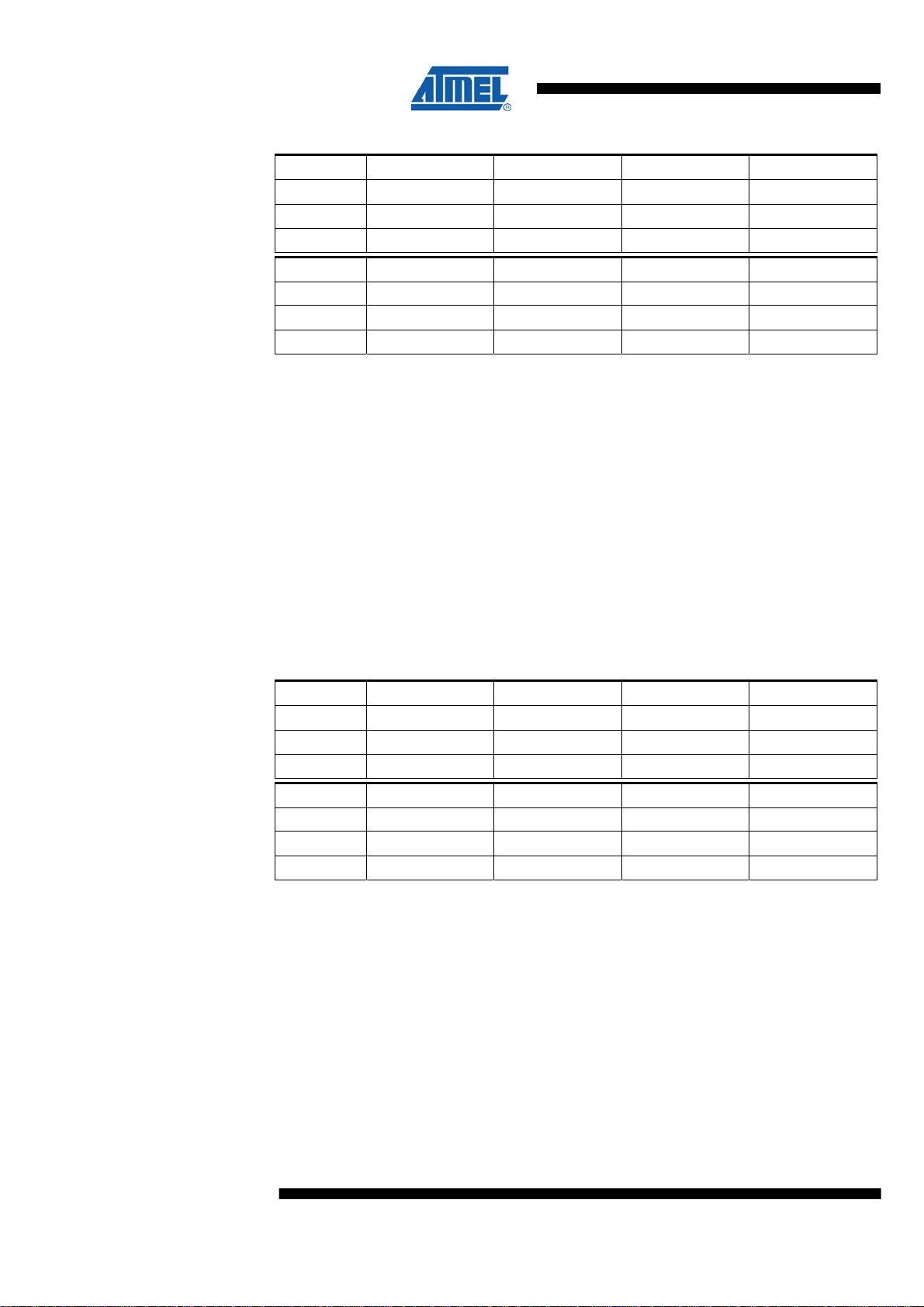

AT86RF212

• Bit 5:4 – PAD_IO_CLKM

These register bits set the output driver current of pin CLKM. Refer also to section

Table 2-7. CLKM Driver Strength

Register Bits Value Description

PAD_IO_CLKM

• Bit 3 – CLKM_SHA_SEL

Refer to section

• Bit 2:0 – CLKM_CTRL

Refer to section

0 2 mA

1 4 mA

2 6 mA

3 8 mA

7.7.

7.7.

7.7.

8168A-AVR-06/08

9

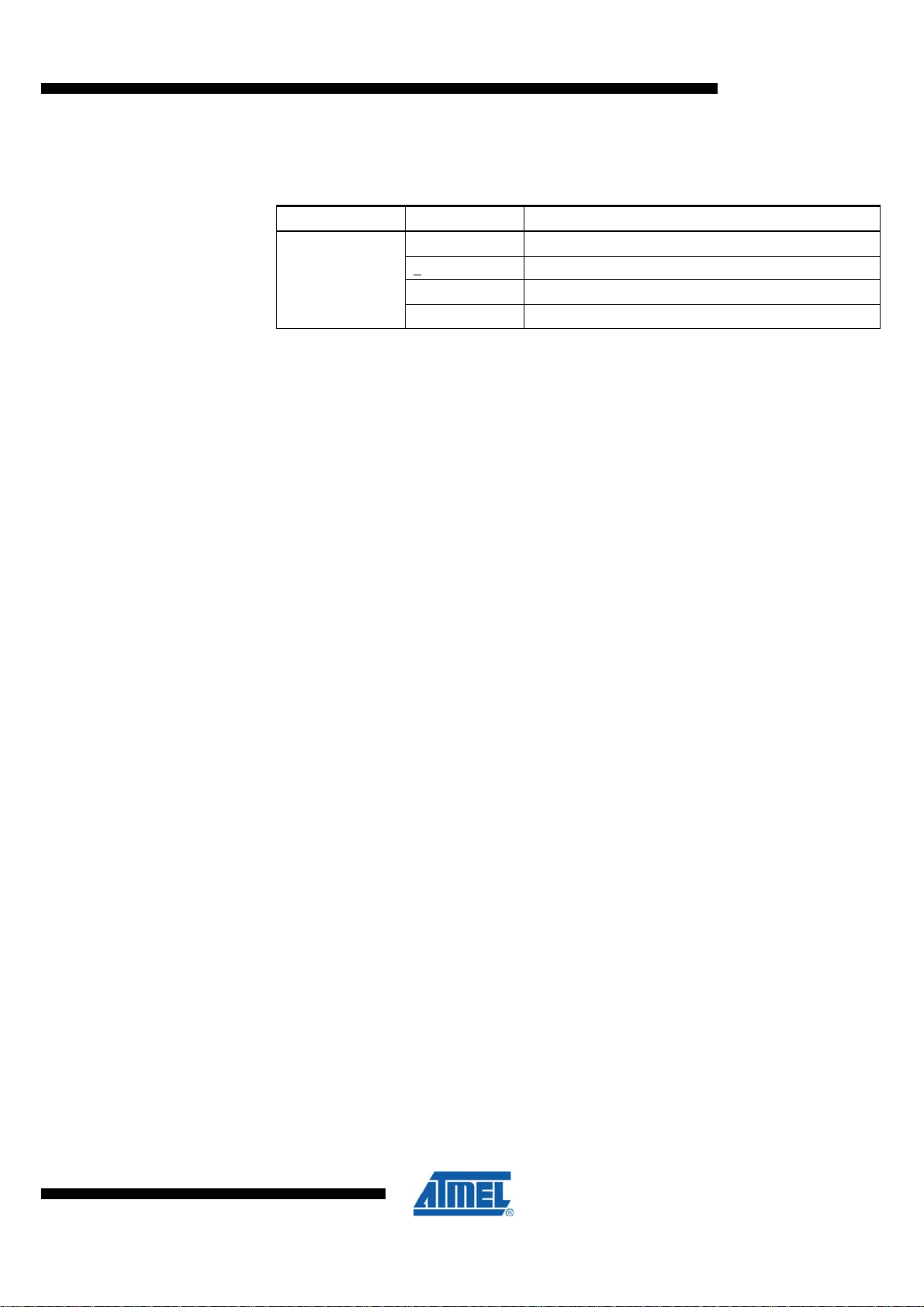

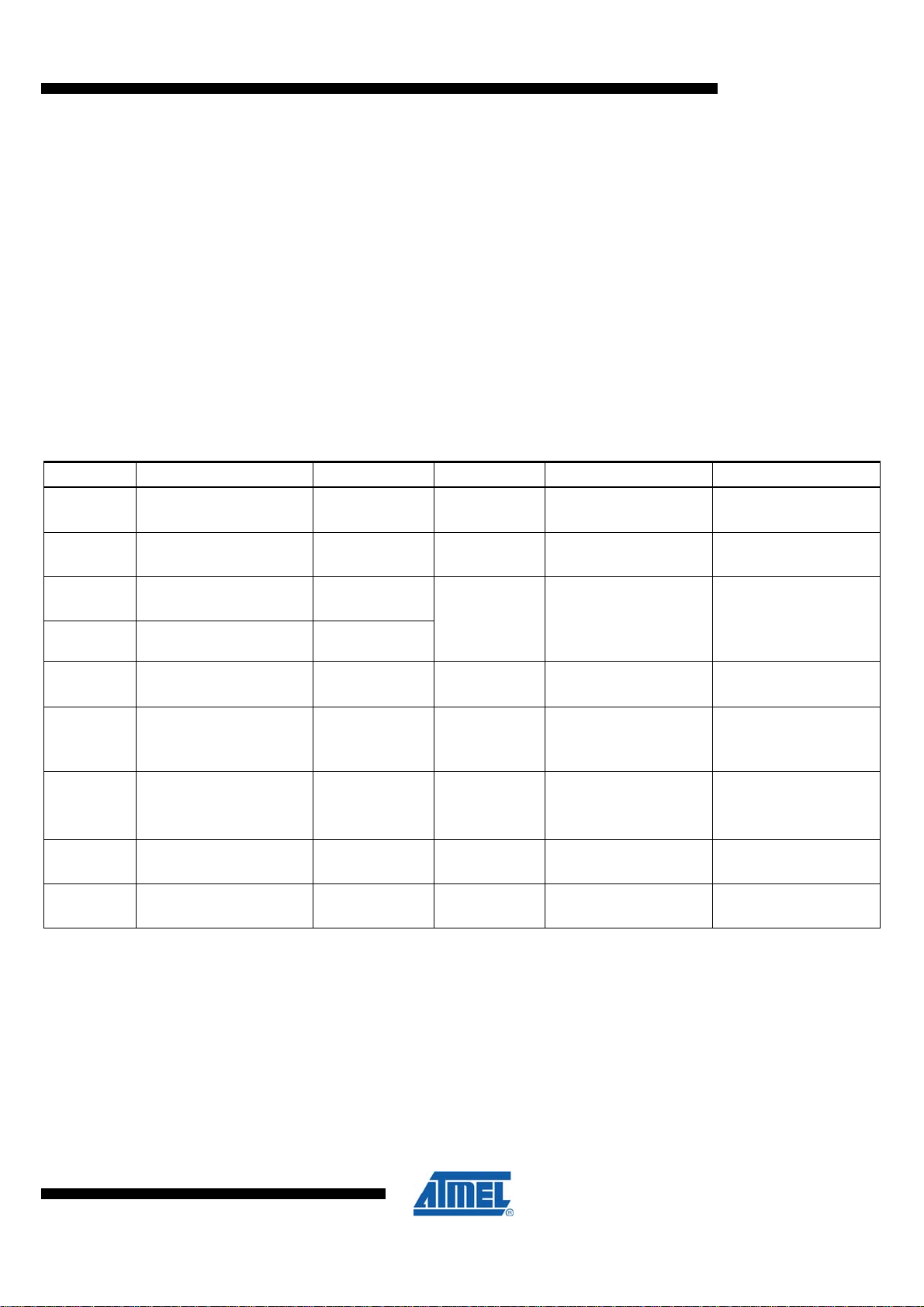

3 Application Circuits

3.1 Basic Application Schematic

A basic application schematic of the AT86RF212 with a single-ended RF connector is

shown in

differential RF port impedance using balun B1. The capacitors C1 and C2 provide AC

coupling of the RF input to the RF port. Regulatory rules like FCC 47 section 15.247,

ERC/REC 70-03 or ETSI EN 300 220 may require an external filter F1, depending on

used transmit power levels.

Figure 3-1. Basic Application Schematic

Figure 3-1. The 50 Ω single-ended RF input is transformed to the 100 Ω

V

CC

RF

F1

B1

C1

C2

1

2

3

4

5

6

7

8

DIG3

DIG4

AVSS

RFP

RFN

AVSS

DVSS

/RST

AVSS

DIG1

9

CB1

AVSS

AVSS

AT86RF212

DIG2

SLP_TR

10 11

CB2

12

CX1 CX2

AVDD

EVDD

DVSS

DVDD

13 14

AVSS

DVDD

XTAL

XTAL1

DEVDD

15 16

2526272829303132

XTAL2

MOSI

DVSS

MISO

SCLK

DVSS

CLKM

DVSS

IRQ

/SEL

24

23

22

21

20

19

18

17

Digital Interface

R1

C3

10

AT86RF212

CB3 CB4

The power supply bypass capacitors (CB2, CB4) are connected to the external analog

supply pin (EVDD, pin 28) and external digital supply pin (DEVDD, pin 15). Capacitors

CB1 and CB3 are bypass capacitors for the integrated analog and digital voltage

regulators to ensure stable operation. All bypass capacitors should be placed as close

8168A-AVR-06/08

AT86RF212

as possible to the pins and should have a low-resistance and low-inductance

connection to ground to achieve the best performance.

The crystal (XTAL), the two load capacitors (CX1, CX2), and the internal circuitry

connected to pins XTAL1 and XTAL2 form the crystal oscillator. To achieve the best

accuracy and stability of the reference frequency, large parasitic capacitances should

be avoided. Crystal lines should be routed as short as possible and not in proximity of

digital I/O signals. This is especially required for the High Data Rate Modes, refer to

chapter

degrade the system performance. Therefore, a low-pass filter (C3, R1) is placed close

to the CLKM output pin to reduce the emission of CLKM signal harmonics. This is not

needed if the CLKM pin is not used as a microcontroller clock source. In that case, the

output should be turned off during device initialization.

The ground plane of the application board should be separated into four independent

fragments, the analog, the digital, the antenna and the XTAL ground plane. The

exposed paddle shall act as the reference point of the individual grounds.

Table 3-1. Example Bill of Materials (BoM) for Basic Application Schematic

Designator Description Value Manufacturer Part Number Comment

B1 SMD balun 900 MHz Wuerth

F1 SMD low pass filter 900 MHz Wuerth

CB1, CB3 LDO VREG

bypass capacitor

CB2, CB4

CX1, CX2 Crystal load capacitor

C3 CLKM low-pass

R1 CLKM low-pass

XTAL Crystal CX-4025 16 MHz

Power supply bypass

capacitor

RF coupling capacitor

filter capacitor

filter resistor

7.1.4. Crosstalk from digital signals on the crystal pins or the RF pins can

748431090

JTI

JTI

1 μF

1

μF

12 pF

68 pF

2.2 pF AVX

680 Ω Designed for f

SX-4025 16 MHz

AVX

Murata

AVX

Murata

Epcos

Epcos

AVX

Murata

ACAL Taitien

Siward

0900BL18B100

748131009

0898LP18A035

0603YD105KAT2A

GRM188R61C105KA12D

06035A120JA

GRP1886C1H120JA01

B37930

B37920

06035A680JAT2A

06035A229DA

GRP1886C1H2R0DA01

XWBBPL-F-1

A207-011

X5R

(0603)

COG

(0603)

C0G 5% C1, C2

(0402 or 0603)

COG

(0603)

Designed for f

±0.5 pF 50 V

10% 16 V

5% 50 V

50 V

= 1 MHz

CLKM

= 1 MHz

CLKM

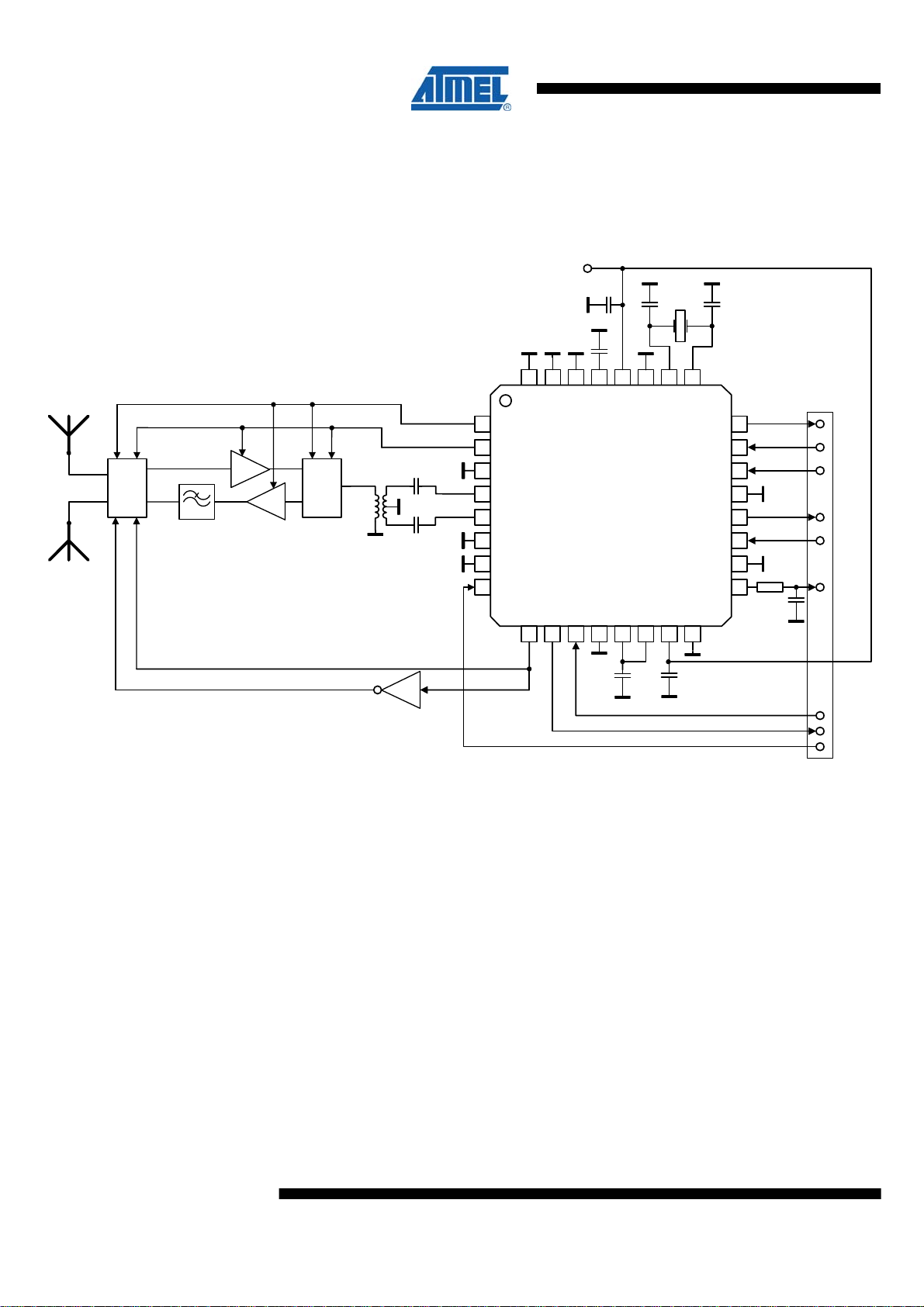

3.2 Extended Feature Set Application Schematic

For using the extended features

• Antenna Diversity uses pins DIG1/DIG2

• RX/TX Indicator uses pins DIG3/DIG4 section

• RX Frame Time Stamping uses pin DIG2 section

an extended application schematic is required.

All other extended features (see section

8168A-AVR-06/08

(1)

section 9.3

9) do not need an extended schematic.

9.4

9.5

11

An extended feature set application schematic illustrating the use of the AT86RF212

Extended Feature Set is shown in

additional hardware features combined, it is possible to use all features separately or in

various combinations.

Figure 3-2. Extended Feature Application Schematic

ANT0

N2

ANT1

SW2

RF-

LNA

Switch

F1

PA

N1

RF-

SW1

Switch

C1

B1

C2

1

2

3

4

5

6

7

8

DIG3

DIG4

AVSS

RFP

RFN

AVSS

DVSS

/RST

Figure 3-2. Although this example shows all

V

CC

CB2

CX1 CX2

XTAL

CB1

2526272829303132

AVSS

DIG1

9

AVSS

AVSS

AT86RF212

DIG2

SLP_TR

10 11

12

AVDD

DVSS

13 14

EVDD

DVDD

AVSS

DVDD

XTAL1

DEVDD

15 16

XTAL2

IRQ

/SEL

MOSI

DVSS

MISO

SCLK

DVSS

CLKM

DVSS

24

23

22

21

20

19

18

R1

17

C3

Digital Interface

CB3 CB4

In this example, a balun (B1) transforms the differential radio transceiver RF pins

(RFP/RFN) to a single ended RF signal, similar to the Basic Application Schematic;

refer to

Figure 3-1. The RF-Switches (SW1, SW2) separate between receive and

transmit path in an external RF front-end.

These switches are controlled by the RX/TX Indicator, represented by the differential

pin pair DIG3/DIG4, refer to

9.4.

During receive the corresponding microcontroller may search for the most reliable RF

signal path using an Antenna Diversity algorithm or stored statistic data of link signal

quality. One antenna is selected (SW2) by the Antenna Diversity RF switch control pin

(1)

DIG1

, the RF signal is amplified by an optional low-noise amplifier (N2) and fed to the

radio transceiver using the second RX/TX switch (SW1).

During transmit the AT86RF212 TX signal is amplified using an external PA (N1), low

pass filtered to suppress spurious harmonics emission and fed to the antennas via an

RF switch (SW2). In this example RF switch SW2 further supports Antenna Diversity

controlled by pin DIG1

Note: 1. DIG1/DIG2 can be used as a differential pin pair to control an RF switch if RX

Frame Time Stamping is not used, refer to sections

(1)

.

9.3 and 9.5, respectively.

12

AT86RF212

8168A-AVR-06/08

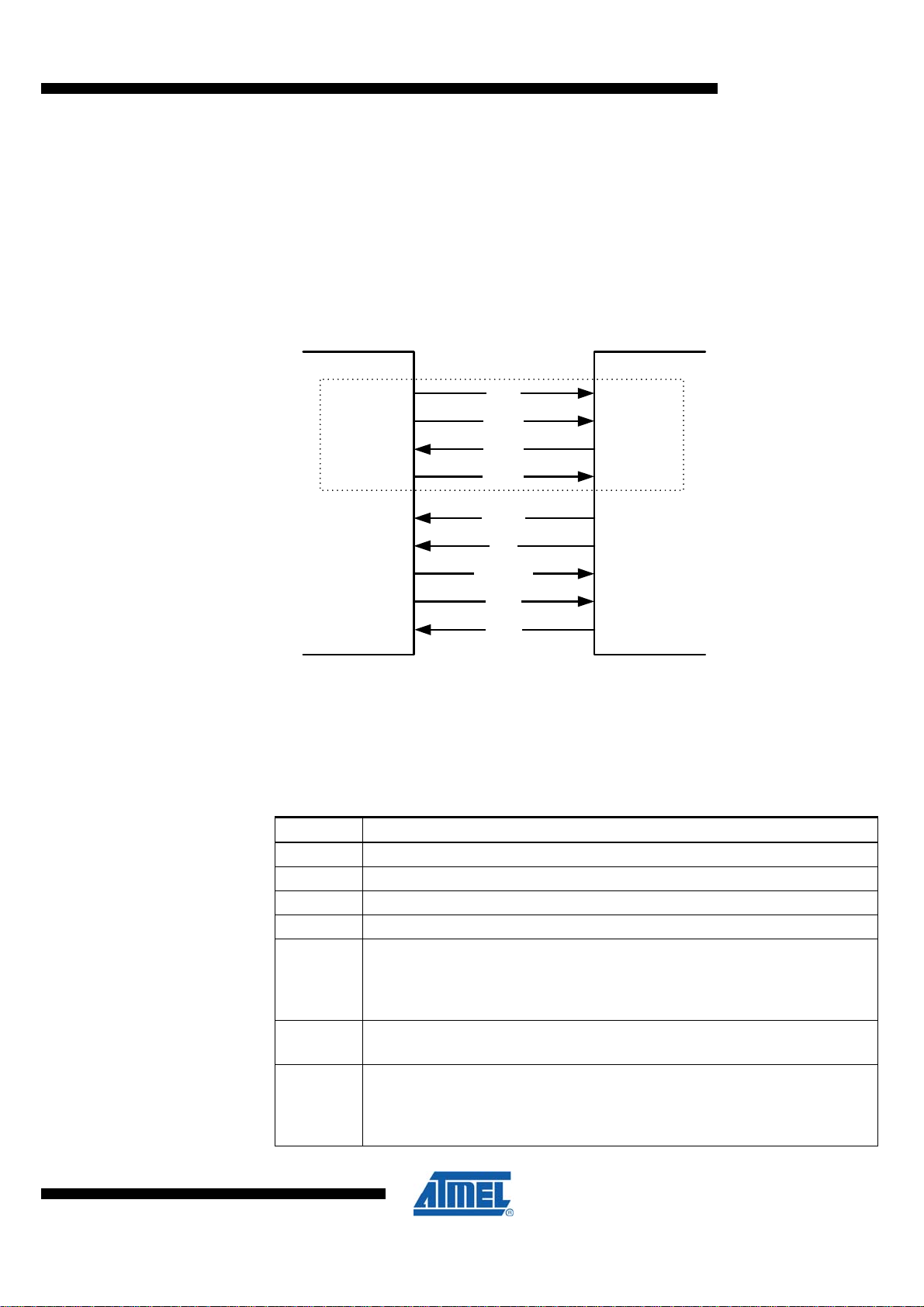

4 Microcontroller Interface

4.1 Overview

This section describes the AT86RF212 to microcontroller interface. The interface

comprises a slave SPI and additional control signals; see

and protocol are described below.

Figure 4-1. Microcontroller to AT86RF212 Interface

AT86RF212

Figure 4-1. The SPI timing

Microcontroller AT86RF212

/SEL /SEL

MOSI

MISO

SPI - Master

SCLK

GPIO1/CLK

GPIO2/IRQ

GPIO3

GPIO4

SPI

/SEL

MOSI

MISO

SCLK

CLKM

IRQ

SLP_TR

/RST

MOSI

MISO

SCLK

CLKM

IRQ

SLP_TR

/RST

SPI - Slave

DIG2GPIO5 DIG2

Microcontrollers with a master SPI such as Atmel’s AVR family interface directly to the

AT86RF212. The SPI is used for register, Frame Buffer, SRAM, and AES access. The

additional control signals are connected to the GPIO/IRQ interface of the

microcontroller.

Table 4-1 introduces the radio transceiver I/O signals and their functionality.

Table 4-1. Signal Description of Microcontroller Interface

Signal Description

/SEL SPI select signal, active low

MOSI SPI data (Master Output Slave Input) signal

MISO SPI data (Master Input Slave Output) signal

SCLK SPI clock signal

CLKM

IRQ Interrupt request signal, further used as:

SLP_TR

Clock output, refer to section

- microcontroller clock source

- high precision timing reference

- MAC timer reference

- Frame Buffer Empty indicator, refer to section

Multi purpose control signal, see section

- Sleep/Wakeup

- TX start

- disable/enable CLKM

7.7.4, usable as:

9.6.

4.6:

8168A-AVR-06/08

13

4.2 SPI Timing Description

Signal Description

/RST AT86RF212 reset signal, active low

Pin 17 (CLKM) can be used as a microcontroller master clock source. If the

microcontroller derives the SPI master clock (SCLK) directly from CLKM, the SPI

operates in synchronous mode, otherwise in asynchronous mode.

In synchronous mode, the maximum SCLK frequency is 8 MHz.

In asynchronous mode, the maximum SCLK frequency is limited to 7.5 MHz. The signal

at pin CLKM is not required to derive SCLK and may be disabled to reduce power

consumption and spurious emissions.

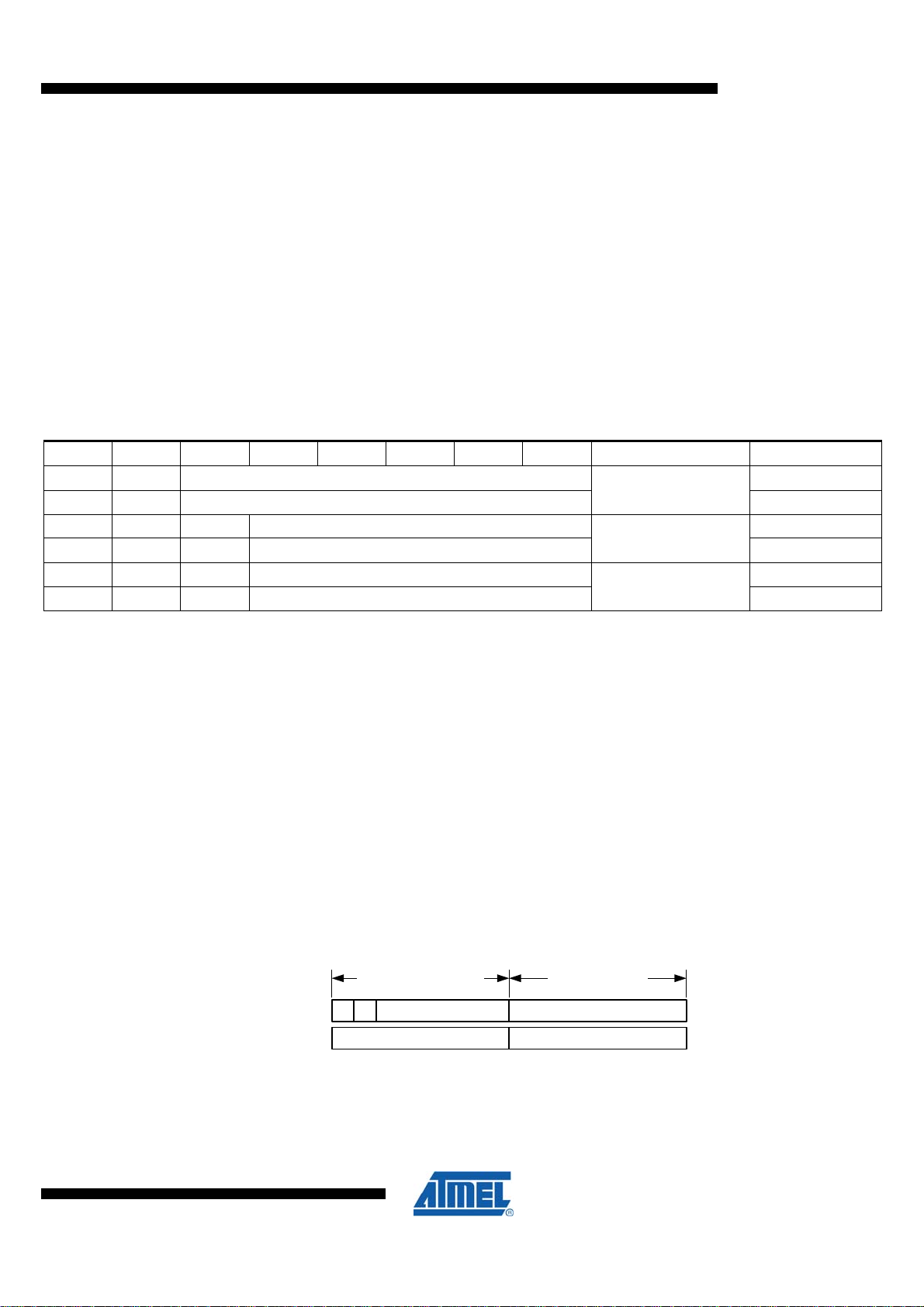

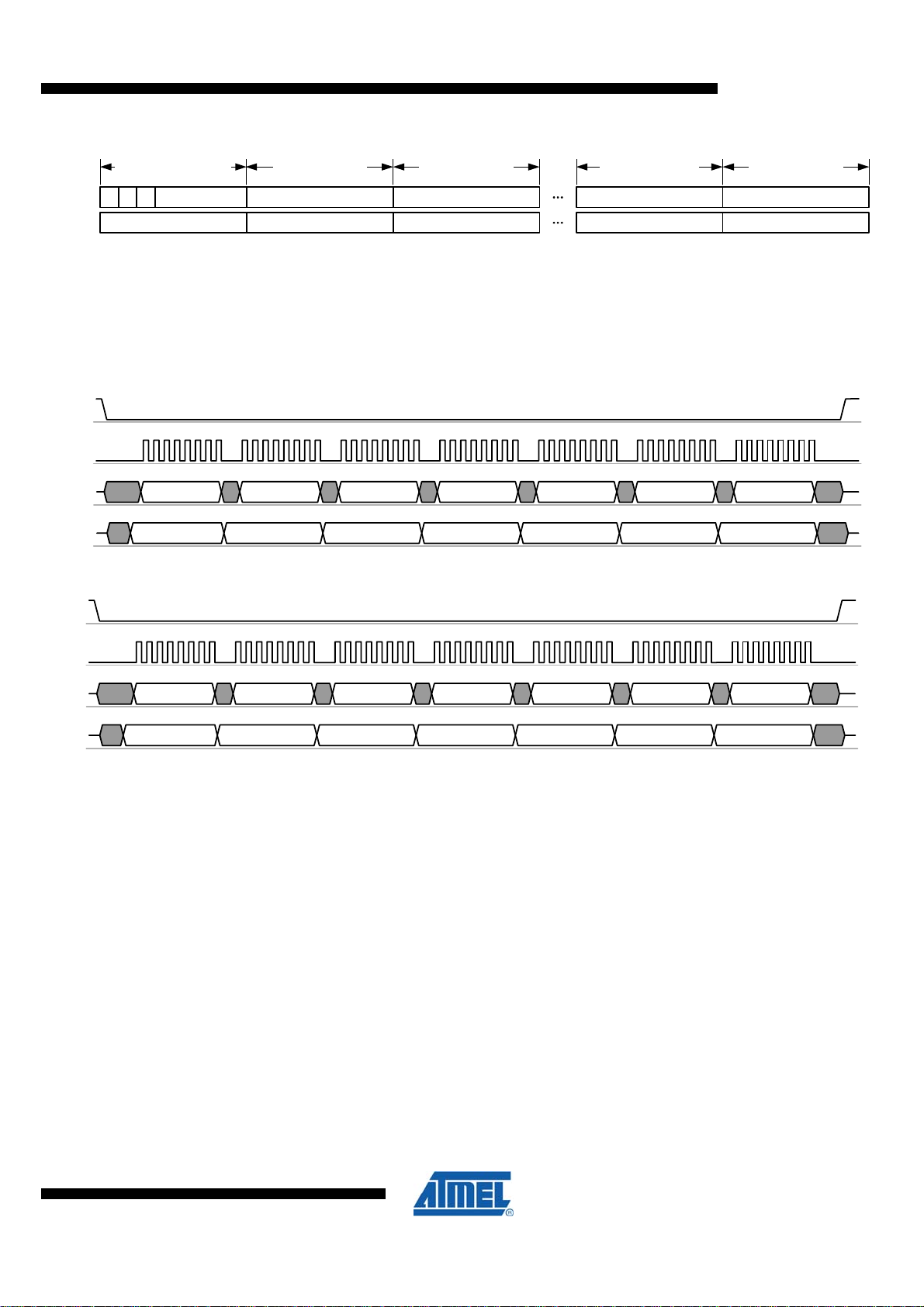

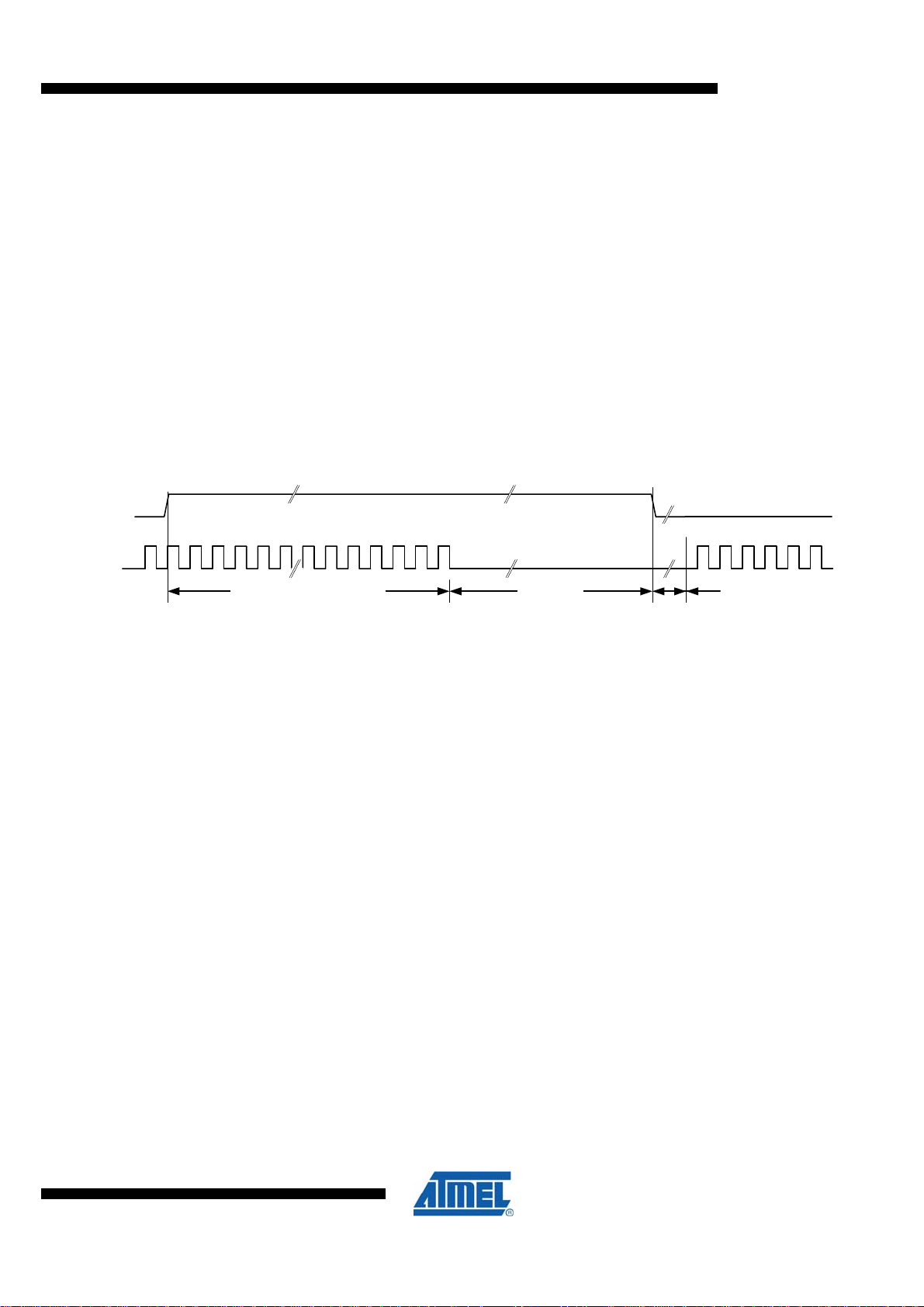

Figure 4-2 and Figure 4-3 illustrate the SPI timing and introduces its parameters. The

corresponding timing parameter definitions t

– t9 are defined in section 10.4.

1

Figure 4-2. SPI Timing, Global Map, and Definition of Timing Parameters t

/SEL

SCLK

MOSI

MISO

Figure 4-3. SPI Timing, Detailed Drawing of Timing Parameter t

/SEL

SCLK

MOSI

MISO

67 5 4 3 2 1 0 67 5 4 3 2 1 0

t

5

Bit 6 Bit 5 Bit 3 Bit 2 Bit 1 Bit 0Bit 4 Bit 6 Bit 5 Bit 3 Bit 2 Bit 1 Bit 0Bit 4Bit 7

t

t

4

3

Bit 7 Bit 6 Bit 5

t

1

Bit 7 Bit 6

t

2

Bit 7

to t4

1

, t6, t8 and t9

5

Bit 5

t

9

t

8

t

6

14

AT86RF212

The SPI is based on a byte-oriented protocol and is always a bidirectional

communication between master and slave. The SPI master starts the transfer by

asserting /SEL = L. Then the master generates eight SPI clock cycles to transfer one

byte to the radio transceiver (via MOSI). At the same time, the slave transmits one byte

to the master (via MISO). When the master wants to receive one byte of data from the

slave it must also transmit one byte to the slave. All bytes are transferred with MSB first.

An SPI transaction is finished by releasing /SEL = H.

/SEL = L enables the MISO output driver of the AT86RF212. The MSB of MISO is valid

after t

(see section 10.4, parameter 510.4.3) and is updated at each falling edge of

1

SCLK. If the driver is disabled, there is no internal pull-up resistor connected to it.

8168A-AVR-06/08

AT86RF212

Driving the appropriate signal level must be ensured by the master device or an

external pull-up resistor. Note, when both /SEL and /RST are active, the MISO output

driver is also enabled.

Referring to

Figure 4-2 and Figure 4-3 MOSI is sampled at the rising edge of the SCLK

signal and the output is set at the falling edge of SCLK. The signal must be stable

before and after the rising edge of SCLK as specified by t

parameters

510.4.5 and 510.4.6.

and t4, refer to section 10.4,

3

This SPI operational mode is commonly known as “SPI mode 0”.

4.3 SPI Protocol

Each SPI sequence starts with transferring a command byte from the SPI master via

MOSI (see

and additional mode-dependent information.

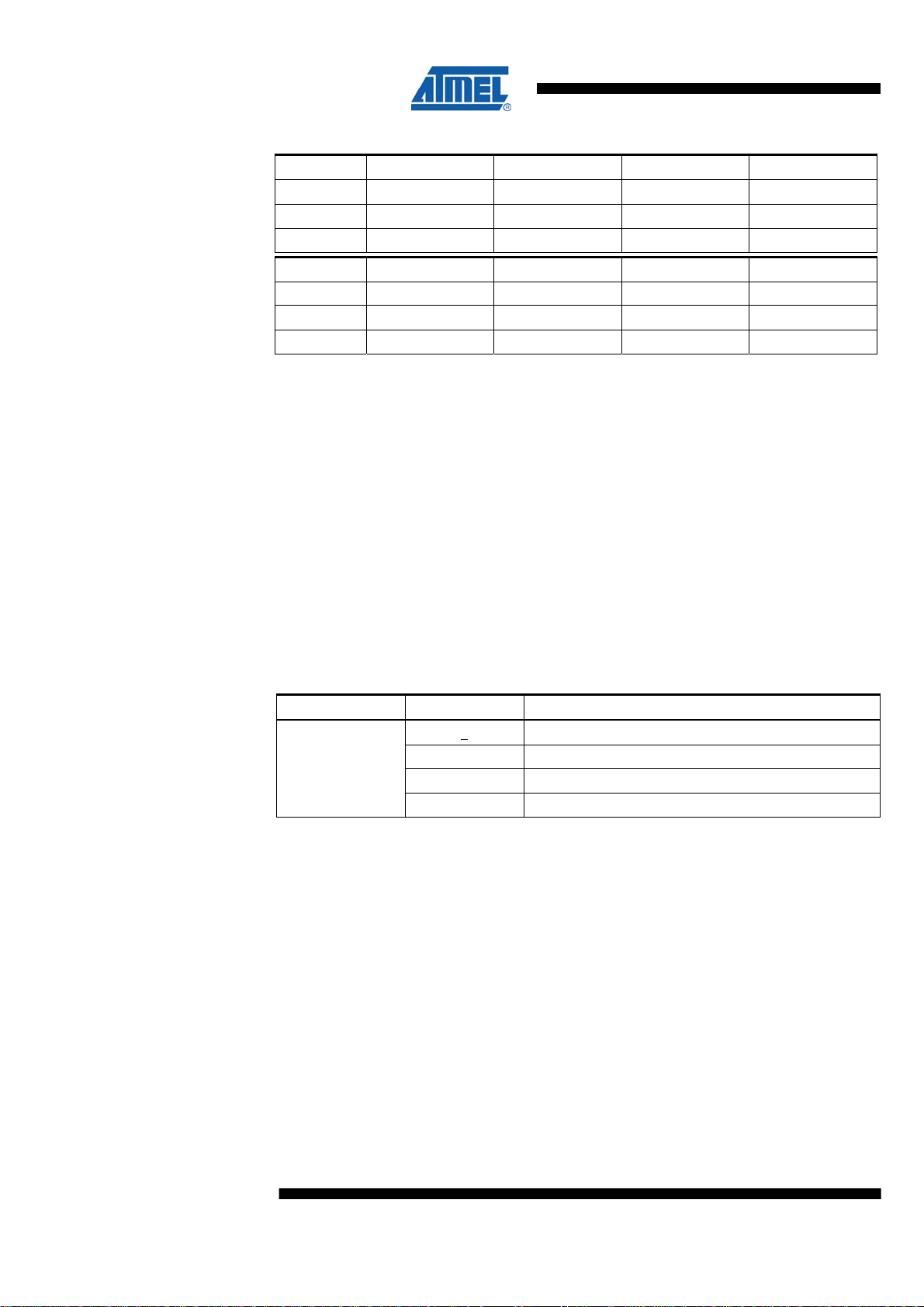

Table 4-2. SPI Command Byte Definition

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Access Mode Access Type

1 0 Register address [5:0] Read access

1 1 Register address [5:0]

0 0 1 Reserved Read access

0 1 1 Reserved

0 0

0 1

0

0

Each SPI transfer returns bytes back to the SPI master on MISO. The content of the

first byte is the PHY_STATUS field, see section

Table 4-2) with MSB first. This command byte defines the SPI access mode

Register access

Frame Buffer access

Reserved Read access

Reserved

SRAM access

Write access

Write access

Write access

4.4.

4.3.1 Register Access Mode

In

Figure 4-4 to Figure 4-14 and the following chapters logic values stated with XX on

MOSI are ignored by the radio transceiver, but need to have a valid logic level. Return

values on MISO stated as XX shall be ignored by the microcontroller.

The different access modes are described within the following sections.

A register access mode is a two-byte read/write operation initiated by /SEL = L. The first

transferred byte on MOSI is the command byte including an identifier bit (bit7 = 1), a

read/write select bit (bit 6), and a 6-bit register address.

On read access, the content of the selected register address is returned in the second

byte on MISO (see

Figure 4-4).

Figure 4-4. Register Access Mode – Read Access

byte 1 (command byte) byte 2 (data byte)

1 ADDRESS[5:0]0 XXMOSI

PHY_STATUS

(1)

READ DATA[7:0]MISO

Note: 1. Each SPI access can be configured to return PHY status information

(

PHY_STATUS) on MISO, refer to section 4.4.

8168A-AVR-06/08

15

On write access, the second byte transferred on MOSI contains the write data to the

selected address (see

Figure 4-5. Register Access Mode – Write Access

byte 1 (command byte) byte 2 (data byte)

1 ADDRESS[5:0]1 WRITE DATA[7:0]MOSI

Figure 4-6).

PHY_STATUS XXMISO

Each register access must be terminated by setting /SEL = H.

Figure 4-6 illustrates a typical SPI sequence for a register access sequence for write

and read respectively.

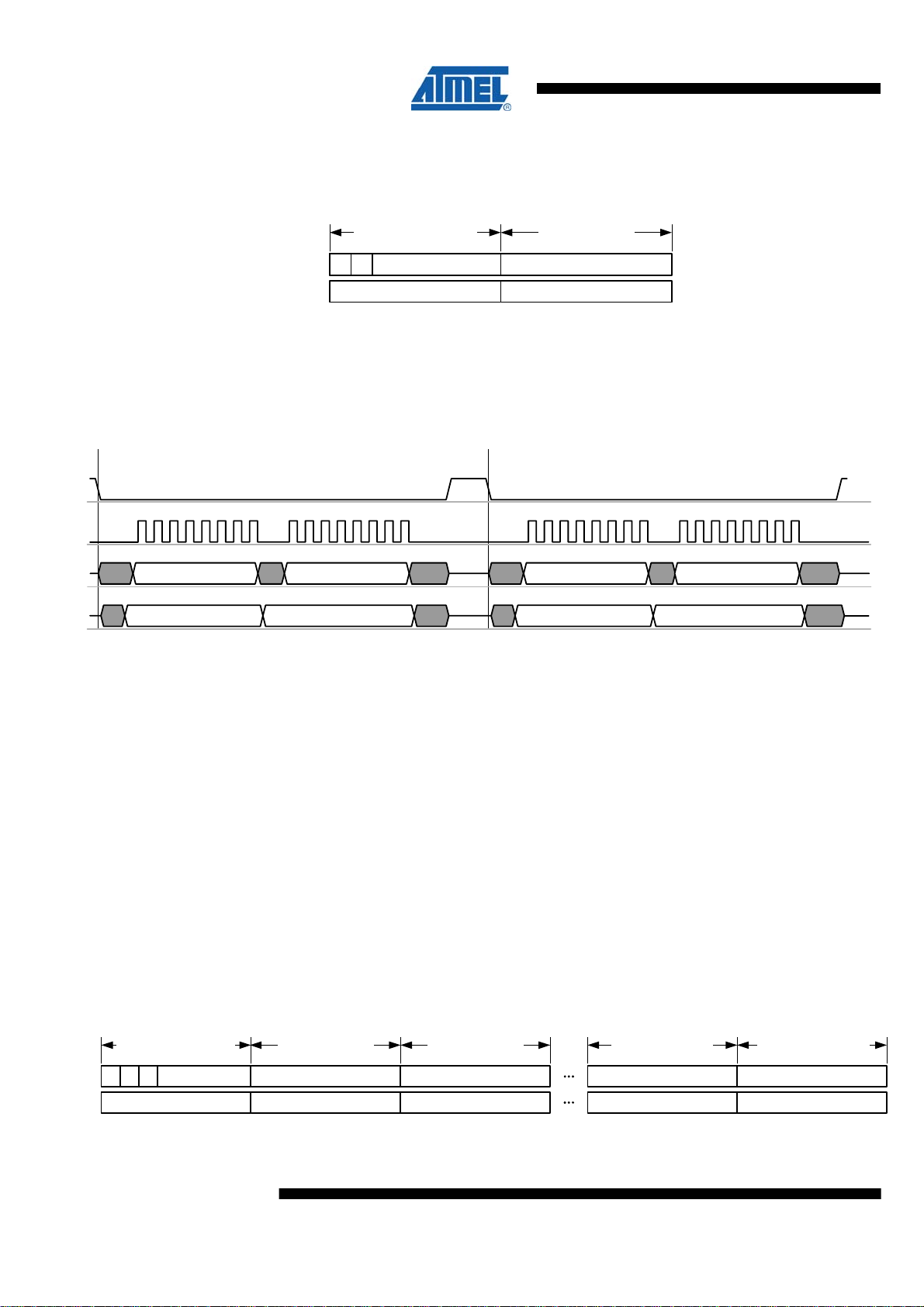

Figure 4-6. Example SPI Sequence – Register Access Mode

Register Write Access Register Read Access

/SEL

SCLK

MOSI

MISO

WRITE COMMAND WRITE DATA READ COMMAND XX

PHY_STATUS XX PHY_STATUS READ DATA

4.3.2 Frame Buffer Access Mode

The 128-byte Frame Buffer can hold the PHY service data unit (PSDU) data of one

IEEE 802.15.4 compliant RX or one TX frame of maximum length at a time. A detailed

description of the Frame Buffer can be found in section

IEEE 802.15.4 frame format can be found in section

7.4. An introduction to the

6.1.

Frame Buffer read and write accesses are used to read or write frame data (PSDU and

additional information) from or to the Frame Buffer. Each access starts with /SEL = L

followed by a command byte on MOSI. If this byte indicates a frame read or write

access, the next byte PHR indicates the frame length followed by the PSDU data, see

Figure 4-7 and Figure 4-8.

On Frame Buffer read access, PHY header (PHR) and PSDU are transferred via MISO

starting with the second byte. After the PSDU data, three more bytes are transferred

containing the link quality indication (LQI) value, the energy detection (ED) value and

the status information (RX_STATUS) of the received frame.

packet structure of a Frame Buffer read access. The structure of RX_STATUS is

described in

Table 4-3.

Figure 4-7. Packet Structure - Frame Read Access

byte 1 (command byte)

0 reserved[5:0]0MOSI

1 XX

PHY_STATUSMISO

byte 2 (data byte)

PHR[7:0]

16

AT86RF212

byte 3 (data byte)

XX

PSDU[7:0]

byte n-1 (data byte)

XX

ED[7:0]

Figure 4-7 illustrates the

byte n (data byte)

XX

RX_STATUS[7:0]

8168A-AVR-06/08

Table 4-3. RX_STATUS

Bit 7 6 5 4

Register 0x06, PHY_RSSI[7] 0x02, TRX_STATE[7:5]

Name RX_CRC_VALID TRAC_STATUS

Section 6.3.5 5.2.6

Bit 3 2 1 0

Register 0x0c, TRX_CTRL_2[3:0]

Name BPSK_OQPSK SUB_MODE OQPSK_DATA_RATE

Section 7.1.5

Note, the Frame Buffer read access can be terminated at any time without any

consequences by setting /SEL = H, e.g. after reading the frame length byte only. A

successive Frame Buffer read operation starts again at the PHR field.

On Frame Buffer write access the second byte transferred on MOSI contains the frame

length (PHR field) followed by the payload data (PSDU) as shown by

Figure 4-8. Packet Structure - Frame Write Access

byte 1 (command byte)

byte 2 (data byte)

byte 3 (data byte)

byte n-1 (data byte)

AT86RF212

Figure 4-8.

byte n (data byte)

0 reserved[5:0]1MOSI

1 PHR[7:0]

PHY_STATUSMISO

XX

PSDU[7:0]

XX

PSDU[7:0]

The number of bytes n for one frame buffer access is calculated as follows:

Read Access: n = 5 + frame_length

[PHY_STATUS, PHR, PSDU data, LQI, ED, and RX_STATUS]

Write Access: n = 2 + frame_length

[command byte, PHR, and PSDU data]

The maximum value of frame_length is 127 bytes. That means that n ≤ 132 for Frame

Buffer read and n ≤ 129 for Frame Buffer write accesses.

Each read or write of a data byte automatically increments the address counter of the

Frame Buffer until the access is terminated by setting /SEL = H.

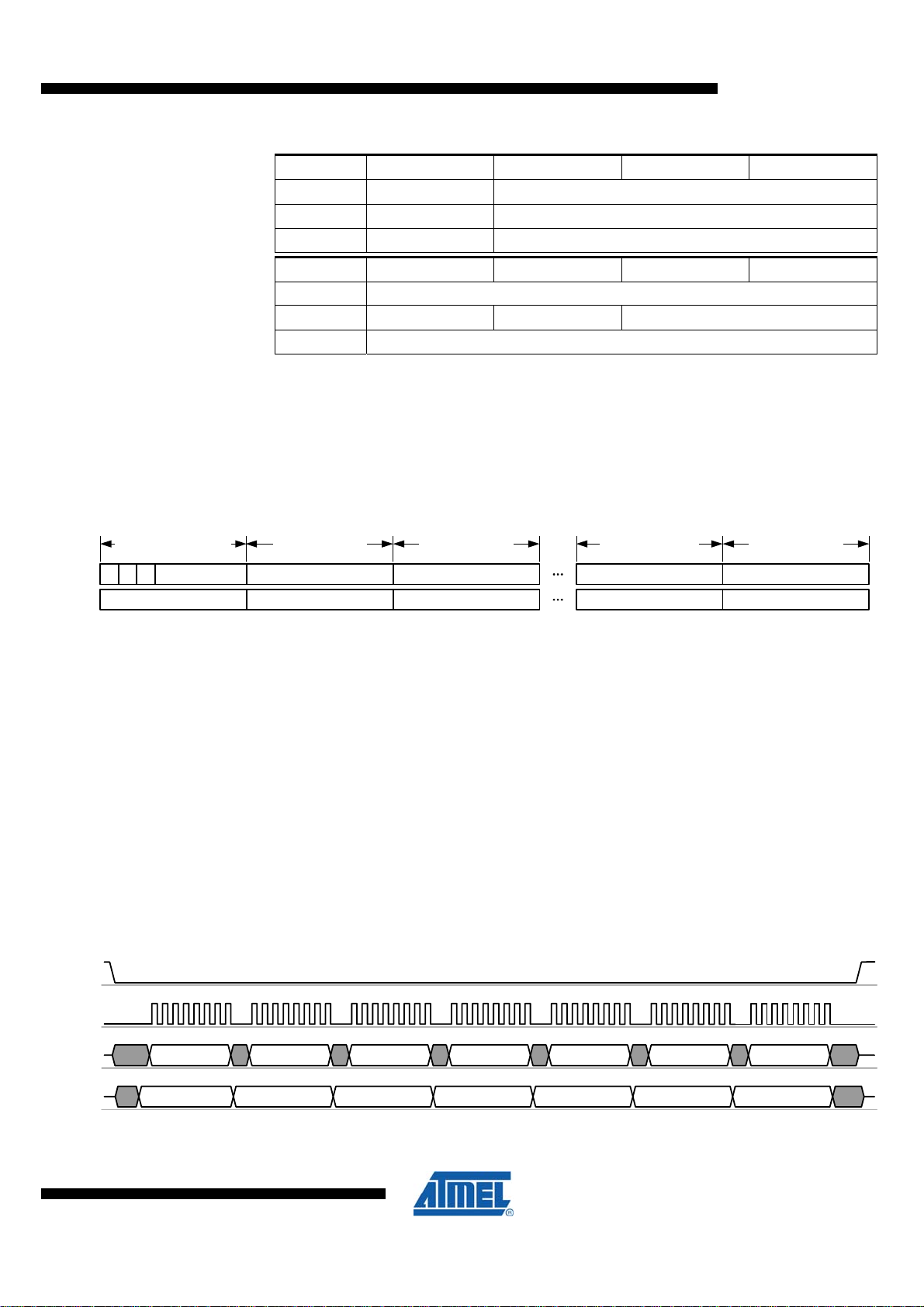

Figure 4-9 and Figure 4-10 illustrate an example SPI sequence of a Frame Buffer

access to read a frame with 2-byte PSDU and write a frame with 4-byte PSDU.

Figure 4-9. Example SPI Sequence - Frame Buffer Read of a Frame with 2-byte PSDU

/SEL

SCLK

XX

PSDU[7:0]

XX

MOSI

MISO

8168A-AVR-06/08

COMMAND XX XX XX XX XX

PHY_STATUS PHR PSDU 2PSDU 1 EDLQI

XX

RX_STATUS

17

Figure 4-10. Example SPI Sequence - Frame Buffer Write of a Frame with 4-byte PSDU

/SEL

SCLK

MOSI

MISO

COMMAND PHR PSDU 1 PSDU 2 PSDU 3 PSDU 4

PHY_STATUS XX XXXX XXXX

4.3.3 SRAM Access Mode

Access violations during a Frame Buffer read or write access are indicated by interrupt

IRQ_6 (TRX_UR). For further details, refer to section

7.4.

Notes

• The Frame Buffer is shared between RX and TX; therefore, the frame data are

overwritten by new incoming frames. If the TX frame data are to be retransmitted, it

must be ensured that no frame was received in the meanwhile.

• To avoid overwriting during receive Dynamic Frame Buffer Protection can be

enabled, refer to section

9.7.

• For exceptions, e.g. receiving acknowledgement frames in Extended Operating Mode

(TX_ARET) refer to section

5.2.4.

The SRAM access mode allows accessing dedicated bytes within the Frame Buffer.

This may reduce the SPI traffic.

During frame receive after occurrence of IRQ_2 (RX_START) an SRAM access can be

used to upload the PHR field while preserving Dynamic Frame Buffer Protection, see

9.7.

Each SRAM access starts with /SEL = L. The first transferred byte on MOSI shall be the

command byte and must indicate an SRAM access mode according to the definition in

Table 4-2. The following byte indicates the start address of the write or read access.

The address space is 0x00 to 0x7F for radio transceiver receive or transmit operations.

The security module (AES) uses an address space from 0x82 to 0x94, refer to

section

9.1.

On SRAM read access, one or more bytes of read data are transferred on MISO

starting with the third byte of the access sequence (see

Figure 4-11. Packet Structure – SRAM Read Access

byte 1 (command byte)

0 reserved[5:0]0MOSI

0 ADDRESS[7:0]

PHY_STATUSMISO

byte 2 (address)

XX

On SRAM write access, one or more bytes of write data are transferred on MOSI

starting with the third byte of the access sequence (see

read or write bytes beyond the SRAM buffer size.

byte 3 (data byte)

XX

DATA[7:0]

Figure 4-11).

byte n-1 (data byte)

XX

DATA[7:0]

Figure 4-12). Do not attempt to

byte n (data byte)

XX

DATA[7:0]

18

AT86RF212

8168A-AVR-06/08

Figure 4-12. Packet Structure – SRAM Write Access

byte 1 (command byte)

0 reserved[5:0]1MOSI

0 ADDRESS[7:0]

PHY_STATUSMISO

byte 2 (address)

XX

byte 3 (data byte)

DATA[7:0]

XX

byte n-1 (data byte)

DATA[7:0]

As long as /SEL = L, every subsequent byte read or byte write increments the address

counter of the Frame Buffer until the SRAM access is terminated by /SEL = H.

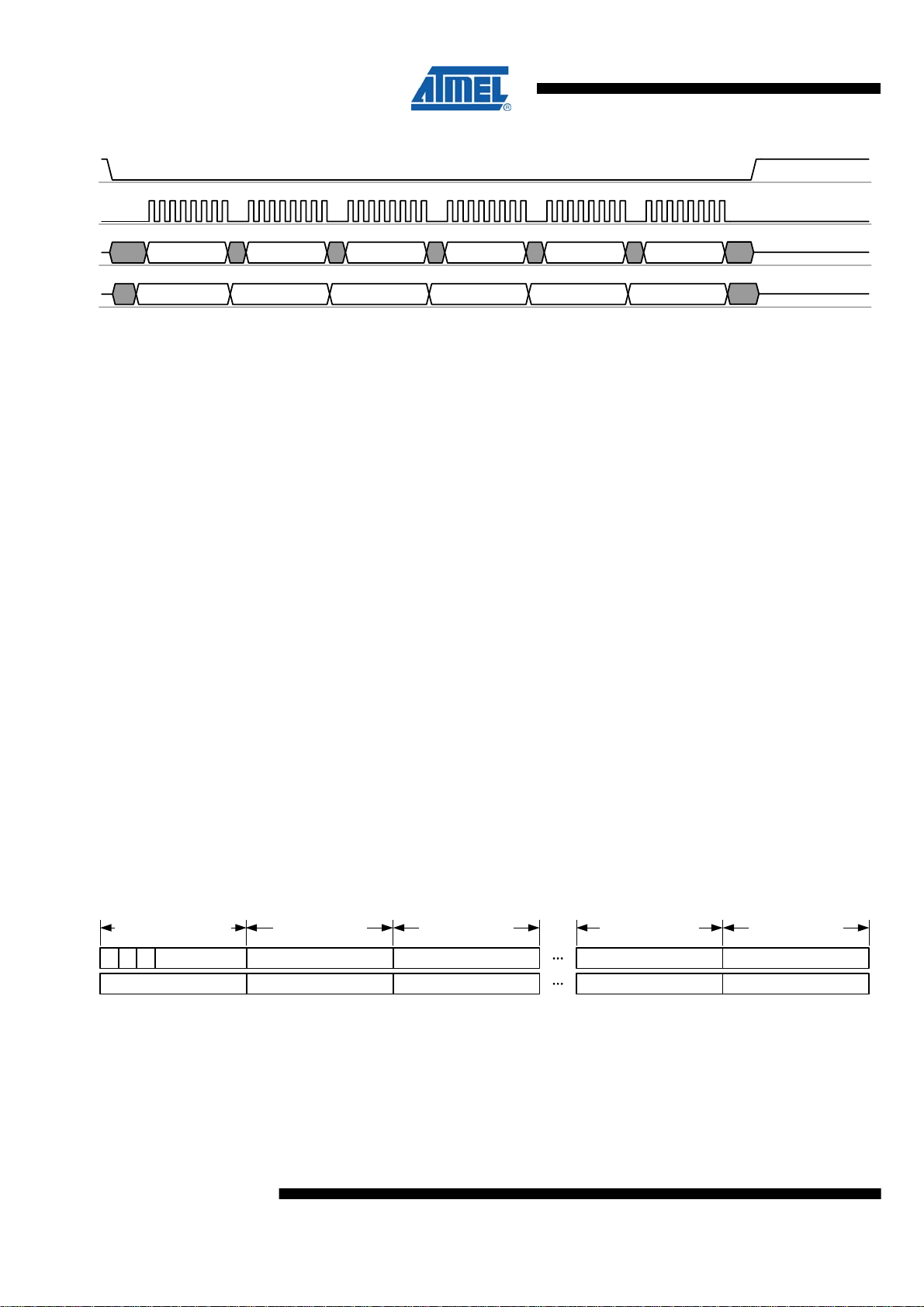

Figure 4-13 and Figure 4-14 illustrate an example SPI sequence of a SRAM access to

read and write a data package of 5-byte length respectively.

Figure 4-13. Example SPI Sequence – SRAM Read Access of a 5-byte Data Package

/SEL

SCLK

XX

AT86RF212

byte n (data byte)

DATA[7:0]

XX

MOSI

MISO

COMMAND ADDRESS XX XX XX XX

PHY_STATUS XX DATA 2DATA 1 DATA 4DATA 3

Figure 4-14. Example SPI Sequence – SRAM Write Access of a 5-byte Data Package

/SEL

SCLK

MOSI

MISO

COMMAND ADDRESS DATA 1 DATA 2 DATA 3 DATA 4

PHY_STATUS XX XXXX XXXX

Notes

• The SRAM access mode is not intended to be used as an alternative to the Frame

Buffer access modes (see section

4.3.2).

• Frame Buffer access violations are not indicated by a TRX_UR interrupt when using

the SRAM access mode, for further details refer to section

4.4 PHY Status Information

7.4.3.

XX

DATA 5

DATA 5

XX

Each SPI access can be configured to return status information of the radio transceiver

(PHY_STATUS) to the microcontroller using the first byte of the data transferred via MISO.

The content of the radio transceiver status information can be configured using register

bits SPI_CMD_MODE (register 0x04, TRX_CTRL_1). After reset, the content on the

first byte send on MISO to the microcontroller is set to 0x00.

4.4.1 Register Description – SPI Control

Register 0x04 (TRX_CTRL_1):

The TRX_CTRL_1 register is a multi purpose register to control various operating

modes and settings of the radio transceiver.

8168A-AVR-06/08

19

Table 4-4. Register 0x04 (TRX_CTRL_1)

Bit 7 6 5 4

Name PA_EXT_EN IRQ_2_EXT_EN TX_AUTO_CRC_ON RX_BL_CTRL

Read/Write R/W R/W R/W R/W

Reset Value 0 0 1 0

Bit 3 2 1 0

Name SPI_CMD_MODE SPI_CMD_MODE IRQ_MASK_MODE IRQ_POLARITY

Read/Write R/W R/W R/W R/W

Reset Value 0 0 0 0

• Bit 7 – PA_EXT_EN

Refer to section

• Bit 6 – IRQ2_EXT_EN

Refer to section

• Bit 5 – TX_AUTO_CRC_ON

Refer to section

9.4.3.

9.5.2.

6.3.5.

• Bit 4 – RX_BL_CTRL

Refer to section

• Bit 3:2 – SPI_CMD_MODE

Each SPI transfer returns bytes back to the SPI master. The content of the first byte can

be configured using register bits SPI_CMD_MODE. The transfer of the following status

information can be configured as follows:

Table 4-5. PHY Status Information

Register Bits Value Description

SPI_CMD_MODE

• Bit 1 – IRQ_MASK_MODE

Refer to section

• Bit 0 – IRQ_POLARITY

Refer to section

4.5 Radio Transceiver Identification

9.6.2.

4.7.2.

4.7.2.

0 default (empty, all bits 0x00)

1 monitor TRX_STATUS register see 5.1.5

2 monitor PHY_RSSI register see 6.4

3 monitor IRQ_STATUS register see

4.7

20

AT86RF212

The AT86RF212 can be identified by four registers. One register contains a unique part

number and one register the corresponding version number. Additional two registers

contain the JEDEC manufacture ID.

8168A-AVR-06/08

4.5.1 Register Description

AT86RF212

Register 0x1C (PART_NUM):

Table 4-6. Register 0x1C (PART_NUM)

Bit 7 6 5 4 3 2 1 0

Name PART_NUM[7:0]

Read/Write R

Reset Value 0 0 0 0 0 1 1 1

• Bit 7:0 – PART_NUM

This register contains the radio transceiver part number.

Table 4-7. Radio Transceiver Part Number

Register Bits Value State Description

PART_NUM 7 AT86RF212 part number

Register 0x1D (VERSION_NUM):

Table 4-8. Register 0x1D (VERSION_NUM)

Bit 7 6 5 4 3 2 1 0

Name VERSION_NUM[7:0]

Read/Write R

Reset Value 0 0 0 0 0 0 0 1

• Bit 7:0 – VERSION_NUM

This register contains the radio transceiver version number.

Table 4-9. Radio Transceiver Version Number

Register Bits Value State Description

VERSION_NUM 1 Revision A

Register 0x1E (MAN_ID_0):

Table 4-10. Register 0x1E (MAN_ID_0)

Bit 7 6 5 4 3 2 1 0

Name MAN_ID_0[7:0]

Read/Write R

Reset Value 0 0 0 1 1 1 1 1

• Bit 7:0 – MAN_ID_0

Bits [7:0] of the 32-bit JEDEC manufacturer ID are stored in register bits MAN_ID_0.

Bits [15:8] are stored in register 0x1F (MAN_ID_1). The highest 16 bits of the ID are not

stored in registers.

Table 4-11. JEDEC Manufacturer ID – Bits [7:0]

Register Bits Value State Description

MAN_ID_0 0x1F Atmel JEDEC manufacturer ID,

Bits [7:0] of 32 bit manufacturer ID: 00 00 00 1F

8168A-AVR-06/08

21

Register 0x1F (MAN_ID_1):

Table 4-12. Register 0x1F (MAN_ID_1)

Bit 7 6 5 4 3 2 1 0

Name MAN_ID_1[7:0]

Read/Write R

Reset Value 0 0 0 0 0 0 0 0

• Bit 7:0 – MAN_ID_1

Bits [15:8] of the 32-bit JEDEC manufacturer ID are stored in register bits MAN_ID_1.

Bits [7:0] are stored in register 0x1E (MAN_ID_0). The higher 16 bits of the ID are not

stored in registers.

Table 4-13. JEDEC Manufacturer ID – Bits [15:8]

Register Bits Value State Description

MAN_ID_1 0x00 Atmel JEDEC manufacturer ID

Bits [15:8] of 32 bit manufacturer ID: 00 00 00

1F

4.6 Sleep/Wake-up and Transmit Signal (SLP_TR)

Pin 11 (SLP_TR) is a multi-functional pin. Its function relates to the current state of the

AT86RF212 and is summarized in

explained in detail in section

5.

Table 4-14. SLP_TR Multi-functional Pin

Transceiver Status Function Transition Description

PLL_ON TX start L Æ H Starts frame transmission

TX_ARET_ON TX start L Æ H Starts TX_ARET transaction

BUSY_RX_AACK TX start L Æ H

TRX_OFF Sleep L Æ H Takes the radio transceiver into SLEEP state, CLKM disabled

SLEEP Wakeup H Æ L Takes the radio transceiver back into TRX_OFF state, level sensitive

RX_ON Disable CLKM L Æ H Takes the radio transceiver into RX_ON_NOCLK state and disables CLKM

RX_ON_NOCLK Enable CLKM H Æ L Takes the radio transceiver into RX_ON state and enables CLKM

RX_AACK_ON Disable CLKM L Æ H

RX_AACK_ON_NOCLK Enable CLKM H Æ L Takes the radio transceiver into RX_AACK_ON state and enables CLKM

Starts ACK transmission during RX_AACK slotted operation, see section

5.2.3.5.

Takes the radio transceiver into RX_AACK_ON_NOCLK state and

disables CLKM

In states PLL_ON and TX_ARET_ON, pin SLP_TR is used as trigger input to initiate a

TX transaction. Here pin SLP_TR is sensitive on rising edge only.

Table 4-14. The radio transceiver states are

22

AT86RF212

After initiating a state change by a rising edge at pin SLP_TR in radio transceiver states

TRX_OFF, RX_ON or RX_AACK_ON, the radio transceiver remains in the new state as

long as the pin is logical high and returns to the preceding state with the falling edge.

8168A-AVR-06/08

AT86RF212

SLEEP state

The SLEEP state is used when radio transceiver functionality is not required, and thus

the AT86RF212 can be powered down to reduce the overall power consumption.

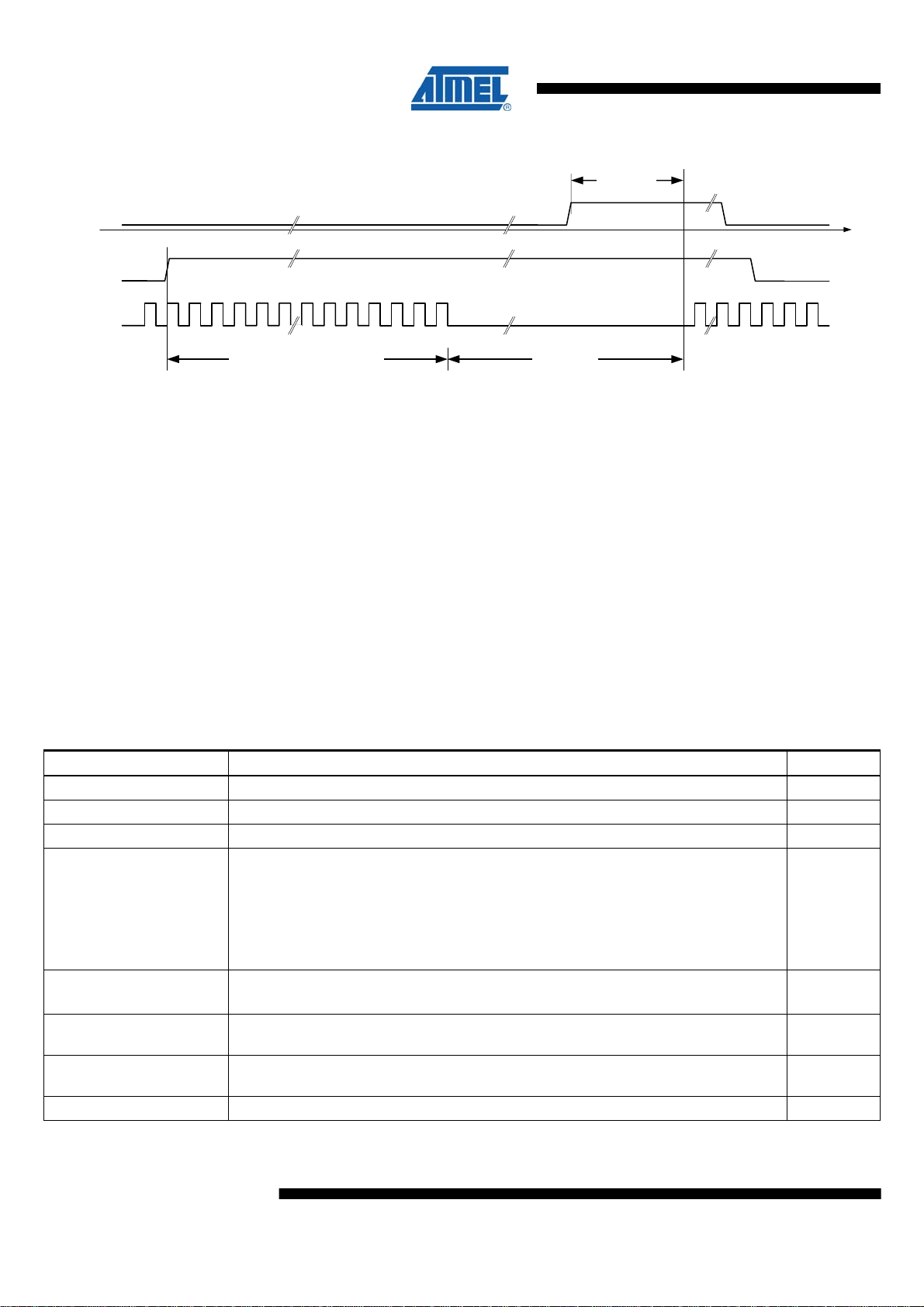

A power-down scenario is shown in

Figure 4-15. When the radio transceiver is in

TRX_OFF state the microcontroller forces the AT86RF212 to SLEEP by setting

SLP_TR = H. If pin 17 (CLKM) provides a clock to the microcontroller this clock is

switched off after 35 clock cycles. This enables a microcontroller in a synchronous

system to complete its power-down routine and prevent deadlock situations. The

AT86RF212 awakes when the microcontroller releases pin SLP_TR. This concept

provides the lowest possible power consumption.

The CLKM clock frequency settings for CLKM_CTRL values 6 and 7 are not intended to

directly clock the microcontroller. When using these clock rates, CLKM is turned off

immediately when entering SLEEP state.

Figure 4-15. Sleep and Wake-up Initiated by Asynchronous Microcontroller Timer

SLP_TR

CLKM

35 CLKM clock cycles CLKM off

Note: Timing figure t

refer to Table 5-1.

TR2

t

TR2

async timer elapses

(microcontroller)

RX_ON and RX_AACK_ON states

For synchronous systems, where CLKM is used as a microcontroller clock source and

the SPI master clock (SCLK) is directly derived from CLKM, the AT86RF212 supports

an additional power-down mode for receive operating states (RX_ON and

RX_AACK_ON).

If an incoming frame is expected and no other applications are running on the

microcontroller, it can be powered down without missing incoming frames.

This can be achieved by a rising edge on pin SLP_TR that turns off the CLKM. Then

the radio transceiver state changes from RX_ON or RX_AACK_ON (Extended

Operating Mode) to RX_ON_NOCLK or RX_AACK_ON_NOCLK respectively.

In case that a frame is received (e.g. indicated by an IRQ_2 (RX_START) interrupt) the

clock output CLKM is automatically switched on again.

This scenario is shown in

Figure 4-16. In RX_ON state, the clock at pin 17 (CLKM) is

switched off after 35 clock cycles when setting the pin SLP_TR = H.

The CLKM clock frequency settings for CLKM_CTRL values 6 and 7 are not intended to

directly clock the microcontroller. When using these clock rates, CLKM is turned off

immediately when entering RX_ON_NOCLK and RX_AACK_ON_NOCLK respectively.

In states RX_(AACK)_ON_NOCLK and RX_(AACK)_ON, the radio transceiver current

consumptions are equivalent. However, the RX_(AACK)_ON_NOCLK current

consumption is reduced by the current required for driving pin 17 (CLKM).

8168A-AVR-06/08

23

Figure 4-16. Wake-Up Initiated by Radio Transceiver Interrupt

o

IRQ

SLP_TR

CLKM

4.7 Interrupt Logic

4.7.1 Overview

radio transceiver

typ. 5 µs

IRQ issued

35 CLKM clock cycles CLKM off

The AT86RF212 supports 8 interrupt requests as listed in

Table 4-15. Each interrupt is

enabled by setting the corresponding bit in the interrupt mask register

0x0E (IRQ_MASK). Internally, each pending interrupt is stored in a separate bit of the

interrupt status register. All interrupt events are OR-combined to a single external

interrupt signal (IRQ, pin 24). If an interrupt is issued (pin IRQ = H), the microcontroller

shall read the interrupt status register 0x0F (IRQ_STATUS) to determine the source of

the interrupt. A read access to this register clears the interrupt status register and thus

the IRQ pin, too.

Interrupts are not cleared automatically when the event that caused them vanishes.

Exceptions are IRQ_0 (PLL_LOCK) and IRQ_1 (PLL_UNLOCK) because the

occurrence of one clears the other.

The supported interrupts for the Basic Operating Mode are summarized in

Table 4-15.

Table 4-15. Interrupt Description in Basic Operating Mode

IRQ Name Description Section

IRQ_7 (BAT_LOW) Indicates a supply voltage below the programmed threshold. 7.6.4

IRQ_6 (TRX_UR) Indicates a Frame Buffer access violation. 7.4.3

IRQ_5 (AMI) Indicates address matching. 6.2

IRQ_4 (CCA_ED_READY) Multi-functional interrupt:

1. AWAKE_END:

• Indicates radio transceiver reached TRX_OFF state at the end of P_ON Ö

TRX_OFF and SLEEP

2. CCA_ED_READY:

• Indicates the end of a CCA or ED measurement

IRQ_3 (TRX_END) RX: Indicates the completion of a frame reception.

TX: Indicates the completion of a frame transmission.

IRQ_2 (RX_START)

IRQ_1 (PLL_UNLOCK)

IRQ_0 (PLL_LOCK) Indicates PLL lock. 7.8.5

Indicates the start of a PSDU reception. The TRX_STATE changes to BUSY_RX, the

PHR is valid to be read from Frame Buffer.

Indicates PLL unlock. If the radio transceiver is in BUSY_TX / BUSY_TX_ARET state,

the PA is turned off immediately.

Ö TRX_OFF state transition

5.1.2.3

6.6.4

5.1.3

5.1.3

7.8.5

24

AT86RF212

8168A-AVR-06/08

AT86RF212

The interrupt IRQ_4 has two meanings, depending on the current radio transceiver

state, refer to register 0x01 (TRX_STATUS).

After P_ON, SLEEP, or RESET, the radio transceiver issues an interrupt

IRQ_4 (AWAKE_END) when it enters state TRX_OFF.

The second meaning is only valid for receive states. If the microcontroller initiates an

ED or CCA measurement, the completion of the measurement is indicated by interrupt

IRQ_4 (CCA_ED_READY), refer to sections

After P_ON or RESET all interrupts are disabled. During radio transceiver initialization it

is recommended to enable IRQ_4 (AWAKE_END) to be notified once the TRX_OFF

state is entered. Note that AWAKE_END interrupt can usually not be seen when the

transceiver enters TRX_OFF state after RESET, because register 0x0E (IRQ_MASK) is

reset to mask all interrupts. In this case, state TRX_OFF is normally entered before the

microcontroller could modify the register.

6.5.4 and 6.6.4 for details.

4.7.2 Register Description

The interrupt handling in Extended Operating Mode is described in section

5.2.5.

If register bit IRQ_MASK_MODE (register 0x04, TRX_CTRL_1) is set, an interrupt

event can be read from IRQ_STATUS register even if the interrupt itself is masked.

However, in that case no timing information for this interrupt is provided.

The IRQ pin polarity can be configured with register bit IRQ_POLARITY (register 0x04,

TRX_CTRL_1). The default behavior is active high, which means that pin IRQ = H

issues an interrupt request.

If “Frame Buffer Empty Indicator” is enabled during Frame Buffer read access the IRQ

pin has an alternative functionality, refer to section

9.6 for details.

Register 0x0E (IRQ_MASK):

The IRQ_MASK register is used to enable or disable individual interrupts. An interrupt is

enabled if the corresponding bit is set to 1. All interrupts are disabled after power up

sequence (P_ON state) or reset (RESET state).

Table 4-16. Register 0x0E (IRQ_MASK)

Bit 7 6 5 4

Name MASK_BAT_LOW MASK_TRX_UR MASK_AMI MASK_

CCA_ED_READY

Read/Write R/W R/W R/W R/W

Reset Value 0 0 0 0

Bit 3 2 1 0

Name MASK_TRX_END MASK_RX_START MASK_

PLL_UNLOCK

Read/Write R/W R/W R/W R/W

Reset Value 0 0 0 0

MASK_PLL_LOCK

If an interrupt is enabled it is recommended to read the interrupt status register 0x0F

(IRQ_STATUS) first to clear the history.

8168A-AVR-06/08

Register 0x0F (IRQ_STATUS):

The IRQ_STATUS register contains the status of the pending interrupt requests.

25

Table 4-17. Register 0x0F (IRQ_STATUS)

Bit 7 6 5 4

Name BAT_LOW TRX_UR AMI CCA_ED_READY

Read/Write R R R R

Reset Value 0 0 0 0

Bit 3 2 1 0

Name TRX_END RX_START PLL_UNLOCK PLL_LOCK

Read/Write R R R R

Reset Value 0 0 0 0

By reading the register after an interrupt is signaled at pin 24 (IRQ) the source of the

issued interrupt can be identified. A read access to this register resets all interrupt bits,

and so clears the IRQ_STATUS register.

If register bit IRQ_MASK_MODE (register 0x04, TRX_CTRL_1) is set, an interrupt

event can be read from IRQ_STATUS register even if the interrupt itself is masked.

However in that case no timing information for this interrupt is provided.

If register bit IRQ_MASK_MODE is set, it is recommended to read the interrupt status

register 0x0F (IRQ_STATUS) first to clear the history.

Register 0x04 (TRX_CTRL_1):

The TRX_CTRL_1 register is a multi purpose register to control various operating

modes and settings of the radio transceiver.

Table 4-18. Register 0x04 (TRX_CTRL_1)

Bit 7 6 5 4

Name PA_EXT_EN IRQ_2_EXT_EN TX_AUTO_CRC_ON RX_BL_CTRL

Read/Write R/W R/W R/W R/W

Reset Value 0 0 1 0

Bit 3 2 1 0

Name SPI_CMD_MODE SPI_CMD_MODE IRQ_MASK_MODE IRQ_POLARITY

Read/Write R/W R/W R/W R/W

Reset Value 0 0 0 0

• Bit 7 – PA_EXT_EN

RX/TX Indicator, refer to section

9.4.3.

• Bit 6 – IRQ2_EXT_EN

The timing of a received frame can be determined by a separate pin. If register bit

IRQ_2_EXT_EN is set to 1, the reception of a PHR field is directly issued on

pin 10 (DIG2), similar to interrupt IRQ_2 (RX_START). Note that this pin is also active

even if the corresponding interrupt event IRQ_2 (RX_START) mask bit in register

0x0E (IRQ_MASK) is set to 0. The pin remains at high level until the end of the frame

receive procedure.

26

AT86RF212

For further details refer to section

9.5.

8168A-AVR-06/08

AT86RF212

• Bit 5 – TX_AUTO_CRC_ON

Refer to section

• Bit 4 – RX_BL_CTRL

Refer to section

• Bit 3:2 – SPI_CMD_MODE

Refer to section

• Bit 1 – IRQ_MASK_MODE

The AT86RF212 supports polling of interrupt events. Interrupt polling can be enabled by

register bit IRQ_MASK_MODE. Even if an interrupt request is masked by the

corresponding bit in register 0x0E (IRQ_MASK), the event is indicated in register

0x0F (IRQ_STATUS).

Table 4-19. Interrupt Polling Configuration

Register Bit Value Description

• Bit 0 – IRQ_POLARITY

The default polarity of the IRQ pin is active high. The polarity can be configured to

active low via register bit IRQ_POLARITY, see

6.3.5.

9.6.2.

4.4.1.

0 Interrupt polling disabled IRQ_MASK_MODE

1 Interrupt polling enabled

Table 4-20.

Table 4-20. Configuration of Pin 24 (IRQ)

Register Bit Value Description

0 pin IRQ high active IRQ_POLARITY

1 pin IRQ low active

This setting does not affect the polarity of the Frame Buffer Empty Indicator, refer to

section

9.6. The Frame Buffer Empty Indicator is always active high.

8168A-AVR-06/08

27

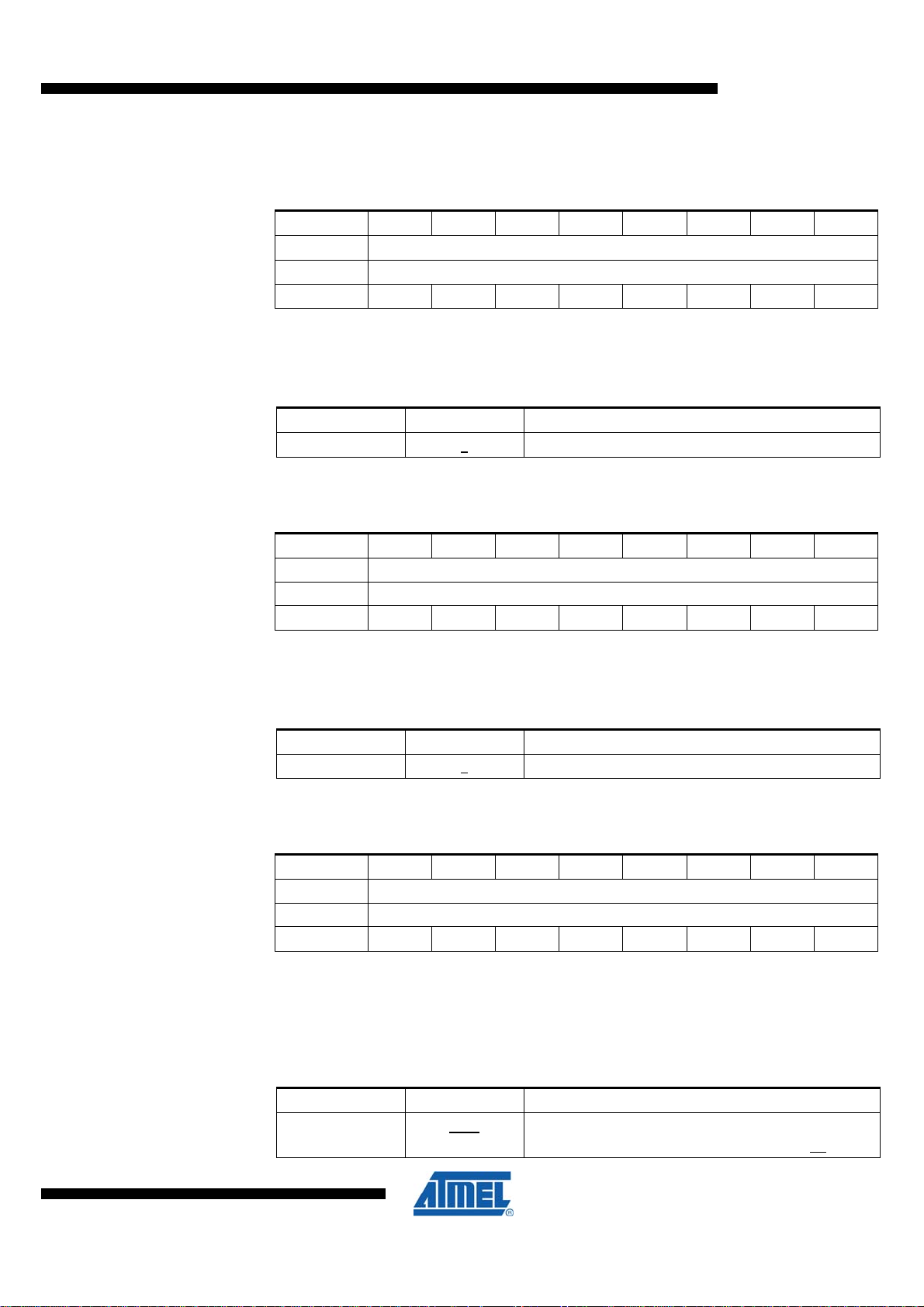

5 Operating Modes

5.1 Basic Operating Mode

This section summarizes all states to provide the basic functionality of the AT86RF212,

such as receiving and transmitting frames, the power up sequence and sleep. The

Basic Operating Mode is designed for IEEE 802.15.4 and ISM applications; the

corresponding radio transceiver states are shown in

Figure 5-1.

Figure 5-1. Basic Operating Mode State Diagram (for timing refer to

P_ON

(Power-on after EVDD)

XOSC=ON

Pull=ON

T

BUSY_RX

(Receive State)

SHR

Detected

FORCE_TRX_OFF

(all states except SLEEP)

6

SHR

Detected

RX_ON

Frame

End

SLP_TR = H

(Rx Listen State)

= L

R

T

P_

SL

R

X

_O

F

1

F

12

R

O

_

X

TRX_OFF

(Clock State)

XOSC=ON

Pull=OFF

N

F

F

_O

X

R

T

8

RX_ON

PLL_ON

FORCE_PLL_ON

(all states except SLEEP,

P_ON, TRX_OFF, RX_ON_NOCLK)

P

L

S

2

57

T

R

X

_O

9

RX_ON_NOCLK

(Rx Listen State)

CLKM=OFF

Table 5-1)

SLEEP

(Sleep State)

XOSC=OFF

Pull=OFF

L

=

R

_T

F

F

H

=

R

_T

P

L

S

13

(all states except P_ON)

P

L

L

_

O

N

4

PLL_ON

(PLL State)

14

3

/RST = H

(from all states)

/RST = L

RESET

Frame

11

End

BUSY_TX

(Transmit State)

10

SLP_TR = H

or

TX_START

Legend:

Blue: SPI Write to Register TRX_STATE (0x02)

Red: Control signals via IC Pin

Green: Event

Basic Operating Mode States

X

State transition number, see Table 7-1

5.1.1 State Control

28

AT86RF212

The radio transceiver states are controlled either by writing commands to register bits

TRX_CMD (register 0x02, TRX_STATE), or directly by two signal pins:

pin 11 (SLP_TR) and pin 8 (/RST). A successful state change can be verified by

reading the radio transceiver status from register 0x01 (TRX_STATUS).

8168A-AVR-06/08

AT86RF212

If TRX_STATUS = 0x1F (STATE_TRANSITION_IN_PROGRESS) the AT86RF212 is in

a state transition. Do not try to initiate a further state change while the radio transceiver

is in STATE_TRANSITION_IN_PROGRESS.

Pin SLP_TR is a multifunctional pin, refer to section

transceiver state, a rising edge of pin SLP_TR causes the following state transitions:

• TRX_OFF → SLEEP

• RX_ON → RX_ON_NOCLK

• PLL_ON → BUSY_TX

whereas the falling edge of pin SLP_TR causes the following state transitions:

• SLEEP → TRX_OFF

• RX_ON_NOCLK → RX_ON

Pin 8 (/RST) causes a reset of all registers (register bits CLKM_CTRL are shadowed,

for details refer to section

radio transceiver into TRX_OFF state. However, if the device was in P_ON state it

remains in P_ON state.

For all states except SLEEP, the state change commands FORCE_TRX_OFF or

TRX_OFF lead to a transition into TRX_OFF state. If the radio transceiver is in active

receive or transmit states (BUSY_*), the command FORCE_TRX_OFF interrupts these

active processes, and forces an immediate transition to TRX_OFF. By contrast a

TRX_OFF command is stored until an active state (receiving or transmitting) has been

finished. After that the transition to TRX_OFF is performed.

For a fast transition from receive or active transmit states to PLL_ON state the

command FORCE_PLL_ON is provided. Active processes are interrupted. In contrast

to FORCE_TRX_OFF this command does not disable the PLL and the analog voltage

regulator AVREG. It is not available in states SLEEP, RESET, and all *_NOCLK states.

7.7.4), and the content of the SRAM it deleted. It forces the

4.6. Depending on the radio

The completion of each requested state change shall always be confirmed by reading

the register bits TRX_STATUS (register 0x01, TRX_STATUS).

5.1.2 Description

5.1.2.1 P_ON – Power-On after EVDD

When the external supply voltage (EVDD) is applied first to the AT86RF212 the radio

transceiver goes into P_ON state performing an on-chip reset. The crystal oscillator is

activated and the default 1 MHz master clock is provided at pin 17 (CLKM) after the

crystal oscillator has stabilized. CLKM can be used as a clock source to the

microcontroller. The SPI interface and digital voltage regulator are enabled.

The on-chip power-on-reset sets all registers to their default values. A dedicated reset

signal from the microcontroller at pin 8 (/RST) is not necessary, but recommended for

hardware/software synchronization reasons.

All digital inputs have pull-up or pull-down resistors during P_ON state, refer to section

2.2.2.2. This is necessary to support microcontrollers where GPIO signals are floating

after power on or reset. The input pull-up and pull-down resistors are disabled when the

radio transceiver leaves P_ON state. Leaving P_ON state, outputs pins DIG1/DIG2 are

internally connected to digital ground, whereas pins DIG3/DIG4 are internally connected

to analog ground, unless their configuration is changed. A reset at pin 8 (/RST) does

not enable the pull-up or pull-down resistors.

8168A-AVR-06/08

29

5.1.2.2 SLEEP – Sleep State

Prior to leaving P_ON, the microcontroller must set the input pins to the default

operating values: SLP_TR = L, /RST = H and /SEL = H.

All interrupts are disabled by default. Thus, interrupts for state transition control are to

be enabled first, e.g. enable IRQ_4 (AWAKE_END) to indicate a state transition to

TRX_OFF state. In P_ON state a first access to the radio transceiver registers is

possible after a default 1 MHz master clock is provided at pin 17 (CLKM), refer to t

Table 5-1.

Once the supply voltage has stabilized and the crystal oscillator has settled (see section

10.5, parameter t

SPI write access to register bits TRX_CMD (register 0x02, TRX_STATE) with the

command TRX_OFF or FORCE_TRX_OFF initiates a state change from P_ON towards

TRX_OFF state, which is then indicated by an AWAKE_END interrupt if enabled.

In SLEEP state, the entire radio transceiver is disabled. No circuitry is operating. The

radio transceiver current consumption is reduced to leakage current and the current of a

low power voltage regulator (typ. 100 nA), which provides the supply voltage for the

registers such that the contents of them remains valid. This state can only be entered

from state TRX_OFF, by setting SLP_TR = H.

If CLKM is enabled, the SLEEP state is entered 35 CLKM cycles after the rising edge at

pin 11 (SLP_TR). At that time CLKM is turned off. If the CLKM output is already turned

off (bits CLKM_CTRL = 0 in register 0x03), the SLEEP state is entered immediately.

),. the interrupt mask for the AWAKE_END should be set. A valid

XTAL

TR1

in

5.1.2.3 TRX_OFF – Clock State

At clock rates of 250 kHz and symbol clock rate (CLKM_CTRL values 6 and 7, register

0x03, TRX_CTRL_0), the main clock at pin 17 (CLKM) is turned off immediately.

Setting SLP_TR = L returns the radio transceiver back to the TRX_OFF state. During

SLEEP the register contents remains valid while the content of the Frame Buffer and

the security engine (AES) are cleared.

/RST = L in SLEEP state returns the radio transceiver to TRX_OFF state and thereby

sets all registers to their default values. Exceptions are register bits CLKM_CTRL

(register 0x03, TRX_CTRL_0). These register bits require a specific treatment, for

details see section

In TRX_OFF, the crystal oscillator is running and the master clock is available at

pin 17 (CLKM). The SPI interface and digital voltage regulator are enabled, thus the

radio transceiver registers, the Frame Buffer and security engine (AES) are accessible

(see sections

In contrast to P_ON state, pull-up and pull-down resistors are disabled.

Note that the analog front-end is disabled during TRX_OFF. If TRX_OFF_AVDD_EN

(register 0x0C, TRX_CTRL_2) is set, the analog voltage regulator is turned on, enabling

faster switch to any transmit/receive state.

Entering the TRX_OFF state from P_ON, SLEEP, or RESET state, the state change is

indicated by interrupt IRQ_4 (AWAKE_END) if enabled.

7.7.4.

7.4 and 9.1).

30

AT86RF212

8168A-AVR-06/08

Loading...

Loading...