Page 1

Features

• Maximum Supply Voltage 40V

• One Programmable/Adjustable Boost Converter

• Two Programmable Buck Converters

• One Programmable Linear Regulator

• OTP Customer Mode

• 16-bit Serial Interface

• Two ISO9141 Interfaces (One Interface Programmable to LIN Functionality)

• Watchdog

• Various Diagnosis Functions

• 5 Voltage Sources Tailored to Resistor Measurement

• Charge Pump

• Small, 44-pin Package

• ESD Protection Against 2kV and 4kV

1. Description

With the introduction of the ATA6264, Atmel® introduces a new generation of airbag

power supplies for future airbag systems tailored to the needs of the automotive

industry. It is designed in Atmel’s 0.8 micron BCDMOS technology. ATA6264 contains

all the necessary blocks to supply the microcontroller, the firing capacitors, and

peripheral components of the airbag system. The power supply specifically fulfills the

power requirements of dual-voltage microcontrollers used in modern ECUs. The integrated watchdog and diagnosis blocks additionally support the safety aspects. The

8-MHz 16-bit SPI enables a high communication speed. Despite the high-level functionality, ATA6264 comes in a space-saving QFP44 package.

Airbag Power

Supply IC

ATA6264

Preliminary

4929B–AUTO–01/07

Page 2

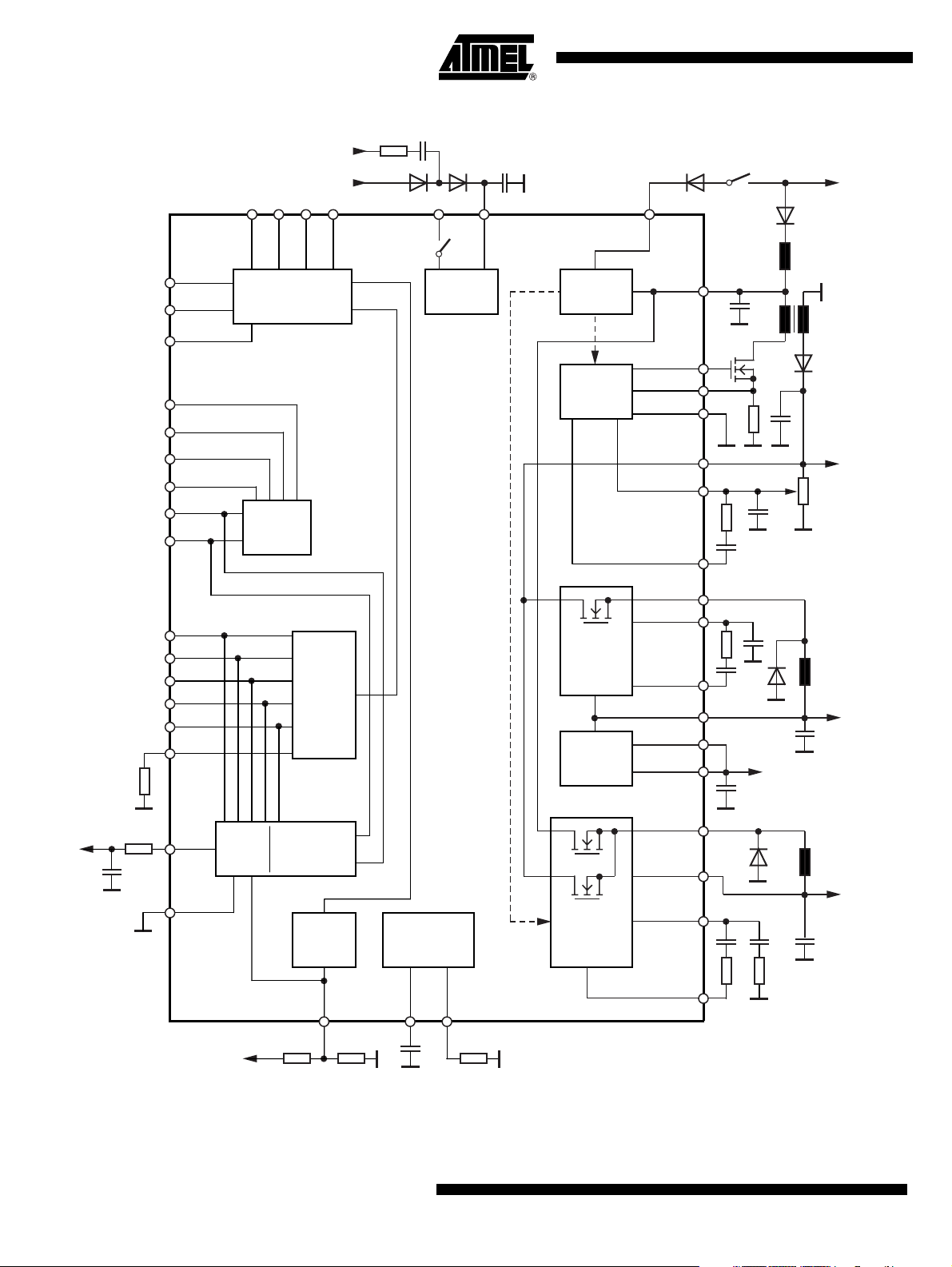

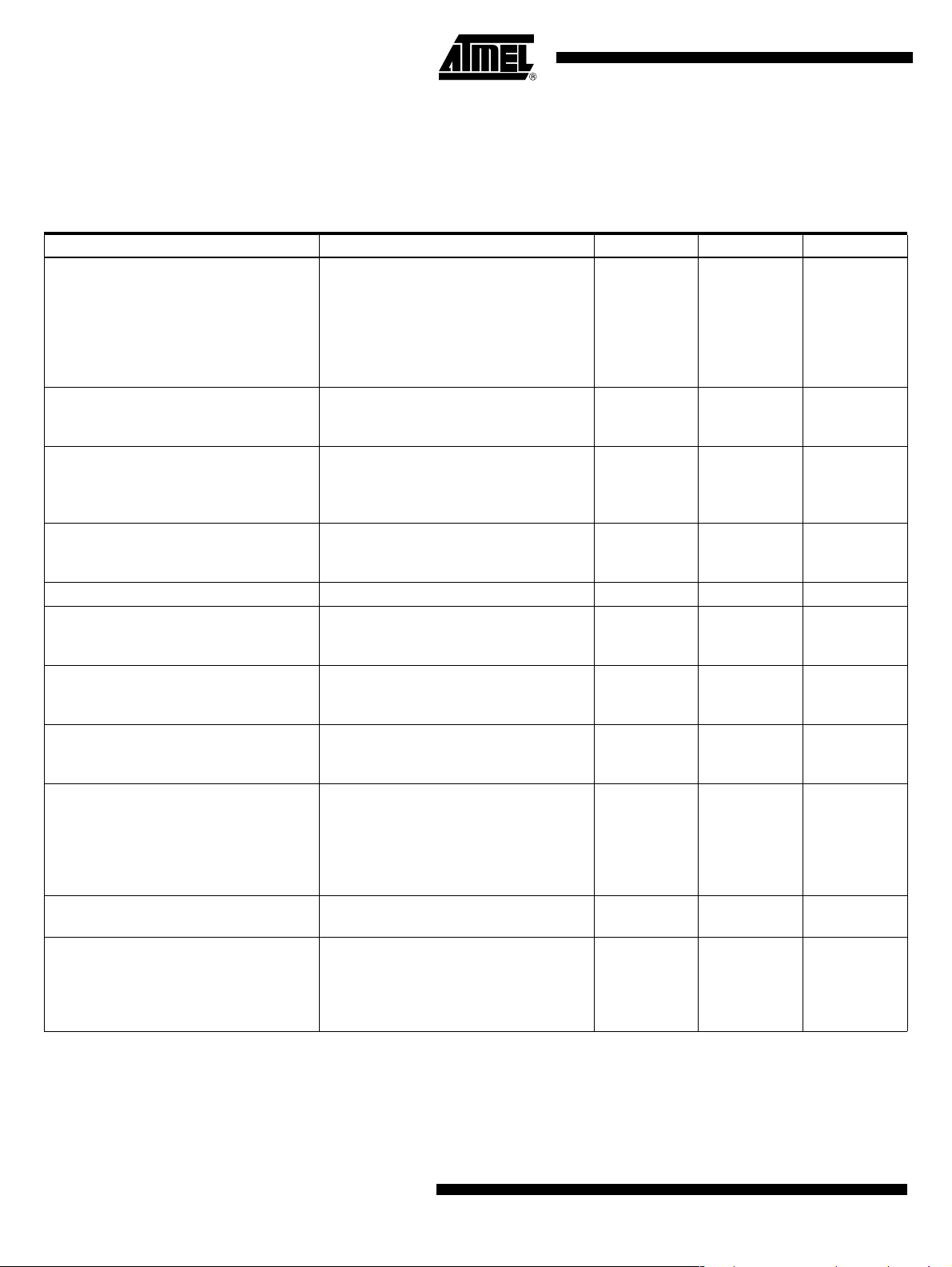

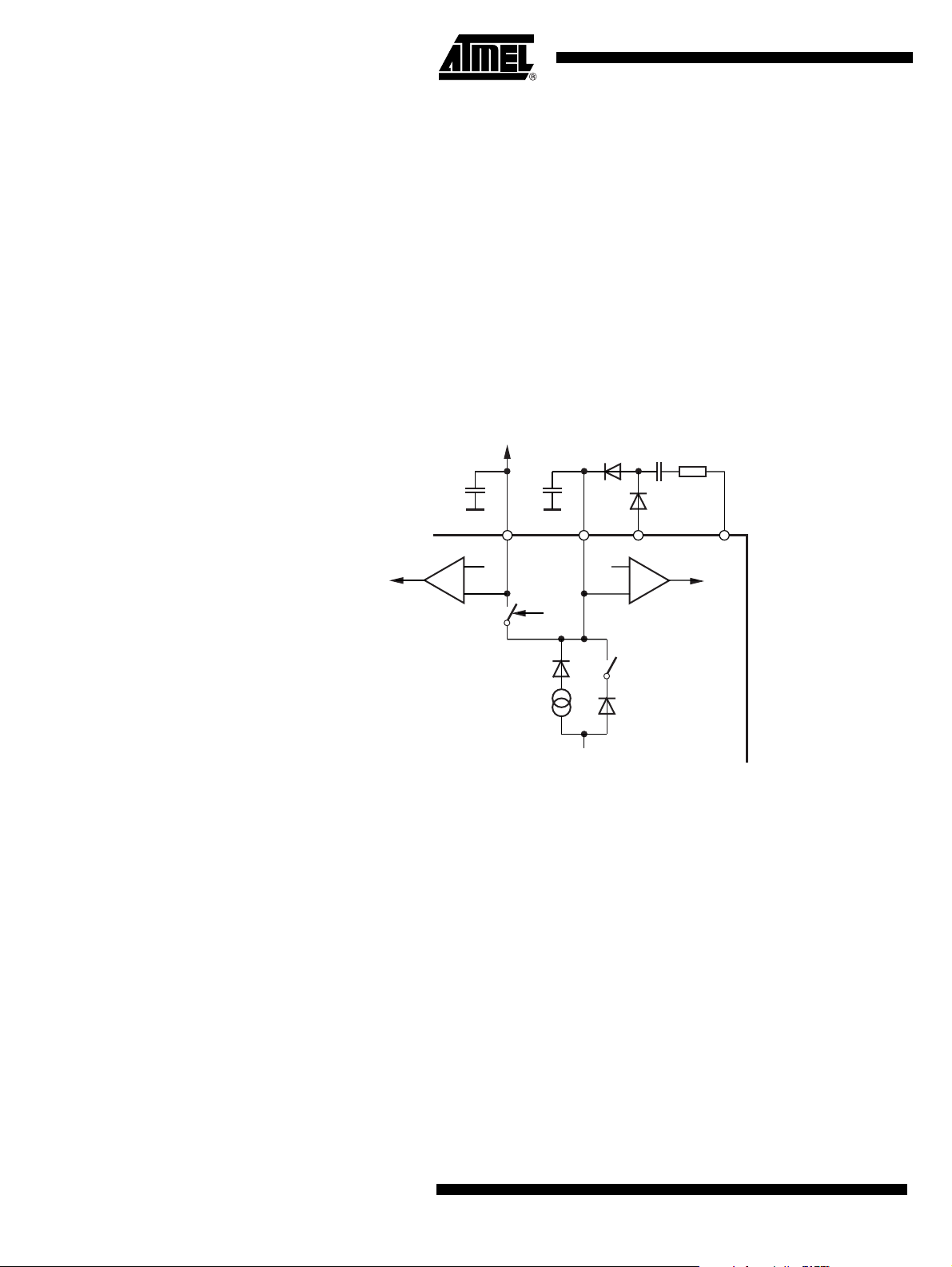

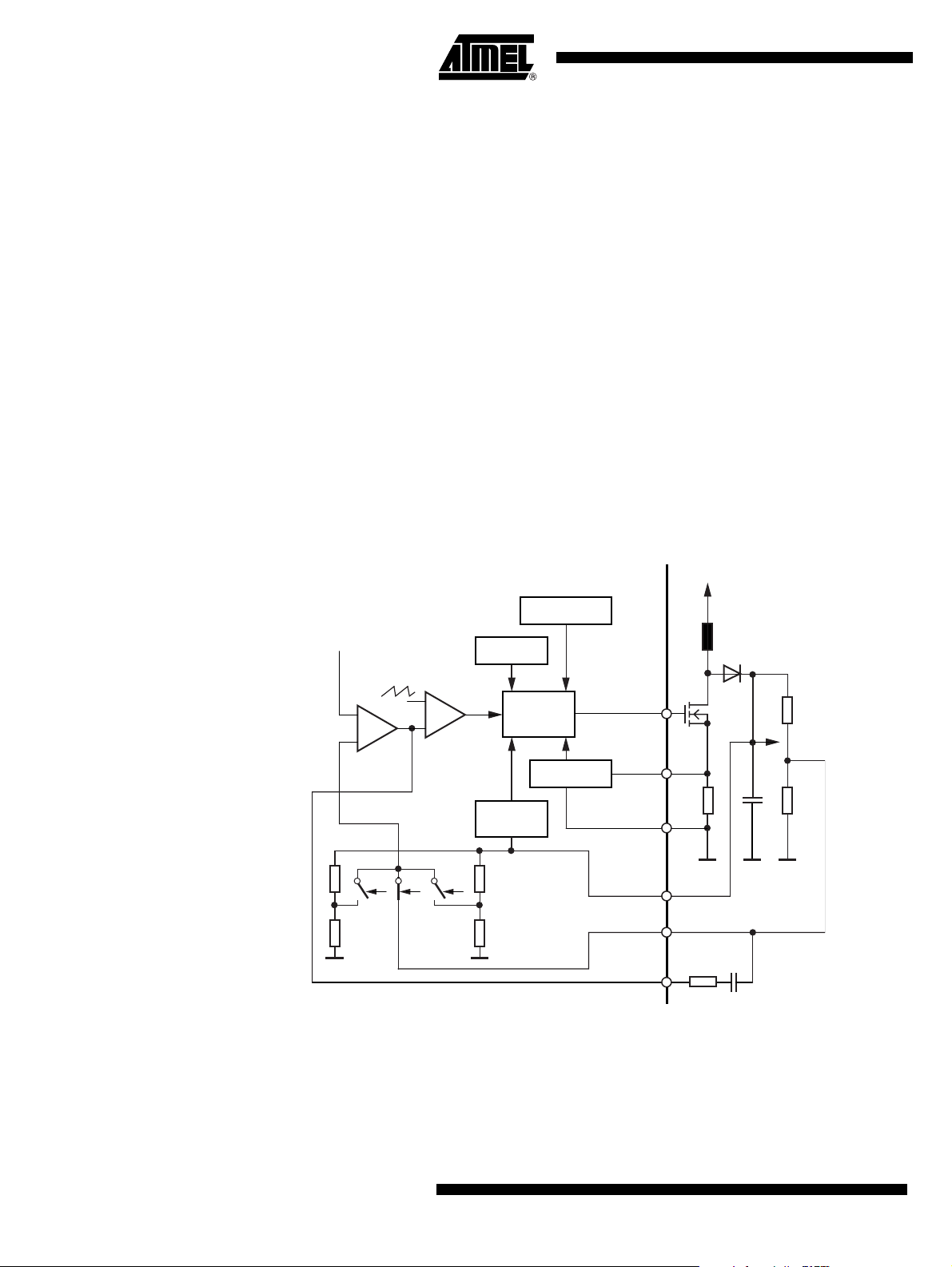

Figure 1-1. Block Diagram

SVSAT

VSAT

V

BATT

RESQ

RESQ2

GNDD

TxD1

RxD1

TxD2

RxD2

K1

K2

IASG1

IASG2

IASG3

IASG4

IASG5

ISENS

MOSI

SSQ

MISO

Serial Interface

Watchdog

Reset

ISO9141

IASG

SCLK

CP_OUT

CP Logic

CP

GKEY-

Logic

EVZ-

Regulator

VSAT-

Regulator

VPERI-

Regulator

K15

K30

GEVZ

OCEVZ

GNDB

EVZ

FBEVZ

COMEVZO

SVSAT

COMSATO

COMSATI

VSAT

SVPERI

VPERI

V

VPERI

V

V

EVZ

VSAT

SVCORE

UZP

GNDA

2

ATA6264 [Preliminary]

UZP

V

BATT

AMUX

USP

USP

Internal Supply

Reference

VINT

IREF

VCORE-

Regulator

VCORE

COMCOI

COMCOO

V

VCORE

4929B–AUTO–01/07

Page 3

1.1 Block Description

1.1.1 Integrated Boost Converter EVZ

With an external n-channel FET, the integrated boost converter EVZ provides 3 different voltages adjustable via the serial interface for the energy reserve and firing capacitors. Two

voltages are fixed values; one voltage can be adjusted using an external resistive divider.

1.1.2 Integrated Buck Converter VSAT

The integrated buck converter VSAT is a fully integrated step-down converter supplied by the

boost converter, EVZ, and providing 7.8V, 9.1V, or 10.4V. The user can program the voltage via

an OTP system.

1.1.3 Integrated Buck Converter VCORE

The integrated buck converter VCORE is a fully integrated step-down converter supplied either

by the boost converter, EVZ, or by the battery, and providing 1.88V, 2.5V, or 5V. The user can

program the voltage via an OTP system.

1.1.4 Linear Regulator VPERI

The linear regulator, VPERI, is supplied from the buck converter VSAT and provides an accurate

voltage of 3.3V ±3% or 5V ±4% as a supply for sensitive elements such as sensors and ADC

references with the current capability of 100 mA. The user can program the voltage via an OTP

system. With a sophisticated power-sequencing concept of VCORE and VPERI, ATA6264 supports dual-voltage-supply microcontrollers, so that under all conditions the voltage difference

between the two linear regulator voltages never drops below a defined value. This measure

guarantees the safe operation of the system.

ATA6264 [Preliminary]

1.1.5 Blocks Included

• A general purpose comparator USP, for, for example, low battery voltage detection

• A band gap as reference for all internal voltages and currents

• Two ISO9141 interfaces, one of which is configurable via OTP in accordance with the LIN

specification

• Five constant voltage sources with current-to-voltage mirrors used for resistance

measurements, such as buckle switch detection in the range from –0.5 mA to –40 mA

• An AMUX block with push-pull buffer stage provides the output of all analog values such as

voltage sources, low voltage detection, or the chip temperature for continuous diagnosis

• A 16-bit serial interface for the communication with the microcontroller which includes a 16-bit

shift register, a 16-bit latch, and a decoder-logic block

• A watchdog to monitor the microcontroller and to generate reset signals in the case of failure

• Internal oscillator generates internal clock signals

• GKEY function to control the main switch of the ECU via a logic signal

4929B–AUTO–01/07

3

Page 4

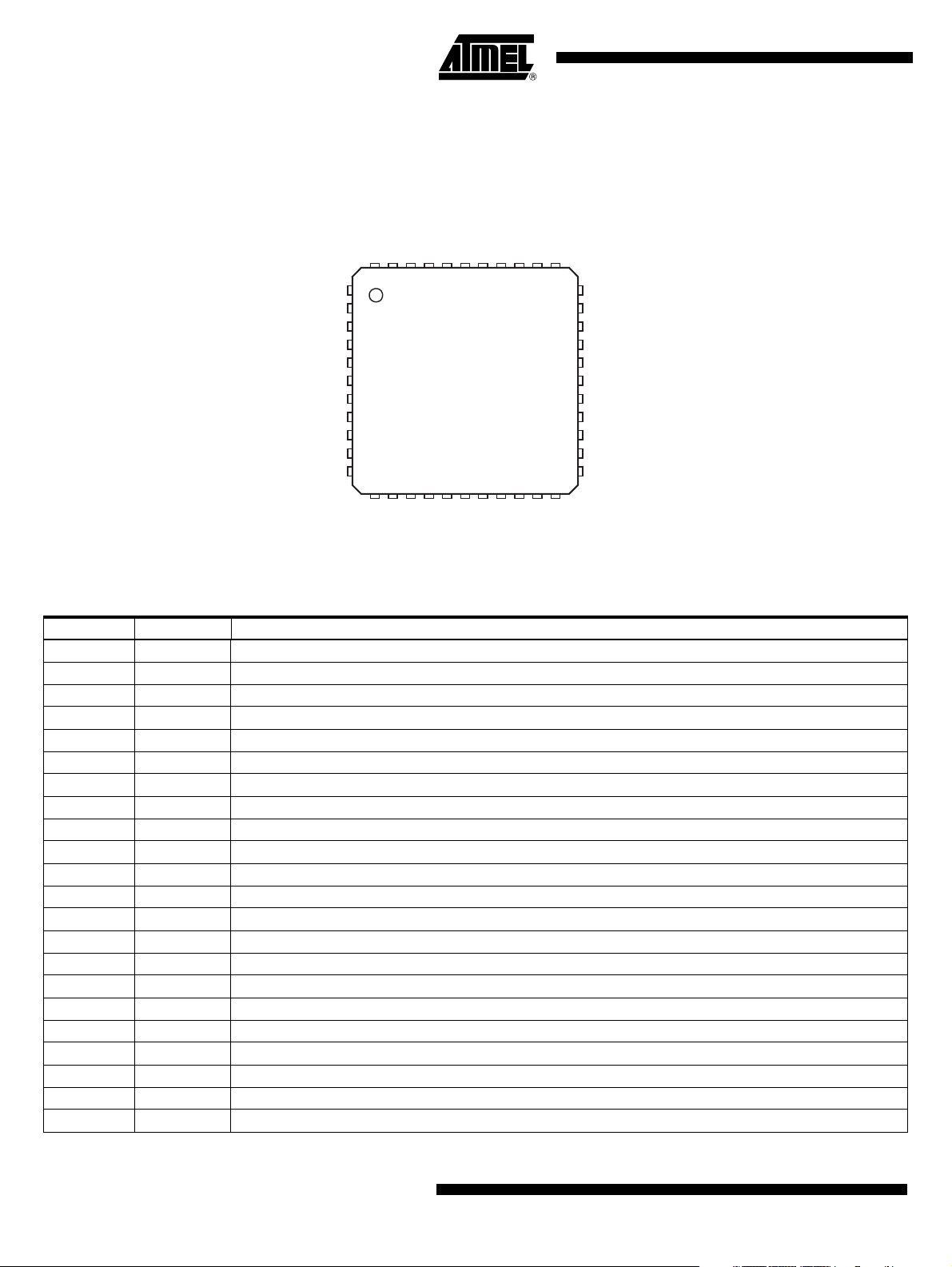

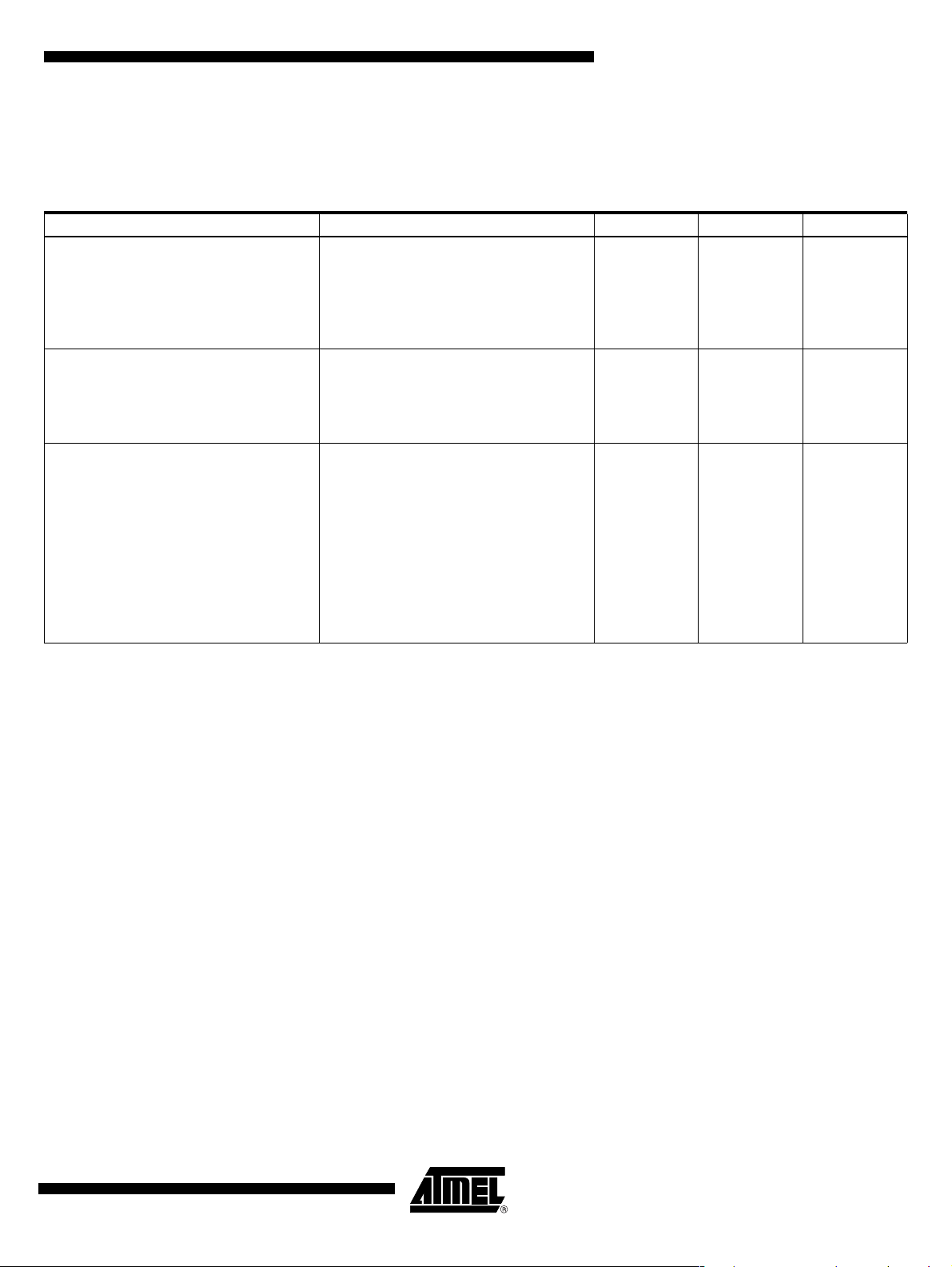

2. Pin Configuration

Figure 2-1. Pinning QFP44

COMEVZO

GNDB

GEVZ

OCEVZ

FBEVZCPSVCORE

CP-OUT

COMCOO

COMCOI

COMSATO

44 43 42 41 35 343638 373940

1

USP

K30

2

K1

3

K2

4

IASG1

IASG2

IASG3

IASG4

IASG5

ISENS

TxD1

5

6

7

8

9

10

11

12 13 14 15 21 222018 191716

RxD2

RxD1

RESQ

TxD2

MISO

SSQ

Table 2-1. Pin Description

Pin Symbol Function

1 USP Comparator input

2 K30 Continuous connection to the car battery

3 K1 Bus line of 1

4 K2 Bus line of 2

5 IASG1 Output of voltage source 1

6 IASG2 Output of voltage source 2

7 IASG3 Output of voltage source 3

8 IASG4 Output of voltage source 4

9 IASG5 Output of voltage source 5

10 ISENS Output of the current mirror from the IASGx interface

11 TXD1 Data input of the 1

12 RESQ Reset output

13 RXD2 Data output of the 2

14 RXD1 Data output of the 1st ISO9141 interface

15 TXD2 Data input of the 2

16 MISO Data output of the serial interface

17 SSQ Chip select of the serial interface

18 SCLK Clock input of the serial interface

19 MOSI Data input of the serial Interface

20 RESQ2 Redundant reset output

21 IREF Connection for the external reference resistor

22 UZP Analog measurement output

st

ISO9141 interface

nd

ISO9141 interface

st

ISO9141 interface

nd

ISO9141 interface

nd

ISO9141 interface

MOSI

SCLK

IREF

RESQ2

33

32

31

30

29

28

27

26

25

24

23

UZP

K15

EVZ

SVSAT

VSAT

GNDD

VINT

COMSATI

VCORE

GNDA

SVPERI

VPERI

4

ATA6264 [Preliminary]

4929B–AUTO–01/07

Page 5

Table 2-1. Pin Description

Pin Symbol Function

23 VPERI Input for the VPERI regulator, internally used VPERI supply

24 SVPERI Output of VPERI regulator power transistor

25 GNDA Analog GND

26 VCORE Input for VCORE regulator

27 COMSATI Input of the VSAT externally compensated error amplifier

28 VINT Output of internal supply voltage

29 GNDD Digital GND

30 VSAT Input for VSAT regulator, internally used VSAT supply

31 SVSAT Output of VSAT regulator power transistor

32 EVZ Input for EVZ regulator, internally used EVZ supply

33 K15 Connection to car battery via the ignition key

34 COMSATO Output of the VSAT externally compensated error amplifier

35 COMCOI Input of the VCORE externally compensated error amplifier

36 COMCOO Output of the VCORE externally compensated error amplifier

37 CP-OUT Switchable output of charge pump voltage

38 SVCORE Output of VCORE regulator power transistor

39 CP Charge pump output

40 FBEVZ Input for external resistor divider to adjust EVZ voltage

41 OCEVZ Input for overcurrent measurement of the EVZ regulator

42 GEVZ Gate driver output for the external FET of the EVZ regulator

43 GNDB GND connection of all power stages

44 COMEVZO Output of the EVZ externally compensated error amplifier

ATA6264 [Preliminary]

4929B–AUTO–01/07

5

Page 6

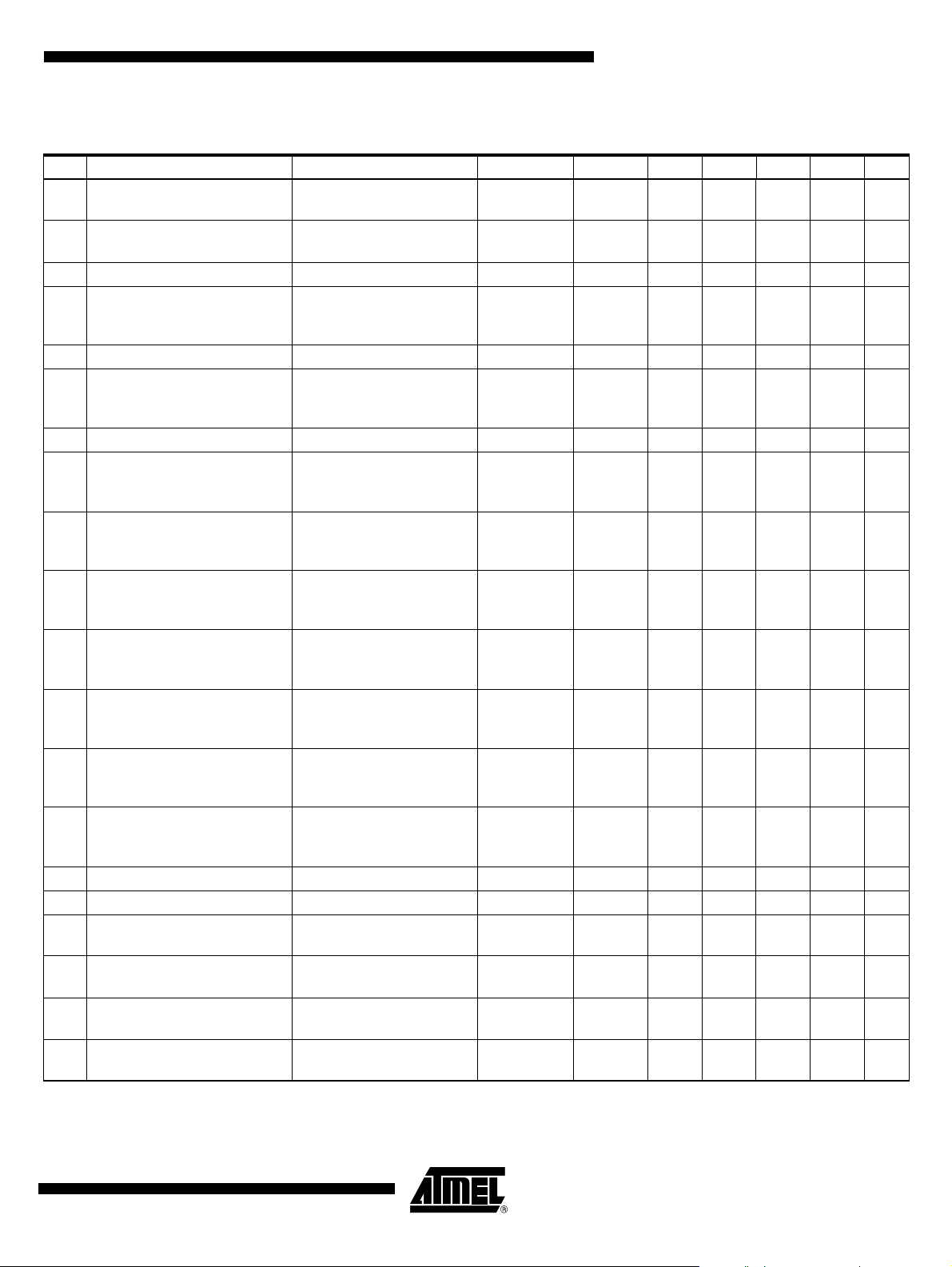

3. Absolute Maximum Ratings

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating

only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

All voltages are referenced to an ideal ground level of an ECU connected to the GNDA, GNDB and GNDD pins.

Parameters Remark Minimum Maximum Unit

Any combination of one or more pins

applied with any voltage between the

Voltage at pins, connected directly or

indirectly to the car battery

(K30, K15, USP)

Voltage at pins, connected directly or

indirectly to the car battery (K1, K2)

Voltage at pins, connected directly or

indirectly to the car battery (IASG1,

IASG2, IASG3, IASG4, IASG5)

Voltage at ECU internal pins (FBEVZ,

EVZ, VSAT)

Maximum rate of change at pin VSAT 1V/µs

Voltage at ECU internal pins (SVSAT,

SVCORE)

Voltage at ECU internal pins (CP,

CP-OUT)

Voltage at ECU internal pins (GEVZ,

OCEVZ)

Voltage at ECU internal pins (COMEVZO,

COMSATO, COMSATI, VPERI, SVPERI,

VCORE, COMCOI, COMCOO, IREF, UZP,

ISENS, RXD1, TXD1, RXD2, TXD2,

RESQ, RESQ2, MISO, MOSI, SSQ,

SCLK, VINT)

Current at logic pins

ESD classification at pins connected to

devices outside the ECU (K30, K15)

limits

K30 and K15 connected via diode to V

USP connected via minimum 5 kΩ to V

(maximum reverse current 5 mA).

Any combination of one or more pins

applied with any voltage between the

limits

Any combination of one or more pins

applied with any voltage between the

limits

Any combination of one or more pins

applied with any voltage between the

limits

Any combination of one or more pins

applied with any voltage between the

limits

Any combination of one or more pins

applied with any voltage between the

limits

Any combination of one or more pins

applied with any voltage between the

limits

These voltages can be applied in any

combination with any voltage between the

limits

Connected to voltages outside of

maximum voltage ratings via resistor

Batt

Batt

–0.3 +45 V

.

–25 +45 V

Voltage

necessary to

drive –40 mA

stored in 20 µH

–0.3 +45 V

–1 +45 V

–0.3 +56 V

–0.3 +10 V

–0.3 +7 V

–3 +3 mA

45 V

Human body model (HBM) HBM

AEC Q100-002

6

ATA6264 [Preliminary]

±4000 V

4929B–AUTO–01/07

Page 7

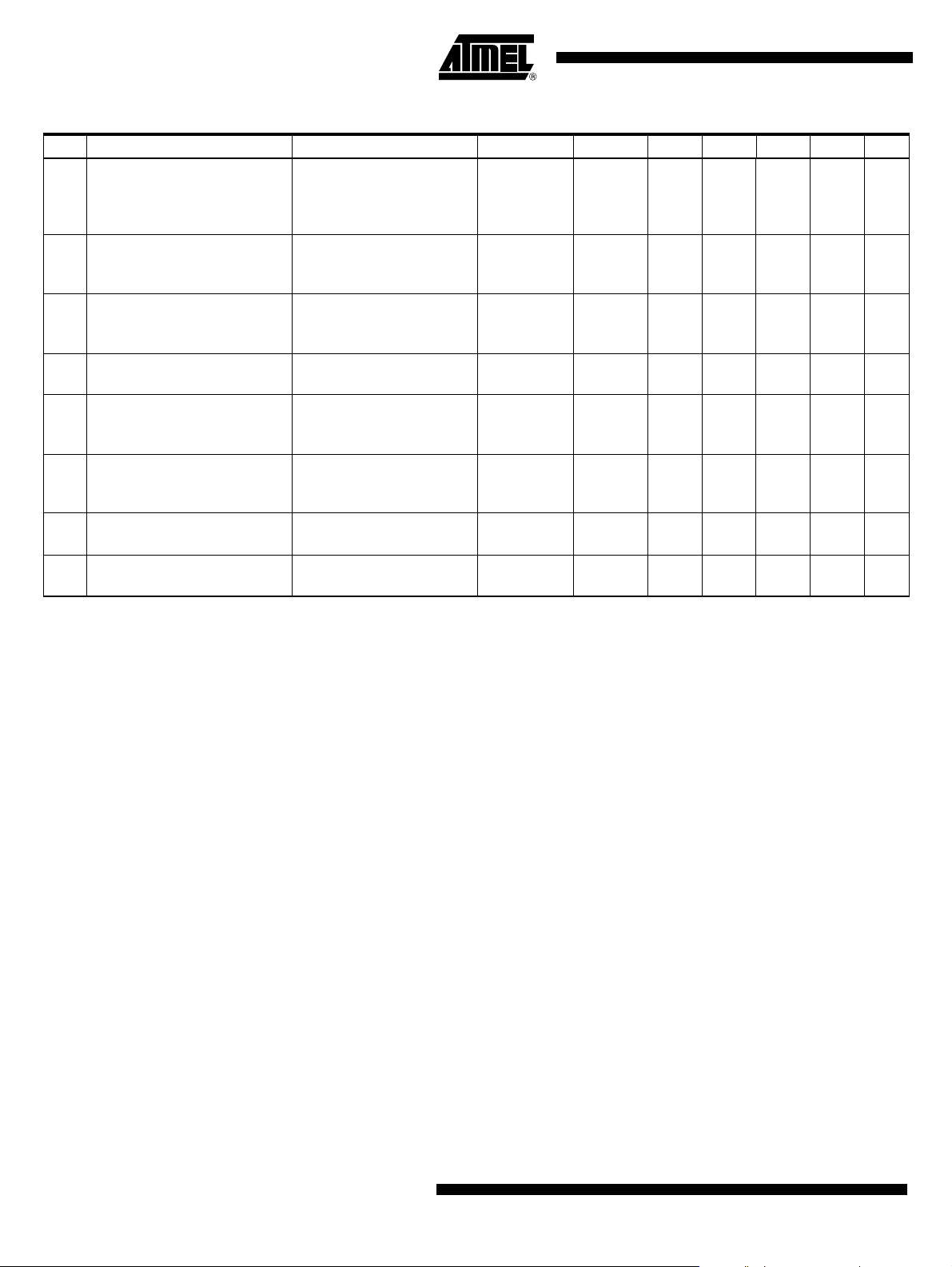

ATA6264 [Preliminary]

3. Absolute Maximum Ratings (Continued)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating

only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

All voltages are referenced to an ideal ground level of an ECU connected to the GNDA, GNDB and GNDD pins.

Parameters Remark Minimum Maximum Unit

ESD classification at pins connected to

devices outside the ECU (IASG1 to

IASG5)

Human body model (HBM) HBM

AEC Q100-002

ESD classification at pins connected to

devices outside the ECU (K1 and K2)

Human body model (HBM) HBM

AEC Q100-002

General ESD classification for all other

pins

Human body model (HBM)

Charged device model (CDM) – no corner

pins

Charged device model (CDM) – corner

pins

HBM

AEC Q100-002

CDM

ESD STM5.3.1-1999

±3000 V

±2500 V

±1500

±500

±750

V

V

V

4929B–AUTO–01/07

7

Page 8

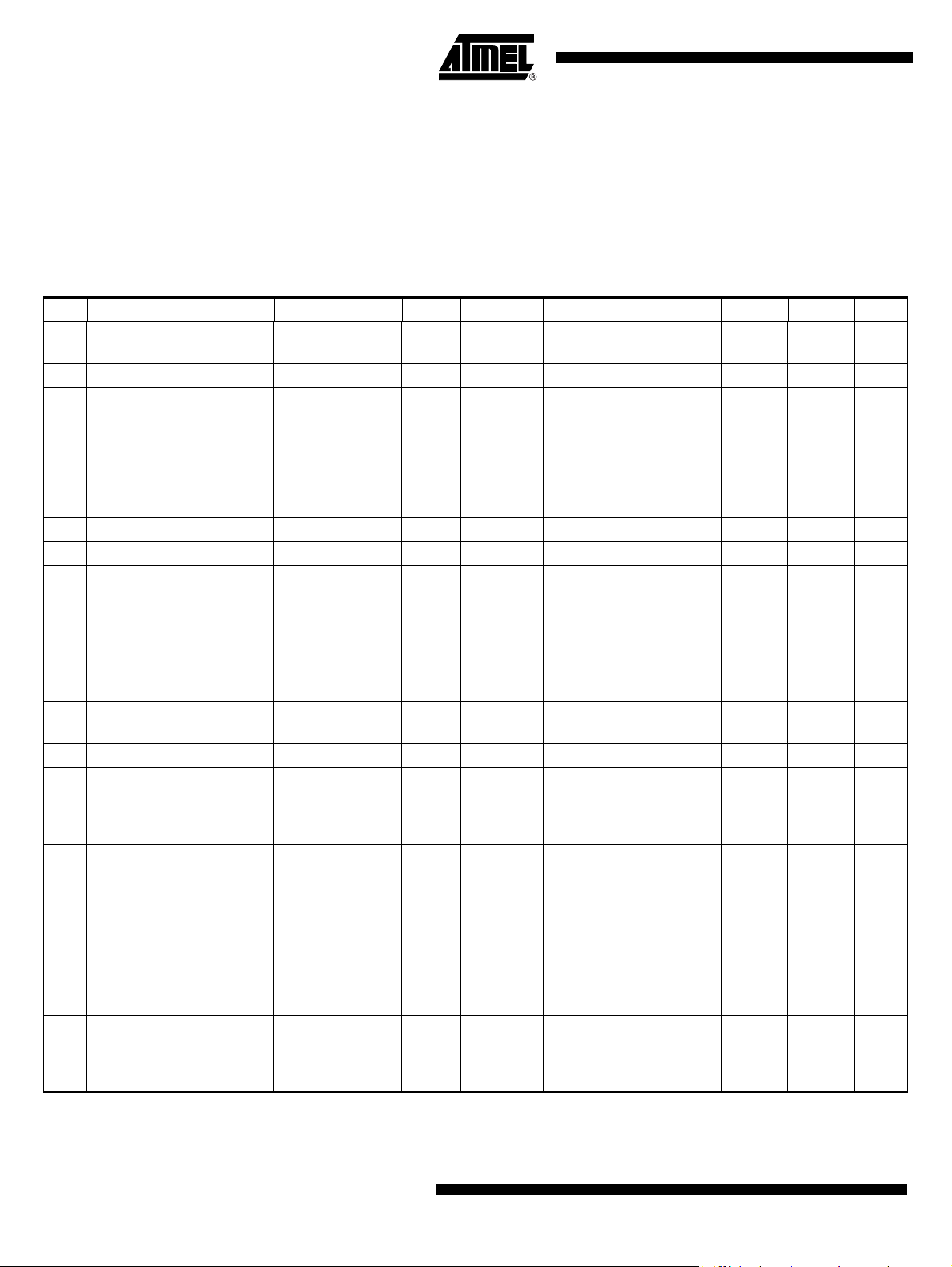

4. Functional Range

Within the functional range, the ATA6264 works as specified. All voltages are referenced to the

ideal ground level of an ECU connected to the GNDA, GNDB and GNDD pins.

At the beginning of each specification table, supply voltage and temperature conditions are

described.

Table 4-1. Electrical Characteristics – Functional Range

No. Parameters Test Conditions Pin Symbol Min. Typ. Max. Unit Type*

Voltage on pins K30, K15,

1.1

USP

1.1a Voltage on pins K1, K2 –25 +40 V

Rate of supply voltage rise

1.2

(K30, K15, K1, K2)

1.3 Supply voltage EVZ –0.3 +40 V

1.4 Supply voltage VSAT –0.3 +14 V

Supply voltages VCORE,

1.5

VPERI

1.6 Supply voltage CP, CP-OUT –0.3 +50 V

1.7 Voltage on digital I/O pins –0.3 +5.5 V

Voltage on pins SVSAT,

1.8

SVCORE

Voltage on pins UZP,

ISENS, COMCOI,

1.9

COMCOO, COMSATO,

COMSATI, COMEVZO,

FBEVZ, IREF, VINT

Voltage on pins GEVZ,

1.10

OCEVZ

1.11 Voltage on pin SVPERI –0.3 +6 V

Voltage on pins IASGx

1.12

(x = 1 to 5)

Temperatures:

Operating ambient

temperature range

1.14

Operating junction

temperature range

Storage ambient/junction

temperature range

Thermal resistance junction

1.15

ambient

Substrate current which can

be drawn without

1.16

disturbances to upper

defined blocks/functions

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Note: 1. No substrate current occurs at pins K1, K2 down to V

(1)

, VK2 > –25V

K1

–0.3 +40 V

–0.3 +5.5 V

–1.0 +40 V

–0.3 +5.5 V

–0.3 +10 V

Voltage

necessary to

drive –40 mA

stored in 20 µH

– 40

– 40

– 55

–40 mA

+ 90

+150

+105

50 V/µs

40 V

°C

°C

°C

60 K/W

8

ATA6264 [Preliminary]

4929B–AUTO–01/07

Page 9

4.1 Protection Against Substrate Currents

Due to the fact that the ATA6264 is connected to the wiring harness and to components outside

of the ECU, negative voltages at the following pins might occur:

• IASG interface: IASG1, IASG2, IASG3, IASG4, IASG5

• USP comparator: USP

If substrate currents occur, it is guaranteed by design that no disturbance and malfunction of the

following blocks and functions will happen:

• No disturbance of RESET block.

• No voltage changes of any regulators outside of their tolerances.

• No impact on digital circuitry (for example, changes of latches, status register, etc.)

• No latch up of any circuitry

ATA6264 [Preliminary]

4929B–AUTO–01/07

9

Page 10

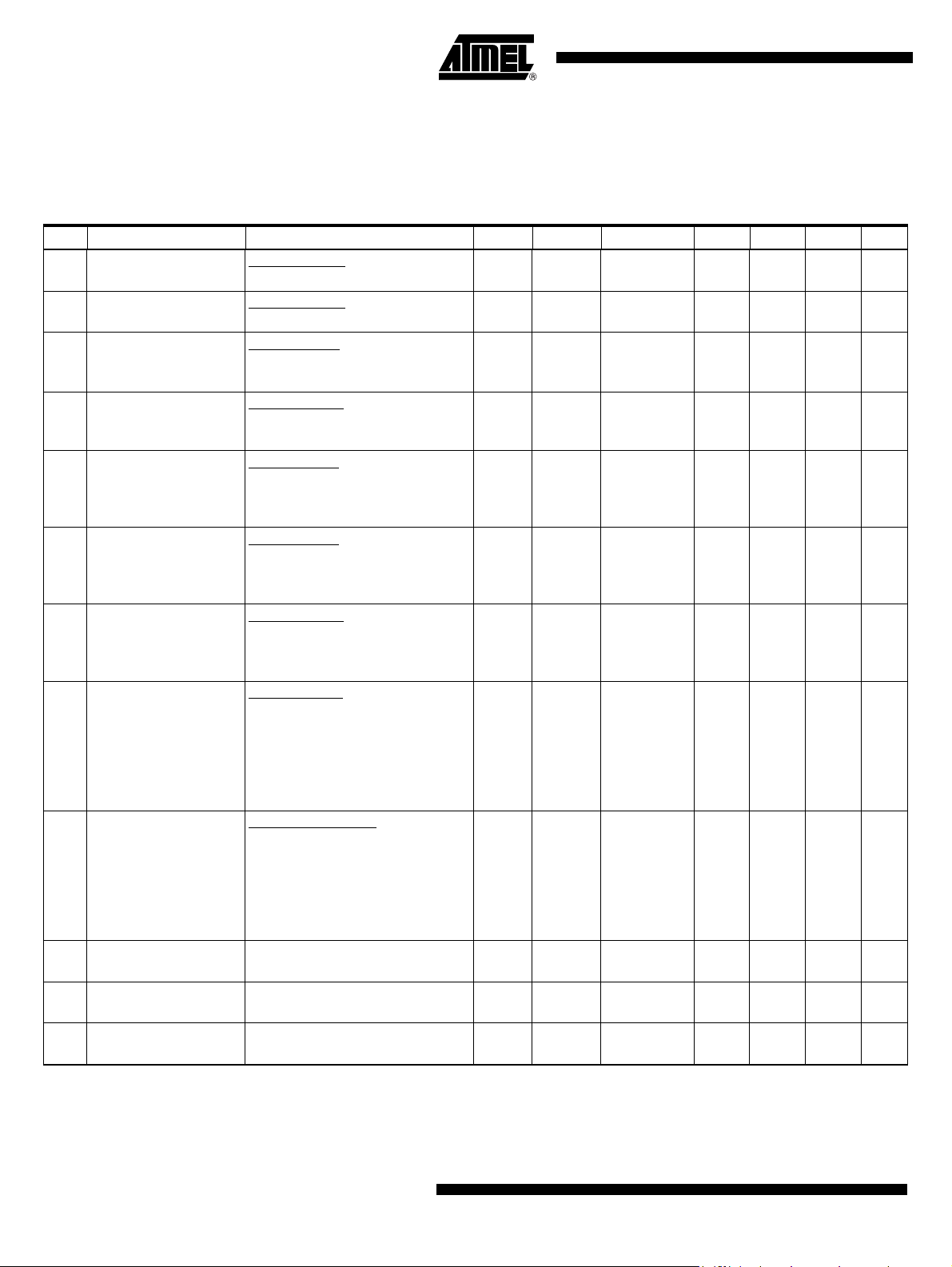

5. Supply Currents

A minimum current has to flow into each pin for proper functioning of the IC.

Table 5-1. Electrical Characteristics – Supply currents

No. Parameters Test Conditions Pin Symbol Min. Typ. Max. Unit Type*

2.1 Supply current at K30

2.1a Supply current at K30

Standby mode:

V

= 3V and KEYLATCH = OFF

K15

Standby mode:

= 3V and KEYLATCH = OFF

V

K15

0V = V

18V < V

Startup mode: 0V < V

2.1b Supply current at K30

2.1c Supply current at K30

2.1d Supply current at K30

V

> 4.15V or KEYLATCH = ON,

K15

V

= 0V, CCP = 47 nF

EVZ

Startup mode:

> 4.15V or KEYLATCH = ON

V

K15

V

= 0V, CCP = 47 nF

EVZ

Normal mode:

V

> V

EVZ

K30

0V < V

, V

K15

18V < V

> 4V or

KEYLATCH = ON, SVCORE open,

AMUX Measurement K30 active

Normal mode: 18V < V

V

> V

, V

2.1e Supply current at K30

EVZ

K30

KEYLATCH = ON, SVCORE open,

> 4.15V or

K15

AMUX Measurement K30 active

Startup mode: 0V < V

2.2 Supply current at EVZ

V

V

SAT

K30

= V

>5V, V

= V

PERI

CORE

> 4.15V, SVCORE

K15

and SVSAT open

Normal mode: 0V < V

2.2a Supply current at EVZ

and V

V

PERI

Threshold, V

= 10V, V

V

SAT

> 4.15V, SVCORE and

V

K15

CORE

EVZ

K30

> Reset

> V

> 5V,

SVSAT open, AMUX Measurement

EVZ active

Autonomous mode:

0V < V

EVZ

= 40V, V

> Reset Threshold, V

2.2b Supply current at EVZ

V

= 10V, V

SAT

< 3V, SVCORE and SVSAT

V

K15

< 3.85V,

K30

open, AMUX Measurement EVZ

active

2.3 Supply current at VSAT

Supply current at

2.4

VPERI

Supply current at

2.5

VCORE

0V < V

AMUX measurement VSAT active

0V < V

measurement VPERI active

0V < V

measurement VCORE active

= 14V, SVPERI open,

SAT

= 5.3V, AMUX

PERI

= 5.3V, AMUX

CORE

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

= 0V,

K30

PERI

K30

K30

K30

K30

K30

K30

EVZ

EVZ

,

and V

EVZ

= 18V,

= 40V,

= 18V,

= 40V

= 18V,

= 40V,

= 40V,

= 40V,

CORE

> V

K30

,

K30

K30

K30 I

K30 I

K30

K30

EVZ

EVZ

EVZ

VSAT

VPERI

VCORE

I

K30

I

K30

K30

K30

I

K30

I

K30

I

EVZ

I

EVZ

I

EVZ

I

VSAT

I

VPERI

I

VCORE

050µAA

05mAA

07mAA

010mAA

06.5mAA

010mAA

05mAA

06mAA

010mAA

01.5mAA

–0.2 2.2 mA A

–0.45 1 mA A

10

ATA6264 [Preliminary]

4929B–AUTO–01/07

Page 11

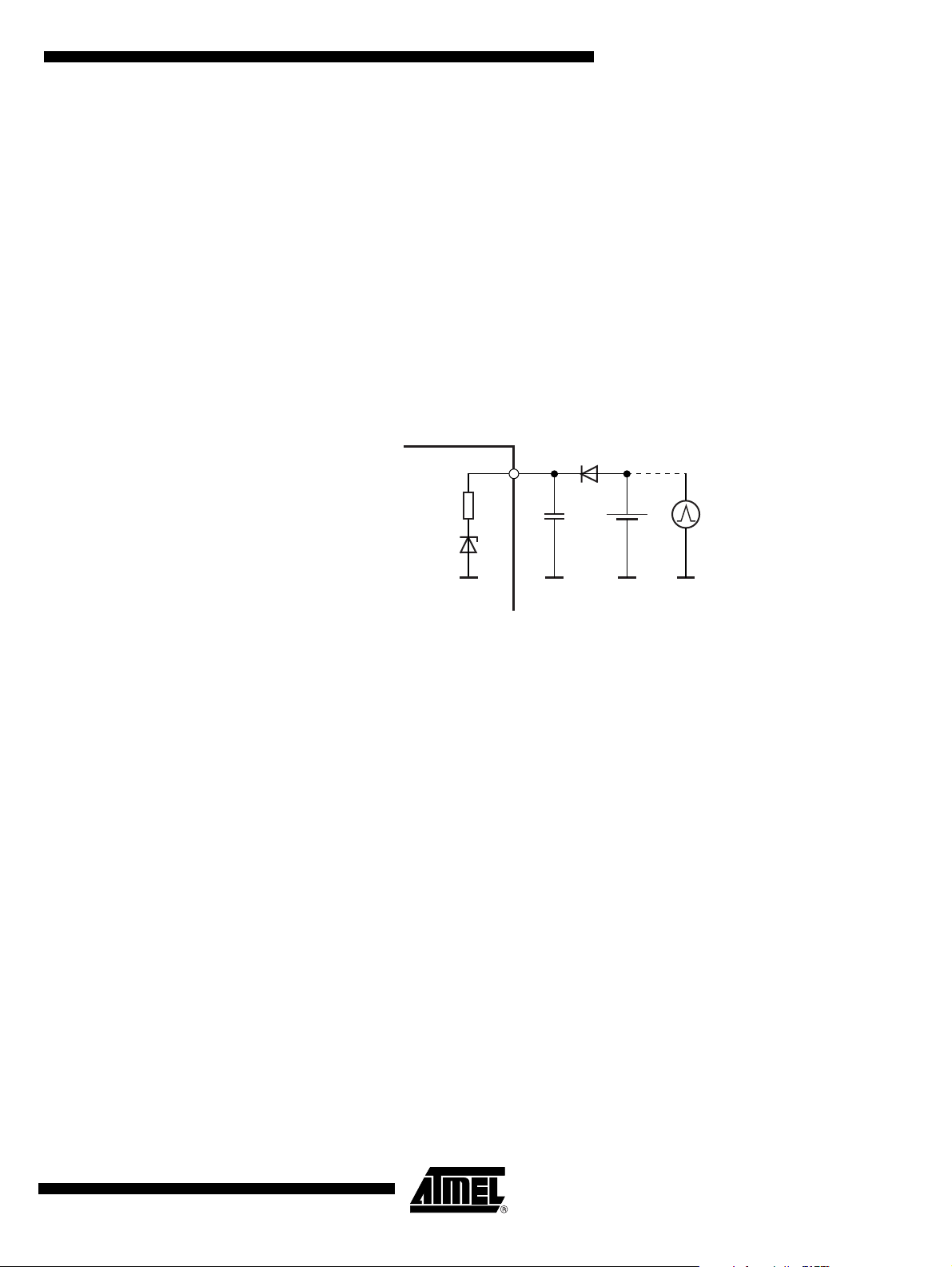

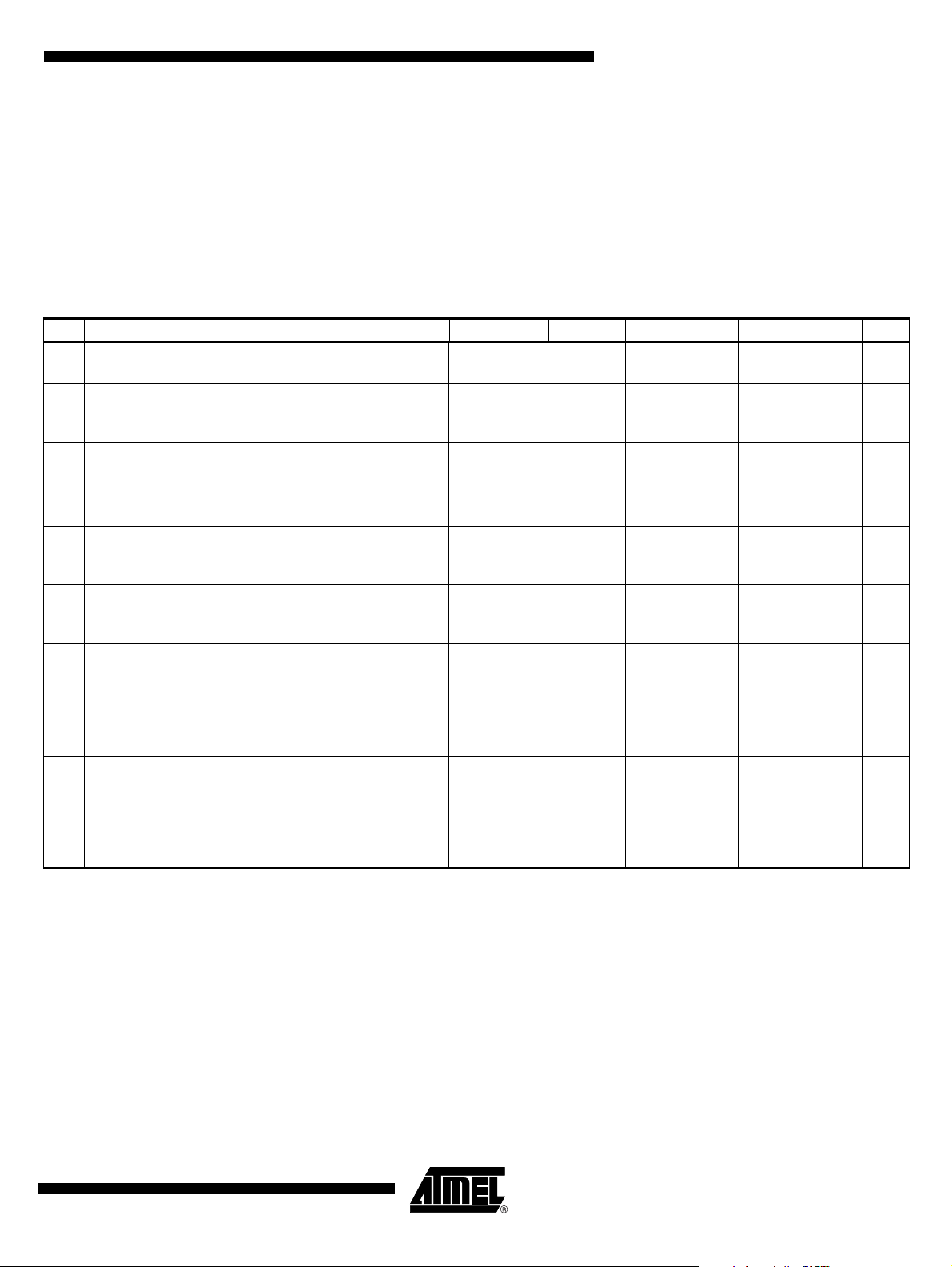

5.1 Discharger Circuit

e

Applications using the ATA6264 usually use a reverse polarity protection diode (D1 in Figure

5-1) in the power supply to prevent any damage if the wrong polarity is applied to V

nately, this method includes some risk as can be seen in the following description:

ATA6264 [Preliminary]

. Unfortu-

K30

During Standby mode (V

I

. Any peaks on the supply voltage (V

K30

K15

capacitor (C1). D1 prevents the capacitor from being discharged via the power supply and the

very small quiescent current via the IC can also be neglected. This means that during long periods of Standby mode, the IC’s supply voltage could increase continuously until finally the

maximum supply voltage limit would be exceeded and the IC could be damaged. ATA6264

therefore features a discharger circuit which avoids such unwanted effects. If V

threshold value of approximately 26.8V, the blocking capacitor is discharged via an integrated

resistor until V

again falls below the threshold.

K30

Figure 5-1. Discharger Circuit

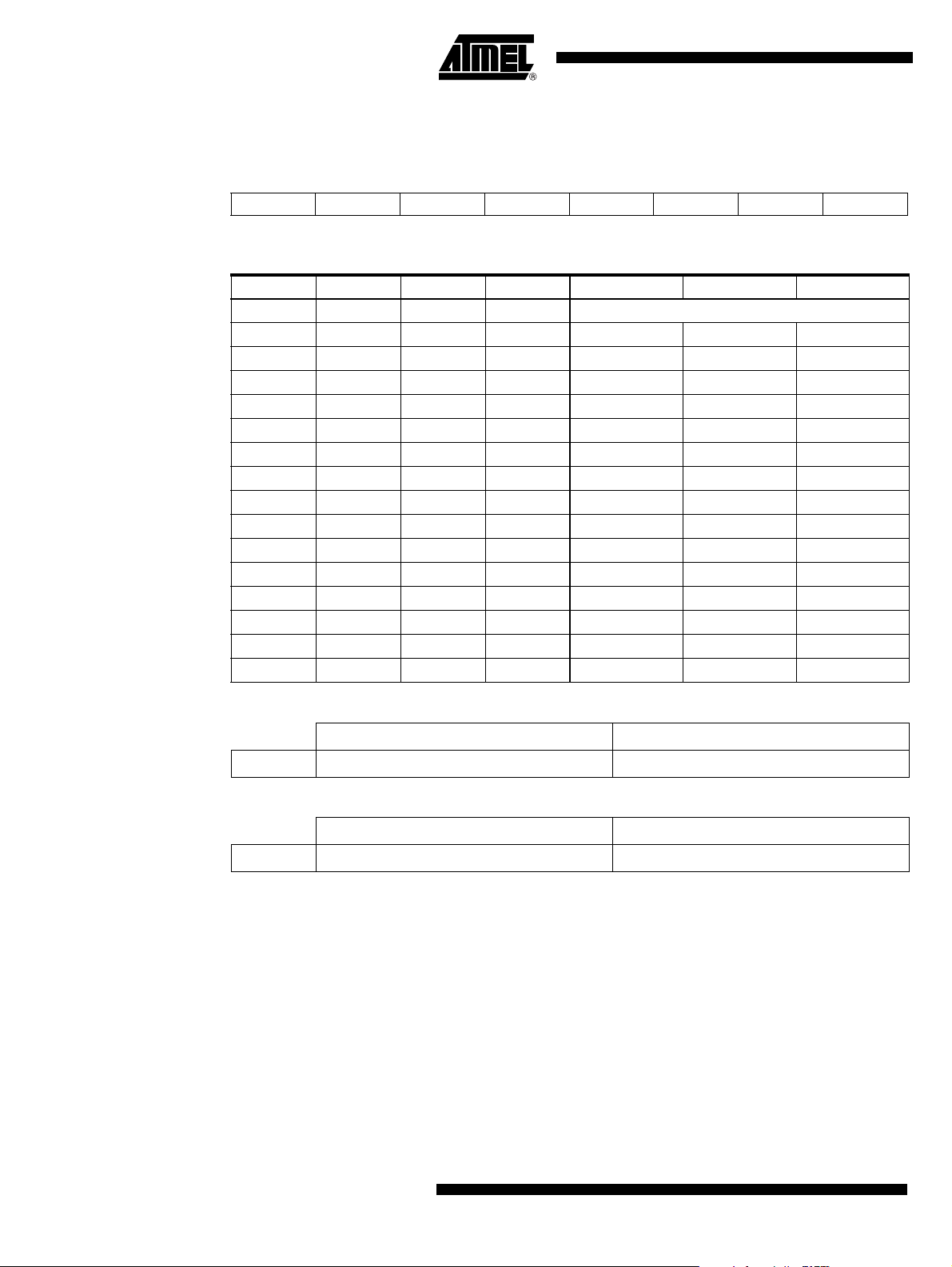

5.2 Initial Programming of the ATA6264

The ATA6264 supports different output voltages at the VSAT, VPERI and the VCORE regulators. In addition, different modes at the ISO9141 interfaces can be adjusted at the initial

programming (IP). The memory cells are one-time programmable (OTP) and cannot be changed

after the IP (default values are “0”). In general, the IP is done after mounting the ATA6264 on the

PCB with an in-circuit tester. The programming voltage of 11.7V has to be applied on pin VSAT.

It is also possible to use the VSAT regulator as the programming voltage because VSAT is programmed to 11.7V (±0.5V) as long as the Test mode is entered and the lock bit is not set. To

ensure proper programming of the ATA6264, at least a 10-µF electrolytic cap and a 100-nF

ceramic cap have to be applied at pin VSAT.

< 3V and KEYLATCH = OFF) the IC consumes only a low current,

in Figure 5-1) will gradually charge the blocking

Pulse

exceeds a

K30

K30

C18 kΩ

26.8V

D1

V

Batt

V

Puls

4929B–AUTO–01/07

11

Page 12

The following settings can be made at the initial programming:

MSBit LSBit

VR1 VR2 VR3 VR4 EXT ISO/LIN Parity Lock bit

Table 5-2. Initial Programming Settings

VR1 VR2 VR3 VR4 VCORE VPERI VSAT

0 0 0 0 All regulators deactivated (default)

0 0 0 1 1.88V 3.3V 7.8V

0 0 1 0 1.88V 3.3V 9.1V

0 0 1 1 1.88V 3.3V 10.4V

0 1 0 0 2.5V 3.3V 7.8V

0 1 0 1 2.5V 3.3V 9.1V

0 1 1 0 2.5V 3.3V 10.4V

0 1 1 1 1.88V 5V 7.8V

1 0 0 0 1.88V 5V 9.1V

1 0 0 1 1.88V 5V 10.4V

1 0 1 0 2.5V 5V 7.8V

1 0 1 1 2.5V 5V 9.1V

1 1 0 0 2.5V 5V 10.4V

1 1 0 1 5V 5V 7.8V

1 1 1 0 5V 5V 9.1V

1 1 1 1 5V 5V 10.4V

12

Set to 0 Set to 1

EXT No external transistor at VPERI (default) External transistor at VPERI applied

Set to 0 Set to 1

ISO/LIN ISO9141 mode is activated at K1 (default) LIN mode is activated at K1

ATA6264 [Preliminary]

4929B–AUTO–01/07

Page 13

ATA6264 [Preliminary]

The IP data is valid only if the parity is odd. If the IP data is not valid, or if the lock bit is not set,

the programming will not be executed.

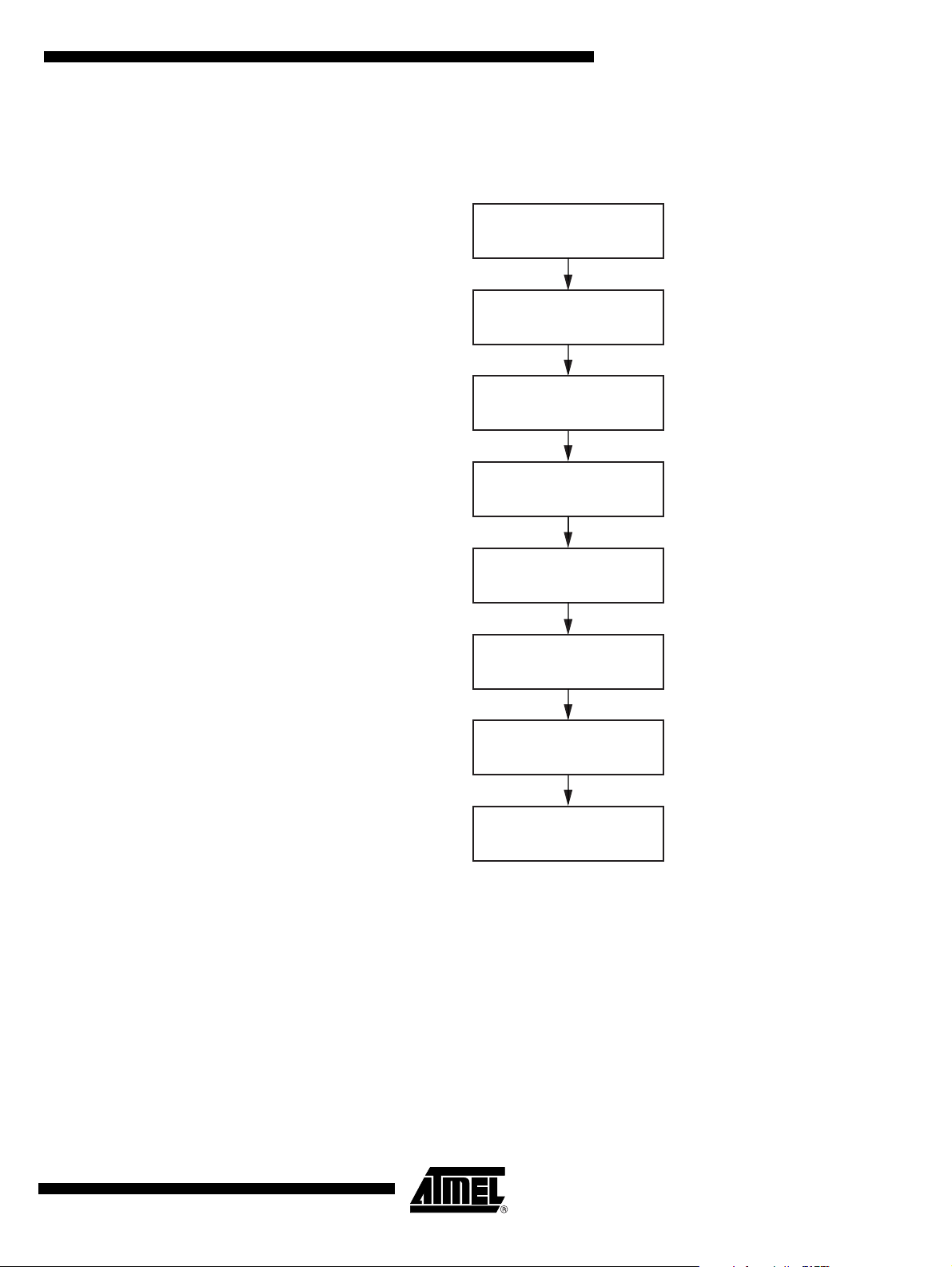

Figure 5-2. Programming Sequence

Contact pins RESQ, RESQ2

TxD1, TxD2, SSQ, MOSI,

SCLK, VPERI, K15, K30

Apply 12V at K15, K30 and5V

Set RESQ and TxD1 to GND

and RESQ2 and TxD2 to 5V

Transmit IP command A9xx(h)

via SPI to configure ATA6264

at VPERI

Transmit 5A5A(h) via SPI

to Enable Testmode

Wait until VSAT = 11.7V

Wait 1 ms

4929B–AUTO–01/07

Remove all voltages and pinloads

to get out of Test mode

13

Page 14

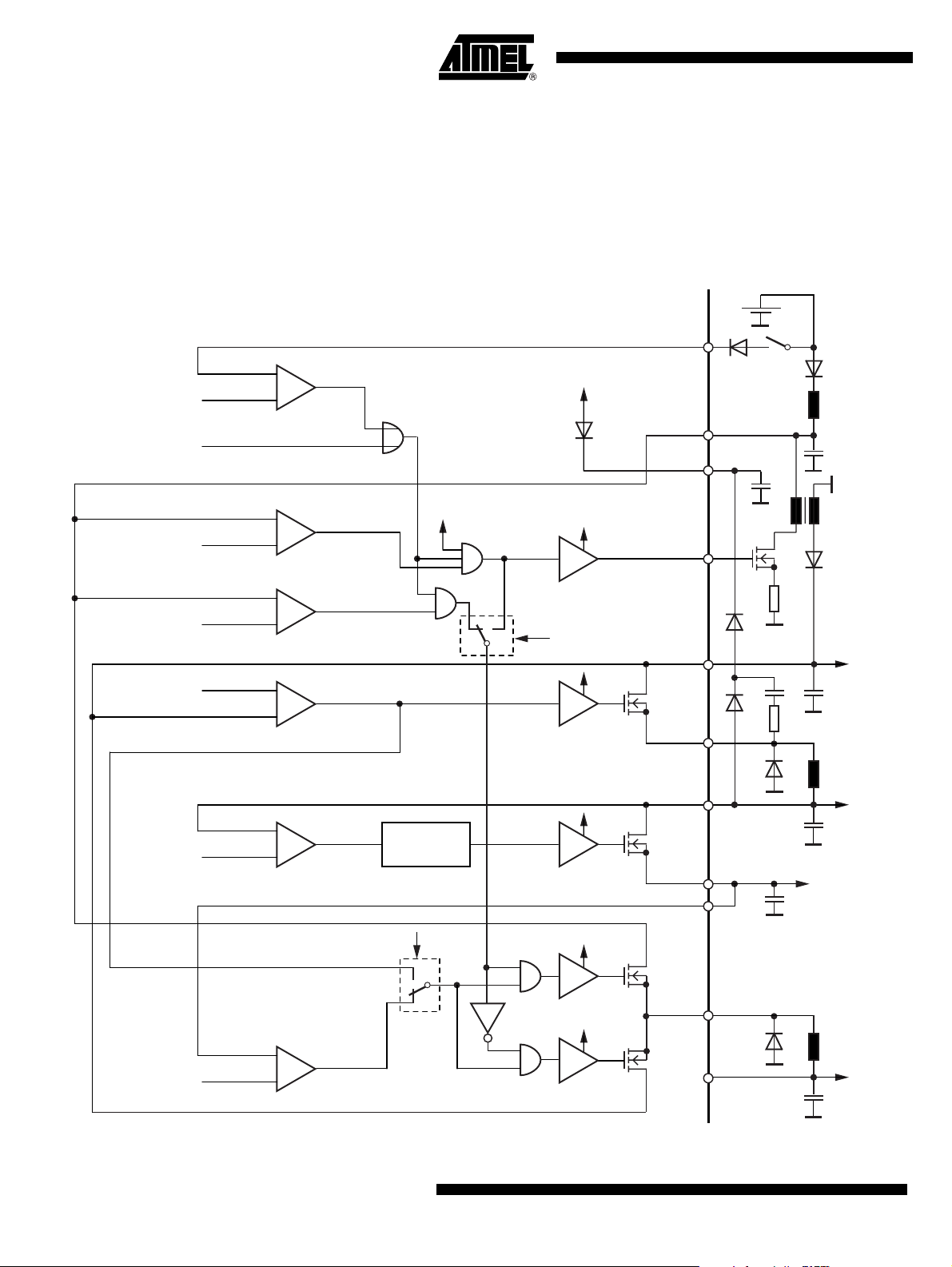

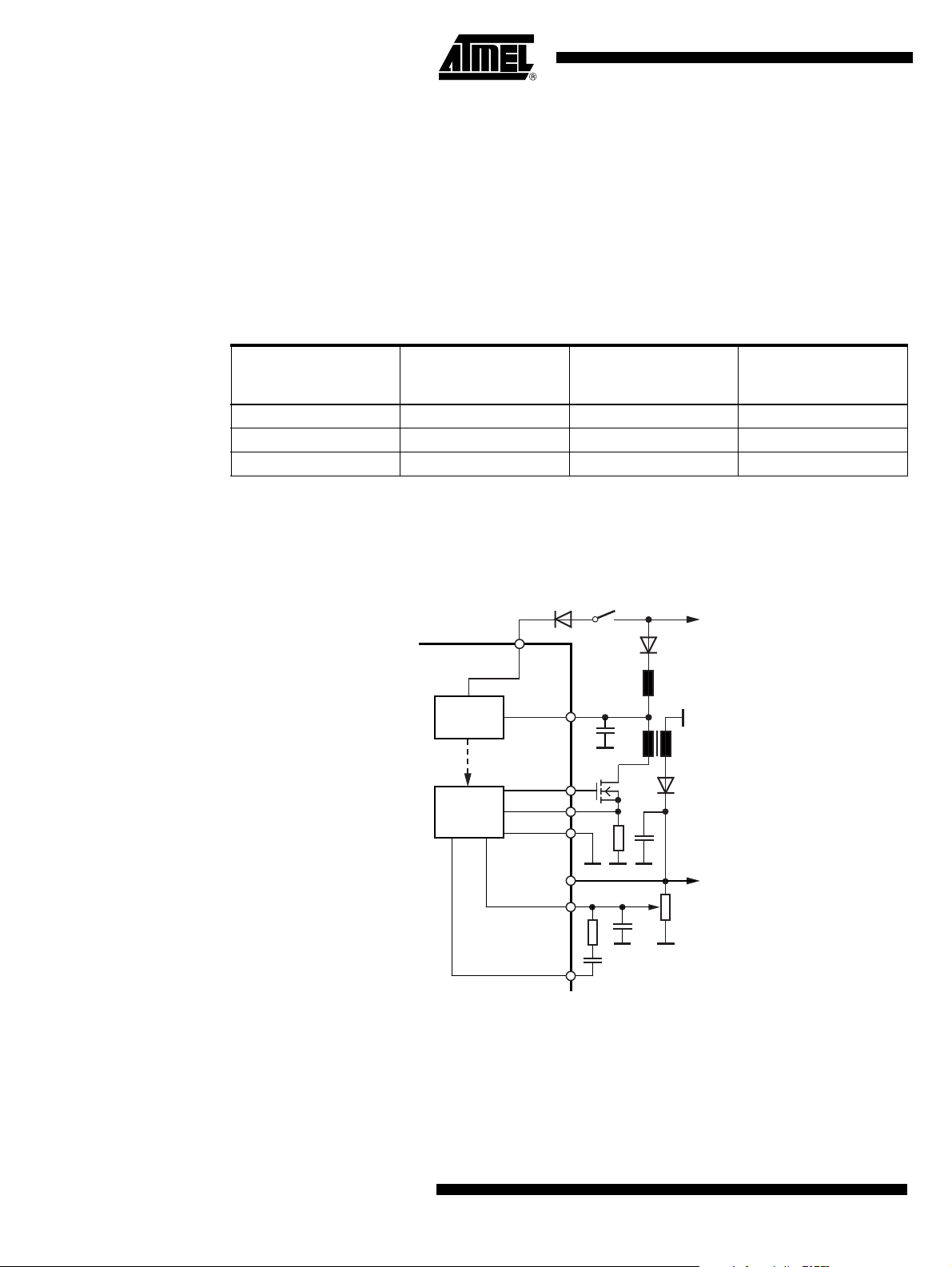

5.3 Start-up and Power-down Procedure

E

The ATA6264 is powered via the pin K30 (battery voltage) and via a diode or a resistor it is connected to the ignition key line K15. In order to detect an interruption on one of these pins

correctly, resistors are implemented at these pins. Normally, the main supply pin of ATA6264 is

pin K30. In the case of a missing or a too-low voltage at pin K30, the whole IC is supplied from

the backup power supply capacitor hooked up to pin EVZ.

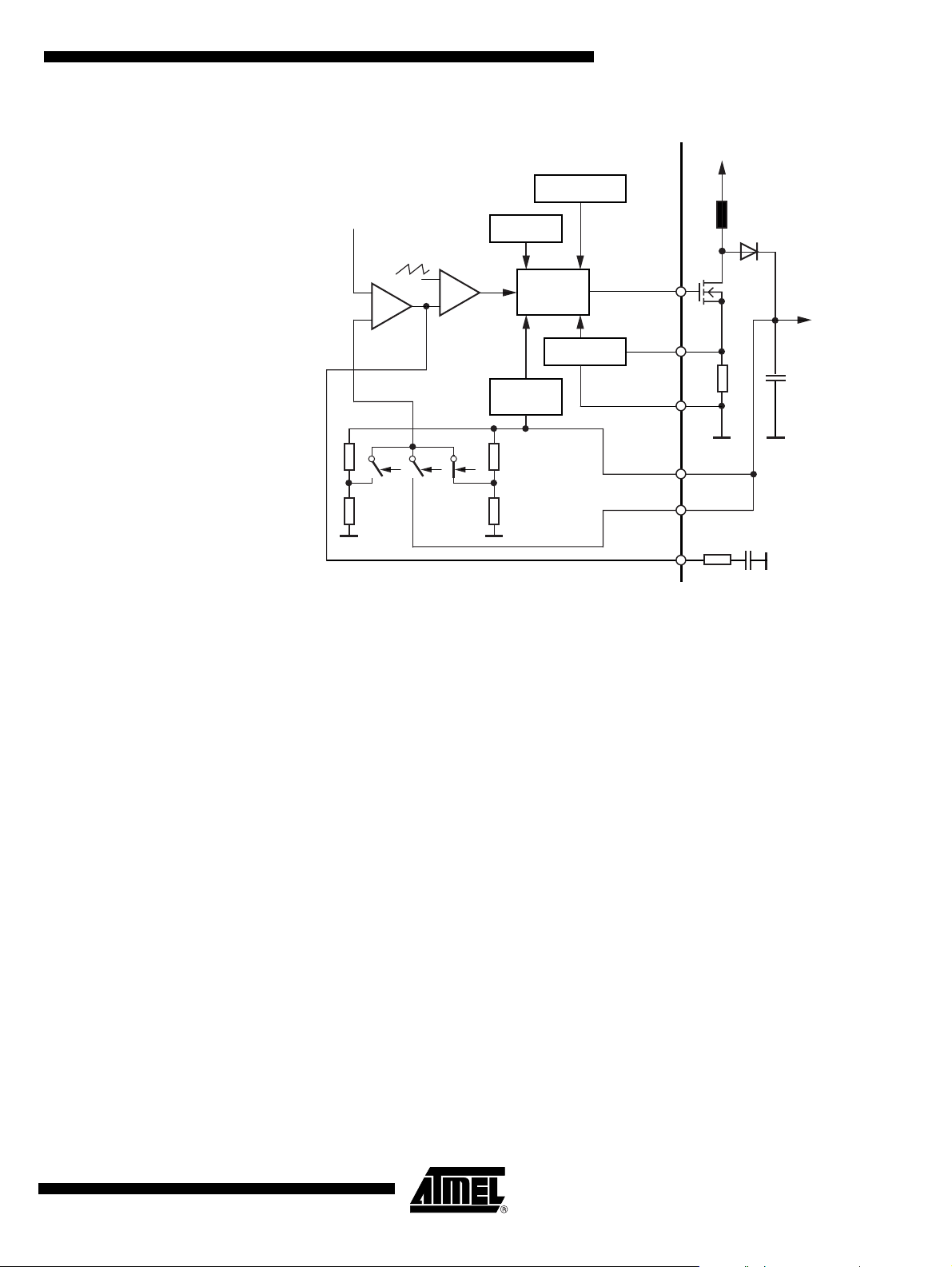

Figure 5-3. Block Diagram Start-up and Power-down Procedure

K15

V

= 3V to 4.15V

K15

(40 mV to 175mV Hysteresis)

Serial interface

(KEY - LATCH)

= 3.85V to 5V

V

K30

(50 mV to 150 mV Hysteresis)

V

= 6.1V to 8.1V (ON)

K30

(0.5V to 1V Hysteresis)

V

= 7.5V to 9V (ON)

EVZ

V

= 5.5V to 6.2V (OFF)

EVZ

V

= 6.77V to 7.2V

SAT

(200 mV to 500 mV Hysteresis)

K15GOOD

Comp

K30GOOD

Comp

CORESWAP

Comp

EVZGOOD

Comp

VSATGOOD

Comp

5V

IREF lost

signal

Power

sequencing

VEVZ

K30

CP

VK30

VEVZ

driver

IP

VCP

VSAT

driver

VEVZ

VPERI

driver

GEVZEVZEN

EVZ

SVSAT

VSAT

SVPER

VPERI

V

CP

V

EVZ

V

VSAT

V

VPERI

14

CORE_EN

V

= 1.25V to 1.7V

PERI

(50 mV to 150 mV Hysteresis)

Comp

ATA6264 [Preliminary]

driver

driver

VCP

VCP

K30

EVZ

SVCORE

VCORE

V

VCOR

4929B–AUTO–01/07

IP

VCORE

VCore

Page 15

ATA6264 [Preliminary]

Depending on the initial programming of the ATA6264, the start-up procedure takes place in different phases.

5.3.1 Start-up Procedure if V

is Programmed to Be 5V or 2.5V

VCORE

Phase1: After switching on the ignition key, K15 voltage will apply at pin K15. If, in addition, the

voltage at pin K30 is larger than 3.85V to 5V, the EVZ regulator will be enabled. The signal

K15GOOD can be replaced by the serial interface command KEYLATCH which can be set via

the serial interface.

Phase2: If V

is larger than 7.5V to 9V the VSAT regulator starts operating and the VCORE

EVZ

regulator will be enabled.

Phase3: After V

has reached 6.77V to 7.2V, the VPERI regulator starts working. The

VSAT

VCORE regulator starts operating depending on the charge pump voltage.

5.3.2 The Power-down Procedure Takes Place in Different Phases Phase1: If the ignition key is switched off, K15 voltage will vanish at pin K15. If the serial inter-

face command KEYLATCH is not set, the EVZ regulator stops working. The external charge

pump is still working because EVZ is above VSAT and the VSAT regulator is not in Perma-

nent-on mode. The charge-pump voltage still supplies the VSAT regulator and the VCORE

regulator. Because the EVZ regulator stops working, VCORE will be switched to EVZ.

Phase2: The EVZ capacitor will be discharged, and as soon as the voltage at pin VSAT drops to

low, the VSAT regulator will go into Permanent-on mode. If VSAT reaches Permanent-on mode,

the external charge pump stops working and the VSAT voltage falls analog to the EVZ voltage. If

the voltage at VSAT is below 6.27V to 7V, the VPERI regulator will be switched off. Depending

on the charge-pump voltage, the VCORE regulator stops working.

Phase3: When the voltage at the EVZ capacitor gets to be lower than 5.5V to 6.2V, VSAT is

switched off.

4929B–AUTO–01/07

15

Page 16

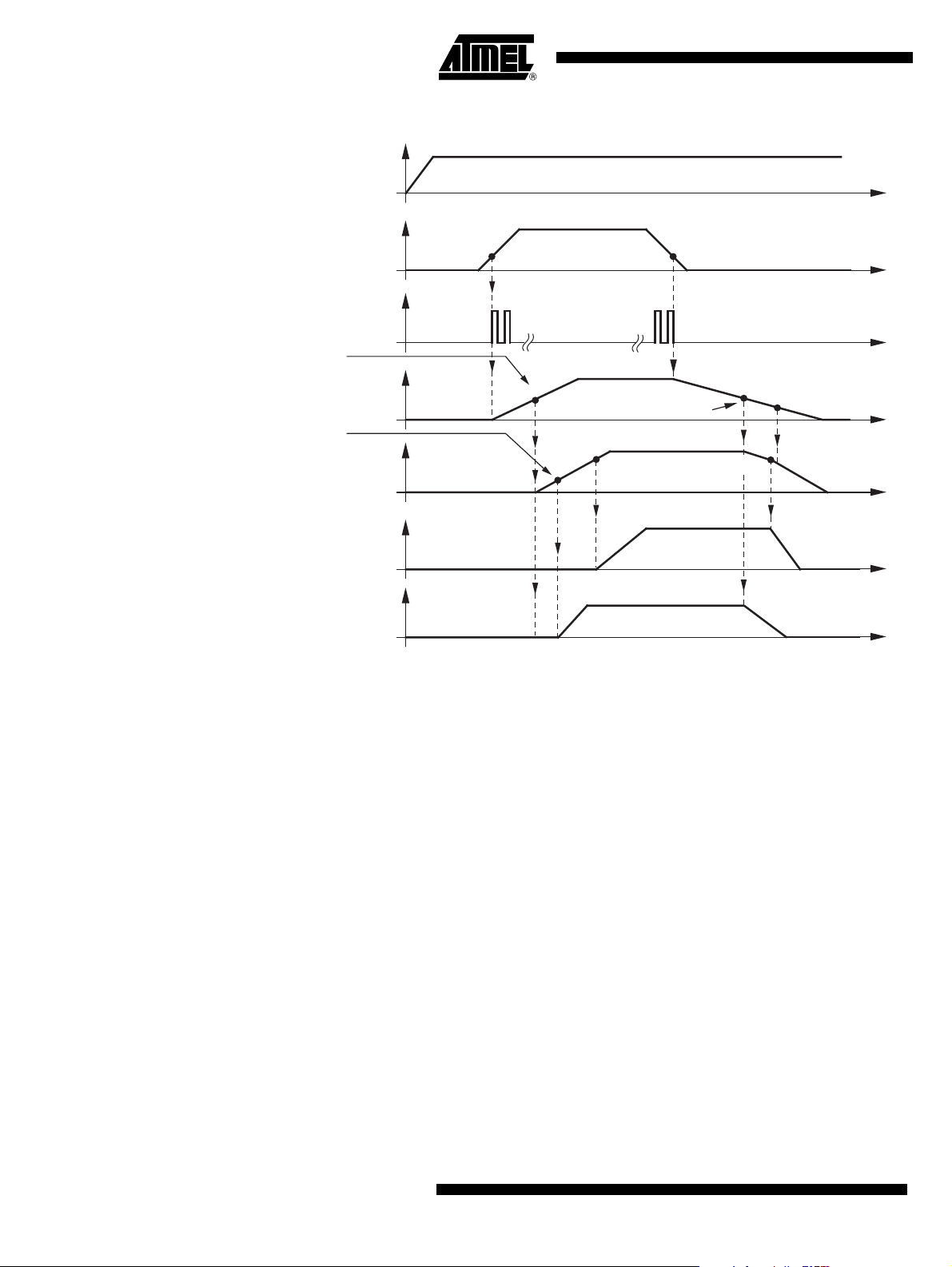

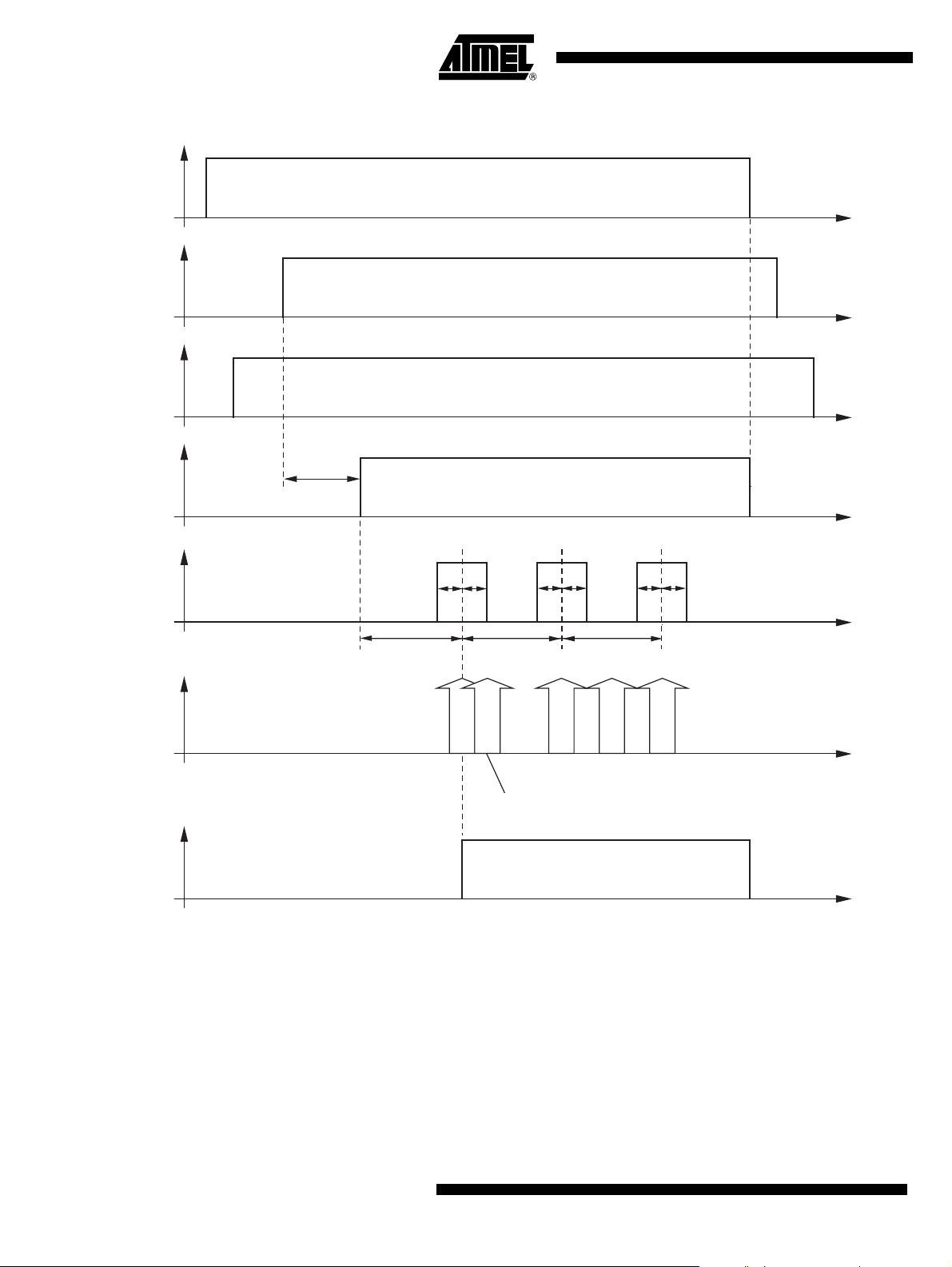

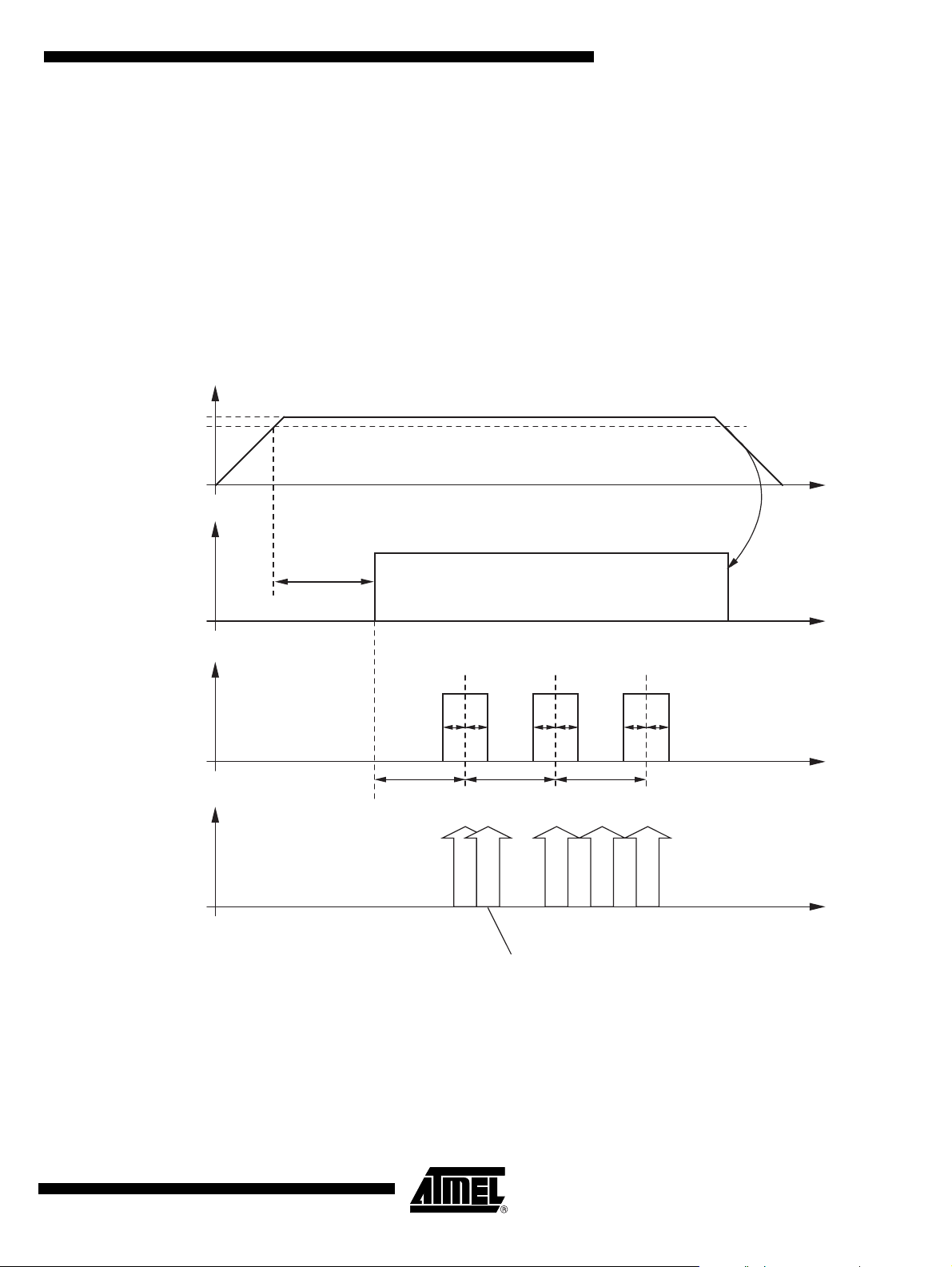

Figure 5-4. Start-Up and Power-Down Procedure if V

V

K30

V

K15

3V to 4.15V3V to 4.15V

Programmed to Be 5V or 2.5V

VCORE

t

Threshold to enable

VCORE regulator

Threshold to start

VCORE regulator

5.3.3 Start-up Procedure if V

Phase1: After switching on the ignition key, the K15 voltage will appear at pin K15. If, in addi-

tion, the voltage at pin K30 is larger than 3.85V to 5V, the EVZ regulator will be enabled. The

signal K15GOOD can be replaced by the serial interface command KEYLATCH which can be

set by the serial interface.

V

GEVZ

V

EVZ

V

VSAT

V

VPERI

V

VCORE

Programmed to Be 1.88V

VCORE

7.5V to 9V

too low EVZ voltage

VSAT goes into On Mode

charge pump deactivated

6.77V to 7.2V 7V to 6.27V

t

t

5.5V to 6.2V

t

t

t

t

16

Phase2: If VEVZ is larger than 7.5V to 9V, the VSAT regulator starts operating.

Phase3: After VVSAT has reached 6.77V to 7.2V, the VPERI regulator starts working.

Phase4: If VVPERI is higher than 1.25V to 1.7V, the VCORE regulator will be enabled.

ATA6264 [Preliminary]

4929B–AUTO–01/07

Page 17

ATA6264 [Preliminary]

5.3.4 The Power-down Procedure for V

Phase1: If the ignition key is switched off, the K15 voltage will vanish at pin K15. If the serial

interface command KEYLATCH is not set, the EVZ regulator stops working. The external charge

pump is still working because EVZ is above VSAT and the VSAT regulator is not in the Permanent-on mode. The charge-pump voltage still supplies the VSAT regulator and the VCORE

regulator. Because the EVZ regulator stops working, VCORE will be switched to EVZ.

Phase2: The EVZ capacitor will be discharged, and as soon as the voltage at pin VSAT drops

too low, the VSAT regulator will go into Permanent-on mode. If VSAT reaches Permanent-on

mode, the external charge pump stops working and the VSAT voltage falls analog to the EVZ

voltage. If the voltage at VSAT is below 6.27V to 7V, the VPERI regulator will be switched off.

Depending on the charge-pump voltage, the VCORE regulator stops working. The power

sequencing function for the VPERI regulator is still active and guarantees a maximum voltage

difference between VPERI and VCORE of 2.8V

Phase3: After VVPERI becomes lower than 1.1V to 1.55V, the VCORE regulator has to stop

working.

Phase4: When the voltage at the EVZ capacitor is lower than 5.5V to 6.2V, VSAT is switched

off.

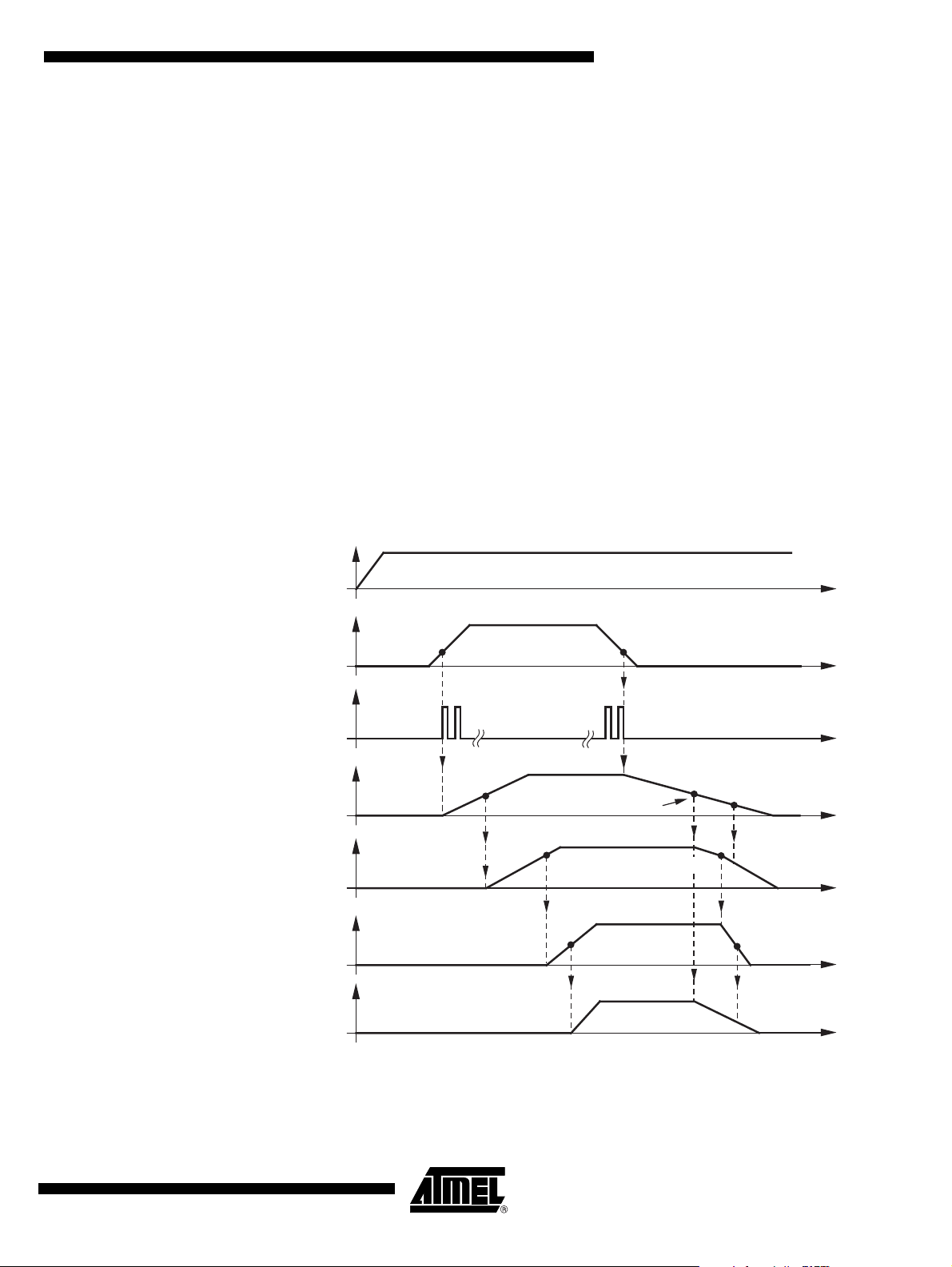

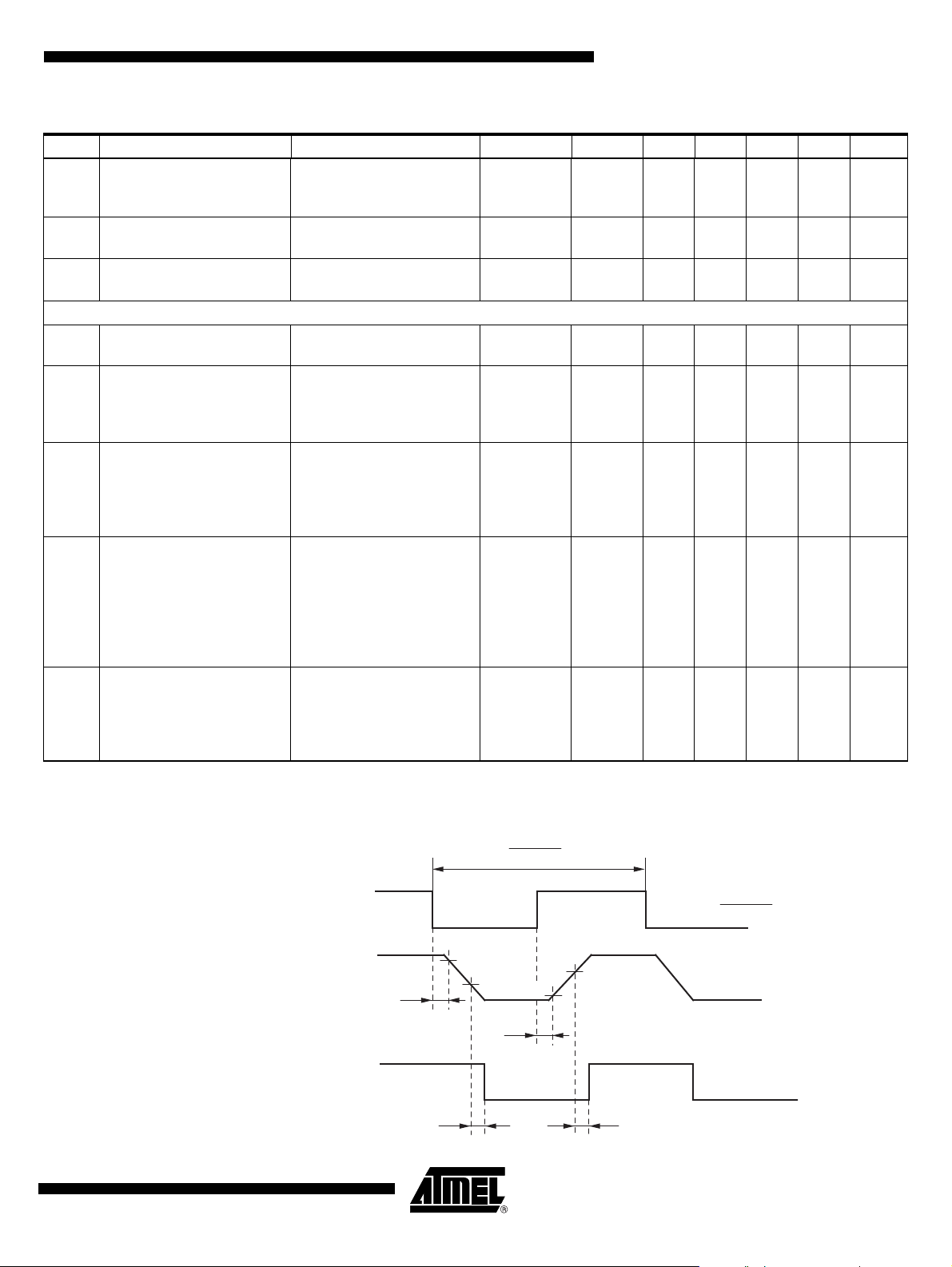

Figure 5-5. Start-up and Power-down Procedure if V

V

K30

is Programmed to be 1.88V

VCORE

Programmed to Be 1.88V

VCORE

V

V

V

V

VCORE

V

K15

GEVZ

V

EVZ

VSAT

VPERI

7.5V to 9V

3V to 4.15V3V to 4.15V

too low EVZ voltage

VSAT goes into On Mode

charge pump deactivated

t

t

t

5.5V to 6.2V

t

7V to 6.27V6.77V to 7.2V

t

1.1V to 1.55V1.25V to 1.7V

t

t

4929B–AUTO–01/07

17

Page 18

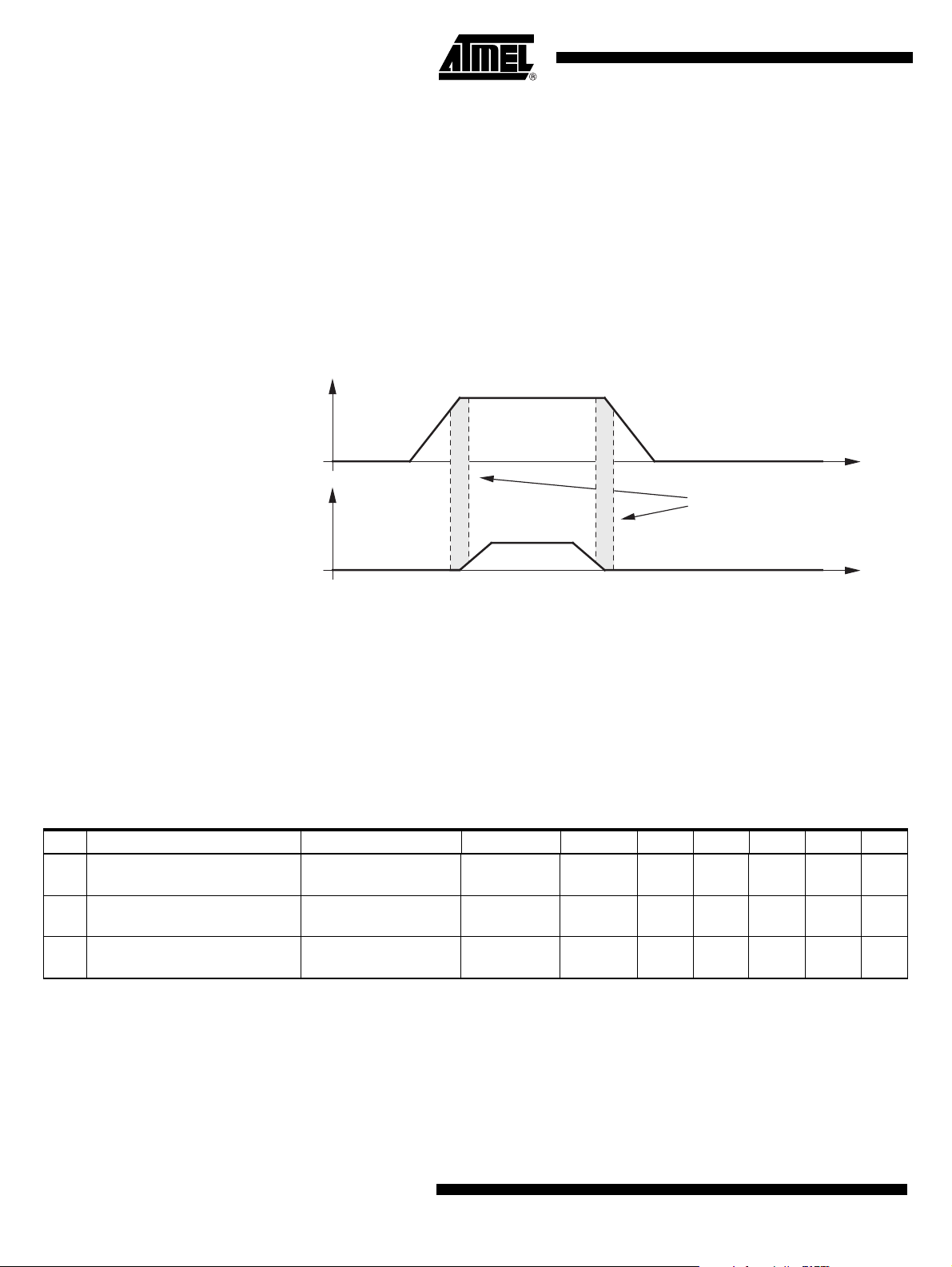

6. Power Supply Sequencing

(Only active when initial programming sets V

In order to meet the requirements of several dual-voltage-supply microcontrollers, a

power-sequencing function is implemented. The ATA6264 ensures that the voltage difference

VPERI – VCORE will not exceed 2.8V.

The voltage difference between VPERI and VCORE is monitored. In error cases, for example, if

the VCORE regulator does not start to work, the difference may rise above the 2.8V threshold. In

this case, the VPERI regulator is switched off before reaching this level and switched on again if

the voltage difference drops below a hysteresis value.

Figure 6-1. Example for Incorrect Ramp Up

V

VPERI

3.3V

= 1.88V and V

VCORE

VPERI

= 3.3V)

V

VCORE

1.88V

Not allowed area:

- V

V

VPERI

VCORE

>

2.8V

t

Necessary for operation:

t

V

= 0V to 40V, V

EVZ

= 3.7V to 5.47V

INT

Operating conditions of all other supply pins:

V

K30

, V

VSAT

, V

VPERI

and V

are within functional range limits, Tj = –40°C to 150°C

VCORE

Other pins:

As defined in Section 4. ”Functional Range” on page 8.

Table 6-1. Electrical Characteristics – Power Supply Sequencing

No. Parameters Test Conditions Pin Symbol Min Typ. Max. Unit Type*

Maximum voltage difference

5.1

5.2a

5.2b

– V

V

VPERI

VCORE

Voltage level V

switch off VPERI regulator

Hysteresis for V

enable VPERI regulator

VPERI

VPERI

– V

– V

VCORE

VCORE

to

to

VPERI,

VCORE

VPERI,

VCORE

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

V

– V

V

– V

VPERI

VCORE

VPERI

VCORE

V

HYS

02.8VA

2.3 2.8 V A

100 mV A

18

ATA6264 [Preliminary]

4929B–AUTO–01/07

Page 19

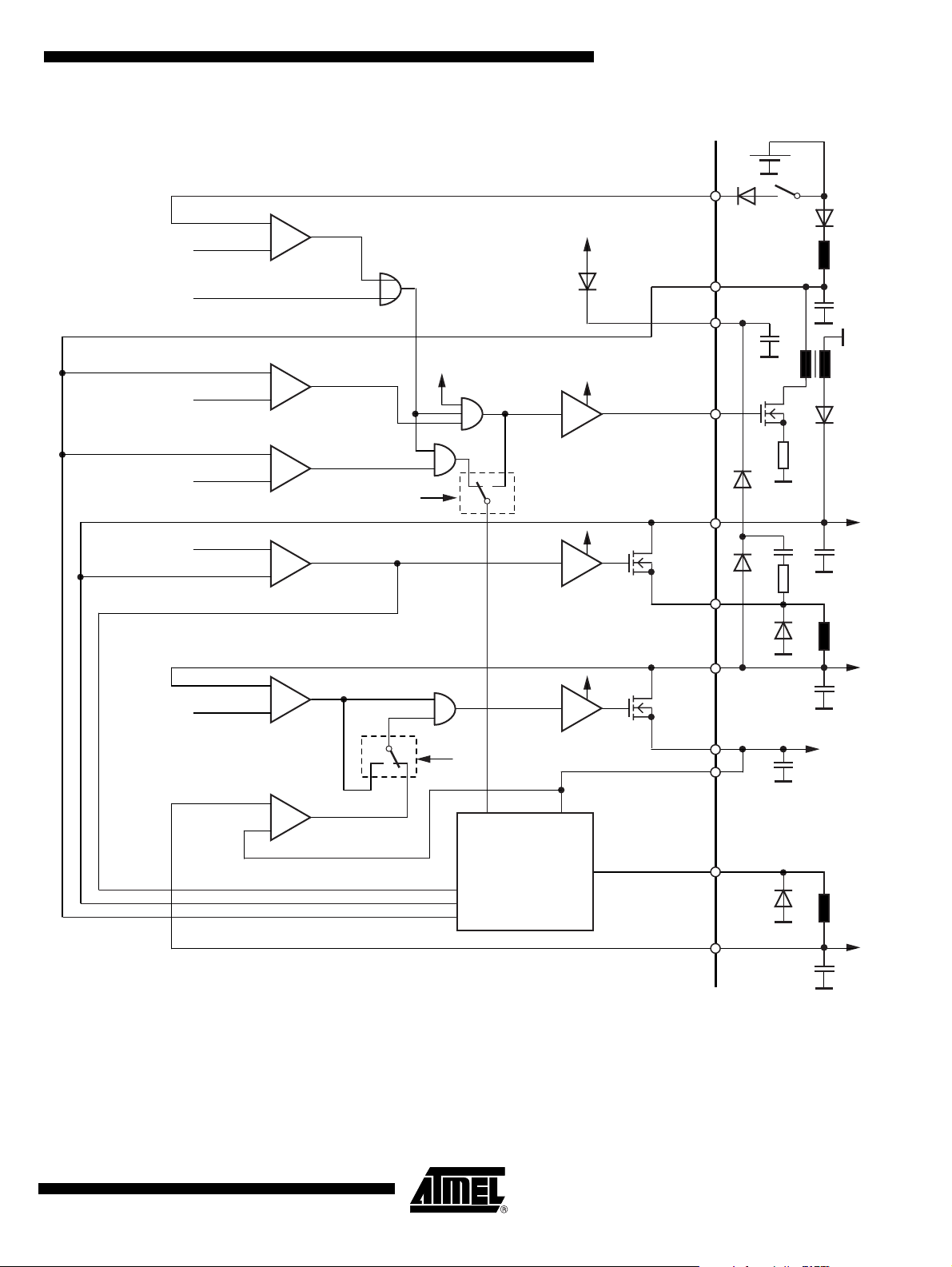

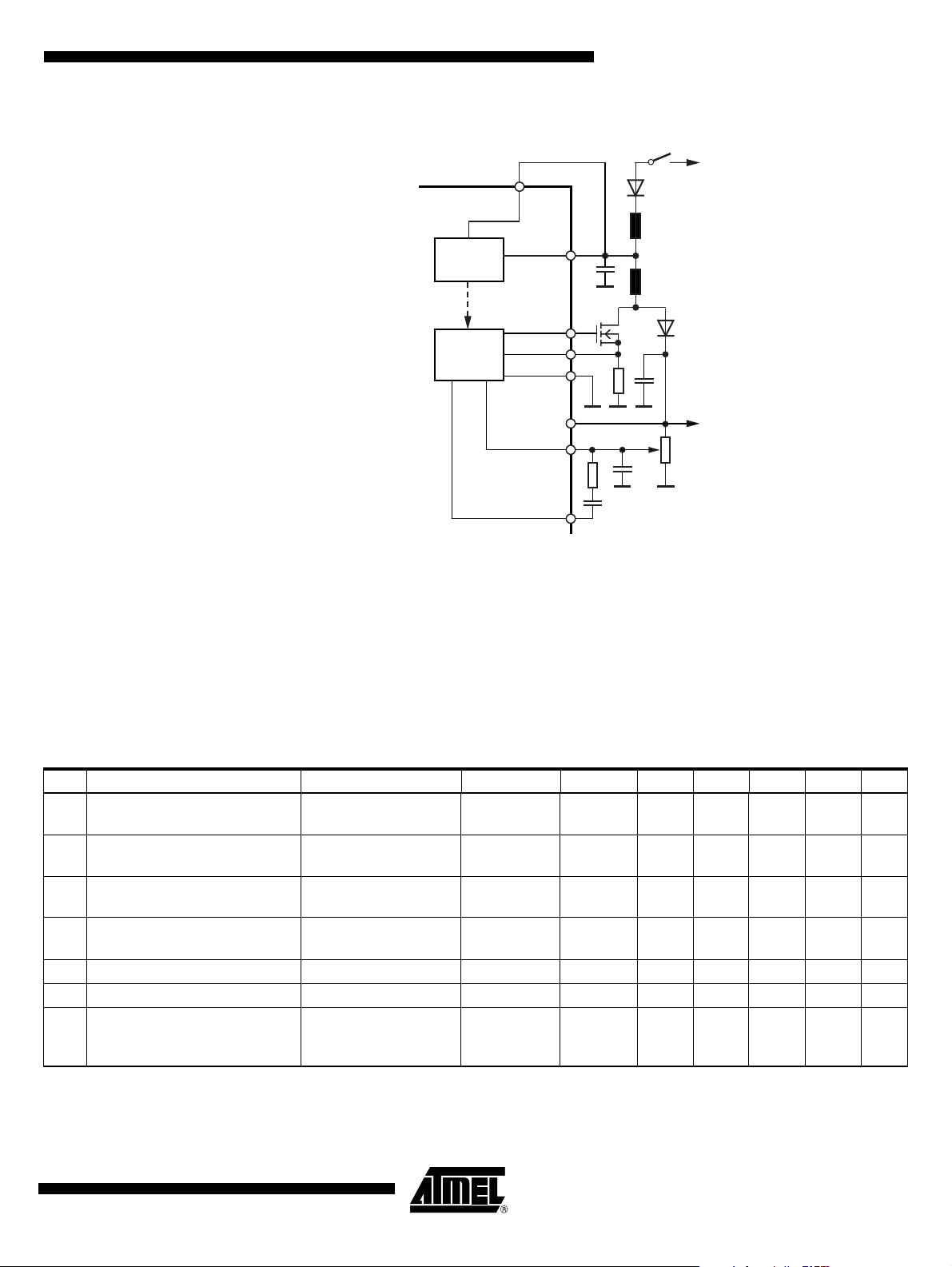

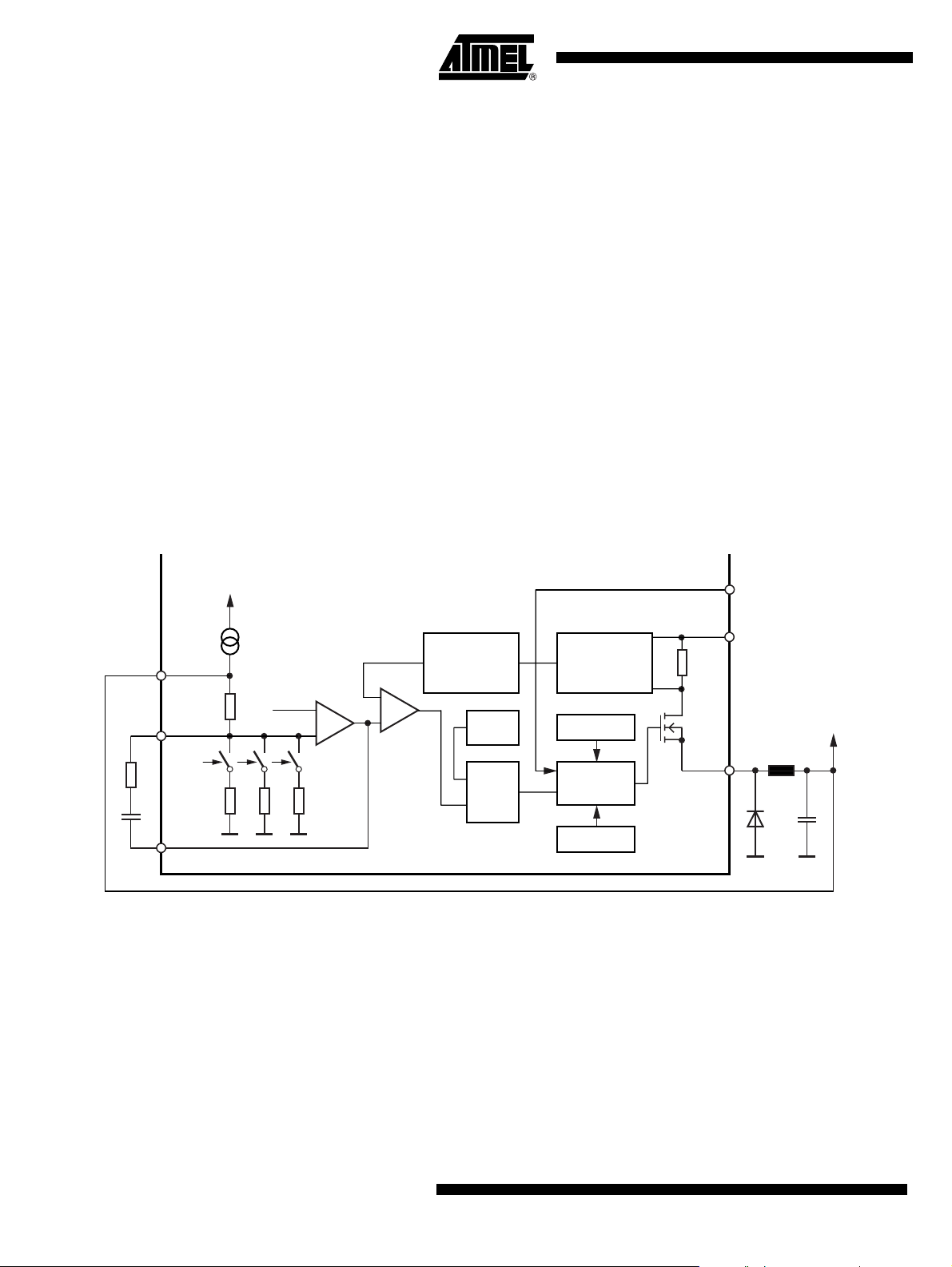

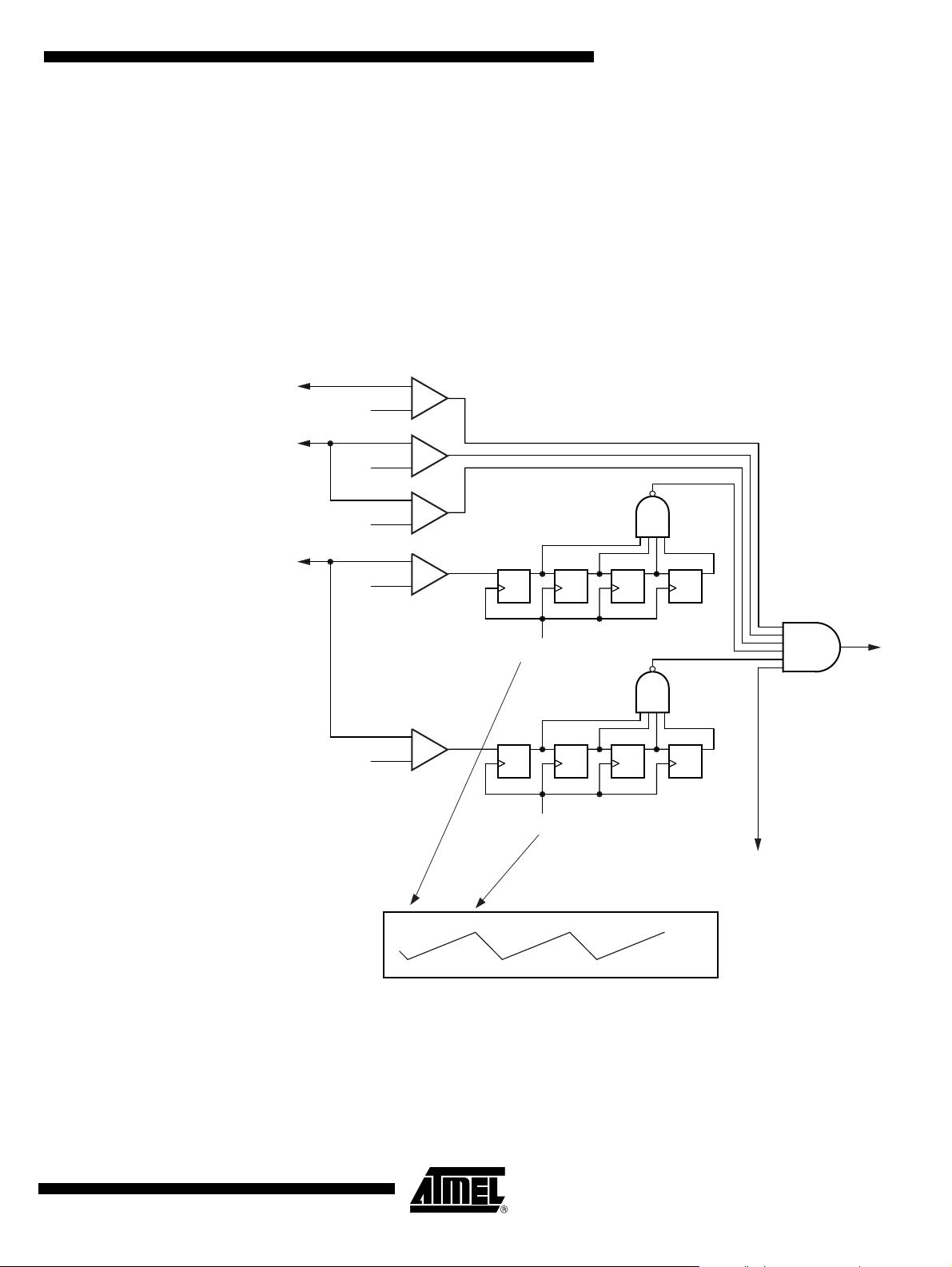

Figure 6-2. Block Diagram Power Supply Sequencing

E

ATA6264 [Preliminary]

K15

V

= 3V to 4.15V

K15

(40 mV to 175mV Hysteresis)

Serial interface

(KEY - LATCH)

= 3.85V to 5V

V

K30

(50 mV to 150 mV Hysteresis)

V

= 6.1V to 8.1V (ON)

K30

(0.5V to 1V Hysteresis)

V

= 7.5V to 9V (ON)

EVZ

V

= 5.5V to 6.2V (OFF)

EVZ

V

= 6.77V to 7.2V

SAT

(200 mV to 500 mV Hysteresis)

K15GOOD

Comp

K30GOOD

Comp

CORESWAP

Comp

EVZGOOD

Comp

VSATGOOD

Comp

5V

IREF lost

signal

IP

IP

VEVZ

VEVZ

driver

VSAT

driver

VPERI

driver

VK30

VCP

VEVZ

K30

CP

GEVZEVZEN

EVZ

SVSAT

VSAT

SVPER

VPERI

V

CP

V

EVZ

V

VSAT

V

VPERI

4929B–AUTO–01/07

Delta

< 2.8V

V

CORE

- Regulator

SVCORE

VCORE

V

VCOR

19

Page 20

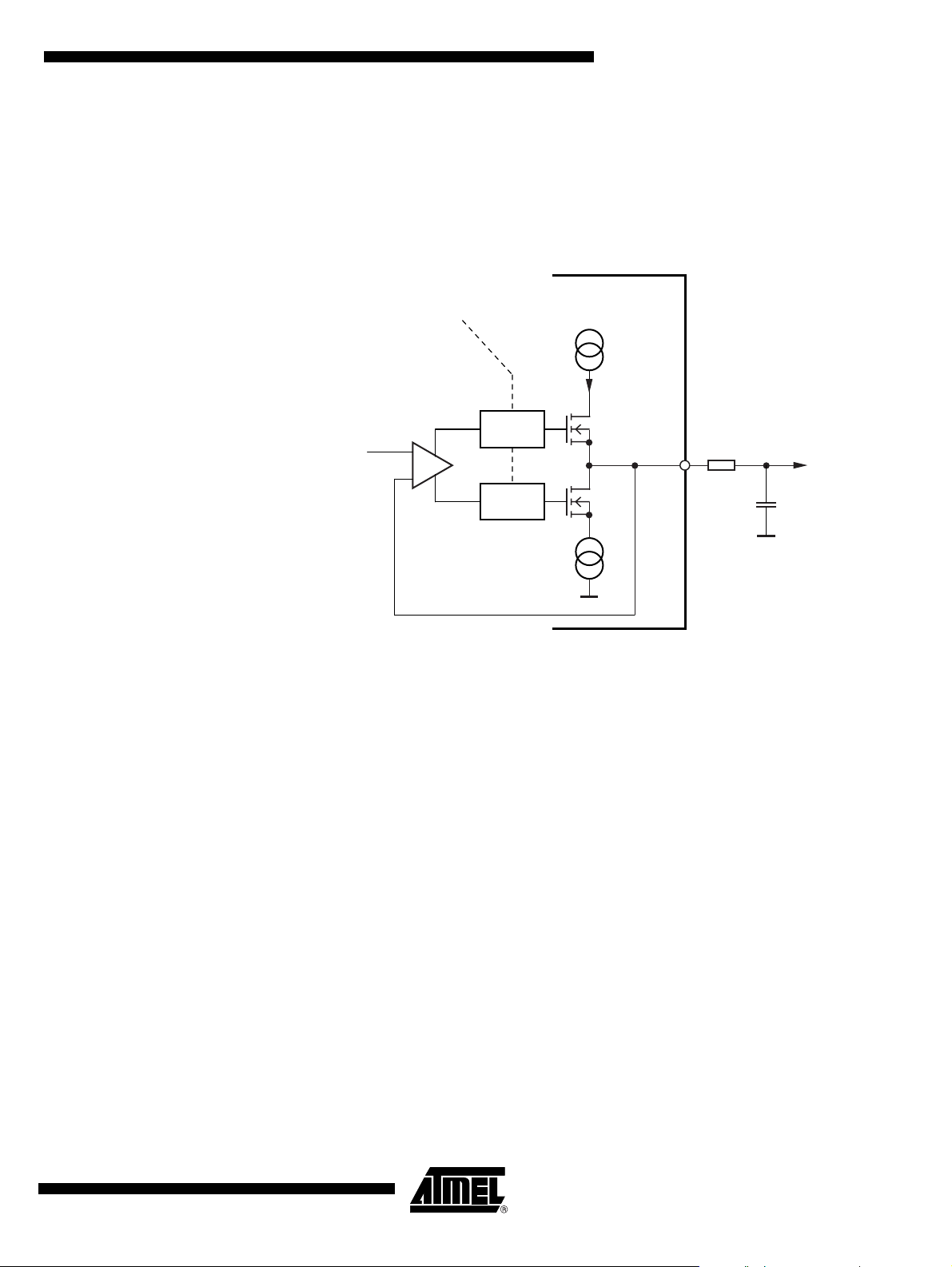

7. Charge Pump

To supply the VSAT and VCORE drivers, an external charge pump is provided. Both FETs

driven by the high charge pump voltage V

to ensure that they can be switched to a low-ohmic

CP

(1)

are

state. For correct function of the charge pump, an external capacitor of C = 47 nF has to be connected to pin SVSAT, and another of C = 100 nF to pin CP. A double diode has to be

implemented for proper function of the charge pump. An external series resistor is recommended to suppress spikes during switching of the SVSAT. The CP block is supplied by EVZ

and VSAT voltage and starts to operate as soon as the thresholds for VK15, K30 and EVZ are

achieved. An additional start-up circuitry is implemented to support the VSAT driver during the

start-up phase, thus enabling a reliable system startup.

The charge pump has an output CP-OUT to supply the external circuitry, and can be switched

via the SPI. It is capable of 250 µA.

Figure 7-1. Block Diagram Charge Pump

External circuit

CP-Out

Status

register

I = 1.4 mA

CP

Serial

interface

Note: 1. Connected to the drivers (see Figure 5-3)

EVZ

SVSATVSAT

REFREF

Status

register

20

ATA6264 [Preliminary]

4929B–AUTO–01/07

Page 21

ATA6264 [Preliminary]

Necessary for operation:

V

= 5.5V to 40V or V

EVZ

Operating conditions of all other supply pins:

V

VSAT

, V

VPERI

and V

VCORE

Other pins:

As defined in Section 4. ”Functional Range” on page 8.

Table 7-1. Electrical Characteristics – Charge Pump

No. Parameters Test Conditions Pin Symbol Min Typ. Max. Unit Type*

6.11 Supply current at pin CP

Time between wrong CP-OUT

6.12

voltage and valid data in status

register

Current limitation at pin

6.13

CP-OUT

Voltage difference VCP – V

6.14

for detecting wrong CP

Time between wrong CP

6.15

voltage and valid data in status

register

Voltage difference V

V

6.16

for detecting wrong

EVZ

CP-OUT

CP-OUT

6.17 Voltage at pin CP

6.18 Voltage at pin CP

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

CP off, supply of

internal circuitry

Note: Threshold is in

EVZ

the range of 5V to 7V

–

Note: Threshold is in

the range of 5V to 7V

= 5.5V to 40V,

V

EVZ

V

< V

K30

ICP+I

EVZ

CP_Out

(current consumption of

V

and V

SAT

be added)

= 5.5V to 40V,

V

EVZ

< V

V

K30

ICP+I

EVZ

CP_Out

(current consumption of

and V

V

SAT

be added)

= –100 µA

CORE

= –100 µA

CORE

= 5.5V to 40V, V

K30

> 3V, V

K15

= 3.7V to 5.47V

VINT

are within functional range limits, Tj = –40°C to 150°C

have to

have to

CP I

CP-OUT t

CP-OUT I

CP-OUT

CP V

CP t

CP-OUT V

CP V

CP V

CP

d

Diff

d

Diff

CP

CP

050µAA

050µsA

–0.8 –4.2 mA A

050µsA

V

+ 7 V

EVZ

V

+ 7 V

K30

5VA

5VA

+ 11 V A

EVZ

+ 11 V A

K30

4929B–AUTO–01/07

21

Page 22

8. GKEY Function

The GKEY function is used to enable or disable the ECU via a powerless signal. If the voltage at

pin K15 is larger than 3V to 4.15V, the charge pump and the EVZ regulator (for correct EVZ

function, the K30 pin has to be connected to the battery) will start operating. If the K15 pin is

open, an internal pull-down resistor of approximately 220 kΩ discharges the pin. A logical con-

nection between the voltage at the K15 pin, a serial-interface-driven latch command, and the

K30 voltage determines the EVZ Enable signal. In order to achieve the Switch Function of the

GKEY function, a transformer has to be used.

Table 8-1. Overview of the Start-up Conditions

Note: 1. Less than the value shown in number 7.3 of Table 8-2 on page 23

Figure 8-1. Application With Low-current Switch (GKEY Function Used)

Serial-interface-

driven Latch

V

K30

Low

High

High

1)

2)

2)

V

K15

(Default: “0” = OFF) EVZ Regulator

x x Disabled

3)

High

xEnabled

x1Enabled

2. Greater than the value shown in number 7.3 of Table 8-2 on page 23

3. Greater than the value shown in number 7.1 of Table 8-2 on page 23

V

BATT

GKEY-

Logic

EVZ

K15

COMEVZO

K30

GEVZ

OCEVZ

GNDB

EVZ

FBEVZ

V

EVZ

22

ATA6264 [Preliminary]

4929B–AUTO–01/07

Page 23

ATA6264 [Preliminary]

Figure 8-2. Application With High Current Switch (GKEY Function Not Used)

V

BATT

K15

GKEY-

Logic

EVZ

K30

GEVZ

OCEVZ

GNDB

EVZ

FBEVZ

COMEVZO

Necessary for operation:

= 3V to 40V, V

V

K15

= 3.85V to 40V

K30

Operating conditions of all other supply pins:

V

, V

, V

EVZ

SAT

PERI

and V

are within functional range limits, Tj = –40°C to 150°C

CORE

Other pins:

As defined in Section 4. ”Functional Range” on page 8.

V

EVZ

Table 8-2. Electrical Characteristics – GKEY Function

No. Parameters Test Conditions Pin Symbol Min Typ. Max. Unit Type*

Voltage level at K15 to enable

7.1

the EVZ regulator

Hysteresis at K15 to disable the

7.2

EVZ regulator

Voltage level at K30 to enable

7.3

the EVZ regulator

Hysteresis at K30 to disable the

7.4

EVZ regulator

7.5 Pull-down resistor at K15 K15 R

7.6 Pull-down resistor at K30 K30 R

7.7 Current at K15

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

4929B–AUTO–01/07

increasing,

V

K15

V

> 5V

K30

V

increasing,

K30

> 4.15V

V

K15

0V ≤ V

K15

≤ 40V,

AMUX measurement

EVZ active

K15 V

K15 V

K30 V

K30 V

K15 I

K15

K15

K30

K30

K15

K30

K15

34.15VA

40 175 mV A

3.85 5 V A

50 150 mV A

70 365 kΩ A

320 1700 kΩ A

01.1mAA

23

Page 24

9. EVZ Step-up Regulator

A boost converter generates the supply voltage for energy reserve and firing capacitors in the

system. Using a voltage divider at pin FBEVZ, this voltage can be adjusted between 15V and

40V. Thus, high-voltage charged capacitors will be used to supply the whole system during the

stand-alone time (for example, broken K30 line after a crash). The step-up regulator has to start

running as soon as a certain threshold voltage at the K15 pin is exceeded. The regulator has to

stop running again if the voltage at the K15 pin falls below a voltage level (or voltage at pin K30

is missing, see Section 5.3 ”Start-up and Power-down Procedure” on page 14).

An inductor is PWM-switched by an external n-channel power FET with a fixed frequency of

100 kHz. A driver stage for the external FET is integrated into the ATA6264. The current limitation of the external FET is implemented by using an external resistor in series between the

source connection of the external FET and GND, sensing the voltage drop at this resistor via the

pins OCEVZ and GNDA.

The reference section provides a reference voltage of 1.24V for the regulation loop. An error

amplifier compares the reference voltage with the feedback signal, which is provided either from

two different serial-interface-programmable internal dividers (VEVZ1 = 22V, VEVZ2 = 31.5V) or

an external voltage divider network (VEVZExt). These dividers determine the output voltage

EVZ.

Figure 9-1. EVZ Regulator With External Divider

K30

Bandgap

reference

Sawtooth oscillator

+

+

-

Error

amp.

SPI

-

SPI

PWM

comp.

SPI

Max. duty-cycle

Low battery

Logic and

driver

EVZ

overvoltage

Overcurrent

GEVZ

OCEVZ

GNDA

EVZ

FBEVZ

COMEVZO

L

R

VZ1

R

C

VZ2

+

24

ATA6264 [Preliminary]

4929B–AUTO–01/07

Page 25

Figure 9-2. EVZ Regulator With Internal Divider

ATA6264 [Preliminary]

K30

Bandgap

reference

Sawtooth oscillator

+

+

-

Error

amp.

SPI

-

SPI

PWM

comp.

SPI

Max. duty-cycle

Low battery

Logic and

driver

EVZ

overvoltage

Overcurrent

GEVZ

OCEVZ

GNDA

EVZ

FBEVZ

COMEVZO

L

C

+

A draft formula for calculating the EVZ voltage, which is programmed by the external voltage

divider network at pin FBEVZ, is:

R

+

VZ1RVZ2

V

EVZ

V

REF

--------------------------------

×=

R

VZ2

The pins EVZ and FBEVZ have to be shorted in applications without an external divider in order

to ensure a safe operation of the ATA6264 in the case of an EVZ-pin fault. If the voltage at pin

FBEVZ is larger than the voltage at pin EVZ, the ATA6264 switches the feedback path automatically to pin FBEVZ. The remaining voltage at FBEVZ causes the regulator to switch off.

The output of the error amplifier is compared with a periodic linear ramp of a saw-tooth generator by the PWM comparator. A logic signal with variable pulse width is generated, which controls

the PWM frequency of the external FET. A maximum duty cycle is determined by the duration of

the falling ramp of the saw-tooth oscillator. The saw-tooth generator is controlled by the internal

100-kHz oscillator.

4929B–AUTO–01/07

25

Page 26

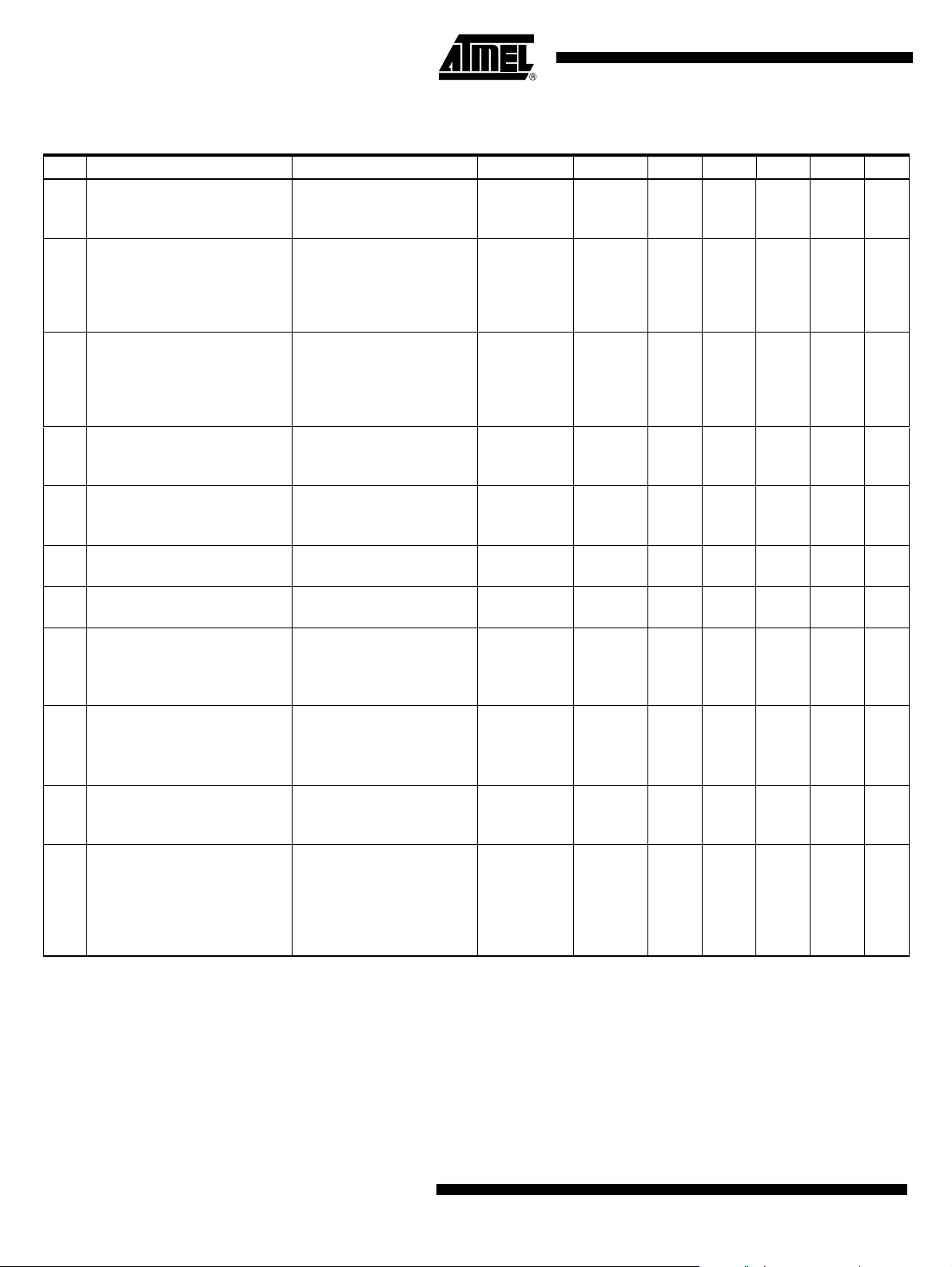

Figure 9-3. Functional Principle of the EVZ Regulator

Sawtooth

Error amp. output = f (V

on

PWM

output

off

EVZ

)

t

t

The output transistor conduction is suppressed immediately if the current through the power

FET exceeds a certain level, determined by the voltage drop across an external resistor in the

range of 0.2Ω. The ATA6264 itself will see a voltage at the OCEVZ pin. If this voltage exceeds

typically 0.5V, the output transistor conduction has to be suppressed.

The external FET also has to be switched off if a low battery voltage at K30 or overvoltage on pin

EVZ is detected. Multiple output pulses at pin GEVZ during one oscillator period are suppressed

by internal logic.

In the default state - for example, before the minimum input voltage for starting the regulator has

been reached - the external transistor is switched off.

During startup, the voltage on pin EVZ is too low and the PWM comparator requires a duty cycle

of more than 90%. Due to an increasing inductance current, after several periods the overcurrent sensor becomes active and reduces the maximum duty cycle to improve magnetic energy

transfer.

Figure 9-4. Output Current During Start-up

Output

current

Current limit

t

A capacitance of 10 mF or more may be applied at pin EVZ. The equivalent series resistance

(ESR) should have a value of less than 0.5Ω.

After power-on, the default state of the internal dividers should always be the low EVZ voltage

divider.

The voltage at pin GNDA is compared with the voltage at pin GNDD, and if GNDA is not connected, bit b6 of the APACE status register is set. Pin GNDB is also compared with pin GNDD.

Pin GNDB not being connected will also result in bit b6 being set, and, additionally, in the EVZ

regulator being switched off.

26

ATA6264 [Preliminary]

4929B–AUTO–01/07

Page 27

ATA6264 [Preliminary]

Necessary for operation:

V

= 3V to 40V, V

K15

Operating conditions of all other supply pins:

V

, V

PERI

and V

SAT

Other pins:

As defined in Section 4. ”Functional Range” on page 8.

Table 9-1. Electrical Characteristics – EVZ Step-up Regulator

No. Parameters Test Conditions Pin Symbol Min Typ. Max. Unit Type*

V

≥ 8V or V

8.1 Switching frequency

8.2 Switching frequency

Voltage level at K15 to start the

8.3

EVZ regulator

Hysteresis at K15 to stop the

8.4

EVZ regulator

Voltage level at K30 to start the

8.5

EVZ regulator

Hysteresis at K30 to stop the

8.6

EVZ regulator

Voltage at pin GEVZ to switch

8.7

through the external driver

Voltage at pin GEVZ to switch

8.8

through the external driver

Driving current at pin GEVZ to

8.9

switch through the external

driver

Gate charge delivered to the

8.10

external FET

Gate charge delivered to the

8.11

external FET

8.12 Pull-down resistor at pin GEVZ GEVZ R

of dynamic sinking

R

8.13

8.15

Dson

transistor at GEVZ

Voltage between pins OCEVZ

and GND to detect overcurrent

8.16 Maximum switch duty cycle

8.17 Maximum switch duty cycle

8.18 Minimum switch duty cycle GEVZ D

Overvoltage at pin EVZ to switch

8.19

off the regulator

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

K30

(after startup)

4V < V

4V < V

(after startup)

See number 7.1 of

Table 8-2 on page 23

See number 7.2 of

Table 8-2 on page 23

See number 7.3 of

Table 8-2 on page 23

See number 7.4 of

Table 8-2 on page 23

≥ 3.85V to 5V

V

K30

(ON threshold)

≥ 7V GEVZ V

V

K30

V

GEVZ

V

GEVZ

V

GEVZ

≥ 8V or V

V

K30

(after startup)

V

EVZ

4V < V

4V < V

(after startup)

V

EVZExt

(via external divider)

= 5V to 40V, C

K30

are within functional range limits, Tj = –40°C to 150°C

CORE

≥ 8V

EVZ

< 8V or

K30

< 8V

EVZ

≤ 5V GEVZ I

= 5V GEVZ Q

= 10V GEVZ Q

≥ 8V

EVZ

= 200 pF to 2 nF, V

GEVZ

GEVZ f

GEVZ f

GEVZ V

GEVZ R

OCEVZ V

GEVZ D

GEVZ

GEVZ

GEVZ

GEVZ

GEVZ

GEVZ

GEVZ

GEVZ

GEVZ

OCEVZ

GEVZ

–5% 100 +5% kHz A

–10% 100 +10% kHz A

V

K30

0.5V

610VA

–600 –80 mA A

10 nC D

20 nC D

20 50 kΩ A

0.475 0.525 V A

87.5 90 92.5 % A

≥ 8V

< 8V or

K30

< 8V

EVZ

programmed

GEVZ D

VEVZ V

GEVZ

GEVZ

EVZ

75 90 92.5 % A

40.5 46.2 V A

= 3.7V to 5.47V

INT

–

V

K30

VA

28 Ω A

0%A

A

A

A

A

4929B–AUTO–01/07

27

Page 28

Table 9-1. Electrical Characteristics (Continued)– EVZ Step-up Regulator

No. Parameters Test Conditions Pin Symbol Min Typ. Max. Unit Type*

Overvoltage at pin EVZ to switch

8.19a

off the regulator

Overvoltage at pin EVZ to switch

8.19b

off the regulator

8.20 Overvoltage switch-off time

8.21 Overcurrent switch-off time

Switch-on delay time for the

8.22

boost converter output stage

Switch-on rise time for the boost

8.23

converter output stage

Switch-off delay time for the

8.24

boost converter output stage

Switch-off fall time for the boost

8.25

converter output stage

8.26 Leakage current at pin OCEVZ OCEVZ I

8.27 Leakage current at pin FBEVZ FBEVZ I

8.28 Switch-on threshold via FBEVZ

8.29 Switch-on threshold via FBEVZ

8.30 V

8.31

8.31a

8.31b

voltage #1 set by SPI

EVZ

V

voltage #2

EVZ

set by SPI

Temperature shutdown

activation

Hysteresis for reactivation of

GEVZ

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

V

programmed VEVZ V

EVZ1

programmed VEVZ V

V

EVZ2

Time between reaching

overvoltage and

reaching 90% of the

value at numbers 8.7

GEVZ t

and 8.8 of Table 9-1 on

page 27

Time between reaching

overcurrent and

reaching 90% of the

value at numbers 8.7

GEVZ t

and 8.8 of Table 9-1 on

page 27

GEVZ t

Time between 0.5V and

4.5V at GEVZ,

=2nF

C

GEVZ

GEVZ t

GEVZ t

Time between 4.5V and

0.5V at GEVZ,

=2nF

C

GEVZ

Band-gap tolerance

included

Band-gap tolerance

included

V

programmed,

EVZ1

Band-gap tolerance

GEVZ t

FBEVZ V

FBEVZ V

EVZ V

included

programmed,

V

EVZ2

Band-gap tolerance

EVZ V

included

EVZ

EVZ

offov

offoc

don

ron

doff

foff

OCEVZ

OCEVZ

FBEVZ

FBEVZ

EVZ1

EVZ2

T

off

T

hys

25 28.5 V A

35 39.5 V A

200 ns D

500 ns A

50 250 ns A

10 200 ns A

50 150 ns A

10 100 ns A

–10 +10 µA A

–10 +10 µA A

1.20 1.24 V A

1.24 1.28 V A

20 23 V A

28.6 33 V A

155 185 °C B

525KB

28

ATA6264 [Preliminary]

4929B–AUTO–01/07

Page 29

ATA6264 [Preliminary]

Table 9-1. Electrical Characteristics (Continued)– EVZ Step-up Regulator

No. Parameters Test Conditions Pin Symbol Min Typ. Max. Unit Type*

Error Amplifier

Output current at pin COMEVZO

8.32

sinking to low

Output current at pin COMEVZO

8.33

driving to high

8.34 Input offset voltage –10 +10 mV D

8.35 DC open-loop gain 70 dB D

8.36 Unity-gain bandwidth 2 MHz D

Output voltage low on pin

8.37

COMEVZO

Output voltage high on pin

8.38

COMEVZO

I

COMEVZO

I

COMEVZO

= 100 µA COMEVZO V

= –100 µA COMEVZO V

GNDA/GNDB Disconnect

8.40 GNDA lost detection V

GNDA

– V

GNDD

8.41 Delay for GNDA lost detection GNDA td 10 50 µs A

8.42 GNDB lost detection V

GNDB

– V

GNDD

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

COMEVZO I

COMEVZO I

GNDA V

GNDB V

COMEVZO

COMEVZO

COMEVZO

COMEVZO

GNDA

GNDB

0.4 3 mA A

–1000 –150 µA A

00.2VA

VINT –

0.3V

VINT V A

0.2 0.4 V A

0.2 0.4 V A

4929B–AUTO–01/07

29

Page 30

10. VSAT Power Supply

A stabilized VSAT supply is realized by a buck converter. An external inductance is

PWM-switched with a frequency of 200 kHz via an internal high-side DMOS power transistor.

The VSAT power supply is connected to the boost converter output (EVZ), and uses the stored

energy of the boost converter capacitor if the voltage at K30 is missing. The regulator uses both

current and voltage feedback. The basis for the regulation loop is a temperature-compensated

band-gap reference voltage, which is compared with the internally divided output voltage VSAT.

The error amplifier output is applied to the inverting input of a comparator, the current feedback

is connected with the positive input. The PWM flip-flop (which is set every 5 µs by the oscillator)

is reset if the current feedback reaches the error amplifier level. In order to adjust the compensation of the regulation loop and therefore improve the behavior in case of load changes in

continuous-mode operation, pin COMSATO has to be connected to COMSATI via a compensation network. Because of the fact that current-mode-controlled converters exhibit sub-harmonic

oscillations when operating at duty cycles higher than 50%, a slope compensation (which adds

an artificial ramp to the comparator) is implemented. If the regulator input voltage at pin EVZ is

too low, the regulator switches to a duty cycle of 100% (Permanent-on mode).

The VSAT voltage can be programmed via the serial interface to one of three different voltage

values during initial programming.

Figure 10-1. Functional Principle of the VSAT Regulator

CP

VSAT

COMSATI

SPI

OTP

COMSATO

EVZ

VSAT

SVSAT

+

Bandgap

reference

Slope

compensation

Current

measurement

and leading edge

blanking

+

+

-

Error

amp.

-

Comp.

S

R

OSC

Overcurrent

Logic and

Q

driver

Overvoltage

The duration of the output transistor conduction depends on the VSAT level and current feedback. Conduction is suppressed immediately if the current through the output transistor exceeds

850 mA typically. A logic circuit disables, in the case of short spikes, multiple-pulse operation

during one oscillating period. If pin VSAT is open (VSAT loss), an internal current source connected to a higher voltage than VSAT acts as pull-up for this pin, to prevent the VSAT voltage

from rising up to EVZ. In order to ensure the gate voltage for the output transistor, the driver

stage is supplied by the charge pump (pin CP).

30

ATA6264 [Preliminary]

4929B–AUTO–01/07

Page 31

ATA6264 [Preliminary]

Necessary for operation:

V

= 5.5V to 40V, VCP > V

EVZ

Operating conditions of all other supply pins:

V

, V

K30

PERI

and V

are within functional range limits, Tj = –40°C to +150°C

CORE

Other pins:

As defined in Section 4. ”Functional Range” on page 8.

Table 10-1. Electrical Characteristics – VSAT Power Supply

No. Parameters Test Conditions Pin Symbol Min Typ. Max. Unit Type*

V

voltage for the buck

EVZ

9.1

converter to start running

V

voltage for the buck

EVZ

9.2

converter to stop

Regulator switch-on time via pin

9.3

EVZ

Regulator switch-off time via pin

9.4

EVZ

9.5 Regulator switching frequency V

9.5a Regulator switching frequency 5.5V > V

9.6 Output current limit SVSAT I

9.7 R

9.8

of output transistor SVSAT R

Dson

Output voltage #1 only at

=3.3V

V

PERI

9.9 Output voltage #2

9.10 Output voltage #3

9.11 Output transistor switch-on time

9.12 Output transistor switch-on time

Overvoltage switching off the

9.13

regulator

9.14 Overvoltage switch-on time

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Notes: 1. Depending on implementation of slope compensation; sub-harmonics must be prevented

2. The value of the minimum load current must be higher than the internal pull-up current at pin VSAT to ensure proper function of the regulator

EVZ V

≥ 8V SVSAT f

EVZ

≥ 8V SVSAT f

EVZ

Band-gap tolerance

included

V

programmed,

VSAT2

Band-gap tolerance

included

V

programmed,

VSAT3

Band-gap tolerance

included

Time between reaching

0.1 × (V

EVZmax

– V

and

0.9 × (V

EVZmax

– V

Time between reaching

0.9 × (V

EVZmax

– V

and

0.1 × (V

EVZmax

– V

Time between reaching

overvoltage and reaching

90% of V

SVSAT

maximum

under on condition

+ 7V, V

EVZ

SVSATmin

SVSATmin

SVSATmin

SVSATmin

INT

EVZ V

SVSAT t

SVSAT t

VSAT V

VSAT V

VSAT V

)

)

)

)

VSAT V

SVSAT t

= 3.7V to 5.45V

EVZ

EVZ

SVSAT

SVSAT

SVSAT

SVSAT

SVSAT

SVSAT

VSAT1

VSAT2

VSAT3

VSAT

SVSAToff

7.5 9 V A

5.5 6.2 V A

020µsA

05µsA

–5% 200 +5% kHz A

–10% 200 +10% kHz A

0.8 1 A A

1 Ω A

–4% 7.8 +4% V A

–4% 9.1 +4% V A

–4% 10.4 +4% V A

150 ns A

150 ns A

1.1 ×

V

SATX

VA

00.4µsA

4929B–AUTO–01/07

31

Page 32

Table 10-1. Electrical Characteristics (Continued)– VSAT Power Supply

No. Parameters Test Conditions Pin Symbol Min Typ. Max. Unit Type*

Time between reaching

9.15 Overcurrent switch-on time

9.16 Leakage current at pin SVSAT Output transistor off SVSAT I

Error Amplifier

Maximum output current at pin

9.17

COMSATO sinking to low

Maximum output current at pin

9.18

COMSATO sourcing to high

Input impedance at pin

9.19

COMSATI

9.20 Input offset voltage –10 +10 mV D

9.21 DC open-loop gain 70 dB D

9.22 Unity-gain bandwidth 2 MHz D

9.23 Output voltage low I

9.24 Output voltage high I

9.25 Leading-edge blanking time t

Slope of artificial ramp for slope

9.26

compensation

9.27 VSAT loss detection threshold

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Notes: 1. Depending on implementation of slope compensation; sub-harmonics must be prevented

2. The value of the minimum load current must be higher than the internal pull-up current at pin VSAT to ensure proper function of the regulator

overcurrent and reaching

90% of V

SVSAT

maximum

under on condition

COMSATO

COMSATO

(2)

= 165 µA COMSATO V

= –85 µA COMSATO V

SVSAT t

COMSATO I

COMSATO I

COMSATI R

SVSAToff

SVSAT

COMSATO

COMSATO

COMSATI

COMSATO

COMSATO

blank

V

dV/dt 150

I

Load

00.5µsA

–10 +10 µA A

200 3000 µA A

–165 –85 µA A

923kΩ A

00.3VA

–

VINT

0.6V

V

VINT

VA

150 200 ns D

(1)

240

(1)

mV/µs D

01.5mAD

32

ATA6264 [Preliminary]

4929B–AUTO–01/07

Page 33

11. VPERI Power Supply

With the V

voltage. This voltage is intended to be used for sensitive components, for example, sensors or

reference inputs of A/D converters from microcontrollers. For this reason, a linear regulator is

implemented to guarantee high ripple rejection and a precise voltage. The regulator output is

short-circuit protected by an overcurrent protection. If pin VPERI is disconnected, the regulator

is switched off and RESQ/RESQ2 are set to low.

ATA6264 [Preliminary]

regulator a stabilized and ripple-free voltage is generated out of the VSAT supply

PERI

Figure 11-1. Functional Principle of the V

V

Peripheral

Linear regulator

Peripheral

VSAT

SVPERI

VPERI

Regulator

V

SAT

V

Peripheral

If a higher current capability of the regulator is requested or if the power dissipation of the linear

regulator is too high, an external transistor can boost the regulator.

Figure 11-2. Functional Principle of the VPERI Regulator With External Boost Transistor

V

SAT

V

Peripheral

V

Peripheral

Linear regulator

VSAT

SVPERI

VPERI

4929B–AUTO–01/07

The VPERI voltage can be programmed via the serial interface to one of two different voltage

values during initial programming.

33

Page 34

Necessary for operation:

V

> 7.5V, V

SAT

= 3.7V to 5.47V, V

INT

CORE

< V

PERI

+ 0.3V

Operating conditions of all other supply pins:

V

, V

K30

EVZ

and V

are within functional range limits, Tj = –40°C to 150°C

CORE

Other pins:

As defined in Section 4. ”Functional Range” on page 8.

Table 11-1. Electrical Characteristics – VPERI Power Supply

No. Parameters Test Conditions Pin Symbol Min Typ. Max. Unit Type*

Voltage level at VSAT to enable

10.1

VPERI regulator

Hysteresis at VSAT to disable

10.2

VPERI regulator

V

programmed,

10.3 Output voltage #1

VPERI1

band-gap tolerance

included

programmed,

V

VPERI2

10.4 Output voltage #2

band-gap tolerance

included

10.5 Output current V

= 7.5V to 12.5V VPERI I

VSAT

10.6 Short-circuit current VPERI I

= 8V to 12.5V

V

VSAT

I

= –1 mA to –100 mA

10.7 Line regulation

PERI

is constant during

(I

PERI

measurement)

V

= 8V to 12.5V (V

10.8 Load regulation

10.10 Supply voltage rejection

SAT

is constant during

measurement)

= –1 mA to –100 mA

I

PERI

= –100 mA,

I

PERI

f = 100 kHz – 20 MHz,

= 47 µF + 100 nF

C

PERI

VSAT

(ceramic)

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

VSAT V

VSAT V

VPERI V

VPERI V

VPERI V

VPERI V

VSAT

VSAT

VPERI

VPERI

VPERI

VPERI

VPERI

VPERI

6.77 7.2 V A

0.2 0.5 V A

–3.6% 5 +4% V A

–4% 3.3 +3% V A

–100 mA A

–200 –110 mA A

–10 +10 mV A

–10 +10 mV A

40 dB D

34

ATA6264 [Preliminary]

4929B–AUTO–01/07

Page 35

12. VCORE Power Supply

The voltage of the VCORE regulator is generated out of the K30 voltage using a step-down regulator as long as the K30 voltage is available. During times when K30 is not present

(power-down or stand-alone time), the VCORE regulator is supplied out of VEVZ. Depending on

the initial programming, the supply switch signal is derived from the CORESWAP comparator or

the EVZEN comparator. The VCORE voltage can be programmed via the serial interface to 3

different voltage values during initial programming. In the case of short spikes, a logic circuit disables multiple-pulse operation during one oscillating period. The regulator uses both current and

voltage feedback. In the following cases, the output transistor of the regulator is switched off at

once and may be switched on again with the beginning of the next clock period:

1. If the current through the transistor exceeds the output current limit value, the transistor

is switched off immediately.

2. If overvoltage is detected at the pin VCORE, the transistor is switched off immediately.

3. If the feedback voltage at the pin VCORE is missing (disconnected pin), the regulator is

switched off.

Figure 12-1. Functional Principle of the VCORE Regulator

Control-

signal

K30/EVZ

ATA6264 [Preliminary]

VCORE

COMCOI

SPI

OTP

COMCOO

K30

VCORE

SVCORE

+

EVZ

CP

Bandgap

reference

Slope

compensation

OSC

S

+

-

Error

amp.

+

-

Comp.

compensation

Q

R

Slope

Current

measurement

and leading edge

blanking

Overcurrent

Logic and

driver

Overvoltage

Current

measurement

and leading edge

blanking

In order to trim the compensation of the regulation loop and to improve the behavior at load

changes, pin COMCOO has to be connected to COMCOI via a compensation network. Because

of the fact that current-mode-controlled converters exhibit sub-harmonic oscillations when operating at duty cycles larger than 50%, a slope compensation (which adds an artificial ramp to the

comparator) is implemented. If the regulator input voltage at pin EVZ or pin K30 is too low, the

regulator switches to a duty cycle of 100% (Permanent-on mode). Backward feeding of EVZ and

K30 is avoided. In order to ensure the gate voltage for the output transistors of the regulator, the

driver stages are supplied by the charge pump (pin CP).

4929B–AUTO–01/07

35

Page 36

Necessary for operation:

V

= 5.5V to 40V or V

EVZ

V

PERI>VCORE

– 0.3V, V

= 5.5V to 40V, VCP > V

K30

= 3.7V to 5.47V

INT

+ 7V or VCP > V

EVZ

K30

+ 7V,

Operating conditions of all other supply pins:

V

is within functional range limits, Tj = –40°C to 150°C

SAT

Other pins:

As defined in Section 4. ”Functional Range” on page 8.

Table 12-1. Electrical Characteristics – VCORE Power Supply

No. Parameters Test Conditions Pin Symbol Min Typ. Max. Unit Type*

V

voltage for the VCORE

11.1

11.1a

EVZ

regulator to start running

V

voltage for the

VPERI

VCORE regulator to start

running

V

voltage for the VCORE

11.2

EVZ

regulator to stop running

Hysteresis at VPERI for the

11.2a

VCORE regulator to stop

running

11.3 Switch-on time via pin EVZ SVCORE t

11.4 Switch-off time via pin EVZ SVCORE t

Regulator switching

11.5

frequency

11.6 Output current limit SVCORE I

11.7 R

of output transistor SVCORE R

Dson

11.8 Output voltage #1

11.9 Output voltage #2

11.10 Output voltage #3

11.11

Output transistor switch-on

time

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Notes: 1. Depending on implementation of slope compensation, sub-harmonics have to be prevented.

2. The value of the minimum load current must be higher than the internal pull-up current at pin VCORE to ensure proper

function of the regulator.

Initial programming:

V

VCORE

= 5V or 2.5V

Initial programming:

VCORE

= 1.88V

V

Initial programming:

V

VCORE

= 5V or 2.5V

Initial programming:

VCORE

= 1.88V

V

See numbers 8.1 and 8.2

of Table 9-1 on page 27

V

VCORE1

programmed,

band-gap tolerance

included

VCORE2

programmed,

V

band-gap tolerance

included

V

VCORE3

programmed,

band-gap tolerance

included

Time between reaching

0.1 × (V

K30max

– V

VCOREmin

and

0.9 × (V

K30max

– V

VCOREmin

or

0.1 × (V

EVZmax

– V

VCOREmin

and

0.9 × (V

EVZmax

– V

VCOREmin

EVZ V

VPERI V

EVZ V

VPERI V

SVCORE f

VCORE V

VCORE V

VCORE V

)

)

SVORE t

)

)

EVZ

VPERI

EVZ

HYS

SVCORE

SVCORE

SVCORE

SVCORE

SVCORE

VCORE1

VCORE2

VCORE3

SVCOREon

7.5 9 V A

1.25 1.7 V A

5.5 6.2 V A

50 150 mV A

020µsA

010µsA

0.7 0.9 A A

1.2 Ω A

–4% 5.0 +4% V A

–4% 2.5 +4% V A

–4% 1.88 +4% V A

150 ns A

A

36

ATA6264 [Preliminary]

4929B–AUTO–01/07

Page 37

ATA6264 [Preliminary]

Table 12-1. Electrical Characteristics (Continued)– VCORE Power Supply

No. Parameters Test Conditions Pin Symbol Min Typ. Max. Unit Type*

Time between reaching

0.1 × (V

and

11.12

Output transistor switch-off

time

0.9 × (V

or

0.1 × (V

and

0.9 × (V

11.13

11.13a

11.13b

Overvoltage at pin VCORE

for switching off the regulator

and setting pin RESQ to low

(VCORE is set to 5V)

Overvoltage at pin VCORE

for switching off the regulator

and setting pin RESQ to low

(VCORE is set to 2.5V)

Overvoltage at pin VCORE

for switching off the regulator

and setting pin RESQ to low

(VCORE is set to 1.8V)

See numbers 14.6 and

14.6a of Table 15-2 on

page 45

See numbers 14.7 and

14.7a of Table 15-2 on

page 45

See numbers 14.8 and

14.8a of Table 15-2 on

page 45

Time between reaching

11.14 Overvoltage switch-off time

overvoltage and reaching

90% of V

under on condition

Time between reaching

11.15 Overcurrent switch-off time

overcurrent and reaching

90% of V

under on condition

11.16

Leakage current at pin

SVCORE

Output transistor off SVCORE I

Error Amplifier

11.17

Maximum output current at

pin COMCOO sinking to low

Maximum output current at

11.18

pin COMCOO sourcing to

high

11.19

Input impedance at pin

COMCOI

V

V

CORE

CORE

= 1.88V

= 2.5V/5V

11.20 Input offset voltage –10 10 mV D

11.21 DC open loop gain 70 dB D

11.22 Unity-gain bandwidth 2 MHz D

11.23

11.24

Output voltage low at pin

COMCOO

Output voltage high at pin

COMCOO

I

COMCOO

I

COMCOO

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Notes: 1. Depending on implementation of slope compensation, sub-harmonics have to be prevented.

2. The value of the minimum load current must be higher than the internal pull-up current at pin VCORE to ensure proper

function of the regulator.

K30max

K30max

EVZmax

EVZmax

SCORE

SCORE

– V

VCOREmin

– V

VCOREmin

– V

VCOREmin

– V

VCOREmin

maximum

maximum

)

)

SVCORE t

)

)

SVORE t

SVCORE t

COMCOO I

COMCOO I

COMCOI R

= 165 µA COMSATO V

= –85 µA COMSATO V

SVCOREoff

SVCOREoff

SVCOREoff

SVCORE

COMCOO

COMCOO

COMCOI

COMSATO

COMSATO

150 ns A

00.4µsA

00.5µsA

–10 10 µA A

200 3000 µA A

–165 –85 µA A

7.5

13

18

27

kΩ

kΩ

00.3VA

VINT –

0.6

VINT V A

A

4929B–AUTO–01/07

37

Page 38

Table 12-1. Electrical Characteristics (Continued)– VCORE Power Supply

No. Parameters Test Conditions Pin Symbol Min Typ. Max. Unit Type*

11.25 Leading-edge blanking time t

11.26

11.27

Slope of artificial ramp for

slope compensation

Voltage level at K30 to switch

VCORE supply from EVZ to

K30 (V

= 1.8V or 2.5V

VCORE

V

increasing

K30

See number 7.3 of Table

8-2 on page 23

blank

dV/dt 80

programmed)

Hysteresis at K30 to switch

V

decreasing

K30

See number 7.4 of Table

8-2 on page 23

11.28

VCORE supply from K30 to

EVZ

(V

= 1.8V or 2.5V

VCORE

programmed)

Voltage level at K30 to switch

11.29

VCORE supply from EVZ to

VCORE

= 5V

K30 (V

increasing K30 V

V

K30

K30

programmed)

Hysteresis at K30 to switch

11.30

VCORE supply from K30 to

VCORE

= 5V

EVZ (V

decreasing K30 V

V

K30

K30

programmed)

Time to switch VCORE

11.31

supply from EVZ to K30 or

SVCORE t

switch

K30 to EVZ

11.32

VCORE loss-detection

threshold

(2)

VCORE I

Load

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Notes: 1. Depending on implementation of slope compensation, sub-harmonics have to be prevented.

2. The value of the minimum load current must be higher than the internal pull-up current at pin VCORE to ensure proper

function of the regulator.

150 200 ns D

(1)

150

(1)

mV/µs D

6.1 8.1 V A

0.5 1 V A

07.6µsD

01mAD

A

A

38

ATA6264 [Preliminary]

4929B–AUTO–01/07

Page 39

13. USP Comparator for General Purpose

The USP comparator is used for general purposes, for example, low battery detection. An external resistive voltage divider provides the input signal for pin USP. A missing USP connection or

V

< 2.44V sets the status register bit b7 to low. During normal operation (V

USP

status register bit b7 stays high.

Figure 13-1. Functional Principle of the USP Comparator

USP

2.44V

GNDA

to AMUX

+

-

ATA6264 [Preliminary]

> 2.44V) the

USP

Status register

Necessary for operation:

V

= 5.5V to 40V, V

EVZ

> reset threshold, V

PERI

> reset threshold, V

CORE

= 3.7V to 5.47V

INT

Operating conditions of all other supply pins:

V

SAT

and V

are within functional range limits, Tj = –40°C to 150°C

K30

Other pins:

As defined in Section 4. ”Functional Range” on page 8.

Table 13-1. Electrical Characteristics – USP Comparator for General Purpose

No. Parameters Test Conditions Pin Symbol Min Typ. Max. Unit Type*

12.1 Input current at pin USP V

12.2 Input current at pin USP V

= 2.44V USP I

USP

= 0 to 40V USP I

USP

USP

USP

Trigger voltage for status

12.3 Threshold voltage at pin USP

12.4 De-glitching time t

register bit 7= high with

increasing V

USP

USP V

USP

deglitch

*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

–2.5 +2.5 µA A

–2.5 +2.5 µA A

2.44 ±5% V A

20 60 µs D

4929B–AUTO–01/07

39

Page 40

14. Reference Voltage and Reference Current Generation

The pin IREF is an output derived directly from the chip’s internal reference voltage. This reference source is a band gap. All internally used precise voltages are derived from this band-gap

voltage. At pin IREF a reference resistor of 12.4 kΩ has to be applied, providing a reference cur-

rent. All internally used precise currents are derived from this current. In case of a missing

resistor at IREF, the regulators will stop. The power-sequencing block still operates as specified.