Page 1

AT91SAM9M10-G45-EK

....................................................................................................................

User Guide

6495B–ATARM–21-Apr-10

Page 2

Section 1

Introduction.................................................................................................................1-1

1.1 Scope ................................................................................................................................. 1-1

1.2 Applicable Documents ....................................................................................................... 1-2

Section 2

Kit Contents ................................................................................................................2-1

2.1 Deliverables ....................................................................................................................... 2-1

2.2 Evaluation Board Specifications......................................................................................... 2-2

2.3 Electrostatic Warning ......................................................................................................... 2-2

Section 3

Power up.....................................................................................................................3-1

3.1 Power Up the Board...........................................................................................................3-1

3.2 Battery................................................................................................................................ 3-1

3.3 DevStart ............................................................................................................................. 3-1

3.4 Recovery Procedure .......................................................................................................... 3-2

3.5 Sample Code and Technical Support ................................................................................ 3-2

Section 4

Board Description .......................................................................................................4-1

4.1 Equipment on the Board .................................................................................................... 4-1

4.1.1 Interfaces ............................................................................................................. 4-1

4.1.2 Board Interface Connection ................................................................................. 4-2

4.1.3 Push Button Switches .......................................................................................... 4-2

4.1.4 Display LCD and LEDs ........................................................................................ 4-3

4.2 Hardware Layout and Configuration .................................................................................. 4-3

4.2.1 Processor............................................................................................................. 4-3

4.2.2 Clock Circuitry...................................................................................................... 4-4

4.2.3 Reset Circuitry ..................................................................................................... 4-4

4.2.4 Memory................................................................................................................ 4-4

4.2.5 Power Supplies .................................................................................................... 4-7

4.2.6 Debug Interface ................................................................................................. 4-10

4.2.7 Audio Stereo Interface ....................................................................................... 4-15

4.2.8 TV-Out Extension .............................................................................................. 4-17

4.2.9 Software Controlled LEDs ................................................................................. 4-18

4.2.10 Serial Peripheral Interface Controller (SPI) ....................................................... 4-19

4.2.11 Two Wire Interface (TWI)................................................................................... 4-19

4.2.12 SD/MMC Interface ............................................................................................. 4-19

4.2.13 TFT LCD with Touch Panel ............................................................................... 4-20

4.2.14 Push Buttons ..................................................................................................... 4-22

AT91SAM9M10-G45-EK User Guide 1-i

6495B–ATARM–21-Apr-10

Page 3

4.2.15 Expansion Slot ................................................................................................... 4-22

Section 5

Configuration ..............................................................................................................5-1

5.1 JTAG/ICE Configuration..................................................................................................... 5-1

5.2 ETHERNET Configuration ................................................................................................. 5-1

5.3 Jumpers Configuration ....................................................................................................... 5-2

5.4 Miscellaneous Configuration Items .................................................................................... 5-3

5.5 PIO Configuration............................................................................................................... 5-3

5.5.1 Peripheral Signals Multiplexing on I/O Lines ....................................................... 5-3

5.5.2 Multiplexing on PIO Controller A (PIOA).............................................................. 5-3

5.5.3 Multiplexing on PIO Controller B (PIOB).............................................................. 5-5

5.5.4 Multiplexing on PIO Controller C (PIOC) ............................................................. 5-6

5.5.5 Multiplexing on PIO Controller D (PIOD) ............................................................. 5-7

5.5.6 Multiplexing on PIO Controller E (PIOE).............................................................. 5-8

Section 6

Connectors .................................................................................................................6-1

6.1 Power Supply ..................................................................................................................... 6-1

6.2 RS232 Connector with RTS/CTS Handshake Support ...................................................... 6-1

6.3 DBGU................................................................................................................................. 6-2

6.4 Ethernet.............................................................................................................................. 6-3

6.5 USB Host ........................................................................................................................... 6-3

6.6 USB Host/Device ............................................................................................................... 6-4

6.7 JTAG Debugging Connector .............................................................................................. 6-4

6.8 SD/MMC- MCI0.................................................................................................................. 6-6

6.9 SD/MMC- MCI1.................................................................................................................. 6-7

6.10 AC97 .................................................................................................................................. 6-8

6.11 Image Sensor - ISI ............................................................................................................. 6-9

6.12 Video ................................................................................................................................ 6-10

6.13 Display Devices................................................................................................................ 6-10

6.13.1 TFT LCD ............................................................................................................ 6-10

6.14 LCD Extension ................................................................................................................. 6-11

Section 7

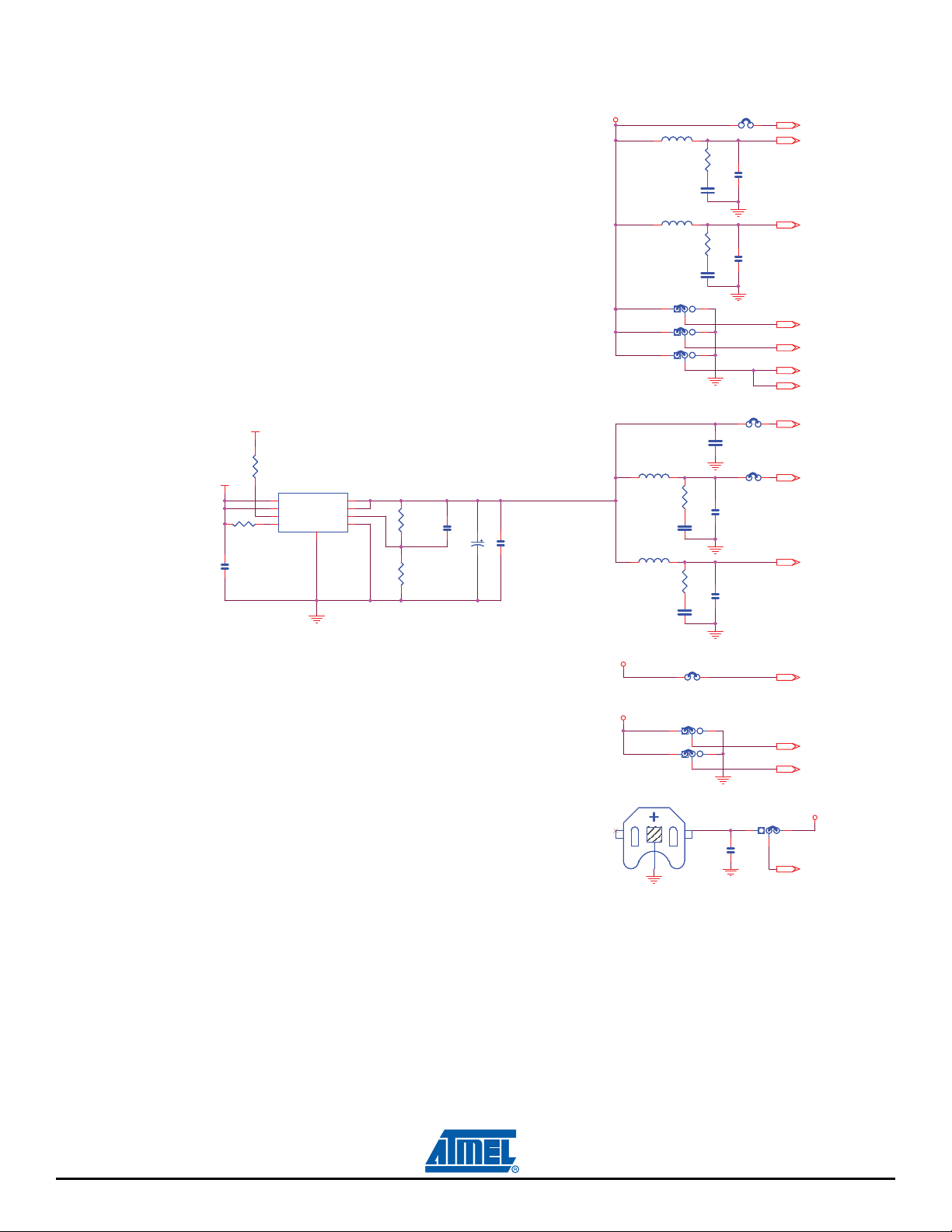

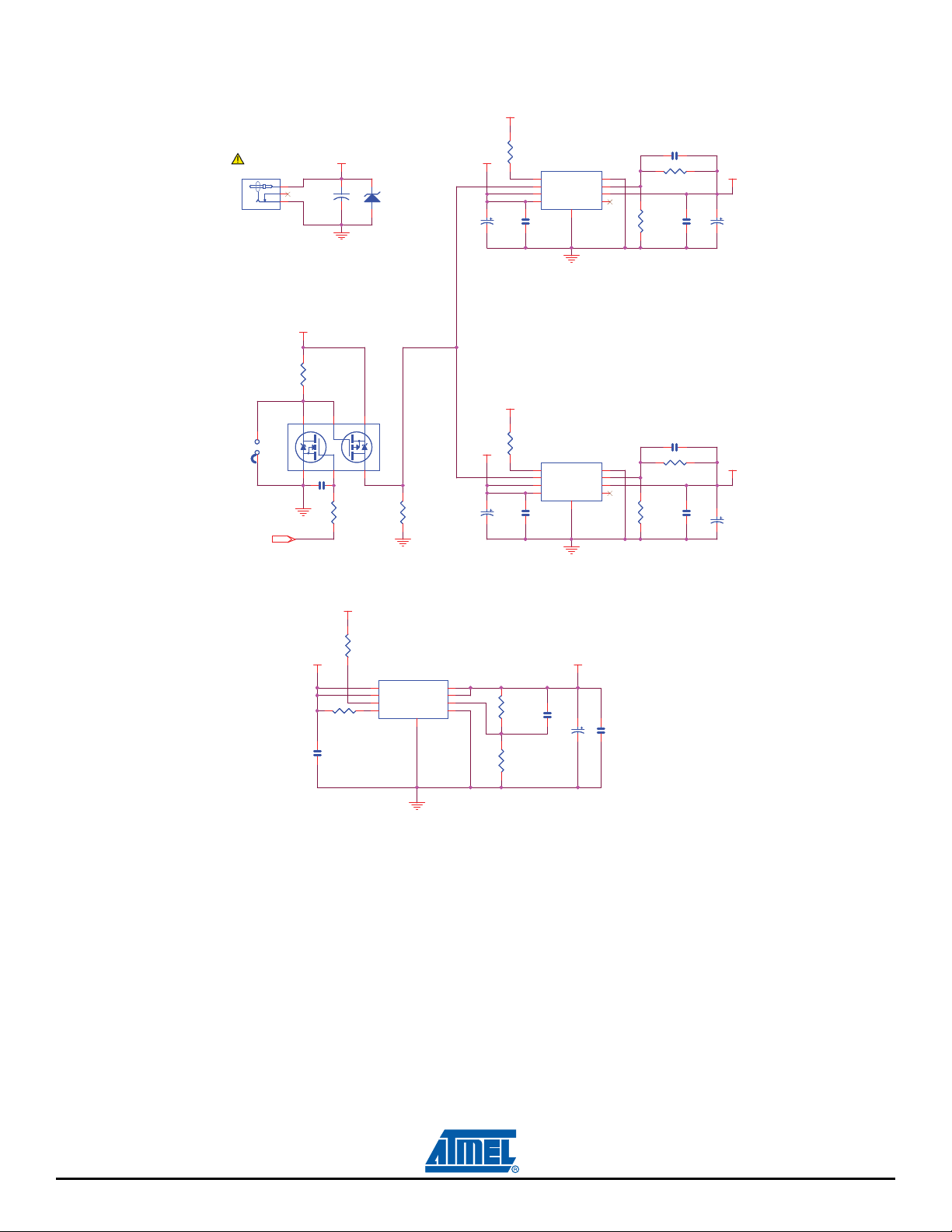

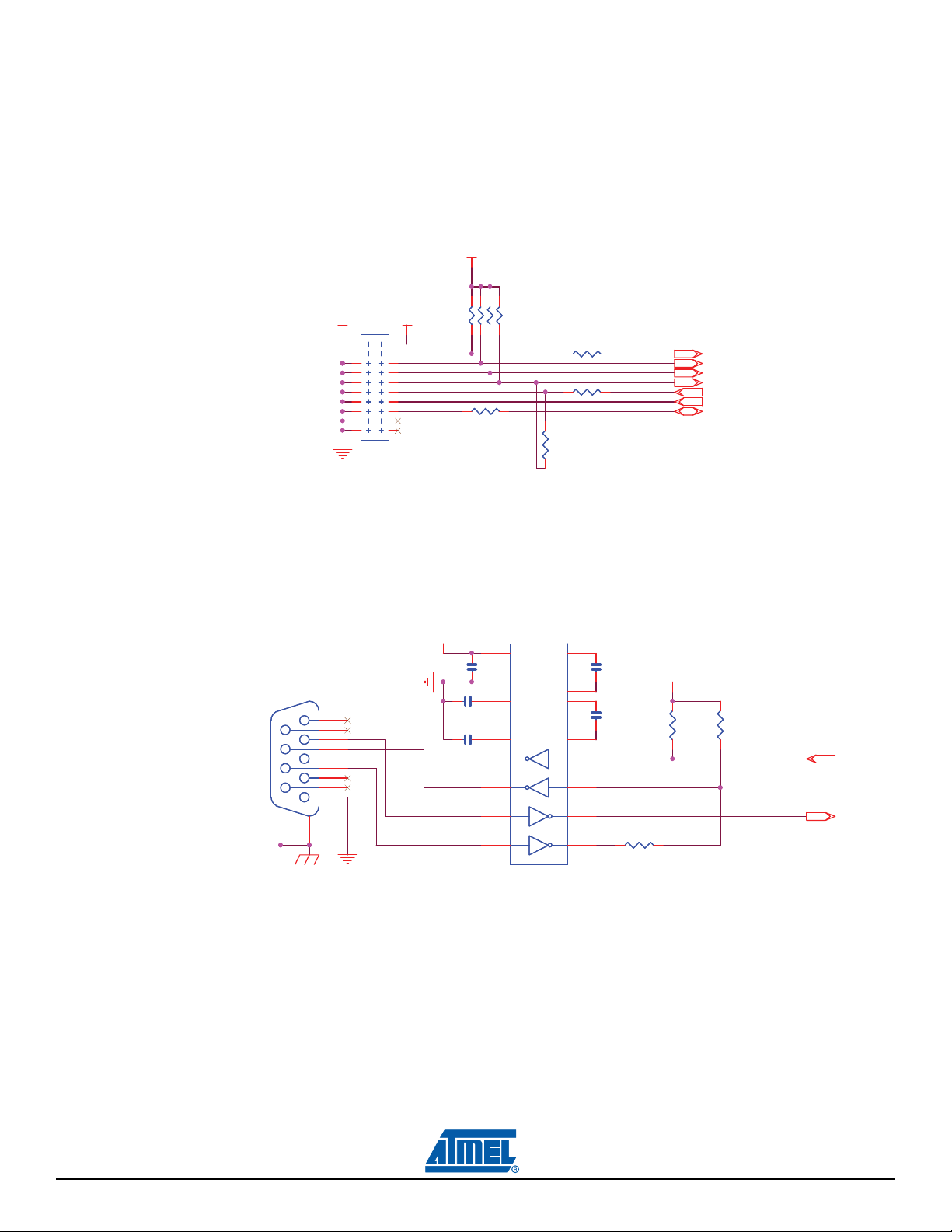

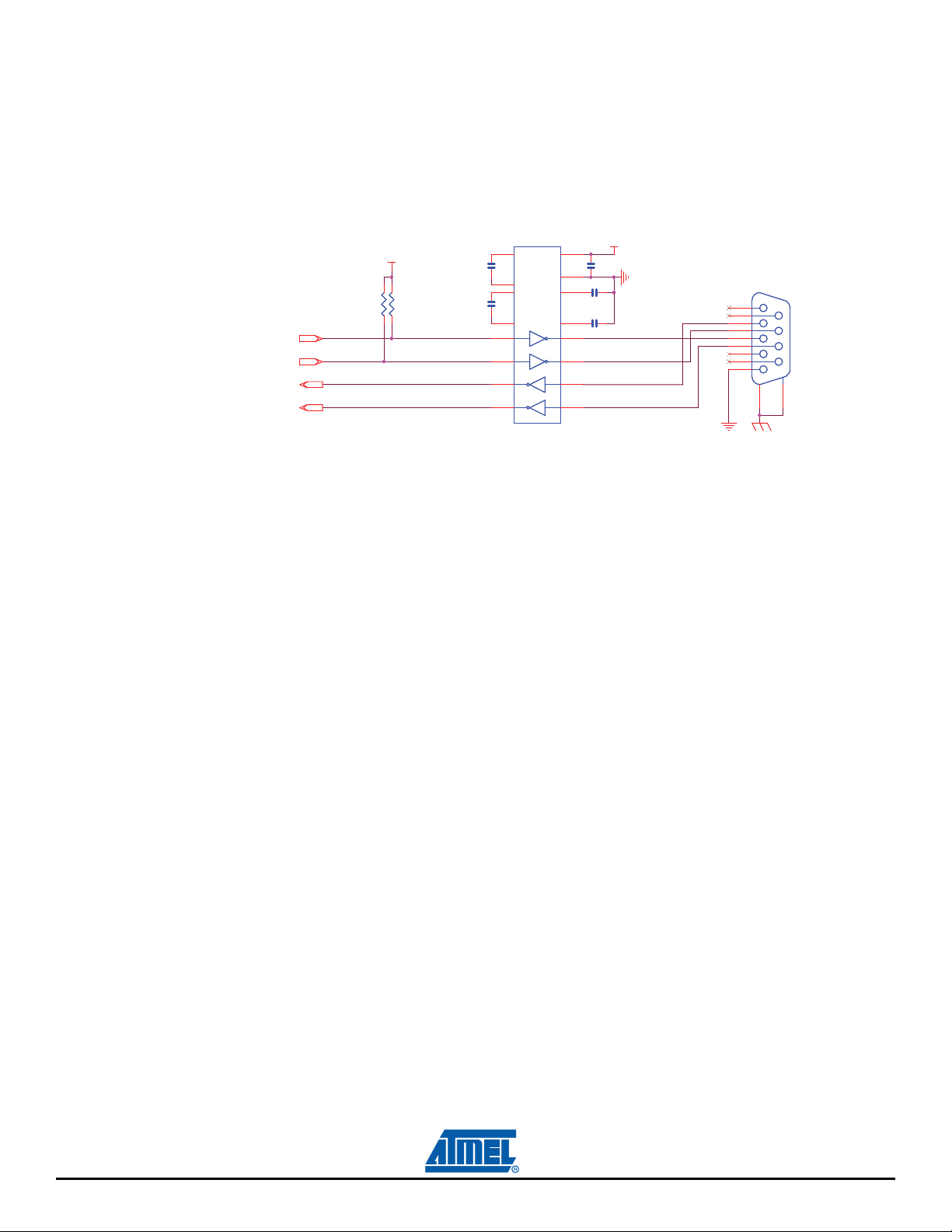

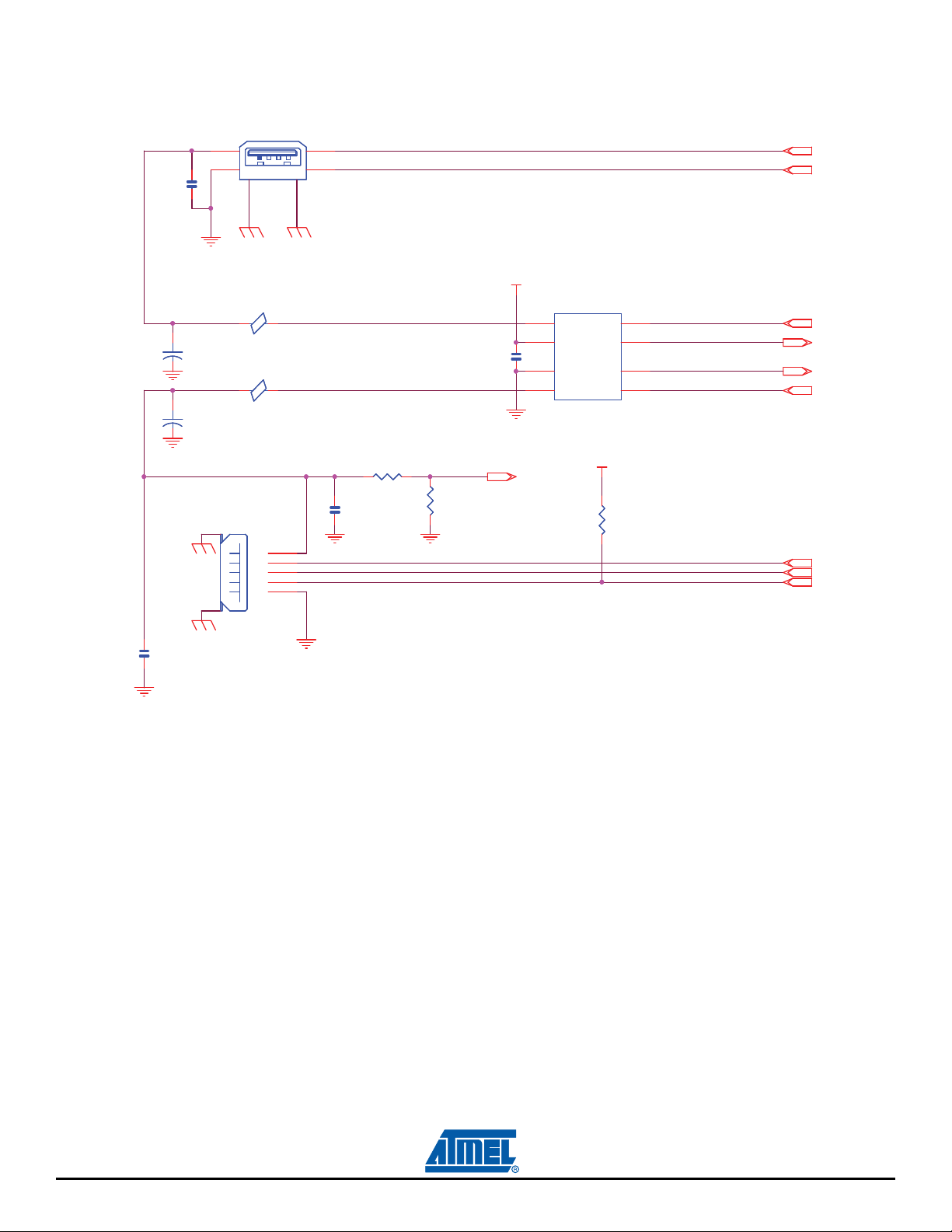

Schematics .................................................................................................................7-1

7.1 Schematics......................................................................................................................... 7-1

Section 8

Revision History..........................................................................................................8-1

8.1 Revision History ................................................................................................................. 8-1

1-ii AT91SAM9M10-G45-EK User Guide

6495B–ATARM–21-Apr-10

Page 4

1.1 Scope

Section 1

Introduction

This User Guide introduces the AT91SAM9M10(G45) Evaluation Kit and describes its development and

debugging capabilities.

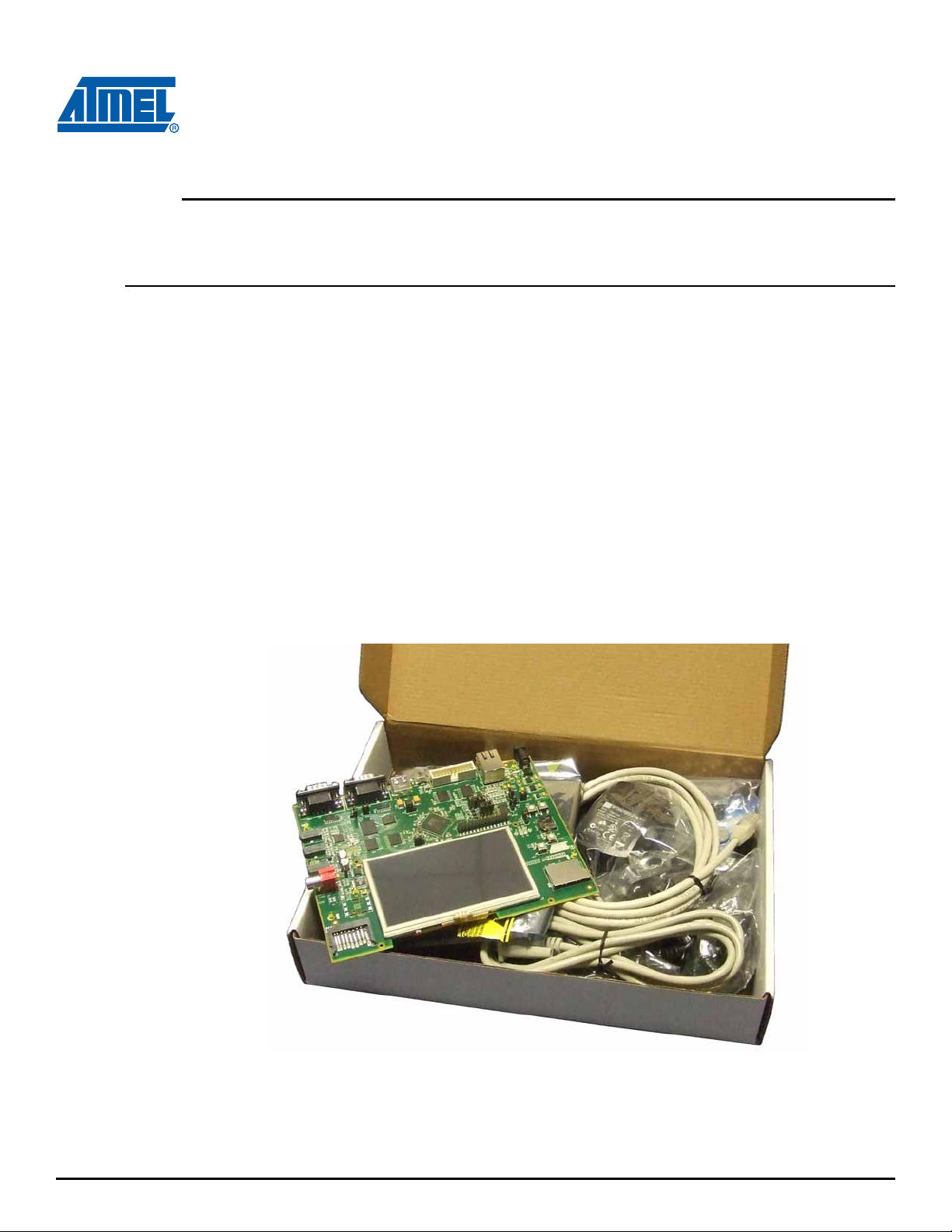

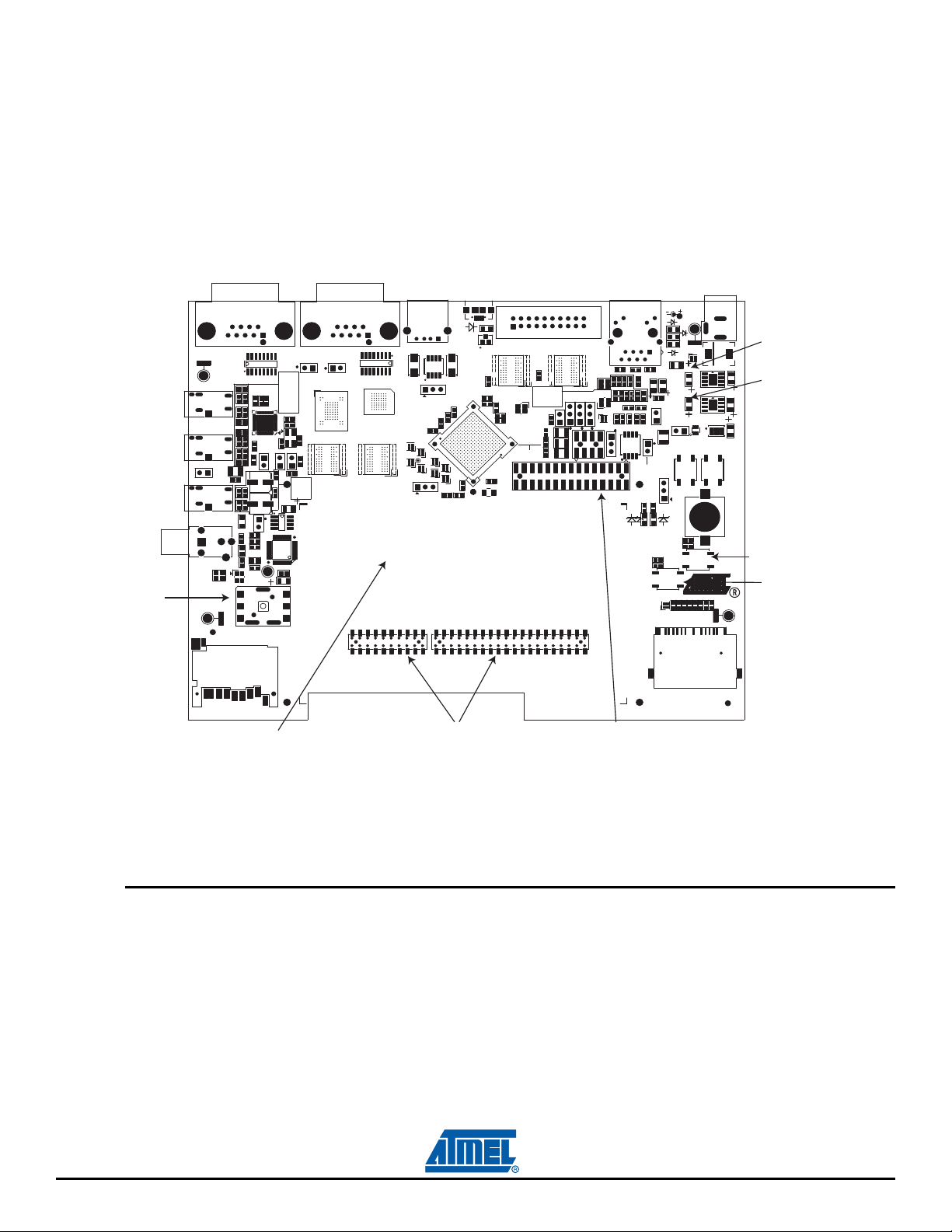

Figure 1-1. Board Photo

The Atmel® SAM9M10-G45-EK is a fully-featured evaluation platform for the Atmel AT91SAM9M10 or

AT91SAM9G45 microcontroller. The kit is equipped with an AT91SAM9M10 chip, which is a superset of

the AT91SAM9G45, and therefore allows evaluating that reference as well. The evaluation kit allows

users to extensively evaluate, prototype and create application-specific designs.

The SAM9M10-G45-EK includes many hardware peripherals such as:

Two high speed USB hosts and one high speed device port

An Ethernet 10/100 interface

Two high speed multimedia card interfaces

AT91SAM9M10-G45-EK User Guide 1-1

6495B–ATARM–21-Apr-10

Page 5

Introduction

An LCD TFT display (480*272 RGB) with resistive touch panel

A composite video output

A camera interface

Several communication peripherals such as:

– Universal Synchronous/Asynchronous Receiver Transmitter (USART)

– Two-Wire Interface (TWI)

The external memory block is made of 3 memory types:

DDR2-SDRAM

NAND Flash

NOR Flash (not populated by default)

1.2 Applicable Documents

Table 1-1. Applicable Documents

Reference Title Comments

Atmel Literature n° 6438 SAM9G45 Preliminary

Atmel Literature n° 6355 SAM9M10 Preliminary

This document describes the SAM9G45, which is part of the

Atmel's Smart ARM

®

Microcontrollers.

It is available from

http://www.atmel.com/dyn/resources/prod_documents/doc6438.pdf

This document describes the SAM9M10, which is part of the

Atmel's Smart ARM® Microcontrollers

http://www.atmel.com/dyn/resources/prod_documents/doc6355.pdf

1-2 AT91SAM9M10-G45-EK User Guide

6495B–ATARM–21-Apr-10

Page 6

2.1 Deliverables

The Atmel SAM9M10-G45-EK toolkit includes:

Board

– The SAM9M10-G45-EK board

Power supply

– Universal input AC/DC power supply with US, Europe and UK plug adapters

– One 3V Lithium Battery type CR1225

Cables

– One micro A/B-type USB cable

– One serial RS232 cable

– One RJ45 crossed cable

A Welcome Letter

Figure 2-1. Unpacked SAM9M10-G45-EK

Section 2

Kit Contents

Unpack and inspect this kit carefully. Contact your local Atmel distributor, should you have issues concerning the contents of the kit.

AT91SAM9M10-G45-EK User Guide 2-1

6495B–ATARM–21-Apr-10

Page 7

Kit Contents

2.2 Evaluation Board Specifications

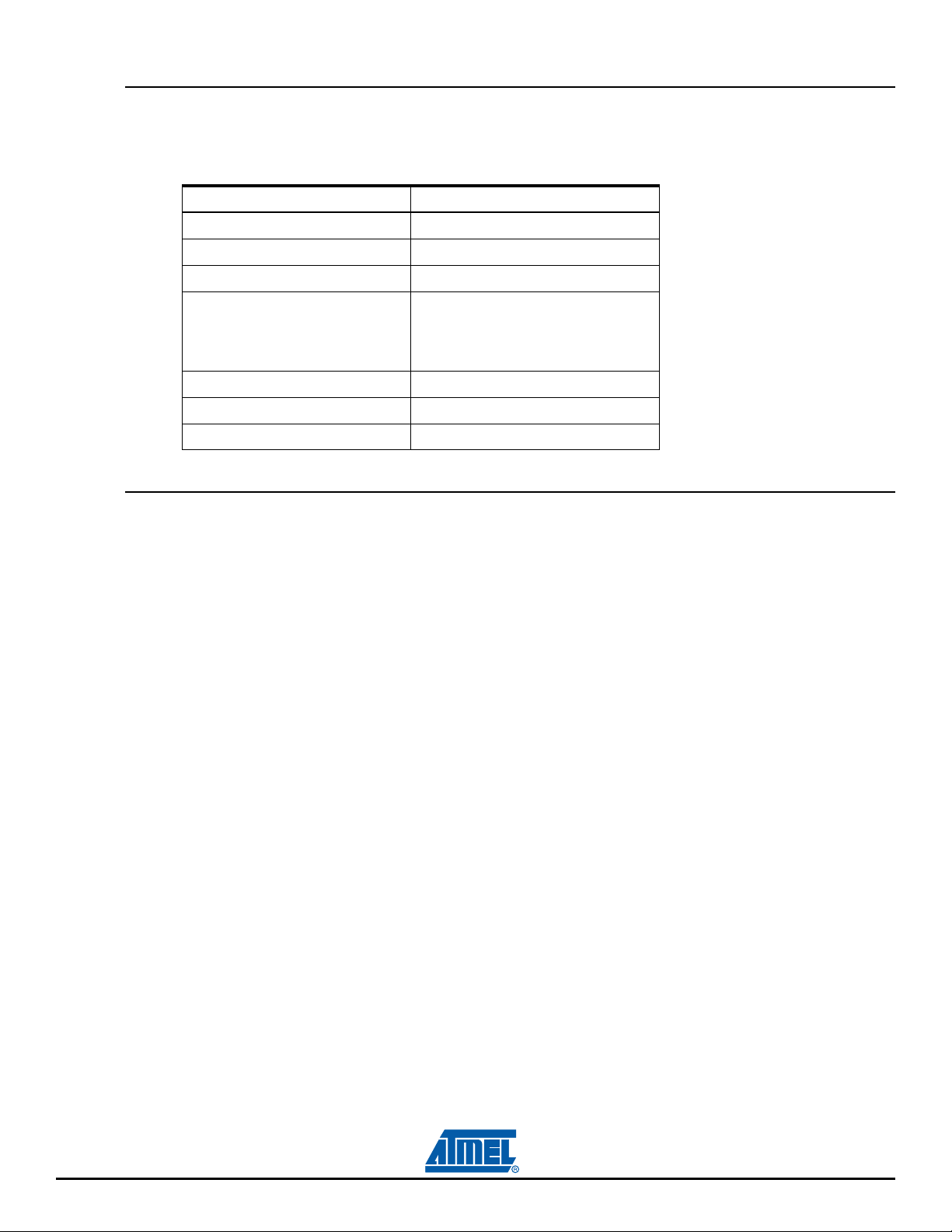

Table 2-1. SAM9M10-G45-EK Specifications

Characteristics Specifications

Clock speed 400 MHz PCK, 133 MHz MCK

Ports Ethernet, USB, RS232, DBGU, JTAG

Board supply voltage 5 VDC from connector

Temperature

- operating

- storage

Relative humidity 0 to 90% (non condensing)

Dimensions 180 mm x 140 mm

RoHS status Compliant

-10° to +50° C

-40° to +85° C

2.3 Electrostatic Warning

The SAM9M10-G45-EK evaluation board is shipped in a protective anti-static package. The board must

not be subjected to high electrostatic potentials. We strongly recommend using a grounding strap or sim

ilar ESD protective device when handling the board in hostile ESD environments (offices with synthetic

carpet, for example...). Avoid touching the component pins or any other metallic element on the board.

-

2-2 AT91SAM9M10-G45-EK User Guide

6495B–ATARM–21-Apr-10

Page 8

3.1 Power Up the Board

Unpack the board taking care to avoid electrostatic discharge. Unpack the power supply, select the right

power plug adapter corresponding to that of your country, and insert it in the power supply.

Connect the power supply DC connector to the board and plug the power supply to an AC power plug.

The board LCD should light up and display a welcome page. Then, click or touch icons displayed on the

screen and enjoy the demo.

3.2 Battery

The SAM9M10-G45-EK ships with a 3V coin battery.

This battery is not required for the board to start up.

The coin battery is provided for user convenience in case the user would like to exercise the date and

time backup function of the SAM9M10 series devices when the board is switched off.

Section 3

Power up

3.3 DevStart

The on-board NAND Flash contains a “SAM9M10-G45-EK DevStart”.

It is stored in the “SAM9M10-G45-EK DevStart” folder on the USB Flash disk available when the

SAM9M10-G45-EK is connected to a host computer.

Click the file “welcome.html” in this folder to launch SAM9M10-G45-EK DevStart.

SAM9M10-G45-EK DevStart guides you through installation processes of IAR™ EWARM, Keil MDK and

GNU toolkits. Then, it gives you step-by-step instructions on how to rebuild a single example project and

how to program it into the SAM9M10-G45-EK. Optionally, if you have a SAM-ICE™, instructions are also

given about how to debug the code.

We recommend that you backup the “SAM9M10-G45-EK DevStart” folder on your computer

before launching it.

AT91SAM9M10-G45-EK User Guide 3-1

6495B–ATARM–21-Apr-10

Page 9

Power up

3.4 Recovery Procedure

The DevStart ends by giving step-by-step instructions on how to recover the SAM9M10-G45-EK to the

state as it was when shipped by Atmel.

Follow the instructions if you deleted the contents of the NAND Flash and want to recover from this

situation.

3.5 Sample Code and Technical Support

After boot up, you can run some sample code or your own application on the development kit. You can

download sample code and get Technical support from

http://www.atmel.com/dyn/products/tech_support.asp?Faq=y&family_id=689%20.

3-2 AT91SAM9M10-G45-EK User Guide

6495B–ATARM–21-Apr-10

Page 10

4.1 Equipment on the Board

PARALLEL

FLASH

AT91SAM9M10

AT91SAM9M10

DEBUG

DEBUG

JTAG/ICEDBGU

System Controller

System Controller

External Memory

External Memory

EBI0

EBI0

EBI1 / 1.8v

EBI1 / 1.8v

DDR2

SDRAM

DDR2

SDRAM

NAND

FLASH

Multimédia Cards Interface

Multimedia Cards Interface

MCI0

MCI0

SPI0

SPI0

MCI1

MCI1

Data

Flash

USART

USART

USB

USB

Host A

Host A

Host B

Host B

Device

Device

ETHERNET

10/100 MAC

ETHERNET

10/100 MAC

LCD Interface

LCD Interface

AC97

AC97

PIO

PIO

TWI

TWI

oooooooo

oooooooo

Serial

Eeprom

oooooooo

oooooooo

4 bits

interface

SD/MMC

8 bits

interface

SD/MMC

Micro

Line In

Line Out

oooooooo

oooooooo

LCD TFT

480*272

LCD TFT

480*272

PWM

PWM

PHY RMII

RS232

Codec

NPCS0

NCS0

NCS3

NCS1

Led

CD

User I/OAudioVidéoLCD TFTMultimedia cardsMain Memory

Touch

Screen

Touch

Screen

Composite

video

VCC 5V PIOJTAG/ICEDBGUUSB

Hub / Device

USB Hub

High / Full

RS232Ethernet RMII/MIIISI

Image Sensor

Interface

Image Sensor

Interface

Power /

Shdn

Joystick

& P.B

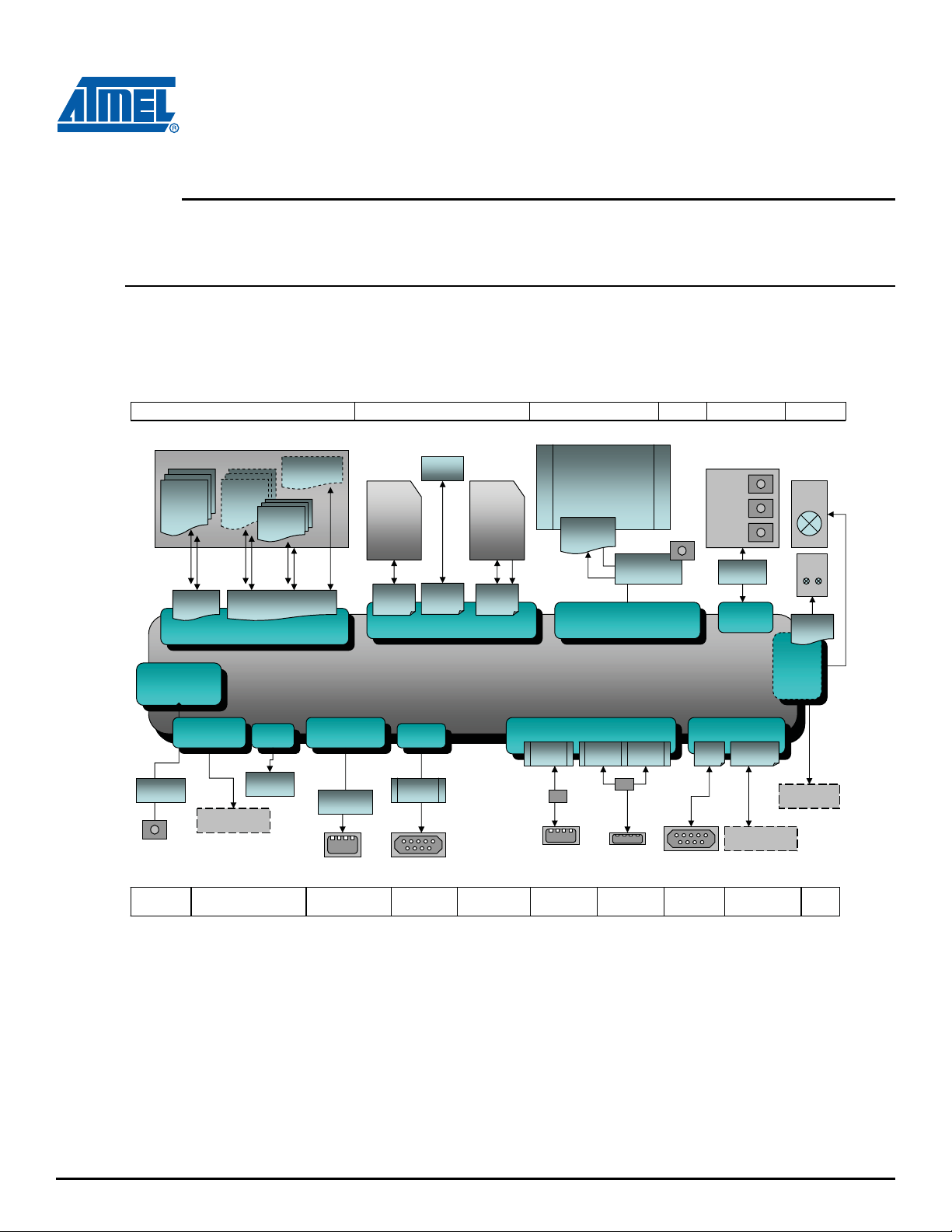

Figure 4-1. Board Architecture

Section 4

Board Description

4.1.1 Interfaces

The board is equipped with an AT91SAM9M10-CU embedded microprocessor (324-ball TFBGA package) together with the following interfaces or peripherals:

DDR2/LPDDR memory interface is connected to 128 MB DDR2-SDRAM memory

External Bus Interface (EBI) is connected to three kinds of memory devices (DDR2-SDRAM, NAND

Flash and NOR Flash (not populated))

AT91SAM9M10-G45-EK User Guide 4-1

6495B–ATARM–21-Apr-10

Page 11

Board Description

One TWI serial memory

One USB Host/Device multiplexed port interface

One USB Host port interface

One RS232 serial communication port

One DBGU serial communication port

One JTAG/ICE debug interface

One Ethernet 100-base TX with three status LEDs

One AC97 Audio CODEC with headphone line out, line in and mono/stereo microphone inputs

One TV interface (composite video output)

One 4.3" TFT LCD Module with touch screen and back light

One ISI connector (camera interface)

One power red LED and two general-purpose green LEDs

Two user input push buttons

One joystick with 4-direction control and selector

One wakeup input push button

One reset input push button

One SD/SDIO/MMC plus card slot (4/8 bit interface)

One SD/SDIO/MMC card slot (4-bit interface)

One Lithium Coin Cell Battery Retainer for 12 mm cell size (memory backup usage)

4.1.2 Board Interface Connection

Ethernet using RJ45 connector (J15)

USB Host, support USB host using a type A connector (J12)

USB Host/Device, support USB host/device using a type micro AB connector (J14)

UART1 (RX, TX, RTS, CTS) connected to a 9-way male D-type RS232 connector (J11)

DBGU (RX and TX only) connected to a 9-way male D-type RS232 connector (J10)

JTAG, 20 pin IDC connector (J13)

SD/MMCplus connector (J5)

SD/MMC connector (J6)

Headphone (J7), line-in (J8) and microphone headset (J9)

Speaker output (JP15)

Image sensor connector (J17)

TFT LCD display, with TouchScreen and backligth (J24)

Test points; various test points are located throughout the board

Main power supply (J2)

4.1.3 Push Button Switches

Reset, board reset (BP1)

Wake up, push button to bring processor out of low power mode (BP2)

Right and left click, user push button switches (BP4 and BP5)

Joystick (BP3)

4-2 AT91SAM9M10-G45-EK User Guide

6495B–ATARM–21-Apr-10

Page 12

4.1.4 Display LCD and LEDs

DBGU RS232 JTAG ETHERNET

WAKE-UP

BUTTON

RESET

BUTTON

BACKUP

BATTERY

«RIGHT»

USER BUTTON

«LEFT»

USER BUTTON

SD/MMC 1

SLOT

SD/MMC 0

SLOT

USER

JOYSTICK

VIDEO

OUTPUT

HEADPHONES

HEADER

MICROPHONE

INPUT

LINE

INPUT

LCD DISPLAY AREA

LCD EXTENSION

CONNECORS

ISI/CAMERA

CONNECTOR

POWER

HOST

USB

HOST

DEVICE

USB

Y6

TP2

J20

J7

R85

L11

JP15

J9

J8

TP4

J6

R185

Y7

BP3

C205

R181

R183

L22

L20

MN20

TP6

C203

C206

MN12

JP13

C201

C141

C143

JP14

JP17

JP18

MN14

C139

C146

C147

J10

L17

C198

C128

R71

R69

C126

C199

C133

C129

MN9

R72

R74

R73

R70

C127

C137

C155

C156

R75

R84

R83

R78

L10

Y3

C148

C149

R79

R80

L12

L9

L8

MN15

JP10

J11

J18

MN8

MN11

MN16

MN10

JP9

RR19

RR17

RR13

RR11

JP6

JP5

C168

J12

R203

R204

C59

RR25

RR23

RR21

TP5

C48

R40

R42

R44

M

N

5

RR9

C170

MN17

J14

Y2

C64

C41

C47

C38

C66

R37

R46

MN6

Q2

D3

J17

R20R5

L4

C186

R99

R106

R39R12

R100

R101

R120

L3

L2

JP8

C177

C179

R117

R116

R48

Y1

J13

J23

RR45

JP11

J1

C183

Y5

Y4

JP3JP2JP1

MN7

J15

R191

R192

R193

R194

R195

R196

RR36

C37

R29

R22

R21

D2D1

JP12

MN13

C185

R114

R109

R104

R115

R105

R112

C178

C176

C182

J5

C31

R27

BP5

L5

JP7

BP2

Q1

JP16

JP4

C23

R110

MN2

C187

C180

C181

C9

RR47

J2

D6

D4

D5

CR1

TP1

R197

R198

TP3

BP4

J3

BP1

C27

C6

MN1

MN4

C12

19

20

1

29

30

39

40

71

82

12

34

1

2

12

34

1

1

2

1

4

2

1

SD/MMC

VIDEO

HEAD PHONE

MIC IN

LINE IN

DBGU

SELECT

E2PROM

NANDCS NCS0

RS232

VDDIOM1

USB

LCD EXTENSION

VDDIOM0

HOST

USB

HOST

/DEV

1

ISI

J1

VDDUTMII

VDDUTMIC

VDDCORE

VDDPLLUTMI

ICE

BMS

JP2/P2/JD3

VDDIOPn

ETHERNET

LEFT

BAT

VDDBU

3V3

NPCS0

SD/MMC+

CR1225

3V

WAKEUP

5VCC POWER

RIGHT

NRST

Display, 480xRGBx272 pixels LCD module display connected to the PIO port E (LCD1)

One surface-mounted power red LED, user interface (D3)

Two surface-mounted green LEDs, user interface (D1 and D2)

Three surface-mounted LEDs indicate Ethernet status (D4, D5, D6)

Figure 4-2. Board Layout Commented

Board Description

4.2 Hardware Layout and Configuration

4.2.1 Processor

The major components of the SAM9M10-G45-EK board are shown in Figure 4-1.

The board features the Atmel SAM9M10-CU 324-ball TFBGA package. This chip runs at a nominal frequency of 400 MHz for the core and 133 MHz for the system bus.

For more information, refer to the latest SAM9M10 datasheet available from http://www.atmel.com/

AT91SAM9M10-G45-EK User Guide 4-3

6495B–ATARM–21-Apr-10

Page 13

Board Description

4.2.2 Clock Circuitry

The SAM9M10-G45-EK includes six clock sources:

Two are alternatives for the SAM9M10 main clock,

One crystal and one crystal oscillator are used for the Ethernet MII/RMII chip,

One crystal is used for the AC97 codec chip,

One crystal or one crystal oscillator is used for the TV encoder.

Table 4-1. Main Components Associated with the Clock Systems

Quantity Description Component assignment

1 Crystal for Internal Clock, 12 MHz Y1

1 Crystal for RTC Clock, 32.768 kHz Y2

1 Oscillator for Ethernet Clock RMII, 50 MHz Y4

1 Crystal for Ethernet Clock MII, 25 MHz (not populated) Y5

1 Crystal for AC97 Codec Clock, 24.576 MHz Y3

1

4.2.3 Reset Circuitry

The reset sources are:

Power on reset

Push button reset

JTAG reset from an in-circuit emulator interface.

4.2.4 Memory

4.2.4.1 External Memories

The SAM9M10 features a DDR2/LPDDR memory interface and an External Bus Interface (EBI) to permit

interfacing to a wide range of external memories and to almost any kind of parallel peripheral.

The SAM9M10-G45-EK board is equipped with DDR2/LPDDR devices featuring 128 MB of DDR2SDRAM memory (16Meg*8*4).

The External Bus Interface (EBI) is connected to three kinds of memory devices:

One Parallel Flash (not populated by default)

Two DDR2-SDRAM

One NAND Flash (2Gb, 8 bit bus)

Crystal for TV Encoder Clock, 13 MHz, or

Oscillator for TV Encoder, 13 MHz (not populated)

Y7

Y6

The chip selects NCS0, NCS1 and NCS3 are used for NOR Flash, DDR2-SDRAM and NAND Flash

memories, respectively. Furthermore, a dedicated jumper can disconnect each of the two NCS0 and

NCS3 signals, making them available for other functions.

4-4 AT91SAM9M10-G45-EK User Guide

6495B–ATARM–21-Apr-10

Page 14

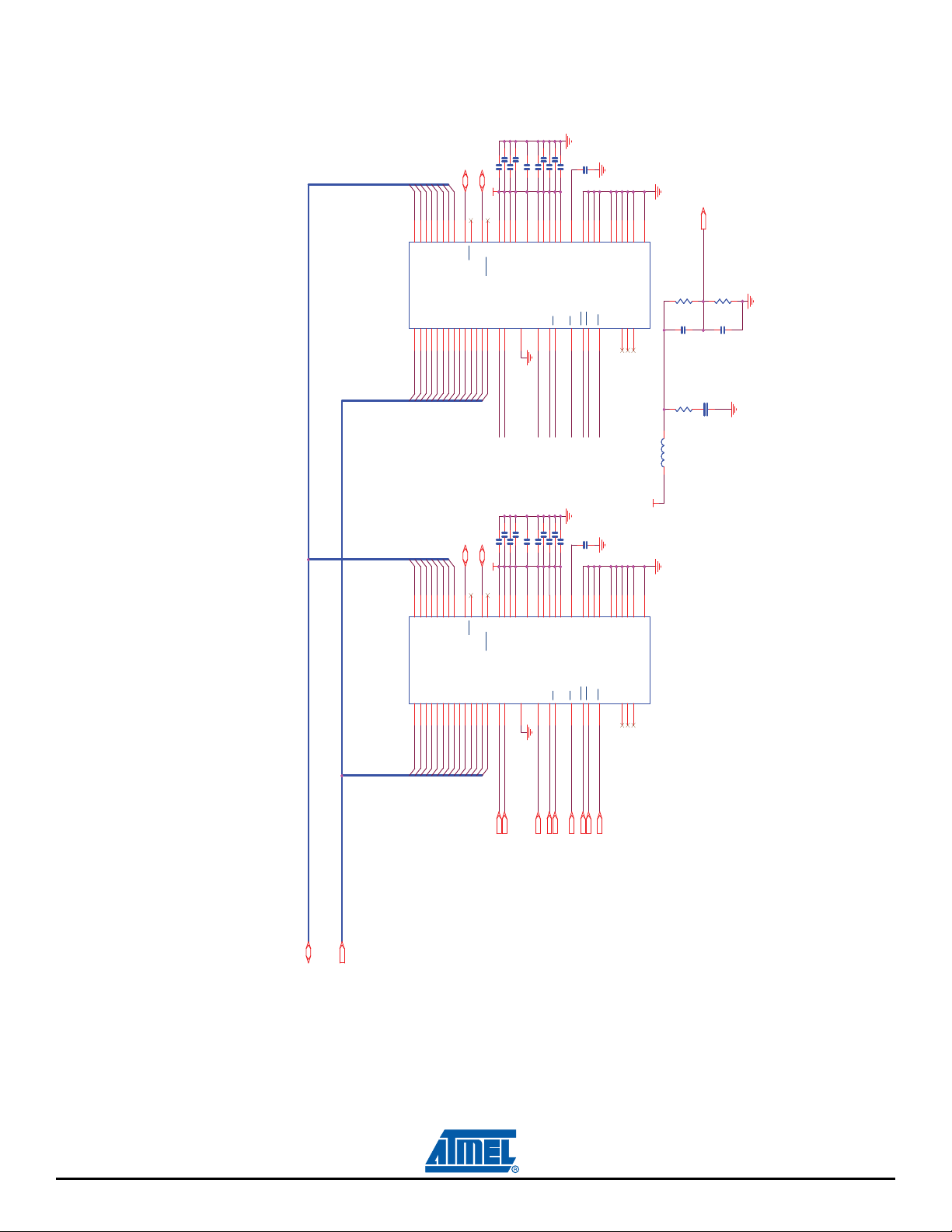

Figure 4-3. EBI0 - DDR2

Board Description

C88

DDR_DQM1

DDR_DQS1

C68 100nC68 100n

C70 100nC70 100n

C74 100nC74 100n

C76 100nC76 100n

1V8

DDR_D12

DDR_D15

DDR_D10

DDR_D14

DDR_D11

DDR_D8

DDR_D9

DDR_D13

C8

C2

D3

D7

DQ1

DQ3

DQ0

DQ2

DDR2 SDRAM

A3

A1H3A2

A0

MN7

MN7

J2

H8

H7

DDR_A0

DDR_A2

DDR_A1

DDR_A3

D1

D9

DQ4

A4

J8

DDR_A4

DDR_A5

B1

DQ5

DQ6

A5J3A6J7A7K2A8

DDR_A6

B9

DQ7

K8

DDR_A7

DDR_A8

A8

B7

DQS

A9K3A10

H2

DDR_A9

DDR_A10

B3

DQS

A11

L2

K7

DDR_A11

DDR_A12

E1

E9

A2

L1

A1

H9

VDD

VDD

VDD

VDD

VDDL

RDQS/NU

RDQS/DM

BA0

BA1

A12

ODT

A13

L8

F9

G2

G3

DDR_A13

BA0

BA1

C88

100n

100n

C84100nC84100n

C86100nC86100n

C80100nC80100n

C82100nC82100n

C78 100nC78 100n

DDR_VREF

DDR_VREF

E3

C3

A9

C1

C9

C7

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

CKE8CK

CKE

F8

F2

CK

NCK

CKE

A7

K9

A3

E2

J1

VSS

VSS

VSS

VREF

CS

CASG7RAS

F7

G8

CS

CAS

RAS

E7

B8

D8

B2

D2

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSDL

RFU1G1RFU2

WE

RFU3

L3

L7

F3

NWE

DDR_VREF

R51

1.5k

R51

1.5k

R52

1.5k

R52

1.5k

C91

100n

C91

100n

C89

C89

100n

100n

R501RR50

1R

4.7u

4.7u

C90

C90

L5 10uHL5 10uH

1V8

DDR_DQM0

DDR_DQS0

C71 100nC71 100n C72 100nC72 100n

C69 100nC69 100n

C73 100nC73 100n

C67 100nC67 100n

C75 100nC75 100n

1V8

DDR_D3

DDR_D7

DDR_D2

DDR_D4

DDR_D5

DDR_D6

DDR_D0

DDR_D1

C8

D1

B3

E9

A8

B1

D3

B7

B9

D9

DQ4

DQ1C2DQ2D7DQ3

DQ5

DQ0

DQ7

DQ6

DQS

DQS

DDR2 SDRAM

A6

A2

A4J8A5

A7

A9K3A10H2BA0

A1

A3

A8

J3

DDR_A4

DDR_A5

J7

K2

DDR_A6

DDR_A7

K8

DDR_A8

DDR_A9

DDR_A10

A11

K7

DDR_A11

A0

MN6

MN6

J2

H8

H7

H3

DDR_A2

DDR_A0

DDR_A1

DDR_A3

A2

RDQS/NU

RDQS/DM

A12L2A13

L8

DDR_A12

DDR_A13

A1

VDD

G2

G3

BA0

BA1

DDR_BA0

DDR_BA1

E1

L1

VDDH9VDD

VDD

VDDL

ODT

BA1

F9

C79 100nC79 100n

C77 100nC77 100n

A9

C1

VDDQ

CKEF2CK

CKE

DDR_CKE

C85100nC85100n

C83 100nC83 100n

C81100nC81100n

C7

C9

C3

VDDQ

VDDQ

VDDQ

CKF8CASG7RAS

E8

CK

NCK

DDR_CLK

DDR_NCLK

VDDQ

C87

C87

DDR_VREF

A3

E2

VREF

CS

G8

CS

CAS

DDR_CS

100n

100n

E3

J1

VSS

VSS

VSS

F7WEF3

RAS

DDR_CAS

DDR_RAS

E7

B8

A7

K9

B2

D8

D2

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSDL

RFU1

RFU2

RFU3

L3

L7

G1

NWE

DDR_WE

DDR_D[0..15]

DDR_A[0..13]

AT91SAM9M10-G45-EK User Guide 4-5

6495B–ATARM–21-Apr-10

Page 15

Board Description

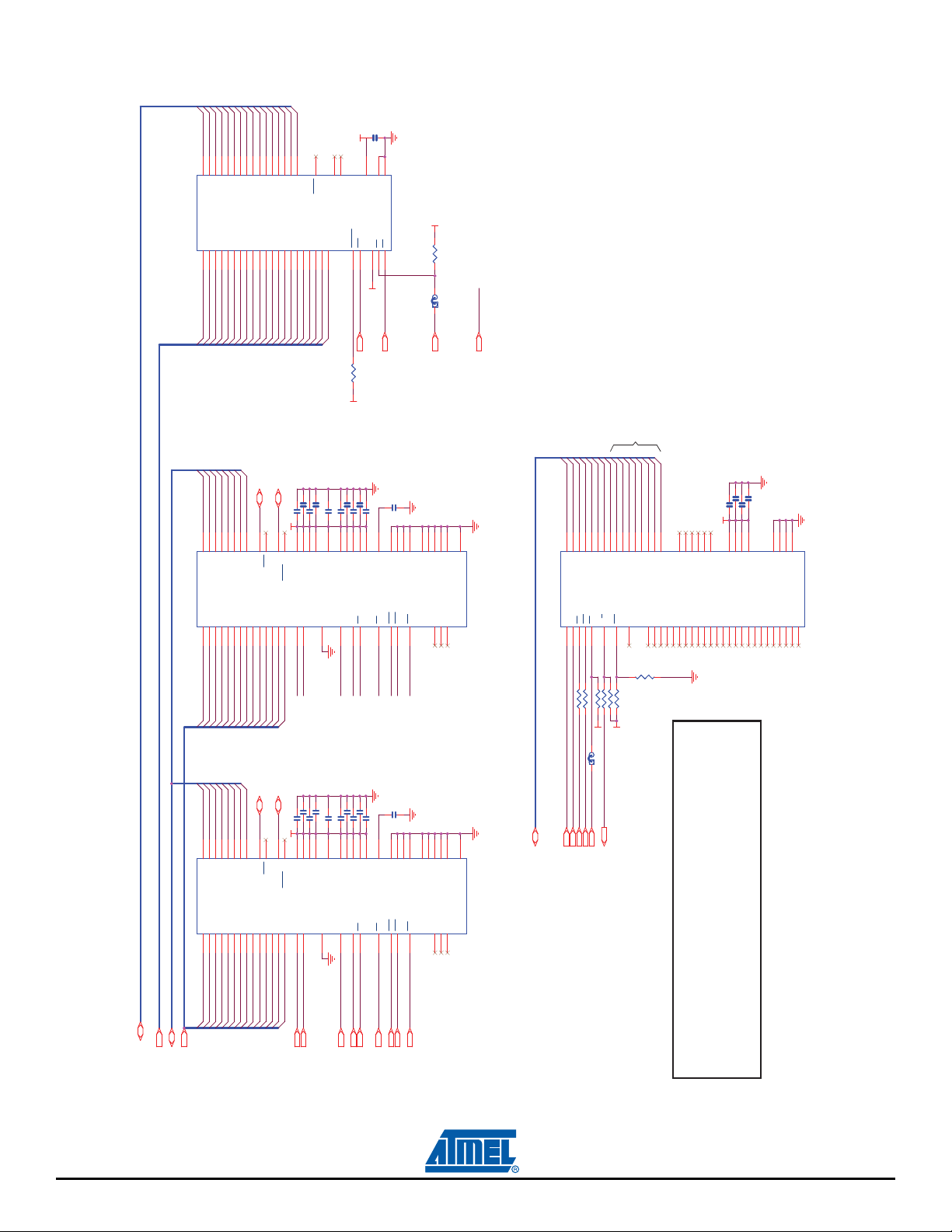

Figure 4-4. EBI1 - DDR2 + Flash

0

_D

LASH

EBI1_F

E2

10

10

N

N

M

M

_A1

LASH

EBI1_F

1_FLASH_D1

EBI

2

H

1

00

O

/

/

I

I

A0E1A1D1A2

_A2

EBI1_FLASH

EBI1_FLASH_D2

E3

H

H

FLAS

FLAS

1

C

_A3

LASH

EBI1_F

2

O

/

I

EBI1_FLASH_D3

H3

3

O

/

I

A3A1A4B1A5

_A4

LASH

EBI1_F

EBI1_FLASH_D4

EBI1_FLASH_D5

EBI1_FLASH_D6

E4

H4

H5

4

O

/

I

I/O5

DT

DT

2

2

AT49SV32

AT49SV32

2

D

_A5

_A6

LASH

LASH

EBI1_F

EBI1_F

EBI1_FLASH_A7

8

7

_D

_D

LASH

LASH_D9

EBI1_FLASH_D10

EBI1_F

EBI1_FLASH

EBI1_F

2

E5

G

F2

I/O6

I/O8

I/O7

I/O9

A6C2A7A2A8B5A9A5A10C5A11

EBI1_FLASH_A10

EBI1_FLASH_A8

EBI1_FLASH_A9

EBI1_FLASH_A11

EBI1_FLASH_D13

EBI1_FLASH_D12

EBI1_FLASH_D14

EBI1_FLASH_D11

I/O10F3I/O11G3I/O12F4I/O13G5I/O14F5I/O15

A12

A13

B6

A6

C6

D5

EBI1_FLASH_A12

EBI1_FLASH_A14

EBI1_FLASH_A15

EBI1_FLASH_A13

A14

EBI1_FLASH_D15

G6

A15

D6

EBI1_FLASH_A16

A16

E6

EBI1_FLASH_A17

100nF

100nF

C100

C100

1V8

G4

A3

RDY/ BUSY

A17B2A18

A19

D4

C3

D3

1_FLASH_A20

1_FLASH_A19

EBI1_FLASH_A21

EBI1_FLASH_A18

EBI

EBI

H1

C4

F6

H6

NC

NC1

VCC

GND

GND

CBGA

CBGA

WE

OE

VPP

A20

RESET

CE

F1

A4

B3

B4

G1

1V8

1V8

DNP

DNP

R40 470KR40 470K

JP9JP9

VREF1

..15]

0

FLASH_D[

_

EBI1

R39 100KR39 100K

EBI1_NRD/CFOE

1V8

EBI1_NWE/NWR0/CFWE

DQS1_EBI1

DQM1_EBI1

C83 100nFC83 100nF

C81 100nFC81 100nFC

C87 100nFC87 100nF

C95 100nFC95 100nF

C89 100nFC89 100nF

C99 100nFC99 100nF

C91 100nFC91 100nF

C93 100nFC93 100nF

C97 100nFC97 100nF

C102

C102

100nF

100nF

VREF1

C1

C7

E3

B8

A7

A3

J1

C9

A9

C3

E1

L1

DT

F9

00nFC

00nF

1

1

6

6

8

8

C

E1

L1

D

VD

ODT

F9

VDDL

88 100nFC88 100nF

C

VDDL

VDDQ

KE

C

F2

EBI1

KE_

C

F

F

n

n

0

0

0 10

0 10

9

9

C

C

A9

VDDQ

CKEF2CK

CKE_EBI1

EBI1

KE_

C

VDDQ

F

F

n

n

0

0

2 10

2 10

9

9

C

C

C1

VDDQ

VDDQ

VDDQ

CK

CK

F8

E8

EBI1

K_

CLK_EBI1

NCL

F

F

F

F

n

n

n

n

0

0

0

0

6 10

6 10

4 10

4 10

9

9

9

9

C

C

C

C

C7

C3

VDDQ

VDDQ

CKF8C

E8

NCLK_EBI1

CLK_EBI1

EBI1

EBI1

K_

L

C

NCLK_

C9

VDDQ

nFC98 100nF

0

C98 10

VDDQ

E2

VREF

CS

G8

CS_EBI1

VREF1

E2

F

VRE

S

C

G8

(NCS1)

CS_EBI1

EBI1

CS_

G7

AS_EBI1

C

C101

C101

A3

G7

CAS_EBI1

VSS

AS

C

VSS

AS

1

EBI

CAS_

VSS

AS

R

F7WEF3

AS_EBI1

R

100nF

100nF

E3

VSS

AS

R

F7

RAS_EBI1

RAS_EBI1

K9

B2

VSS

VSS

VSSQ

VSSQ

G1

WE_EBI1

B2

B8

K9

A7

J1

VSS

VSS

VSSQ

VSSQ

E

W

1

F3

G

EBI1

E_

W

EBI1

E_

W

A8

H2

SDA10)

(

2

A1

R_

D

EBI1_D

A8

H2

(SDA10)

2

A1

R_

D

D

_

EBI1

DQS

A10

K7

R_A13

D

EBI1_D

S

Q

D

A10

K7

3

A1

R_

D

D

_

EBI1

B3

A2

RDQS/NU

RDQS/DM

A11

A13

A12

L8

L2

EBI1_DDR_A14

EBI1_DDR_A15

EBI1

_

0

M

Q

D

1V8 1V8

A2

B3

U

M

S/D

Q

RDQS/N

RD

2

1

A1

A1

A13

2

L8

L

4

5

A1

A1

R_

R_

D

D

_

_DD

EBI1

EBI1

E9

A1

VDD

VDD

BA0G2O

BA1

G3

1

EBI

BA1_EBI1

BA0_

nFC

nF

00

00

0 1

0 1

2 100nFC82 100nF

8

8

8

C

H9

A1

E9

D

D

VD

VD

BA1

BA0

3

2

G

G

1

EBI

_EBI1

_

BA1

BA0

BA1_EBI1

BA0_EBI1

C85 100nFC85 100nF

VDDH9VDD

00nFC84100nF

1

C84

D

VD

10

11

9

D12

_D

_

_D

_D

R

R

R

R

D

D

D

D

1_D

1_D

EBI

EBI1_D

EBI1_DDR_D8

EBI1_D

EBI

EBI1_DDR_D14

EBI1_DDR_D15

EBI1_DDR_D13

9

1

D

B1

C8

D7

D

B9

C2

D3

B7

7

Q4

Q6

Q5

Q

DQ0

DQ2

D

DQ1

DQ3

D

D

D

DQS

F-3

F-3

C

C

DRAM

DRAM

M8

M8

4

4

MN9

MN9

S

S

2

2

R

R

DD

DD

MT47H6

MT47H6

A0

A2

A4

A1

A3

A6

A8

A5

A7

2

J

A5

_

_DDR

1

EBI

1_DDR_D3

EBI

D3

DQ2

3

3

-

F

F

C

C

M8

M8

4

4

H6

H6

7

7

MT4

MT4

A2

J2

DDR_A5

_

EBI1

J8

DR_A6

D

BI1_

E

D4

_

1_DDR

EBI

D1

4

DQ3

DQ

A3

A4J8A5

DDR_A6

_

EBI1

J7

J3

A8

A7

_

R_

D

DR

D

D

_

_

I1

EB

EBI1

D5

D6

_

_

1_DDR

1_DDR

EBI

EBI

D9

B1

6

5

DQ

DQ

A6

J3

J7

DDR_A7

DDR_A8

_

_

EBI1

EBI1

K2

K8

0

A1

A9

R_

R_

D

D

D

D

_

1

EBI

EBI1_

D7

_

1_DDR

EBI

B9

7

DQ

A7

K2

K8

0

A9

A1

R_

R_

D

D

D

D

_

_

EBI1

EBI1

A9

K3

1

A1

R_

D

EBI1_D

EBI1

_

S0

Q

D

B7

S

Q

D

A8

A9

K3

1

A1

R_

D

D

_

EBI1

3

8

7

H

H

H

A3

_

DR_A2

DR_A4

DR

D

D

D

_

1

EBI1_

EBI1_

EBI

1_DDR_D2

1_DDR_D0

1_DDR_D1

EBI

EBI

EBI

C2

C8

D7

DQ1

DQ0

AM

AM

R

R

SD

SD

MN8

MN8

2

2

R

R

DD

DD

A1

A0

H8

H3

H7

_A2

R

DDR_A4

_

EBI1_DDR_A3

EBI1_DD

EBI1

]

5

15]

.

1

..

0.

[

A[1..21]

_

A[2

_D

_

R

DR

DD

FLASH

D

_

_

_

EBI1

EBI1

EBI1

DDR_VREF

EBI1_NCS0

Optional 16bits DATA BUS

With AT29F2G16ABD Micron

C103 100nFC103 100nF

C104 100nFC104 100nF

C106 100nFC106 100nF

C105 100nFC105 100nF

EBI1_NAND_FSH_D4

EBI1_NAND_FSH_D3

EBI1_NAND_FSH_D1

EBI1_NAND_FSH_D5

EBI1_NAND_FSH_D0

EBI1_NAND_FSH_D2

D8

E7

D2

VSSQ

VSSQ

VSSQ

VSSDL

RFU2

RFU1

RFU3

L3

L7

D2

E7

D8

VSSQ

VSSQ

VSSQ

VSSDL

2

1

U

U

F

F

R

R

RFU3

7

L

L3

H4

K4

K7

K6

K5

J7

J4

I/O3

I/O5

I/O0

I/O2

I/O6

I/O4

I/O1

SH

SH

8ABD

8ABD

A

A

G0

G0

29F2

29F2

NAND FL

NAND FL

MT

MT

1

1

WE

CE

RE

R/B

CLE

ALE

MN1

MN1

6

C7

C4

C

D4

C8

D5

REWECE

RB EBI1_NAND_FSH_D6

R

R

0

0

0R

0R

R430RR43

R46 470KR46 470K

R420RR42

R44

R44

1V8

JP10JP10

)

)

E

DAL

DCLE)

AN

AN

(RDY/BSY

(N

(N

(NCS3)

E

E

PC8

O

W

PC4

PC5

PC14

EBI1_NAND

EBI1_NAND

1_NAND_FSH_D[0..15]

EBI

EBI1_NAND_FSH_D7

J8

K

K

1

1

5

5

4

4

R

R

EBI1_NAND_FSH_D14

EBI1_NAND_FSH_D8

EBI1_NAND_FSH_D12

EBI1_NAND_FSH_D11

EBI1_NAND_FSH_D9

EBI1_NAND_FSH_D13

EBI1_NAND_FSH_D15

EBI1_NAND_FSH_D10

G6

H7

H6

H3

G7

J5

J3

I/O7

N.C32

N.C29

N.C27

N.C31

N.C33

N.C28H5N.C30

N.C26

P

OCK

N.C1

N.C3

W

N.C2

L

N.C4

A2

B1

A9

A1

C3

G5

A10

WP

470K

470K

R47

R47

DNP

DNP

1

1

4

4

R

R

1V8

1V8

L9

M2

G4

J6

K3

D3

VCC

VCC

N.C13

N.C15

N.C14

E6

E7

h,

ated

Flas

oc

l

be l

o

Seria

,

ram t

g

lash

aF

p pro

(Dat

ra

m

ootst

b

ootro

b

the

the

se

by

advi

e

rted

po

ore w

sup

ef

ce

Ther

.

devi

er

free

r

noth

a

s erro

i

into

C5

F7

H8

E8

K8

VSS

VSS

VSS

VSS

VCC

VCC

VFBGA-63

VFBGA-63

4

5

2

2

.C22

.C

.C19

.C21

.C23

.C

.C20

N.C16

F3

CC.

E

N

N

N

N.C17

F4

N

N

N

N

N.C18

F5

MT29F2G08ABDHC:D

MT29F2G08ABDHC:D

1

2

L

L

F6

F8

G3

G8

with

ss

acce

h

Flas

nd

t Na

men

mple

i

and

OM)

EEPR

r

RD o

DCA

S

M9

M1

L10

M10

N.C34

N.C38

N.C35

N.C37

N.C39

N.C36

1

2

1

1

.C

.C9

.C8

.C10

.C

N

N

N.C5

N.C7

N

N.C6

N

N

B9

E3

E5

E4

D8

D6

D7

B10

and

ected

nn

co

sh

that block 0

ror Checking

r

dFla

an

ymore

n

f a N

o

ntee a

a

ature ECC (E

ck 0

e

lo

guar

t

g:

not f

n

the b

m

do no

booti

s

fro

ng

.

endor

ystem

v

bootROM does

s

booti

about

llows

a

e NandFlash

note

h

T

tROM

tion) on NandFlash

oo

c

PORTAN

M

I

The b

Corre

on CS3. However, the

Most of t

4-6 AT91SAM9M10-G45-EK User Guide

6495B–ATARM–21-Apr-10

Page 16

4.2.5 Power Supplies

The SAM9M10 Board contains four regulated power supplies:

3.3 VDC Supply

1.8 VDC Supply

1.0 VDC Core Supply

1.0 VDC Core UTMI Supply, PLL

The outputs of these regulated power supplies1 are distributed as necessary to each part of the circuit

board.

The 3.3 VDC Supply is generated by an adjustable LDO. It accepts VIN 5 VCC power and outputs a

regulated +3.3 V to most other circuits on the board.

The 1.8 VDC Supply (VDDIOM0, VDDIOM1) is generated by an adjustable LDO. It is powered by VIN

5 VCC power and outputs a regulated +1.8V.

The 1.0 VDC Core Supply (VDDCORE) is generated by an adjustable LDO. It is powered by the

output of the 3.3 VDC Supply.

The 1.0 VDC Core Supply (VDDUTMIC, VDDPLLUTMI and VDDPLLA) is generated by an adjustable

LDO RT9186A series. It is powered by the output of the 3.3 VDC Supply.

Board Description

Note: 1. Corresponding test points (TP1 to TP4, GND) are used with jumpers (JP1.1 to JP7) to

permit probing of these voltages.

AT91SAM9M10-G45-EK User Guide 4-7

6495B–ATARM–21-Apr-10

Page 17

Board Description

1V_VDDUTMIC

3V3

3V3

3V3

1V

1V8

1V_VDDUTMIC

VDDUTMII

VDDANA

VDDOSC

VDDIOP0

VDDIOP1

VDDIOP2

VDDISI

VDDUTMIC

VDDPLLUTMI

VDDPLLA

VDDCORE

VDDIOM0

VDDIOM1

VDDBU

J3J3

JP3JP3

1

2

3

C29

4.7u

C29

4.7u

J1-1J1-1

1

2

C2

4.7uC24.7u

JP1JP1

1

2

3

C14

4.7u

C14

4.7u

R201RR20

1R

C221uC22

1u

JP2JP2

1

2

3

C1

100nC1100n

J1-3J1-3

5 6

R13

100k

R13

100k

R10

100k

R10

100k

C15

2.2u

C15

2.2u

R121RR12

1R

JP7JP7

1

2

3

C18

100n

C18

100n

JP6JP6

1

2

3

C251uC25

1u

C20

4.7u

C20

4.7u

MN3

RT9186A

MN3

RT9186A

VIN

1

VIN

2

PGOOD

3

EN

4

GND

5

ADJ

6

VOUT

7

VOUT

8

EP

9

C30

100n

C30

100n

JP5JP5

1

2

3

C28

100n

C28

100n

L4 10uHL4 10uH

R51RR5

1R

J1-2J1-2

3 4

C21

10u

C21

10u

C19

10n

C19

10n

L3 10uHL3 10uH

L1 10uHL1 10uH

R19

47k

R19

47k

R14

12k

R14

12k

C8

100nC8100n

J1-4J1-4

7

8

L2 10uHL2 10uH

R11RR1

1R

Figure 4-5. Power Supply

4-8 AT91SAM9M10-G45-EK User Guide

6495B–ATARM–21-Apr-10

Page 18

Figure 4-6. Management Power Block

PWR_EN

5V

1V

1V

5V

1V8

1V8

5V

3V3

3V3

5V

3V3

SHDN

FORCE

POWER

ON

REGULATED

5V ONLY

MN4

RT9018A

MN4

RT9018A

PGOOD

1

EN

2

VIN

3

VDD

4

NC

5

VOUT

6

ADJ

7

GND

8

EP

9

C9

10uC910u

C12

10u

C12

10u

R9

100kR9100k

R18

12k

R18

12k

C111uC11

1u

C261uC26

1u

R11

100k

R11

100k

C23

10u

C23

10u

R16

10k

R16

10k

C3 10nC3 10n

MN1

RT9186A

MN1

RT9186A

VIN

1

VIN

2

PGOOD

3

EN

4

GND

5

ADJ

6

VOUT

7

VOUT

8

EP

9

R2

100kR2100k

C16 10nC16 10n

C5

10nC510n

C4

33u

+

C4

33u

R6

12kR612k

R4 47kR4 47k

C17

15p

C17

15p

R15 15kR15 15k

C71uC7

1u

R7

15kR715k

JP4

SIP2

JP4

SIP2

12

CR15VCR1

5V

MN2

RT9018A

MN2

RT9018A

PGOOD

1

EN

2

VIN

3

VDD4NC

5

VOUT

6

ADJ

7

GND

8

EP

9

Q1

Si1563EDH

Q1

Si1563EDH

1 3

2

4

5

6

C6

10uC610u

R199

100k

R199

100k

J2

DC POWER JACK

J2

DC POWER JACK

1

2

3

R8

47kR847k

C131uC13

1u

R17

10k

R17

10k

C27

10u

C27

10u

C101uC10

1u

C241uC24

1u

R3

100kR3100k

Board Description

AT91SAM9M10-G45-EK User Guide 4-9

6495B–ATARM–21-Apr-10

Page 19

Board Description

TDI

RTCK

TDO

TMS

TCK

NTRST

NRST

3V3 3V3

3V3

NTRST

RTCK

TDI

TMS

TCK

TDO

NRST

ICE INTERFACE

R92 0RR92 0R

J13

HTST-110-01-SM-D

J13

HTST-110-01-SM-D

12

3

4

5

6

7

8

9

10

11

12

13

15

17

19

14

16

18

20

R94

0R

DNP

R94

0R

DNP

R93 0RR93 0R

R91 0R

DNP

R91 0R

DNP

RR43

100k

RR43

100k

123

4 5

678

3V3

3V3

PB13

PB12

SERIAL DEBUG PORT

C1+

V+

VCC

C1C2+

C2-V-

T

T

R

R

GND

MN15

ADM3202ARNZ

C1+

V+

VCC

C1C2+

C2-V-

GND

MN15

ADM3202ARNZ

1

16

3

4

5

15

11

10

12

98

13

7

14

2

6

R87

100k

R87

100k

C159

100n

C159

100n

R90 0RR90 0R

C163

100n

C163

100n

C157 100nC157 100n

R88

100k

R88

100k

C158 100nC158 100n

J10J10

5

4

3

2

1

9

8

7

6

10

11

C165 100nC165 100n

4.2.6 Debug Interface

4.2.6.1 JTAG/ICE

Software debug is accessed by a standard 20-pin JTAG connection. This allows connection to a standard USB-to-JTAG in-circuit emulator.

Figure 4-7. JTAG Interface

4.2.6.2 DBGU Com Port

This UART is connected to the DB-9 male socket through an RS-232 Transceiver (TXD and RXD only).

Figure 4-8. DBGU Com Port

4-10 AT91SAM9M10-G45-EK User Guide

6495B–ATARM–21-Apr-10

Page 20

4.2.6.3 User Serial Com Port

3V3

3V3

PB5

PD17

PB4

PD16

RS232 COM PORT

C161

100n

C161

100n

C1+V+VCC

C1C2+

C2- V-

T

T

R

R

GND

MN16

ADM3202ARNZ

C1+V+VCC

C1C2+

C2- V-

GND

MN16

ADM3202ARNZ

1 16

3

4

5

15

11

10

12

9 8

13

7

14

2

6

C166 100nC166 100n

C162 100nC162 100n

C160

100n

C160

100n

J11J11

5

4

3

2

1

9

8

7

6

10

11

R86

100k

R86

100k

C164

100n

C164

100n

R89

100k

R89

100k

The USART1 is used as a user serial communication port. This USART1 is buffered with an RS-232

Transceiver (TXD, RXD and handshake CTS/RTS control) and connected to the DB-9 male socket. Soft

ware must assign the appropriate PIO pins (PB5 = RXD1, PB4 = TXD1, PD16 = RTS1, PD17 = CTS1) to

enable the UART1 function.

Figure 4-9. User Serial Com Port

Refer to the SAM9M10 datasheet for more information about the SAM9M10 USARTs.

Board Description

-

4.2.6.4 USB Port

The SAM9M10-G45-EK features USB communication ports:

Two Host Ports: Full speed OHCI and High speed EHCI

One Device Port: High speed.

USB Host Port0 is directly connected to the first UTMI transceiver. The second Host Port (Port1) is multiplexed with the USB Device High speed and connected to the second UTMI port.

One USB high/full speed type standard A connector

One USB interface Host/Device Micro AB connector

Refer to the SAM9M10 datasheet for detailed programming information.

AT91SAM9M10-G45-EK User Guide 4-11

6495B–ATARM–21-Apr-10

Page 21

Board Description

5V

3V3

PD2

PD4

PD1

HDMA

HDPA

PD3

HDMB

HDPB

PD28

PB19

USB HOST/DEVICE INTERFACE

USB HOST INTERFACE

(ENA)

(ENB)

(FLGA)

(FLGB)

(VBUS)

(IDUSB)

C171

10p

C171

10p

R96

68k

R96

68k

R95 47kR95 47k

+

C170

33u

+

C170

33u

C169

100n

C169

100n

J12

G3505-4NBT1S1W

J12

G3505-4NBT1S1W

1

4

5

2

3

6

SHIELD

J14

G3515-09010101-00

VBUS

DM

DP

ID

GND

USB-A

J14

G3515-09010101-00

1

2

3

4

5

7

6

+

C168

33u

+

C168

33u

R97

47k

R97

47k

L14

220ohm at 100MHz

L14

220ohm at 100MHz

1

2

C167

100n

C167

100n

MN17

AIC1526-0GS

MN17

AIC1526-0GS

ENA

1

FLGA

2

ENB

4

OUTA

8

GNG6FLGB

3

IN

7

OUTB

5

L13

220ohm at 100MHz

L13

220ohm at 100MHz

1 2

C172

100n

C172

100n

Figure 4-10. USB Port

4.2.6.5 Ethernet 10/100 (EMAC) Port

The port is compatible with IEEE® Standard 802.3.

The SAM9M10-G45-EK is equipped with a Davicom DM9161AEP 10/100 Mbps Fast Ethernet Physical

Layer TX/FX Single Chip Transceiver. It contains the entire physical layer functions of 100BASE-TX as

defined by IEEE 802.3u, including the Physical Coding Sublayer (PCS), Physical Medium attachment

(PMA), Twisted Pair Physical Medium Dependent Sublayer (TP-PMD), 10BASE-TX Encoder/Decoder

(ENC/DEC), and Twisted Pair Media Access Unit (TPMAU).

The Ethernet interface integrates an RJ45 connector with an embedded transformer, and three status

LEDs.

The Ethernet interface provides two selectable modes, MII or RMII (Reduced MII), for 100Base-TX or

10Base-TX. The MII and RMII interfaces are capable of both 10Mb/s and 100Mb/s data rates as

described in the IEEE 802.3u standard. The signals used by MII and RMII interfaces are described in the

table below.

4-12 AT91SAM9M10-G45-EK User Guide

6495B–ATARM–21-Apr-10

Page 22

Board Description

Table 4-2. Pin Mapping for Normal MII and Reduced MII

Pin Name Normal MII Mode Reduced MII Mode

SAM9M10 DM9161 SAM9M10 DM9161

ETX0-ETX1 ETX[0:1] transmit data TXD [0:1] ETX[0:1] TXD [0:1]

ETX2-ETX3 ETX[2:3] transmit data TXD [2:3] NC NC

ETXEN ETXEN: transmit enable TXEN ETXEN: transmit enable TXEN

ETXER ETXER: transmit error TXER/TXD[4] NC NC

ETXCK/REFCK ETXCK: transmit clock TXCLK REFCK: reference clock REF_CLK

ERX0-ERX1 ERX[0:1]: receive data RXD [0:1] ERX[0:1]: receive data RXD [0:1]

ERX2-ERX3 ERX[2:3]: receive data RXD [2:3] NC NC

ERXER ERXER: receive error

ERXDV ERXDV: receive valid data RXDV

RXER/RXD[4]/

RPTR/NODE

ERXER: receive error RPTR/NODE

ECRSDV: carrier sense /

data valid

CRS DV

ERXCK ERXCK: receive clock RXCLK NC NC

ECOL ECOL: collision detect COL NC NC

ECRS

EMDC EMDC: management data clock MDC

EMDIO

NRST NRST: microcontroller reset

ECRS: carrier sense /

data valid

EMDIO: management data

input / output

CRS (PHYAD[2:4] NC NC

MDIO

RESET# XT1

(25 MHz)

EMDC: management data

clock

EMDIO: management data

input / output

NRST: microcontroller reset

MDC

MDIO

RESET# XT1

(REF_CLK 50MHz)

AT91SAM9M10-G45-EK User Guide 4-13

6495B–ATARM–21-Apr-10

Page 23

Board Description

Figure 4-11. Ethernet Port

GND_ETH

C176

100n

C176

100n

R107

R107

R102

R102

49.9R

49.9R

49.9R

49.9R

1

TX+

16

15

J15

J15

TD+

1

3

AVDDT

RX+

RD+

365

6

RX-

RD-

CT

2

TX-

TD-

CT

2

4

5

7

4

8

75

75

7575

1nF

J00-0061NL

NC

7

C178

100n

C178

100n

49.9R

49.9R

R113

R113

R111

49.9R

R111

49.9R

AVDDT

2

L15

2200R

L15

2200R

1

J00-0061NL

8

RJ45 ETHERNET CONNECTOR

GND_ETH

C183

100n

C183

100n

GND_ETH

10V

10V

C181

10u

C181

10u

GND_ETH

3V3

C180

10u

10V

C180

10u

10V

6

7

8

3V3

R118

R118

10k

10k

RR47

RR47

SPEED 100

FULL DUPLEX

470R

470R

470R

470R

R119

R119

1

12

D4 YellowD4 Yellow

D5 GreenD5 Green

2

4 5

3

2

1

R121

R121

LINK&ACT

470R

470R

GreenD6Green

12

D6

R117

6.8k

R117

6.8k

AVDDT

MDC

R116 0RR116 0R

C182 100nC182 100n

11

48

31

BGRES

LEDMODE

DGND

15

33

RR46

RR46

RR45

RR45

RR44

RR44

10k

10k

10k

10k

10k

10k

44

DGND

45

14

N.C

LED2/OP213LED1/OP112LED0/OP0

CABLESTS/LINKSTS

C187

PWRDWN10DGND

RESET

40

R120 0RR120 0R

NRST

C187

3V3

GND_ETH

R123 0RR123 0R

10u

10u

10V

10V

R122 0RR122 0R

9

6

46

47

AGND5AGND

AGND

AVDDT

BGRESG

DM9161AEP

DM9161AEP

MDIO25MDINTR

DVDD

DISMDIX

32

39

3V3

2

JP16JP16

6

7

8

6

7

8

6

7

8

41

C184100nC184100n

1

DVDD

DVDD

23

30

C186100nC186100n

C185100nC185100n

4 5

3

2

1

3V3

4 5

3

2

1

4 5

3

2

1

C177 100nC177 100n

C179 100nC179 100n

4

3

TXD317TXD2

DNP

DNP

R108 0R

R108 0R

R103 0R DNPR103 0R DNP

7

18

TX+

TX_EN

TXD020TXD119TX_CLK/ISOLATE

21

22

R106 0R DNPR106 0R DNP

8

TX-

RX+

RXD0/PHYAD029RXD1/PHYAD128RXD2/PHYAD227RXD3/PHYAD3

26

DNP

DNP

R104 0R DNPR104 0R DNP

R105 0R

R105 0R

43

C175

22p

DNP

C175

22p

DNP

Y5

24

1 3

C174

22p

DNP

C174

22p

DNP

DNP

DNP

R100 0R

R100 0R

C173

100n

C173

3V3

100n

32

41

VDD

VDD

50MHz

50MHz

VSS OUT

OE

VSS OUT

OE

R98 10kR98 10k

Y4

Y4

XT1

25MHz

DNPY525MHz

DNP

REF_CLK/XT2

MN18

MN18

42

R101 0RR101 0R

R990RR99

0R

34

DNP

DNP

R109 0R

R109 0R

RX_CLK/10BTSER

37

RX-

RX_DV/TESTMODE

R110 0R DNPR110 0R DNP

16

TX_ER/TXD4

38

RX_ER/RXD4/RPTR

1

AVDDR

COL/RMII

36

R112 0R DNPR112 0R DNP

R114 0R DNPR114 0R DNP

35

2

AVDDR

CRS/PHYAD4

24

R115 1.5kR115 1.5k

3V3

(TX_CLK)

PA17

(TXD3)

(TXD2)

PA7

(RXD2)

(TXD1)

(TXD0)

(TX_EN)

(RXD3)

PA14

PA6

PA11

PA9

PA10

(TX_ER)

(RXD1)

PA8

(RX_ER)

(RXD0)

(RX_CLK)

(RX_DV)

PA27

PA15

PA28

PA12

PA13

(MDINTR)

(COL)

(CRS)

(MDC)

(MDIO)

PD5

PA19

PA16

PA18

PA29

PA30

For more information about the Ethernet controller device, refer to the Davicom DM9161 controller manufacturer's datasheet.

4-14 AT91SAM9M10-G45-EK User Guide

6495B–ATARM–21-Apr-10

Page 24

4.2.7 Audio Stereo Interface

The SAM9M10-G45-EK includes a WM9711L AC97 CODEC for digital sound input and output. This

interface includes audio jacks for MIC input (J9), line audio input (J8), headphone line output (J7) and a

2-point speaker output connector (JP15).

It is compliant with AC97 Component Specification V2.2.

Board Description

AT91SAM9M10-G45-EK User Guide 4-15

6495B–ATARM–21-Apr-10

Page 25

Board Description

Figure 4-12. Audio Stereo Interface

R73 10kR73 10k

JP17/JP18 are used

as testpoints

3V3

C136

C136

100n

100n

R74 100kR74 100k

3V3

AGND_AC97

1

2

3

4

5

6

7

8

9

10

11

12

MN14

MN14

DBVDD

XTLIN

XTLOUT

DGND1

SDATAOUT

BITCLK

DGND2

SDATAIN

DCVDD

SYNC

RESET

CREF

PE31

PD7

PD9

PD6

PD8

NRST

(EXT_CLK)

C133 22pC133 22p

C137 22pC137 22p

DNP

DNP

R75 0R

R75 0R

Y3

2 4

24.576MHzY324.576MHz

1 3

(AC97TX)

(AC97CK)

(AC97RX)

(AC97FS)

C134

C134

C135

C135

10u

10u

10V

10V

100n

100n

R78 49.9RR78 49.9R

AVDD_AC97

JP17 DNPJP17 DNP

12

DNP

DNP

JP18

JP18

12

48

47

46

49

GPIO4

THERMAL

GPIO5/SPDIF

44

45

43

42

GPIO3

GPIO1

HPVDD

GPIO2/IRQ

WM9711L

WM9711L

41

AGND2

HP_OUT_R

40

HP_GND

38

39

SPKVDD

HP_OUT_L

C130

C130

100n

100n

37

C131

C131

100n

100n

AGND_AC97

OUT3

ROUT2

LOUT2

SPKGND

MONOOUT

CAP2

COMP3

COMP2

COMP1

MICBIAS

VREF

AGND

AVDD1

10u

10u

10V

10V

36

35

34

33

32

31

30

29

28

27

26

25

C132

C132

R69 0RR69 0R

R70 0RR70 0R

1 2

JP14

JP14

DNP

DNP

C138

C138

100n

100n

C126 100u/6.3V

C126 100u/6.3V

C127 100u/6.3V

C127 100u/6.3V

AGND_AC97

C139

C139

100n

100n

C140

C140

10u

10u

10V

10V

+

+

+

+

C141

C141

100n

100n

R71

R71

47k

47k

R76 0RR76 0R

R77 0RR77 0R

C142

C142

10u

10u

10V

10V

C143

C143

100n

100n

R72

R72

47k

47k

AGND_AC97

C144

C144

10u

10u

10V

10V

L6

L6

220ohm at 100MHz

220ohm at 100MHz

2

1

1 2

L7

L7

220ohm at 100MHz

220ohm at 100MHz

12

JP15

JP15

8 Ohm SPEAKER

DNP

DNP

OUTPUT

C128

C128

470p

470p

C129

C129

470p

470p

1

HEADPHONE

LINE-OUT

2 5

3

STEREO_3.5mm

STEREO_3.5mm

J7

J7

4

AVDD_AC97

C145

C145

100n

100n

AGND_AC97

3V3 AVDD_AC97

L11

L11

10uH

10uH

C152

C152

C153

C153

10u

10u

100n

100n

10V

10V

R850RR850R

C154

C154

10u

10u

10V

10V

AGND_AC97

NC114NC215PHONE20PCBEEP19AGND118LINE_IN_L23LINE_IN_R

MIC121MIC2

AVDD2

NC417NC3

22

13

16

AGND_AC97

R83

R83

680R

680R

AGND_AC97

R84

R84

680R

680R

R81

R81

8.2K

8.2K

R82

R82

8.2K

8.2K

AGND_AC97

R79 8.2KR79 8.2K

R80 8.2KR80 8.2K

L8

L8

220ohm at 100MHz

220ohm at 100MHz

1 2

L9

L9

1 2

220ohm at 100MHz

220ohm at 100MHz

L10

L10

220ohm at 100MHz

220ohm at 100MHz

2

1

1 2

L12

L12

220ohm at 100MHz

220ohm at 100MHz

C148

C148

470p

470p

C155

C155

470p

470p

C149

C149

470p

470p

C156

C156

470p

470p

2 5

1

3 4

STEREO_3.5mm

STEREO_3.5mm

MONO / STEREO

MICROPHONE INPUT

2 5

1

3 4

STEREO_3.5mm

STEREO_3.5mm

LINE-IN

J8

J8

J9

J9

24

C1461uC146

1u

C1471uC147

1u

C1501uC150

1u

C1511uC151

1u

AGND_AC97

For more information about the AC97 codec device, refer to the Wolfson WM9711L controller manufacturer's datasheet.

4-16 AT91SAM9M10-G45-EK User Guide

6495B–ATARM–21-Apr-10

Page 26

4.2.8 TV-Out Extension

PE23

PE24

PE25

PE26

PE27

PE28

PE29

PE30

PE15

PE16

PE17

PE18

PE19

PE20

PE21

PE22

PE7

PE8

PE9

PE10

PE11

PE12

PE13

PE14

PE6

PE6

PE17

PE12

PE28

PE23

PE7

PE1

PE18

PE13

PE29

PE24

PE8

PE2

PE0

PE19

PE3

PE14

PE25

PE9

PE20

PE4

PE15

PE26

PE10

PE21

PE5

PE16

PE11

PE27

PE30

PE22

1V8

3V3

3V3

3V3

3V3

3V3

PE[0..30]

PA21

NRST

PA20

TV_XCLK

TV_HSYNC

TV_VSYNC

Composite

Video

Output

(LCDMOD)

(G4)

(R6)

(B3)

(LCDPWR)

(G5)

(LCDDEN)

(LCDCC)

(R7)

(G0)

(B4)

(G6)

(B5)

(R2)

(G7)

(B0)

(G1)

(B6)

(R3)

(G2)

(B7)

(R1)

(R4)

(B1)

(G3)

(LCDDOTCK)

(R5)

(R0)

(B2)

(HSYNC)

(VSYNC)

(TW DO)

(TW CK0)

L21

2200R

L21

2200R

1

2

C197

100n

C197

100n

MN20

CH7024B

MN20

CH7024B

D7

1

D8

2

D9

3

D10

4

D11

5

D12

6

D13

7

D14

8

D15

9

D16

10

D17

11

D18

12

D19

13

D20

14

D21

15

D22

17

D23

19

D0

42

D1

43

D2

44

D3

45

D4

46

D5

47

D6

48

V

39

H

40

XCLK

41

DE

20

RESET

23

VDDIO

38

AVDD_DAC

25

DVDD

16

AVDD_PLL

32

AVDD

33

DGND

18

AGND_DAC

29

AGND_PLL

31

AGND

36

SPD

21

SPC

22

NC

24

C/CVBS

26

Y

27

CVBS

28

ISET

30

XI/FIN34XO

35

P-OUT

37

D8

BAT54SLT1G

D8

BAT54SLT1G

1 2

3

R1804.7kR1804.7k

C204 33pC204 33p

C206

100p

C206

100p

C200

100n

C200

100n

R183 75RR183 75R

C205

100p

C205

100p

C208

10p

C208

10p

R178 1.2k

1%

R178 1.2k

1%

L18

2200R

L18

2200R

1

2

J20J20

RCA JACK

3

1

C203

100n

C203

100n

C199

10u

10V

C199

10u

10V

C202

100n

C202

100n

R1860R

DNP

R1860R

DNP

VDD

VSS OUT

OE

Y6

13MHz

DNP

VDD

VSS OUT

OE

Y6

13MHz

DNP

41

32

C207

100n

DNP

C207

100n

DNP

R18175RR18175R

TP6TP6

R1850RR185

0R

L17

2200R

L17

2200R

1

2

L22

1.8uH

L22

1.8uH

R179 4.7kR179 4.7k

R182

75R

R182

75R

C198

10u

10V

C198

10u

10V

L19

2200R

L19

2200R

1

2

L20

2200R

L20

2200R

1

2

C196

100n

C196

100n

Y7

13MHzY713MHz

1 3

24

C209

10p

C209

10p

R18410kDNPR18410kDNP

C201

10u

10V

C201

10u

10V

The Chrontel™ CH7024 chip provides an interface between the SAM9M10 LCD Controller and a TV set

by converting LCD signals to TV signals.

The CH7024 is a TV encoder device which encodes the video signals and generates synchronization

signals for NTSC and PAL standards. Supported TV output formats are NTSC-M, NTSC-J, NTSC-433,

PAL-B/D/G/A/I, PAL-M, PAL-N and PAL-60. The CH7024 provides video output support for CVBS or Svideo.

Figure 4-13. TV-Out Extension Port

Board Description

AT91SAM9M10-G45-EK User Guide 4-17

6495B–ATARM–21-Apr-10

Page 27

Board Description

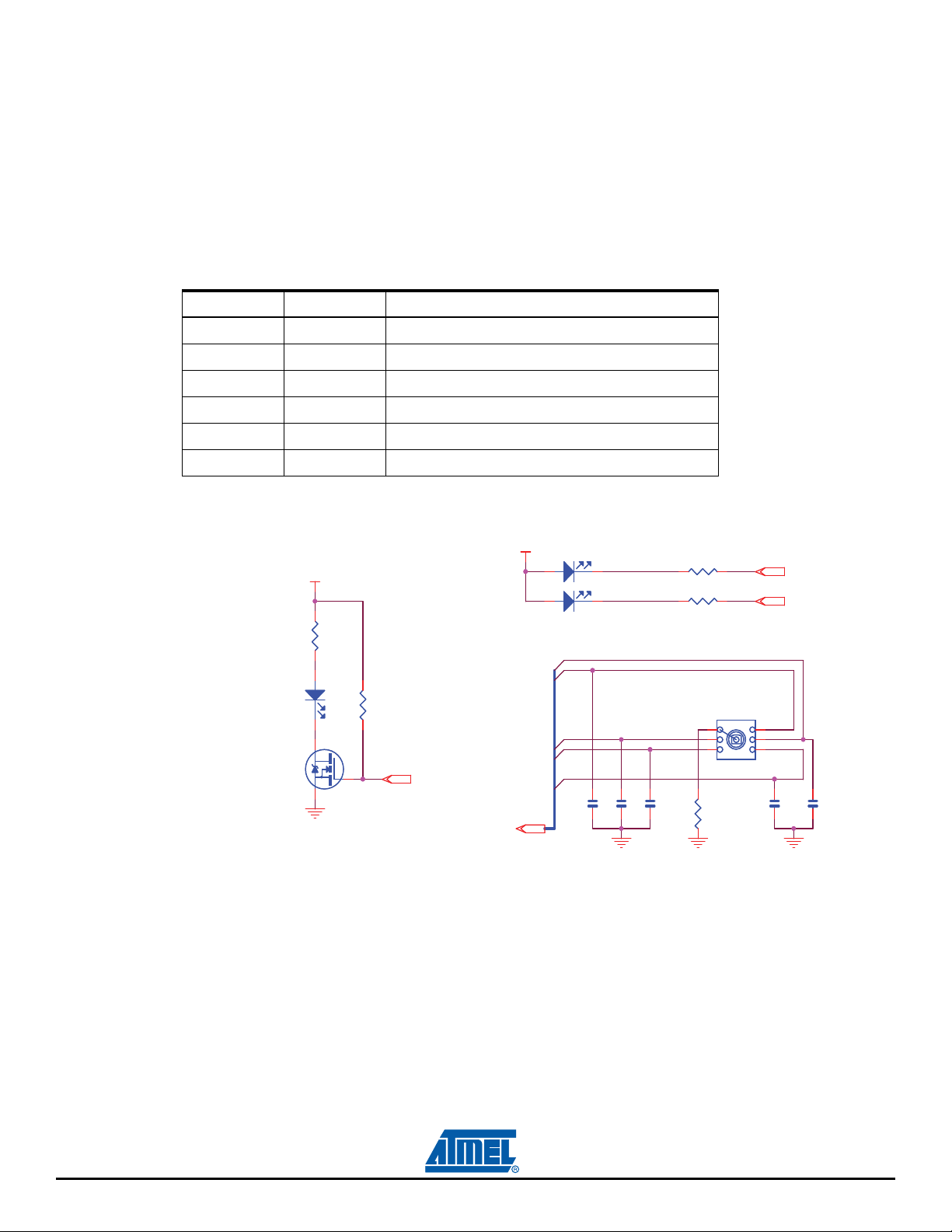

4.2.9 Software Controlled LEDs

Three users LED are provided for general use. The LEDs are connected to PIO port lines, allowing their

control through either GPIO or PWM control.

LEDs D1 to D3 are software controlled by PIO pins.

LEDs D4 to D6 indicate Ethernet traffic and link status. These are automatically managed by on-chip

microcontroller hardware. See Section 7.1 ”Schematics” .

Table 4-3. Discrete LEDs

LED Description Comment

D1 Green LED User software controlled

D2 Green LED User software controlled

D3 Red LED User software controlled

D4 Yellow LED Indicates transmission or reception via Ethernet

D5 Green LED Indicates speed 100

D6 Green LED Is lit when a good link test has been detected

Figure 4-14. Software Controlled LEDs

USER INTERFACE

3V3

R25

R25

470R

470R

12

IRLML2402

IRLML2402

D3

RedD3Red

3

Q2

Q2

2

R26

R26

100k

100k

1

PD30

POWER LED

PB[14..18]

3V3

GreenD1Green

D1

1

D2

1 2

GreenD2Green

PB15

PB16

PB14

PB18

PB17

C32

C32

10n

10n

R21 470RR21 470R

R22 470RR22 470R

LEFT

PUSH

C34

C34

10n

10n

BP3BP3

1

2

3

JOYSTICK

R28

R28

100R

100R

4

5

6

UP

RIGHT

DOWN

C35

C35

10n

10n

PD0

PD31

C36

C36

10n

10n

2

C33

C33

10n

10n

4-18 AT91SAM9M10-G45-EK User Guide

6495B–ATARM–21-Apr-10

Page 28

4.2.10 Serial Peripheral Interface Controller (SPI)

3V3

3V3

PB1

PB2

PB3

PB0

NRST

SERIAL DATAFLASH

(test points)

(SPI0_MISO)

(SPI0_MOSI)

(SPI0_SPCK)

(SPI0_NPCS0)

JP12

SIP2

JP12

SIP2

1

2

C124

100n

C124

100n

JP11

DNP

JP11

DNP

1

2

3

R67

470k

R67

470k

MN13MN13

RESET

3

GND

7

VCC

6

CS

4

SCK

2

SI

1

SO

8

WP

5

R68

0R

DNP

R68

0R

DNP

3V3

3V3

PA21

PA20

SERIAL EEPROM

(TW CK0)

(TW DO)

JP13

SIP2

JP13

SIP2

12

R66

10k

R66

10k

C125 100nC125 100n

MN12MN12

A0

1

A1

2

WP

7

SCL

6

VCC

8

A3

3

SDA

5

GND

4

Board Description

The SAM9M10 provides two high-speed Serial Peripheral Interface (SPI) controllers. One port is used to

interface with the on-board serial DataFlash

Figure 4-15. SPI

4.2.11 Two Wire Interface (TWI)

The SAM9M10 has a full speed (400 kHz) master/slave I2C Serial Controller. The controller is fully compatible with the industry standard I2C and SMBus Interfaces. This port is used to interface with the onboard Serial EEPROM, ISI and TV encoder interface.

Figure 4-16. TWI

®

.

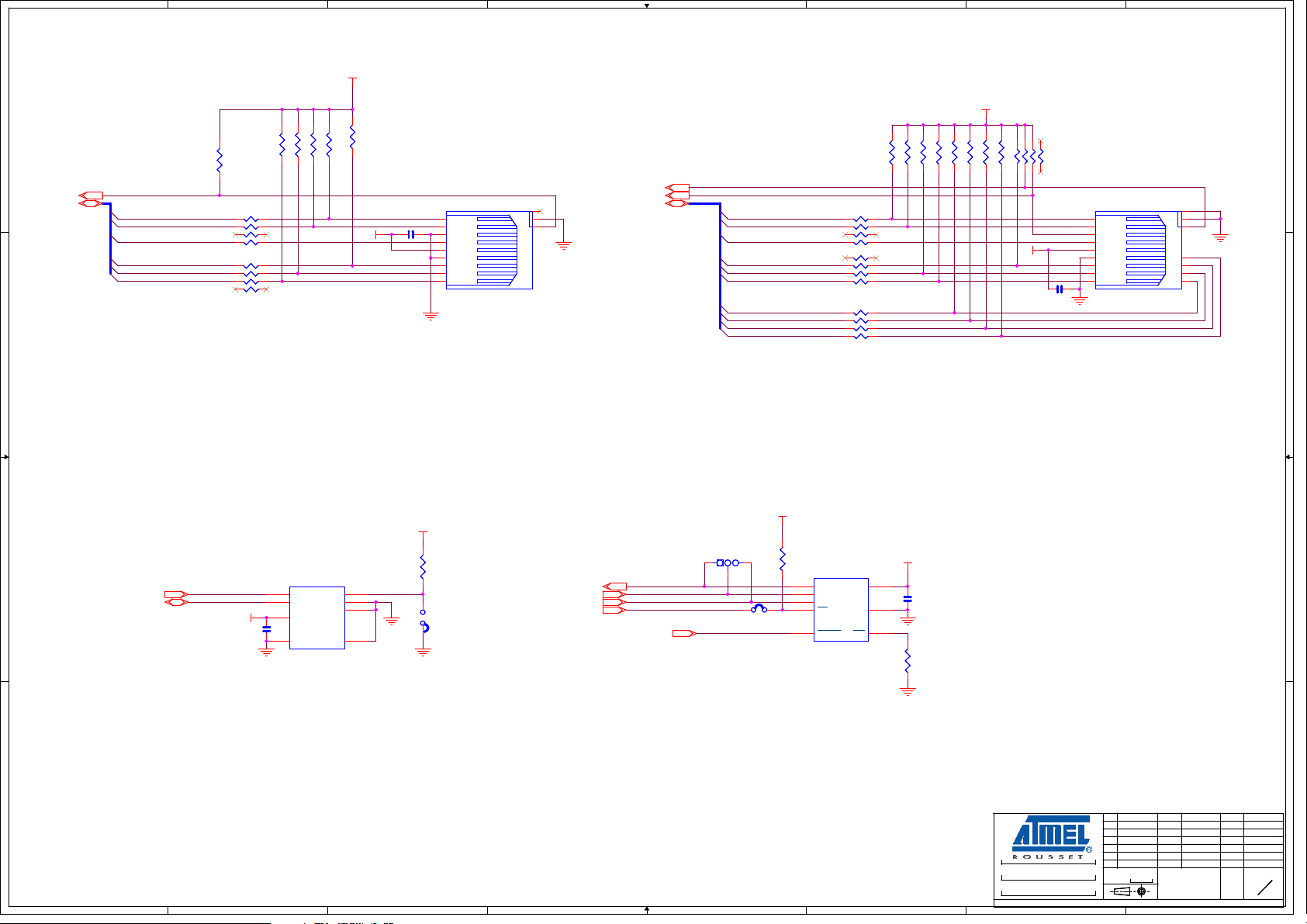

4.2.12 SD/MMC Interface

The SAM9M10-G45-EK has two high-speed 8-bit multimedia interfaces MMC/MMCPlus v4.1. The first

interface is used as an 8-bit interface (MCI1), connected to a CE-ATA connector footprint and an 8-bit

SD/MMC card slot. The second interface is used as a 4-bit interface (MCI0), connected to a 4-bit

SD/MMC card slot.

The users must provide their own compatible cards for use with these connectors.

Please note that the power is connected to VCC, which is 3.3 volts.

AT91SAM9M10-G45-EK User Guide 4-19

6495B–ATARM–21-Apr-10

Page 29

Board Description

PA26

PA25

PA27

PA28

PA29

PA30

PA24

PA23

PA31

PA22

3V3

3V3

PD29

PD11

PA[22..31]

SD/MMCPlus CARD INTERFACE - MCI1

(MCI1_DA1)

(MCI1_DA0)

(MCI1_CK)

(MCI1_CDA)

(MCI1_DA3)

(MCI1_DA2)

(MCI1_DA4)

(MCI1_DA5)

(MCI1_DA7)

(MCI1_DA6)

(MCI1_CD)

(MCI1_W P)

RR36

10k

RR36

10k

123

4 5

678

R192

68k

R192

68k

RR39

27R

RR39

27R

1

2

3

4

5

6

7

8

R193

68k

R193

68k

C123

100n

C123

100n

R194

68k

R194

68k

RR41 27RRR41 27R

1

2

3

4

5

6

7

8

R195

68k

R195

68k

RR42

27R

RR42

27R

1

2

3

4 5

6

7

8

R196

68k

R196

68k

R197

68k

R197

68k

R198

68k

R198

68k

J5J5

8

5

7

6

4

3

2

1

9

14

15

16

13

12

11

10

R191

68k

R191

68k

PA1

PA5

PA4

PA

3

PA2

PA0

3V3

3V3

PD10

PA[0..5]

SD/MMC CARD INTERFACE - MCI0

(MCI0_DA1)

(MCI0_DA0)

(MCI0_CK)

(MCI0_CDA)

(MCI0_DA3)

(MCI0_DA2)

(MCI0_CD)

R188

68k

R188

68k

R189

68k

R189

68k

R187

68k

R187

68k

R64

10k

R64

10k

R190

68k

R190

68k

R65

10k

R65

10k

RR38 27RRR38 27R

1

2

3

4

5

6

7

8

J6J6

8

5

7

6

4

3

2