特点

• 集成了 ARM7TDMI

– 高性能的 32 位 RISC 架构

– 高密度的 16 位指令集

– 性能 / 功耗 (MIPS/Watt) 的领先者

– 嵌入式 ICE 电路仿真,支持调试通讯

• 64K 字节的片内高速 Flash 存储器,共 512 页,每页 128 字节

– 在最坏的条件下可以 30 MHz 的速度进行单时钟周期访问 ,

预取 (Prefetch) 缓冲器可以实现 Thumb 指令的优化,使处理器以最快的速度执行指令

– 页编程时间为 4 ms,包括页自动擦除,全片擦除时间为 10 ms

– 10,000 次的写寿命, 10 年数据保持能力,扇区锁定功能, Flash 安全锁定位

– 适合量产的快速 Flash 编程接口

• 16K 字节的片内高速 SRAM,可以在最高时钟速度下进行单时钟周期访问操作

• 存储器控制器 (MC)

– 嵌入式 Flash 控制器,异常中断 (Abort) 状态及未对齐 (Misalignment) 检测

• 复位控制器 (RSTC)

– 上电复位和经过工厂标定的掉电检测

– 提供复位源信息以及给外部电路使用的复位信号

• 时钟发生器 (CKGR)

– 低耗 RC 振荡器, 3 到 20MHz 的片上振荡器和一个 PLL

• 电源管理控制器 (PMC)

– 可以通过软件进行电源优化,包括慢速时钟模式 ( 低至 500 Hz) 和空闲 (Idle) 模式

– 三个可编程的外部时钟信号

• 先进的中断控制器 (AIC)

– 可以单独屏蔽的、具有 8 个优先级的向量式中断源

– 两个外部中断源和一个快速中断源,可以防止虚假 (spurious) 中断

• 调试单元 (DBGU)

–2线 UART,支持调试通讯通道中断 ; 可通过程序来禁止通过 ICE 进行访问

• 周期性间隔定时器 (PIT)

–20位可编程的计数器,加上 12 位的间隔计数器

• 时间窗看门狗 (WDT)

–12位受预设值 (key)保护的可编程计数器

– 为系统提供复位或中断信号

– 当处理器处于调试状态或空闲模式时可以停止计数器

• 实时定时器 (RTT)

–32位自由运行的具有报警功能的计数器

– 时钟来源于片内 RC 振荡器

• 一个并行输入 / 输出控制器 (PIOA)

–32个可编程的复用 I/O,每个 I/O 最多可以支持两个外设功能

– 输入电平改变时,每个 I/O 都可以产生中断

– 可以独立编程为开漏输出、使能上拉电阻以及同步输出

• 11 个外设数据控制器 (PDC) 通道

• 一个 USB 2.0 全速 (12 Mbps) 设备端口

– 片上收发器, 328 字节可编程的 FIFO

• 一个同步串行控制器 (SSC)

– 每个接收器和发送器都具有独立的时钟和帧同步信号

– 支持 I²S,支持时分多址

– 支持 32 位数据传输的高速连续数据流功能

• 两个通用的同步 / 异步收发器 (USART)

– 独立的波特率发生器, IrDA 红外调制 / 解调

– 支持 ISO7816 T0/T1 智能卡,硬件握手信号,支持 RS485

–USART1支持全功能的调制解调器信号

• 主 / 从串行外设接口 (SPI)

–8到 16 位可编程的数据长度,4 个片选线

• 一个 3 通道的 16 位定时器 / 计数器 (TC)

–3个外部时钟输入端,每个通道有两个多功能 I/O 引脚

– 倍速 PWM 发生功能,捕捉 / 波形模式,递增 / 递减计数

®

ARM® Thumb® 处理器

AT91 ARM®

Thumb

®

微处理

器

AT91SAM7S64

初稿

本文是英文数据手册的中文翻

译,其目的是方便中国用户的阅

读。它无法自动跟随 原稿的更

新,同 时 也可能存在翻译上的错

误。读者应该以英文原稿为参考

以获得更准确的信息。

6070A–ATARM–07-Jun-05

• 一个 4 通道的 16 位 PWM 控制器 (PWMC)

• 一个两线接口 (TWI)

– 只支持主机模式,支持所有的 Atmel 两线 EEPROM

• 一个 8 通道的 10 位模数转换器,其中 4 个通道与数字 I/O 复用

• IEEE 1149.1 JTAG 边界扫描支持所有的数字引脚

• 5V 兼容的 I/O,包括 4 个高达 16 mA 的大电流驱动 I/O

• 电源

– 片上 1.8V 电压调节器,可以为内核及外部元件提供高达 100 mA 的电流

– 为 I/O 口线提供电源的 3.3V VDDIO,以及独立的为 Flash 供电的 3.3V VDDFLASH

– 内核电源为 1.8V VDDCORE,并具有掉电检测 (BoD) 功能

• 全静态操作:极限条件下 (1.65V, 85°C ) 高达 55 MHz

• 封装为 64 脚的 LQFP

描述 AT91SAM7S64是Atmel 32位 ARM RISC 处理器小引脚数Flash微处理器家族的一员。它

拥有 64K 字节的高速 Flash 和 16K 字节的 SRAM,丰富的外设资源,包括一个 USB 2.0

设备,使外部器件数目减至最低的完整系统功能集。这个芯片是那些正在寻求额外处理能

力和更大存储器的 8 位处理器用户的理想选择。

Flash 存储器可以通过 JTAG-ICE 进行编程,或者是在贴装之前利用编程器的并行接口进

行编程。锁定位可以防止固件不小心被改写,而安全锁定位则可以保护固件的安全。

AT91SAM7S64 的复位控制器可以管理芯片的上电顺序以及整个系统。BOD 和看门狗则

可以监控器件是否正确工作。

AT91SAM7S64 是一个通用处理器。它 集成了 USB 设备端口,使得它成为

的外设应用的理想芯片。极 具竞争力的性价比进一步拓展了它在低成本、大产量的消费类

产品中的应用。

连接 PC或手机

2

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

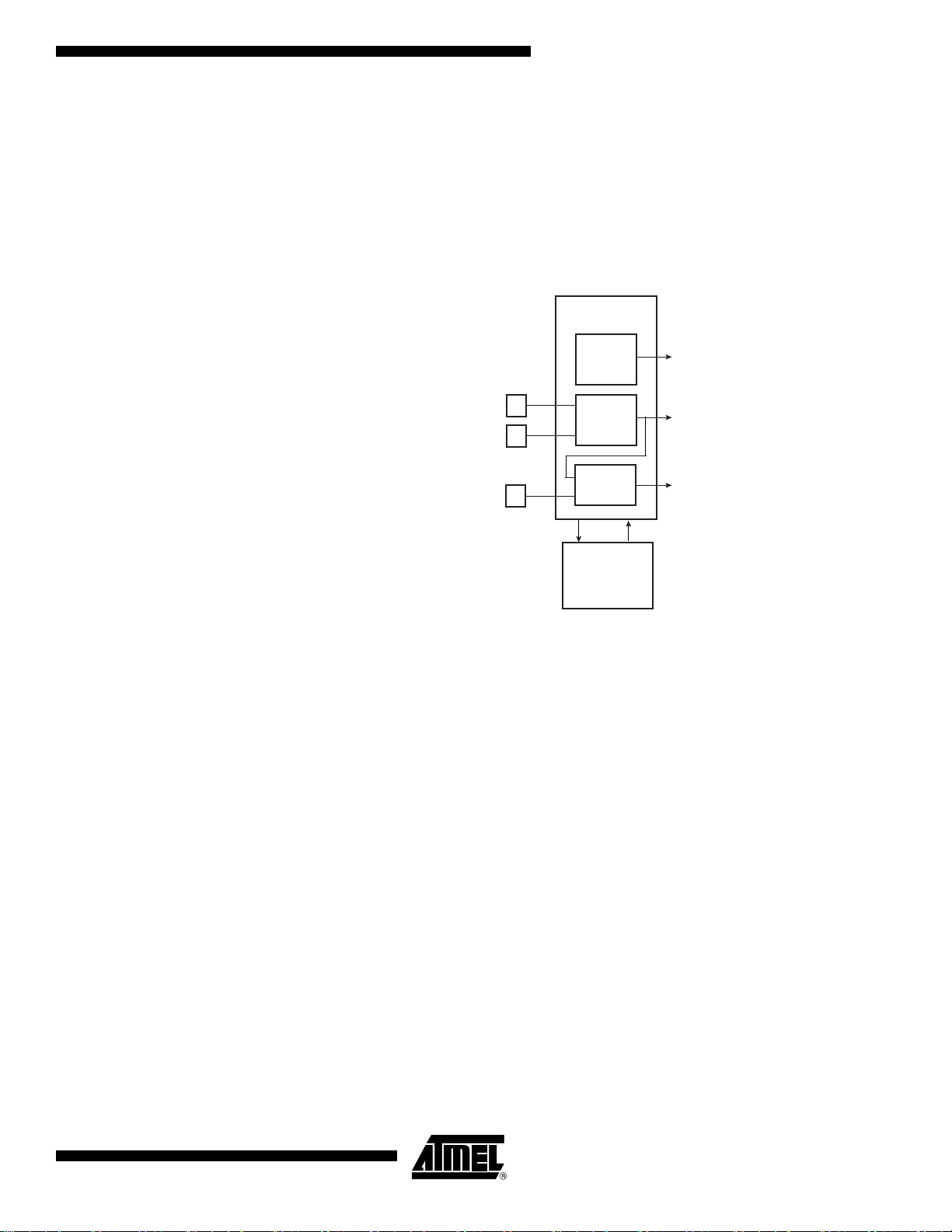

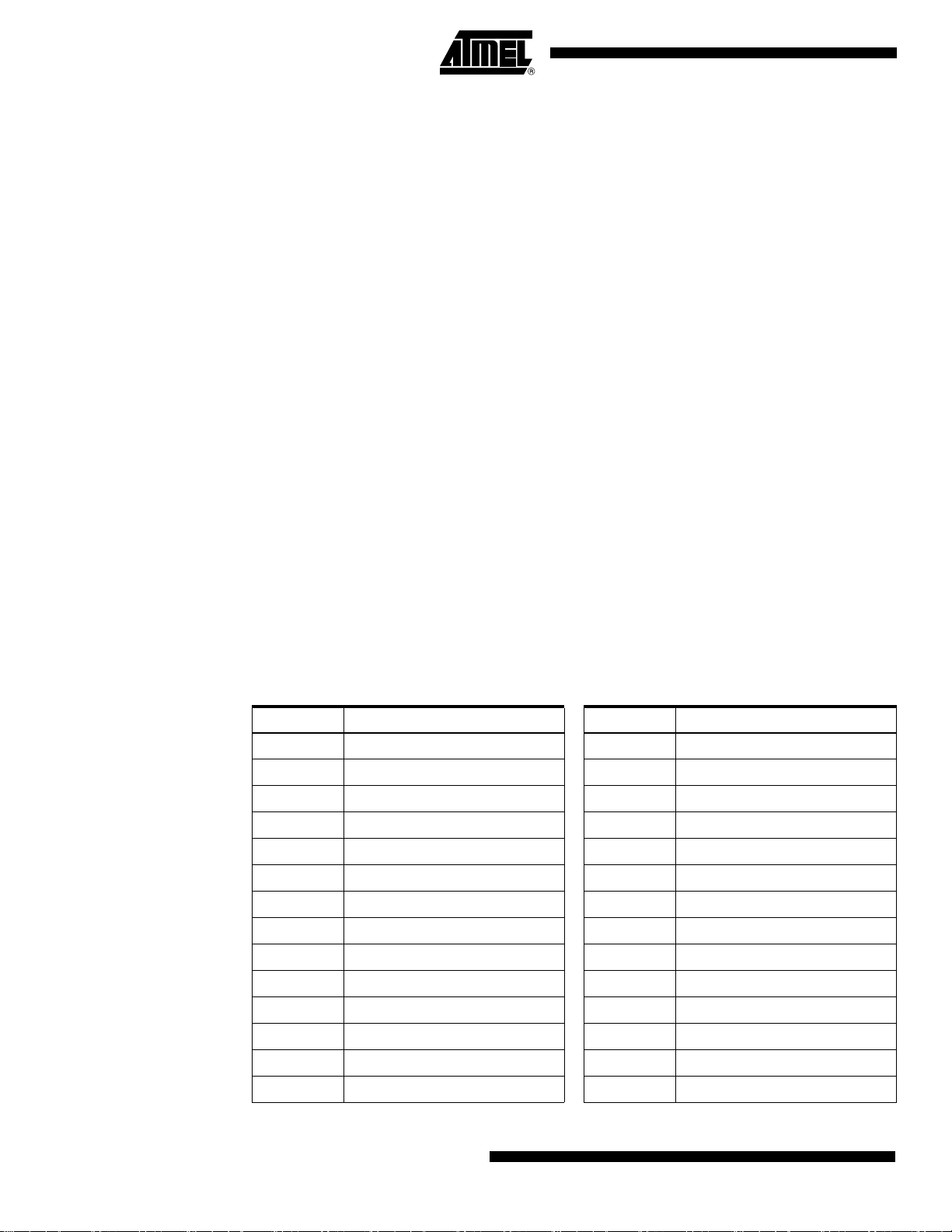

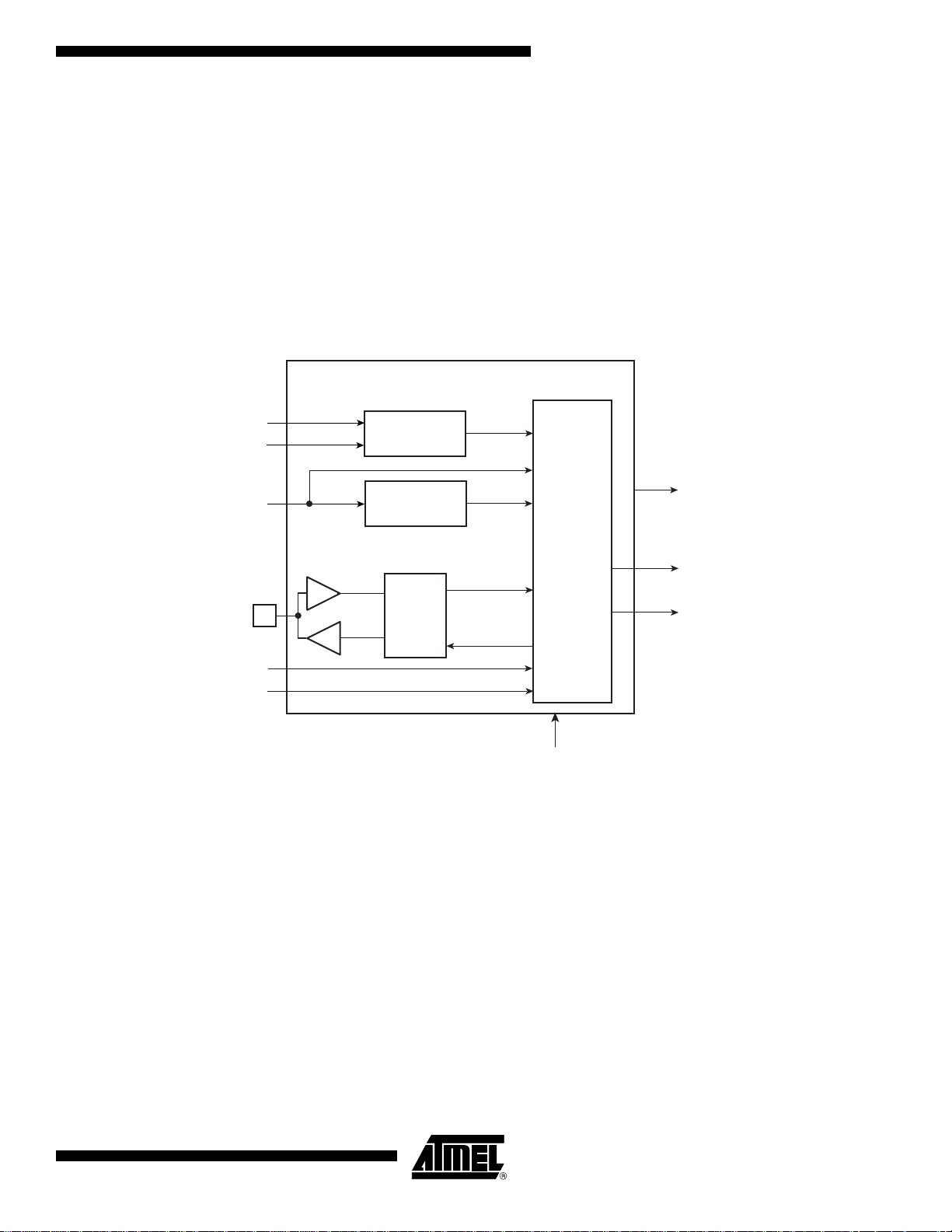

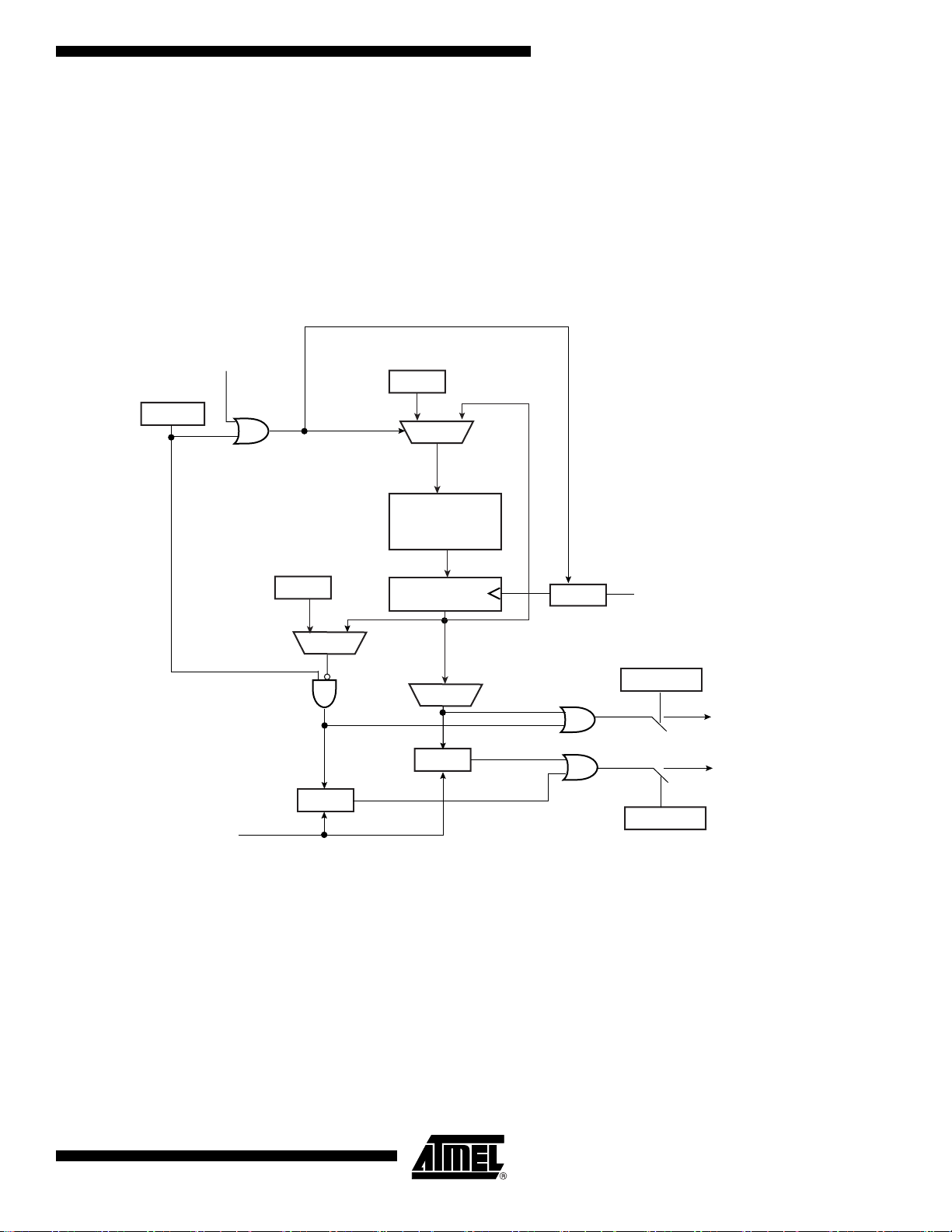

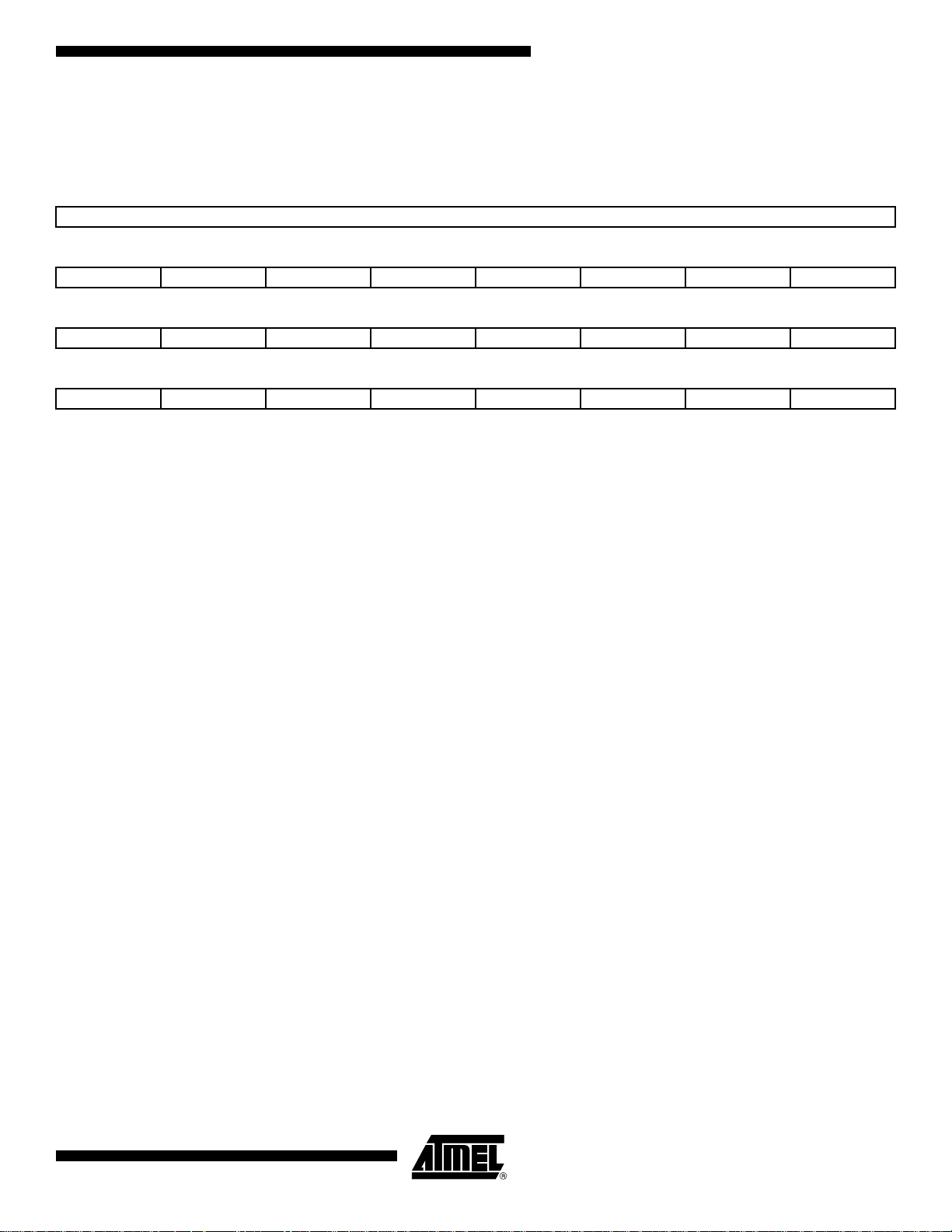

方框图

Figure 1. AT91SAM7S64 框图

TDI

TDO

TMS

TCK

JTAGSEL

TST

FIQ

IRQ0-IRQ1

PCK0-PCK2

PLLRC

XIN

XOUT

VDDCORE

VDDCORE

NRST

DRXD

DTXD

RXD0

TXD0

SCK0

RTS0

CTS0

RXD1

TXD1

SCK1

RTS1

CTS1

DCD1

DSR1

DTR1

RI1

NPCS0

NPCS1

NPCS2

NPCS3

MISO

MOSI

SPCK

ADTRG

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

ADVREF

System Controller

PIO

PLL

OSC

RCOSC

BOD

POR

PIO

PIO

JTAG

SCAN

Controller

DBGU

AIC

PMC

Reset

PIT

WDT

RTT

PIOA

PDC

PDC

ICE

USART0

USART1

SPI

ADC

ARM7TDMI

Processor

Memory Controller

Embedded

Flash

Controller

Abort

Status

Peripheral Bridge

Peripheral DMA

Controller

11 Channels

APB

PDC

PDC

PDC

PDC

PDC

PDC

PDC

Address

Decoder

Misalignment

Detection

FIFO

PDC

PDC

AT91SAM7S64 Preliminary

USB Device

PWMC

SSC

Timer Counter

TC0

TC1

TC2

TWI

1.8 V

Voltage

Regulator

SRAM

16 Kbytes

Flash

64 Kbytes

Fast Flash

Programming

Interface

Transceiver

PIO

VDDIN

GND

VDDOUT

VDDCORE

VDDIO

VDDFLASH

ERASE

PGMRDY

PGMNVALID

PGMNOE

PGMCK

PGMM0-PGMM3

PGMD0-PGMD15

PGMNCMD

PGMEN0-PGMEN2

DDM

DDP

PWM0

PWM1

PWM2

PWM3

TF

TK

TD

RD

RK

RF

TCLK0

TCLK1

TCLK2

TIOA0

TIOB0

TIOA1

TIOB1

TIOA2

TIOB2

TWD

TWCK

6070A–ATARM–07-Jun-05

3

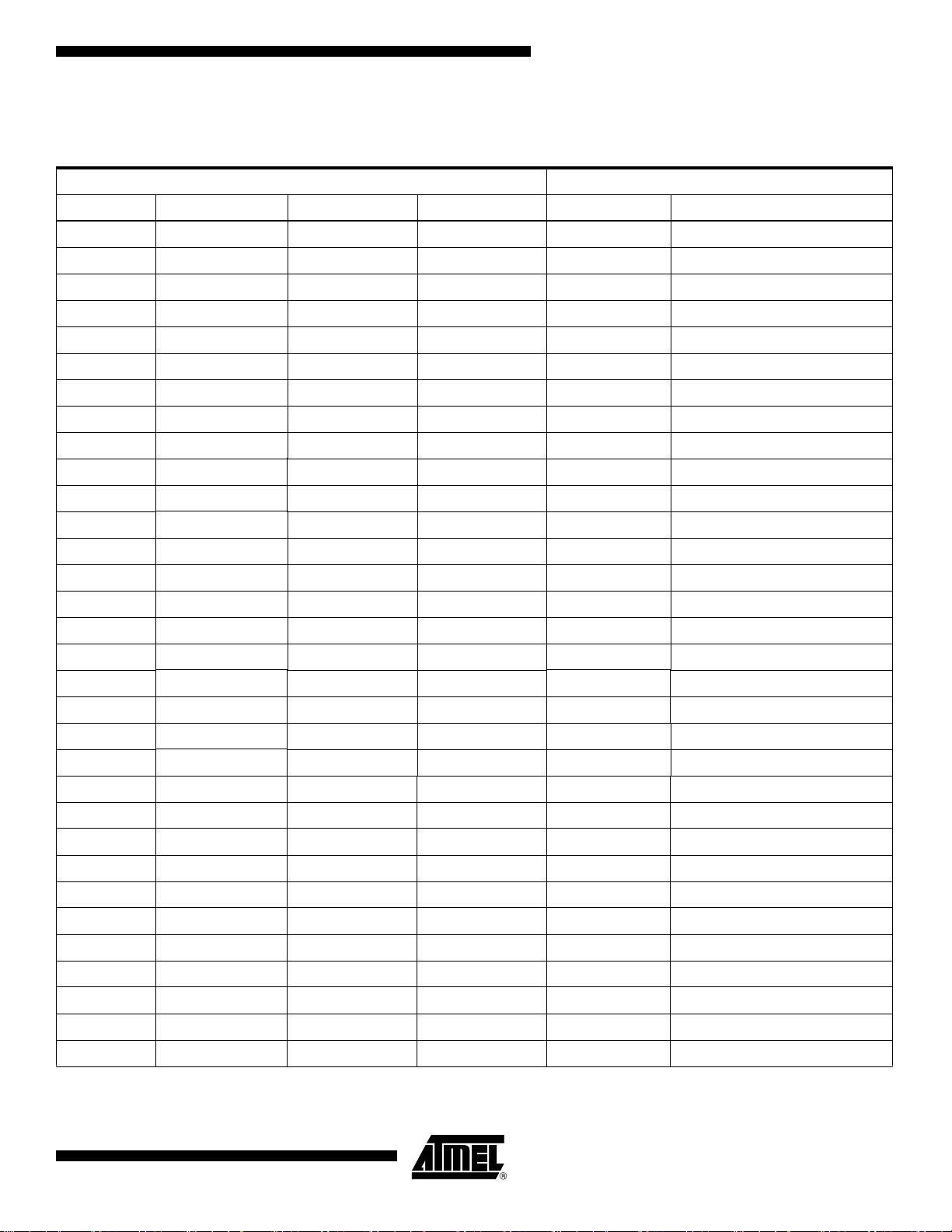

信号说明

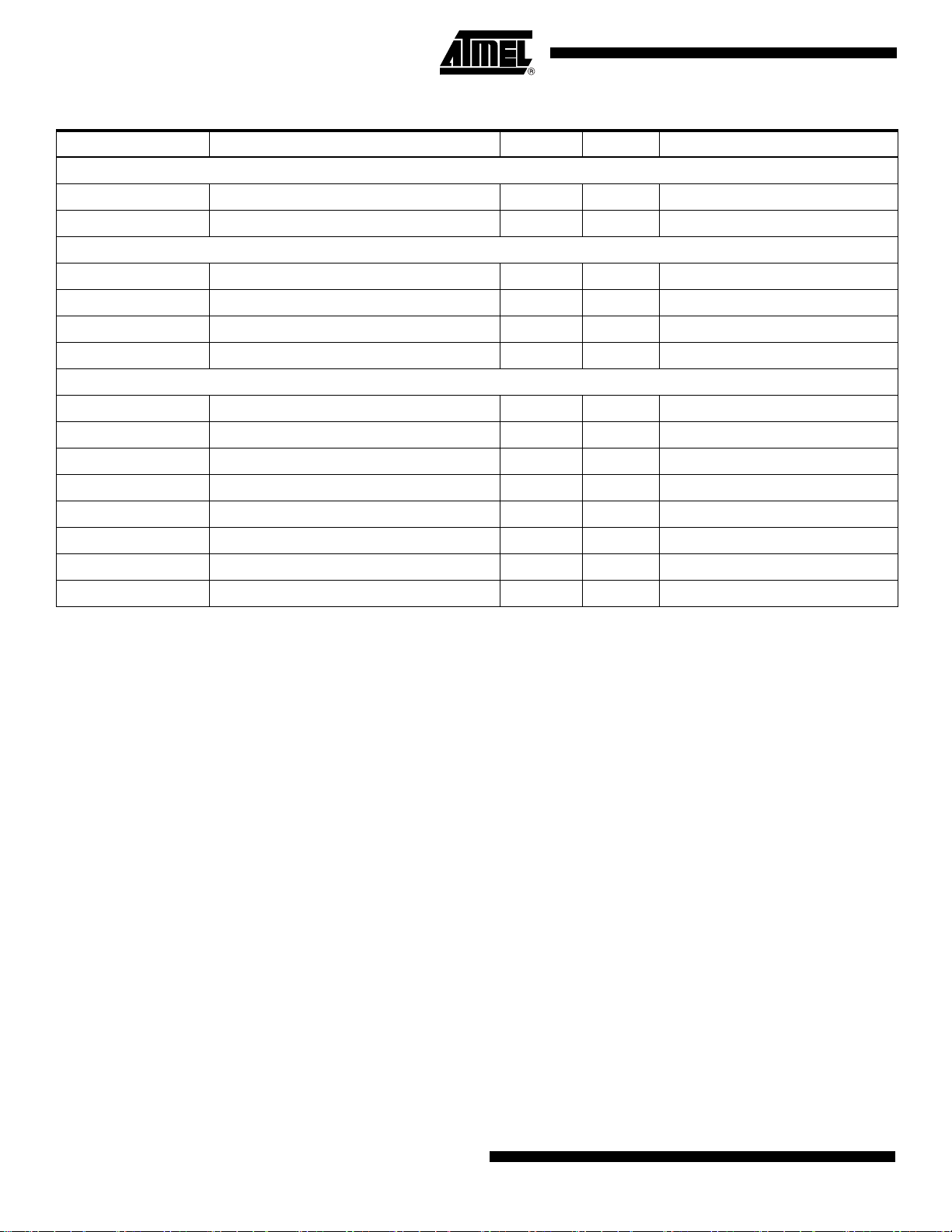

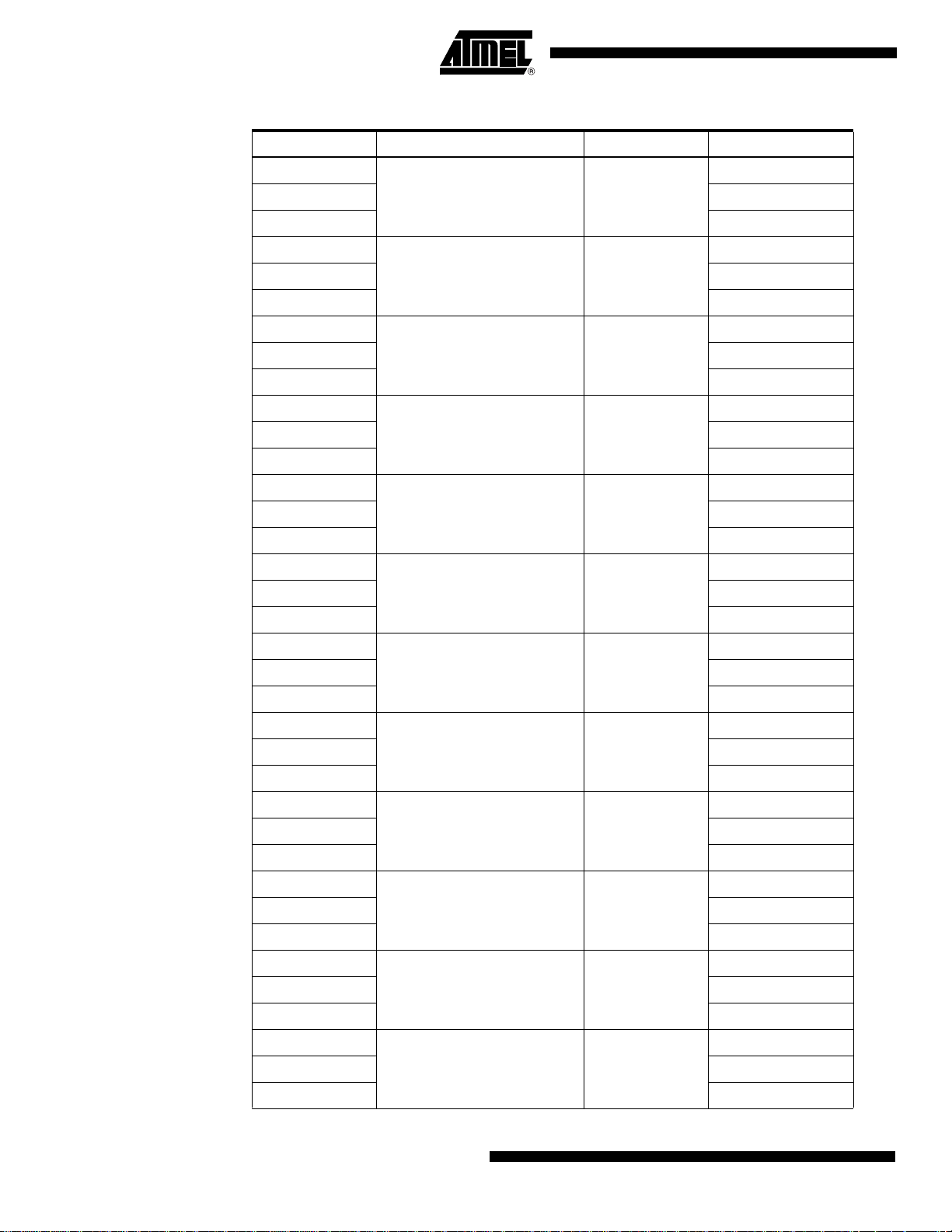

Table 1. 信号说明列表

信号名称 功能 类型 有效电平 说明

电源

VDDIN 电压调节器电源输入端 电源 3.0V - 3.6V

VDDOUT 电压调节器输出 电源 1.85V,标称值

VDDFLASH Flash 存储器的电源 电源 3.0V - 3.6V

VDDIO I/O 电源 电源 3.0V - 3.6V

VDDCORE 内核电源 电源 1.65V - 1.95V

VDDPLL PLL 电源 1.65V - 1.95V

GND 地地

时钟,振荡器和 PLL

XIN 主时钟振荡器输入 输入

XOUT 主时钟振荡器输出 输出

PLLRC PLL 滤波器输入

PCK0 - PCK2 可编程的时钟输出 输出

ICE 和 JTAG

TCK 测试时钟 输入 没有上拉电阻

TDI 测试数据输入 输入 没有上拉电阻

TDO 测试数据输出 输出

TMS 测试模式选择 输入 没有上拉电阻

JTAGSEL JTAG 选择 输入 下拉电阻

Flash 存储器

ERASE Flash 和 NVM 配置位擦除命令 输入 高电平 下拉电阻

复位 / 测试

NRST 处理器复位 I/O 低电平 上拉电阻

TST 测试模式选择 输入 下拉电阻

调试单元

DRXD 调试数据接收 输入

DTXD 调试数据发送 输出

AIC

IRQ0 - IRQ1 外部中断输入 输入

FIQ 快速中断输入 输入

4

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

Table 1. 信号说明列表

信号名称 功能 类型 有效电平 说明

PIO

PA0 - PA31 并行 IO 控制器 AI/O复位时为带上拉电阻的输入端

USB Device Port

DDM USB 设备端口数据 - 模拟

DDP USB 设备端口数据 + 模拟

USART

SCK0 - SCK1 串行时钟 I/O

TXD0 - TXD1 发送数据 I/O

RXD0 - RXD1 接收数据 输入

RTS0 - RTS1 请求发送 输出

CTS0 - CTS1 清零后发送 输入

DCD1 数据载波检测 输入

DTR1 数据终端准备好 输出

DSR1 数据设备准备好 输入

RI1 振铃指示 输入

同步串行控制器

TD 发送数据 输出

RD 接收数据 输入

TK 发送时钟 I/O

RK 接收时钟 I/O

TF 发送帧同步 I/O

RF 接收帧同步 I/O

定时器 / 计数器

TCLK0 - TCLK2 外部时钟输入 输入

TIOA0 - TIOA2 I/O 口线 AI/O

TIOB0 - TIOB2 I/O 口线 BI/O

PWM 控制器

PWM0 - PWM3 PWM 通道 输出

SPI

MISO 主机输入,从机输出 I/O

MOSI 主机输出,

从机输入 I/O

SPCK SPI 串行时钟 I/O

NPCS0 SPI 外设片选 0I/O低电平

NPCS1-NPCS3 SPI 外设片选 1 到 3 输出 低电平

6070A–ATARM–07-Jun-05

5

Table 1. 信号说明列表

信号名称 功能 类型 有效电平 说明

两线接口

TWD 串行数据 I/O

TWCK 串行时钟 I/O

模数转换器

AD0-AD3 模拟输入 模拟 复位时为带上拉电阻的数字输入端口

AD4-AD7 模拟输入 模拟 模拟输入

ADTRG ADC 触发输入

ADVREF ADC 参考电压 模拟

快速 Flash 编程接口

PGMEN0-PGMEN1 编程使能 输入

PGMM0-PGMM3 编程模式 输入

PGMD0-PGMD15 编程的数据 I/O

PGMRDY 编程结束 输出 高电平

PGMNVALID 数据方向 输出 低电平

PGMNOE 编程过程中读数据 输入 低电平

PGMCK 编程时钟 输入

PGMNCMD 编程命令 输入 低电平

6

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

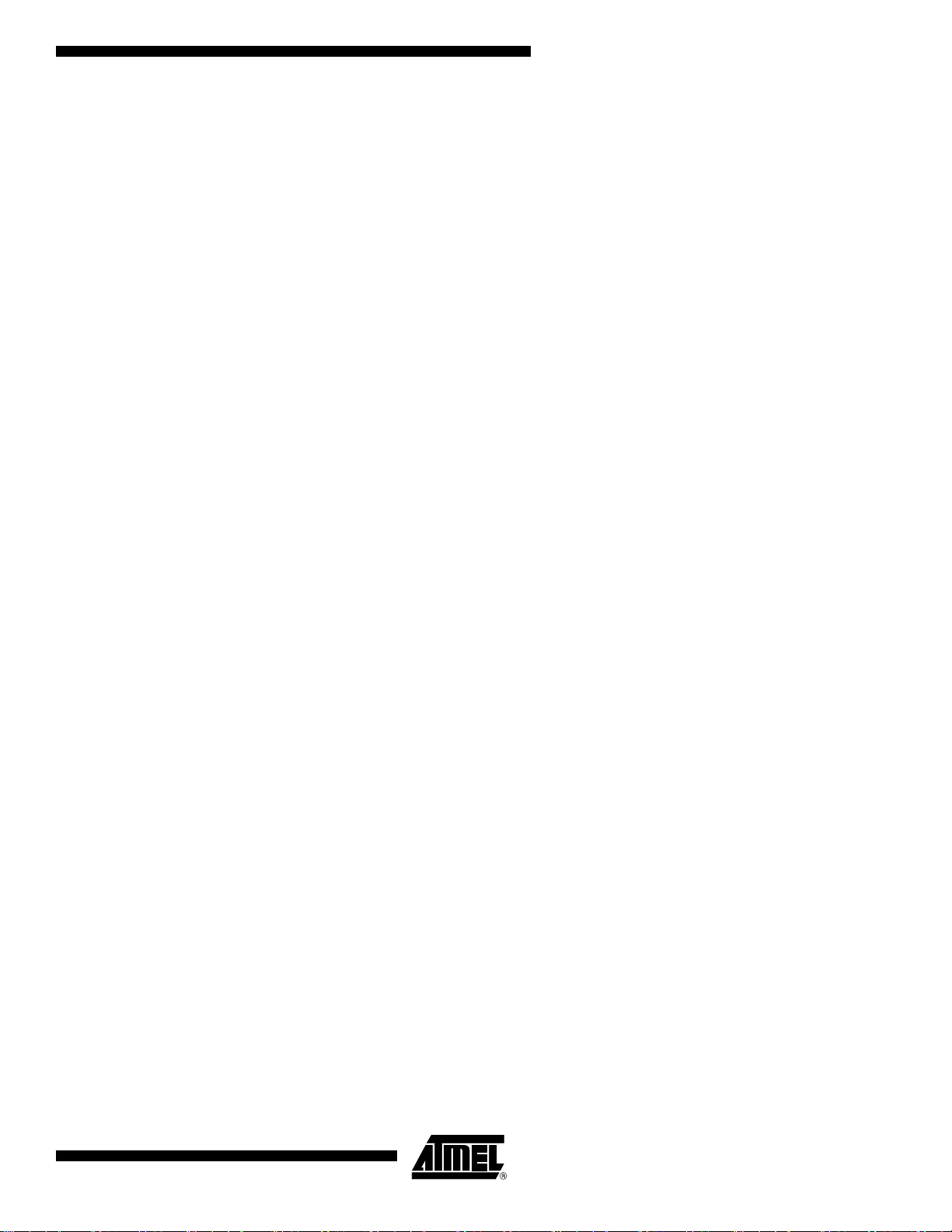

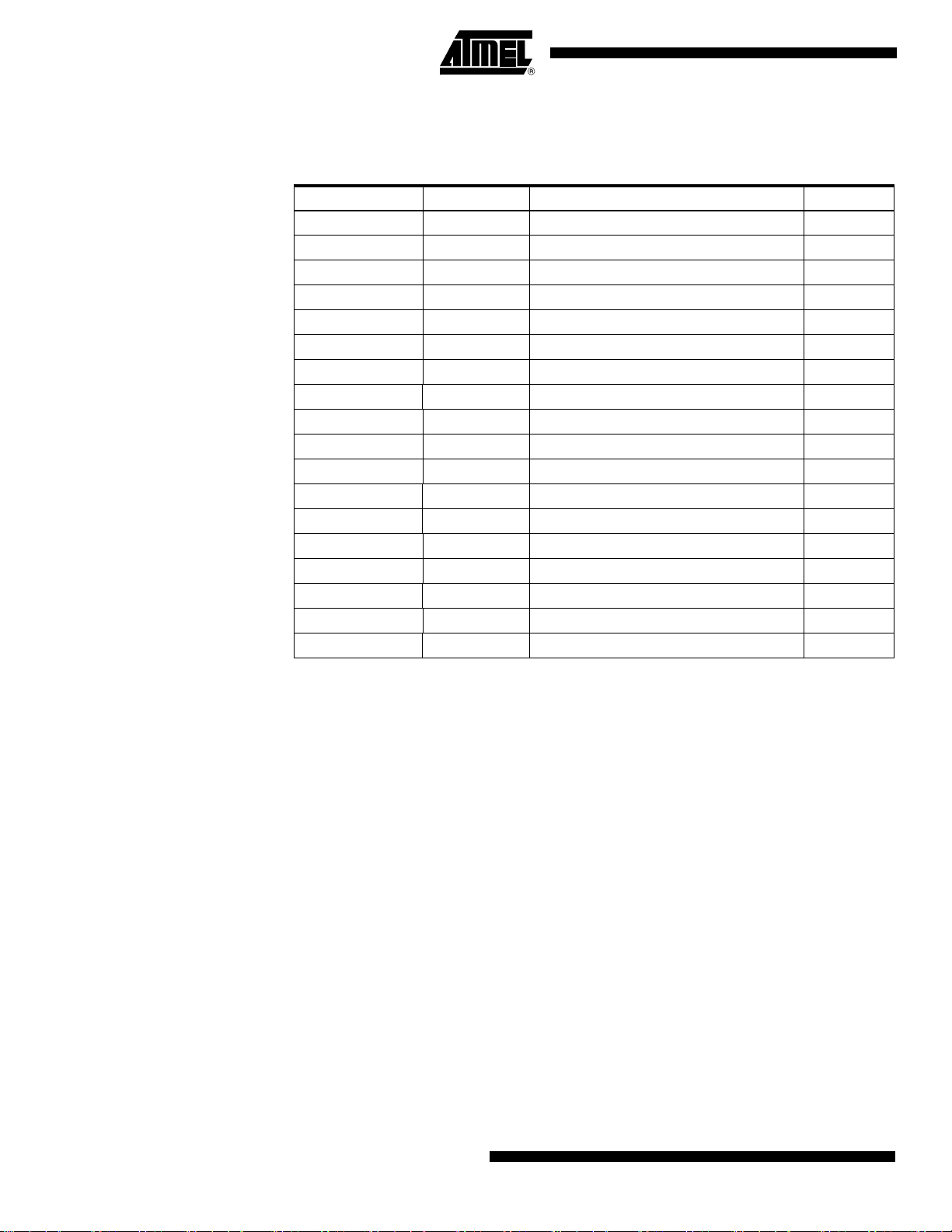

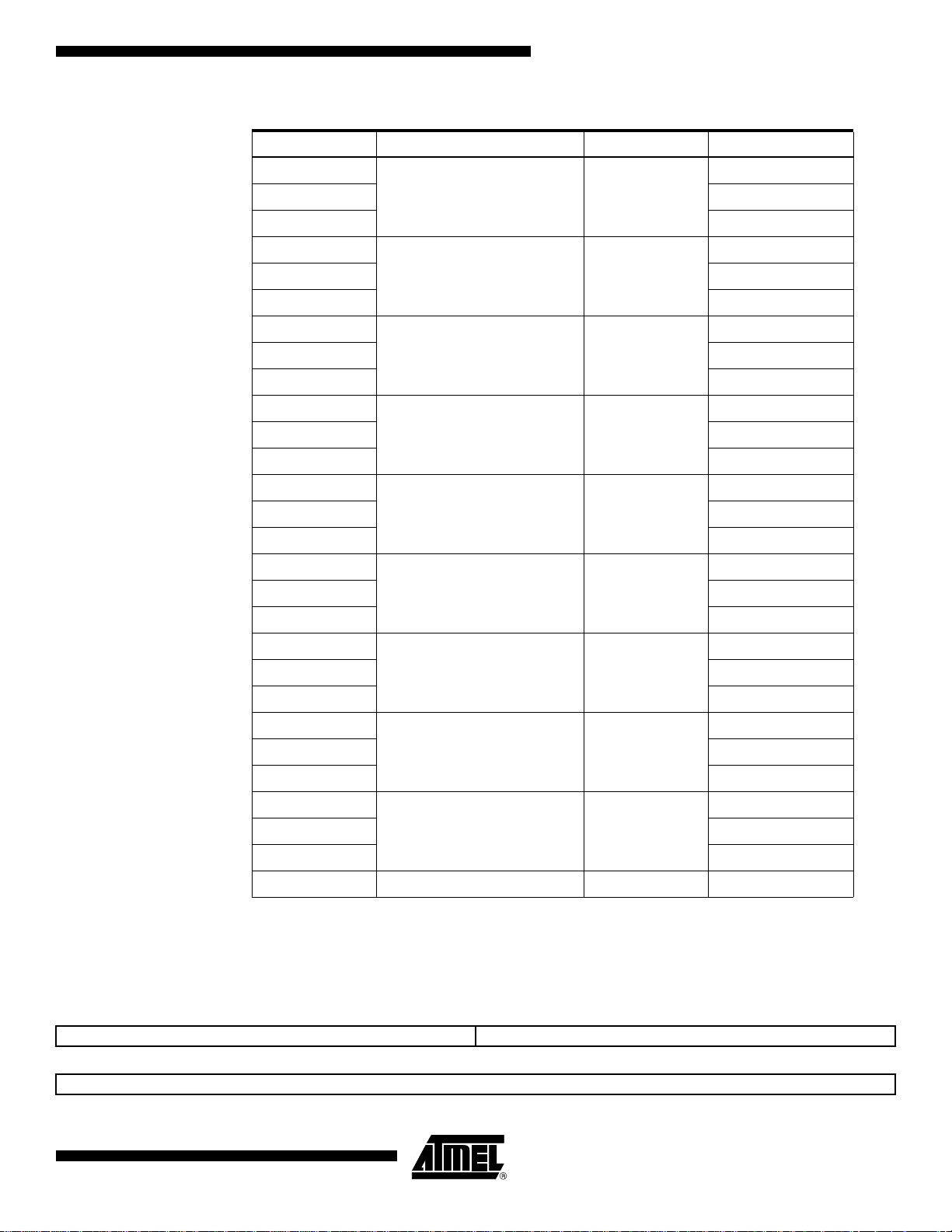

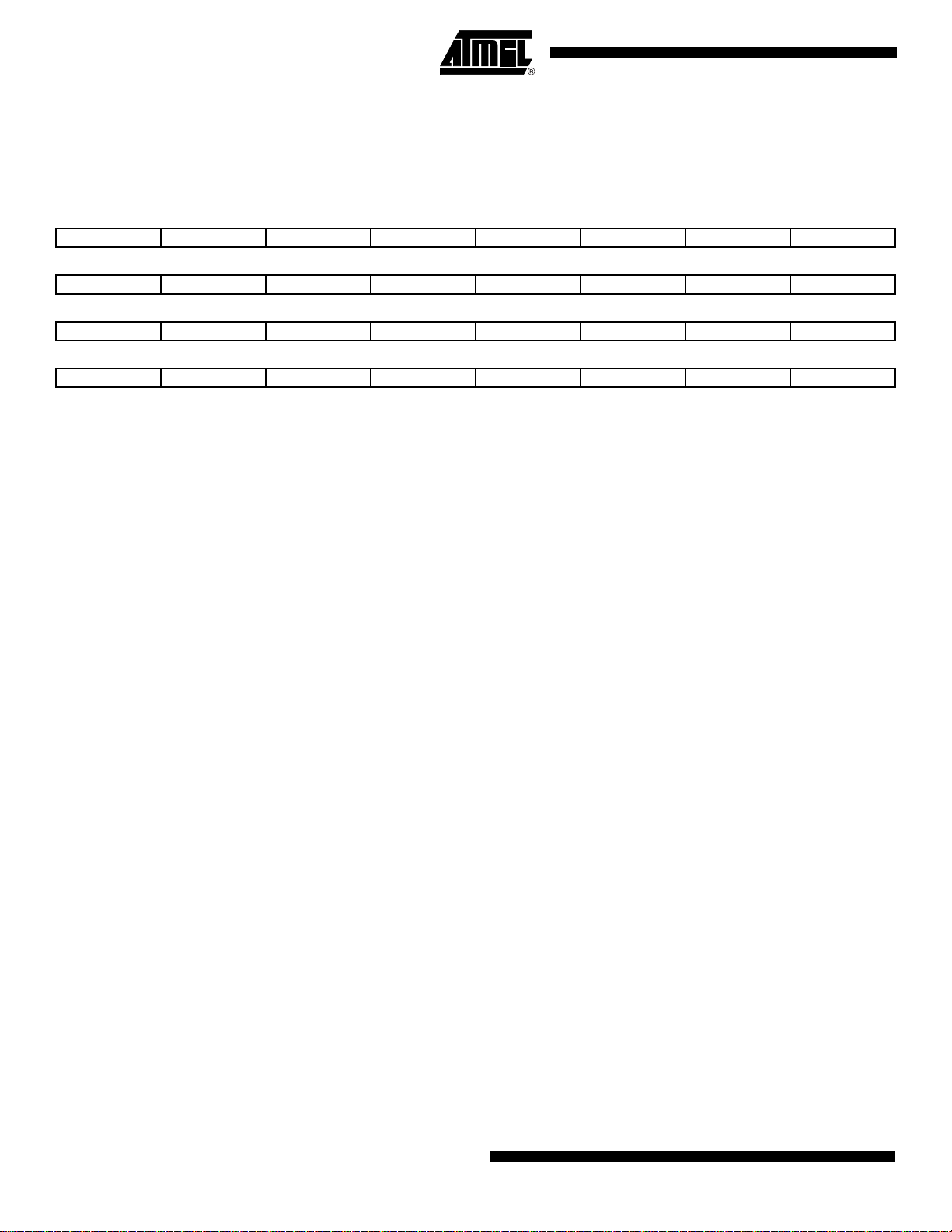

封装和引脚排列 AT91SAM7S64 的封装为 64 脚的 LQFP。

64脚LQFP封装的机械形状 Figure 2 给出了 64 脚 LQFP 封装的定位。具体的机械尺寸在机械特性一节有详细说明。

Figure 2. 64 脚 LQFP 封装引脚 ( 顶视图 )

48

49

64

1

33

32

17

16

引脚排列

Table 2. AT91SAM7S64 引脚排列 (64 脚 LQFP 封装)

1 ADVREF 17 GND 33 TDI 49 TDO

2 GND 18 VDDIO 34 PA6/PGMNOE 50 JTAGSEL

3 AD4 19 PA16/PGMD4 35 PA5/PGMRDY 51 TMS

4 AD5 20 PA15/PGM3 36 PA4/PGMNCMD 52 PA31

5 AD6 21 PA14/PGMD2 37 PA27/PGMD15 53 TCK

6 AD7 22 PA13/PGMD1 38 PA28 54 VDDCORE

7 VDDIN 23 PA24/PGMD12 39 NRST 55 ERASE

8 VDDOUT 24 VDDCORE 40 TST 56 DDM

9 PA17/PGMD5/AD0 25 PA25/PGMD13 41 PA29 57 DDP

10 PA18/PGMD6/AD1 26 PA26/PGMD14 42 PA30 58 VDDIO

11 PA21/PGMD9 27 PA12/PGMD0 43 PA3 59 VDDFLASH

12 VDDCORE 28 PA11/PGMM3 44 PA2 60 GND

13 PA19/PGMD7/AD2 29 PA10/PGMM2 45 VDDIO 61 XOUT

14 PA22/PGMD10 30 PA9/PGMM1 46 GND 62 XIN/PGMCK

15 PA23/PGMD11 31 PA8/PGMM0 47 PA1/PGMEN1 63 PLLRC

16 PA20/PGMD8/AD3 32 PA7/PGMNVALID 48 PA0/PGMEN0 64 VDDPLL

6070A–ATARM–07-Jun-05

7

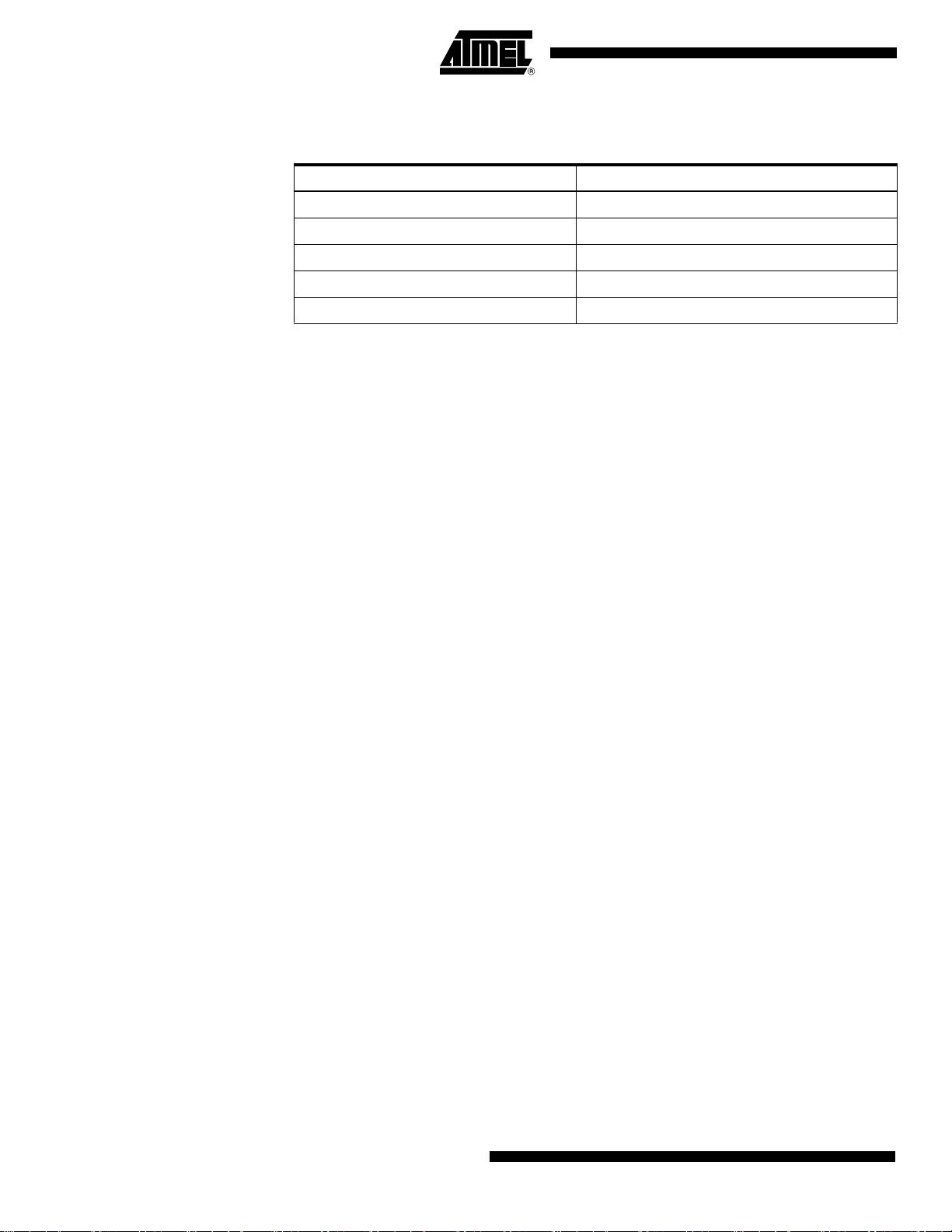

电源的考虑

电源 AT91SAM7S64 有 6 种类型的电源输入引脚以及一个集成的电源调节器,使得器件可以工

作于单一电压。这 6 种电源引脚类型为:

•VDDIN:电压调节器的电源输入。输入电压范围是 3.0V 到 3.6V,标称值为 3.3V。如

果不用电压调节器,则 VDDIN 应该连接到 GND。

•VDDOUT:电压调节器的输出, 1.8V。

•VDDIO:I/O 及 USB 的电源。支持电压范围为 3.0V 到 3.6V,标称值为 3.3V。

• VDDFLASH:为 Flash 部分地提供电源,而且是 Flash 正确工作的先决条件。电压范

围为 3.0V 到 3.6V,标称值为 3.3V。

• VDDCORE:芯片逻辑部分的电源。电

以通过解耦电容连接到 VDDOUT 引脚。 VDDCORE 是器件内核,包括 Flash 正确

工作的前提。

•VDDPLL: 振荡器和 PLL 的电源。可以直接连接到 VDDOUT。

各个输入电源并没有独立的地回路引脚。因此 GND 与系统地平面的连接应尽可能短。

功耗 在 25°C 时,VDDCORE 的静态电流小于 60 µA,包括 RC 振荡器、电压调节器和上电复

位。使能掉电复位 BOD 将额外增加 20 µA 的静态电流。

全速工作且运行不基于 Flash 时 VDDCORE 的动态功耗 小于 50 mA。若 程序在 Flash 上

运行则 VDDFLASH 的电流不超过 10 mA。

压范围从 1.65V 到 1.95V,典型值为 1.8V。可

电压调节器 AT91SAM7S64 有一个由系统控制器管理的电压调节器。

在正常模式下,电压调节器消耗的静态电流还不到 100 µA,而输出电流则高达 100 mA。

电压调节器支持低功耗模式。在此模式下它只消耗不到 20 µA 的静态电流,输出电流可达

1 mA。

VDDOUT 必须有足够的解耦电容以减少纹波和防止振荡。最好的方法是并联两个电容于

VDDOUT和 GND 之间:一个 470 pF (或1 nF) NPO材质的电容,尽量靠近芯片;另一个是

2.2 µF ( 或 3.3 µF) X7R 材质的电容。

VDDIN 也需要足够的解耦

芯片。例如可以将两个电容并联在一起:100 nF 的 NPO 电容和 4.7 µF 的 X7R 电容。

来提高启动稳定性以及减少电压降。输入电容也需要尽量靠近

典型的电源连接图

3.3V 单电源 AT91SAM7S64 支持 3.3V 单电源模式。片内电压调节器连接到 3.3V,输出则连接到

VDDCORE 和 VDDPLL。 Figure 3 给出了通过 USB 总线供电的线路图。

8

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

Figure 3. 3.3V 单电源供电系统

AT91SAM7S64 Preliminary

VDDFLASH

Power Source

ranges

from 4.5V (USB)

to 18V

DC/DC Converter

3.3V

VDDIO

VDDIN

Voltage

Regulator

VDDOUT

VDDCORE

VDDPLL

6070A–ATARM–07-Jun-05

9

I/O 的考虑

JTAG 引脚 TMS、TDI和 TCK 都是施密特触发器型的输入引脚。TMS和TCK与 5V兼容,TDI 则不是。

TMS、 TDI 和 TCK 都没有上拉电阻。

TDO 为输出引脚,输出电平可达 VDDIO,没有上拉电阻。

引脚 JTAGSEL 拉高时选择 JTAG 边界扫描功能。此引脚集成了阻值约为 15 k Ω 的片内

下拉电阻,所以在正常工作模式下可以悬空。

测试引脚 TST用于生产测试,或是拉高以进入快速编程模式。TST集成了阻值约为 15 kΩ 的片内下

拉电阻,所以在正常工作模式下可以悬空。

为了使能快速编程模式,引脚 TST 和 PA0、 PA1 都需要拉高。

TST 为高时,若 PA0 或 PA1 为 0 将导致不可预测的结果。

复位引脚 NRST 是双向引脚。它可以被片内的复位控制器拉低,从而为外部器件产生复位信号;也

可以被外部电路拉低以复位处理器。复位脉冲没有持续时间的限制,复位控制器可以保证

产生最小长度的脉冲。从而可以在引脚 NRST 上简单地连接一个摁键开关作为用户的系

统复位控制,同时也可以利用 NRST 信号来复位系统的其他原器件。

NRST 引脚有一个上拉电阻连接到 VDDIO。

ERASE 引脚 引脚 ERASE 用于 Flash 及其一些 NVM 位的擦除。引脚具有阻值约为 15 k Ω 的下拉电

阻,所以在正常工作模式下可以悬空。

PIO 控制器 A 端口 I/O口线PA0-PA31与5V兼容,且每个I/O都具有可编程的上拉电阻。通过PIO 控制器可以

对每一个 I/O 的上拉电阻进行单独控制。

与 5V 兼容意味着 I/O 可以输出 VDDIO 的电平,而输入则可以高达 5.5V。但此时不能使

能 I/O 的上拉电阻,否则将导致不可预测的结果。特别是在复位时一定要注意,因为在复

位阶段所有的 I/O 都缺省为带上拉电阻的输入引脚。

I/O 驱动电平 PA0-PA3 可以输出大电流。每个 I/O 都可以驱动高达 16 mA 的电流。

其余的 I/O 只能输出 8 mA 的电流。

要注意的是,所有 I/O 输出的电流之和不能超过 150 mA。

10

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

处理器和结构

ARM7TDMI 处理器 • 基于 ARMv4T 冯 - 诺依曼结构的 RISC 处理器

– 运行速度可达 55 MHz, 0.9 MIPS/MHz 的性能

• 两个指令集

–ARM

–Thumb

•3级流水线结构

– 指令获取 (F)

– 指令解码 (D)

– 执行 (E)

调试和测试特点 • 集成的片上仿真器

– 两个观察点 (watchpoint) 单元

– 通过 JTAG 协议访问测试访问端口 TA P

– 调试通讯通道

• 调试单元

– 两线 UART

– 可以处理调试通讯通道中断

– 芯片 ID 寄存器

• IEEE1149.1 JTAG 边界扫描支持所有的数字引脚

®

高性能 32 位指令集

®

高代码密度 16 位指令集

存储器控制器 • 总线仲裁

– 处理来自 ARM7TDMI 和外设数据控制器的请求

• 地址译码器可以提供如下片选信号

–3个 1M 字节的片内存储区

– 一个 256M 字节的片内外设区

• 仲裁状态寄存器

– 保存了引发仲裁的来源、类型以及其他所有参数

– 通过检测被破坏的指针以方便调试

• 对齐 (alignment) 检测

– 访问数据时的对齐检查

– 发生未对齐情况时产生异常中断

• 重映射 (Remap) 命令

– 将 SRAM 映射到片内非易失性存储器 (NVM) 的位置

– 允许例外向量的动态处理

• 嵌入式 Flash 控制器

– 嵌入式 Flash 接口,最多可有 3 个可编程的等待

– 预取缓冲器,用于缓冲及预留 16 位请求,从而减少等待周期

– 受预设值保护的编程、擦除和锁定 / 解锁定序器

– 存储器擦除、编程和锁定操作都只需要一个命令

– 执行被禁止的操作将引发中断

周期

6070A–ATARM–07-Jun-05

11

外设数据控制器 • 处理外设与存储器之间的数据传输

•11个通道

– 每个 USART 有两个

– 调试单元有一个

– 串行同步控制器 (SSC) 有两个

– SPI 有两个

– 模数转换器有一个

• 低的总线仲裁开销

– 从存储器到外设的传输只需要一个主时钟周期

– 从外设到存储器的传输只需要两个主时钟周期

• “ 下一个指针” 管理减少了中断时间

12

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

存储器 •64K字节 Flash

–512页,每页 128 字节

– 快速的访问时间,在最坏的条件下访问周期可达到 30 MHz

– 页编程时间:4 ms,包括页自动擦除时间

– 没有自动擦除操作的页编程时间:2 ms

– 全片擦除时间:10 ms

– 10,000 次写寿命, 10 年数据保存时间

–16个锁定位,每个保护一个扇区 ( 每个扇区包含 32 页 )

– 保护 Flash 内容安全的保护模式

•16K字节的快速 SRAM

– 在全速工作时仍然可以单时钟进行访问

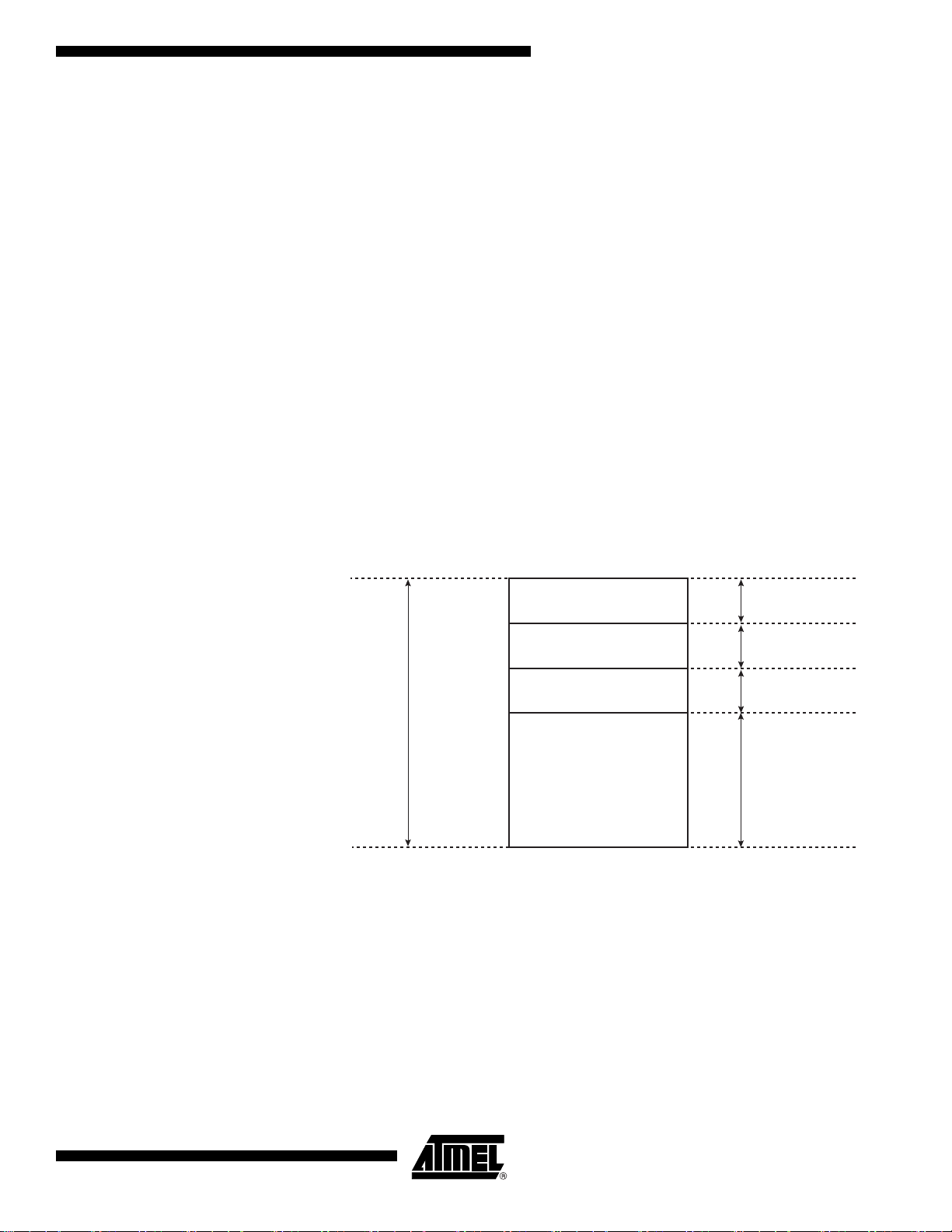

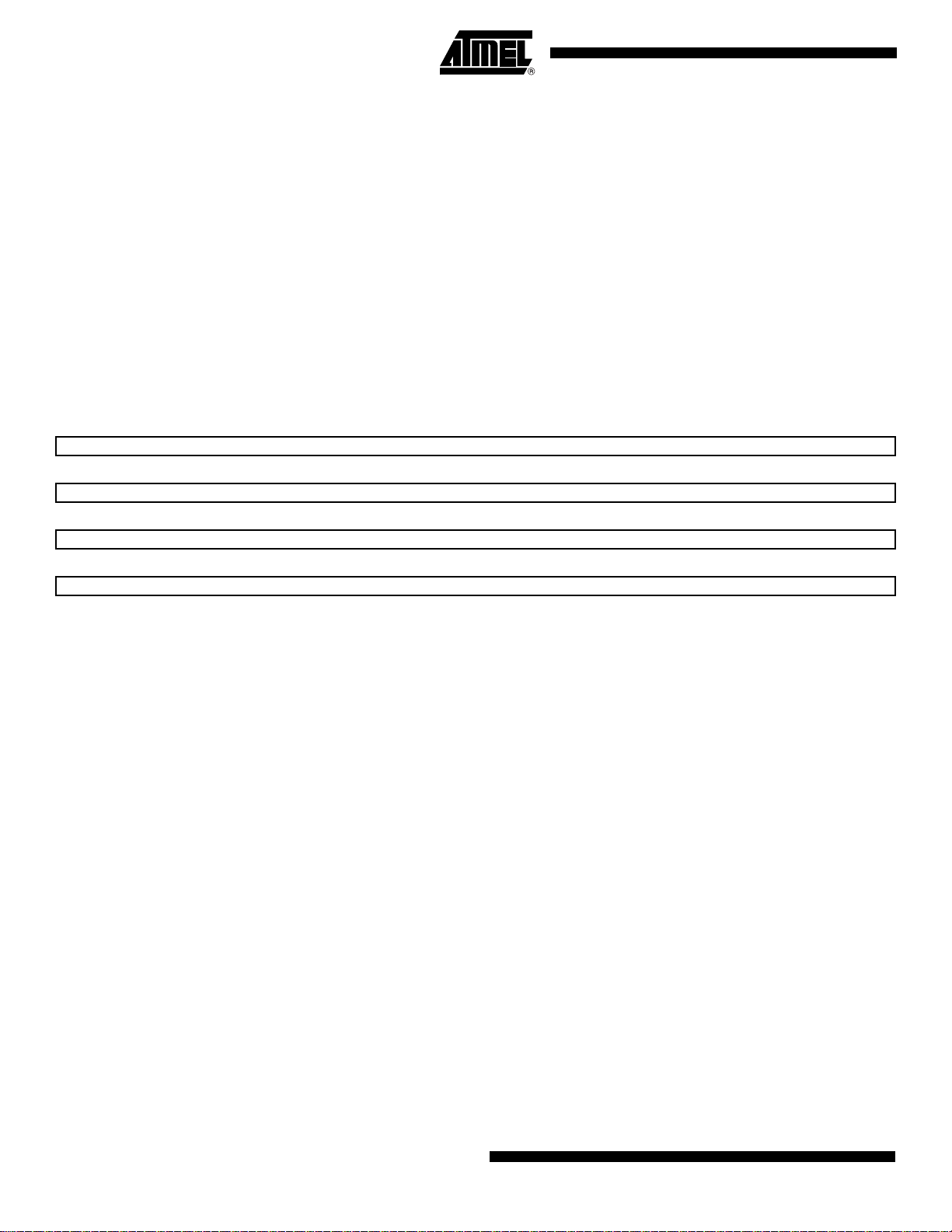

存储器映射

片内 SRAM AT91SAM7S64有16K字节的高速SRAM。芯 片复位后,直到执行 Remap 命令,SRAM 的

访问地址为 0x0020 0000。重映射之后, SRAM 的访问地址变为 0x0。

片内 Flash AT91SAM7S64有64K字节的Flash。在任何时候它的访问地址都是 0x0010 0000。此 外,

在芯片复位之后, Remap 之前,也可以从 0x0 进行访问。

Figure 4. 片内存储器映射

0x0000 0000

0x000F FFFF

0x0010 0000

0x001F FFFF

0x0020 0000

256M Bytes

0x002F FFFF

0x0030 0000

0x0FFF FFFF

Flash Before Remap

SRAM After Remap

Internal Flash

Internal SRAM

Undefined Areas

(Abort)

1 M Bytes

1 M Bytes

1 M Bytes

253 M Bytes

6070A–ATARM–07-Jun-05

13

片内 Flash

Flash 概览 AT91SAM7S64的Flash组织为512页,每页128字节。全部65,536字节以32位字的方式组

织在一起。

Flash 包含了一个 128 字节的写缓冲区,可以 32 位的接口进行访问。

片内复位单元和低电压检测器 BOD可以帮助 Flash 在电压变化时防止代码毁坏,即使在

最坏的情况之下。

片内 Flash 控制器 片内 ( 嵌入式 )Flash 控制器 (EFC) 管理系统各个主机执行的存储器访问。它 控制对 Flash

的读访问以及对写缓冲区的写访问。它还包括了一个用户接口,映射到 APB 的存储器控

制器。用户接口允许:

• 编程 Flash 的访问参数 ( 等待周期的个数,时序,等等 )

• 启动诸如全片擦除、页擦除、页写、 NVM 位设置 / 清除等命令

• 获取上一个命令的结束状态

• 获取错误状态

• 上一个命令结束或发生错误时产生中断

片内 Flash 控制器还提供双 32 位预取缓冲器以优化对 Flash 存储器的 16 位访问。这 对运

行于 Thumb 模式的处理器特别有效。

锁定区域 EFC管理着16个锁定位以保护 flash的16个区,防止这些区域被意外地擦除或编程。 每个

锁定区域包含 32 页,共 4K 字节。

如果对已经被锁住的区域进行擦除或编程,这些命令将终止,同时 EFC 激发一个中断。

通过 EFC

作; “ 清除锁定位” 命令解除锁定区域的锁定状态。

将 ERASE 拉高将清除所有的锁定位,从而将全部的 Flash 解锁。

安全位的特点 AT91SAM7S64 有一个安全位。它 是 一个特殊的 NVM位。当安全位使能时,对 Flash 的所

有访问,包括通过 ICE 接口或快速Flash编程接口,都被禁止。从 而 保护了 Flash 的内容。

这个安全位只能通过 EFC 用户接口的 “ 设置安全位” 命令来使能。而禁止安全位只能通

过将 ERASE 引脚拉高,将整个 flash 全部擦除。在安全位为禁止状态的情况下,对 flash

的所有操作都可以进行。

很重要的一点是,拉高 ERASE 引脚的时间必须大于 50 ms。

由于 ERASE 集成了下拉电阻,在正常工作模式下这个引脚可以悬空。不 过将它直接连接

到 GND 也是安全的。

非易失性掉电检测控制 掉电检测 (BOD) 由两个通用的 NVM (GPNVM) 位控制。因此即使没有了电源,掉电检测

仍然可以保持用户的定义。

两个 GPNVM 位的清除和设置分别通过 EFC 用户接口的 “ 清除通用 NVM 位” 命令和

“ 设置通用 NVM 位” 命令来实现。

• GPNVM 位 0 用于控制掉电检测的使能。设置 GPNVM0 将使能 BOD,清除它

• GPNVM 位 1 控制掉电检测信号是否可以用于系统复位。置位 GPNVM1 使能这个功

用户接口可以对 16 个 NVM 位实行软件编程。“ 设置锁定位” 命令启 动保护操

即禁止

BOD。拉高 ERASE 将清除 GPNVM0,从而禁止 BOD。

能,清零 GPNVM1 则禁止掉电检测信号复位整个芯片。拉高 ERASE 将禁止掉电检

测复位。

标定位 8 个NVM位用于标定掉电检测器及电压调节器。这 些 位的配置在出厂之前完成,用户不能

进行修改。 ERASE 引脚的状态对标定位没有影响。

14

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

快速 Flash 编程接口 FFPI 快速 Flash 编程接口允许用户通过串行 JTAG 接口或实现了握手信号的并行口对 Flash 进

行快速编程。这样就可以通过符合市场标准的工业编程器进行批量编程。

FFPI 支持读、页编程、页擦除、全片擦除、锁定、解锁和保护命令。

拉高引脚 TST、 PA0 和 PA1 即使能 FFPI,并使芯片进入快速编程模式。

6070A–ATARM–07-Jun-05

15

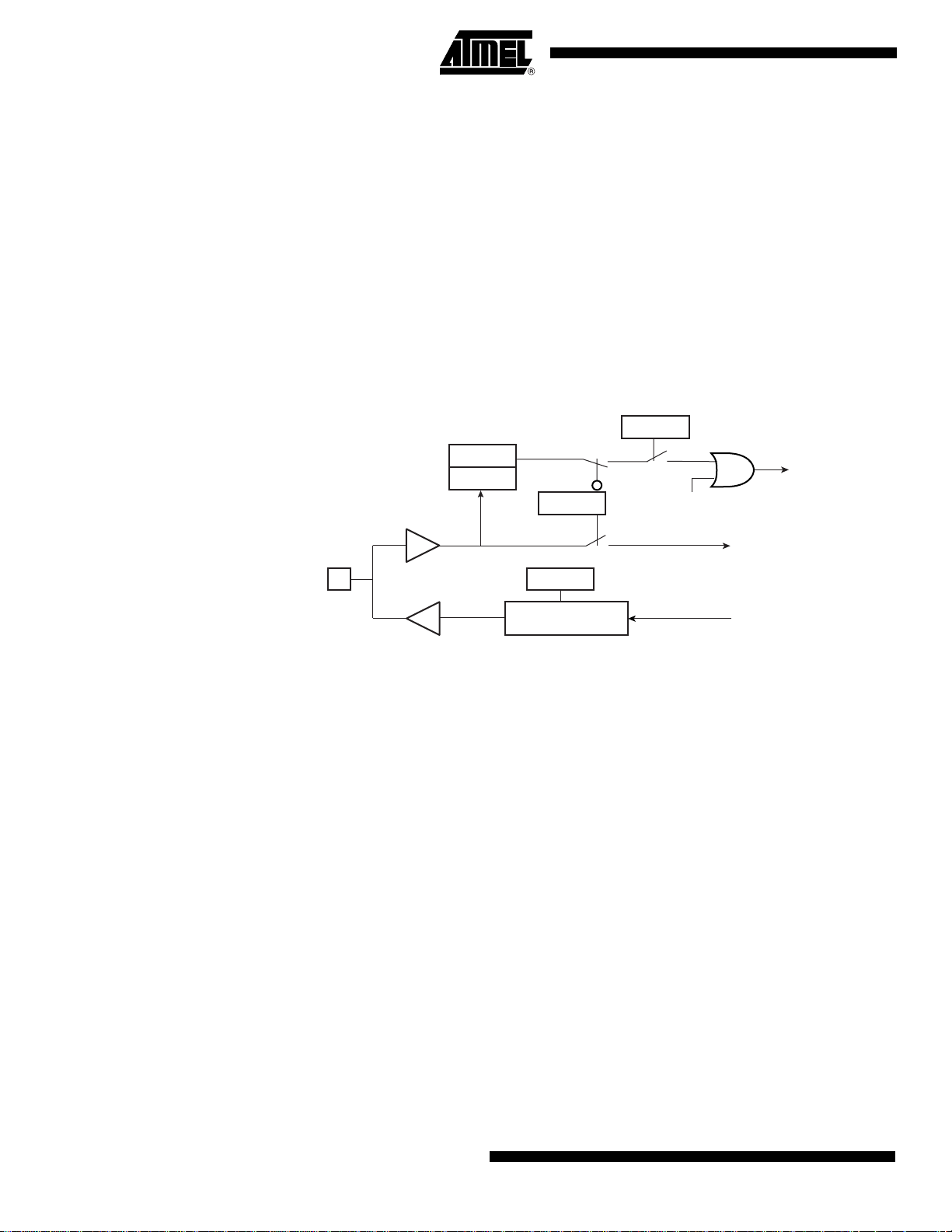

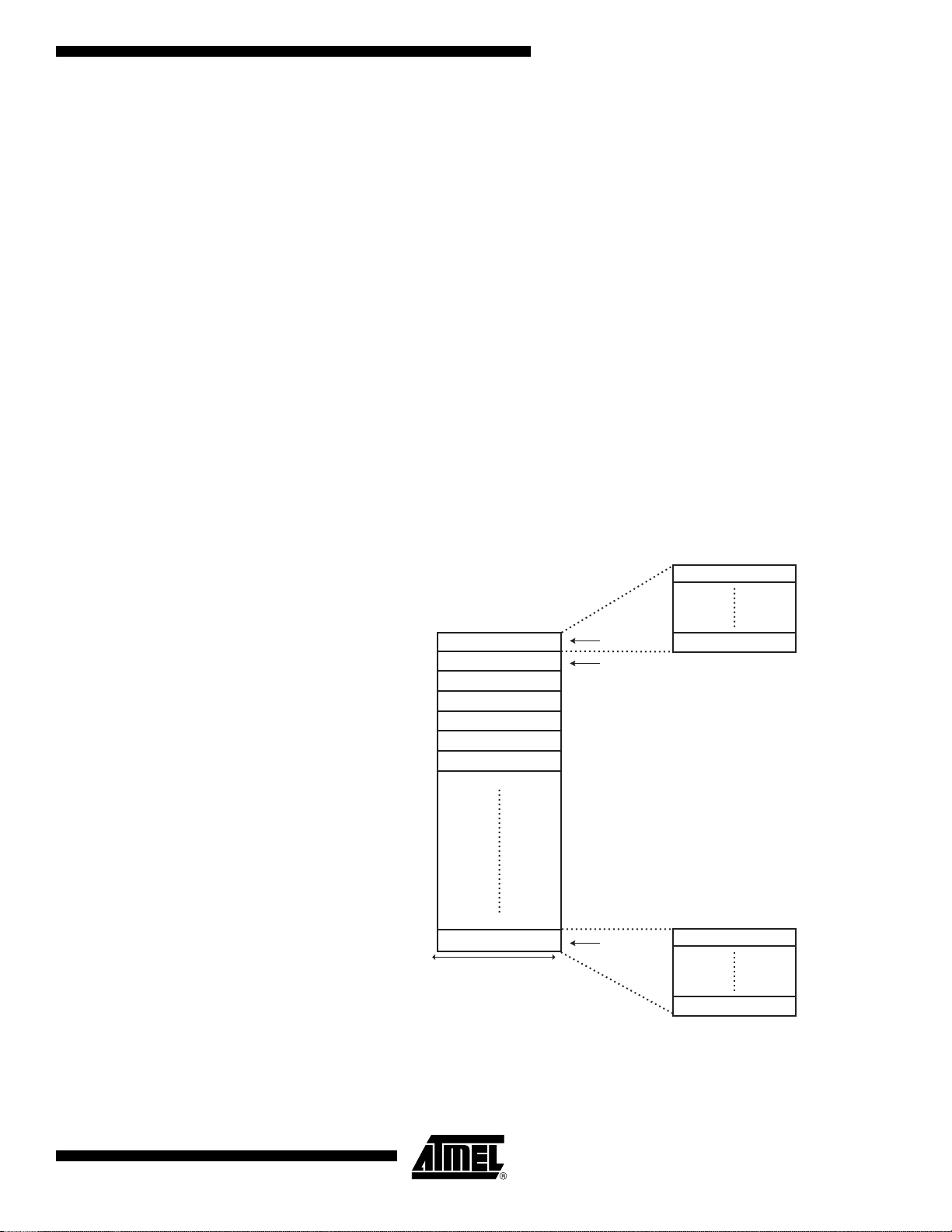

系统控制器 系统控制器管理处理器所有重要的模块:中断、时钟、电源、时序、调试以及复位。

Figure 5. 系统控制器框图

NRST

irq0-irq1

periph_irq[2..14]

pit_irq

rtt_irq

wdt_irq

dbgu_irq

pmc_irq

rstc_irq

periph_nreset

dbgu_rxd

debug

periph_nreset

SLCK

periph_nreset

SLCK

debug

proc_nreset

cal

gpnvm[0]

en

BOD

POR

SLCK

fiq

MCK

MCK

idle

gpnvm[1]

flash_wrdis

ice_nreset

jtag_nreset

flash_poe

System Controller

Advanced

Interrupt

Controller

Debug

Unit

Periodic

Interval

Timer

Real-Time

Timer

Watchdog

Timer

wdt_fault

WDRPROC

bod_rst_en

Reset

Controller

int

dbgu_irq

force_ntrst

dbgu_txd

pit_irq

rtt_irq

wdt_irq

periph_nreset

proc_nreset

rstc_irq

Voltage

Regulator

Mode

Controller

jtag_nreset

proc_nreset

PCK

debug

ice_nreset

force_ntrst

security_bit

flash_poe

flash_wrdis

cal

gpnvm[0..1]

MCK

proc_nreset

standby

cal

Boundary Scan

TAP Controller

nirq

nfiq

ARM7TDMI

Embedded

Flash

Memory

Controller

Voltage

Regulator

16

XIN

XOUT

PLLRC

RCOSC

OSC

PLL

MAINCK

PLLCK

periph_nreset

usb_suspend

periph_clk[2]

dbgu_rxd

SLCK

Power

Management

Controller

int

PIO

Controller

PA0-PA31

AT91SAM7S64 Preliminary

periph_clk[2..14]

pck[0-2]

PCK

UDPCK

MCK

pmc_irq

idle

periph_irq{2]periph_nreset

irq0-irq1

fiq

dbgu_txd

UDPCK

periph_clk[11]

periph_nreset

periph_irq[11]

usb_suspend

periph_clk[4..14]

periph_nreset

periph_irq[4..14]

in

out

enable

USB Device

Por t

Embedded

Peripherals

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

系统控制器映射 系统控制器外设映射到 4K 字节的最高地址空间,界于 0xFFFF F000 和 0xFFFF FFFF。

Figure 6 给出了系统控制器的映射情况。要注意的是,存储器控制器配置用户接口也映射

于这一地址区间。

Figure 6. 系统控制器映射

Peripheral Name SizeAddress Peripheral

0xFFFF F000

0xFFFF F1FF

0xFFFF F200

0xFFFF F3FF

0xFFFF F400

0xFFFF F5FF

0xFFFF F600

0xFFFF FBFF

0xFFFF FC00

0xFFFF FCFF

0xFFFF FD00

0xFFFF FD0F

0xFFFF FD20

0xFFFF FC2F

0xFFFF FD30

0xFFFF FC3F

0xFFFF FD40

0xFFFF FD4F

0xFFFF FD60

0xFFFF FC6F

0xFFFF FD70

0xFFFF FEFF

0xFFFF FF00

AIC

DBGU

PIOA

Reserved

PMC

RSTC

Reserved

RTT

PIT

WDT

Reserved

VREG

Reserved

Advanced Interrupt Controller

Debug Unit

PIO Controller A

Power Management Controller

Reset Controller

Real-time Timer

Periodic Interval Timer

Watchdog Timer

Voltage Regulator Mode Controller

512 Bytes/128 registers

512 Bytes/128 registers

512 Bytes/128 registers

256 Bytes/64 registers

16 Bytes/4 registers

16 Bytes/4 registers

16 Bytes/4 registers

16 Bytes/4 registers

4 Bytes/1 register

6070A–ATARM–07-Jun-05

0xFFFF FFFF

MC

Memory Controller

256 Bytes/64 registers

17

复位控制器 复位控制器包括上电复位和掉电检测复位。它可以给出上一次复位的状态,指明上一次复

位是上电复位、软件复位、用户复位、看门狗复位还是掉电检测复位。此外,它还控制内

部复位以及 NRST 引脚的输出,并控制 NRST 脉冲的长度以满足系统要求。

掉电检测及上电复位 AT91SAM7S64 嵌入了掉电检测电路和上电复位单元。两个电路都由VDDCORE供电,并

反过来监视 VDDCORE。两个信号都输送到 Flash,以防止在上电和下电的过程中,或是

电压跳变的过程中, Flash 中的代码被损毁。

上电复位单元具有有限精度的门限值,大约是 1.5V。在 VDDCORE 达到这个电平之前其

输出一直保持为低。这个信号输送到复位控制器,实现对芯片的重新初始化。

掉电检测器监视 VDDCORE 的电平,将其与固定的触发电平进行比较。它可以在大多数

情况下保证系统安全工作,并保

掉电检测器只监视 VDDCORE。这 是 因 为 VDDFLASH 或其他电源的跌落对 Flash 的意外

改写没有影响。

掉电检测器使能后,一旦 VDDCORE 下降到触发电平 (Vbot-,定义为 Vbot - hyst/2),掉

电检测输出立即被激活。

当 VDDCORE 上升到触发电平 (Vbot+,定 义为 Vbot + hyst/2),复位信号即被释放。掉电

检测器只监视 VDDCORE 跌落到门限值以下,持续时间大于 1µs 的情况。

证在 VDDCORE 发生跳变时存储器里的代码不被损毁。

为了防止电压尖峰的影响,门限电压有大约为 50 mV 的

1.68V,精度为 ± 2%。

掉电检测器是低功耗单元,只消耗大约 20 µA 的静态电流。为了进一步降低系统静态功

耗,还可以将其关闭。此时它消耗的静态电流小于 1µA。关闭掉电检测器是通过配置

GPNVM0 来实现的。

滞后值。门限电压的典型值为

18

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

时钟发生器 时钟发生器包括一个低功耗 RC 振荡器,一个主振荡器和一个 PLL。其特性为:

•RC振荡器的频率范围是 22 KHz 到 42 KHz

• 主振荡器的频率范围是 3 到 20 MHz

• 主振荡器可以被旁路

•PLL输出范围是 80 到 200 MHz

它提供了 SLCK、 MAINCK 以及 PLLCK。

Figure 7. 时钟发生器框图

Clock Generator

XIN

XOUT

PLLRC

Embedded

RC

Oscillator

Main

Oscillator

PLL and

Divider

Status

Power

Management

Controller

Control

Slow Clock

SLCK

Main Clock

MAINCK

PLL Clock

PLLCK

6070A–ATARM–07-Jun-05

19

电源管理控制器 电源管理控制器利用时钟发生器的输出提供 :

• 处理器时钟 PCK

• 主时钟 MCK

•USB时钟 UDPCK

• 所有独立可控的外设时钟

•3个可编程的时钟输出

通过编程,主时钟 (MCK) 可以从几百赫兹一直到芯片的最大工作频率。

处理器进入空闲模式等待中断发生时,处理器时钟 (PCK) 被关闭,从而降低器件功耗。

Figure 8. 电源管理控制器框图

Master Clock Controller

SLCK

MAINCK

PLLCK

SLCK

MAINCK

PLLCK

PLLCK

Prescaler

/1,/2,/4,...,/64

Programmable Clock Controller

Prescaler

/1,/2,/4,...,/64

USB Clock Controller

ON/OFF

Divider

/1,/2,/4

先进的中断控制器 • 控制 ARM 处理器的中断线 (nIRQ 和 nFIQ)

• 可以单独屏蔽的向量化中断源

– 中断源 0 为快速中断输入 (FIQ)

– 中断源 1 为系统外设 (RTT, PIT, EFC, PMC, DBGU,等 )

– 其他中断源控制外设中断或外部中断

– 可编程的边沿触发或电平敏感的内部中断源

– 可编程的正 / 负边沿触发或高 / 低电平敏感的外部中断源

•8级优先级控制器

– 驱动处理器的正常中断

– 处理中断源的优先级

– 高优先级中断可以插入正在执行的低优先级中断

• 向量化

– 优化中断服务例程的跳转及执行

– 每个中断源都有一个 32 位的向量寄存器

– 中断向量寄存器读取对应的当前中断向量

Processor

Clock

Controller

Idle Mode

Peripherals

Clock Controller

ON/OFF

PCK

int

MCK

periph_clk[2..14]

pck[0..2]

usb_suspend

UDPCK

20

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

• 保护模式

– 通过禁止自动操作简化调试

• 强制更新为快速中断

– 允许将任意一个中断源重定义为快速中断

• 通用的中断屏蔽

– 使处理器保持与事件的同步,同时不引发中断

调试单元 • 构成元素:

– 两线 UART

– 支持调试通讯通道 (DCC) 的接口

– 一组芯片 ID 寄存器

– 一个禁止 ICE 访问的接口

• 两线 UART

– 实现与 USART 兼容的特性

– 可编程的波特率发生器

– 奇偶校验、帧错误和超速错误

– 自动回应、本地回环和远程回环通道模式

• 支持调试通讯通道

– 输出了 ARM 处理器的 COMMRX 和 COMMTX 信号

• 芯片 ID 寄存器

– 识别器件的版本,片内存储器的大小及外设集

– 芯片 ID 为 0x27090540 ( 版本 0)

AT91SAM7S64 Preliminary

周期性间隔定时器 •20位可编程的计数器,外加 12 位的间隔计数器

看门狗定时器 •12位受预设值保护的可编程计数器,计数时钟为经过预分频的 SLCK

• 为系统提供复位或中断信号

• 处理器处于调试状态或空闲模式时可以停止计数器

实时定时器 •32位自由运行的计数器,带闹铃功能,计数时钟为经过预分频的 SLCK

• 可编程的 16 位预分频器用于 SLCK 精度补偿

PIO 控制器 • 一个 PIO 控制器,掌管 32 个 I/O 口线

• 通过设置 / 清除寄存器实现对 I/O 的完全控制

• 每个 I/O 都被两个外设功能所复用

• 每一个 I/O 口 ( 不论是分配给外设使用还是作为通用 I/O) 都支持

– 输入电平变化中断

– 半个时钟周期的尖峰滤波器

– 多种驱动选择,可以工作于开漏状态

– 可编程的上拉电阻

– 引脚数据状态寄存器给出了任意时候引脚上的电平

• 同步输出,设置和清零几个 I/O 口线只需要一个写操作

6070A–ATARM–07-Jun-05

21

电压调节器控制器 这个控制器的作用是选择电压调节器的工作模式:正 常模式 ( 位 0 清零 ) 或 Standby 模式

( 位 0 置位 )。

22

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

外设

外设映射 每个外设都分配了 16K 字节的地址空间。

Figure 9. 用户外设映射

0xF000 0000

Reserved

0xFFF9 FFFF

0xFFFA 0000

0xFFFA 3FFF

0xFFFA 4000

0xFFFA FFFF

0xFFFB 0000

0xFFFB 3FFF

0xFFFB 4000

0xFFFB 7FFF

0xFFFB 8000

0xFFFB BFFF

0xFFFB C000

0xFFFB FFFF

0xFFFC 0000

0xFFFC 3FFF

0xFFFC 4000

0xFFFC 7FFF

0xFFFC 8000

0xFFFC BFFF

0xFFFC C000

0xFFFC FFFF

0xFFFD 0000

0xFFFD 3FFF

0xFFFD 4000

0xFFFD 7FFF

0xFFFD 8000

0xFFFD BFFF

0xFFFD C000

0xFFFD FFFF

0xFFFE 0000

0xFFFE 3FFF

0xFFFE 4000

0xFFFE FFFF

TC0, TC1, TC2 Timer/Counter 0, 1 and 2

Reserved

UDP USB Device Port

Reserved

TWI Two-Wire Interface

Reserved

USART0 Universal Synchronous Asynchronous

USART1 Universal Synchronous Asynchronous

Reserved

PWMC

Reserved

SSC Serial Synchronous Controller

ADC Analog-to-Digital Converter

Reserved

SPI Serial Peripheral Interface

Reserved

Peripheral Name Size

16 Kbytes

16 Kbytes

16 Kbytes

16 Kbytes

Receiver Transmitter 0

16 Kbytes

Receiver Transmitter 1

PWM Controller

16 Kbytes

16 Kbytes

16 Kbytes

16 Kbytes

6070A–ATARM–07-Jun-05

23

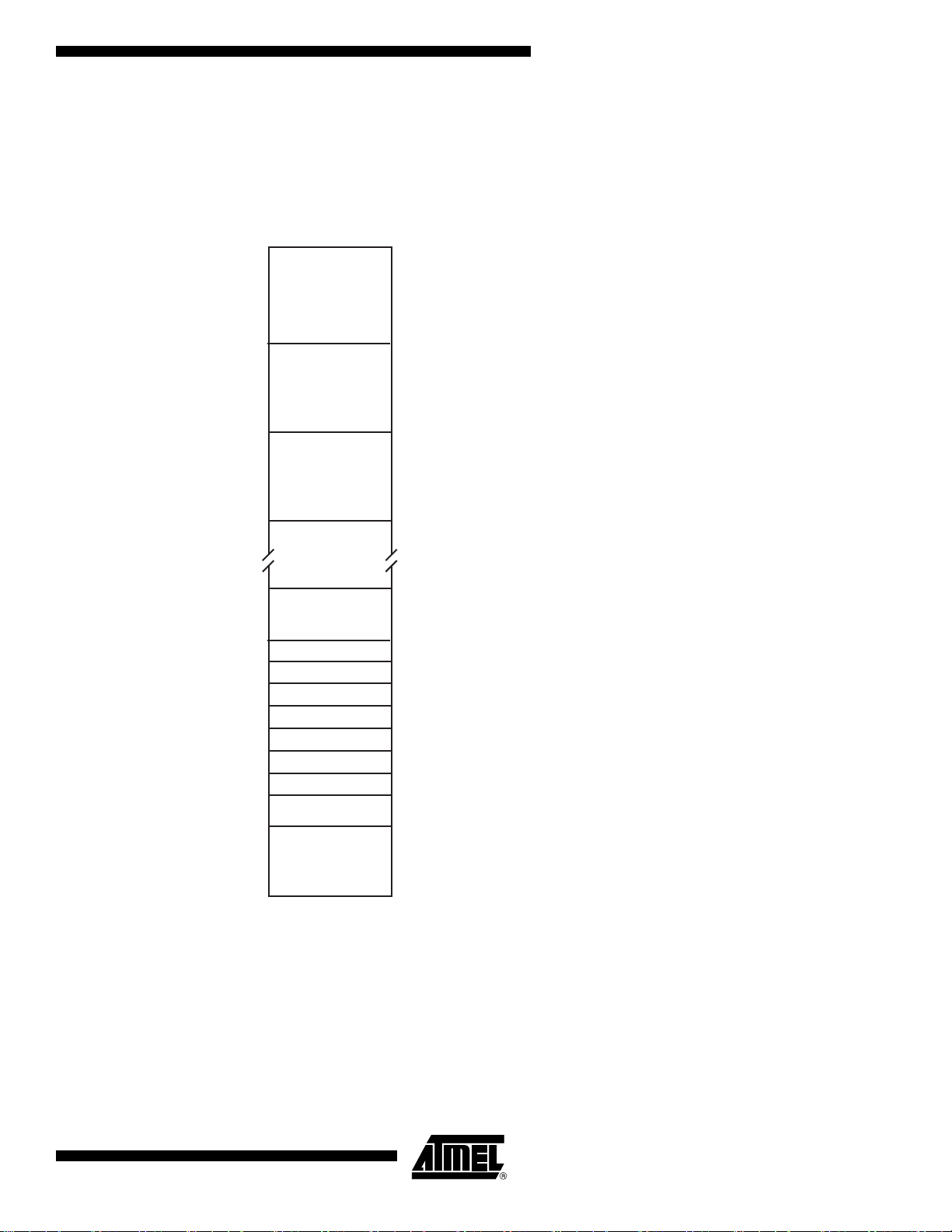

外设功能在 PIO 口线上的复用

AT91SAM7S64 的 PIO 控制器 PIOA 复用了 I/O 口线作为外设功能。

PIO控制器A控制32个口线。每个口线都可以分配为两个外设功能的一个,A或B。其 中的

一些还可以复用为 ADC 控制器的模拟输入。

Table 3 on page 25 说明了PIO 控制器 A的 I/O口线是如何被外设 A,B 或模拟输入所复用

的。 “ 功能 ” 及 “ 说明 ” 这两列主要是方便用户针对具体应用做注释以跟踪各个引脚是如

何被分配使用的。

要注意某些只能作为输出的外设功能在表中被复制了多次。

复位时所有的并行 I/O 都配置为输入,且

上拉电阻使能。

24

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

PIO 控制器 A 引脚复用

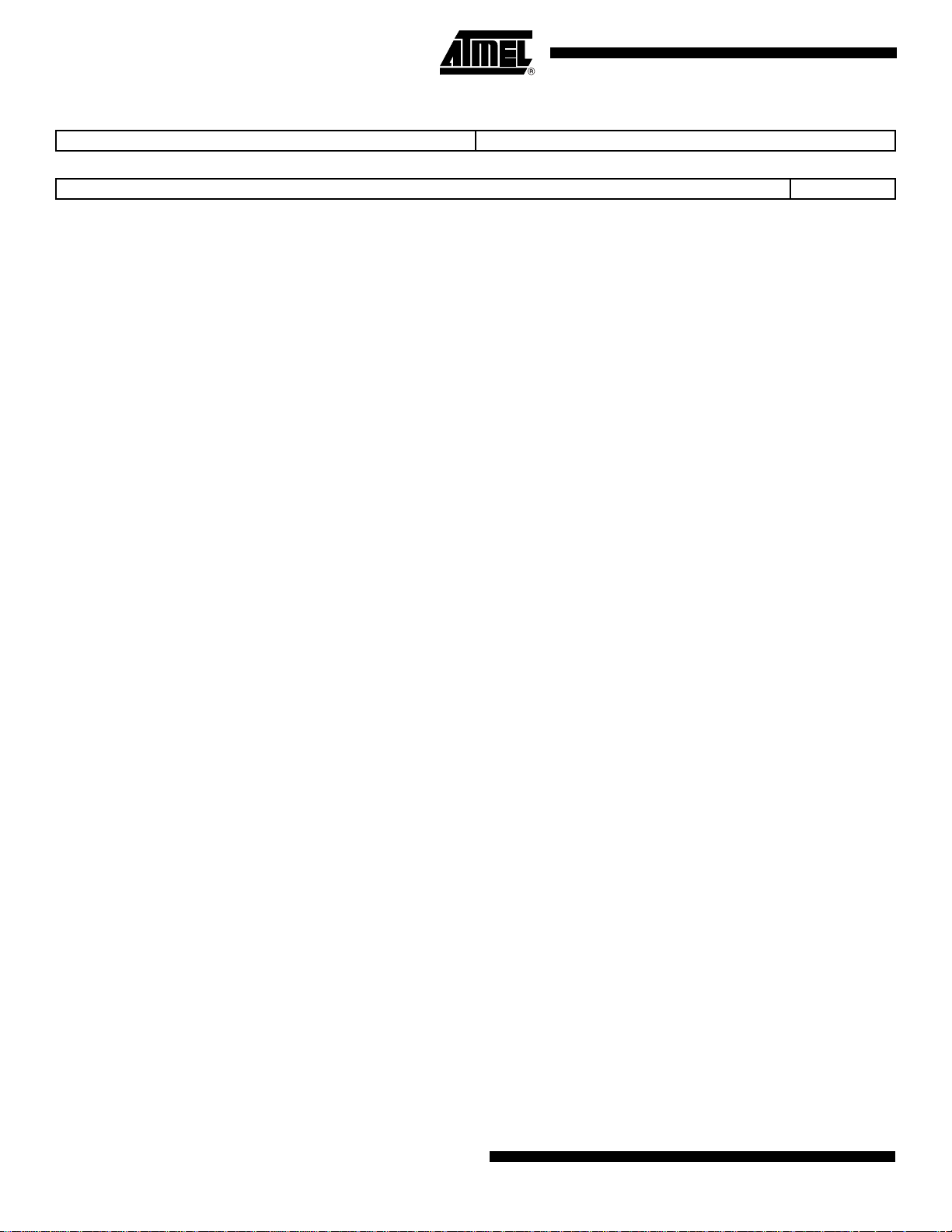

Table 3. PIO 控制器 A 引脚复用

PIO 控制器 A 应用

I/O 外设 A 外设 B 说明 功能 说明

PA 0 P WM0 T I OA 0 大电流驱动

PA 1 P WM1 T IOB0 大电流驱动

PA 2 P WM2 S C K 0 大电流驱动

PA 3 T WD N P C S3 大电流驱动

PA 4 T W CK T C LK 0

PA5 RXD0 NPCS3

PA 6 TX D 0 PC K 0

PA 7 RT S 0 PW M 3

PA 8 CT S 0 AD T R G

PA9 DRXD NPCS1

PA10 DTXD NPCS2

PA11 NPCS0 PWM0

PA12 MISO PWM1

PA13 MOSI PWM2

PA14 SPCK PWM3

PA15 TF TIOA1

PA 16 T K TI O B 1

PA17 TD PCK1 AD0

PA18 RD PCK2 AD1

PA 19 RK FIQ AD2

PA 20

PA21 RXD1 PCK1

PA22 TXD1 NPCS3

PA23 SCK1 PWM0

PA24 RTS1 PWM1

PA25 CTS1 PWM2

PA26 DCD1 TIOA2

PA27 DTR1 TIOB2

PA28 DSR1 TCLK1

PA 29 R I1 T C LK2

PA 30 I R Q 1 N PCS2

PA31 NPCS1 PCK2

RF IRQ0 AD3

6070A–ATARM–07-Jun-05

25

外设标识符 AT91SAM7S64 拥有很多外设。Table 4 给出了各种外设的标识符。中断控制器用标识符

来控制外设中断,而电源管理控制器则用标识符来控制外设时钟。

Table 4. 外设标识符

外设 ID 外设助记符 外设名称 外部中断

0AIC先进的中断控制器 FIQ

1 SYSIRQ

2PIOA并行 I/O 控制器 A

3 保留

4ADC

5 SPI 串行外设接口

6US0USART 0

7US1USART 1

8 SSC 同步串行接口

9TWI两线接口

10 PWMC PWM 控制器

11 UDP USB 设备端口

12 TC0 定时器 / 计数器 0

13 TC1 定时器 / 计数器 1

14 TC2 定时器 / 计数器 2

15 - 29 保留

30 AIC 先进的中断控制器 IRQ0

31 AIC 先进的中断控制器 IRQ1

Note: 1. 对电源管理控制器(PMC)时钟置位/清除寄存器的SYSIRQ以及ADC进行置位操作不会

引起任何作用。系统控制器总是有时钟驱动的。进行第一次转换时 ADC 时钟自动启

动。在休眠模式下,每一次转换结束后 ADC 时钟自动停止。

(1)

(1)

系统中断

模数转换器

串行外设接口 SPI • 支持与其他串行设备的通讯

–4个片选线,在解码芯片的协助下可以与多达 15 个器件进行通讯

– 串行存储器,如 DataFlash

– 串行外设,如 ADC, DAC, LCD 控制器, CAN 控制器和传感器等

– 外部协处理器

• 主 / 从 SPI 总线

– 每个片选线都支持 8 到 16 位可编程的数据长度

– 每个片选线都支持可编程的信号相位和极性

– 每个片选线都支持可编程的连续数据帧间传输延迟,以及时钟和数据之间的

传输延迟

– 可编程的连续传输延迟

– 可选择的模式错误检测

– 最高频率为主时钟

两线接口 TWI • 只支持主机模式

• 与标准的两线串行存储器兼容

26

AT91SAM7S64 Preliminary

®

和 3 线 EEPROM

6070A–ATARM–07-Jun-05

• 从机地址可以为一个字节,两个字节和三个字节

• 连续的读 / 写操作

USART • 可编程的波特率发生器

•5到 9 位的全双工同步或异步串行通讯

–1、 1.5 或 2 个停止位,异步模式

–1或 2 个停止位,同步模式

– 奇偶校验发生器和错误检测

– 帧错误检测,超速错误检测

–MSB先发送或 LSB 先发送

– 可选的中断 (break) 产生及检测

– 接收器采样频率为数据频率的 8 或 16 倍

– 硬件握手信号 RTS - CTS

– Modem 信号管理 DTR-DSR-DCD-RI, USART1

– 接收器时间溢出,发送器时间保护 (timeguard)

– 具有地址产生和检测功能的多地址 (Multi-drop) 通讯模式

• 支持 RS485 通讯,具有驱动器控制信号

• 支持 ISO7816 的 T = 0 或 T = 1 协议

–NACK信号处理,有限重复次数的错误计数器

•IrDA调制与解调

– 通讯速率可达 115.2 Kbps

• 测试模式

– 远程回环,本地回环,自动回发

AT91SAM7S64 Preliminary

,实现与智能卡的接口

串行同步控制器 • 为语音和电信应用提供了串行同步通讯链路

• 包括一个独立的接收器和独立的发送器,以及共用的时钟分频器

• 可配置的帧同步和数据长度

• 接收器和发送器都可以编程为自动启动,或是在检测到帧同步信号上的不同事件之

后再启动

• 接收器和发送器包括了数据信号、时钟信号和帧同步信号

定时器 / 计数器 •3个 16 位的定时器 / 计数器通道

–3个输出比较或两个输入捕捉

• 如下多种功能:

– 频率测量

– 事件计数

– 时间间隔测量

– 脉冲产生

– 延迟

–PWM

– 向上递增计数和向下递减计数的能力

• 每个通道都可以进行配置,并包括了:

–3个外部时钟输入

6070A–ATARM–07-Jun-05

27

–5个外部时钟输入,如 Table 5 所示。

Table 5. 定时器 / 计数器时钟分配

TC 时钟输入 时钟

TIMER_CLOCK1 MCK/2

TIMER_CLOCK2 MCK/8

TIMER_CLOCK3 MCK/32

TIMER_CLOCK4 MCK/128

TIMER_CLOCK5 MCK/1024

– 两个多功能输入 / 输出信号

– 两个作用于所有 3 个 TC 通道的全局寄存器

PWM 控制器 •4个通道,每个通道有一个 16 位的计数器

• 公共的时钟发生器,可以提供 13 个不同的时钟

– 一个 Mod(n) 计数器,提供 11 个时钟

– 作用于 Mod(n) 计数器输出的两个独立的线性分频器

• 通道的编程是独立的

– 独立的使能 / 禁止命令

– 独立的时钟选择

– 独立的双缓冲周期和占空比

– 可编程的输出波形极性选择

– 可编程的输出波形对准方式:中心对准或左边对准

USB 设备端口 • 与 USB V2.0 全速标准兼容,通讯速率为 12 Mbps

• 片内 USB V2.0 全速收发器

• 为端点所使用的片 内 328 字节双口 RAM

•4个端点

– 端点 0: 8 字节

– 端点 1 和端点 2: 64 字节, ping-pong

– 端点 3: 64 字节

–bulk端点支持 Ping-pong 模式 ( 两个存储区 )

• 挂起 / 继续 (suspend/resume) 逻辑

模数转换器 •8通道的 ADC

•10位数据,每秒采样次数高达 100K,连续逼近寄存器 ADC

• -2/+2 LSB 积分非线性误差, -1/+2 LSB 差分非线性误差

• 集成的 8-1 多工器,可以有 8 个独立的 3.3V 模拟输入

• 每个通路可以单独使能和禁止

• 对于低电压输入信号可以使用外部电压基准源来提高转换精度

• 多个触发源

– 硬件或软件触发

– 外部触发引脚

– 利用定时器 / 计数器 0-2 的输出 TIOA0-2 进行触发

28

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

• 休眠模式和转换序列

– 触发信号将使芯片自动唤醒;所有使能的通道转换结束之后器件又进入睡眠

模式

•8个模拟输入中的的 4 个与数字信号共享引脚

6070A–ATARM–07-Jun-05

29

30

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

ARM7TDMI 处理器综述

AT91SAM7S64 Preliminary

概述 ARM7TDMI内核既可以执行32位的ARM

使用户在高性能和高代码密度之间进行平衡。 ARM7TDMI 处理器为冯 - 诺依曼结构,具有三级

流水线,即指令获取、解码和执行三个阶段。

ARM7TDMI 处理器的主要特点是:

•ARM7TDMI基于 ARMv4T 结构

• 两个指令集

–ARM

–Thumb

• 三级流水线结构

– 指令获取 (F)

– 指令解码 (D)

– 执行 (E)

®

高性能 32 位指令集

®

高代码密度 16 位指令集

®

指令集,也可以执行16位的Thumb®指令集,从而可以

6070A–ATARM–07-Jun-05

31

ARM7TDMI 处理器

有关 ARM7TDMI 更详细的信息请参阅下面的 ARM 文档:

ARM Architecture Reference Manual (DDI 0100E)

ARM7TDMI Technical Reference Manual (DDI 0210B)

指令类型 指令或者是 32 位 (ARM 模式 ),或者是 16 位 (THUMB 模式 )。

数据类型 ARM7TDMI支持字节(8位),半字(16位)以及字(32位)这三种数据类型。字必须与4字节的边界对

齐,半字必须与 2 字节的边界对齐。

未对齐的数据访问行为取决于指令类型。

ARM7TDMI 工作模 式

ARM7TDMI 基于 ARM 结构 v4T,支持如下 7 种处理器模式:

User:一般的 ARM 程序执行状态

FIQ:设计为高速数据传输或通道处理

IRQ:用于通常的中断处理

Supervisor:用于操作系统的保护模式

Abort mode:实现虚拟内存和 / 或内存保护

System:操作系统的特权用户模式

Undefined:支持硬件协处理器的软件仿真

模式之间的转换可以通过软件进行控制,也可能由中断或例外处理引起。大多数应用程序运行

于 User 模式。而 非用户模式,或特权用户模式,则针对中断或例外,或者是访问受保护的资源。

ARM7TDMI 寄存器 ARM7TDMI 处理器总共有 37 个寄存器:

•31个通用 32 位寄存器

•6个状态寄存器

这些寄存器不能够在同一时间都访问到。处理器状态及工作模式决定了哪些寄存器可以被程序

员使用。

在任意时刻有 16 个寄存器是可访问的。其他的则与这 16 个寄存器拥有相同的名字,并用于加

速例外的处理。

32

寄存器 R15 为程序计数器 (PC),可以用于所有的指令来获取相对于当前指令的数据。

R14 保留着子程序调用的返回地址。

R13 通常用做堆栈指针。

.

Table 6. ARM7TDMI ARM 模式及

User 和

System 模式

R0 R0 R0 R0 R0 R0

R1 R1 R1 R1 R1 R1

R2 R2 R2 R2 R2 R2

R3 R3 R3 R3 R3 R3

Supervisor模

式 Abort 模式

AT91SAM7S64 Preliminary

寄存器规划

Undefined 模

式 IRQ 模式 FIQ 模式

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

Table 6. ARM7TDMI ARM 模式及寄存器规划

User 和

System 模式

R4 R4 R4 R4 R4 R4

R5 R5 R5 R5 R5 R5

R6 R6 R6 R6 R6 R6

R7 R7 R7 R7 R7 R7

R8 R8 R8 R8 R8

R9 R9 R9 R9 R9

R10 R10 R10 R10 R10 R10_FIQ

R11 R11 R11 R11 R11

R12 R12 R12 R12 R12

R13 R13_SVC R13_ABORT R13_UNDEF R13_IRQ R13_FIQ

R14 R14_SVC R14_ABORT R14_UNDEF R14_IRQ R14_FIQ

PC PC PC PC PC PC

CPSR CPSR CPSR CPSR CPSR CPSR

Supervisor模

式 Abort 模式

SPSR_SVC SPSR_ABORT SPSR_UNDEF SPSR_IRQ SPSR_FIQ

Undefined 模

式 IRQ 模式 FIQ 模式

R8_FIQ

R9_FIQ

R11_FIQ

R12_FIQ

与模式相关的分区的寄存器

寄存器 R0 到 R7 是不分区的。也就是说,在所有的工作模式下,它们指向的是相同的 32 位物

理寄存器。它们也是通用寄存器,与处理器结构没有直接的关系,可 以 出现在任何指令允许它

们出现的地方。

R8 到 R14 则是分区的寄存器。它们指向的物理寄存器根据处理器工作模式的不同而不同。

模式和例外处理 所有的例外都有分区的寄存器 R14 和 R13。

例外发生后, R14 保存了例外处理的返回地址。例外处理结束后,通过这个地址程序

外发生时的指令。

对于各种例外模式, R13 也是分区的,从而可以外各个例外处理程序提供单独的堆栈指针。

快速中断模式还实现了 R8 到 R12 的分区,从而中断处理程序可以不保存这些寄存器就开始执

行中断处理。

第 7 个处理模式,即 System 模式,没有任何分区的寄存器。它 使用与 User 模式相同的寄存器。

在 System 模式里可以运行那些需要特权模式的任务,并允许它们引发各种级别的例外。

状态寄存器 所 有 其 他 的处理器状态保存于状态寄 存器。当前 处理器状态保存于当

(Current Program Status Register,CPSR)。其内容为:

• 4 个 ALU 标志 ( 负,零,进位,溢出 )

• 两个中断禁止位 ( 每种中断一个 )

• 一个比特用来指示 ARM 状态还是 Thumb 状态

• 5 个比特用来解码当前的处理器模式

所有 5 个例外模式还拥有一个保存的程序状态寄存器(Saved Program Status Register,SPSR),

这个寄存器保存了在例外发生之前的那个任务的 CPSR。

返回到例

前程序状态寄存器

6070A–ATARM–07-Jun-05

33

例外类型 ARM7TDMI 支持 5 种类型的例外,每一种都有对应的特权处理模式。这些例外类型是:

• 快速中断 (FIQ)

• 普通中断 (IRQ)

• 内存异常中断 ( 用来实现内存保护或虚拟内存 )

• 尝试执行未定义的指令

• 软件中断 (SWI)

例外由片内外的中断源产生。

在同一时间可以有多个例外发生。

例外发生时,此例外对应的、分区的 R14 和 SPSR 将当前状态保存下来。

从例外返回时需要将 SPSR 拷贝回 CPSR,同 时 将 R14 的值赋给 PC。实现的方法有如下两个:

• 使用数据处理指令, S 置位, PC 为目的寄存器

• 使用 LDM 指令

ARM 指令集概览 ARM 指令集分为:

• 分支跳转指令

• 数据处理指令

• 状态寄存器传输指令

• 加载和保存指令

• 协处理器指令

• 例外产生指令

ARM 指令可以有条件地执行。每个指令都包括 4 比特的条件代码域 (bit[31:28])。

Table 7 给出了 ARM 指令表。

Table 7. ARM 指令表

助记符 操作 助记符 操作

MOV Move CDP Coprocessor Data Processing

ADD Add MVN Move Not

SUB Subtract ADC Add with Carry

RSB Reverse Subtract SBC Subtract with Carry

CMP Compare RSC Reverse Subtract with Carry

TST Test CMN Compare Negated

AND Logical AND TEQ Test Equivalence

EOR Logical Exclusive OR BIC Bit Clear

MUL Multiply ORR Logical (inclusive) OR

SMULL Sign Long Multiply MLA Multiply Accumulate

SMLAL Signed Long Multiply Accumulate UMULL Unsigned Long Multiply

MSR Move to Status Register UMLAL Unsigned Long Multiply Accumulate

B Branch MRS Move From Status Register

BX Branch and Exchange BL Branch and Link

34

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

Table 7. ARM 指令表

助记符 操作 助记符 操作

LDR Load Word SWI Software Interrupt

LDRSH Load Signed Halfword STR Store Word

LDRSB Load Signed Byte STRH Store Half Word

LDRH Load Half Word STRB Store Byte

LDRB Load Byte STRBT Store Register Byte with Translation

LDRBT Load Register Byte with Translation STRT Store Register with Translation

LDRT Load Register with Translation STM Store Multiple

LDM Load Multiple SWPB Swap Byte

SWP Swap Word MRC Move From Coprocessor

MCR Move To Coprocessor STC Store From Coprocessor

LDC Load To Coprocessor

Thumb 指令集概览 Thumb 指令集是 ARM 指令集经过重新编码的子集。

Thumb 指令集分为:

• 分支跳转指令

• 数据处理指令

• 加载和保存指令

• 加载和保存 ( 多个数据 ) 指令

• 例外产生指令

在 Thumb 模式中 8 个通用寄存器,R0 到 R7,是可访问的。还可以访问的是程序计数器 (ARM

寄存器 15),链接寄存器 (ARM 寄存器 14) 以及堆栈指针 (ARM 寄存器 13)。还有一些指令对

ARM 寄存器 R8 到 R15 有有限的访问权限。

Table 8 给出了 Thumb 指令集。

Table 8. Thumb 指令集

助记符 操作 助记符 操作

MOV Move MVN Move Not

ADD Add ADC Add with Carry

SUB Subtract SBC Subtract with Carry

CMP Compare CMN Compare Negated

TST Test NEG Negate

AND Logical AND BIC Bit Clear

EOR Logical Exclusive OR ORR Logical (inclusive) OR

LSL Logical Shift Left LSR Logical Shift Right

ASR Arithmetic Shift Right ROR Rotate Right

MUL Multiply

B Branch BL Branch and Link

BX Branch and Exchange SWI Software Interrupt

LDR Load Word STR Store Word

6070A–ATARM–07-Jun-05

35

Table 8. Thumb 指令集

助记符 操作 助记符 操作

LDRH Load Half Word STRH Store Half Word

LDRB Load Byte STRB Store Byte

LDRSH Load Signed Halfword LDRSB Load Signed Byte

LDMIA Load Multiple STMIA Store Multiple

PUSH Push Register to stack POP Pop Register from stack

36

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

AT91SAM7S64 调试及测试特点

说明 AT91SAM7S64 具有调试及测试能力。 JTAG/ICE (In-Circuit Emulator) 用于标准的调试功能,

如下载代码,在程序里实现单步执行等。调试单元提供了一个两线 UART,可以利用它将应用

程序上载到片内 SRAM。它管理着 COMMTX 和 COMMRX 信号的中断处理,实现对调试通讯

通道活动的跟踪。

通过一整套复杂的调试与测试输入 / 输出引脚, PC 端的测试环境可以直接访问这些调试 / 测试

功能。

方框图

Figure 10. 调试及测试框图

TMS

TCK

TDI

PDC

Boundary

TA P

ARM7TDMI

ICE

DBGU

ICE/JTAG

TA P

Reset

and

Test

PIO

JTAGSEL

TDO

POR

TST

DTXD

DRXD

6070A–ATARM–07-Jun-05

37

应用例子

调试环境 Figure 11 on page 38 展示了一个完整的调试环境例子。 ICE/JTAG 接口用于标准的调试功能,

如下载代码和单步执行程序。

Figure 11. 调试环境例子

Host Debugger

ICE/JTAG

Interface

ICE/JTAG

Connector

AT91SAM7S64

AT91SAM7S64-based Application Board

RS232

Connector

Terminal

38

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

测试环境 Figure 12 on page 39 展示了测试环境的例子。测试向量由测试仪发送和解释。在这个例子中,

接受测试的板子上有一些与 JTAG 兼容的器件。这些器件可以连接到一起组成一个扫描链。

Figure 12. 测试环境例子

调试及测试引脚

说明

Test Adaptor

JTAG

Interface

ICE/JTAG

Connector

AT91SAM7S64

AT91SAM7S64-based Application Board In Test

Chip 2Chip n

Chip 1

Tester

Table 9. 调试及测试引脚列表

引脚名称 功能 类型 有效电平

复位 / 测试

NRST 处理器复位 输入 / 输出 低

TST 测试模式选择 输入 高

ICE 及 JTAG

TCK 测试时钟 输入

TDI 测试数据输入 输入

TDO 测试数据输出 输出

TMS 测试模式选择 输入

JTAGSEL JTAG 选择 输入

调试单元

DRXD 调试接收数据 输入

DTXD 调试发送数据 输出

6070A–ATARM–07-Jun-05

39

功能描述

测试引脚

嵌入式在线仿真器 -

ICE

TST引脚用来定义芯片工作模式。在正常工作模式下用户必须保证这个引脚接到低电平。高电平

则用于生产测试。

ARM7TDMI 嵌入式在线仿真是通过 ICE/JTAG 得到支持的。 ARM7TDMI 的内部状态通过

ICE/JTAG 得以检查。

ARM7TDMI 处理器具有实现先进的调试特性的硬件扩展:

• 在暂停 (halt) 模式下,“ 存储多个数据” (STM) 可以插入到指令流水线。这个指令可以输出

ARM7TDMI 寄存器的内容。然后这些数据以串行的方式从 TDI 输出 ,而不影响系统的其他

部分。

• 在监控模式下, JTAG 接口用于在调试器和运行于 ARM7TDMI 处理器内部的简单监控程序

之间传输数据。

ARM7TDMI处理器有三个扫描链分别支持测试、调试及编程。所 有扫描链都由 ICE/JTAG控制。

JTAGSEL引脚为低时选择嵌入式ICE模式

SEL 变化后必须进行芯片复位。

进一步的嵌入式ICE信息请参阅 ARM7TDMI (Rev4) Technical Reference Manual (DDI0210B)。

。不 能在ICE和JTAG模式之间直接进行切换。JTAG-

调试单元 调试单元提供了两线 (DXRD 和 TXRD) USART 用于一些调试及跟踪的目的。同时这也是现场编

程和调试监控通讯的理想方法。此外,由于两个外设数据控制器通道的存在,处理器处理数据

包的时间可以减至最小。

调试单元还管理着 COMMTX 和 COMMRX 的中断处理。这是两个来自 ICE 的信号,它们跟踪

着调试通讯通道的活动。调试单元可以阻止通过 ICE 接口对系统进行的访问。

IEEE 1149.1 JTAG

边界扫描

JTAG 边界扫描寄存器

调试单元可以用来上载应用程序到片内 SRAM。当引导程序没有发现有效的应用程序时即激活

这个功能。用来加载应用程序的协议是 XMODEM。

调试单元芯片 ID 寄存器保存了有关产品版本及内部配置的信息。

AT91SAM7S64 的调试单元芯片 ID 的数值为 0x27090540。

有

关调试单元的更多信息请参阅 “Debug Unit (DBGU)” on page 179。

通过 IEEE 1149.1 JTAG 边界扫描可以访问每个引脚,而不必关心器件的封装形式。

JTAGSEL 为高时使能 IEEE 1149.1 JTAG 边界扫描。实现的功能有 SAMPLE、 EXTEST 和

BYPASS。在 ICE 调试模式下,ARM 处理器将返回一个非 JTAG芯片 ID 到 ICE 系统。这 与 IEEE

1149.1 JTAG 是不兼容的。

JTAG 模式和 ICE 模式不能直接进行切换。 JTAGSEL 电平改变之后必须对芯片进行复位。

Atmel 提供了边界扫描叙词语言 (BSDL) 文件以方便客户设置测试系统。

边界扫描寄存器 (BSR) 包含与各个引脚和相关控制信号对应的 96 个比特。

40

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

每个 AT91SAM7S64 输入 / 输出引脚在 BSR 里都占 3 个比特。OUTPUT 表示数据可以强制输

出到引脚; INPUT 用来观察加载于引脚的数据; CONTROL 则控制引脚的方向。

Table 10. AT91SAM7S64 JTAG 边界扫描寄存器

比特流的顺序号 引脚名称 引脚类型 相关的 BSR 单元

96

95 OUTPUT

94 CONTROL

93

92 OUTPUT

91 CONTROL

90

89 OUTPUT

88 CONTROL

87

86 OUTPUT

85 CONTROL

84

83 OUTPUT

82 CONTROL

81

80 OUTPUT

79 CONTROL

78

77 OUTPUT

PA17/PGMD5/AD0 IN/OUT

PA18/PGMD6/AD1 IN/OUT

PA21/PGMD9 IN/OUT

PA19/PGMD7/AD2 IN/OUT

PA20/PGMD8/AD3 IN/OUT

PA16/PGMD4 IN/OUT

PA15/PGM3 IN/OUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

6070A–ATARM–07-Jun-05

76 CONTROL

75

74 OUTPUT

73 CONTROL

72

71 OUTPUT

70 CONTROL

69

68 OUTPUT

67 CONTROL

66

65 OUTPUT

64 CONTROL

PA14/PGMD2 IN/OUT

PA13/PGMD1 IN/OUT

PA22/PGMD10 IN/OUT

PA23/PGMD11 IN/OUT

INPUT

INPUT

INPUT

INPUT

41

Table 10. AT91SAM7S64 JTAG 边界扫描寄存器

比特流的顺序号 引脚名称 引脚类型 相关的 BSR 单元

63

62 OUTPUT

61 CONTROL

60

PA24/PGMD12 IN/OUT

INPUT

INPUT

59 OUTPUT

58 CONTROL

57

56 OUTPUT

55 CONTROL

54

53 OUTPUT

52 CONTROL

51

50 OUTPUT

49 CONTROL

48

47 OUTPUT

46 CONTROL

45

44 OUTPUT

43 CONTROL

42

PA12/PGMD0 IN/OUT

INPUT

PA11/PGMM3 IN/OUT

INPUT

PA10/PGMM2 IN/OUT

INPUT

PA 9 /P G M M1 I N /O U T

INPUT

PA 8 /P G M M0 I N /O U T

INPUT

PA7/PGMNVALID IN/OUT

INPUT

42

41 OUTPUT

40 CONTROL

39

38 OUTPUT

37 CONTROL

36

35 OUTPUT

34 CONTROL

33

32 OUTPUT

31 CONTROL

30

29 OUTPUT

28 CONTROL

PA6/PGMNOE IN/OUT

PA 5/ PG M R DY I N /O U T

PA4/PGMNCMD IN/OUT

PA25/PGMD13 IN/OUT

PA26/PGMD14 IN/OUT

AT91SAM7S64 Preliminary

INPUT

INPUT

INPUT

INPUT

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

Table 10. AT91SAM7S64 JTAG 边界扫描寄存器

比特流的顺序号 引脚名称 引脚类型 相关的 BSR 单元

27

26 OUTPUT

25 CONTROL

24

PA27/PGMD15 IN/OUT

INPUT

INPUT

23 OUTPUT

22 CONTROL

21

20 OUTPUT

19 CONTROL

18

17 OUTPUT

16 CONTROL

15

14 OUTPUT

13 CONTROL

12

11 OUTPUT

10 CONTROL

9

8OUTPUT

7 CONTROL

6

PA 28 I N /OUT

INPUT

PA 3 I N / OUT

INPUT

PA 2 I N / OUT

INPUT

PA1/PGMEN1 IN/OUT

INPUT

PA0/PGMEN0 IN/OUT

INPUT

PA 29 I N /OUT

INPUT

5OUTPUT

4 CONTROL

3

2OUTPUT

1 CONTROL

0 ERASE IN INPUT

PA 30 I N /OUT

PA 31 I N /OUT

ID 代码寄存器

访问类型:只读

31 30 29 28 27 26 25 24

VERSION PART NUMBER

23 22 21 20 19 18 17 16

PART NUMBER

6070A–ATARM–07-Jun-05

INPUT

43

15 14 13 12 11 10 9 8

PART NUMBER MANUFACTURER IDENTITY

76543210

MANUFACTURER IDENTITY 1

VERSION[31:28]: 芯片版本号

0x1

PART NUMBER[27:12]: 芯片型号

0x5B06

MANUFACTURER IDENTITY[11:1]

0x01F

Bit[0] Required by IEEE Std. 1149.1.

0x1

JTAG ID 代码为 05B0_603F

44

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

复位控制器 (RSTC)

概述 基于上电复位单元的复位控制器 (RSTC) 处理系统的所有复位,而无需其它器件。它 可以给出上

一次复位源的信息。

复位控制器可以独立地、或同时驱动外部复位和外设及处理器复位。

掉电检测可以防止处理器进入不可预测的状态。

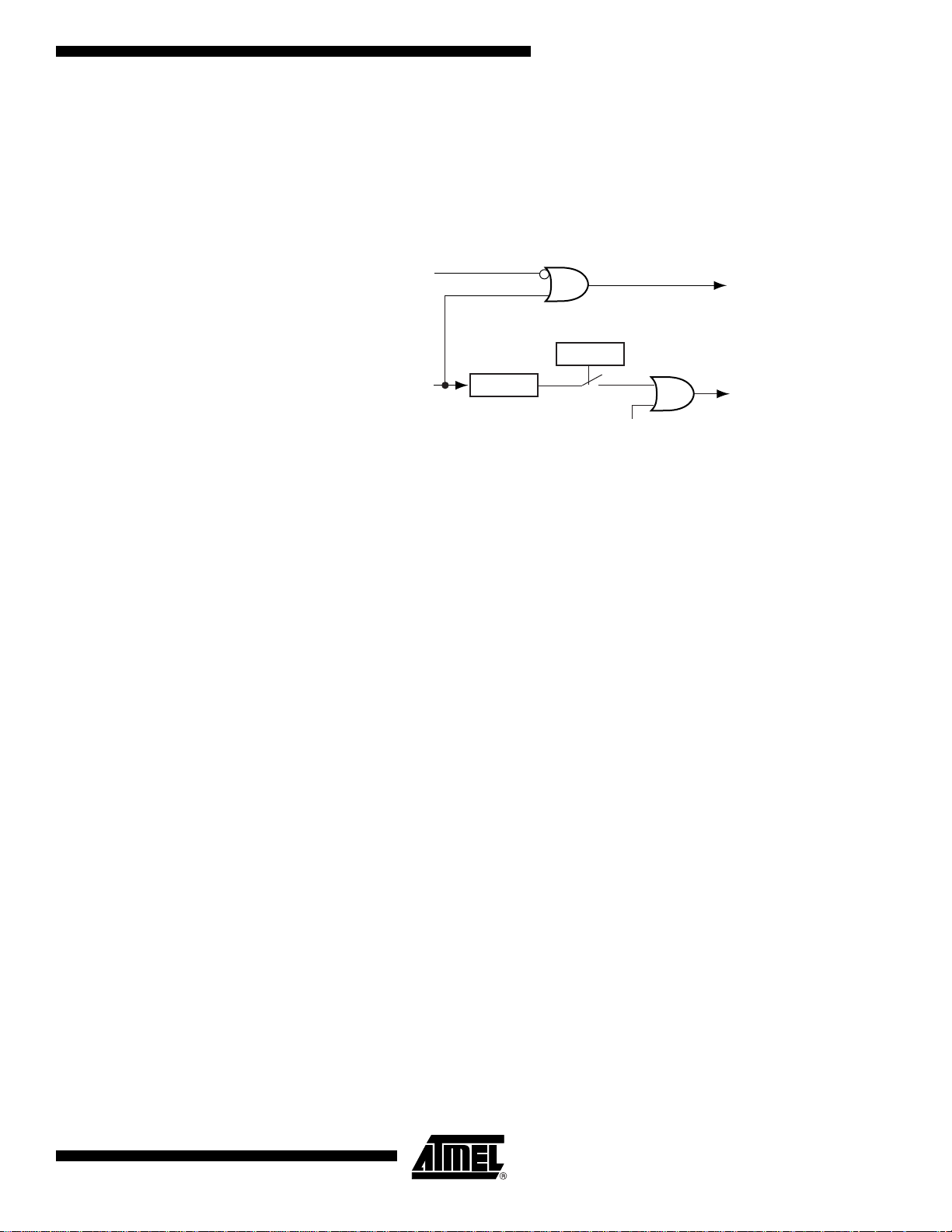

方框图

Figure 13. 复位控制器框图

Reset Controller

bod_rst_en

brown_out

Main Supply

POR

NRST

WDRPROC

wd_fault

nrst_out

Brownout

Manager

Startup

Counter

NRST

Manager

bod_reset

user_reset

exter_nreset

Reset

State

Manager

SLCK

rstc_irq

proc_nreset

periph_nreset

6070A–ATARM–07-Jun-05

45

功能说明 复位控制器由 NRST 管理器、掉电检测管理器、启动计数器和复位状态管理器组成。它运行于

慢速时钟,可以产生如下复位信号:

• proc_nreset:处理器复位。它同时也复位看门狗定时器。

• periph_nreset:作用于所有的外设。

•nrst_out:驱动 NRST 引脚。

这些复位信号由复位控制器或者基于外部事件,或者基于软件行为产生。复位状态管理器控制

着这些信号的产生,并在需要激活 NRST 引脚的时候为 NRST 管理器提供信号。

NRST 管理器控制 NRST 信号保持预先编好程的一段时间,从而控制外部器件的复位。

NRST 管理器 NRST 管理器对NRST 引脚的输入进行采样,并在复位状态管理器需要的时候将引脚电平拉低。

Figure 14 给出了 NRST 管理器的方框图。

Figure 14. NRST 管理器

RSTC_MR

RSTC_SR

URSTS

NRSTL

RSTC_MR

URSTEN

URSTIEN

rstc_irq

Other

interrupt

sources

NRST

nrst_out

RSTC_MR

ERSTL

External Reset Timer

user_reset

exter_nreset

NRST 信号或中断

NRST 管理器以低速时钟对 NRST引脚信号进行采样。当检测到信号为低时,用户复位的信号将

报告给复位状态管理器。

此外,通过编程还可以使 NRST 管理器在 NRST 为低时并不触发复位。这 可以通过将RSTC_MR

寄存器的 URSTEN 位清零来实现。

引脚 NRST 的电平可以在任何时候通过读取寄存器 RSTC_SR 的 NRSTL 来了解。一旦 NRST

上施加了有效信号,寄存器 RSTC_SR 的位 URSTS 置位。只有读取 RSTC_SR 之后这一位才

清零。

通过编程

还可以使复位控制器产生中断,而不是复位。方法就是置位 RSTC_MR 寄存器的

URSTIEN。

NRST 外部复位控制 复位状态管理器产生 ext_nreset 信号来拉低 NRST 引脚。同时, “nrst_out” 信号被 NRST 管理

器拉低,并持续由 RSTC_MR 寄 存器的 ERSTL 域 控制的一段 时间。这段 名 为

EXTERNAL_RESET_LENGTH的时间持续2

(ERSTL+1)

个慢速时钟周期。所 以其时间范围为60 µs

到 2 秒。 ERSTL 为 0 时 NRST 脉冲持续两个时钟周期。

这个特性使得复位控制器可以塑造 NRST 引脚的电平,从而保证 NRST 低电平持续时间满足连

接到系统复位的外部器件的复位要求。

掉电检测管理器 掉电检测可以防止处理器在电源下降到某个特定电平之后进入不可预测的状态。当 VDDCORE

低于掉电检测门限时,掉电检测管理器通过激活 bod_reset 信号来请求掉电检测复位。

46

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

程序员可以通过拉低 bod_rst_en 信号的方法来禁止掉电检测复位,即锁定 Flash 中对应的通用

NVM位。然后掉电检测复位就不会再发生了。此 时可以通过 寄存器RSTC_SR的位BODSTS 来

查看是否发生了掉电检测。 BODSTS 置位后只能通过读取 RSTC_SR 来清除。

若寄存器 RSTC_MR 的 BODIEN 置位,则 BODSTS 可以触发中断。

芯片出厂时掉电检测复位是禁止的。

Figure 15. 掉电检测管理器

bod_rst_en

brown_out

RSTC_SR

BODSTS

RSTC_MR

BODIEN

Other

interrupt

sources

bod_reset

rstc_irq

6070A–ATARM–07-Jun-05

47

复位状态 复位状态管理器处理不同的复位源,并产生内部复位信号。它通过状态寄存器 RSTC_SR 的

RSTTYP 域来报告复位状态。处理器复位释放后 RSTTYP 即得以更新。

上电复位 VDDCORE 上电后,主电源 POR 单元输出被运行于慢速时钟的启动计数器所过滤。这个计数器

的目的是保证启动芯片之前慢速时钟振荡器先稳定下来。

Figure 16 所示的启动时间是硬件决定的,并与慢速时钟振荡器的启动时间兼容。经过启动时间

之后,复位信号被释放, RSTC_SR 寄存器的 RSTTYP 得以更新,指明发生了上电复位。

当主电源 POR 单元检测到 VDDCORE 为低时,所有的复位信号立即生效。

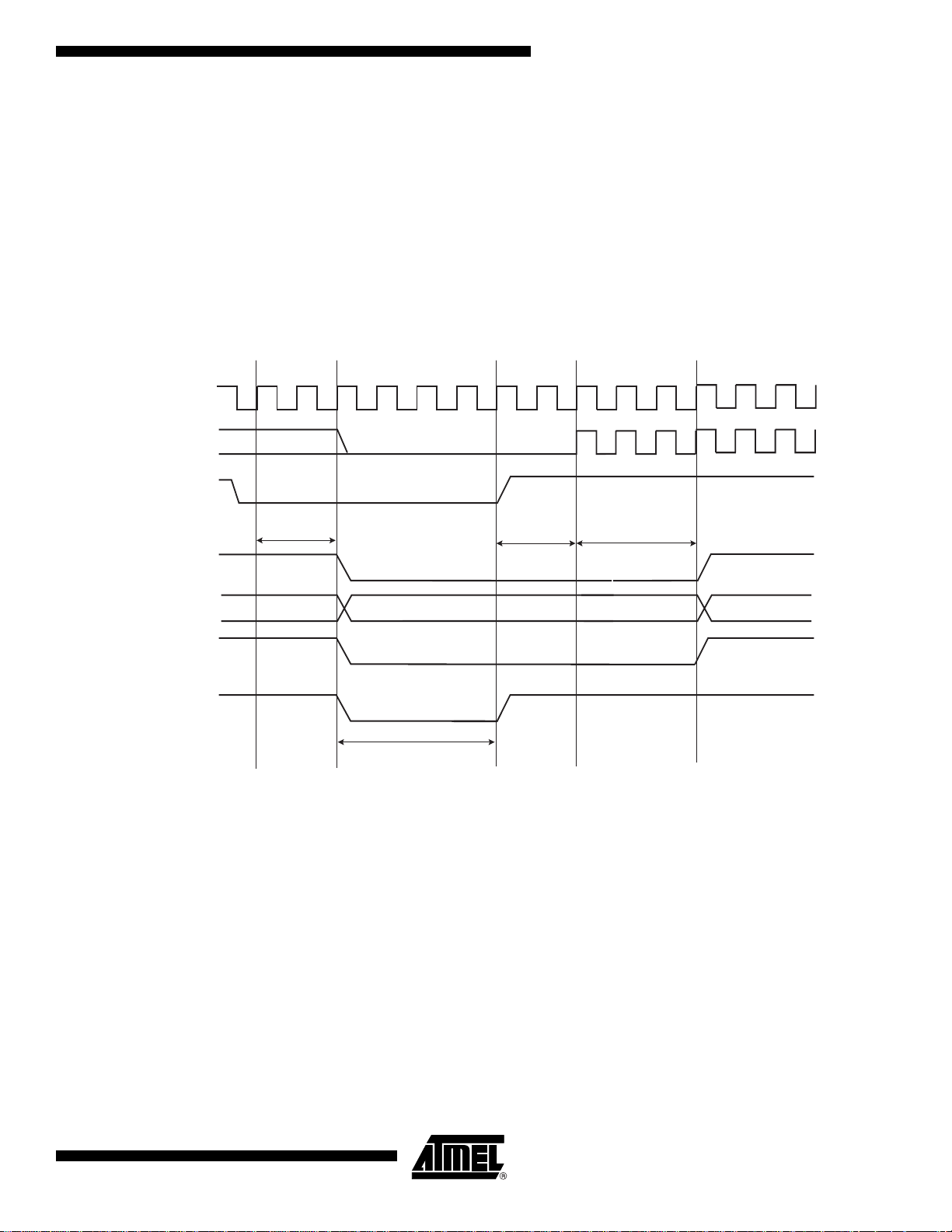

Figure 16.

上电复位

SLCK

MCK

Main Supply

POR output

proc_nreset

periph_nreset

NRST

(nrst_out)

Startup Time

Processor Startup

= 3 cycles

EXTERNAL RESET LENGTH

= 2 cycles

Any

Freq.

48

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

用户复位 当 NRST 引脚电平为低,且寄存器 RSTC_MR 的 URSTEN 为 1 时即进入用户复位。 NRST 输

入信号被同步到 SLCK 以保证系统的正确运行。

一旦检测到 NRST 为低电平,系统即进入用户复位。同时还引发处理器复位和外设复位。

NRST 电平拉高后,经过两个周期的重新同步时间和三个周期的处理器启动时间,处理器即退出

用户复位。一旦 NRST 为高,处理器时钟即重新使能。

处理器复位信号释放之后,状态寄存器的 RSTTYP 域即更新为 0x4,表示发生了用户复位。

NRST 管理器保证 NRST 信号持续 EXTERNAL_RESET_LENGTH 个慢速时钟周期,正如域

ERSTL 编程的那样

部复位将保持有效直到 NRST 变高。

Figure 17. 用户复位状态

SLCK

。然而,如果由于被外部电路拉低而使得 NRST 并没有在预定时间变高,内

MCK

NRST

proc_nreset

RSTTYP

periph_nreset

NRST

(nrst_out)

Any

Freq.

Resynch.

2 cycles

Any XXX

>= EXTERNAL RESET LENGTH

Resynch.

2 cycles

Processor Startup

= 3 cycles

0x4 = User Reset

6070A–ATARM–07-Jun-05

49

掉电检测复位 brown_out/bod_reset 信号有效时,复位状态管理器立即进入掉电检测复位。处理器复位、外设

复位和外部复位信号同时生效。

brown_out/bod_reset 变高后,经过两个周期的重新同步时间和额外的 3 个慢速时钟周期,处理

器退出掉电检测复位。同时外部复位被触发。

处理器复位释放之后, RSTC_SR 寄存器的 RSTTYP 更新为 0x5,表明发生了掉电检测复位。

Figure 18. 掉电检测复位状态

SLCK

MCK

brown_out

or bod_reset

proc_nreset

RSTTYP

periph_nreset

NRST

(nrst_out)

Any

Freq.

Any

Resynch.

2 cycles

XXX

Processor Startup

= 3 cycles

0x5 = Brownout Reset

EXTERNAL RESET LENGTH

8 cycles (ERSTL=2)

50

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

软件复位 复位控制器提供了几 个命令来激活不 同的复位信号。执行这些命令只需要将控制寄存器

RSTC_CR 的如下控制位写 1:

• PROCRST:置 1 将复位处理器和看门狗

• PERRST:置 1 将复位所有的外设,包括存储器系统,特别是重映像 (Remap) 命令。外设复

位一般用于调试的目的。

• EXTRST:置 1将拉低 NRST 引脚,并保持由模式寄存器RSTC_MR的 ERSTL 域定义的一段

时间。

一旦软件设置了上述的某一位或某几位,处理器即进入软件复位。所 有这些命令可以单独执行,

也可以同时执行。软件复位持续 3 个慢速时钟周期。

Figure 19. 软件复位

一旦执行了控制寄存器写操作,内部各个复位信号立即

生产。这可以通过主时钟 (MCK) 检测出

来:处理器退出软件复位时这些复位信号即被释放,亦即它们都同步于 SLCK。

如果 EXTRST 置 1, nrst_out 信号是否有效还取决于 ERSTL 的设置。然而 NRST 的下降沿并

不会导致用户复位。

若仅有 PROCRST 置位,复位控制器将通过状态寄存器 RSTC_SR 的 RSTTYP 域报告软件复

位。 RSTTYP 不报告其它的软件复位。

一旦发生了 软件复位,状态寄存器 RSTC_SR 的位 SRCMP (Software Reset Command in

Progress- 正在执行软件复位命令 )即置位。处理器退出软件复位后它

即被清零。SRCMP 置位后

无法执行其它软件复位,对 RSTC_CR 的写操作也没有任何效果。

SLCK

MCK

Write RSTC_CR

proc_nreset

if PROCRST=1

RSTTYP

Any

Freq.

Any

Resynch.

1 cycle

Processor Startup

= 3 cycles

XXX

0x3 = Software Reset

6070A–ATARM–07-Jun-05

periph_nreset

if PERRST=1

NRST

(nrst_out)

if EXTRST=1

SRCMP in RSTC_SR

EXTERNAL RESET LENGTH

8 cycles (ERSTL=2)

51

看门狗复位 看门狗错误发生时引发看门狗复位。这个状态将持续 3 个慢速时钟周期。

看门狗复位时,内部各个复位信号的产生取决于 WDT_MR 寄存器的位 WDRPROC:

• 若 WDRPROC 为 0,处理器复位和外设复位信号有效。NRST 引脚也被拉低,持续时间与

ERSTL 有关。但是 NRST 引脚的低电平并不会引起用户复位。

• 若 WDRPROC = 1,则只有处理器复位有效。

看门狗定时器由 proc_nreset 信号复位。如果 WDRSTEN 置位,看门狗溢出总是会引起处理器

复位,因此看门狗定时器总是在看门狗复位之后复位。在缺省条件下看门狗是使能的,而且溢

出时间设置为最长。

Figure 20. 看门狗复位

Only if

WDRPROC = 0

寄存器WDT_MR的WDRSTEN清零时,看门狗错误(

SLCK

MCK

wd_fault

proc_nreset

RSTTYP

periph_nreset

NRST

(nrst_out)

Any

Freq.

Any

Processor Startup

= 3 cycles

XXX

EXTERNAL RESET LENGTH

8 cycles (ERSTL=2)

定时器溢出)对复位控制器没有任何影响。

0x2 = Watchdog Reset

52

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

复位状态优先级 复位状态管理器管理的复位源优先级以递减的方式排列如下:

• 上电复位

• 掉电检测复位

• 看门狗复位

• 软件复位

• 用户复位

特例则排列如下:

• 用户复位状态:

– 看门狗事件永远不会发生,因为看门狗定时器被 proc_nreset 信号复位了

– 软件复位不会发生,因为处理器复位已经被激活了

• 软件复位状态:

– 看门狗事件优先级高于当前状态

–NRST没有效用

• 看门狗复位状态:

– 处理器复位已经激活,所以不可能进行软件复位的编程

– 不能进入用户复位

复位控制器状态寄存 器

复位控制器状态寄存器 (RSTC_SR) 给出了如下几个状态域:

•RSTTYP:表明了上一次复位的复位源

•SRCMP:表明软件复位命令正在执行当中,不能够执行其它的软件复位。当前软件复位

结束后这一位自动清零。

•NRSTL:给出了在每一个主时钟 MCK 上升沿采样到的 NRST 引脚的电平

•URSTS:NRST 信号从高电平到低电平的变化将置位 RSTC_SR 寄存器的 URSTS。这 个电

平变换也是在主时钟 MCK 的上升沿采样到的 ( 参见 Figure 21)。如果用户复位已经被禁止

(URSTEN = 0),而且通过 RSTC_MR 寄存器的URSTIEN使能了中断,则 URSTS将触发中

断。读取状态寄存器 RSTC_SR 将复位 URSTS

•BODSTS:当掉电检测复位被禁止时 (bod_rst_en = 0) 这一位表示发生了掉电检测。如果

通过 RSTC_MR 寄存器的 URSTIEN 使能了中断则 BODSTS 将触发中断。读取状态寄存

器 RSTC_SR 将复位 BODSTS 并清除中断。

Figure 21. 复位控制器状态和中断

MCK

Peripheral Access

2 cycle

resynchronization

NRST

并清除中断。

read

RSTC_SR

2 cycle

resynchronization

if (URSTEN = 0) and

(URSTIEN = 1)

6070A–ATARM–07-Jun-05

NRSTL

URSTS

rstc_irq

53

复位控制器 (RSTC) 用户接口

Table 11. 复位控制器寄存器

地址偏移 寄存器 名称 访问类型 复位值

0x00 控制寄存器 RSTC_CR 只写 -

0x04 状态寄存器 RSTC_SR 只读 0x0000_0000

0x08 模式寄存器 RSTC_MR 读 / 写 0x0000_0000

54

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

复位控制器控制寄存器

寄存器名称 : RSTC_CR

访问类型 : 只写

31 30 29 28 27 26 25 24

KEY

23 22 21 20 19 18 17 16

––––––––

15 14 13 12 11 10 9 8

–––––– –

76543210

––––EXTRSTPERRST–PROCRST

• PROCRST: 处理器复位

0 = 无效。

1 = 若 KEY 是正确的,则复位处理器。

• PERRST: 外设复位

0 = 无效。

1 = 若 KEY 是正确的,则复位所有外设。

• EXTRST: 外部复位

0 = 无效。

1 = 若 KEY 是正确的,则拉低 NRST 引脚。

•KEY: 预设值

0xA5。写入其它任何数值都将使本次写操作失败。

6070A–ATARM–07-Jun-05

55

复位控制器状态寄存器

寄存器名称 : RSTC_SR

访问类型 : 只读

31 30 29 28 27 26 25 24

––––––––

23 22 21 20 19 18 17 16

––––––SRCMPNRSTL

15 14 13 12 11 10 9 8

––––– RSTTYP

76543210

––––––BODSTSURSTS

• URSTS: 用户复位状态

0 = 自上次读取 RSTC_SR 以来 NRST 引脚上没有发生从高电平到低电平的转换。

1 = 自上次读取 RSTC_SR 以来 NRST 引脚上至少检测到一次从高电平到低电平的转换。

• BODSTS: 掉电检测状态

0 = 自上次读取 RSTC_SR 以来没有发生掉电检测。

1 = 自上次读取 RSTC_SR 以来已经发生过掉电检测。

• RSTTYP: 复位类型

报告上一次处理器复位的原因。读取 RSTC_SR 不会影响它的数值。

RSTTYP 复位类型 说明

000上电复位 VDDCORE 上升

010看门狗复位 发生了看门狗错误 ( 定时器溢出 )

011软件复位 软件要求的处理器复位

100用户复位 NRST 引脚检测为低

101掉电检测复位 发生了掉电检测复位

• NRSTL: NRST 引脚电平

记录了主时钟 MCK 上升沿时刻的 NRST 引脚电平。

•SRCMP: 软件复位命令执行中

0 = 复位控制器没有在执行软件复位命令。

复位控制器可以执行软件复位命令了。

1 = 复位控制器正在执行软件复位命令。复位控制器忙。

56

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

复位控制器模式寄存器

寄存器名称 : RSTC_MR

访问类型 : 读 / 写

31 30 29 28 27 26 25 24

KEY

23 22 21 20 19 18 17 16

–––––––BODIEN

15 14 13 12 11 10 9 8

–––– ERSTL

76543210

– – URSTIEN – – – URSTEN

• URSTEN: 用户复位使能

0 = 检测到 NRST 引脚为低电平不产生用户复位。

1 = 检测到 NRST 引脚为低电平产生用户复位。

• URSTIEN: 用户复位中断使能

0 = 寄存器 RSTC_SR 的位 USRTS 为 1 时对 rstc_irq 没有作用。

1 = 若 URSTEN = 0 则寄存器 RSTC_SR 的位 USRTS 为 1 时触发 rstc_irq。

•BODIEN: 掉电检测中断使能

0 = 寄存器 RSTC_SR 的位 BODSTS 为 1 时对 rstc_irq 没有作用。

1 = 寄存器 RSTC_SR 的位 BODSTS 为 1 时触发 rstc_irq。

• ERSTL: 外部复位持续时间

这个

域定义了外部复位的持续时间。外部复位一直持续 2

•KEY: 预设值

0xA5。写入其它任何数值都将使本次写操作失败。

(ERSTL+1)

个慢速时钟周期。时间范围为 60 µs 到 2 秒。

6070A–ATARM–07-Jun-05

57

58

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

实时定时器 (RTT)

概述 实时定时器基于一个 32 位的计数器,用来记录经过的秒数。它可以产生周期性的中断或 / 和基

于一个预选编好程的数值触发闹铃。

方框图

Figure 22. 实时定时器

SLCK

RTT_MR

RTTRST

reload

16-bit

Divider

RTT_MR

RTPRES

RTT_MR

RTTRST

0

10

RTT_SR

RTT_MR

RTTINCIEN

set

RTTINC

reset

RTT_VR

RTT_AR

32-bit

Counter

CRTV

ALMV

RTT_SR

RTT_SR

=

read

reset

set

rtt_int

RTT_MR

ALMIEN

ALMS

rtt_alarm

6070A–ATARM–07-Jun-05

59

功能描述

实时定时器用来记录经历的秒数。它基于 32 位的计数器。而这个计数器的时钟来源为慢速 时

钟,并经过 16 位数值的预分频。这个数值要写入实时模式寄存器 RTT_MR 的 RTPRES 域。

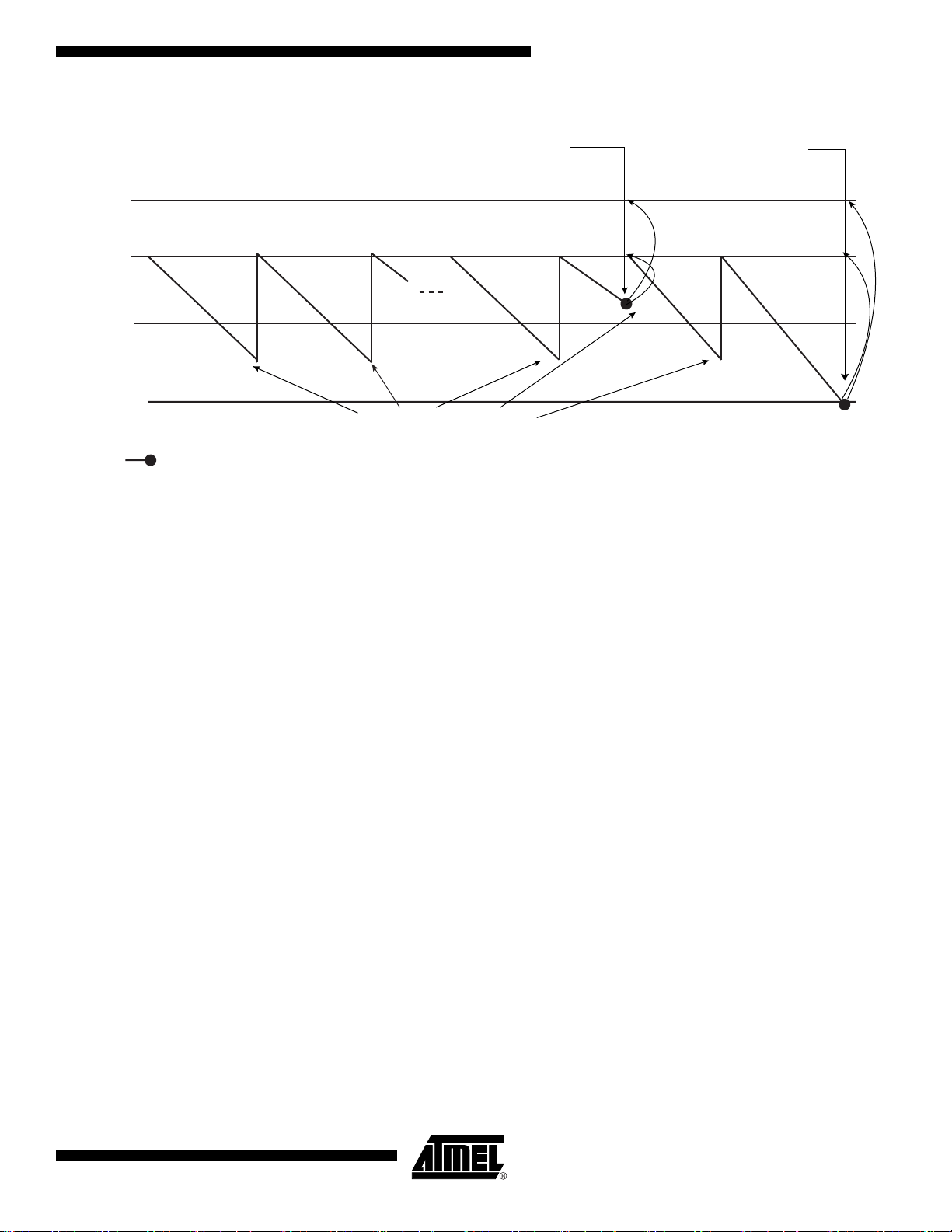

Figure 23. RTT 计数

将 RTPRES 设置为 0x00008000 相当于给实时计数器提供 1Hz 的时钟信号 ( 如果慢速时钟为

32.768 Hz)。 32 位的计数器可以计 2

32

秒,相当于 136 年,然后计数器数值恢复为 0。

实时定时器也可以用做自由运行的基于慢速时钟的定时器。获得最佳精度的方法是将 RTPRES

设置为 1。此时提供给实时计数器的时钟信号的周期为 30.52 µs ( 慢速时钟为 32.768 Hz 时 )。

实时定时器可以应付 131072 秒,相当于 36 天。

可以在任何时候通过读取寄存器 RTT_VR 来获得实时定时器的数值 (CRTV)。因为这个数值由

主时钟进行异步更新,所以建议在读取的时候连续读两次,以解决数值归零可能带来的问题。

计数器的当前值与写入闹铃寄存器 RTT_AR ( 实时

闹铃寄存器 ) 的数值进行比较。两个数值相等

将置位寄存器 RTT_SR 的 ALMS。复位时闹铃寄存器的数值设置为最大值 0xFFFF_FFFF。

每一次实时定时器计数器数值增加时 RTT_SR 寄存器的位 RTTINC 即置位。这一位可以用来产

生周期性中断。当 RTPRES 编程为 0x8000,且慢速时钟等于 32.768 Hz 时周期为一秒。

读取状态寄存器 RTT_SR 将复位 RTTINC 和 ALMS。

执行对寄存器 RTT_MR 的位 RTTRST 的写操作将立即使 RTT 重新加载及启动时钟分频器。这

个操作同时也复位 32 位的计数器。

APB cycle

MCK

APB cycle

RTPRES - 1

Prescaler

RTT

RTTINC (RTT_SR)

ALMS (RTT_SR)

APB Interface

0

...

ALMVALMV-10 ALMV+1

read RTT_SR

ALMV+2 ALMV+3

60

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

实时定时器 (RTT) 用户接口

Table 12. 实时定时器寄存器映射

地址偏移 寄存器 名称 访问类型 复位值

0x00 模式寄存器 RTT_MR 读 / 写 0x0000_8000

0x04 闹铃寄存器 RTT_AR 读 / 写 0xFFFF_FFFF

0x08 数值寄存器 RTT_VR 只读 0x0000_0000

0x0C 状态寄存器 RTT_SR 只读 0x0000_0000

6070A–ATARM–07-Jun-05

61

实时定时器模式寄存器

寄存器名称 : RTT_MR

访问类型 : 读 / 写

31 30 29 28 27 26 25 24

––––––––

23 22 21 20 19 18 17 16

–––––RTTRSTRTTINCIENALMIEN

15 14 13 12 11 10 9 8

RTPRES

76543210

RTPRES

• RTPRES: 实时定时器预分频数值

定义使实时定时器加一的 SLCK 个数。

RTPRES = 0:预分频值为 2

RTPRES ≠ 0:预分频值为 RTPRES。

•ALMIEN: 中断使能

0 = RTT_SR 寄存器的 ALMS 对中断不起作用。

1 = ALMS 将引发中断。

• RTTINCIEN: 实时定时器增一中断使能

0 = RTT_SR 寄存器的 RTTINC 对中断不起作用。

1 = RTTINC 将引发中断。

•RTTRST: 实时定时器重新启动

1 = 重新加载及重新启动时钟分频器。此操作同时复位 32 位的计数器。

16

。

62

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

实时定时器闹铃寄存器

寄存器名称 : RTT_AR

访问类型 : 读 / 写

31 30 29 28 27 26 25 24

ALMV

23 22 21 20 19 18 17 16

ALMV

15 14 13 12 11 10 9 8

ALMV

76543210

ALMV

•ALMV: 闹铃值

定义了与实时定时器进行比较的数值, (ALMV+1)。

6070A–ATARM–07-Jun-05

63

实时定时器数值寄存器

寄存器名称 : RTT_VR

访问类型 : 只读

31 30 29 28 27 26 25 24

CRTV

23 22 21 20 19 18 17 16

CRTV

15 14 13 12 11 10 9 8

CRTV

76543210

CRTV

•CRTV: 当前实时数值

返回实时定时器的当前数值。

64

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

实时定时器状态寄存器

寄存器名称 : RTT_SR

访问类型 : 只读

31 30 29 28 27 26 25 24

––––––––

23 22 21 20 19 18 17 16

––––––––

15 14 13 12 11 10 9 8

––––––––

76543210

––––––RTTINCALMS

•ALMS: 实时状态

0 = 自上一次读取寄存器 RTT_SR 之后实时没有发生过。

1 = 自上一次读取寄存器 RTT_SR 之后发生了实时。

• RTTINC: 实时定时器增加

0 = 自上一次读取寄存器 RTT_SR 之后实时定时器没有增加。

1 = 自上一次读取寄存器 RTT_SR 之后实时定时器增加了。

6070A–ATARM–07-Jun-05

65

66

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

周期性间隔定时器 (PIT)

概述 周期性间隔定时器 (PIT) 为操作系统的调度程序提供时间间隔中断。这 个定时器设计的目的是提

供最大的精确度和高效率的管理,即使对要求长响应时间的系统也是如此。

方框图

Figure 24. 周期性间隔定时器

PIT_MR

PIV

MCK

Prescaler

MCK/16

= ?

0

0

1

0

20-bit

Counter

CPIV

CPIV PICNT

PIT_PIVR

PIT_PIIR

12-bit

Adder

PICNT

PIT_MR

PITIEN

set

PIT_SR

10

PITS

reset

read PIT_PIVR

pit_irq

6070A–ATARM–07-Jun-05

67

功能说明

周期性间隔定时器的目的是为操作系统提供周期性的中断。

PIT 有一个可编程的溢出计数器和读后即复位的特性。它 基 于两个计数器:一个 20 位的 CPIV 计

数器和一个 12 位的 PICNT 计数器。两个计数器的时钟都是主时钟的 1/16。

20位的CPIV计数器从0开始计数,直到模式寄存器 PIT_MR的PIV域定义的溢出数值为止。CPIV

计到这个数值后即复位为 0,同时周期性间隔计数器 PICNT 加一。然后状态寄存器 PIT_SR 的

位 PITS 置位并触发中断,只要此时中断是使能的 (PIT_MR 的位 PITIEN)。

将新的数值赋予给寄存器 PIT_MR 的 PIV 域不会复位

通过读取周期性间隔数值寄存器PIT_PIVR获得CPIV和PICNT的数值之后,溢出计数器(PICNT)

复位, PITS 清零, 从而确认中断。 PICNT 的数值表示自上一次读取 PIT_PIVR 之后发生的周

期性间隔次数。

通过读取周期性间隔映像寄存器 PIT_PIIR 获得 CPIV 和 PICNT 的数值对计数器的 CPIV 和

PICNT,以 及 PITS 没有影响。例 如 ,软 件 剖析工具可以读取 PIT_PIIR 而不会清除任何已经发生

但还未处理的中断,而定时器中断通过读 PIT_PIVR 清除中断。

通过寄存器 PIT_MR 的 PITEN 位可以使能 / 禁止 PIT( 复位时处于禁止状态 )。只有在 CPIV 为

0 时操作 PITEN

CPIV 继续计数,直到达到 PIV 的数值,然后再复位。 PITEN 置位后 PIT 才能重新开始计数。

在内核进入调试状态时 PIT 停止。

Figure 25. 利用 PITEN 使能 / 禁用 PIT

15

MCK Prescaler

0

/ 重启动计数器。

才有作用。Figure 25 演示了 PIT 的计数方式。PIT 使能位复位后 (PITEN= 0),

APB cycle

MCK

APB cycle

restarts MCK Prescaler

68

PITEN

CPIV

PICNT

PITS (PIT_SR)

APB Interface

10

0

PIVPIV - 10

AT91SAM7S64 Preliminary

1

read PIT_PIVR

1

0

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

周期性间隔定时器 (PIT) 用户接口

Table 13. 周期性间隔定时器 (PIT) 寄存器映射

地址偏移 寄存器 名称 访问类型 复位值

0x00 模式寄存器 PIT_MR 读 / 写 0x000F_FFFF

0x04 状态寄存器 PIT_SR 只读 0x0000_0000

0x08 周期性间隔数值寄存器 PIT_PIVR 只读 0x0000_0000

0x0C 周期性间隔映像寄存器 PIT_PIIR 只读 0x0000_0000

6070A–ATARM–07-Jun-05

69

周期性间隔定时器模式寄存器

寄存器名称 : PIT_MR

访问类型 : 读 / 写

31 30 29 28 27 26 25 24

––––––PITIENPITEN

23 22 21 20 19 18 17 16

–––– PIV

15 14 13 12 11 10 9 8

PIV

76543210

PIV

•PIV: 周期性间隔数值

定义了与周期性间隔寄存器 20 位计数器 CPIV 比较的数值。周期等于 PIV + 1。

•PITEN: 使能周期性间隔定时器

0 = 计数值达到 PIV 后周期性间隔寄存器被禁用。

1 = 周期性间隔寄存器使能。

• PITIEN: 使能周期性间隔定时器中断

0 = PIT_SR 寄存器的 PITS 对中断没有影响。

1 = PIT_SR 寄存器的 PITS 可以触发中断。

70

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

周期性间隔定时器状态寄存器

寄存器名称 : PIT_SR

访问类型 : 只读

31 30 29 28 27 26 25 24

––––––––

23 22 21 20 19 18 17 16

––––––––

15 14 13 12 11 10 9 8

––––––––

76543210

–––––––PITS

•PITS: 周期性间隔定时器状态

0 = 自上次读取 PIT_PIVR 之后周期性间隔定时器还没有计数到 PIV。

1 = 自上次读取 PIT_PIVR 之后周期性间隔定时器已经计数到 PIV。

6070A–ATARM–07-Jun-05

71

周期性间隔定时器数值寄存器

寄存器名称 : PIT_PIVR

访问类型 : 只读

31 30 29 28 27 26 25 24

PICNT

23 22 21 20 19 18 17 16

PICNT CPIV

15 14 13 12 11 10 9 8

CPIV

76543210

CPIV

读取该寄存器将清除寄存器 PIT_SR 的 PITS。

•CPIV: 当前周期性间隔数值

返回周期性间隔定时器的当前数值。

•PICNT: 周期性间隔计数器

返回自上一次读取 PIT_PIVR 之后发生的周期性间隔次数。

72

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

周期性间隔定时器映像寄存器

寄存器名称 : PIT_PIIR

访问类型 : 只读

31 30 29 28 27 26 25 24

PICNT

23 22 21 20 19 18 17 16

PICNT CPIV

15 14 13 12 11 10 9 8

CPIV

76543210

CPIV

•CPIV: 当前周期性间隔数值

返回周期性间隔定时器的当前数值。

•PICNT: 周期性间隔计数器

返回自上一次读取 PIT_PIVR 之后发生的周期性间隔次数。

6070A–ATARM–07-Jun-05

73

74

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

看门狗定时器 (WDT)

概述 看门狗定时器可以用来防止由于软件陷于死循环而导致的系统死锁。它 具有一个 12 位的向下计

数器,使得看门狗周期可以达到 16 秒 ( 慢速时钟, 32.768 kHz)。它可以产生通常的复位,或

者仅仅是处理器复位。此外,当处理器处于调试模式或空闲模式时看门狗可以被禁止。

方框图

Figure 26. 看门狗定时器框图

WDT_CR

WDRSTT

read WDT_SR

or

reset

write WDT_MR

WDT_MR

WDD

<= WDD

WDERR

set

reset

reload

WDT_MR

WV

10

12-bit Down

Counter

Current

Value

=

WDUNF

0

set

reset

reload

1/128

SLCK

WDT_MR

WDRSTEN

WDFIEN

WDT_MR

wdt_fault

(to Reset Controlle

wdt_int

r)

6070A–ATARM–07-Jun-05

75

功能描述 看门狗定时器可以用来防止由于软件陷于死循环而导致的系统死锁。它的电源是 VDDCORE。

处理器复位后它从初始值重新开始启动。

看门狗基于一个 12 位的向下计数器,加载的数据可以通过模式寄存器 WDT_MR 的 WV 域来定

义。如果使用经过 128 分频的慢速时钟来驱动看门狗定时器,溢出周期达到最大值 16 秒 ( 慢速

时钟的典型值为 32.768 kHz)。

处理器复位之后, WV 的数值为 0xFFF,对应于计数器的最大值,并使能了外部复位 (Backup

复位时 WDRSTEN 为 1)。也就是说,复位之后看门狗就运行了。如果用户程序没有使用看门

狗,则必须禁止它 ( 置位 WDT_MR

求。

看门狗模式寄存器 (WDT_MR) 只能写一次。只有处理器复位才可以复位它。对 WDT_MR 执行

写操作可以把最后编程的模式参数加载到定时器。

在普通的操作中,用户需要通过置位控制寄存器 WDT_CR 的位 WDRSTT 来定时地重新加载看

门狗,以防止定时器溢出。计数器将立即由 WDT_MR 重新加载并重新启动,慢速时钟的 128

分频器也被复位及重新启动。 WDT_CR 是写保护的。因此,如果预设值不正确,对 WDT_CR

的写操作是没有作用的。如果发生了计数器溢出,并

1,则连接到复位控制器的“wdt_fault” 信号生效,看门狗状态寄存器 WDT_SR的位WDUNF也被

设置为 1。

为了防止软件死锁时持续不断地触发看门狗,看门狗的重新加载必须在由 0和WDT_MR的WDD

定义的时间窗之内发生:

0 ≤ WDT ≤ WDD:执行对 WDRSTT 的写操作将使看门狗定时器重新启动。

任何在 [WDV:WDD] 之间重新启动看门狗定时器的企图都将导致看门狗错误,即使此时看门狗

时禁止的:WDT_SR 的位 WDERR 置位,连接到复位控制器的 “wdt_fault” 信号生效。

寄存器的位 WDDIS),否则必须对它进行编程以满足应用要

且模式寄存器 WDT_MR 的 WDRSTEN 为

要注意的

[0:WDV] 的整个区间都可以重新启动而不产生错误。这也是芯片复位时的缺省配置 (WDD 与

WDV 的数值时相等的 )。

若模式寄存器的 WDFIEN 为 1,状 态 位 WDUNF ( 看门狗溢出 ) 和 WDERR ( 看门狗错误 ) 置位

将触发中断。如果 WDRSTEN 同时也为 1,则连接到复位控制器的 “wdt_fault” 信号将引起看门

狗复位。在这种情况下,处理器和看门狗定时器复位, WDERR 及 WDUNF 标志被清零。

如果复位已经产生,或是读访问了寄存器 WDT_SR,则状态位

位控制器的 “wdt_fault” 信号不再有效。

执行对 WDT_MR 的写操作将重新加载向下计数器,并使其重新启动。

当处理器处于调试状态或空闲模式时,根据寄存器 WDT_MR 的 WDIDLEHLT 和 WDDBGHLT

的设置,计数器可以被停止。

是,当 WDD 等于或大于 WDV 时,这个特性即被禁止。这个配置允许看门狗定时器在

被清零,中断被清除,输送到复

76

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

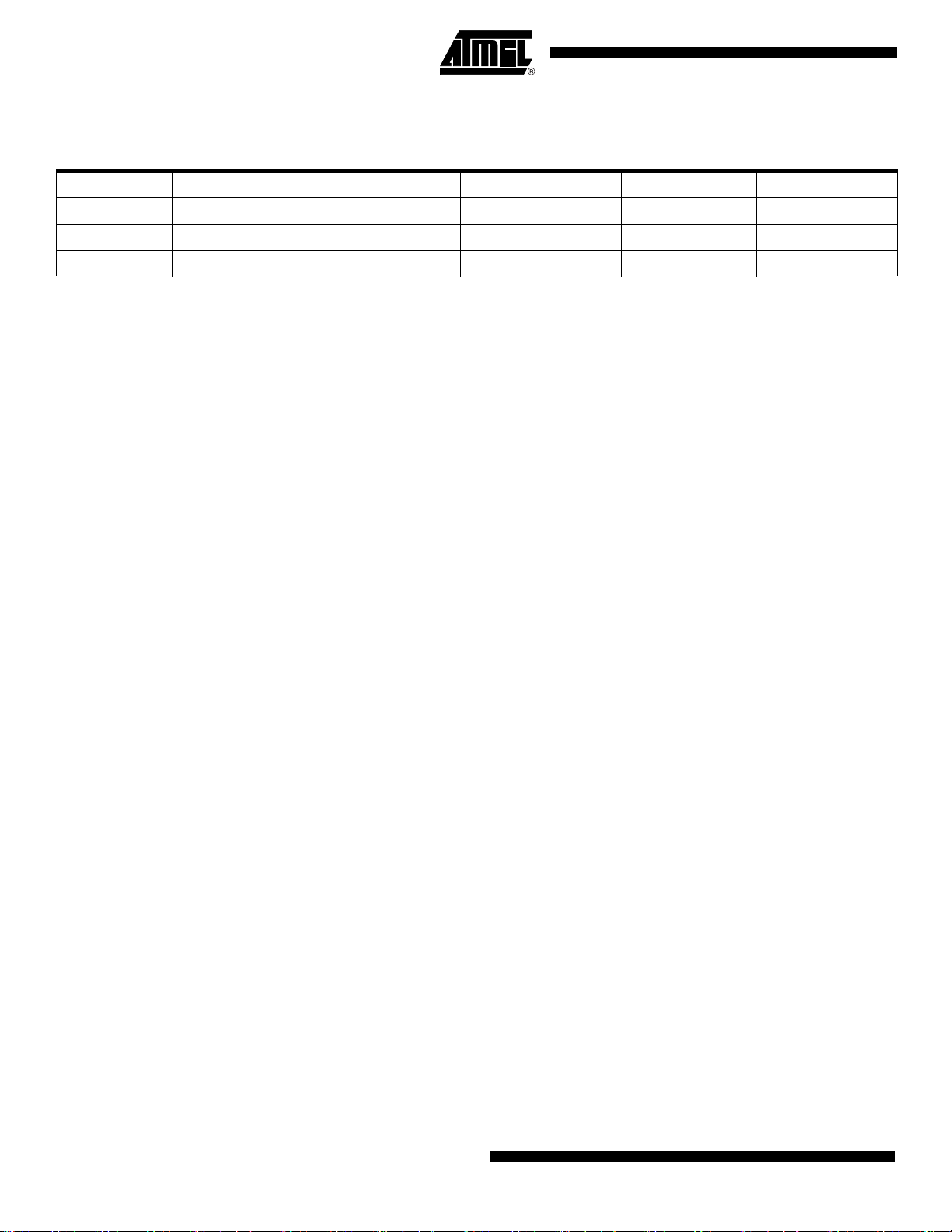

Figure 27. 看门狗的工作行为

AT91SAM7S64 Preliminary

Watchdog Error

Watchdog Underflow

FFF

WDV

Forbidden

Window

WDD

Permitted

Window

0

Watchdog

Fault

Normal behavior

if WDRSTEN is 1

if WDRSTEN is 0

WDT_CR = WDRSTT

6070A–ATARM–07-Jun-05

77

看门狗定时器 (WDT) 用户接口

Table 14. 看门狗定时器 (WDT) 寄存器映射

地址偏移 寄存器 名称 访问类型 复位值

0x00 控制寄存器 WDT_CR 只写 -

0x04 模式寄存器 WDT_MR 读 / 写,一次 0x3FFF_2FFF

0x08 状态寄存器 WDT_SR 只读 0x0000_0000

78

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

看门狗定时器控制寄存器

寄存器名称 : WDT_CR

访问类型 : 只写

31 30 29 28 27 26 25 24

23 22 21 20 19 18 17 16

––––––––

15 14 13 12 11 10 9 8

––––––––

76543210

–––––––WDRSTT

•WDRSTT: 看门狗重新启动

0:无效。

1:重新启动看门狗。

•KEY: 预设值

0xA5。写入其它任何数值都将使本次写操作失败。

KEY

6070A–ATARM–07-Jun-05

79

看门狗定时器模式寄存器

寄存器名称 : WDT_MR

访问类型 : 读 / 写,一次

31 30 29 28 27 26 25 24

WDIDLEHLT WDDBGHLT WDD

23 22 21 20 19 18 17 16

WDD

15 14 13 12 11 10 9 8

WDDIS

76543210

•WDV: 看门狗计数器的数值

定义了加载到 12 位看门狗计数器的数值。

• WDFIEN: 使能看门狗故障中断

0:看门狗故障 ( 溢出或错误 ) 对中断不产生影响。

1:看门狗故障 ( 溢出或错误 ) 将产生中断。

• WDRSTEN: 使能看门狗复位

0:看门狗故障 ( 溢出或错误 ) 对复位没有影响。

1:看门狗故障 ( 溢出或错误 ) 将引发看门狗复位。

•WDRPROC: 看门狗复位处理器

0:若 WDRSTEN 为 1,则看门狗故障 ( 溢出或错误 ) 将引发所有的复位。

1:若 WDRSTEN 为 1,则看门狗故障 ( 溢出或错误 ) 只引发处理器复位。

•WDD: 看门狗 Delta 数值

定义了重新加载看门狗定时器所允许的范围。

如果看门狗定时器的数值小于等于 WDD,置位 WDT_CR 的 WDRSTT 将使定时器重新启动。

如果看门狗定时器的数值大于 WDD,置位 WDT_CR 的 WDRSTT 将产生看门狗错误。

• WDDBGHLT: 看门狗调试停止

0:处理器处于调试状态时看门狗仍然运行。

1:处理器处于调试状态时看门狗停止。

• WDIDLEHLT: 看门狗空闲停止

0:系统处于空闲状态时看门狗仍然运行。

1:系统处于空闲状态时看门狗停止。

•WDDIS: 禁止看门狗

0:使能看门狗定时器。

1:禁止看门狗定时器。

WDRPROC WDRSTEN WDFIEN WDV

WDV

80

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

看门狗定时器状态寄存器

寄存器名称 : WDT_SR

访问类型 : 只读

31 30 29 28 27 26 25 24

––––––––

23 22 21 20 19 18 17 16

––––––––

15 14 13 12 11 10 9 8

––––––––

76543210

––––––WDERRWDUNF

• WDUNF: 看门狗溢出

0:自上一次读取 WDT_SR 之后没有发生看门狗溢出。

1:自上一次读取 WDT_SR 之后至少发生了一次看门狗溢出。

• WDERR: 看门狗错误

0:自上一次读取 WDT_SR 之后没有发生看门狗错误。

1:自上一次读取 WDT_SR 之后至少发生了一次看门狗错误。

6070A–ATARM–07-Jun-05

81

82

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

电压调节器模式控制器 (VREG)

概述 电压调节器模式控制器包括一个读 / 写寄存器 - 电压调节器模式寄存器。它 相对系统控制器的偏

移地址为 0x60。

这个寄存器控制着电压调节器的模式。置位 PSTDBY 将使电压调节器进入待机模式或低功耗模

式。一旦复位, PSTDBY 即清零,从而使电压调节器进入正常模式。

电压调节器电源控制器 (VREG) 用户接口

Table 15. 电压调节器电源控制器寄存器映射

地址偏移 寄存器 名称 访问类型 复位值

0x60 电压调节器模式寄存器 VREG_MR 读 / 写 0x0

电压调节器模式寄存器

寄存器名称 : VREG_MR

访问类型 : 读 / 写

31 30 29 28 27 26 25 24

––––––––

23 22 21 20 19 18 17 16

––––––––

15 14 13 12 11 10 9 8

––––––––

76543210

–––––––PSTDBY

• PSTDBY: 周期性间隔数值

0 = 普通模式。

1 = 待机模式 ( 低功耗模式 )。

6070A–ATARM–07-Jun-05

83

84

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

存储器控制器 (MC)

概述 存储器控制器 (MC) 管理 ASB 总线,并控制主机的访问请求。这里主机指的使 ARM7TDMI 处

理器以及外设数据控制器。它具有一个简单的总线仲裁器,地址译码器,异常中断状态,地址

未对齐检测器和嵌入式 Flash 控制器。

方框图

Figure 28. 存储器控制器框图

Memory Controller

ASB

ARM7TDMI

Processor

Peripheral

DMA

Controller

Abort

Bus

Arbiter

Abort

Status

Misalignment

Detector

User

Interface

Address

Decoder

APB

Bridge

Embedded

Flash

Controller

Internal

Flash

Internal

RAM

6070A–ATARM–07-Jun-05

Peripheral 0

Peripheral 1

Peripheral N

APB

From Master

to Slave

85

功能说明 存储器控制器处理 ASB 总线,并对主机的访问进行仲裁。

其组成部分为:

• 总线仲裁器

• 地址译码器

• 异常中断状态

• 地址未对齐检测器

• 嵌入式 Flash 控制器

MC 只能够处理 little-endian 模式的访问。主机也只能够工作于 little-endian 模式。

总线仲裁器 存储器控制器有一个简单的、硬连接优先级总线仲裁器,控制两个主机对总线的访问。外设数

据控制器的优先级比 ARM 处理器的要高。

地址译码器 存储器控制器的地址译码器首先对 32 位地址总线的高 4 位进行解码,并 定 义了 3 个不同的地址

范围:

•256M字节的内部存储器

• 为片内外设所保留的 256M 字节地址空间

• 未定义的 3584M 字节表现为 14 个 256M 字节的存储区。访问这个区域将导致异常中断

Figure 29 给出了 256M 字节存储区的分配情况。

Figure 29. 存储区

256M Bytes

0x0000 0000

0x0FFF FFFF

0x1000 0000

Internal Memories

86

14 x 256MBytes

3,584 Mbytes

256M Bytes

AT91SAM7S64 Preliminary

0xEFFF FFFF

0xF000 0000

0xFFFF FFFF

Undefined

(Abort)

Peripherals

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

片内存储器映射 在内部存储器地址空间里,地址 译码器将增加 8 个比特的译码,以 便为嵌入式存储器分配 1M 字

节的地址空间。

分配的存储器位于 1M 字节的地址空间,在这个访问空间里可能会重复 n 次, n 等于 1M 字节

除以存储器大小。

访问地址没有定义时,地址译码器将返回异常中断到主机。

Figure 30. 内部存储器映射

0x0000 0000

256M Bytes

0x000F FFFF

0x0010 0000

0x001F FFFF

0x0020 0000

0x002F FFFF

0x0030 0000

Internal Memory Area 0

Internal Memory Area 1

Internal Flash

Internal Memory Area 2

Internal SRAM

1M Bytes

1M Bytes

1M Bytes

Undefined Areas

(Abort)

0x0FFF FFFF

内部存储器 区域 0

内部存储器区域 0 的前 32 个字节包含了 ARM 处理器的例外向量,尤其是位于地址 0x0 的复位

向量。

执行

重映射 (remap) 命令之前,片内 Flash 映射于内部存储器区域 0,因此 ARM7TDMI 可以访

问到位于 Flash 的可执行指令。重映射之后,原来位于地址 0x0020 0000 的片内 SRAM 映射到

内部存储器区域 0。它同时还可以原来的地址进行访问。

重映射命令 重映射之后,片内 SRAM 可以通过 内部存储器区域 0 进行访问。

由于 ARM 向量 ( 复位,异常,数据异常,预取异常,未定义指令,中断和快速中断 ) 从地址 0x0

映射到地址 0x20,重映射命令允许用户通过软件动态地对这些向量重新进行定义。

重映射命令通过存储器控制器用户接口进行控制,方法是将寄存器 MC_RCR ( 重映射控制寄存

器 ) 的 RCB 置位。

再一次置位 MC_RCR 的 RCB 即取消重映射命令。这个功能可以将芯片置于与复位之后相同的

配置,从而简化用户自定义启动序列的调试。

253M bytes

6070A–ATARM–07-Jun-05

87

异常状态 异常发生的原因有三个:

• 访问未定义的地址

• 访问未对齐的地址

异常发生时,所有的主机都将接收到一个信号,不论是哪一个主机产生了这个访问。但是只有

ARM7TDMI 会处理此信号,而且是在这个访问由它自己产生的条件之下。外设数据控制器不处

理异常输入信号。 Figure 28 没有给出信号的连接关系。

为了便利操作系统的调试或错误分析,存储器控制器集成了异常状态寄存器集。

完整的 32 位异常地址保存于 MC_AASR,访问参数则保存于 MC_ASR,其内容有:

• 请求的变量位宽 (ABTSZ)

• 访问类型,看

• 访问的是未定义的地址 (UNDADD) 还是未对齐的地址 (MISADD)

• 导致异常的访问来源 (MST0 和 MST1)

• 自从上一次读取这个寄存器后是否每一个主机都发生了异常 (SVMST0 和 SVMST1),除非

这个信息已经加载到 MSTx

发生来自处理器的数据异常时,数据地址得以保存。这非常有用,因为搜索哪个地址引起异常

要求进行反汇编并明了处理器的上下文。

发生预取异常时,由于预取发生在流水线中,地址可能已经变了。只有在执行读指令时 ARM 处

理器才会理会预取异常,而此时可能

接寄存器。

其是数据读 / 写访问还是代码访问 (ABTTYP)

已经发生几次异常了。因 此最好使用 ARM 处理器的异常链

嵌入式 Flash 控制 器

嵌入式 Flash 控制器被加入存储器控制器以保证 Flash 模块与 32 位内部总线的接口。通过其 32

位的缓冲器可以提高 Thumb 模式下代码获取的性能。它同时还通过完整的命令集管理着 Flash

的编程、擦除、加锁和解锁。

不对齐检测器 存储器控制器的未对齐检测器可以检查内存访问的一致性。

不论内存访问是由哪一个主机发起,检 测 器 将检查每一次内存访问的总线宽度以及位 0 和位 1。

如果以字 (32 位 ) 来访问,而且位 0 和位 1 不为 0,或者以半自字 (16 位 ) 来访问,而位 0 不为

0,则异常返回到主机,此次访问被取消。要注意的是,当 ARM 处理器在获取指令时不执行这种

检查。

地址不对齐通常是由软件缺陷引起的,会引发错误的指针操作

难以检测。

由于请求的地址保存于异常状态寄存器,而引起地址不对齐的指令保存于异常链接寄存器,检

测及修正这类软件缺陷因此得到了简化。

。这些软件缺陷在调试阶段特别

88

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

存储器控制器 (MC) 用户接口

基地址:0xFFFFFF00

Table 16. 存储器控制器 (MC) 寄存器映射

偏移地址 寄存器 名称 访问类型 复位状态

0x00 MC 重映射控制寄存器 MC_RCR 只写

0x04 MC 异常状态寄存器 MC_ASR 只读 0x0

0x08 MC 异常地址状态寄存器 MC_AASR 只读 0x0

0x0C-0x5C 保留 –––

0x60 EFC 配置寄存器 参见 “ 嵌入式 Flash 控制器 (EFC)” on page 93.

6070A–ATARM–07-Jun-05

89

MC 重映射控制寄存器

寄存器名称:MC_RCR

访问类型:只写

偏移地址: 0x00

31 30 29 28 27 26 25 24

––––––––

23 22 21 20 19 18 17 16

––––––––

15 14 13 12 11 10 9 8

––––––––

76543210

–––––––RCB

• RCB: 重映射命令位

0:无效。

1:这一位的作用象是一个切换开关:写 1 将交替地执行 / 取消第零页储存器的重映射。

90

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

MC 异常状态寄存器

寄存器名称: MC_ASR

访问类型:只 读

复位值: 0x0

偏移地址: 0x04

31 30 29 28 27 26 25 24

––––––SVMST1SVMST0

23 22 21 20 19 18 17 16

––––––MST1MST0

15 14 13 12 11 10 9 8

– – – – ABTTYP ABTSZ

76543210

––––––MISADDUNDADD

• UNDADD: 未定义的地址异常状态

0: 上一个异常不是由于执行了对未定义地址的访问而引起的。

1: 上一个异常是由于执行了对未定义地址的访问而引起的。

• MISADD: 未对齐的地址异常状态

0: 上一个异常不是由于地址未对齐引起的。

1: 上一个异常是由于地址未对齐引起的。

• ABTSZ: 异常变量位宽状态

AT91SAM7S64 Preliminary

ABTSZ 异常变量位宽

00 字节

01 半字

10 字

11 保留

• ABTTYP: 异常类型状态

ABTTYP 异常类型

00 读数据

01 写数据

10 获取代码

11 保留

•MST0: ARM7TDMI异常来源

0:上一个异常不是由于 ARM7TDMI 引起的。

1:上一个异常是由于 ARM7TDMI 引起的。

• MST1: PDC 异常来源

0:上一个异常不是由于 PDC 引起的

。

1:上一个异常是由于 PDC 引起的。

6070A–ATARM–07-Jun-05

91

• SVMST0: 保留的 ARM7TDMI 异常来源

0:自上一次读取 MC_ASR,或是通过 MST0 得到通知之后,没有发生由于 ARM7TDMI 造成的异常。

1:自上一次读取 MC_ASR 之后,至少发生了一次由于 ARM7TDMI 造成的异常。

• SVMST1: 保留的 PDC 异常来源

0:自上一次读取 MC_ASR,或是通过 MST1 得到通知之后,没有发生由于 PDC 造成的异常。

1:自上一次读取 MC_ASR 之后,至少发生了一次由于 PDC 造成的异常。

MC 异常地址状态寄存器

寄存器名称 : MC_AASR

访问类型:只 读

复位值: 0x0

偏移地址: 0x08

31 30 29 28 27 26 25 24

23 22 21 20 19 18 17 16

15 14 13 12 11 10 9 8

76543210

ABTADD

ABTADD

ABTADD

ABTADD

• ABTADD: 异常地址

包含了上一次异常访问的地址。

92

AT91SAM7S64 Preliminary

6070A–ATARM–07-Jun-05

AT91SAM7S64 Preliminary

嵌入式 Flash 控制器 (EFC)

概述 嵌入式 Flash 控制器 (EFC) 是存储器控制器的一部分,确保 Flash 块与 32 位内部总线的接口。

通过其 32 位缓冲器系统,EFC 提高了 Thumb 模式下代码获取的性能。它同时还通过一套完整

的命令集管理 Flash 的编程、擦除、加锁和解锁。

功能说明

嵌入式 Flash 的组 织形式

嵌入式 Flash 与 32 位内部总线直接接口。它具体由下面几个接口组成:

• 一个存储面由几个相同大小的页面构成。

• 两个 32 位读缓冲器用来优化代码访问 (See “ 读操作 ” on page 94.)。

• 一个写缓冲区用来管理页面编程。写缓冲区与页面大小相同。这个缓冲区是只写的,而且

可以在 1 M 字节地址空间里进行访问。所以每个字都可以写到它的最终地址 (See “ 写操作

” on page 96.)。

• 几个锁定位用来保护锁定区域的写和擦除操作。锁定区域由几个连续的页面组成,每个锁

定区域具有自己的锁定位。

•

几个通用 NVM 位。每个位控制一个特定的功能。具体请参考产品定义一节。

嵌入式 Flash 大小,页面大小和锁定区域组织在产品定义一节有描述。

Figure 31. 嵌入式 Flash 存储器映射

Page 0

Start Address

Flash Memory

Lock Region 0

Lock Region 1

Lock Bit 0

Lock Bit 1

Page (m-1)

6070A–ATARM–07-Jun-05

Lock Region

32-bit wide

(n-1)

Lock Bit n-1

Page ( (n-1)*m )

Page (n*m-1)

93

读操作 一个优化的控制器管理着嵌入式 Flash 的读操作。系统增加了两个 32 位的缓冲器。其作用是访

问第二个读操作的地址,从而提高了处理器运行于 Thumb(16 位指令集 ) 模式时的性能。图示请

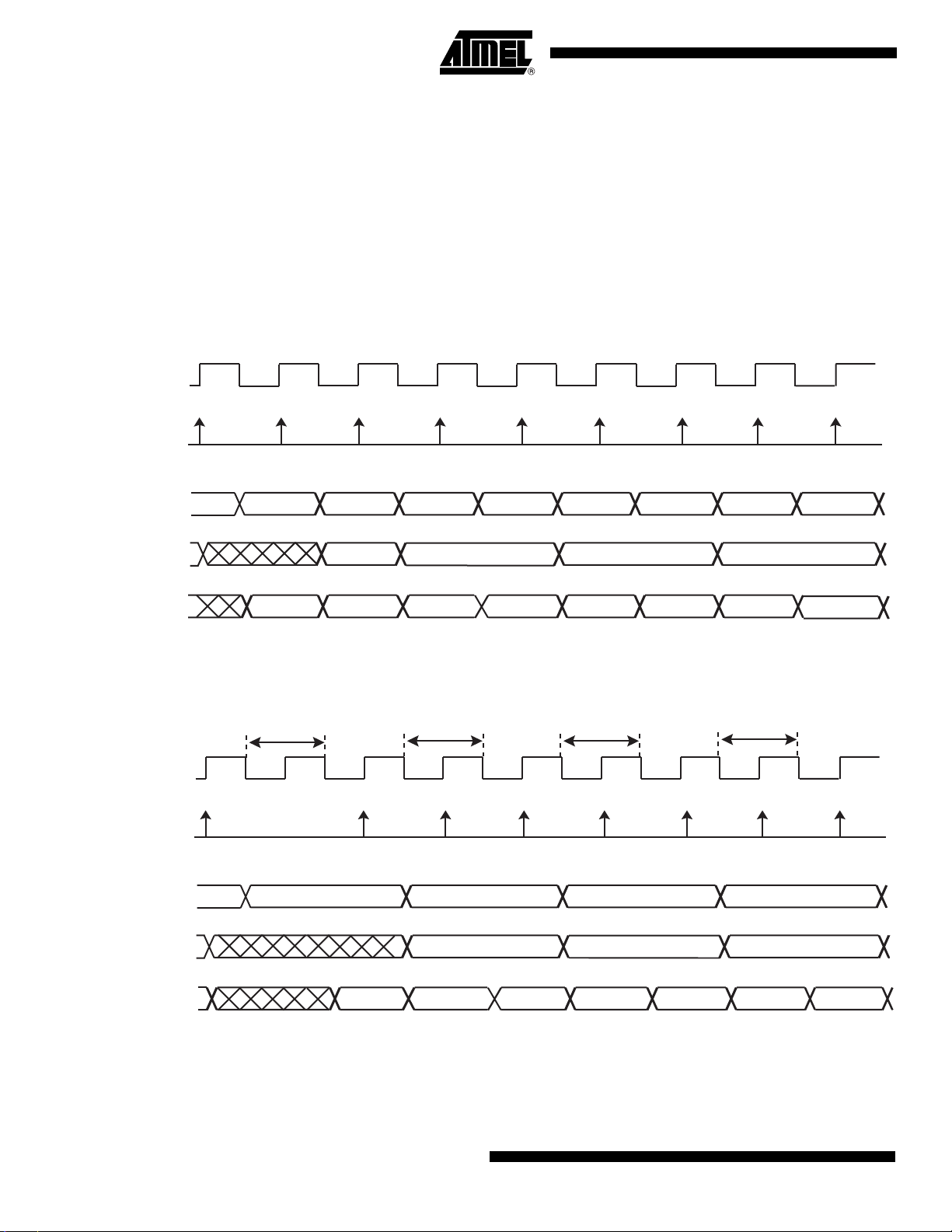

参见 Figure 32, Figure 33 和 Figure 34。

此优化只对代码获取有效,对数据无效。

读操作可以利用等待状态。通过编程 Flash 模式寄存器 MC_FMR ( 见 “MC Flash 模式寄存器 ”

on page 102)的FWS (Flash等待状态),最多可以插入3个等待状态。FWS为 0表示对片内 Flash

进行单周期访问。

Flash 存储器可以 8、 16 和 32 位的方式进行访问

由于 Flash 模块比保留的片内存储区地址空间要小,访问这个地址空间时 Flash 将重复出现。

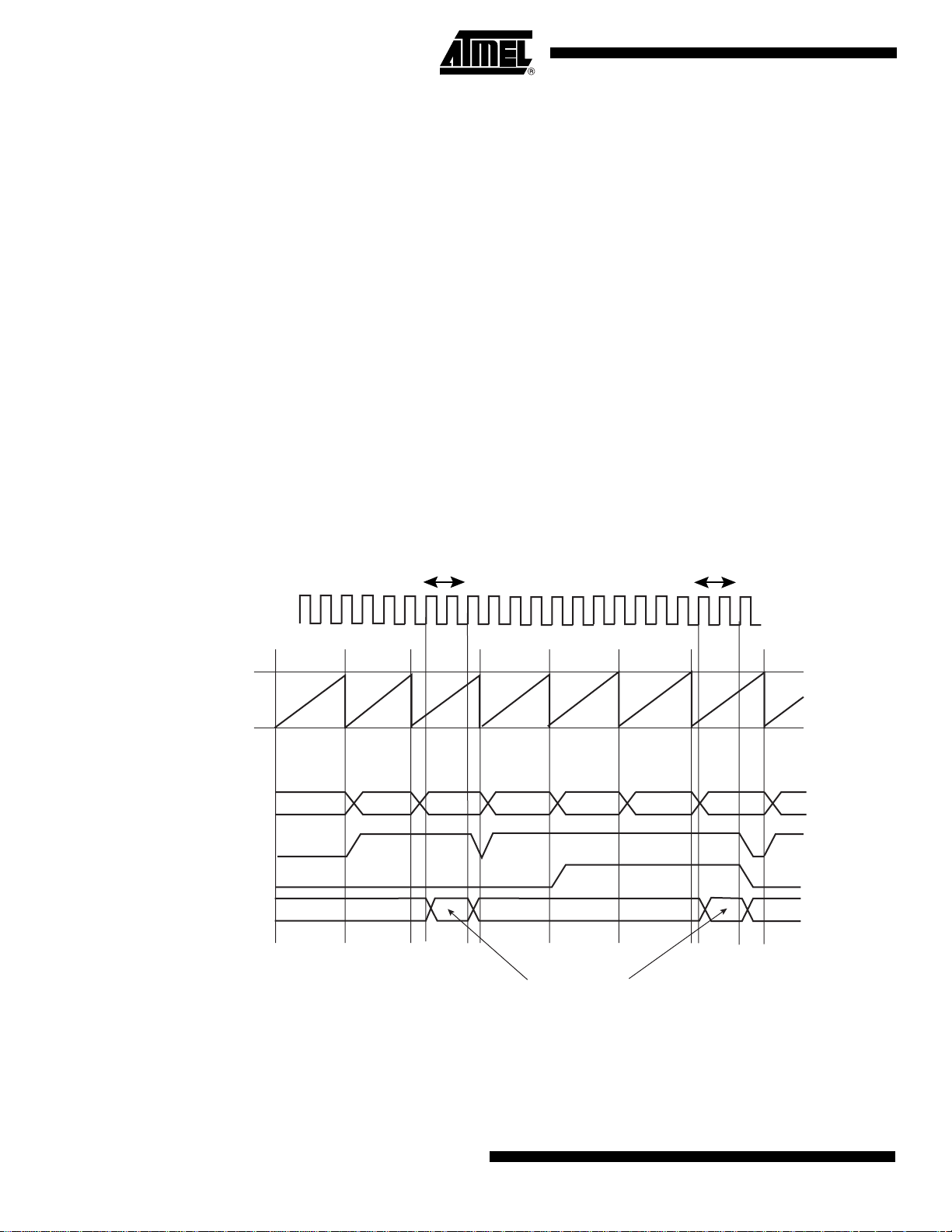

Figure 32. 代码读取优化, Thumb 模式, FWS = 0

Master Clock

ARM Request (16-bit)

Code Fetch

Flash Access

Buffer (32 bits)

Data To ARM

@Byte 0

@Byte 2 @Byte 4

Bytes 0-3 Bytes 4-7

Bytes 0-3

Bytes 0-1

Bytes 2-3 Bytes 4-5 Bytes 6-7

Note: FWS 为 0 时,所有的访问都是单周期访问。

Figure 33. 代码读取优化, Thumb 模式, FWS = 1

1 Wait State Cycle

1 Wait State Cycle 1 Wait State Cycle

@Byte 6

Bytes 4-7

@Byte 8

Bytes 8-11

。

@Byte 10 @Byte 12

Bytes 12-15 Bytes 16-19

Bytes 8-11

Bytes 8-9 Bytes 10-11 Bytes 12-13

@Byte 14 @Byte 16

Bytes 12-15

1 Wait State Cycle

Bytes 14-15

Master Clock

ARM Request (16-bit)

Code Fetch

Flash Access

Buffer (32 bits)

Data To ARM

@Byte 0

@Byte 2

Bytes 0-3 Bytes 4-7

Bytes 0-1

@Byte 4

Bytes 0-3

Bytes 2-3

@Byte 6

Bytes 4-5

Note: FWS 为 1 且执行序列读时,所有的访问都是单周期访问 ( 除了第一次访问 )。

94

AT91SAM7S64 Preliminary

@Byte 8 @Byte 10

Bytes 8-11

Bytes 4-7

Bytes 6-7

Bytes 8-9 Bytes 10-11

@Byte 12 @Byte 14

Bytes 12-15

Bytes 8-11

Bytes 12-13

6070A–ATARM–07-Jun-05

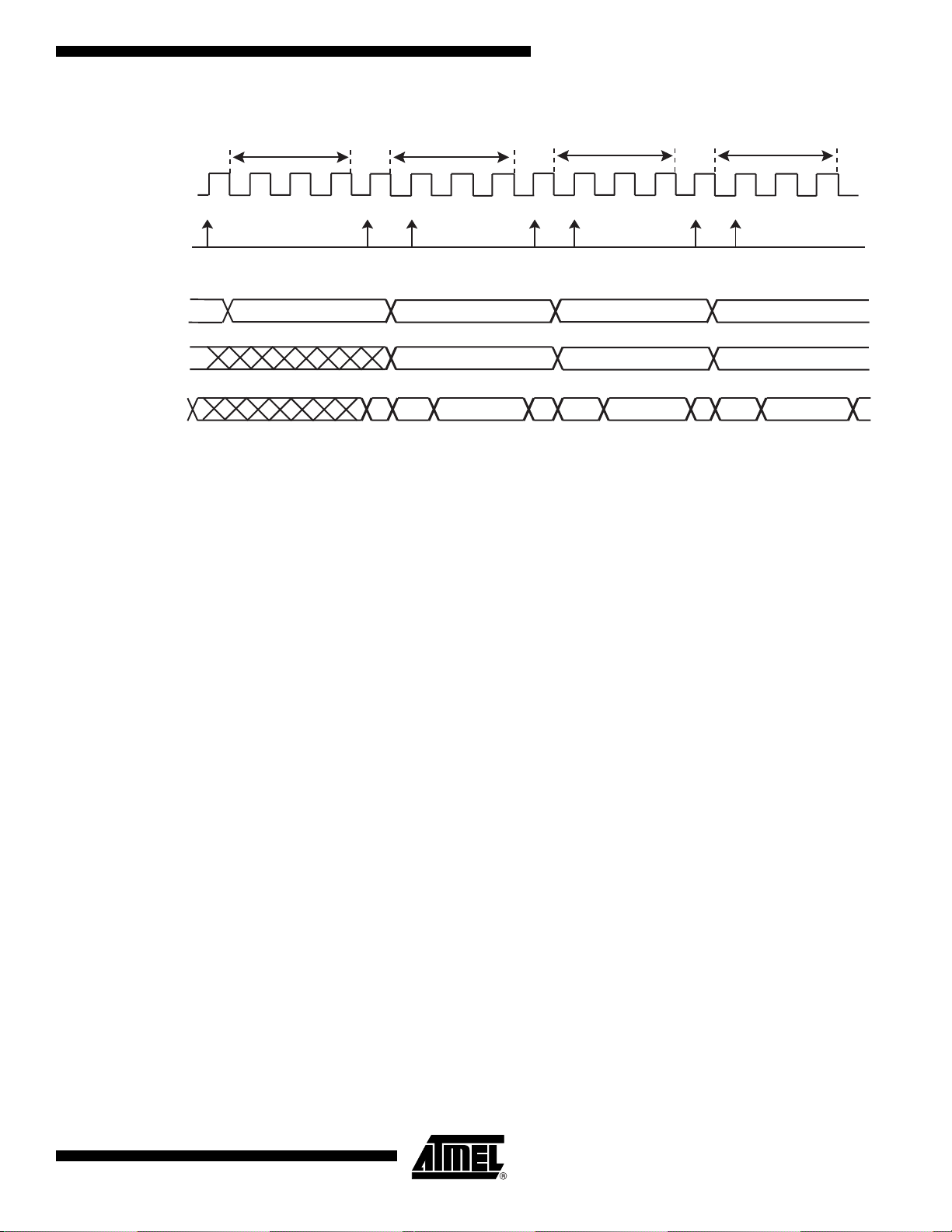

Figure 34. 代码读取优化, Thumb 模式, FWS = 3

3 Wait State Cycles

Master Clock

3 Wait State Cycles

AT91SAM7S64 Preliminary

3 Wait State Cycles 3 Wait State Cycles

ARM Request (16-bit)

Code Fetch

Flash Access

Buffer (32 bits)

Data To ARM

@Byte 0

Bytes 0-3

@2

0-1

@4

2-3

Bytes 4-7

Bytes 0-3

@6

4-5

@12

@8

Bytes 8-11 Bytes 12-15

Bytes 4-7

6-7

@10

8-9

10-11

Bytes 8-11

12-13

Note: FWS为 2 或3,且执行序列读时,第一个访问需要 FWS 个周期,第二个访问需要一个周期, 第三个访问需要FWS 个周期,第四个

访问需要一个周期,依此类推。

6070A–ATARM–07-Jun-05

95

写操作 通过只写锁存缓冲器可以实现对片内保留的 Flash 存储空间的写操作。但是写操作只利用了最

低的8位地址,因此访问整个地址空间时最低地址位,在内部存储器地址空间中反转并重复1024

次。

通过编程存储器保护单元可以禁止写操作。

以 8 位和 16 位方式进行的写操作是不允许的,可能导致不可预期的数据毁坏。

执行写操作时的等待周期等于读等待周期 + 1,除了 FWS = 3 ( 见 “MC Flash 模式寄存器 ” on

page 102) 的情况。

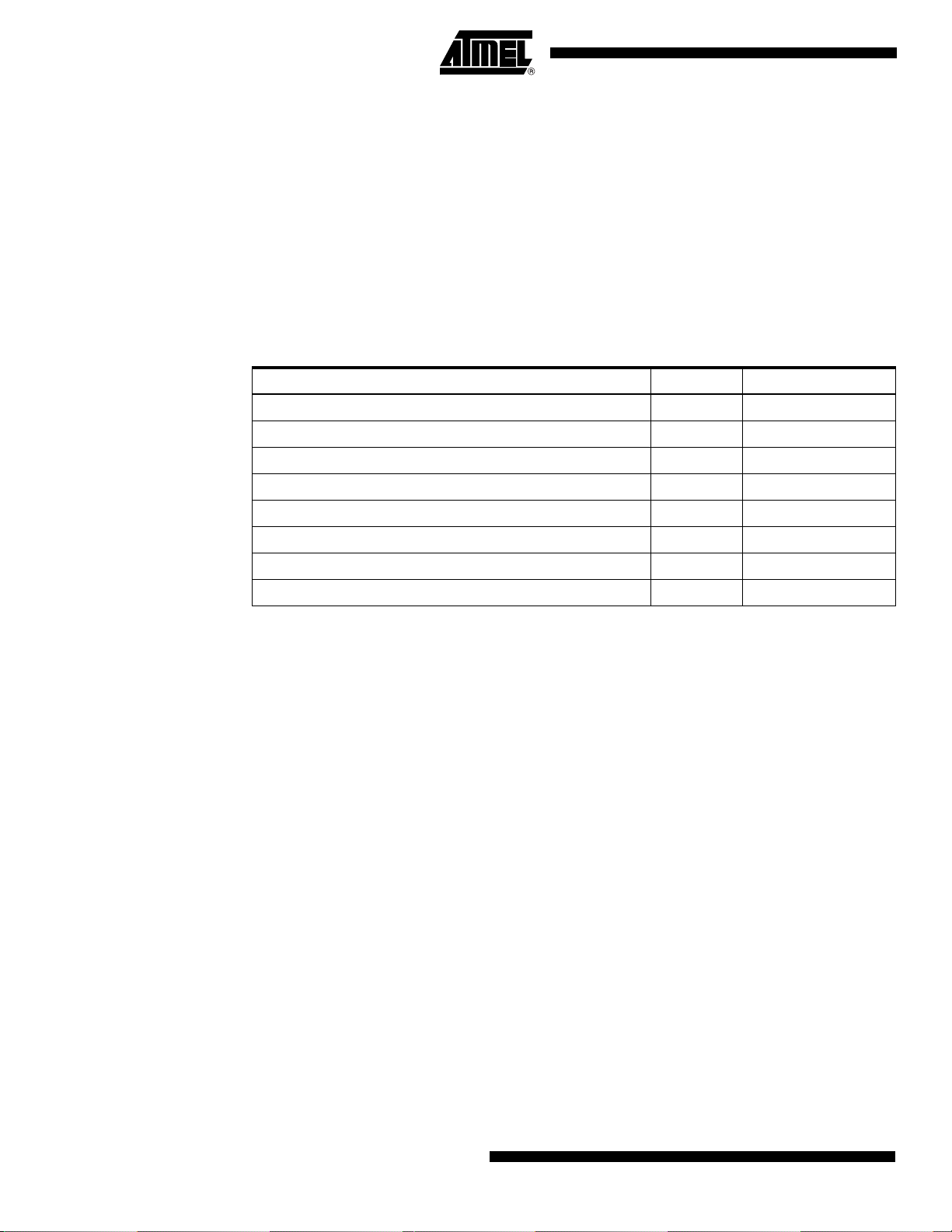

Flash 命令 嵌入式 Flash 控制器提供了一套命令来管理 flash 存储器的编程、扇区加锁和解锁、连续编程与

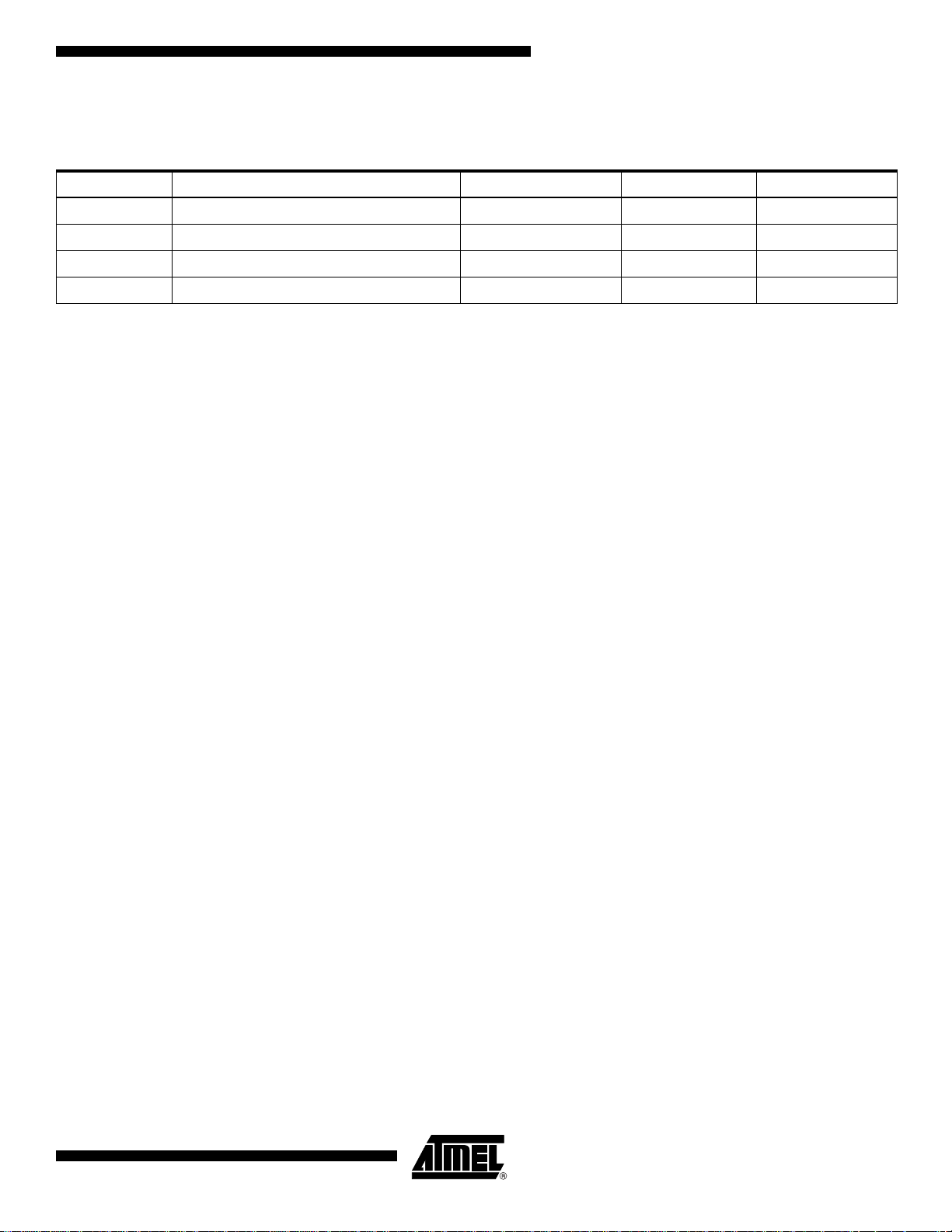

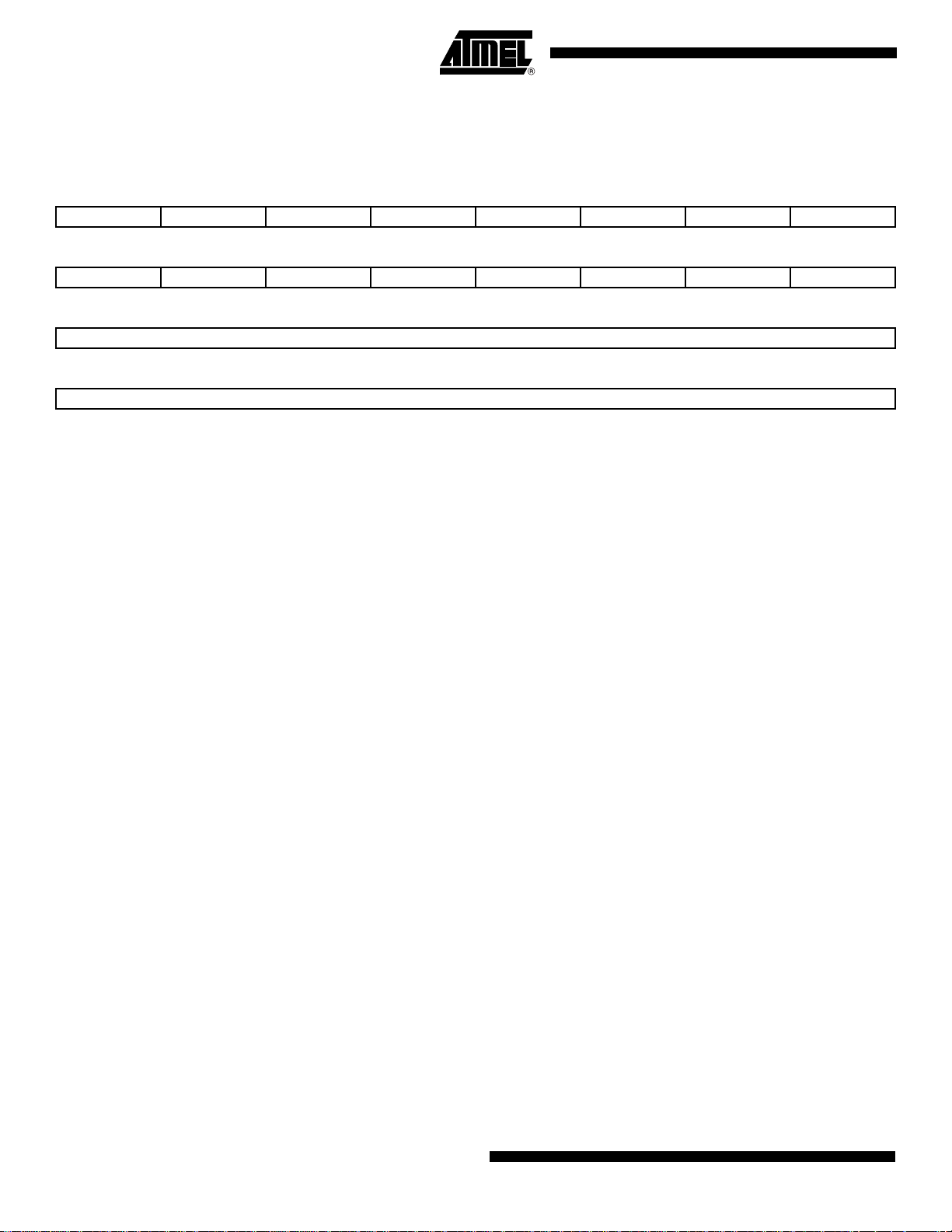

上锁,以及全片擦除。