Datasheet AT90S8515-8JI, AT90S8515-8JC, AT90S8515-8AI, AT90S8515-4PI, AT90S8515-4PC Datasheet (ATMEL)

...

Features

•

AVR - High Performance and Low Power RISC Architecture

•

118 Powerful Instructions - Most Single Clock Cycle Execution

•

8K bytes of In-System Reprogrammable Flash

– SPI Serial Interface for Program Downloading

– Endurance: 1,000 Write/Eras e Cycles

•

512 bytes EEPROM

– Endurance: 100,000 Write/Erase Cycles

•

512 bytes Internal SRAM

•

32 x 8 General Purpose Working Registers

•

32 Programmable I/O Lines

•

Programmable Serial UART

•

SPI Serial Interface

•

VCC: 2.7 - 6.0V

•

Fully Static Operation

– 0 - 8 MHz 4.0 - 6.0V,

– 0 - 4 MHz 2.7 - 4.0V

•

Up to 8 MIPS Throughput at 8 MHz

•

One 8-Bit Timer/Counter with Separate Prescaler

•

One 16-Bit Timer/Counter with Separate Prescaler

and Compare and Capture Modes

•

Dual PWM

•

External and Internal Interrupt Sources

•

Programmable Watchdog Timer with On-Chip Oscillator

•

On-Chip Analog Comparator

•

Low Power Idle and Power Down Modes

•

Programming Lock for Software Security

8-Bit

Microcontroller

with 8K bytes

In-System

Programmable

Flash

AT90S8515

Description

The AT90S8 515 is a low-p ower CMOS 8-bit mic rocontroll er based on the AVR

enhanced RISC architecture . By exe cuting powe rful instruc tions in a single clock

cycle, the AT90S8515 achieves throughpu ts approaching 1 MIPS per MHz allowing

the system designer to optimize power consumption versus processing speed.

The AVR core combines a rich instr uction set with 32 gene ral purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU),

allowing two indep endent r egisters to be acce ssed in one singl e instr uction execute d

in one clock cycle. Th e resulting arc hitecture is mor e code efficie nt while achievin g

throughputs up to ten times faster than conventional CISC microcontrollers.

(continued)

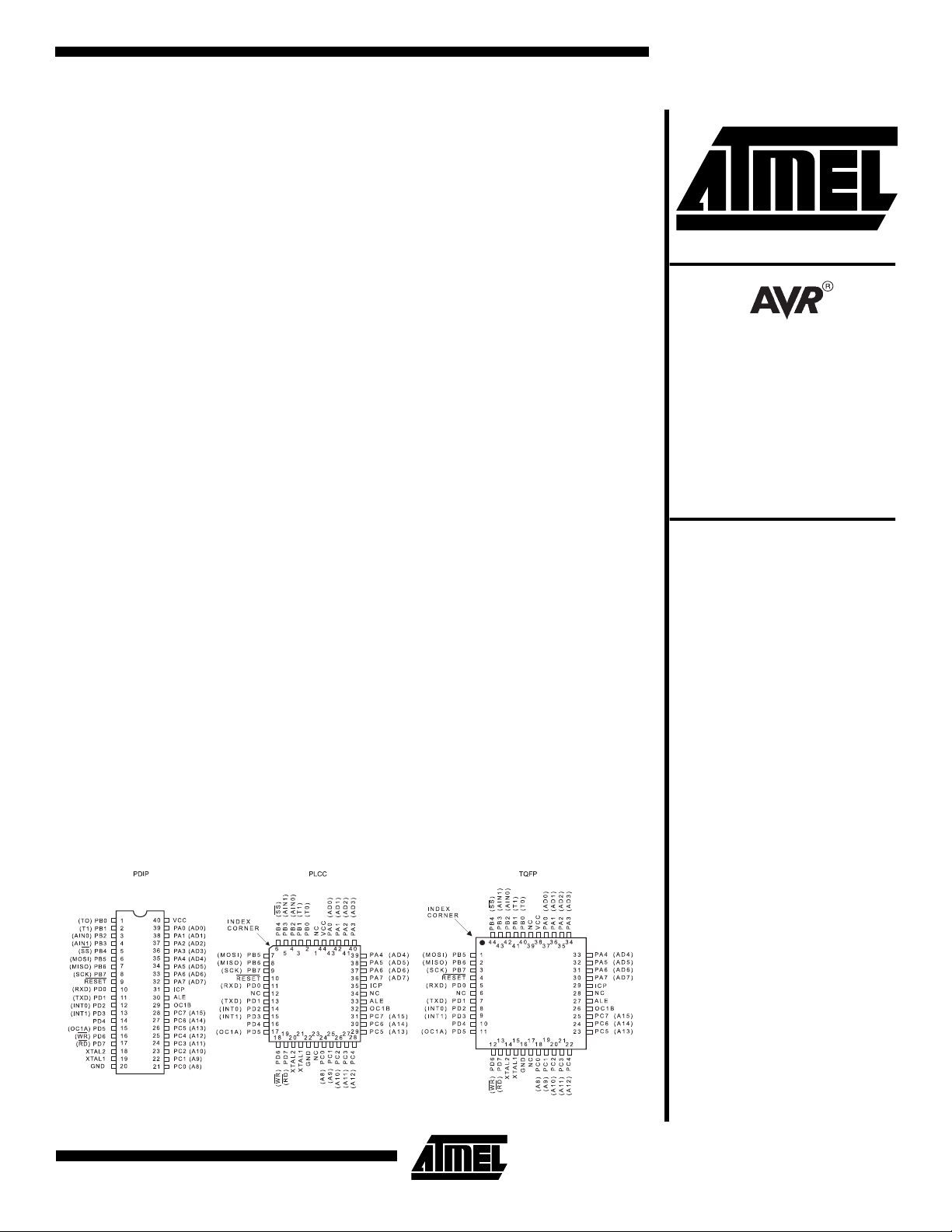

Pin Configurations

Preliminary

®

Rev. 0841D–06/98

1

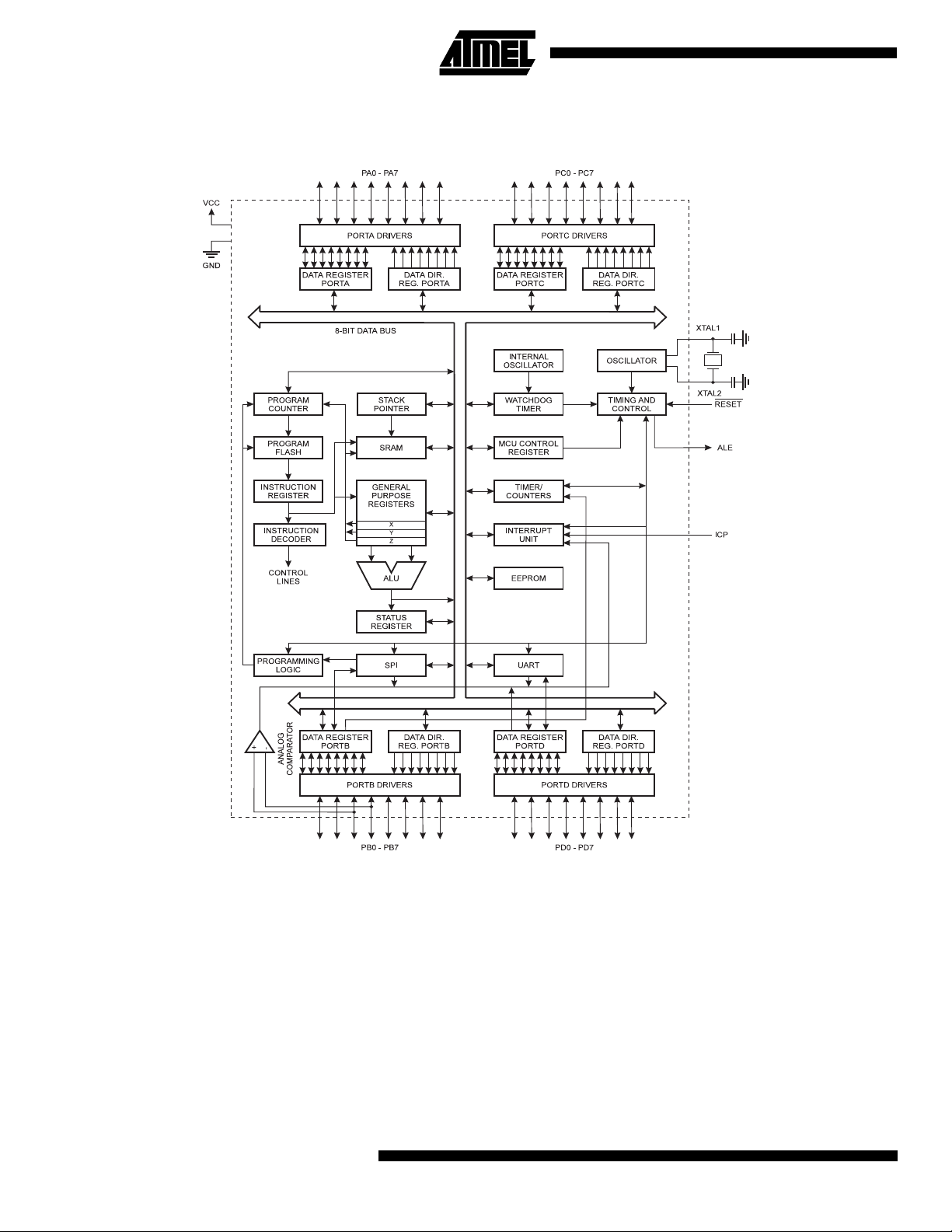

Block Diagram

Figure 1.

The AT90S8515 Block Diagram

The AT90S8515 provides the following features: 8K bytes

of In-System Programmable Flash, 512 bytes EEPROM,

512 bytes SRAM, 32 gen eral purpo se I/O li nes, 3 2 general

purpose working registers, flexible timer/counters with

compare modes, internal and external interrupts, a programmable serial UART, programmable Watchdog Timer

with internal oscillator, an SPI serial port and two software

selectable pow er saving modes. T he Idl e Mode sto ps the

CPU while allowing the SRAM, timer/counters, SPI port

and interrupt syste m to contin ue functioning . The power

down mode saves the register contents but freezes the

oscillator, disabling all other chip functions until the next

interrupt or hardware reset.

2

AT90S8515

The device is manufac tured using Atmel’ s high density

non-volatile memory technology. The on-chip in-system

programmable Flash allows the program memory to be

reprogrammed in-sys tem th ro ugh an S PI se rial i nterface or

by a conventional n onvolatile memo ry programmer. By

combining an enhanced RISC 8-bit CPU wit h In-System

Programmable Flash on a monolithic chip, the Atmel

AT90S8515 is a powerful microcontroller that provides a

highly flexible and co st effect ive solution to many em bedded control applications.

The AT90S8515 AVR is supported with a full s uite of program and system development tools including: C compilers, macro assemblers, program debugger/si mulators, incircuit emulators, and evaluati on kits.

AT90S8515

Pin Descriptions

V

CC

Supply voltage

GND

Ground

Port A (PA7..PA0)

Port A is an 8 -bit b idirec tional I/O port. Port p ins ca n provide internal pull-up resistors (selected for each bit). The

Port A output buffers can sink 20mA and can drive LED displays directly. When pins PA0 to PA7 are used as inputs

and are externally pull ed low, they will source c urrent if the

internal pull-up resistors are activated.

Port A serves as Multiplexed Address/Data input/output

when using external SRAM.

Port B (PB7..PB0)

Port B is an 8-bit bidirectional I/O pins with internal pull-up

resistors. The Port B output buffers can sink 20 mA. As

inputs, Port B pins t hat a re ex ter nally pu ll ed l ow wi ll sour c e

current if the pull-up resistors are activated.

Port B also serves the fu nction s of vario us speci al feat ures

of the AT90S8515 as listed on page 46.

Port C (PC7..PC0)

Port C is an 8-bit bidirectional I/O port with internal pull-up

resistors. The Port C output buffers can sink 20 mA. As

inputs, Port C pins that are exter nal ly pul led low wil l sour ce

current if the pull-up resistors are activated.

Port C als o s erv es as Addr es s ou tp ut when us ing ext ern al

SRAM.

Port D (PD7..PD0)

Port D is an 8-bit bidirectional I/O port with internal pull-up

resistors. The Port D output buffers can sink 20 mA. As

inputs, Port D pins that are exter nal ly pul led low wil l sour ce

current if the pull-up resistors are activated.

Port D also serves th e fu nc tion s of v ario us sp ec ial fea tur es

of the AT90S8515 as listed on page 52.

RESET

Reset input. A low on th is pi n for two machi ne cy cles wh ile

the oscillator is running resets the device.

XTAL1

Input to the inverting os cillator amplifi er and input to th e

internal clock operating circuit.

XTAL2

Output from the inverting oscillator amplifier

ICP

ICP is the input pin for the Time r/Counter1 Inpu t Capture

function.

OC1B

OC1B is the output pin for the Timer/Counter1 Output

CompareB function

ALE

ALE is the Address Latch Enable used when the Ex ternal

Memory is enabled. The ALE strob e is used to latch the

low-order address (8 bits) into an address latch during the

first access cy cle, and the A D0-7 pins a re used for data

during the second access cycle.

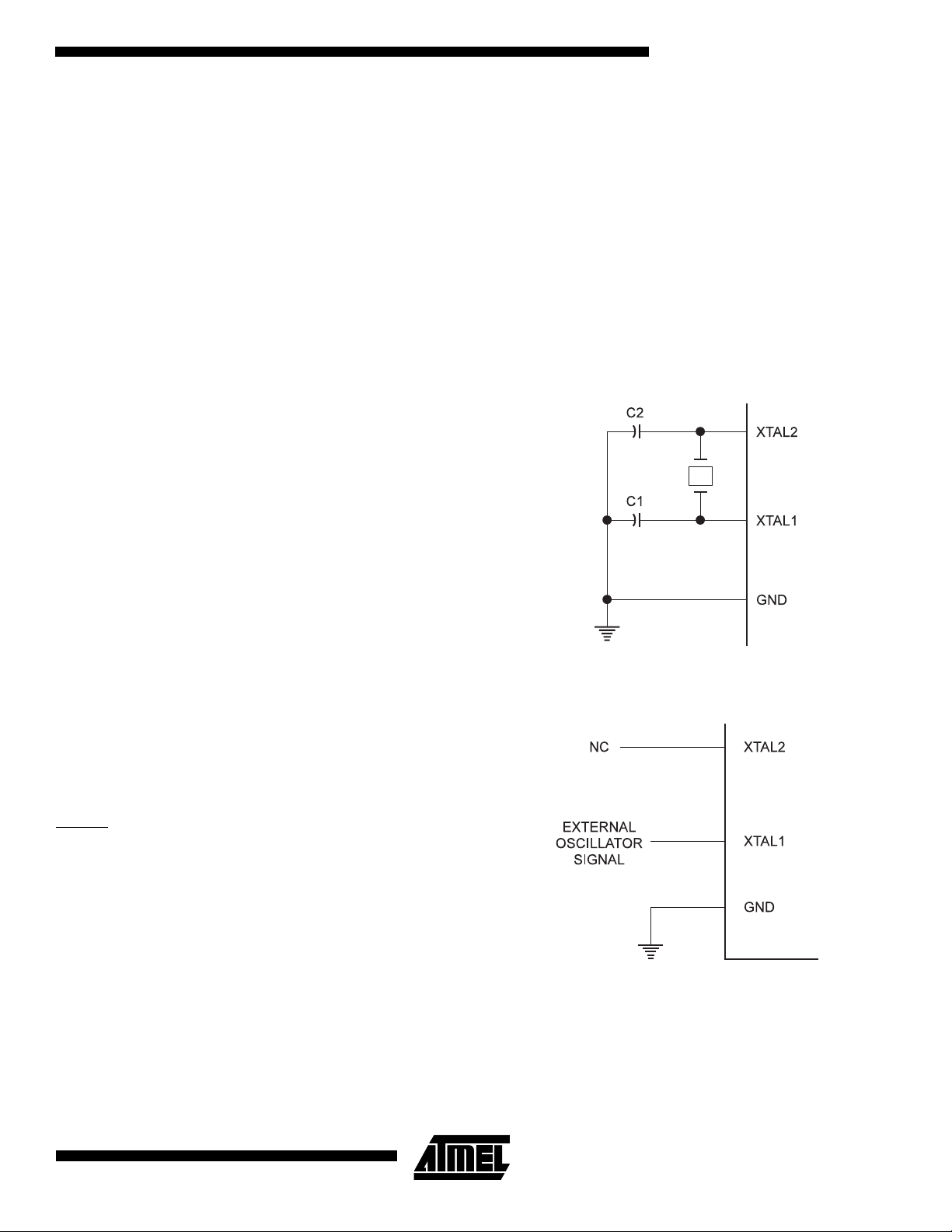

Crystal Oscillator

XTAL1 and XTAL2 are input and output, respectively, of an

inverting amplifier which can be configured for use as an

on-chip oscillator, as shown in Figure 2. Either a quartz

crystal or a ceramic resonator may be used. To drive the

device from an external clock source, XTAL2 should be left

unconnected while XTAL1 is driven as shown in Figure 3.

Figure 2.

Figure 3.

Oscillator Connec tio ns

External Clock Drive Configuration

3

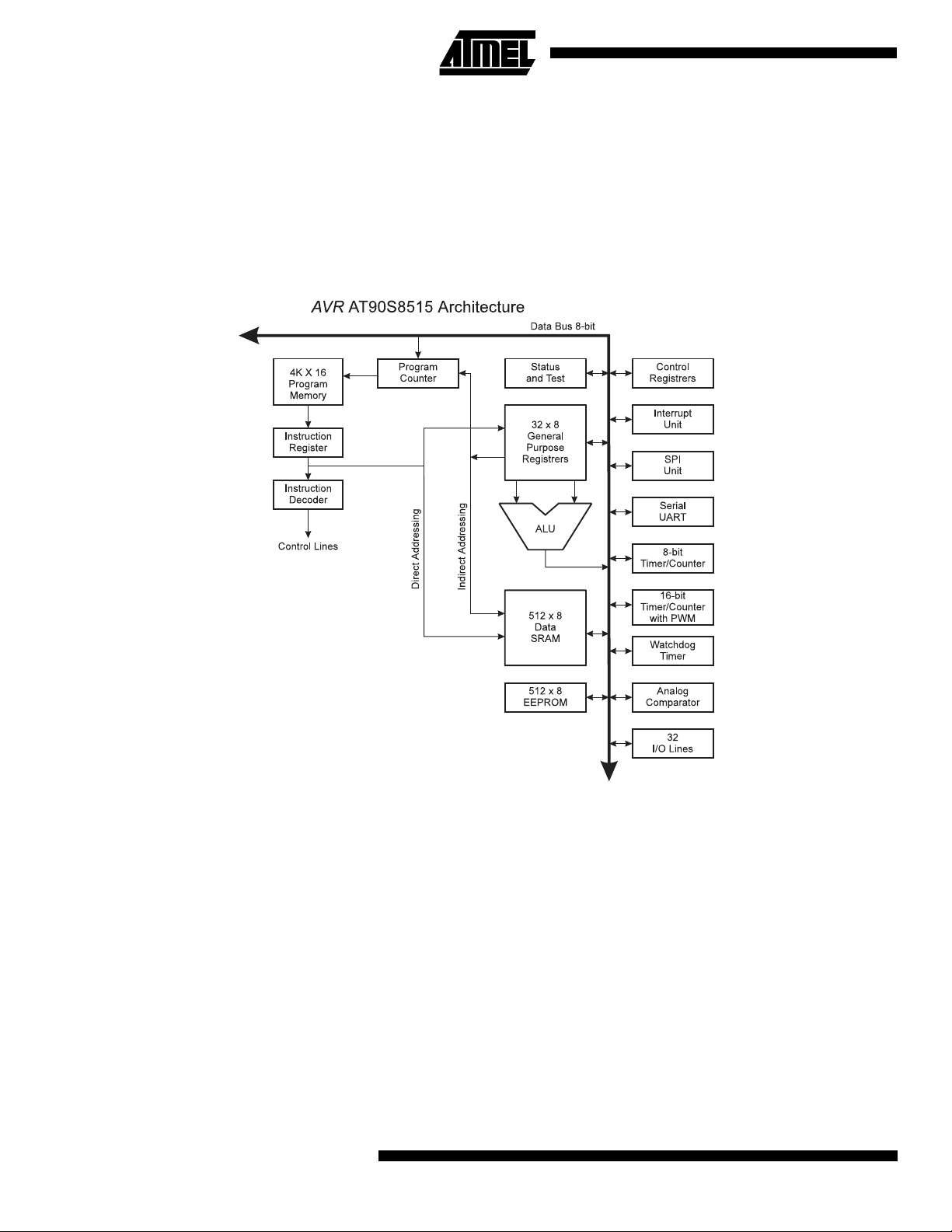

AT90S8515 Architectural Overview

The fast-access register file concept contains 32 x 8-bit

general purpose worki ng regi ster s with a sin gle cl ock c ycle

access time. This means that during one single clock cycle,

one ALU (Arithmetic Logic Unit) operation is executed. Two

operands are output from the register file, the operation is

executed, and the result is stored back in the register file in one clock cycle.

Six of the 32 registers can be used as three 16-bits indirect

address register pointers for Data Space addressing enabling efficient address calculati ons. One of the three

address pointers is also used as the address pointer for the

constant table look up function. These added function registers are the 16-bits X-register, Y-register and Z-register.

Figure 4.

The AT90S8515

AVR

Enhanced RISC Architecture

The ALU supports arithmetic and logic functions between

registers or be tween a const ant and a r egist er. Si ngle re gister operations are also executed in the ALU. Figure 4

shows the AT90S851 5 AVR Enhan ced RISC mi crocontro ller architecture .

In addition to the register operation, the conventional memory addressing mode s can be used on the re gister file as

well. This is e nabled by th e fact that t he register f ile is

assigned the 32 lowermost Data Space addresses ($00 $1F), allowing them to be accessed as though they were

ordinary memory locations.

The I/O memory space contains 64 addresses for CPU

peripheral functions as Control Registers, Timer/Counters,

A/D-converte rs, and ot her I/O fun ctions. T he I/O Mem ory

can be accessed dir ectly, or as the Da ta Space loca tions

following those of the register file, $20 - $5F.

4

AT90S8515

AVR

The

rate memories and buses fo r program and data. The pr ogram memory is executed with a two stage pipeline. While

one instruction is bein g executed, the next ins truction is

pre-fetched from the program memory. This co ncept

enables instructions to be executed in every clock cycle.

The program memory is in-system programmable Flash

memory.

With the relat ive jump an d call i nstructi ons, the w hole 4K

address space i s directl y access ed. Most AVR in struc tions

have a single 16-bit word format. Every program memory

address contains a 16- or 32-bit instruction.

During interrupts and su broutine calls, t he retur n addre ss

program counter (PC) is stor ed on the stack. The stack is

effectively allo cated i n the gene ral dat a SRAM, and cons equently the stack size is only limited by the total SRAM size

and the usage of the SR AM. All user progr ams must initial-

uses a Harvard architecture concept - with sepa-

AT90S8515

ize the SP in the reset routine (before subroutines or inter-

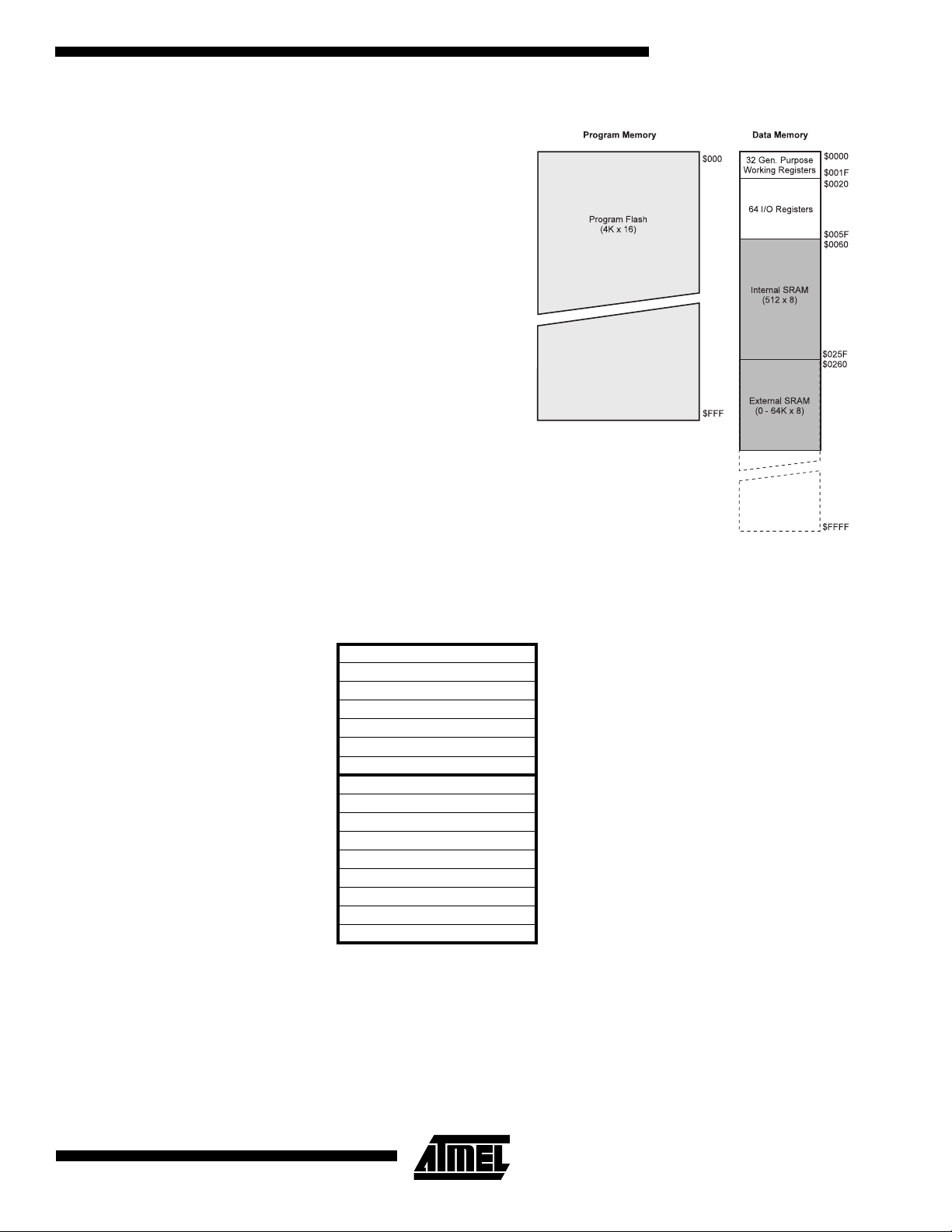

Figure 5.

Memory Maps

rupts are execute d). The 16-bit stack pointer SP is

read/write accessib le in the I/O spac e.

The 512 bytes data SRAM can be easily access ed through

the five different addressing modes supported in th e AVR

architecture.

The memory spaces in the AVR

architecture are all linear

and regular memory maps.

A flexible interrupt module has its control registers in the

I/O space with an additional global interrupt enable bit in

the status register. All the different interrupts have a separate interrupt vector in the interrupt vector table at the

beginning of the program memory. The different interrupts

have priority in accordance with their interrupt vector position. The lower the interrupt vector address the higher the

priority.

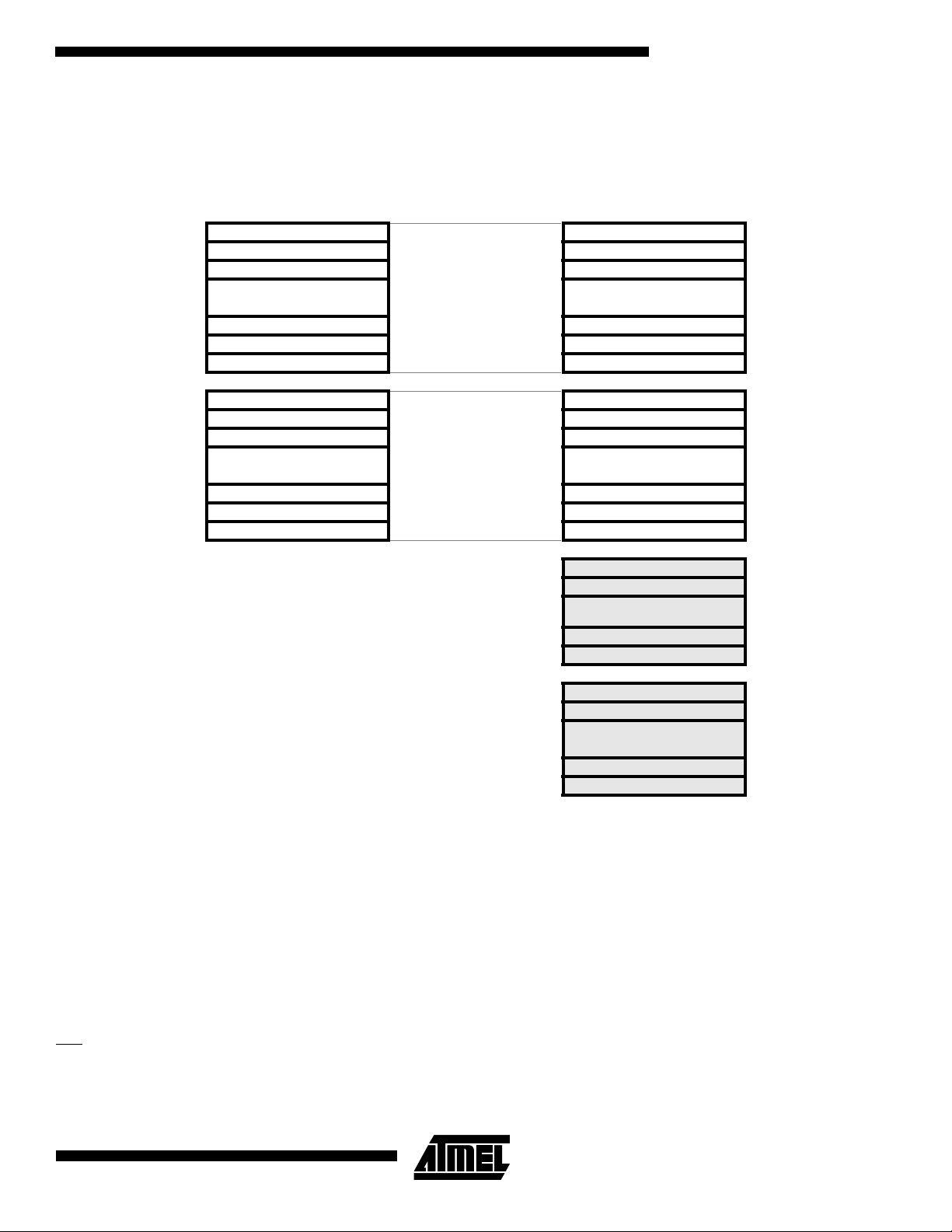

The General Purpose Register File

Figure 6 shows the structure of the 32 general purpose working registers in the CPU.

Figure 6.

AVR CPU General Purpose Working Registers

70Addr.

R0 $00

R1 $01

R2 $02

…

R13 $0D

General R14 $0E

Purpose R15 $0F

Working R16 $10

Registers R17 $11

…

R26 $1A X-register low byte

R27 $1B X-register high byte

R28 $1C Y-register low byte

R29 $1D Y-register high byte

R30 $1E Z-register low byte

R31 $1F Z-register high byte

All the register operating instructions in the i nstruction set

have direct and single cycle access to all registers. The

only exceptio n is the five consta nt arithmetic and logic

instructions SB CI, SUBI , CPI, ANDI and ORI between a

constant and a register and the LDI instruction for load

immediate constant data. These instructions apply to the

second half of the registers in the register file - R16..R31.

The general SBC, SUB, CP, AND and OR and all other

operations between two register s or on a s ingle regis ter

apply to the entire register file.

As shown in Figure 6, each register is also assigned a data

memory address, mapp ing them direc tly into the fi rst 32

locations of the user Data Space. Although not being physically implemented as SRAM locations, this memory organization provides great flexibility in access of the registers,

as the X,Y and Z registers ca n be set to index an y register

in the file.

5

The X-Register, Y-Register And Z-Register

The registers R26..R31 have some added functions to their

general purpose usa ge. Thes e re gister s a re ad dr es s poi nt-

ers for indirect addressing of the Data Space. The three

indirect address registers X, Y and Z are defined as:

Figure 7.

The X, Y and Z Registers

15 0

X - register 7 0 7 0

R27 ($1B) R26 ($1A)

15 0

Y - register 7 0 7 0

R29 ($1D) R28 ($1C)

15 0

Z - register 7 0 7 0

R31 ($1F) R30 ($1E)

In the different addressing modes these address registers

have functions as f ixed d ispl acement , a utoma tic in cre ment

and decrement (see the descriptions for the different

instructions).

The ALU - Arithmetic Logic Unit

The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers.

Within a single clo ck cy cle, AL U oper ations b etween regi sters in the register fil e are executed . The ALU operat ions

are divided into three main categories - arithmetic, logical

and bit-functions.

The In-System Programmable Flash Program

Memory

The AT90S8515 contain s 8K byt es on- chip In- System Programmable Flash memory for program storage. Since all

instructions are 16-or 32-bit words, the Flash is organized

as 4K x 16. The Flash memo ry has an endurance of at

least 1000 write/erase cyc les. The AT90S85 15 Program

Counter (PC) is 12 bits wide, thus addressing the 4096 program memory addresses.

See page 62 for a detailed description on Flash data downloading.

Constant tables mu st be alloc ated wit hin the ad dress 0-4K

(see the LPM - Load Program Memory instruction description).

See page 8 for the different program memory addressing

modes.

6

AT90S8515

The SRAM Data Memory - Internal and External

The following figure shows how the A T90S8515 SRAM

Memory is organized:

AT90S8515

Figure 8.

SRAM Organization

Register File Data Address Space

R0 $0000

R1 $0001

R2 $0002

……

R29 $001D

R30 $001E

R31 $001F

I/O Registers

$00 $0020

$01 $0021

$02 $0022

……

$3D $005D

$3E $005E

$3F $005F

Internal SRAM

$0060

$0061

…

$025E

$025F

External SRAM

$0260

$0261

…

The lower 608 Data Memory locations address the Register file, the I/O Memory and the internal data SRAM. The

first 96 locations address the Register File + I/O Memo ry,

and the next 512 locations addres s the internal data

SRAM. An optiona l externa l data S RAM can be placed in

the same SRAM memory space. This SRAM will oc cupy

the location following the internal SRAM and up to as much

as 64K - 1, depending on SRAM size.

When the addresses accessing the data memory space

exceeds the internal data SRAM locations, the external

data SRAM is acc essed usi ng the sam e inst ructions as for

the internal data SRAM access. When the internal data

space is accessed, the read a nd write s trobe pins (RD and

) are inactive during the wh ole access c ycle. External

WR

SRAM operation is enabled by setting the SRE bit in the

MCUCR register. See page 21 for details.

$FFFE

$FFFF

Accessing external SRAM takes one additional clock cycle

per byte compared to access of the internal SRAM. This

means that the commands LD, ST, LDS, STS, PUSH and

POP take one additional clock cycle. If the stack is placed

in external SRAM, interrupts, subr outine calls and returns

take two clock cycles extra because the two-byte program

counter is pushed and popped. When external SRAM interface is used with wait state, two additional cloc k cycles is

used per byte. This has the follo wing effect: Data transfer

instructions take two extra clock cycles, whereas interrupt,

subroutine calls and returns will need four clock cycles

more than specified in the instruction set manual.

The five differen t address ing modes for the data mem ory

cover: Direct, Indirect with Displacement, Indirect, Indirect

with Pre-Decrement and Indirect with Post-Increment. In

the register file, registers R26 to R31 feature the indirect

addressing pointer registers.

7

The direct addressing reaches the entire data space.

The Indirect with Displacement mode features a 6 3

address locations reach from the base address given by

the Y or Z-r egister.

When using register indirect addressing modes with automatic pre-decr ement and post-in crement , the addr ess registers X, Y and Z are decremented and incremented.

The 32 general purpose working registers, 64 I/O registers,

the 512 bytes of i ntern al da ta SR AM, a nd the 64K bytes of

optional external da ta SRAM in the AT90S8515 are all

accessible through all these addressing modes.

See the next secti on for a det ailed desc ription of the differ ent addressing modes.

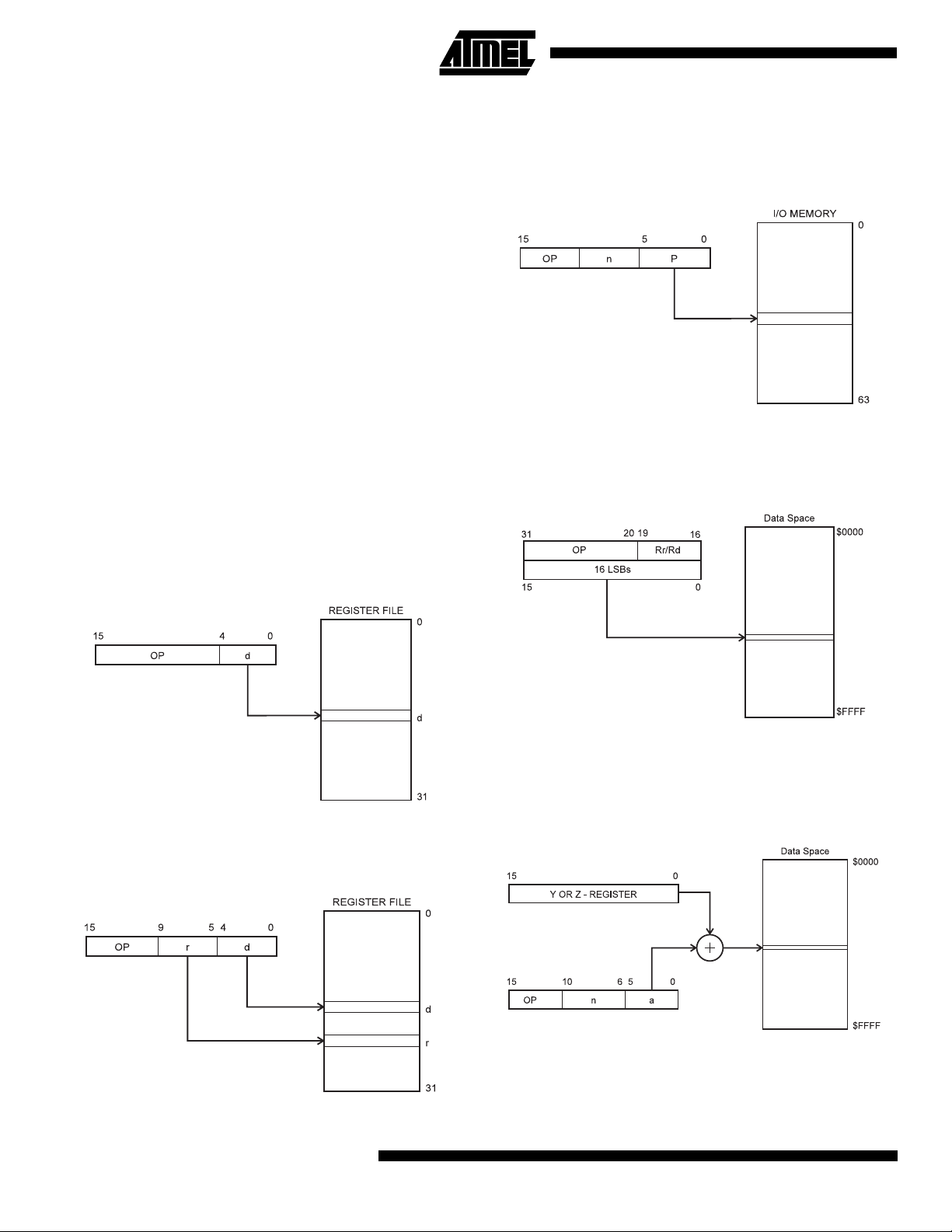

The Program and Data Addressing Modes

The AT90S8515

ports powerful and efficie nt addressing modes for access

to the program memory (Flash) and data memory (SRAM,

Register File and I/O Memory). This section describes the

different addressing modes supported by the

ture. In the figures, OP means the operation code part of

the instruction word. To simplify, not all figures show the

exact location of the addressing bits.

Register Direct, Single Register RD

AVR

Enhanced RISC microcontroller sup-

AVR

architec-

Operands are contained in register r (Rr) and d (Rd). T he

result is stored in register d (Rd).

I/O Direct

Figure 11.

Operand address is contained in 6 bits of the instruction

word. n is the destination or source register address.

Data Direct

Figure 12.

I/O Direct Addressing

Direct Data Addressing

Figure 9.

The operand is contained in register d (Rd).

Register Direct, Two Registers RD AND RR

Figure 10.

Direct Single Register Addressing

Direct Register Addressing, Two Registers

A 16-bit Da ta Ad dr ess is containe d in t h e 16 L SB s o f a t w o word instruction. Rd/Rr specify the destination or source

register.

Data Indirect With Displacement

Figure 13.

Data Indirect with Displacement

Operand address is the result of the Y or Z-register contents added to the address contained in 6 bits of the

instruction wo rd .

8

AT90S8515

AT90S8515

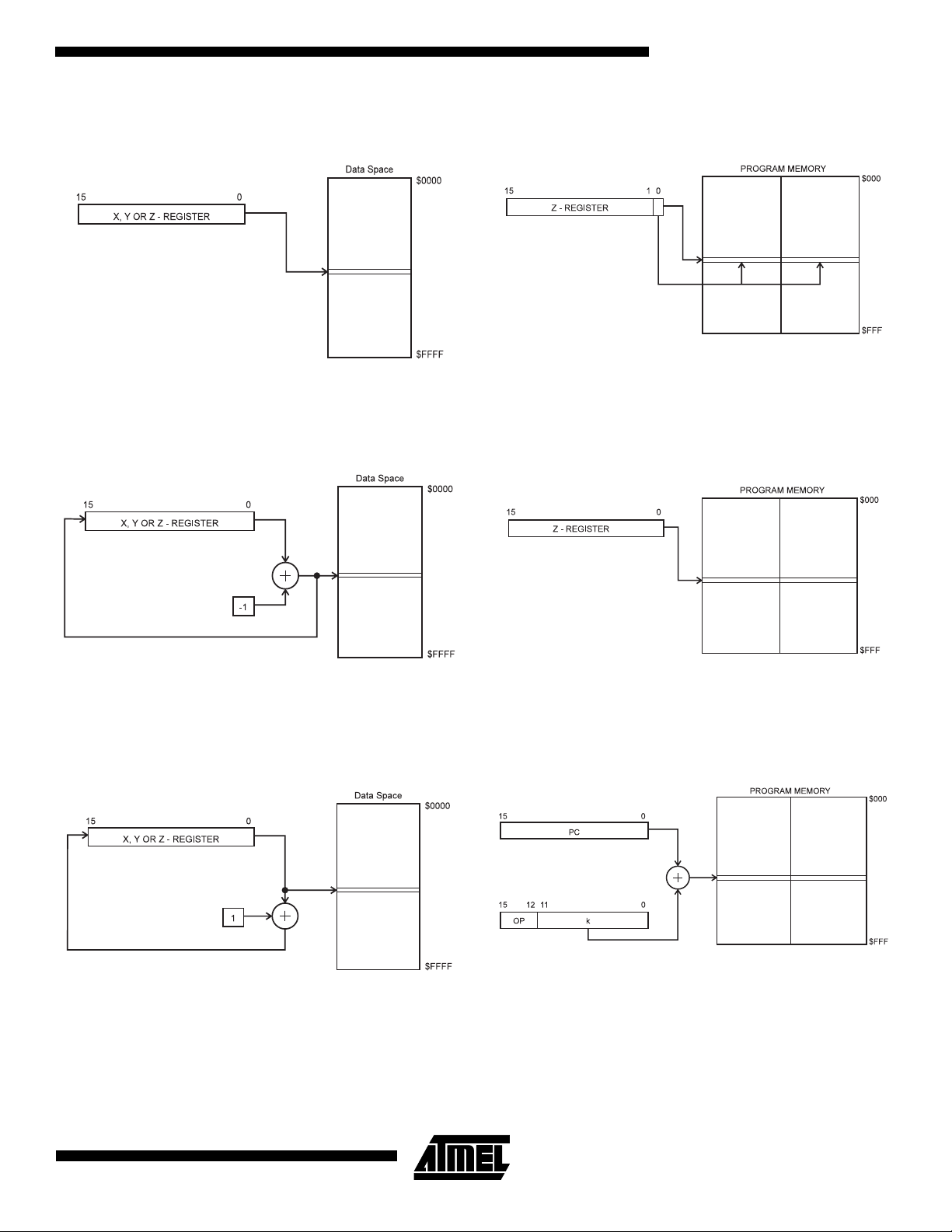

Data Indirect

Figure 14.

Operand address is t he contents of the X, Y or the Z-re gi ster.

Data Indirect With Pre-Decrement

Figure 15.

Data Indirect Addressing

Data Indirect Addressing With Pre-Decrement

Constant Addressing Using The LPM Instruction

Figure 17.

Constant byte address is specified by the Z-register contents. The 15 MSBs sel ec t wo rd ad dres s (0 - 4 K) an d L SB ,

select low byte i f clear ed (LSB = 0) or high b yte if set ( LSB

= 1).

Indirect Program Addressing, IJMP and ICALL

Figure 18.

Code Memory Constant Addressing

Indirect Program Memory Addressing

The X, Y or the Z-register is decremented before the operation. Operand address is the decremented contents of the

X, Y or the Z-register.

Data Indirect With Post-Increment

Figure 16.

The X, Y or the Z- register is incr emented af ter the oper ation. Operand address is the content of the X, Y or the Zregister prior to incrementing.

Data Indirect Addressing With Post-Increment

Program execution continues at address contained by the

Z-register (i.e. the PC is loaded with the contents of the Zregister).

Relative Program Addressing, RJMP and RCALL

Figure 19.

Program execution continues at add ress PC + k + 1. The

relative address k is -2048 to 2047.

Relative Program Memory Addressing

9

The EEPROM Data Memory

The AT90S8515 contains 512 bytes of data EE PROM

memory. It is organized as a separate data space, in which

single bytes can be read and written. The EEPROM has an

endurance of at least 100,000 write/erase cycles. The

access between the EEPROM and the CPU is described

on page 32 sp ecifyi ng the EEPRO M address r egisters, the

EEPROM data register, and the EEPROM control register.

For the SPI data downloading, see page 62 for a detailed

description.

Memory Access Times and Instruction

Execution Timing

This section describes the general access timing concepts

for instruction execution and internal memory access.

AVR

The

generated from th e external clock cryst al for the chip. No

internal clock division is used.

Figure 20 shows the parallel instr uction fetches and

instruction executions enabled by the Harvard architecture

and the fast-access register file concept. This is the basic

pipelining concep t to ob tai n up to 1 MIP S per MHz with the

corresponding unique results for functions per cost, functions per clocks, and functions per power-unit.

CPU is driven by the System Clock Ø, directly

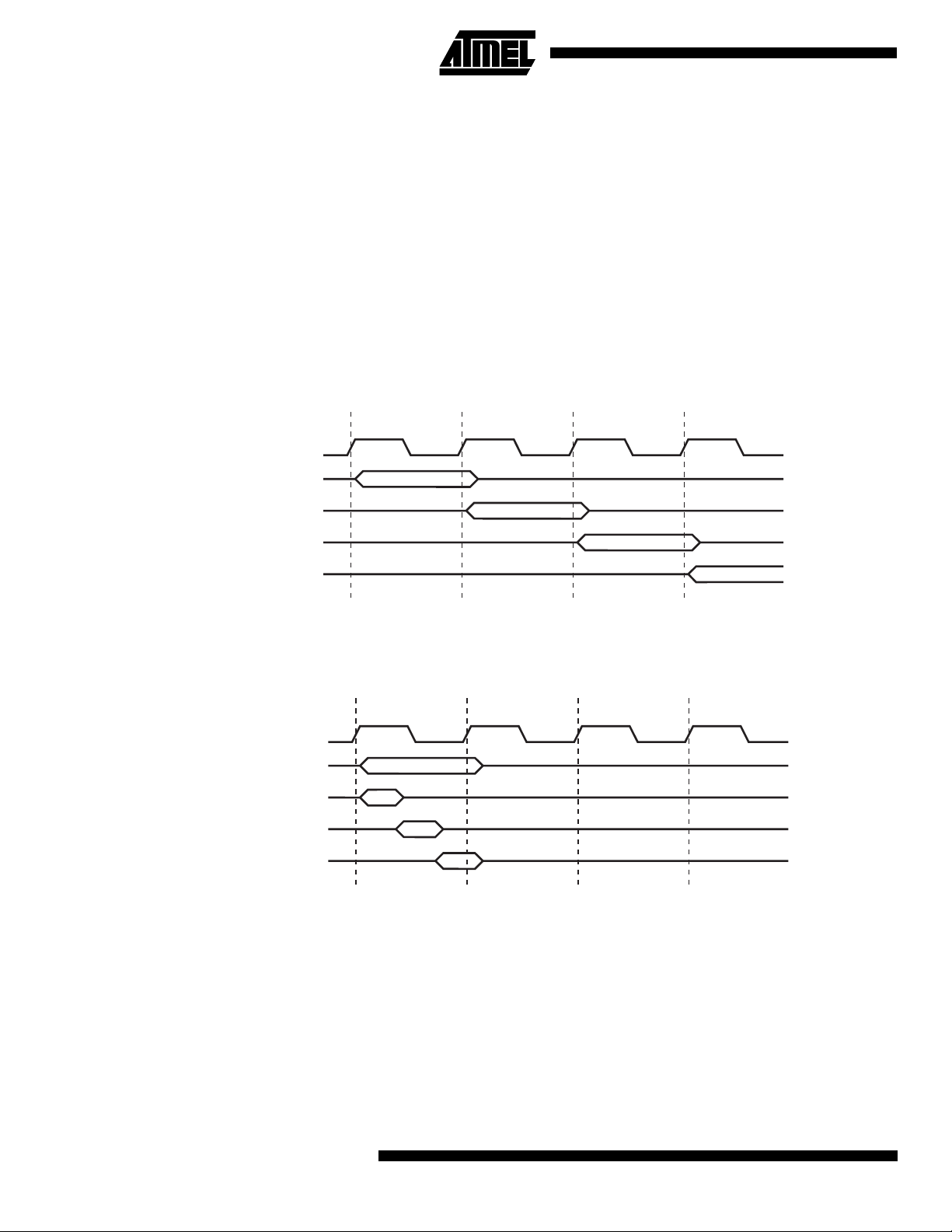

Figure 20.

The Parallel Instruction Fetches and Instruction Executions

T1 T2 T3 T4

System Clock Ø

1st Instruction Fetch

1st Instruction Execute

2nd Instruction Fetch

2nd Instruction Execute

3rd Instruction Fetch

3rd Instruction Execute

4th Instruction Fetch

Figure 21 shows the in ter nal ti min g c oncept for the register

file. In a single clock cycle an ALU operation using two reg-

Figure 21.

Single Cycle ALU Operation

T1 T2 T3 T4

System Clock Ø

Total Execution Time

Register Operands Fetch

ALU Operation Execute

ister operands is executed, and the r esult is stored bac k to

the destination register.

Result Write Back

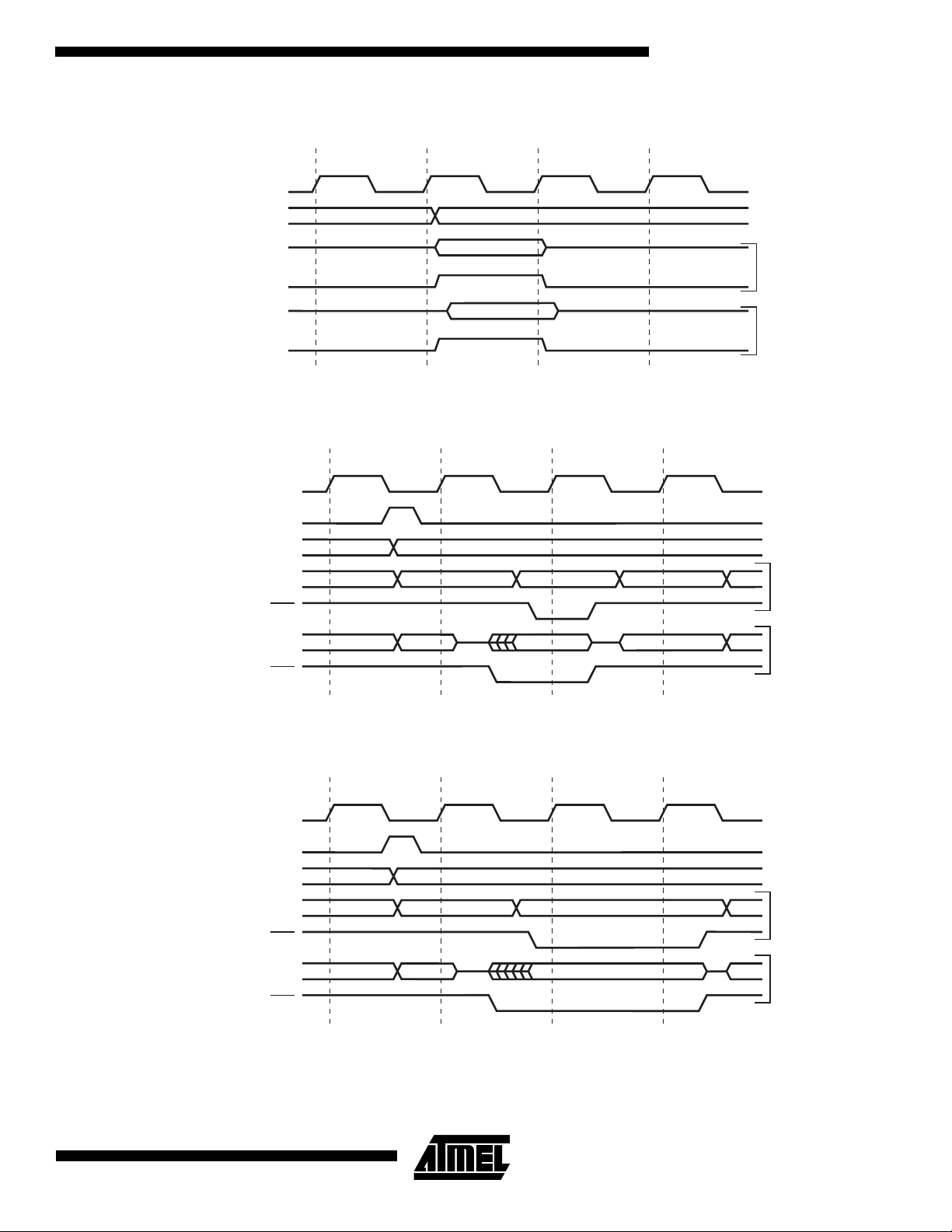

The internal data SRAM access is performed in two System Clock cycles as described in Figure 22.

10

AT90S8515

AT90S8515

Figure 22.

On-Chip Data SRAM Access Cycles

T1 T2 T3 T4

System Clock Ø

Address

Prev. Address

Address

Data

WR

Data

RD

The external data SRAM access is performed in two System Clock cycles as described in Figure 22.

Figure 23.

External Data SRAM Memory Cycles without Wait State

T1 T2 T3

System Clock Ø

ALE

Address [15..8]

Prev. Address

Address

Read Write

Data / Address [7..0]

Prev. Address

Address

Data

Address

WriteRead

WR

Data / Address [7..0]

Prev. Address

Address

Data

Address

RD

The external data SRAM memory access cycle with the Wait State bit enabled (Wait State active) is shown in Figure 24.

Figure 24.

External Data SRAM Memory Cycles with Wait State

T1 T2 T3 T4

System Clock Ø

ALE

WR

RD

Prev. Address

Prev. Address

Prev. Address

Address

Address

Address [15..8]

Data / Address [7..0]

Data / Address [7..0]

Address

Data

Data

Addr.

WriteRead

Addr.

11

I/O Memory

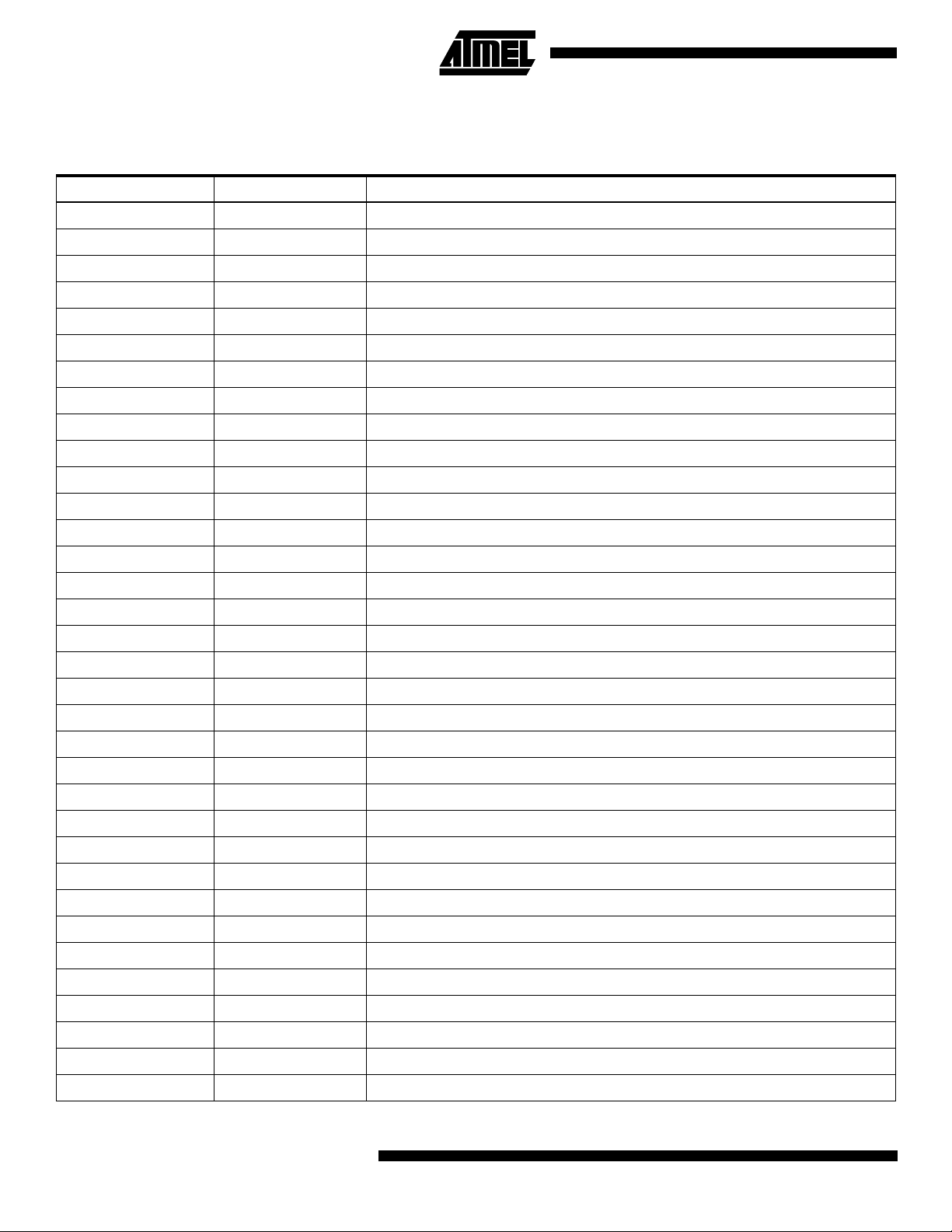

The I/O space definition of the AT90S8515 is shown in the following table:

Table 1.

AT90S8515 I/O Space

Address Hex Name Function

$3F ($5F) SREG Status Register

$3E ($5E) SPH Stack Pointer High

$3D ($5D) SPL Stack Pointer Low

$3B ($5B) GIMSK General Interrupt Mask register

$3A ($5A) GIFR General Interrupt Flag Register

$39 ($59) TIMSK Timer/Counter Interrupt Mask register

$38 ($58) TIFR Timer/Counter Interrupt Flag register

$35 ($55) MCUCR MCU general Control Register

$33 ($53) TCCR0 Timer/Counter0 Control Register

$32 ($52) TCNT0 Timer/Counter0 (8-bit)

$2F ($4F) TCCR1A Timer/Counter1 Control Register A

$2E ($4E) TCCR1B Timer/Counter1 Control Register B

$2D ($4D) TCNT1H Timer/Counter1 High Byte

$2C ($4C) TCNT1L Timer/Counter1 Low Byte

$2B ($4B) OCR1AH Timer/Counter1 Output Compare Register A High Byte

$2A ($4A) OCR1AL Timer/Counter1 Output Compare Register A Low Byte

$29 ($49) OCR1BH Timer/Counter1 Output Compare Register B High Byte

$28 ($48) OCR1BL Timer/Counter1 Output Compare Register B Low Byte

$25 ($45) ICR1H T/C 1 Input Capture Register High Byte

$24 ($44) ICR1L T/C 1 Input Capture Register Low Byte

$21 ($41) WDTCR Watchdog Timer Control Register

$1F ($3E) EEARH EEPROM Address Register High Byte

$1E ($3E) EEARL EEPROM Address Register Low Byte

$1D ($3D) EEDR EEPROM Data Register

$1C ($3C) EECR EEPROM Control Register

$1B ($3B) PORTA Data Register, Port A

$1A ($3A) DDRA Data Direction Register, Port A

$19 ($39) PINA Input Pins, Port A

$18 ($38) PORTB Data Register, Port B

$17 ($37) DDRB Data Direction Register, Port B

$16 ($36) PINB Input Pins, Port B

$15 ($35) PORTC Data Register, Port C

$14 ($34) DDRC Data Direction Register, Port C

$13 ($33) PINC Input Pins, Port C

12

AT90S8515

AT90S8515

Table 1.

Note: reserved and unused locations are not shown in th e table

All the different AT90S8515 I/Os and peripherals are

placed in the I/O space. The different I/O locations are

accessed by the IN and OUT instructions transferring data

between the 32 gener al purpose wo rking regis ters and th e

I/O space. I/O registers wit hin the address range $00 - $ 1F

are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be

AT90S8515 I/O Space (Continued)

Address Hex Name Function

$12 ($32) PORTD Data Register, Port D

$11 ($31) DDRD Data Direction Register, Port D

$10 ($30) PIND Input Pins, Port D

$0F ($2F) SPDR SPI I/O Data Register

$0E ($2E) SPSR SPI Status Register

$0D ($2D) SPCR SPI Control Register

$0C ($2C) UDR UART I/O Data Register

$0B ($2B) USR UART Status Register

$0A ($2A) UCR UART Control Register

$09 ($29) UBRR UART Baud Rate Register

$08 ($28) ACSR Analog Comparator Control and Status Register

When using the I/O specif ic com man ds , IN, OU T, SB IS an d

SBIC, the I/O addresses $00 - $3F must be used. When

addressing I/O registers as SRAM, $20 must be added to

this address. All I/O register addresses throughout this document are shown with the SRAM address in parentheses.

The different I/O and peripherals control registers are

explained in the following ch apte rs.

checked by usi ng the S BI S and S BIC i nst ruc tion s. Re fer to

the instruction set chapter for more details.

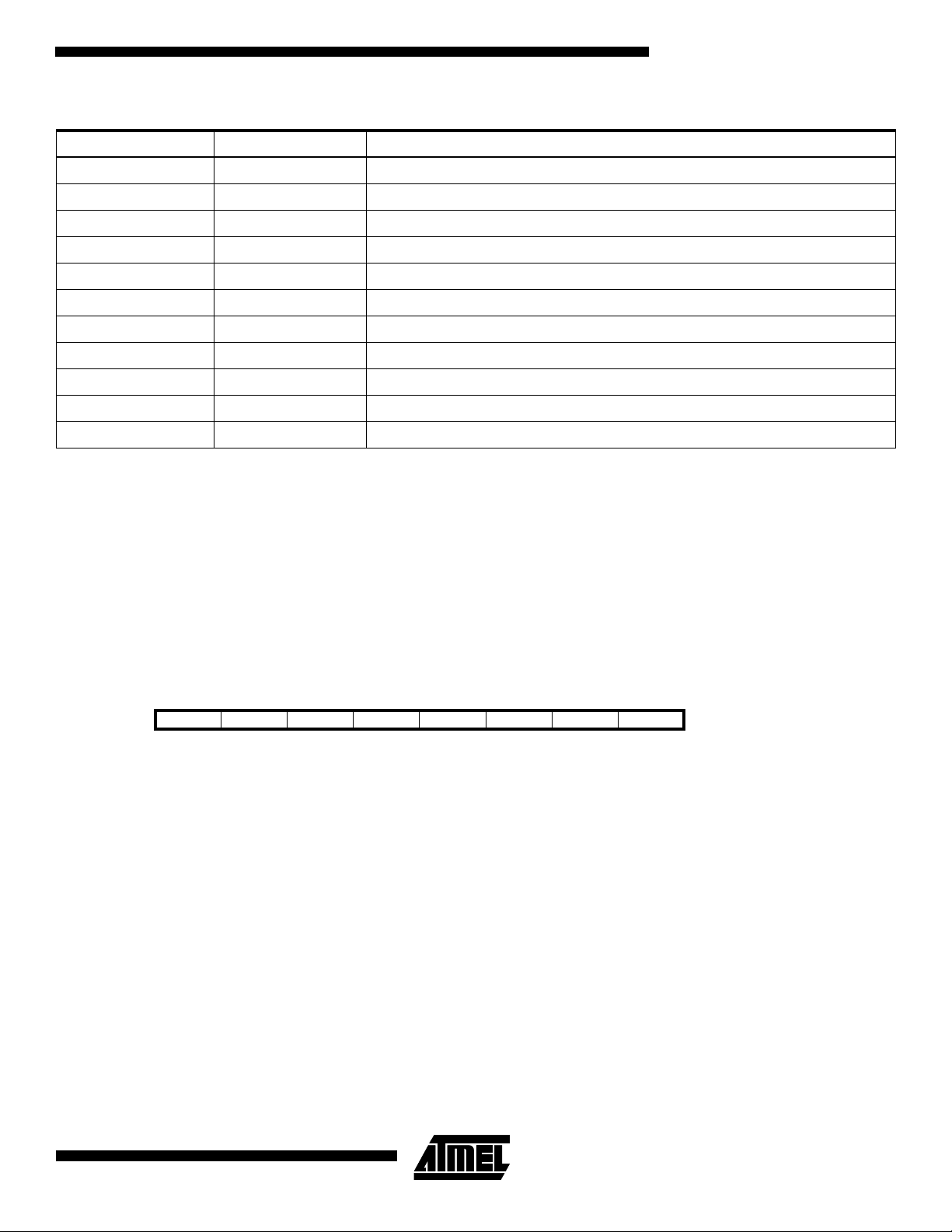

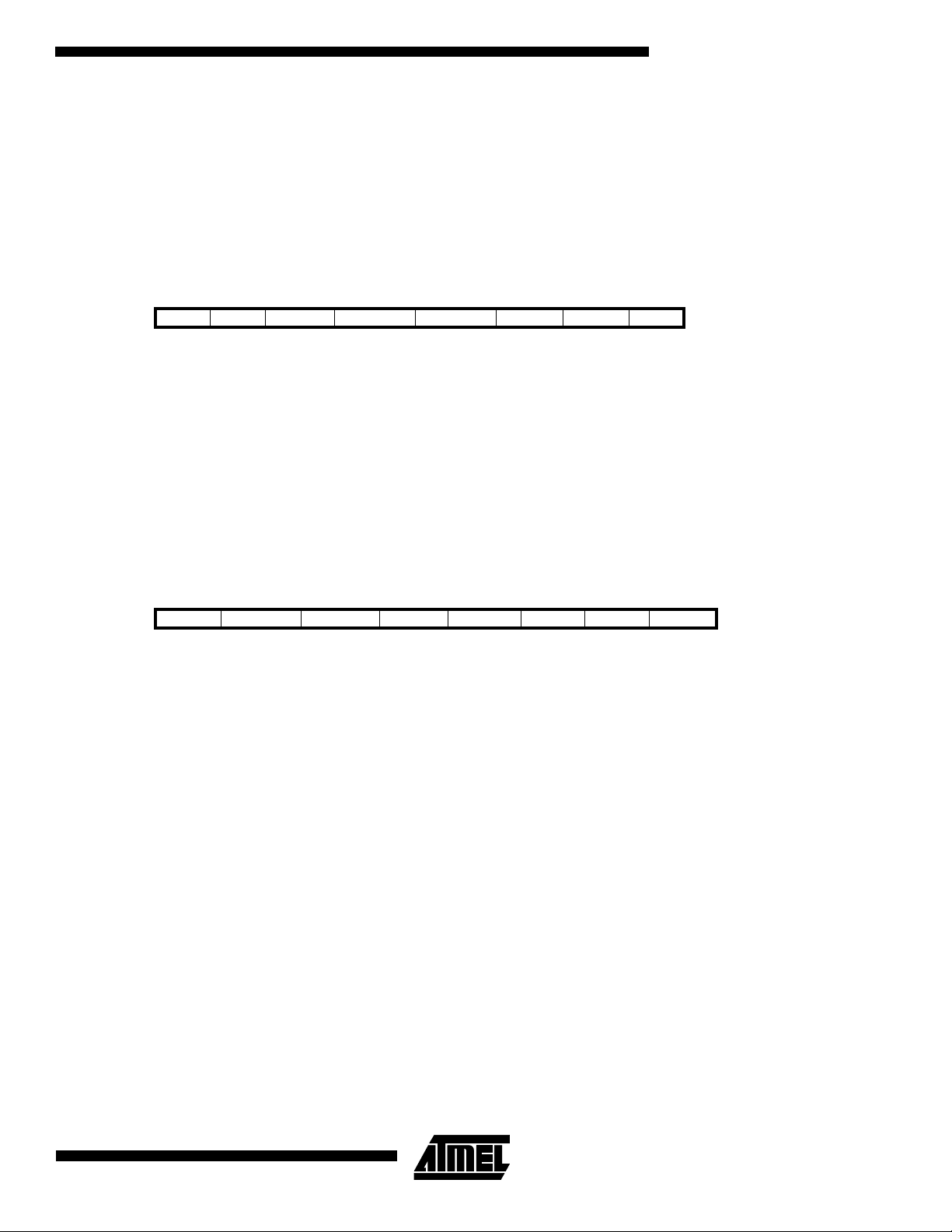

The Status Register - SREG

The AVR status register - SREG - at I/O space location $3F ($5F) is defined as:

Bit 76543210

$3F ($5F)

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial value 0 0 0 0 0 0 0 0

Bit 7 - I: Global Interrupt Enable

•

The global interrupt enable bit must be set (one) for the

interrupts to be enabled. The in dividual int errupt enabl e

control is then perform ed in the interrupt ma sk register s GIMSK and TIMSK. If the global interrupt enable register is

cleared (zero), none of the in terrupts a re en abled indep endent of the GIMSK and TIMSK values. The I-bit is cleared

by hardware after an interrupt has occurred, and is set by

the RETI instruction to enable subsequent interrupts.

Bit 6 - T: Bit Copy Storage

•

The bit copy instructions BLD (Bit LoaD) and BST (Bit

STore) use the T bit as source and destination for the operated bit. A bit from a reg is ter i n th e r eg ist er fi le ca n be c opied into T by the BST instruction, and a bit in T can be

copied into a bit in a registe r in the re gister fi le by the BL D

instruction.

Bit 1 - Z: Zero Flag

•

The zero flag Z indicates a zero result after the different

I T H S V N Z C SREG

Bit 5 - H: Half Carry Flag

•

The half carry flag H indicates a half carry in some arithmetic operations. See the Instruction Set Description for

detailed information.

Bit 4 - S: Sign Bit, S = N ⊕ V

•

The S-bit is always an exclusive or between the negative

flag N and the two’s complement overflow flag V. See the

Instruction Set Description for detailed information.

Bit 3 - V: Two’s Complement Overflow Flag

•

The two’s complement overflow flag V supports two’s complement arithmetics. See the Instruction Set Description for

detailed information.

Bit 2 - N: Negative Flag

•

The negative flag N indicates a negative result after the different arithmetic and logic operation s. See the Ins truction

Set Description for detailed information.

arithmetic and logic operations. See the Instruction Set

Description for detailed information.

13

Bit 0 - C: Carry Flag

•

The carry flag C indicates a c arry in an ar ithmetic or logic

operation. See the Instruction Set Desc ription for detaile d

information.

The Stack Pointer - SP

The general AVR 16-b it Stac k Po inter is ef fectiv ely b uilt u p

of two 8-bit registers in the I/O space l ocations $3E ( $5E)

and $3D ($5D). As the AT90S8515 supports up to 64 kB

external SRAM, all 16-bits are used.

Bit 151413121110 9 8

$3E ($5E)

$3D ($5D)

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial value 0 0 0 0 0 0 0 0

The Stack Poin ter points to the data SR AM stack area

where the Subroutine and Interrupt Stacks are located.

This Stack space in the data SRAM must be defined by the

program before any subroutine calls are executed or interrupts are enabled. The Stack Pointer is decremen ted by

one when data i s pushed o nto the St ack with the PUSH

instruction, and it is decremented by two when data is

pushed onto the St ack with subr outin e CALL and inte rrupt.

The Stack Pointer is incremented by one when data is

popped from th e Stack with the PO P instr uction, and it is

incremented by two when data is popped from the Stack

with return from subroutin e RET or return from interrupt

IRET.

SP15 SP14 SP13 SP12 SP11 SP10 SP9 SP8 SPH

SP7 SP6 SP5 SP4 SP3 SP2 SP1 SP0 SPL

76543210

R/W R/W R/W R/W R/W R/W R/W R/W

00000000

Reset and Interrupt Handling

The AT90S8515 p rovides 12 differe nt interrupt so urces.

These interrupts and the separate reset vector, each have

a separate program vector in the program memory space.

All interrupts are assign ed individual enable bits wh ich

must be set (one) to gether wi th the I -bit in t he stat us r egister in order to enable the interrupt.

The lowest addresses in the program memory space are

automatically defined as the Reset and Interrupt vectors.

The complete list of vectors is shown in Table 2. The list

also determines the priority levels of the different interrupts.

The lower the address the higher is the priority level.

RESET has the highest priority, and next is INT0 - the

External Interrupt Request 0 etc.

14

AT90S8515

AT90S8515

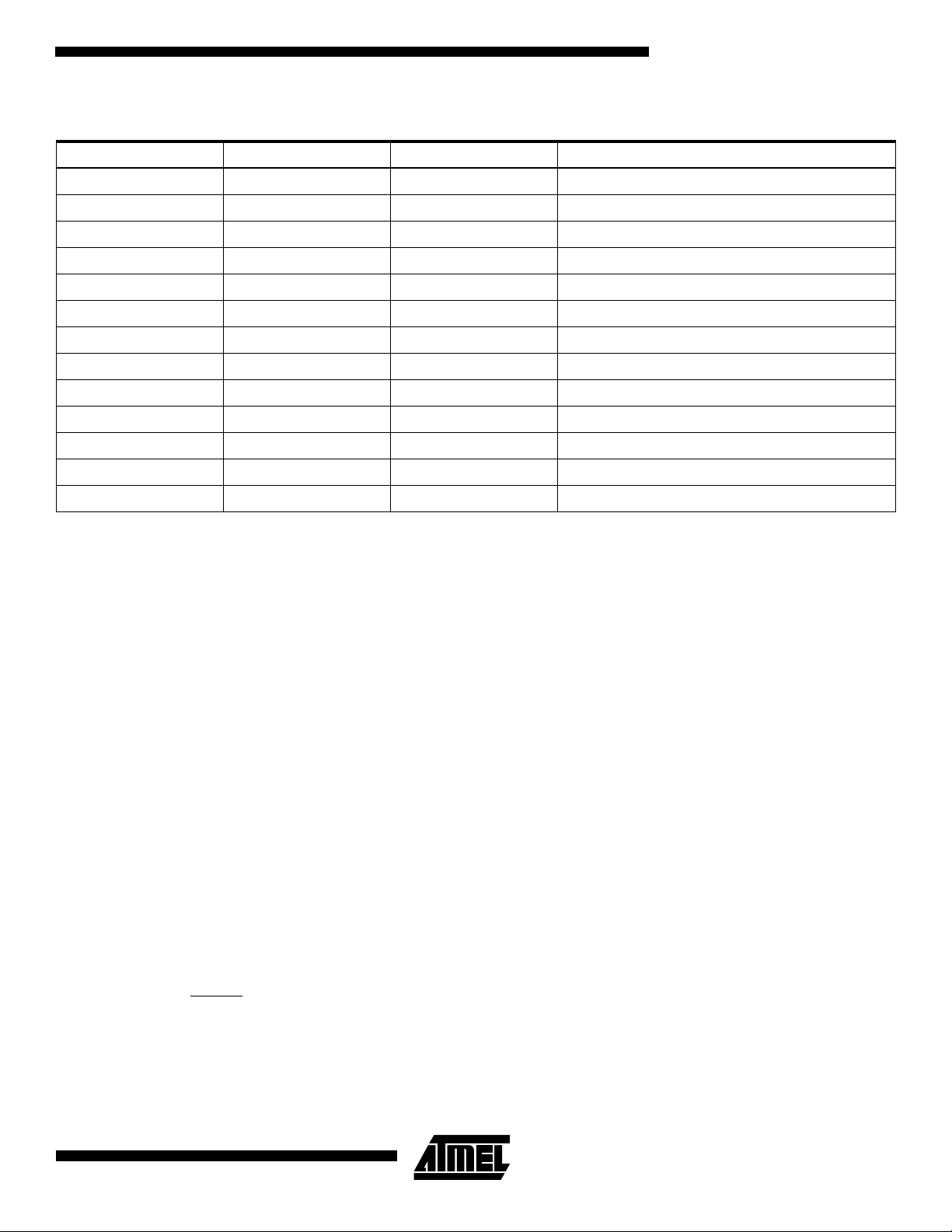

Table 2.

Reset and Interrupt Vectors

Vector No. Program Address Source Interrupt Definition

1 $000 RESET Hardware Pin and Watchdog Reset

2 $001 INT0 External Interrupt Request 0

3 $002 INT1 External Interrupt Request 1

4 $003 TIMER1 CAPT Timer/Counter1 Capture Event

5 $004 TIMER1 COMPA Timer/Counter1 Compare Match A

6 $005 TIMER1 COMPB Timer/Counter1 Compare Match B

7 $006 TIMER1 OVF Timer/Counter1 Overflow

8 $007 TIMER0, OVF Timer/Counter0 Overflow

9 $008 SPI, STC Serial Transfer Complete

10 $009 UART, RX UART, Rx Complete

11 $00A UART, UDRE UART Data Register Empty

12 $00B UART, TX UART, Tx Complete

13 $00C ANA_COMP Analog Comparator

The most typical and general program setup for the Reset and Interrupt Vector Addresses are:

Address Labels Code Comments

$000 rjmp RESET ; Reset Handler

$001 rjmp EXT_INT0 ; IRQ0 Handler

$002 rjmp EXT_INT1 ; IRQ1 Handler

$003 rjmp TIM1_CAPT ; Timer1 Capture Handler

$004 rjmp TIM1_COMPA ; Timer1 CompareA Handler

$005 rjmp TIM1_COMPB ; Timer1 CompareB Handler

$006 rjmp TIM1_OVF ; Timer1 Overflow Handler

$007 rjmp TIM0_OVF ; Timer0 Overflow Handler

$008 rjmp SPI_STC ; SPI Transfer Complete Handler

$009 rjmp UART_RXC ; UART RX Complete Handler

$00a rjmp UART_DRE ; UDR Empty Handler

$00b rjmp UART_TXC ; UART TX Complete Handler

$00c rjmp ANA_COMP ; Analog Comparator Handler

;

$00d MAIN: <instr> xxx ; Main program start

… … … …

Reset Sources

The AT90S8515 has three sources of reset:

• Power-On Reset. The MCU is reset when a supply

voltage is applied to the V

and GND pins.

CC

• External Reset. The MCU is reset when a low level is

present on the RESET

pin for more than two XTAL

cycles.

• Watchdog Reset. The MCU is reset when the Watchdog

timer period expires and the Watchdog is enabled.

During reset, all I/O registers are then set to their initial values, and the program starts execution from address $000.

The instruction placed i n a ddr ess $000 mus t b e an RJM P relative jump - instruction to the reset handling routine. If

the program never enables an interrupt source, the interrupt vectors are not used, and regular program code can

be placed at these locations. The circuit diagram in Figure

25 shows the reset logic. Table 3 defines the timing and

electrical parameters of the reset circuitry.

15

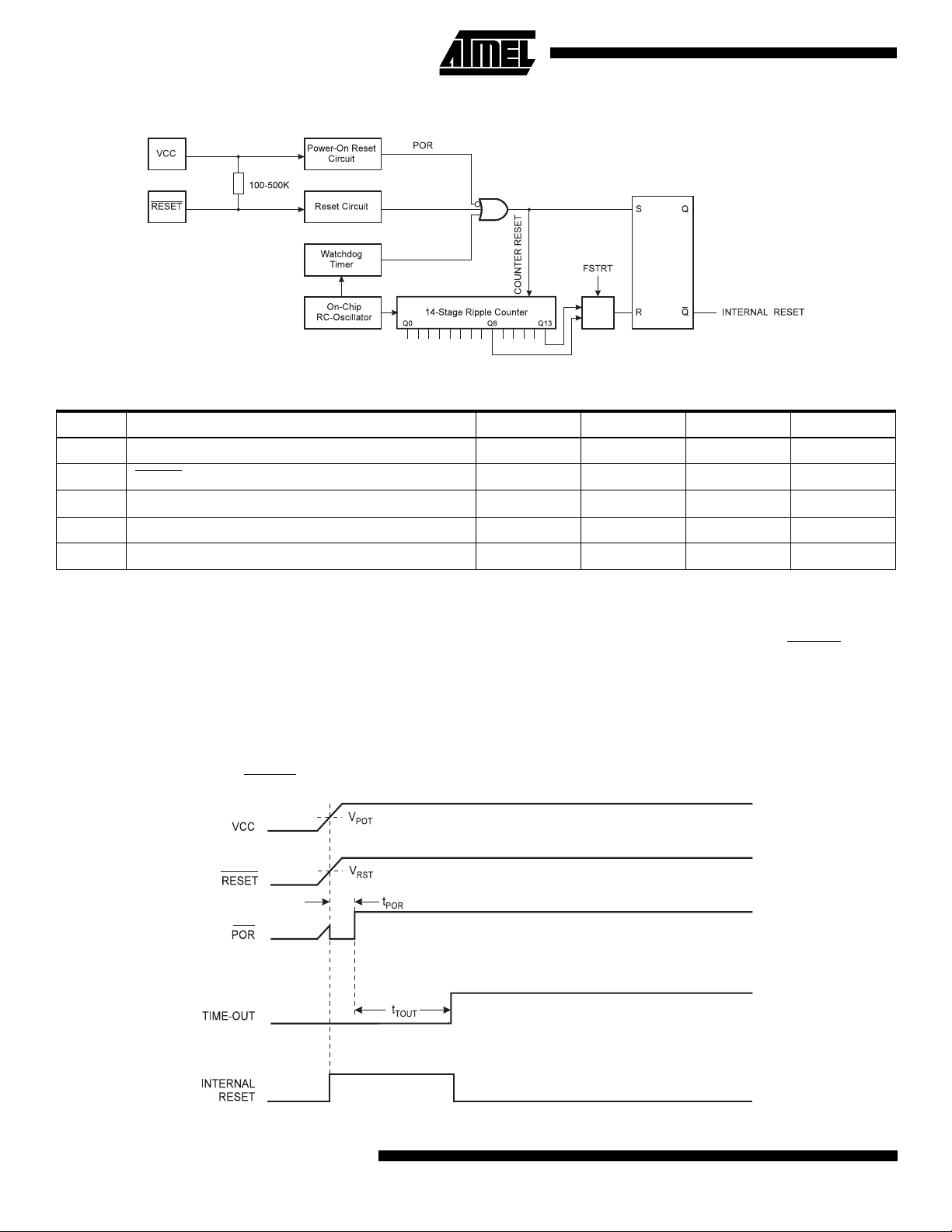

Figure 25.

Reset Logic

Table 3.

Symbol Parameter Min Typ Max Units

V

V

t

POR

t

TOUT

t

TOUT

Reset Characteristics (V

POT

RST

Power-On Reset Threshold Voltage 1.8 2 2.2 V

RESET Pin Threshold Voltage VCC/2 V

Power-On Reset Period 2 3 4 ms

Reset Delay Time-Out Period FSTRT Unprogrammed 11 16 21 ms

Reset Delay Time-Out Period FSTRT Programmed 1.0 1.1 1.2 ms

= 5.0V)

CC

Power-on Reset

A Power-On Reset (POR) circui t ensures that the dev ice is

not started until V

has reached a s afe level . As s how n in

CC

Figure 25, an internal timer clocked from the Watchdog

timer oscillator preven ts the MCU from star ting until after a

certain period after V

old voltage - V

POT

has reached the Power-On Thresh-

CC

, regardless of the VCC rise time (s e e Fi g ure 26 and Figure 27). The total reset period is the PowerOn Reset period - t

+ the Delay Time- ou t p erio d - t

POR

TOUT

give a shorter start-up time if a ceramic resonator or any

other fast-start oscillator is used to clock the MCU.

If the build-in start-up delay is suffic ient, RESET

connected to V

By holding the pin low for a period after V

directly or via an external pull-up resistor.

CC

CC

applied, the Power-On Reset period can be extended.

Refer to Figure 28 for a timing example on this.

.

has been

The FSTRT fuse bi t in the Flash can be programmed to

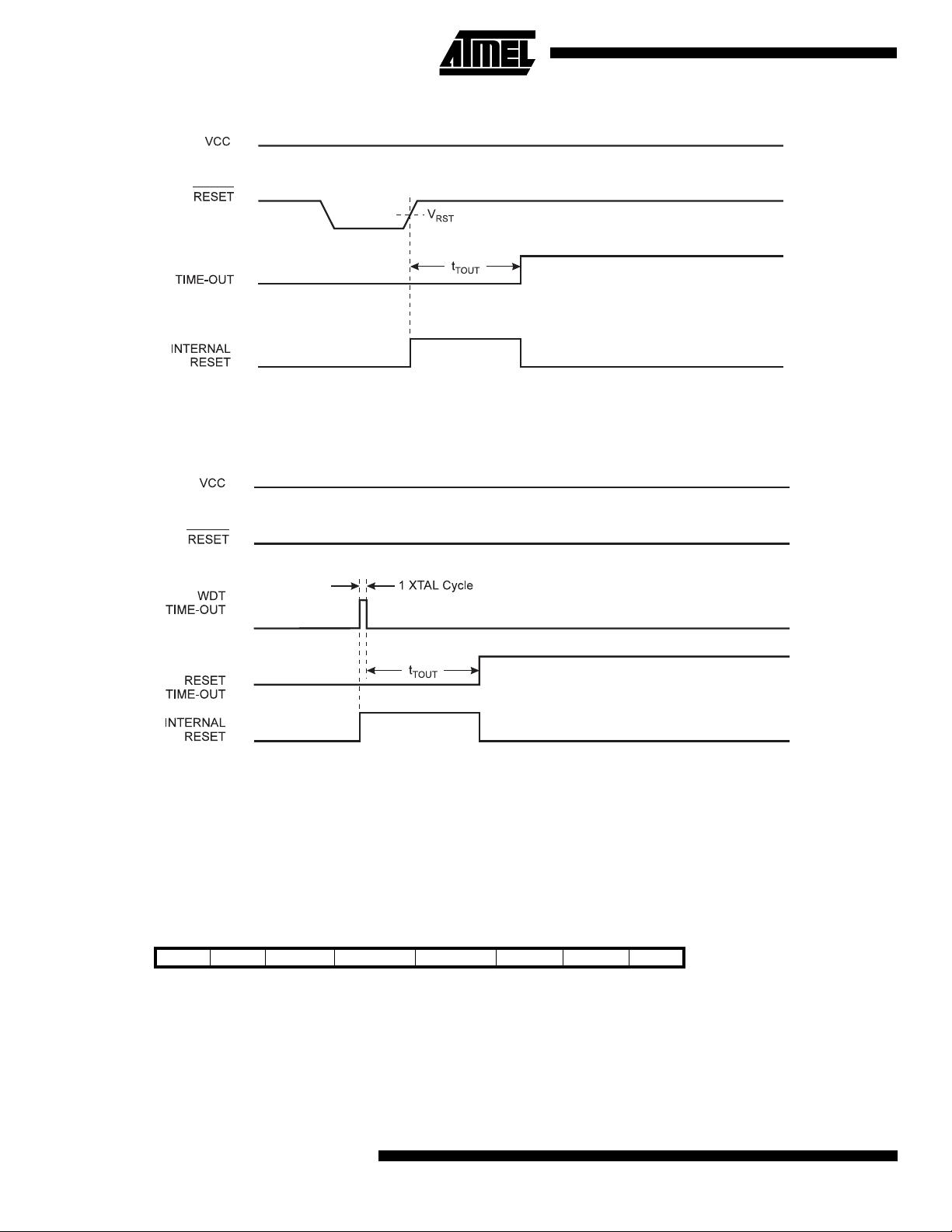

Figure 26.

MCU Start-Up, RESET

Tied to VCC. Rapidly Rising V

CC

can be

16

AT90S8515

AT90S8515

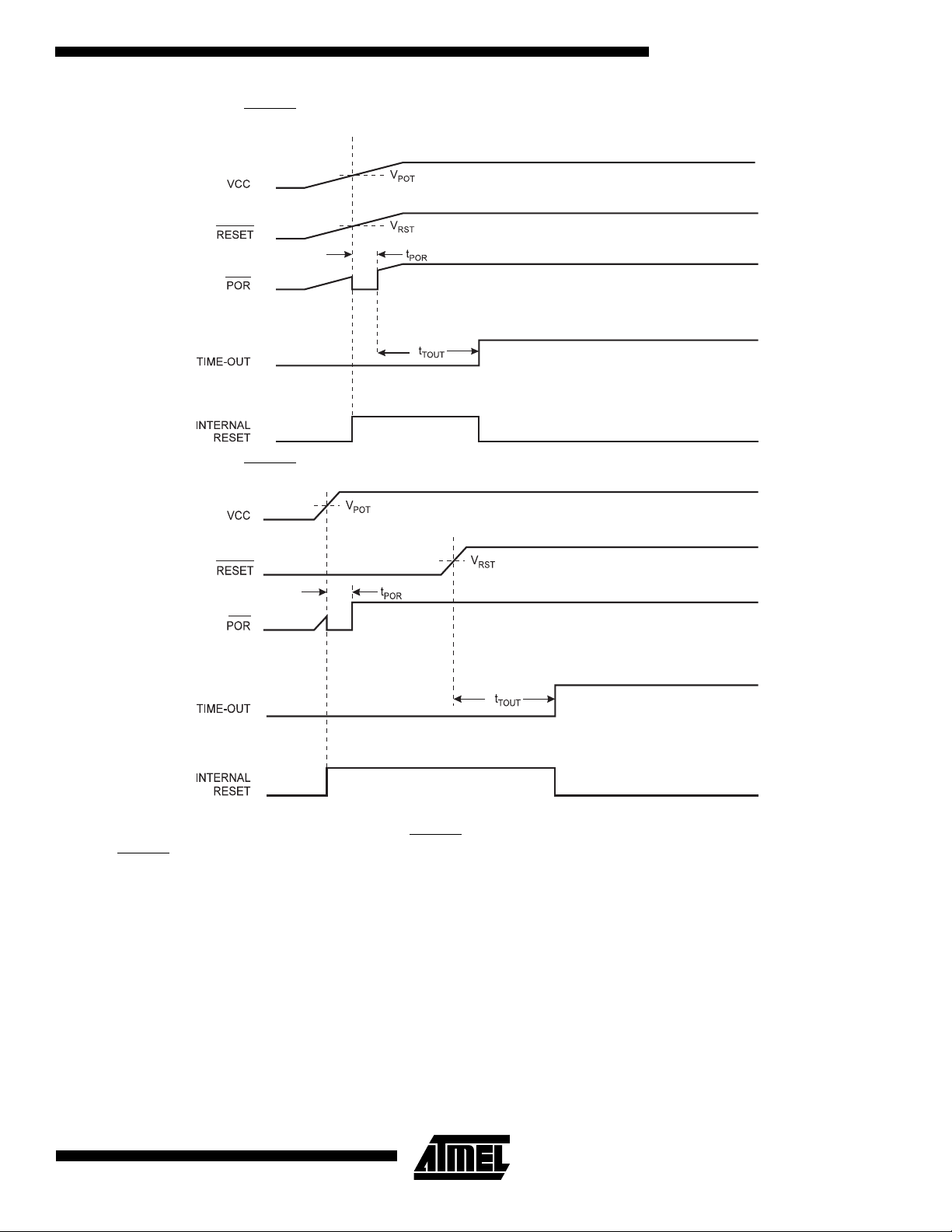

Figure 27.

Figure 28.

MCU Start-Up, RESET

MCU Start-Up, RESET

Tied to VCC or Unconnected. Slowly Rising V

Controlled Externally

CC

External Reset

An external reset is generated by a low level on the RESET

pin. The RESET pin mus t be hel d low fo r at leas t two cry stal clock cycles. When the applied signal reaches the Reset

Threshold Voltage - V

timer starts the MCU after the Time-out period t

on its positive edge, the delay

RST

TOUT

has

expired.

17

Figure 29.

External Reset During Operation

Watchdog Reset

When the Watchdog times out, it will generate a short reset

pulse of 1 XTAL cycle duration. On the falling edge of this

Figure 30.

Watchdog Reset During Operation

Interrupt Handling

The AT90S8515 has two 8-bit In terrupt M ask contr ol regi sters; GIMSK - General Interrupt Mask register and TIMSK Timer/Counter Interrupt Mask register.

When an interrupt occurs, the Global Interrupt Enable I-bit

is cleared (zero) and all inter rupts are dis abled. The us er

software must set (one) the I-bit to enable interrupts.

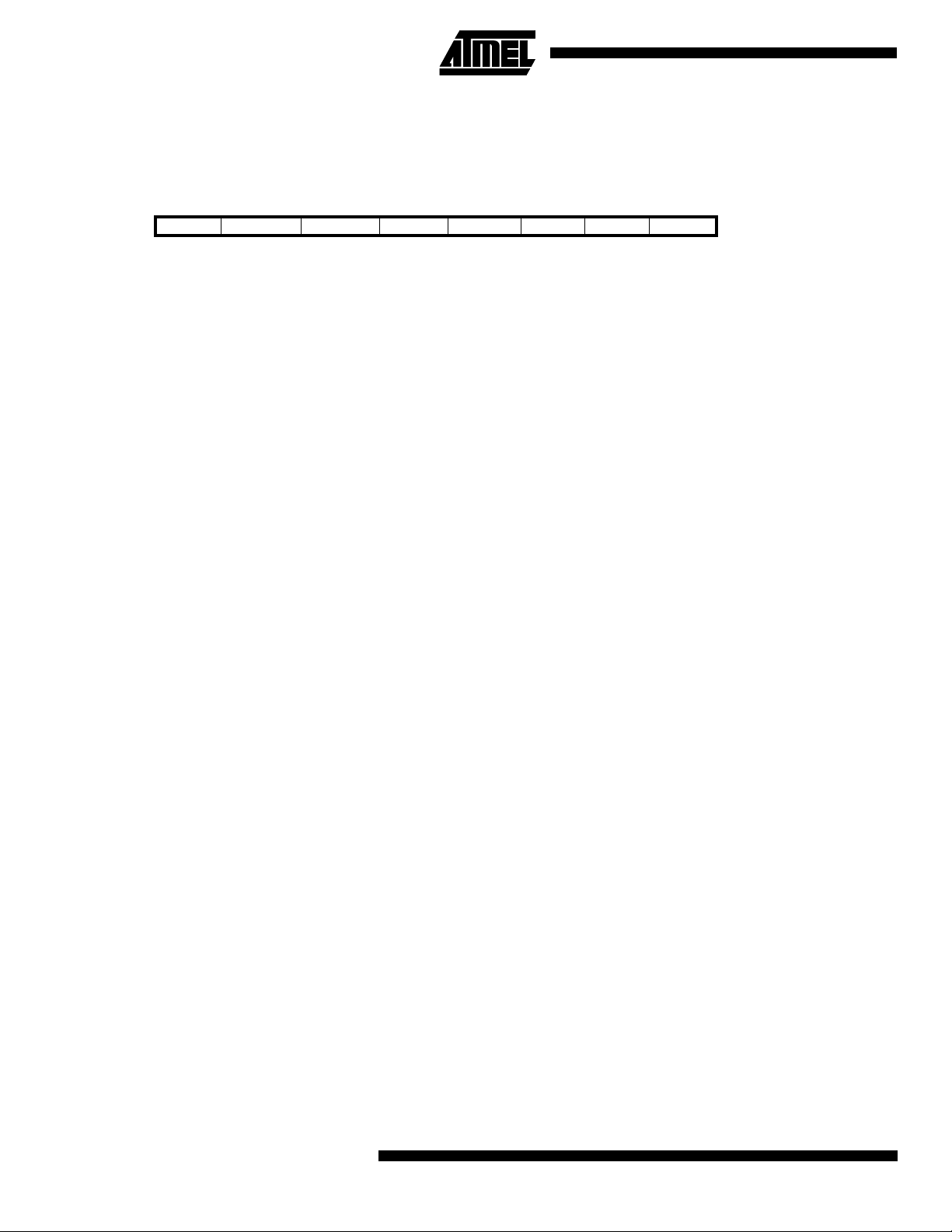

The General Interrupt Mask Register - GIMSK

pulse, the delay tim er starts counting the Time-out period

. Refer to page 30 for details on operation of the

t

TOU T

Watchdog.

When the Program Counter is vectored to the actual interrupt vector in order to execute the interrupt handling routine, hardware clears the corresponding flag that generated

the interrupt. Some of the interrupt flags can also be

cleared by writing a logic one to the flag bit position(s) to be

cleared.

Bit 7 6 5 4 3 2 1 0

$3B ($5B)

Read/Write R/W R/W R R R R R R

Initial value 0 0 0 0 0 0 0 0

Bit 7 - INT1: External Interrupt Request 1 Enable

•

When the INT1 bit is set (one) and the I-bit in the Status

Register (SREG) is set (one), the external pin interrupt is

activated. The Interrupt Sense Control1 bits 1/0 (ISC11 and

ISC10) in the MCU general Control Register (MCUCR)

INT1 INT0 - - - - - - GIMSK

or falling edge of the INT1 pin or level sensed. Ac tivity on

the pin will cause an interrupt request even if INT1 is configured as an ou tput. The corre spond ing int errupt of External Interrupt Request 1 is executed from program memory

address $002. See also “External Interrupts”.

defines whether the exter nal int err upt is acti vated on risin g

18

AT90S8515

Bit 6 - INT0: External Interrupt Request 0 Enable

•

When the INT0 bit is set (one) and the I-bit in the Status

Register (SREG) is set (one), the external pin interrupt is

activated. The Interrupt Sense Control0 bits 1/0 (ISC01 and

ISC00) in the MCU general Control Register (MCUCR)

defines whether the exter nal int err upt is acti vated on risin g

figured as an ou tput. The corre spond ing int errupt of External Interrupt Request 0 is executed from program memory

address $001. See also “External Interrupts.”

Bits 5..0 - Res: Reserved bits

•

These bits are reserved bits in the A T90S 8515 a nd always

read as zero.

or falling edge of the INT0 pin or level sense d. Activity on

the pin will cause an interrupt request even if INT0 is con-

The General Interrupt Flag Register - GIFR

Bit 7 6 5 4 3 2 1 0

$3A ($5A)

Read/Write R/W R/W R R R R R R

Initial value 0 0 0 0 0 0 0 0

Bit 7 - INTF1: External Interrupt Flag1

•

When an event on the IN T1 pin triggers an interr upt

request, INTF1 becomes set (one). If the I-bit in SREG and

the INT1 bit in GIMSK are set (one), the MCU will jump to

the interrupt vector at address $002. The fl ag is clea red

when the interrupt routine is executed. Alternatively, the

flag can be cleared by writing a logical one to it.

Bit 6 - INTF0: External Interrupt Flag0

•

INTF1 INTF0 - - - - - - GIFR

the INT0 bit in GIMSK are set (one), the MCU will jump to

the interrupt vector at address $001. The f lag is cl eared

when the interrupt routine is executed. Alter natively, the

flag can be cleared by writing a logical one to it.

Bits 5..0 - Res: Reserved bits

•

These bits are reserved bits in the A T90S 8515 a nd always

read as zero.

When an event on the IN T0 pin triggers an interr upt

request, INTF0 becomes set (one). If the I-bit in SREG and

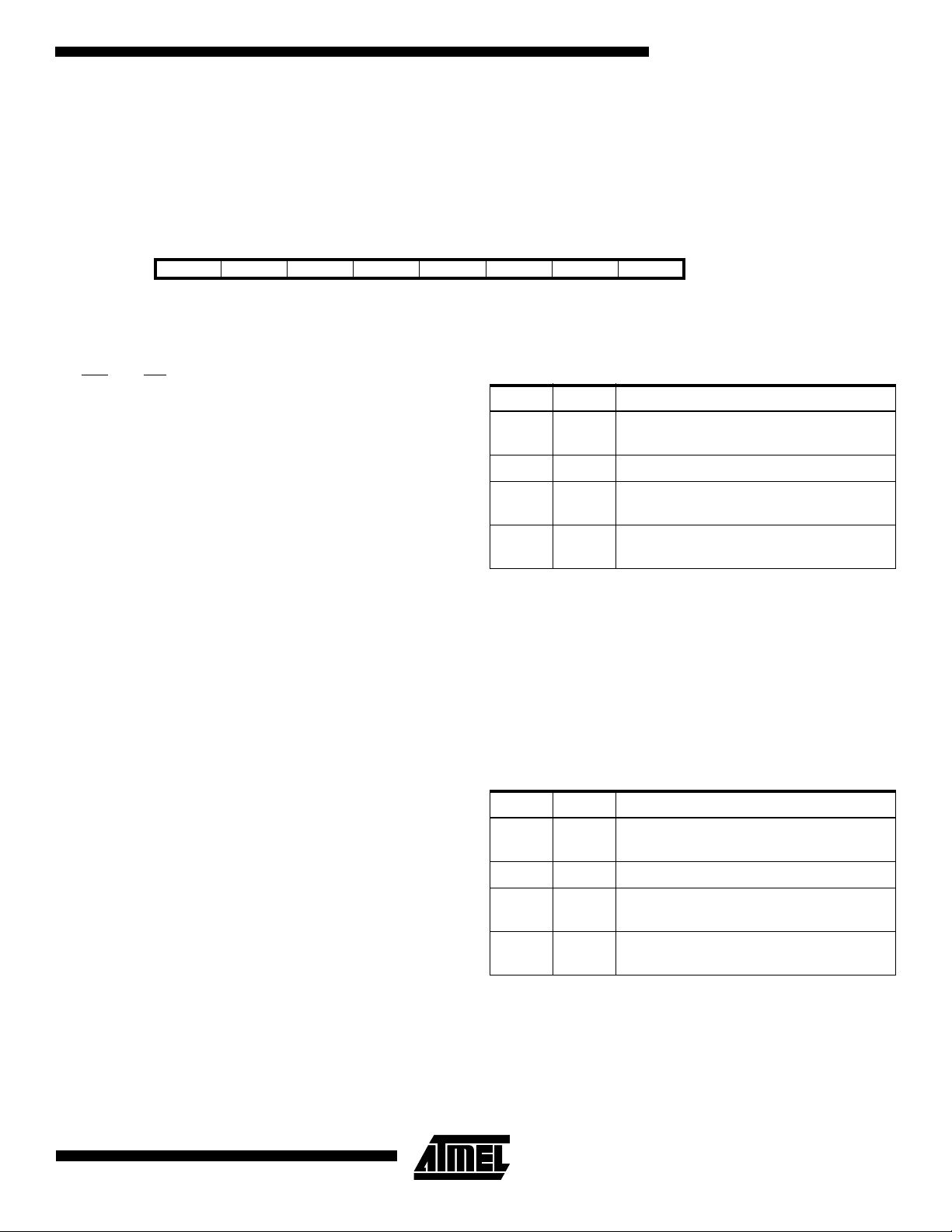

The Timer/counter Interrupt Mask Register - TIMSK

Bit 7 6 5 4 3 2 1 0

$39 ($59)

Read/Write R/W R/W R/W R R/W R R/W R

Initial value 0 0 0 0 0 0 0 0

Bit 7 - TOIE1: Timer/Counter1 Overflow Interrupt Enable

•

When the TOIE1 bit is set (one) and the I-bit in the Status

Register is set (one), the Timer/Counter1 Overflow interrupt

is enabled. The corresponding interrupt (at vector $006) is

executed if an overflo w in Timer/Counter1 occ urs. The

Overflow Flag (Timer/Counter1) is set (one) in the

Timer/Counter Interrupt Flag Register - TIFR. When

Timer/Counter1 is in PWM mode, the Timer Over flow flag

is set when the counter changes counting direction at

$0000.

Bit 6 - OCE1A:Timer/Counter1 Output CompareA Match

•

Interrupt Enable

When the OCIE1A bit is set (one) and the I-bit in the Status

Register is set (one), the Timer/Counter1 CompareA Match

interrupt is enabled. The corresponding interrupt (at vector

$004) is executed if a Compa reA matc h in Timer/Cou nter1

occurs. The Compare A Flag in Tim er /Cou nter1 is s et (o ne)

in the Timer/Counter Interrupt Flag Register - TIFR.

Bit 5 - OCIE1B:Timer/Counter1 Output CompareB Match

•

Interrupt Enable

When the OCIE1B bit is set (one) and the I-bit in the Status

Register is set (one), the Timer/Counter1 CompareB Match

interrupt is enabled. The corresponding interrupt (at vector

TOIE1 OCIE1A OCIE1B - TICIE1 - TOIE0 - TIMSK

occurs. The CompareB Flag in Timer/Counter1 is set (o ne)

in the Timer/Counter Interrupt Flag Register - TIFR.

Bit 4 - Res: Reserved bit

•

This bit is a reserved bit in the AT90S8515 and always

reads zero.

Bit 3 - TICIE1: Timer/Counter1 Input Capture Interrupt

•

Enable

When the TICIE1 bit is set (one) an d the I-b it in the S tatus

Register is set (one), the Timer/Counter1 Input Capture

Event Interrupt is enabled. The corresponding interrupt (at

vector $003) is executed if a capture-triggering event

occurs on pin 31, ICP. The Input Capture Flag i n

Timer/Counter1 is set (one) in the Timer/Counter Interrupt

Flag Register - TIFR.

Bit 2 - Res: Reserved bit

•

This bit is a reserved bit in the AT90S8515 and always

reads zero.

Bit 1 - TOIE0: Timer/Counter0 Overflow Interrupt Enable

•

When the TOIE0 bit is set (one) and the I-bit in the Status

Register is set (one), the Timer/Counter0 Overflow interrupt

is enabled. The corresponding interrupt (at vector $008) is

executed if an overflow in Timer/Counter0 occur s. The

$005) is executed if a Compa reB matc h in Timer/Cou nter1

AT90S8515

19

Bit 0 - Res: Reserved bit

Overflow Flag (Timer0) is set (one) in the Timer/Counter

Interrupt Flag Register - TIFR.

•

This bit is a reserved bit in the AT90S8515 and always

reads zero.

The Timer/Counter Interrupt Flag Register - TIFR

Bit 7 6 5 4 3 2 1 0

$38 ($58)

Read/Write R/W R/W R/W R R/W R R/W R

Initial value 0 0 0 0 0 0 0 0

Bit 7 - TOV1: Timer/Counter1 Overflow Flag

•

The TOV1 is set (one) when an overflow occurs in

Timer/Counter1. TOV1 is cleared b y hardware when executing the cor resp ond ing interrupt hand li ng vector. Alternatively, TOV1 is cleared by writing a logic one to the flag.

When the I-bit in SREG, and TOIE1 (Timer/Counter1 Overflow Interrupt Enable), and TOV1 are set (one), the

Timer/Counter1 Overflow In terrupt is executed. In PWM

mode, this bit is set when Timer/Counter1 changes counting direction at $0000.

Bit 6 - OCF1A: Output Compare Flag 1A

•

The OCF1A bit is set (one) when compare match occurs

between the Timer/Counter1 and the data in OCR1A - Output Compare Register 1A. OCF1A is cleared by hardware

when executing the corresponding interrupt handling vector. Alternatively, OCF1A is cleared by writing a logic one to

the flag. When the I-bit in SREG, and OCIE1A

(Timer/Counter1 Comp are match Interrup tA Enable), an d

the OCF1A are set (one), the Timer/Counter1 Compare

match Interrupt is executed.

Bit 5 - OCF1B: Output Compare Flag 1B

•

The OCF1B bit is set (one) when compare match occurs

between the Timer/Counter1 and the data in OCR1B - Output Compare Register 1B. OCF1B is cleared by hardware

when executing the corresponding interrupt handling vector. Alternatively, OCF1B is cleared by writing a logic one to

the flag.. When the I-bit in SREG, and OCIE1B

(Timer/Counter1 Comp are match Interrup tB Enable), an d

the OCF1B are set (one), the Timer/Counter1 Compare

match Interrupt is executed.

Bit 4 - Res: Reserved bit

•

This bit is a reserved bit in the AT90S8515 and always

reads zero.

Bit 3 - ICF1: - Input Capture Flag 1

•

The ICF1 bit is set (one) to flag an input capture event, indicating that the Timer/Counter1 value has been transferred

to the input capture register - ICR1. ICF 1 is cleared by

hardware when ex ecutin g the cor respo nding int errupt handling vector. Alternatively, ICF1 is cleared by writing a logic

one to the flag.

Bit 2 - Res: Reserved bit

•

This bit is a reserved bit in the AT90S8515 and always

reads zero.

TOV1 OCF1A OCIFB - ICF1 - TOV0 - TIFR

Bit 1 - TOV: Timer/Counter0 Overflow Flag

•

The bit TOV0 is set (one) when an ov erflow occurs in

Timer/Counter0. TOV0 is cleared b y hardware when executing the corresp ond ing i nte rrup t h and li ng v ect or. A lt er natively, TOV0 is cleared by writing a logic one to the flag.

When the SREG I-bit, and TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set (one), the

Timer/Counter0 Overflow interrupt is executed.

Bit 0 - Res: Reserved bit

•

This bit is a reserved bit in the AT90S8515 and always

reads zero.

External Interrupts

The external interrupts are triggered by the INT1 and INT0

pins. Observe that, if enabled, the interrupts will trigger

even if the INT0/INT1 pins are configured as outputs. This

feature provides a way of gen erating a s oftware interrupt.

The external interrupts can be triggered by a falling or rising edge or a low level. This is set up as indicated in the

specification for the MCU Control Register - MCUCR.

When the external interrupt is enabled and is configured as

level triggered, the interrupt will trigger as long as the pin is

held low.

The external interrupts are set up as described in the specification for the MCU Control Register - MCUCR.

Interrupt Response Time

The interrupt execu tion respons e for all the enable d

interrupts is 4 clock cycles minimum. 4 clock cycles after

the interrupt flag has be en s et, the program vector address

for the actual interrupt han dling routine is exec uted. Durin g

this 4 clock cycle period, the Program Counter (2 bytes) is

pushed onto the Stack, and the Stack Pointer is decremented by 2. The vector is a relative jump to the interrupt

routine, and this jump takes 2 clock cycles. If an interrupt

occurs during execution of a multi-cycle i nstructio n, this

instruction is completed before the interrupt is served.

A return from an interrupt hand ling routi ne (same as for a

subroutine call routine) takes 4 clock cycles. During these 4

clock cycles, the Program Counter (2 bytes) is popped

back from the Sta ck, and th e Stack Point er is inc remente d

by 2. When the AVR exits fro m an interrupt, it will always

return to the main program and execute one more instruction before any pending interrupt is served.

Note that th e Status Regi ster - SREG - is n ot han dled by

the AVR hardware, neither for interrupts nor for subrou-

AVR

20

AT90S8515

AT90S8515

tines. For the interrupt handling routines requiring a storage

of the SREG, this must be performed by user software.

For Interrupts trigger ed by events that can remai n static

(E.g. the Output Compare Register1 A matching the value

of Timer/Counter1) the interrupt flag is set when the event

occurs. If the interrupt fla g is c leared an d the int errupt c ondition persists, the fla g wil l n ot be se t unti l t he ev en t occu rs

the next time.

MCU Control Register - MCUCR

The MCU Control Register contains control bits for general MCU functions.

Bit 76543210

$35 ($55)

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial value 0 0 0 0 0 0 0 0

Bit 7 - SRE: External SRAM Enable

•

When the SRE bit is set (one), the external data SRAM is

enabled, and the pin functions AD0 -7 (P ort A) , A8-15 (P ort

C), WR

and RD (Port D) are activated as the alternate pin

functions. Then the SRE bit overrides any pin direction settings in the respective data direction registers. See “The

SRAM Data Memory - Internal and External” for description

of the External SRAM pin functions. When the SRE bit is

cleared (zero), the external data SRAM is disabled, and the

normal pin and data direction settings are used.

Bit 6 - SRW: External SRAM Wait State

•

When the SRW bit is set (one), a one cy cle wait state is

inserted in the external data SRAM access cycle. When the

SRW bit is cl eared ( zero) , the exte rnal data S RAM ac cess

is executed with the normal three-cycle scheme. See Figure 23: External Data SRAM Memory Cycles without Wait

State and Figure 24: External Data SRAM Memory Cycles

with Wait State.

Bit 5 - SE: Sleep Enable

•

The SE bit must be set (one) to make the MCU enter the

sleep mode when the SLEEP instruction is executed. To

avoid the MCU entering the sleep mode unless it is the programmers purpose, it is recommended to set the Sleep

Enable SE bit just befor e the execution of the SLEEP

instruction.

Bit 4 - SM: Sleep Mode

•

This bit selects be tween the two av ailable sleep modes.

When SM is cleared (zero) , Idle Mode is sele cted as Slee p

Mode. When SM is set (one), Power Down mode is

selected as sleep mode. For details, r efer to the par agrap h

“Sleep Modes” below.

Bit 3, 2 - ISC11, ISC10: Interrupt Sense Control 1 bit 1 and

•

bit 0

The External Interrupt 1 is activated by the external pin

INT1 if the SR EG I-flag and the corre spondin g interrup t

mask in the GIMSK is set. The level and edges on the

SRE SRW SE SM ISC11 ISC10 ISC01 ISC00 MCUCR

external INT1 pin that activ ate the interru pt are defined i n

the following table:

Table 4.

ISC11 ISC10 Description

Note: When changing the ISC11/ISC10 bits, INT1 must be dis-

Interrupt 1 Sense Control

00

01Reserved

10

11

abled by clearing its Interrupt Enable bit in the GIMSK

Register. Otherwise an inte rrupt can oc cu r w hen the bits

are changed.

The low level of INT1 generates an

interrupt request.

The falling edge of INT1 generates an

interrupt request.

The rising edge of INT1 generates an

interrupt request.

• Bit 1, 0 - ISC01, ISC00: Interrupt Sense Control 0 bit 1 and

bit 0

The External Interrupt 0 is activated by the external pin

INT0 if the SREG I-flag and the corresponding interrupt

mask is set. The level and edges on the external INT0 pin

that activate the interrupt are defined in the following table:

Table 5.

ISC01 ISC00 Description

Note: When changing the ISC10/ISC00 bits, INT0 must be dis-

Interrupt 0 Sense Control

00

01Reserved

10

11

abled by clearing its Interrupt Enable bit in the GIMSK

Register. Otherwise an inte rrupt can oc cu r w hen the bits

are changed.

The low level of INT0 generates an

interrupt request.

The falling edge of INT0 generates an

interrupt request.

The rising edge of INT0 generates an

interrupt request.

21

Sleep Modes

To enter the sleep modes, the SE bit in MCUCR must be

set (one) and a SLEEP instruction must be executed. If an

enabled interrupt occurs while the MCU is in a sleep mode,

the MCU awakes, executes the interrupt routine, and

resumes execution from the instruction following SLEEP.

The contents of the register file, SRAM and I/O memory are

unaltered. If a reset occurs during sleep mode, the MCU

wakes up and executes from the Reset vector.

Idle Mode

When the SM bit is cleared (zero), the SLEEP instruction

forces the MCU into the Idle Mode stopping the CPU but

allowing Timer/Counters, Watchdog and the interrupt system to continue operating. This enables the MCU to wake

up from external triggered interrupts as well as internal

ones like Timer Overflow interrupt and watchdog reset. If

wakeup from the Analog Comparator interrupt is not

required, the analog comparator can be powered down by

setting the ACD-bit in the Analog Comparator Control and

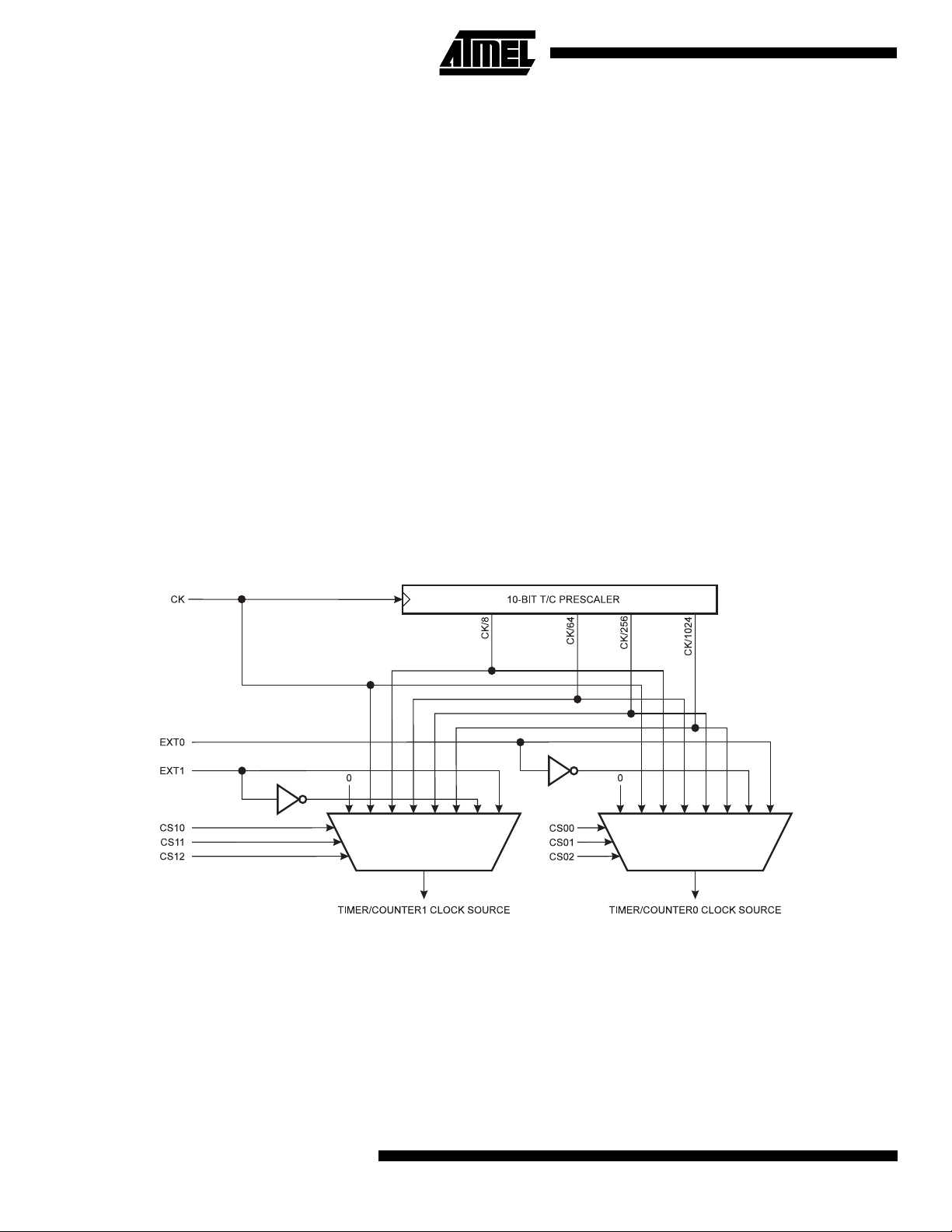

The Timer/Counter Prescaler

Figure 31 shows the general Timer/Counter prescaler.

Status register - ACSR. Thi s will reduce power consumption in Idle Mode.

Power Down Mode

When the SM bit is set (one ), the S LEEP in struc tion fo rces

the MCU into the Power Down Mode. In this mode, the

external oscillator is stopped. The user can select whether

the watchdog shall be enabled during power-down mode. If

the watchdog is enabled, it will wake up the MCU when the

Watchdog Time-out period expires. If the watchdog is disabled, only an external reset or an external level triggered

interrupt can wake up the MCU.

Timer / Counters

The AT90S8515 provides two general purpose

Timer/Counters - one 8-bit T/C and one 16-bit T/C . The

Timer/Counters have individual prescaling selection from

the same 10-bit prescali ng timer. Both Tim er/Counte rs can

either be used as a timer with an internal clock tim ebas e or

as a counter with an external pin connecti on which tri ggers

the counting.

Figure 31.

The four different prescaled selections are: CK/8, CK/64,

CK/256 and CK/1024 where CK is the oscillator clock. For

the two Timer/Counters, added selections as CK, external

source and stop, can be selected as clock sources.

Timer/Counter Prescaler

22

AT90S8515

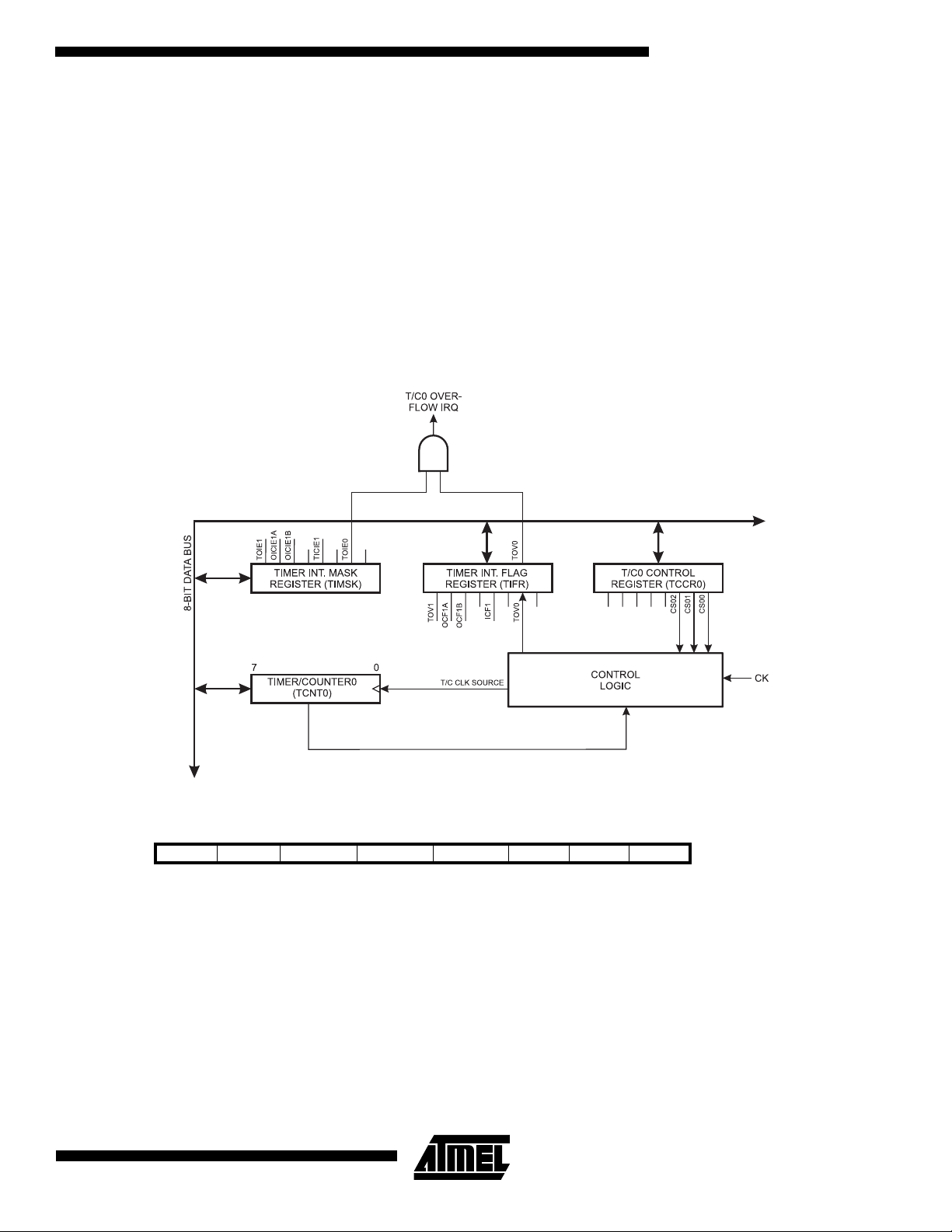

The 8-Bit Timer/Counter0

Figure 32 shows the block diagram for Timer/Counter0.

The 8-bit Timer/Counter 0 ca n s elec t c lock s ourc e fr om CK ,

prescaled CK, or an external pin. In addition it can be

stopped as described in the specification for the

Timer/Counter0 Control Register - TCCR0. The overflow

status flag is foun d in the Timer/Co unter Insterrup t Flag

Register - TIFR. Control sign als are found in the

Timer/Counter0 Control Register - TCCR0. The interrupt

enable/disable settings for Timer/Counter0 are found in the

Timer/Counter Interrupt Mask Register - TIMSK.

AT90S8515

When Timer/Counter0 is externally clocked, the external

signal is synch ronized wi th the o scillator frequenc y of the

CPU. To assure proper sampling of the external clock, the

minimum time between two external clock transitions must

be at least one internal CPU clock period. The external

clock signal is sampled on the rising edge of the internal

CPU clock.

The 8-bit Timer/Counter0 features both a high resolution

and a high accuracy usage with the lower prescaling opportunities. Simila rly, the hi gh prescali ng opportun ities ma ke

the Timer/Counter0 useful for lower spe ed functions or

exact timing functions with infrequent actions.

Figure 32.

Timer/Counter0 Block Diagram

The Timer/Counter0 Control Register - TCCR0

Bit 7 6 5 4 3 2 1 0

$33 ($53)

Read/Write R R R R R R/W R/W R/W

Initial value 0 0 0 0 0 0 0 0

Bits 7,6 - Res: Reserved bits

•

- - - - - CS02 CS01 CS00 TCCR0

These bits are reserved bits i n the A T90S85 15 and a lways

read zero.

Bits 2,1,0 - CS02, CS01, CS00: Clock Select0, bit 2,1 and 0

•

The Clock Select0 bits 2,1 and 0 define the prescaling

source of Timer0.

23

Table 6.

Clock 0 Prescale Select

CS02 CS01 CS00 Description

0 0 0 Stop, the Timer/Counter0 is stopped.

001CK

010CK / 8

011CK / 64

100CK / 256

101CK / 1024

1 1 0 External Pin T0, falling edge

1 1 1 External Pin T0, rising edge

The Stop condition provides a Timer Enable/Disable function. The CK down divided modes are scaled directly from

the CK oscilla tor cl ock. I f t he exter nal pin mo de s are used ,

the corresponding setup must be performed in the actual

data direction control register (cleared to zero gives an

input pin).

The Timer Counter 0 - TCNT0

Bit 76543210

$32 ($52)

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial value 0 0 0 0 0 0 0 0

MSB LSB TCNT0

The Timer/Counter0 is realized as an up-counter with read

and write access. If the T imer/Counter0 is wr itten and a

clock source is present, the Timer/Counter0 continues

counting in the clock cycle following the write operation.

24

AT90S8515

The 16-Bit Timer/Counter1

Figure 33 shows the block diagram for Timer/Counter1.

AT90S8515

Figure 33.

Timer/Counter1 Block Diagram

The 16-bit Timer/Co unter1 can sele ct clock source from

CK, prescaled CK, or an external pin. In addition it can be

stopped as described in the specification for the

Timer/Counter1 Control Registers - TCCR1A and

TCCR1B. The different status flags (overflow, compare

match and capture event) and control signals are found in

the Timer/Counter1 Control Registers - TCCR1A and

TCCR1B. The interrupt enable/disable settings for

Timer/Counter1 are found in the Timer/Counter Interrupt

Mask Register - TIMSK.

When Timer/Counter1 is externally clocked, the external

signal is synchro nized wi th the o scillator frequency of the

CPU. To assure proper sampling of the external clock, the

minimum time between two external clock transitions must

be at least one internal CPU clock period. The external

clock signal is sampled on the rising edge of the internal

CPU clock.

The 16-bit Timer/Counter1 features both a high resolution

and a high accuracy usage with the lower prescaling oppor-

tunities. Similarly, the high prescaling opportunities makes

the Timer/Counter1 useful for lower spe ed functions or

exact timing functions with infrequent actions.

The Timer/Counter1 supports two Output Compare functions using the Output Compare R egister 1 A and B OCR1A and OCR1B as the dat a sources to be compar ed

to the Timer/Counter1 contents. The Output Compare functions include optional clearing of the counter on compareA

match, and actions on the Output Compare pins on both

compare matches.

Timer/Counte r1 ca n also be used as a 8, 9 or 10 -bit Pulse

With Modulator. In this mode the counter and the

OCR1A/OCR1B registe rs se rv e a s a du al gl it ch -fr ee sta ndalone PWM with centered pulses. Refer to page 33 for a

detailed description on this function.

The Input Capture function of Timer/Counter1 provides a

capture of the Timer/Counter1 contents to the Input Capture Register - ICR1, triggere d by an ex ternal ev ent on the

Input Capture Pin - ICP. The actual capture event settings

25

are defined by the Timer/Counter1 Control Register TCCR1B. In addition, the Analog Comparator ca n be set to

trigger the Input Capture. Refer to the section, “The Analog

Comparator”, for details on this. The ICP pin logic is shown

in Figure 34.

Figure 34.

If the noise canceler function is enabled, the actual trigger

condition for the capture event is monitored over 4 samples

ICP Pin Schematic Diagram

before the capture is activated. The input pin signal is sampled at XTAL clock frequenc y.

The Timer/Counter1 Control Register A - TCCR1A

Bit 7 6 5 4 3 2 1 0

$2F ($4F)

Read/Write R/W R/W R/W R/W R R R/W R/W

Initial value 0 0 0 0 0 0 0 0

Bits 7,6 - COM1A1, COM1A0: Compare Output Mode1A,

•

bits 1 and 0

The COM1A1 and COM1A0 control bits determine any output pin action following a compare match in

Timer/Counter1. Any output pin actions affect pin OC1A Output CompareA pin 1. Since this is an alternative function to an I/O port, the corresponding direction control bit

must be set (one) to con tr ol a n ou tput p in . The c ontr ol c onfiguration is shown in Table 7.

Bits 5,4 - COM1B1, COM1B0: Compare Output Mode1B,

•

bits 1 and 0

The COM1B1 and COM1B0 control bits determine any output pin action following a compare match in

Timer/Counter1. Any output pin actions affect pin OC1B Output CompareB. The following con trol configuration is

given:

Table 7.

COM1X1 COM1X0 Description

00

0 1 Toggle t he OC1X output line.

COM1A1 COM1A0 COM1B1 COM1B0 - - PWM11 PWM10 TCCR1A

rupt Enable bits in the TIMSK Regist er. Otherwise an

interrupt can occur when the bits are changed.

Bits 3..2 - Res: Reserved bits

•

These bits are reserved bits in the A T90S 8515 a nd always

read zero.

Bits 1..0 - PWM11, PWM10: Pulse Width Modulator Select

•

Bits

These bits select PWM operation of Timer/Counter1 as

specified in Table 8. This mode is described on page 29.

Table 8.

PWM11 PWM10 Description

Compare 1 Mode Select

Timer/Counter1 disconnected from

output pin OC1X

PWM Mode Select

00

0 1 Timer/Counter1 is an 8-bit PWM

1 0 Timer/Counter1 is a 9-bit PWM

1 1 Timer/Counter1 is a 10-bit PWM

PWM operation of Timer/Counter1 is

disabled

1 0 Clear the OC1X output line (to zero).

1 1 Set the OC1X output line (to one).

X = A or B

In PWM mode, these bits have a different function. Refer to

Table 11 for a detailed description.

When changing the COM1X1/COM1X0 bits, Ou tput Compare Interrupts 1 must be disab led by cleari ng thei r Inter-

26

AT90S8515

The Timer/Counter1 Control Register B - TCCR1B

Bit 7 6 5 4 3 2 1 0

$2E ($4E)

Read/Write R/W R/W R R R/W R/W R/W R/W

Initial value 0 0 0 0 0 0 0 0

•

Bit 7 - ICNC1: Input Capture1 Noise Canceler (4 CKs)

When the ICNC1 bit is cleared (zero), the input capture trigger noise canceler function is disabled. The input capture is

triggered at the first rising/falling edge sampled on the ICP input capture pin - as specified. When the ICNC1 bit is set

(one), four successive samples are measures on the ICP input capture pin, and all samples must be high/low according to the input capture trigger specification in the ICES1

bit. The actual sam pling frequency is XTAL clock frequency.

Bit 6 - ICES1: Input Capture1 Edge Select

•

While the ICES1 bit is cleared (zero), the Timer/Counter1

contents are transferred to the Input Capture Register ICR1 - on the falling edge of the input capture pin - ICP.

While the ICES1 bit is set (one), the T imer/Counter1 c ontents are transferred to the Input Captur e Register - ICR1 on the rising edge of the input capture pin - ICP.

Bits 5, 4 - Res: Reserved bits

•

These bits are reserved bits i n the A T90S85 15 and a lways

read zero.

Bit 3 - CTC1: Clear Timer/Counter1 on Compare Match

•

When the CTC1 control bit is set (one), the Timer/Counter1

is reset to $0000 in the clock cycle after a compareA

match. If the CTC1 control bit is cleared, Timer/Counter1

ICNC1 ICES1 - - CTC1 CS12 CS11 CS10 TCCR1B

... | C-1 | C | C+1 | 0 | 1 | ...

When the prescaler is set to divide by 8, the timer will count

like this:

... | C-1, C-1, C-1, C-1, C-1, C-1, C-1, C-1 | C, C, C, C, C,

C, C, C | C+1, 0, 0, 0, 0, 0, 0, 0, 0 | ...

In PWM mode, this bit has no effect.

Bits 2,1,0 - CS12, CS11, CS10: Clock Select1, bit 2,1 and 0

•

The Clock Select1 bits 2,1 and 0 define the prescaling

source of Timer/Counter1.

Table 9.

CS12 CS11 CS10 Description

Clock 1 Prescale Select

0 0 0 Stop, the Timer/Counter1 is stopped.

001CK

0 1 0 CK / 8

011CK / 64

1 0 0 CK / 256

1 0 1 CK / 1024

1 1 0 External Pin T1, falling edge

1 1 1 External Pin T1, rising edge

continues count ing and is un affected by a compar e match.

Since the compare match is detected in the CPU cl ock

cycle following the match, this function will behave differently when a prescaling hi gher than 1 is used fo r the timer .

When a prescaling o f 1 is u sed , an d the co mpa re A r eg ist er

is set to C, the timer will count as follows i CTC1 is set:

The Stop condition provides a Timer Enable/Disable function. The CK down divided modes are scaled directly from

the CK oscilla tor cl ock. If t he ex ternal pin mode s are used ,

the corresponding setup must be performed in the actual

direction control register (cleared to zero gives an input

pin).

The Timer/Counter1 - TCNT1H AND TCNT1L

AT90S8515

Bit 151413121110 9 8

$2D ($4D)

$2C ($4C)

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial value 0 0 0 0 0 0 0 0

This 16-bit regis ter cont ains th e prescale d valu e of the 16bit Timer/Counter1. To ensure that both the high and low

bytes are read and wri tten sim ultaneous ly when the CP U

accesses these registers, the access is performed using an

8-bit temporary register ( TEMP). This temporary register is

also used when accessing OCR1A, OCR1B and ICR1. If

the main program and also interrupt routines perform

MSB TCNT1H

LSB TCNT1L

76543210

R/W R/W R/W R/W R/W R/W R/W R/W

00000000

access to regi sters using TEMP, interr upts must be disabled during access from the main program.

• TCNT1 Timer/Counter1 Write:

When the CPU writes to the high byte TCNT1H, the

written data is placed in the TEMP register. Next, when

the CPU writes the low byte TCNT1L, this byte of data

is combined with the byte data in the TEMP register,

27

and all 16 bits are written to the TCNT1

Timer/Counter1 register simultaneously. Consequently, the high byte TCNT1H must b e accessed firs t

for a full 16-bit register write operation.

• TCNT1 Timer/Counter1 Read:

When the CPU reads the low byte TCNT1L, the data of

the low byte TCNT1L is sent to the CPU and the data of

the high byte TCNT1H is placed in th e TEMP register.

TCNT1H, the CPU receives the data in th e TEMP register. Consequently, the low byte TCNT1L must be

accessed first for a full 16-bit register read operation.

The Timer/Coun ter1 is real ized as an up or u p/down (in

PWM mode) counter with read and write access. If

Timer/Counter1 is written to and a clock source is selected,

the Timer/Counter1 continues counting in the timer clock

cycle after it is preset with the written value.

When the CPU reads the data in the high byte

Timer/Counter1 Output Compare Register - OCR1AH AND OCR1AL

Bit 151413121110 9 8

$2B ($4B)

$2A ($4A)

Read/Write R/W R/W R/W R/ W R/W R/W R/W R/W

Initial value 0 0 0 0 0 0 0 0

MSB OCR1AH

LSB OCR1AL

76543210

R/W R/W R/W R/W R/W R/W R/W R/W

00000000

Timer/Counter1 Output Compare Register - OCR1BH AND OCR1BL

Bit 151413121110 9 8

$29 ($49)

$28 ($48)

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial value 0 0 0 0 0 0 0 0

MSB OCR1BH

LSB OCR1BL

76543210

R/W R/W R/W R/W R/W R/W R/W R/W

00000000

The output compare registers are 16-bit read/write registers.

The Timer/Counter1 Output Compare Registers contain

the data to be continuously compared with Timer/Counter1.

Actions on compare matc hes are specified in the

Timer/Counter1 Control and Status register.A compare

match does only occur if Tim er/Counter1 coun ts to the

OCR value. A so ftwar e wri te th at s ets TCN T1 and OC R1A

or OCR1B to the same value does not generate a compare

match.

A compare match will set the compare interrupt flag in the

CPU clock cycle following the compare event.

Since the Out put Compare Registers - OCR1A and

OCR1B - are 16-bit registers, a temporary register TEMP is

used when OCR1A/B are written to ensure that both bytes

are updated simultaneously. When the CPU writes the high

byte, OCR1AH or OCR1BH, the data is temporarily stored

in the TEMP register. When the CPU writes the low byte ,

OCR1AL or OCR1BL, the TEMP register is simultaneously

written to OCR1AH or OCR1BH. Consequently, the high

byte OCR1AH or OCR1BH must be written first for a full

16-bit register write operation.

The TEMP register is also used when accessing TCNT1,

and ICR1. If the main program and also interrupt ro utines

perform access to registers using TEMP, interrupts must

be disabled during access from the main program.

28

AT90S8515

AT90S8515

The Timer/Counter1 Input Capture Register - ICR1H AND ICR1L

Bit 151413121110 9 8

$25 ($45)

$24 ($44)

Read/Write RRRRRRRR

Initial value 0 0 0 0 0 0 0 0

MSB ICR1H

LSB ICR1L

76543210

RRRRRRRR

00000000

The input capture register is a 16-bit read-only register.

When the rising or falling e dge (a ccordi ng to the i nput c ap-

ture edge setting - ICES1) of the sign al at the input capt ure

pin - ICP - is detected, the current value of the

Timer/Counter1 is transferred to the Input Capture Register

- ICR1. At the same time, the input capture flag - ICF1 - is

set (one).

Since the Input Cap ture Re giste r - ICR1 - is a 16 -bit reg ister, a temporary register TEMP is used when ICR1 is read

to ensure that both bytes are read simultaneously. When

the CPU reads the low byte ICR1L, the data is sent to the

CPU and the data of the high byte ICR1H is placed in the

TEMP register. When the CPU reads the data in the high

byte ICR1H, the CPU receives the data in the TEMP register. Consequent ly, the low byte ICR 1L must be acce ssed

first for a full 16-bit register read operation.

The TEMP regi ster is a lso used wh en acces sing TCNT 1,

OCR1A and OCR1B. If the main program and also interrupt

routines perform access to registers using TEMP, interrupts must be disabled during access from the main program.

Timer/Counter1 In PWM Mode

When the PWM mode is selected, Timer /Counter1 and the

Output Compare Register1A - OCR1A and the Output

Compare Register1B - OCR1B, form a dual 8, 9 or 10-bit,

free-running, glitch-free and phase correct PW M with outputs on the PD5(OC1A) and OC1B pins. Timer/Counter1

acts as an up/down counter, counting up from $0000 to

TOP (see Table 10) , whe n it turns a nd cou nts down ag ain

to zero before the cycle is repeated. When the counter

value matches the contents of the 10 least significan t bits

of OCR1A or OCR1B, the PD5(OC1A)/OC1B pins are set

or cleared according to the settings of the

COM1A1/COM1A0 or C OM1B1/COM1B0 bits in th e

Timer/Counter1 Control Register TCCR1A. Refer to Table

11 for details.

Table 10.

Timer TOP Values and PWM Frequency

Table 11.

COM1X1 COM1X0 Effect on OCX1

Note: X = A or B

Compare1 Mode Select in PWM Mode

0 0 Not connected

0 1 Not connected

Cleared on compare match,

10

11

upcounting. Set on compare match,

downcounting (non-inverted PWM).

Cleared on compare match,

downcounting. Set on compare

match, upcounting (inverted PWM).

Note that in the PWM mode, the 10 least significant

OCR1A/OCR1B bits, when written, are transferred to a

temporary location. They are latched when Timer/Counter1

reaches the value TOP. This prevents the oc currence of

odd-length PWM pulses (glitches) in the event of an unsynchronized OCR1A/OCR1B write. See Figure 35 for an

example.

PWM Resolution Timer TOP value Frequency

8-bit $00FF (255) f

9-bit $01FF (511) f

10-bit $03FF(1023) f

TC1

TC1

TC1

/510

/1022

/2046

29

Figure 35.

Effects on Unsynchronized OCR1 Latching

During the time between the write and the latch operation,

a read from OCR1A or OCR1B will read the contents of the

temporary location. This means that the mo st recen tly wr itten value always will read out of OCR1A/B

When OCR1 contains $0000 or TOP, the output

OC1A/OC1B is held low or high according to the settings of

COM1A1/COM1A0 or COM1B1/COM1B0. This is shown in

Table 12:

Table 12.

COM1X1 COM1X0 OCR1X Output OC1X

Note: X = A or B

In PWM mode, the Timer Overflow Flag1, T OV1, is set

when the counter change s directi on at $0000. Tim er Overflow Interrupt1 operates exactly as in normal Timer/Counter

mode, i.e. it is executed when TOV1 is set provided that

Timer Overflow Interrupt1 and global interrupts are

enabled. This does also apply to the Timer Output

Compare1 flags and interrupts.

PWM Outputs OCR1X = $0000 or TOP

1 0 $0000 L

10TOP H

1 1 $0000 H

11TOP L

cutes from the reset vector. For timing details on the

Watchdog reset, refer to page 18.

To prevent unintentional disabling of the watchdog, a special turn-off secuence must be followed when the watchdog

is disabled.Refer to the description of the Watchdog Timer

Control Register for details.

Figure 36.

Watchdog Timer

The Watchdog Timer

The Watchdog Timer is clocked from a separate on-chip

oscillator which runs at 1MHz This is the typical value at

= 5V. See characterization data for typical values at

V

CC

other V

caler, the Watchd og reset interva l can be adjusted fr om

16K to 2,048K cycles (nominally 16 - 2048 ms). The WDR Watchdog Reset - instruction resets the Watchdo g Timer.

Eight different clock cycle periods can be selected to determine the reset period. If the reset period expires without

another Watchdog reset, t he AT90S8515 resets and exe-

30

levels. By controlling the Watchdog Timer pres-

CC

AT90S8515

AT90S8515

The Watchdog Timer Control Register - WDTCR

Bit 76543210

$21 ($41)

Read/Write R R R R/W R/W R/W R/W R/W

Initial value 0 0 0 0 0 0 0 0

•

Bits 7..5 - Res: Reserved bits

These bits are reserved bits in the AT90S8515 and will

always read as zero.

Bit 4 - WDTOE: Watch Dog Turn-Off Enable

•

This bit must be set (one) when the WD E bit is clear ed.

Otherwise, the watchdo g will not be disabled. Onc e set,

hardware will clear this bit to zero after four clock cycles.

Refer to the desc ription of th e WDE bit for a watc hdog disable procedure.

Bit 3 - WDE: Watch Dog Enable

•

When the WDE is set (one) the Watchdog Timer is

enabled, and if the WDE is cleared (zero) the W atchdog

Timer function is disabled. WDE can only be cleared if the

WDTOE bit is set(one). To disable an enabled watchdog

timer, the following procedure must be followed:

1. In the same operation, write a logical one to

WDTOE and WDE. A logcal one must be written to

WDE even though it is set to one before the disable

operation starts.

2. Within the next four clock cycles, write a logical 0 to

WDE. This disables the watchdog.

Bits 2..0 - WDP2, WDP1, WDP0 : Watch Dog Timer Presc aler

•

2, 1 and 0

The WDP2, WDP1 and WDP0 bits determine the Watchdog Timer prescaling when the Watchdog Timer is

enabled. The different prescaling values and their corresponding Timeout Periods are shown in Table 13.

Table 13.

Watch Dog Timer Prescale Select

- - - WDTOE WDE WDP2 WDP1 WDP0 WDTCR

EEPROM Read/Write Access

The EEPROM access registers are accessible in the I/O

space.

The write access time is in the range of 2.5 - 4ms, depending on the V

lets the user softwar e detect when the ne xt byte can be

written. If the user code conta ins code that writes the