Page 1

BDTIC www.bdtic.com/ATMEL

特性

• 与 MCS

• 增强型 8051 体系结构

• 非易失性程序存储器

• 外围特性

• 特殊微控制器特性

• I/O 和封装

• 工作条件

®

51 系列相兼容的 8 位微控制器

– 单时钟周期字节取指能力

– 20 MHz 时钟频率下吞吐量达 20 MIPS

– 全静态工作 : 0 Hz 到 20 MHz

– 片上 2 周期硬件乘法器

– 128 x 8 内部 RAM

–4个中断优先级

–2KB系统内可编程 (ISP) Flash 存储器

– 寿命 : 可重复擦写最少 10,000 次

– 数据保持能力 : 最少 10 年

– 程序下载串行接口

–32字节快速页面编程模式

–64字节用户签名数组区

–2级存储锁保证软件安全

– 2个16-bit 增强型定时器 / 计数器

– 2个8-bit PWM 输出端 ( 仅 AT89LP213 )

– 带自动地址识别和帧错误检测的增强型 UART ( 仅 AT89LP214)

– 带双缓冲器可收发增强型主 / 从 SPI

– 可软件复位的可编程看门狗定时器

– 带可选中断和反跳的模拟比较器

–8个通用中断引脚

– 双线 (TW)片上调试接口

– 掉电检测以及用断电标志上电复位

– 内部 RC 振荡器

– 低功耗省电和掉电模式

– 从掉电模式的中断恢复功能

– 共 12 个可编程 I/O 线

– 可配置 I/O:准双向 , 输入 , 推挽式输出 , 开漏共四种模式

–5V耐压能力的 I/O

–14针 TSSOP 或 PDIP

–2.4V到 5.5V V

–-40°C 到 85°C 温度范围

电压范围

CC

带 2K 字节 Flash

的 8-bit 微控制器

AT89LP213

AT89LP214

Preliminary

1. 描述

AT89LP213/214 是低功耗的高性能的 CMOS 8位微控制器,带有 2K 字节的系统内可编

程 Flash 存储器。该设备的生产使用了 Atmel 的高密度非易失性存储器技术并且与工业

标准的 MCS-51 指令集相兼容。 AT89LP213/214 的构建基于增强型的每时钟周期可取

一字节指令的 CPU 核心。在经典的 8051 体系结构中,每取一字节需要 6 个时钟周期,

这使得执行指令需要 12, 24 或 48 个时钟周期。在 AT89LP213/214 CPU 中,执行指令

只需要 1 到 4 个时钟周期,因而吞吐量比标准的 8051 大 6 到 12 倍。百分之七十的指

令的执行只需要与其字节数相同的时钟周期。

本文是英文数据手册的中文

翻译,其目的是方便中国用

户的阅读。它无法自动跟随

原稿的更新,同时也可能存

在翻译上的错误。读者应该

以英文原稿为参考以获得更

准确的信息。

3538A–MICRO–6/06

Page 2

其余的指令的执行只需要比其字节数多一个的时钟周期。增强型的 CPU 核心有 20 MIPS 的吞吐

能力,而经典的 8051 CPU 在同样的工作电流下只能达到4 MIPS。 另一方面,保持与经典的 8051

一样的吞吐量时,这个新的 CPU 核心工作在低得多的速度下从而极大程度地降低了功耗。

AT89LP213/214提供下列标准特性:2K 字节系统内可编程 Flash 存储器,128字节 RAM,12 条 I/O

线,2 个 16 位定时器 / 计数器,2 个 PWM 输出端 ( 仅 AT89LP213 ),一个可编程看门狗定时器,

一个全双工串口 ( 仅 AT89LP214),一个串行外围接口,一个内部 RC 振荡器,片上晶振,一个 4

优先级的 6 向量中断系统。

AT89LP213/214的两个 16位定时器/ 计数器有两个新的模式。模式0可以配置为9到16位可变的定

时器 / 计数器,模式 1 可以配置为 16 位自动重载的定时器 / 计数器。此外, AT89LP213 的两个定

时器 / 计数器还可独立地驱动一个脉冲宽度调制输出端。

AT89LP213/214 的 I/O 口可独立地配置为四个工作模式下的一种。在准双向模式下,端口工作方

式与经典 8051 相同。在输入模式下,端口是三态的。推挽式输出模式提供完全的 CMOS 驱动,

开漏模式提供一个下拉电阻。此外, Port 1 的 8 个引脚都可使用通用中断接口配置为中断源。

AT89LP213/214 的 I/O 的耐压值比设备自身的供电电源要高,可达 5.5V。当设备供电电压为 2.4V

而所有的 I/O 口接收为 5.5V 信号时,所有 I/O 总的回流电流 少于 100 µA。

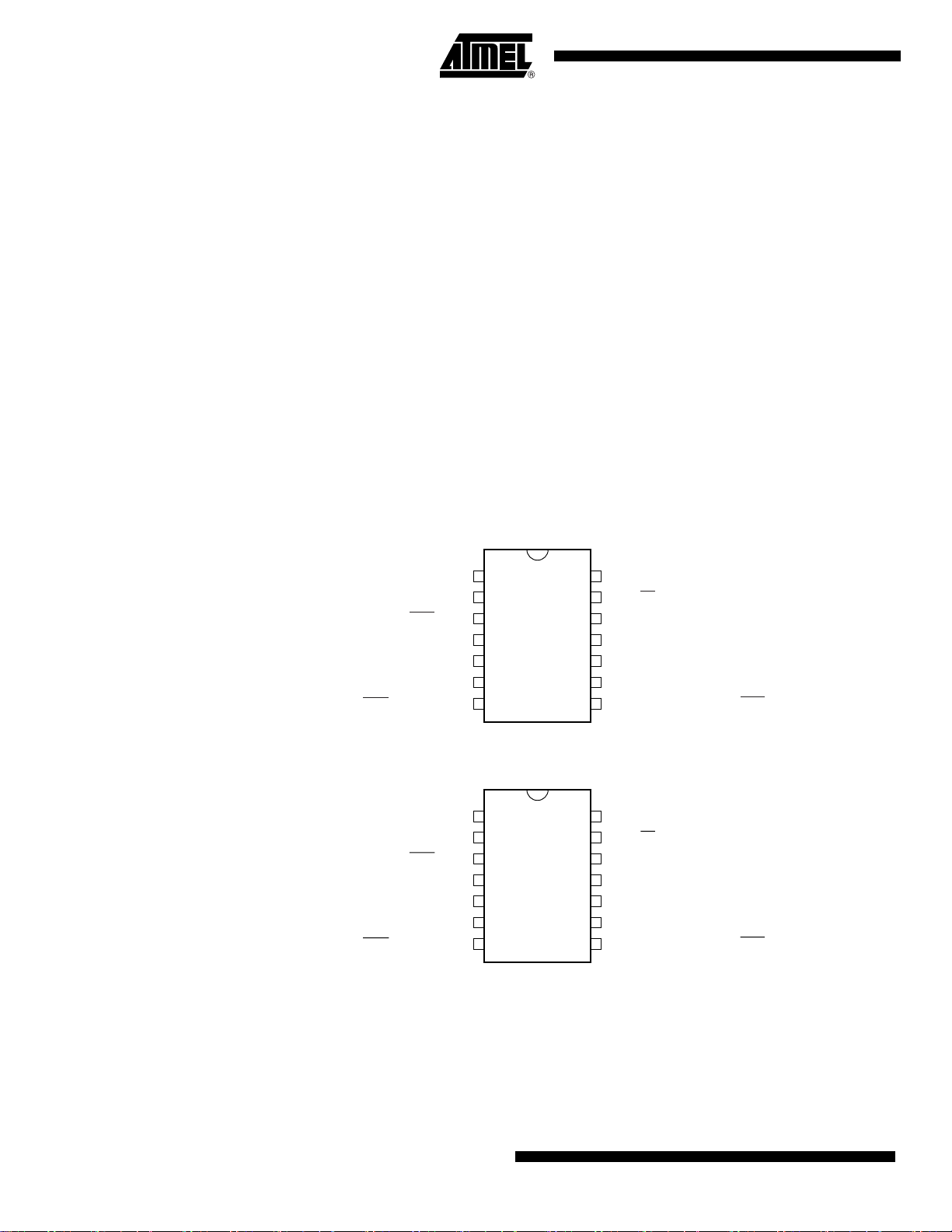

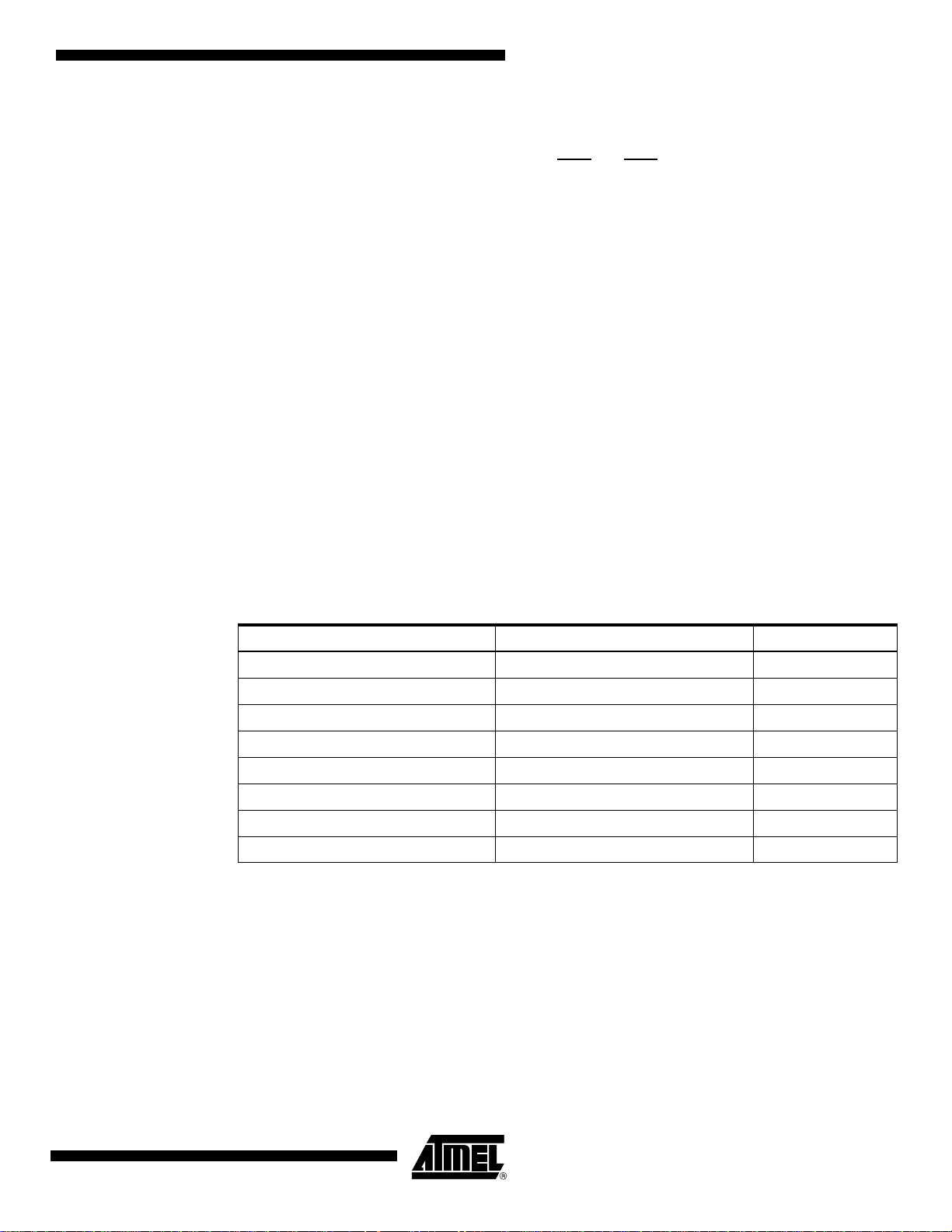

2. 引脚配置

2.1 AT89LP213: 14 针 TSSOP/PDIP

2.2 AT89LP214: 14 针 TSSOP/PDIP

(GPI5/MOSI) P1.5

(GPI7/SCK) P1.7

(GPI5/RST) P1.3

GND

(GPI2) P1.2

(T0) P3.4

(INT0/XTAL1) P3.2

(GPI5/MOSI) P1.5

(GPI7/SCK) P1.7

(GPI5/RST) P1.3

GND

(GPI2) P1.2

(RxD) P3.0

(INT0/XTAL1) P3.2

1

2

3

4

5

6

7

1

2

3

4

5

6

7

14

P1.6 (MISO/GPI6)

13

P1.4 (SS/GPI4)

12

P1.1 (AIN1/GPI1)

11

P1.0 (AIN0/GPI0)

10

VCC

9

P3.5 (T1)

8

P3.3 (XTAL2/CLKOUT/INT1)

14

P1.6 (MISO/GPI6)

13

P1.4 (SS/GPI4)

12

P1.1 (AIN1/GPI1)

11

P1.0 (AIN0/GPI0)

10

VCC

9

P3.1 (TxD)

8

P3.3 (XTAL2/CLKOUT/INT1)

2

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 3

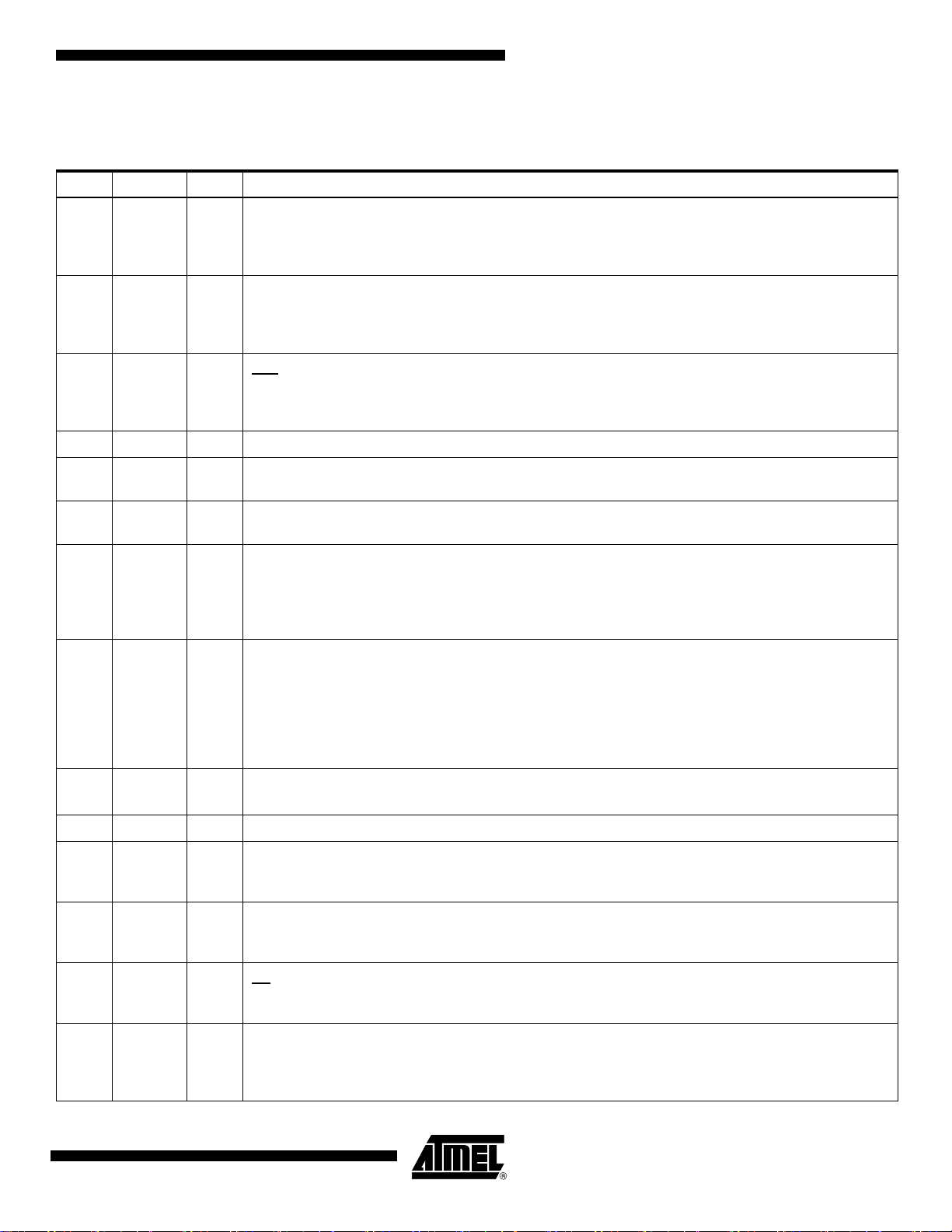

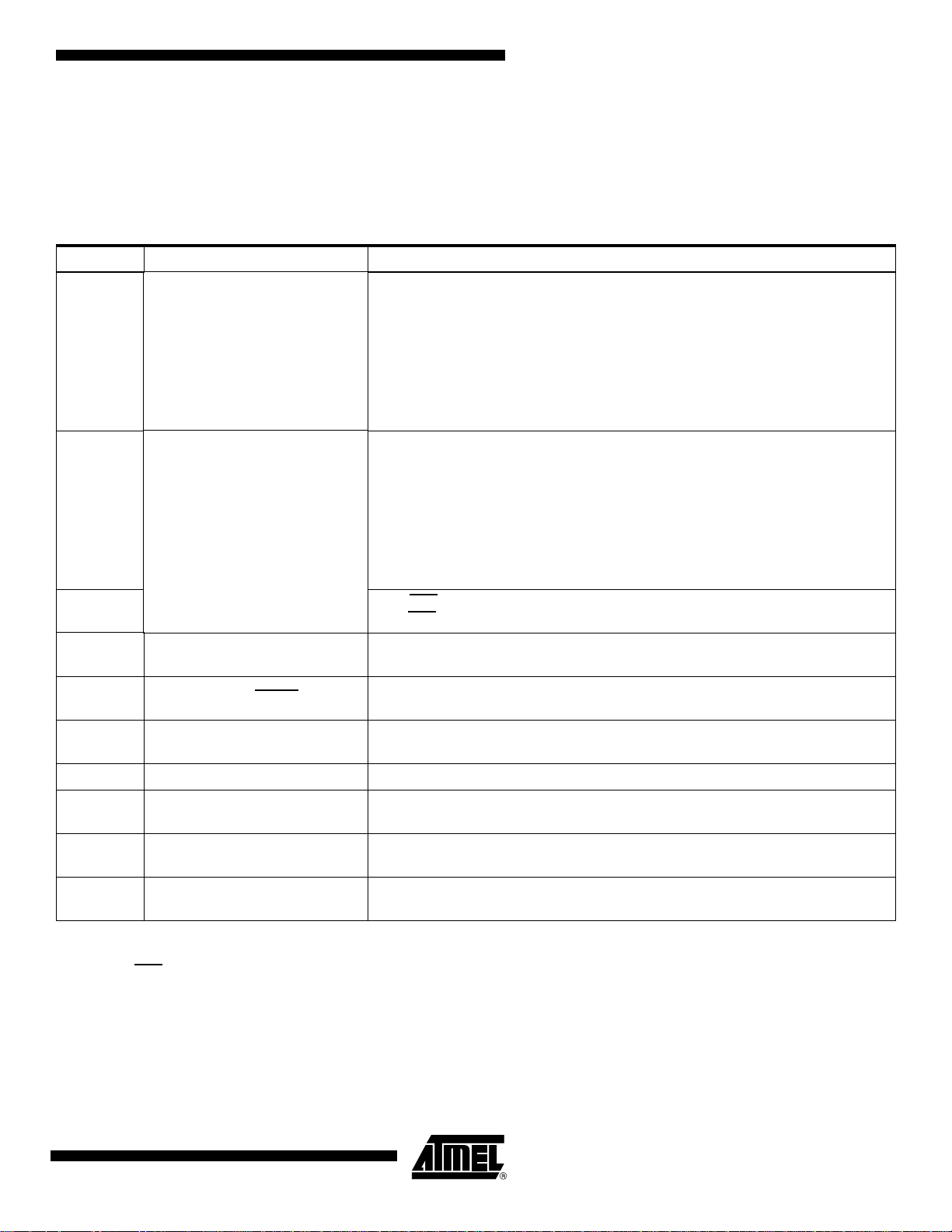

3. 引脚描述

Table 3-1. AT89LP213 引脚描述

引脚 符号 类型 描述

I/O

1P1.5

2P1.7

3P1.3

4GND I地

5P1.2

I/O

I/O

I/O

I/O

I/OIP1.2: 用户可配置 I/O 口, Port 1 bit 2.

P1.5: 用户可配置 I/O, Port 1 bit 5.

MOSI: SPI 主-输出/ 从 - 输入。当配置为主控端时,为输出引脚。当配置为从控端时,为输入引脚。

GPI5: 通用中断输入端 5.

I

P1.7: 用户可配置 I/O 口, Port 1 bit 7.

SCK: SPI 时钟。 当配置为主控端时,为输出引脚。当配置为从控端时,为输入引脚。

GPI7: 通用中断输入端 7.

I

P1.3: 用户可配置 I/O 口, Port 1 bit 3 ( 若禁止复位保险 ).

I

I

I

: 外部 Active-Low 复位输入端 ( 若使能复位保险, See “ 外部复位 ” on page 15).

RST

GPI3: 通用中断输入端 3.

DCL: 当使能 OCD 时作为片上调试接口的串行时钟输入。

GPI2: 通用中断输入端 2.

AT89LP213/214 [Preliminary]

6P3.4

7P3.2

8P3.3

9P3.5

10 VDD I 电源电压

11 P1. 0

12 P1.1

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

P3.4: 用户可配置 I/O 口, Port 3 bit 4.

T0: 定时器 / 计数器 0 外部 输入或 PWM 输出 .

P3.2: 用户可配置 I/O 口, Port 3 bit 2.

I

XTAL1: 输入到反向晶振放大器和内部时钟发生电路。若采用内部 RC 振荡器作为时钟源时,它可用作一

个端口引脚 .

DDA: 当使能 OCD 并采用内部 RC 振荡器作为时钟源时,作为片上调试接口的串行数据输入 / 输出。

O

P3.3: 用户可配置 I/O 口, Port 3 bit 3.

XTAL2: 从反向晶振放大器输出。若采用内部 RC 振荡器作为时钟源时,它可用作一个端口引脚 .

O

CLKOUT: 若采用内部 RC 振荡器作为时钟源时,可用于输出内部时钟的二分频。

DDA: 当使能 OCD 并采用外部时钟作为时钟源时,作为片上调试接口的串行数据输入 / 输出。

P3.5: 用户可配置 I/O 口, Port 3 bit 5.

T1: 定时器 / 计数器 1 外部 输入或 PWM 输出 .

P1.0: 用户可配置 I/O 口, Port 1 bit 0.

I

AIN0: 正极输入模拟比较器 .

I

GPI0: 通用中断输入端 0.

P1.1: 用户可配置 I/O 口, Port 1 bit 1.

I

AIN1: 负极输入模拟比较器 .

I

GPI1: 通用中断输入端 1

13 P1.4

14 P1.6

3538A–MICRO–6/06

I/O

I/O

I/O

P1.4: 用户可配置 I/O 口, Port 1 bit 4.

I

I

I

:SPI 从控选择输入引脚 .

SS

GPI4: 通用中断输入端 4.

P1.6: 用户可配置 I/O 口, Port 1 bit 6.

MISO: SPI 主控 - 输入 / 从控 - 输出。 当配置为主控端时,为输入引脚。当配置为从控端时,为输出引脚。

GPI6: 通用中断输入端 6.

3

Page 4

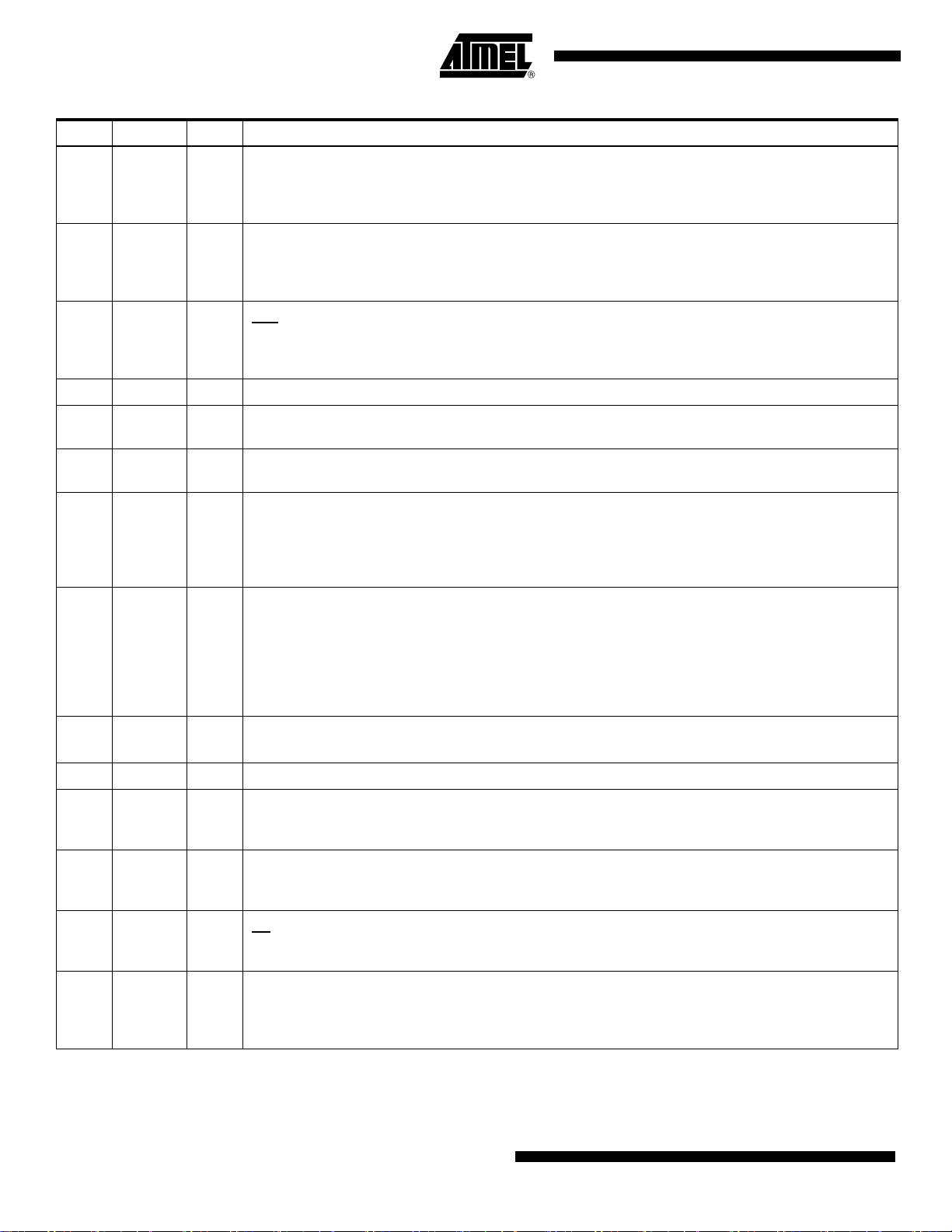

Table 3-2. AT89LP214 引脚描述

引脚 符号 类型 描述

1P1.5

2P1.7

I/O

I/O

I/O

I/O

P1.5: 用户可配置 I/O 口, Port 1 bit 5.

MOSI: SPI 主-输出/ 从 - 输入。当配置为主控端时,为输出引脚。当配置为从控端时,为输入引脚。

GPI5: 通用中断输入端 5.

I

P1.7: 用户可配置 I/O 口, Port 1 bit 7.

SCK: SPI 时钟。 当配置为主控端时,为输出引脚。当配置为从控端时,为输入引脚。 .

GPI7: 通用中断输入端 7.

I

I/O

3P1.3

4GND I地

5P1.2

6P3.0

7P3.2

8P3.3

9P3.1

10 VDD I 电源电压

11 P1. 0

12 P1.1

13 P1.4

14 P1.6

I/OIP1.2: 用户可配置 I/O 口, Port 1 bit 2.

I/OIP3.0: 用户可配置 I/O 口, Port 3 bit 0.

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

P1.3: 用户可配置 I/O 口, Port 1 bit 3 ( 若禁止复位保险 ).

I

I

I

I

O

O

O

I

I

I

I

I

I

I

: 外部 Active-Low 复位输入端 ( 若使能复位保险, See “ 外部复位 ” on page 15).

RST

GPI3: 通用中断输入端 3.

DCL: 片上调试接口的串行时钟输入。

GPI2: 通用中断输入端 2.

RXD: 串行端口接收端输入 .

P3.2: 用户可配置 I/O 口, Port 3 bit 2.

XTAL1: I 输入到反向晶振放大器和内部时钟发生电路。若采用内部 RC 振荡器作为时钟源时,它可用作一

个端口引脚。

DDA: 当使能 OCD 并采用内部 RC 振荡器作为时钟源时,作为片上调试接口的串行数据输入 / 输出。 .

P3.3: 用户可配置 I/O 口, Port 3 bit 3.

XTAL2: 从反向晶振放大器输出。若采用内部 RC 振荡器作为时钟源时,它可用作一个端口引脚 .

CLKOUT: 若采用内部 RC 振荡器作为时钟源时,可用于输出内部时钟的二分频。

DDA: 当使能 OCD 并采用外部时钟作为时钟源时,作为片上调试接口的串行数据输入 / 输出。

P3.1: 用户可配置 I/O 口, Port 3 bit 1.

TXD: 串口发送端输出 .

P1.0: 用户可配置 I/O 口, Port 1 bit 0.

AIN0: 正极输入模拟比较器 .

GPI0: 通用中断输入端 0.

P1.1: 用户可配置 I/O 口, Port 1 bit 1.

AIN1: 负极输入模拟比较器 .

GPI1: 通用中断输入端 1

P1.4: 用户可配置 I/O 口, Port 1 bit 4.

: SPI 从控选择输入引脚 .

SS

GPI4: 通用中断输入端 4.

P1.6: 用户可配置 I/O 口, Port 1 bit 6.

MISO: SPI 主控 - 输入 / 从控 - 输出。 当配置为主控端时,为输入引脚。当配置为从控端时,为输出引脚。

GPI6: 通用中断输入端 6.

4

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 5

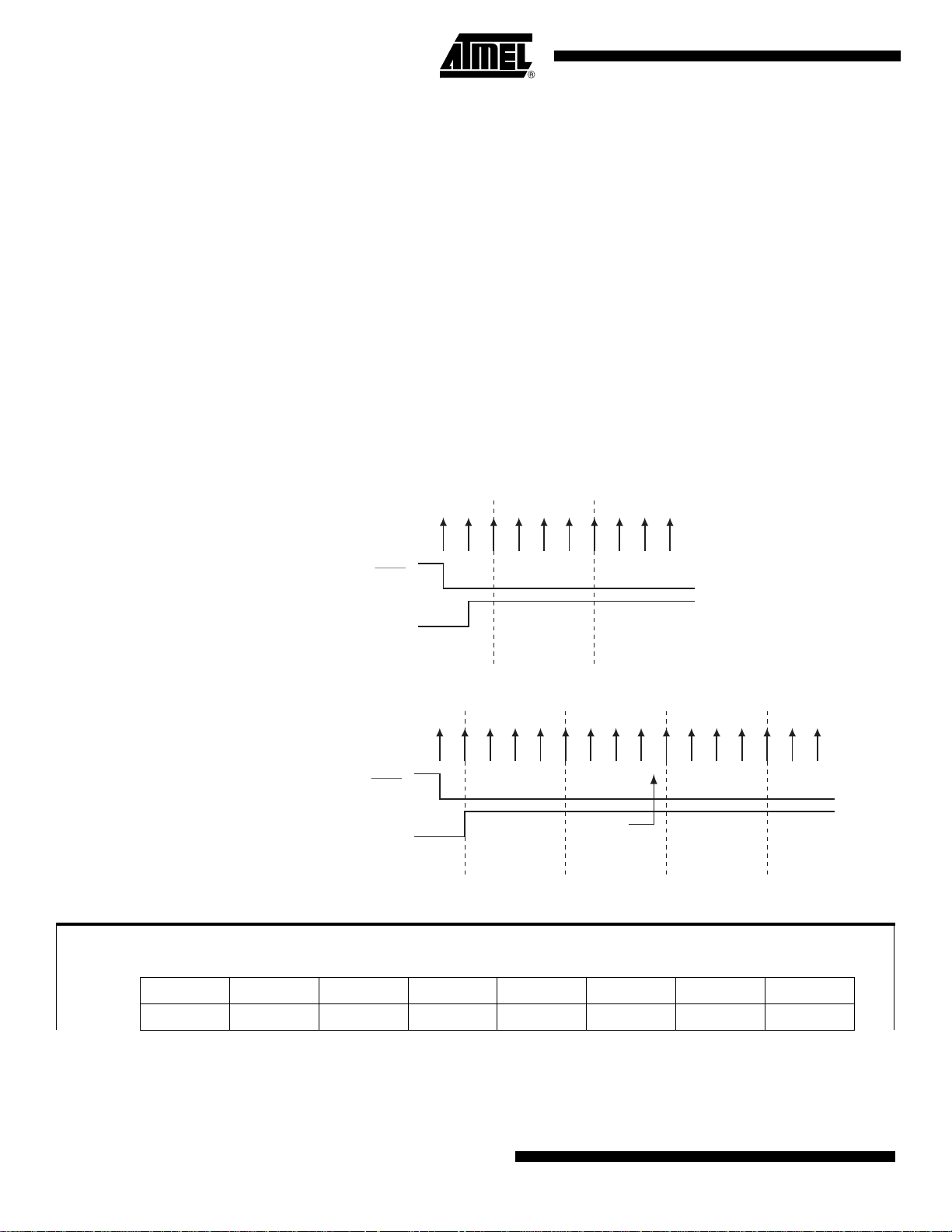

4. 方框图

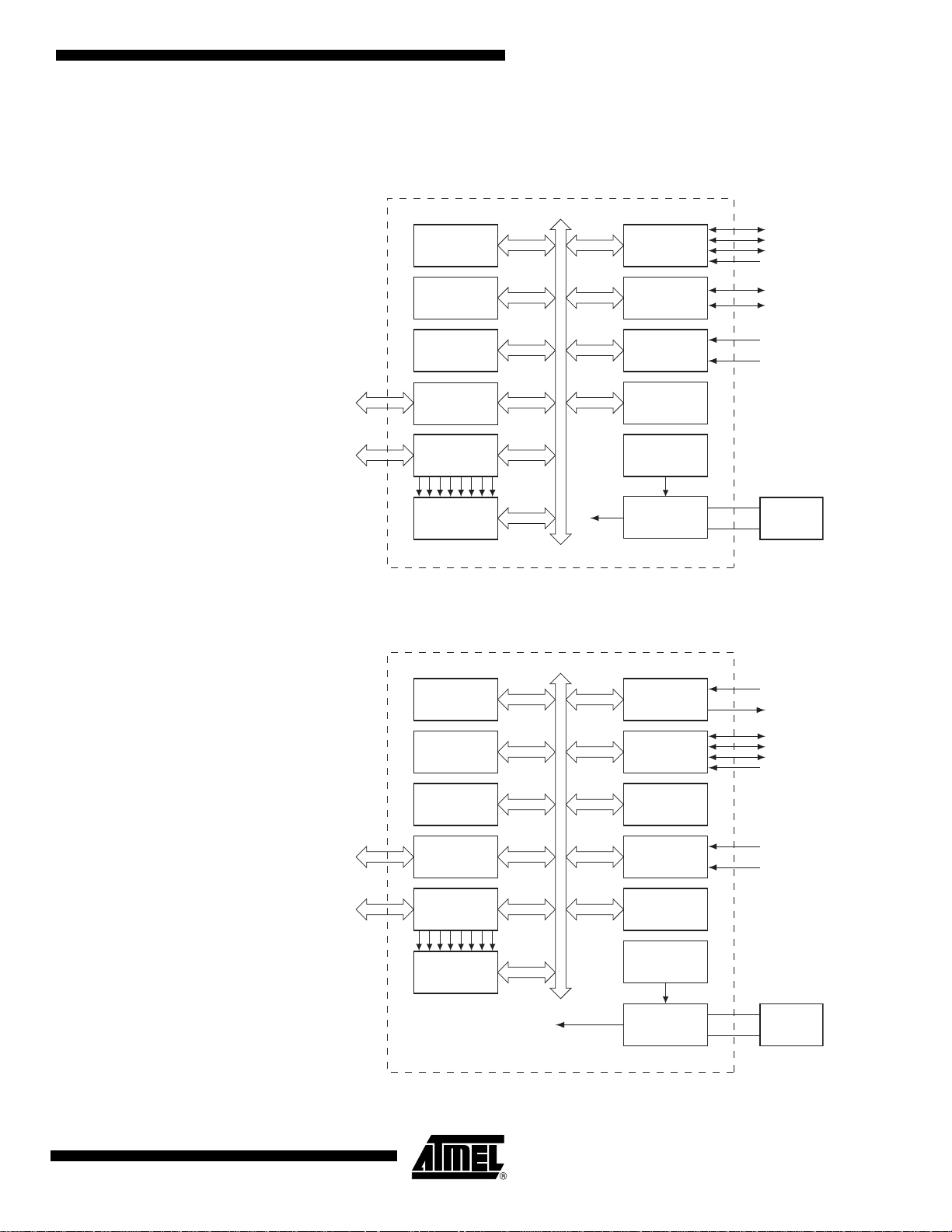

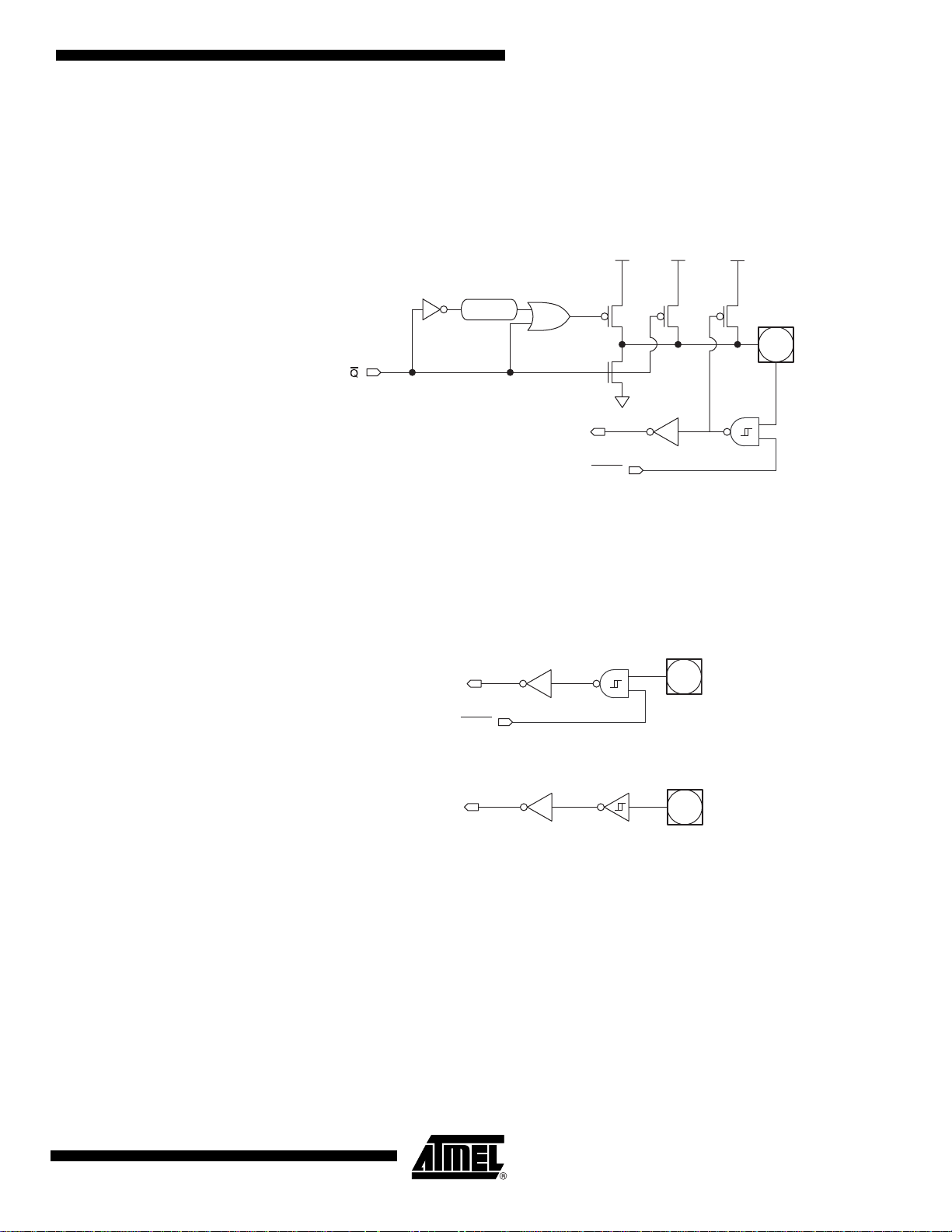

Figure 4-1. AT89LP213 模块框图

Single Cycle

8051 CPU

2KB Flash

128 Bytes

RAM

Por t 3

Configurable I/O

Por t 1

Configurable I/O

General-purpose

Interrupt

AT89LP213/214 [Preliminary]

SPI

Timer 0

Timer 1

Analog

Comparator

Watchdog

Timer

On-Chip

RC Oscillator

CPU Clock

Configurable

Oscillator

Crystal or

Resonator

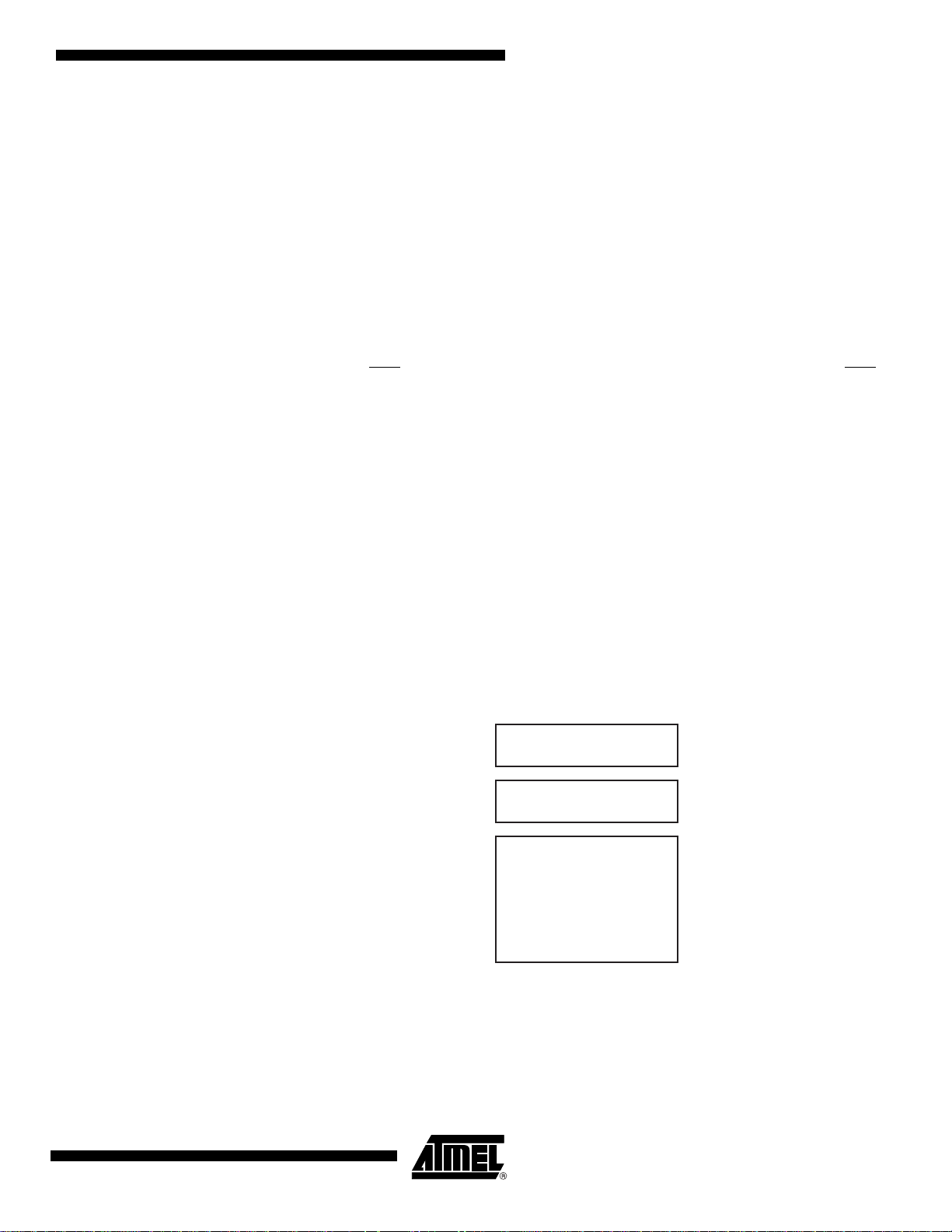

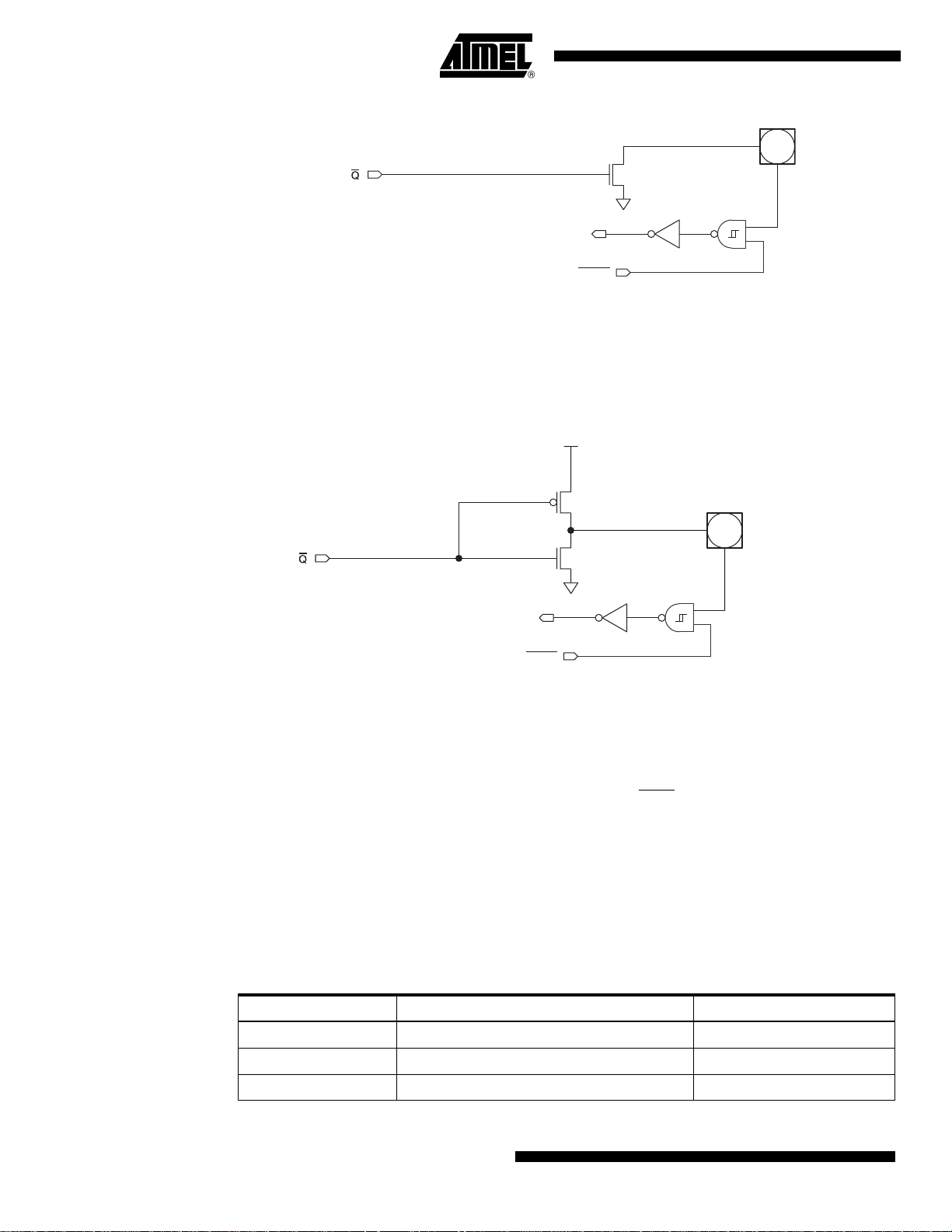

Figure 4-2. AT89LP214 模块框图

Single Cycle

8051 CPU

2KB Flash

128 Bytes

RAM

Port 3

Configurable I/O

Port 1

Configurable I/O

General-purpose

Interrupt

CPU Clock

3538A–MICRO–6/06

UART

SPI

Timer 0

Timer 1

Analog

Comparator

Watchdog

Timer

On-Chip

RC Oscillator

Configurable

Oscillator

Crystal or

Resonator

5

Page 6

5. 与标准 8051 比较

AT89LP213/214 是完全与 MCS-51 指令集兼容的带增强特性的控制器系列的一部分。此外,大部

分 SFR 地址,位分配和引脚转换功能与 Atmel 现有的标准 8051 系列产品相一致。不过,由于该

微控制器有更高的性能,一些系统级行为则与象 AT89S52 或 AT89S2051 这样的 Atmel 的标准

8051 产品有所不同。与标准 8051 的这些不同之处罗列如下:

5.1 系统时钟

CPU 时钟频率与外部 XTAL1 频率相等。振荡器不再作二分频用于提供内部时钟,同时 x2 模式也不

再支持。

5.2 指令执行时每时钟周期取一字节指令

CPU 每一个时钟周期从内存取一字节代码,而不再是 6 个时钟周期。这极大地增加了 CPU 的吞吐

量。于是, CPU 执行指令不再需要 12 到 48 个时钟周期。每条指令的执行仅在 1 到 4 时钟周期

内完成。详细见 See “ 指令机摘要 ” on page 57 .

5.3 中断处理

中断控制器在每个指令的最后的时钟周期轮询中断标志。为使在最后的指令周期响应某个中断请

求,其中断标志需要在该指令的最后的时钟周期到来前一直锁存为有效,如果该指令为单时钟周

期执行的指令则需要在前一指令的最后一个时钟周期内一直保持有效。

5.4 定时器 / 计数器

5.5 串口

外部中断引脚 INT

令时序和更快的中断响应,使得对外部事件的中断的最快响应速率更高。

缺省情况下,定时器 / 计数器的计数频率为一个时钟周期。相比之下,标准 8051 是每 12 个时钟

周期计数一次。 一个通用预定器可用于为所有的定时器划分时间基并降低计数速率。 CLKREG

SFR中的TPS位控制预定器 (Table 9-2 on page 13). 设置TPS = 1011B将使定时器每12时钟周期

计数一次。

外部定时器 / 计数器引脚 T0 和 T1 在每个时钟周期采样一次,而非 12 个时钟周期。这增加了计数

器模块的最大工作速率。

UART在模式0下的波特率是时钟频率的1/2,在 标 准 8051中则是时钟频率的1/12 ;输出数据仅在

串行时钟的上升沿有效。 还应该注意,使用定时器 1 在模式 1 或模式 3 下发生波特率时,定时器

以时钟频率计数而非时钟频率的 1/12。当 AT89LP214 与标准 8051 工作在同一频率时,为保持

AT89LP214具有相同的波特率,则 延迟时间必须为12倍时钟周期。定时器1的模式1支持16位自动

重载,可以用于较长的 时间延迟以产生较低的波特率。

0 和 INT1 每个时钟周期采样,而非每 12 个时钟周期采样一次。有了更端的指

6

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 7

5.6 看门狗定时器

5.7 I/O 端口

5.8 复位

6. 存储器结构

AT89LP213/214 [Preliminary]

AT89LP213/214的看门狗定时器的计数速率与时钟周期一致。相比之下,标准8051则每12 个时钟

周期计数一次。 一个通用预定器可用于为所有的定时器分频时间基并降低计数速率。

AT89LP213/214的I/O端口可配置为四种模式。缺省情况下,掉电或复位时I/O端口回到只读 ( 三态

) 模式 。在 标 准 8051 中,所有端口在掉电或复位时仅下拉至低电平。为使能类似 8051 的端口,端

口必须设置为准双向模式,这通过清零P1M0和P3M0 SFR来实现。用户还可以通过禁止 TristatePort User Fuse(三态用户保险)来将端口配置为准双向模式起始方式。当禁止该保险时,P1M0

和 P3M0 将复位到 00h 而非 FFh,并且端口会上拉到高电位。

AT89LP213/214的 RST 引脚是低电位触发的,而在标准 8051中,则是高电位复位。此外, RST 引

脚每时钟周期采样一次,并且必须最少保持低电位 2 个时钟周期,而非 24 个时钟周期,这样才能

识别为有效的复位信号。

AT89LP213/214 使用哈佛体系结构,程序和数据存储器的地址线分离。程序存储器使用常规的线

性地址空间,支持达 64K 字节的可直接寻址的应用代码。数据存储器有 128 字节的内部 RAM 以及

128字节的特殊功能寄存器I/O 空间。AT89LP213/214不支持外部数据存储器或外部程序存储器。

6.1 程序存储器

AT89LP213/214包含2K字节的片上系统内可编程Flash存储器用于保存程序。Flash存储器的使用

寿命至少为 10,000 次重复擦写,并且数据保持能力可达 10 年。复位和中断向量放在程序存储器

的开头的 59 字节 ( 参考 Table 13-2 on page 23)。常量表放在整个 2K 程序存储器地址空间,可

被 MOVC 指令访问。 AT89LP213/214 不支持外部程序存储器。

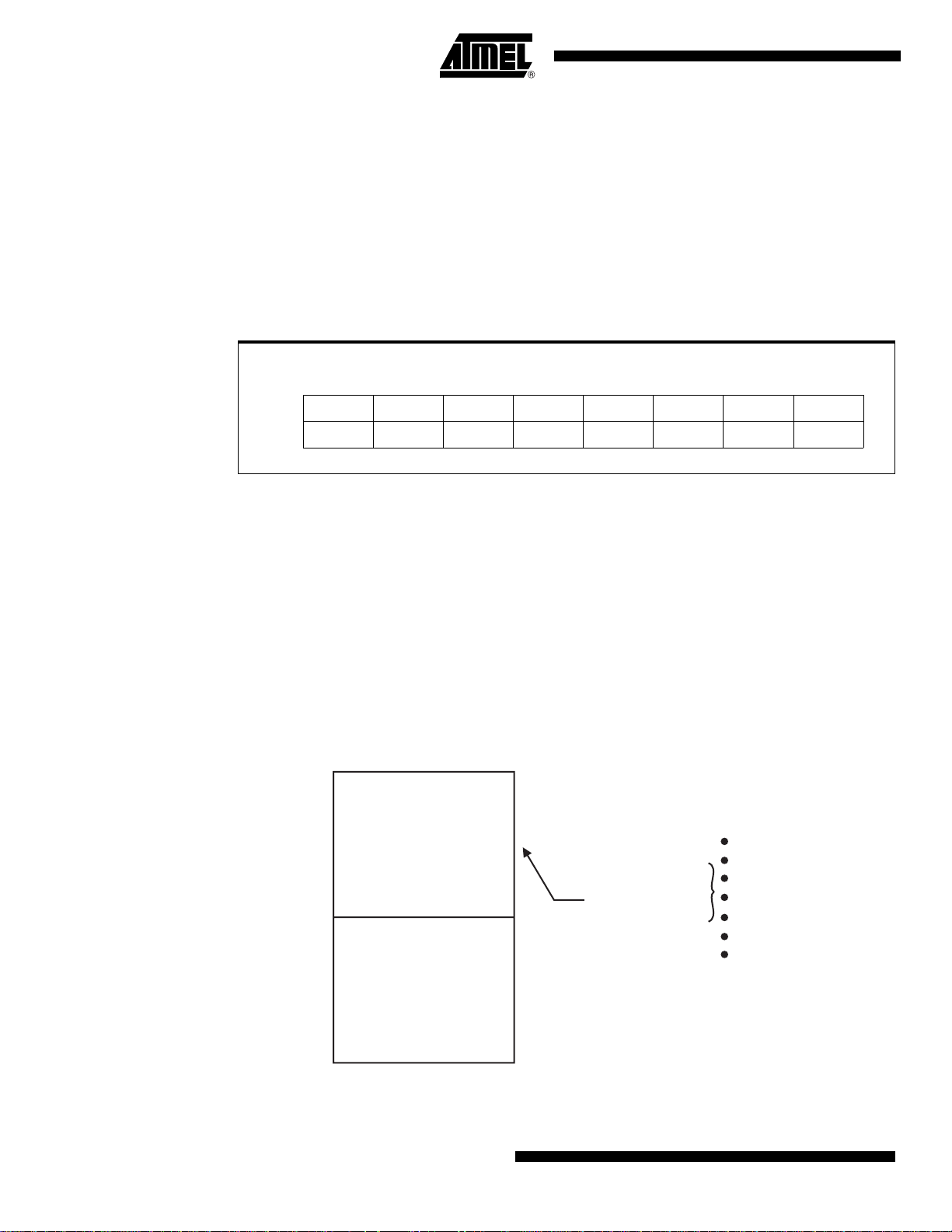

Figure 6-1. 程序存储器映射

007F

User Signature Array

0040

001F

Atmel Signature Array

0000

07FF

Program Memory

0000

3538A–MICRO–6/06

7

Page 8

AT89LP213/214 的程序存储器的一个映射见 Figure 6-1。除 了 2K 从 0000h 到 07FFh 的代码空间

外, AT89LP213/214 还支持一个 64 字节的用户签名数组和一个 32 字节的 Atmel 签名数组,它

们可以只读模式被 CPU 访问。为从签名数组中读取信息,必须设置 AUXR1 的 SIGEN 位。当

SIGEN是1时,MOVC A,@A+DPTR可访问签名数组。用户签名数组映射到地址 0040h到 007Fh,

Atmel签名数组映射到地址 0000h~001Fh。在 使 用 MOVC指令访问代码存储区时必须将 SIGEN清

零。

Atmel签名数组在出厂时用设备ID进行初始化。用户签名数组则可用作用户ID或者常参数据保存。

保存在签名数组中的数据是不安全的。安全位可禁止对该数组的写操作;但是,读取永远是被允

许的。

6.2 数据存储器

Table 6-1.

AUXR1 = A2H 复位值 = XXXX 0XXXB

不可位寻址

位 76543210

AT89LP213/214包含128字节的通用 SRAM数据存储器,另外还有128字节的I/O存储区,映射到

一个 8 位地址空间。128 字节的数据存储器可以通过对低 128 字节地址进行直接或间接寻址 来访

问。 128 字节的 I/O 存储区驻留在较高的 128 字节地址空间 (Figure 6-2)。 I/O 存储区只能通过直

接寻址方式访问并且包含特殊功能寄存器 (SFRs)。对较高的 128 字节地址的间接访问会返回无效

数据。数据存储器的最低的 32 个字节被分为 4 个组,每组有 8 个寄存器。RS0 和 RS1 位 (PSW.3

和 PSW.4) 选择使用哪个寄存器组。使用寄存器寻址的指令只访问当前指定的寄存器组。

AT89LP213/214 不支持外部数据存储器。

Figure 6-2. 数据存储器映射

FFH

AUXR1 – 辅助寄存器 1

––––SIGEN–––

Accessible

UPPER

128

80H

7F H

LOWER

128

0

8

AT89LP213/214 [Preliminary]

By Direct

Addressing

Only

Accessible

By Direct

and Indirect

Addressing

Only

Special Function

Registers

Ports

Status and Control Bits

Timers

Registers

Stack Pointer

Accumulator

(Etc.)

3538A–MICRO–6/06

Page 9

AT89LP213/214 [Preliminary]

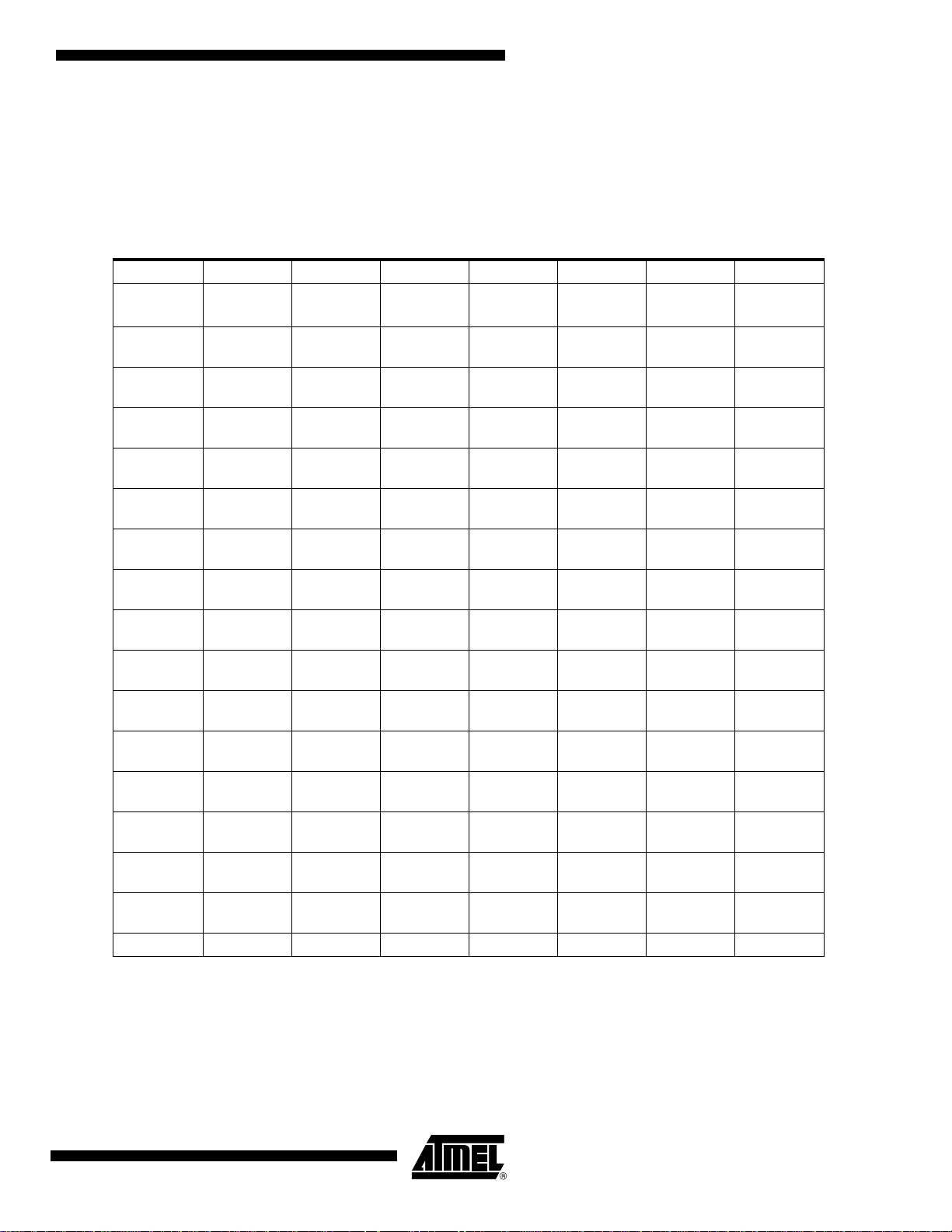

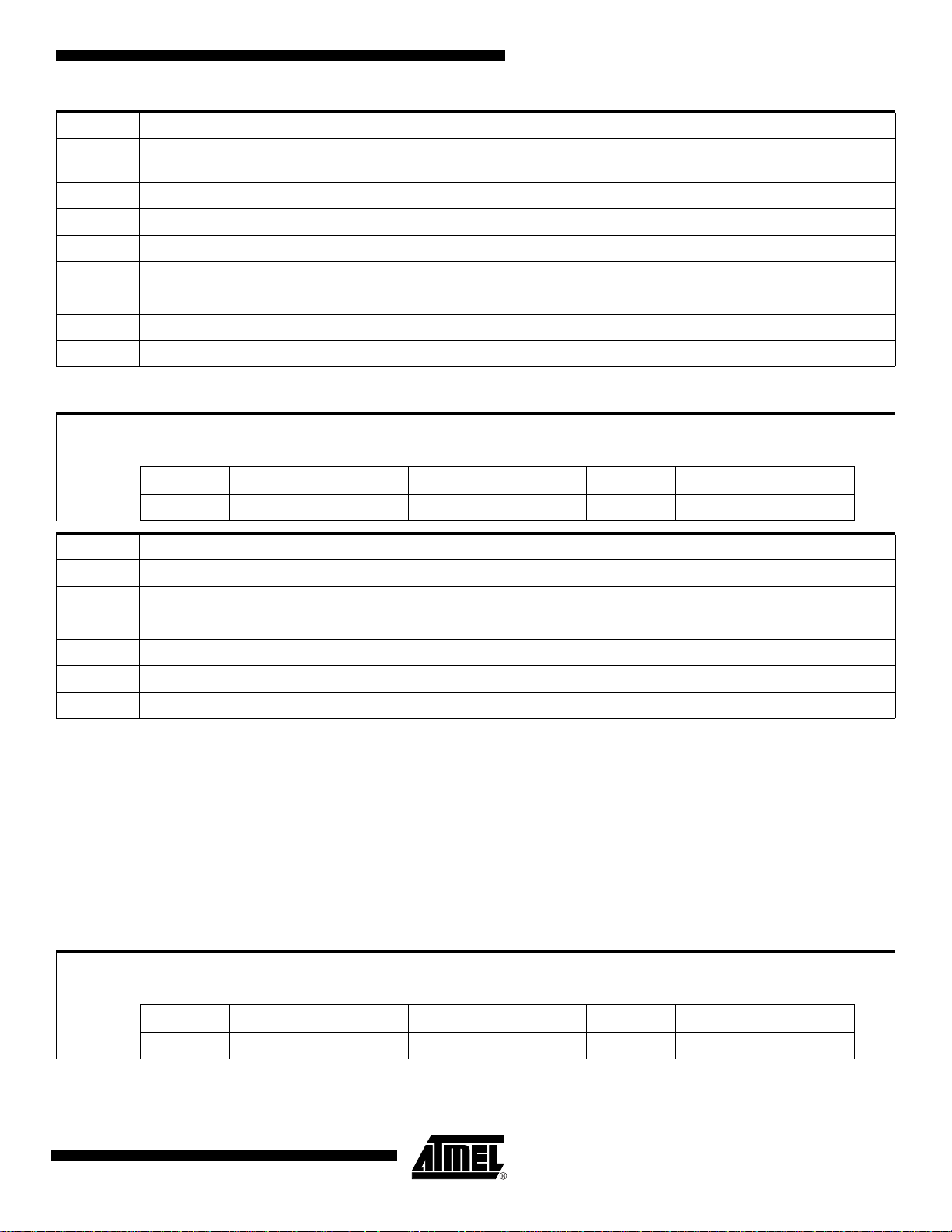

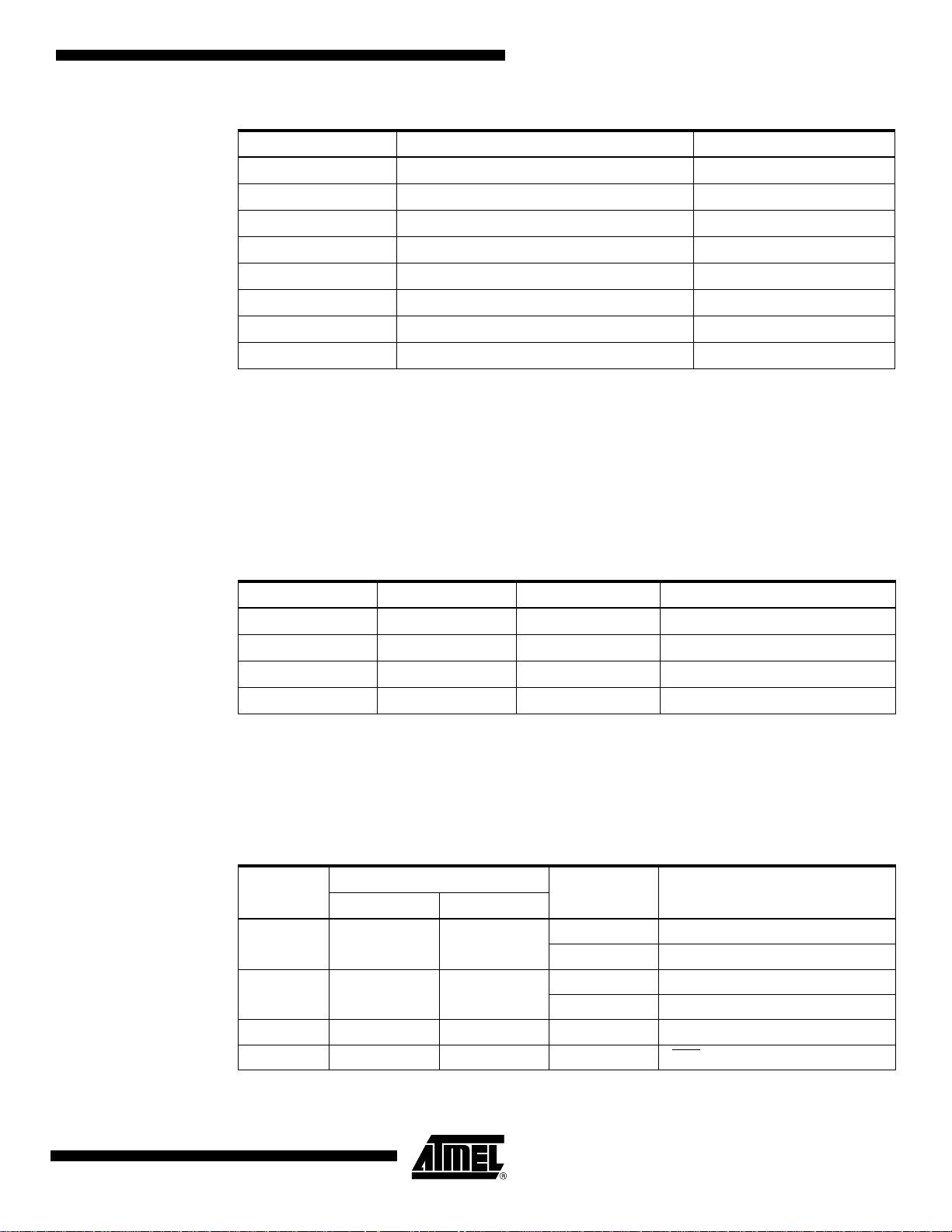

7. 特殊功能寄存器

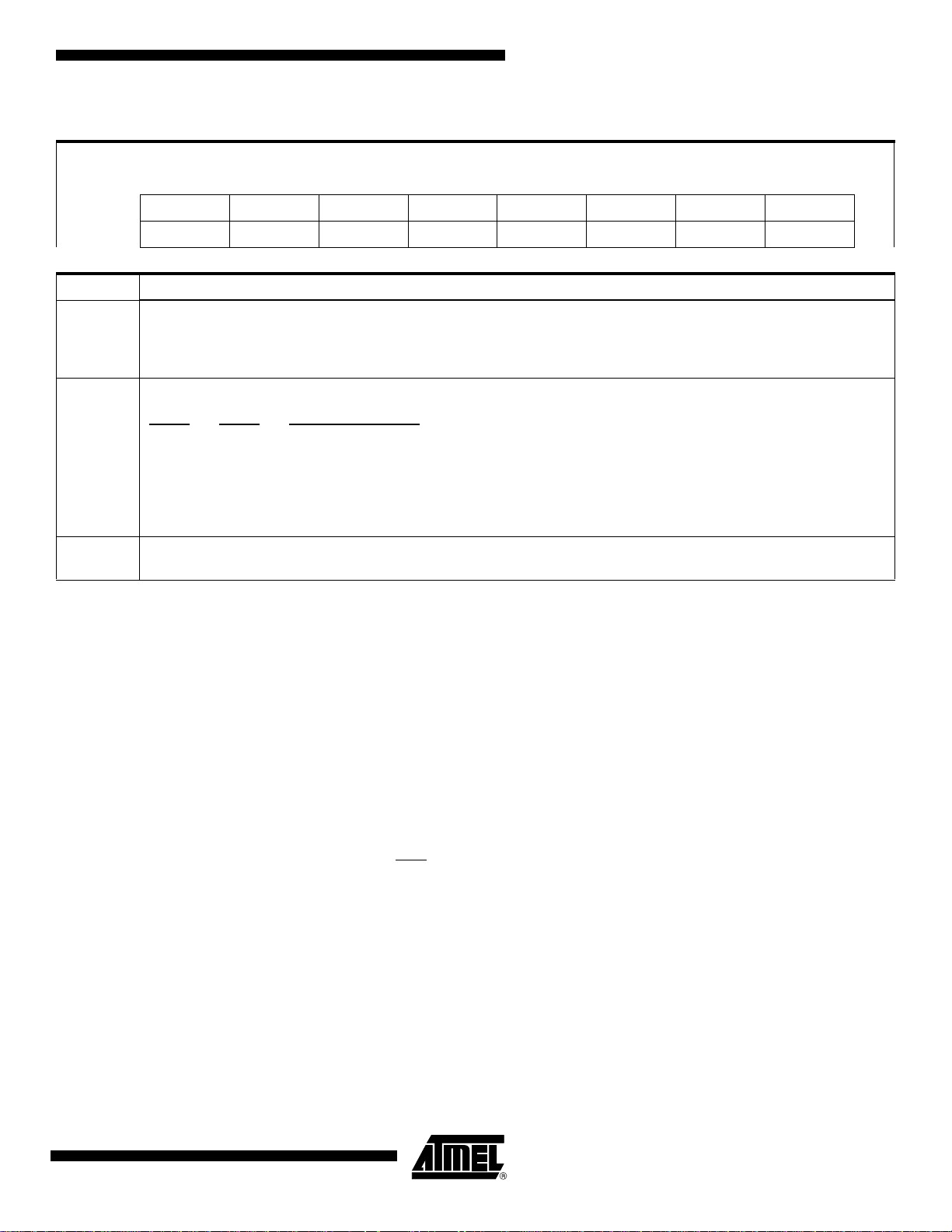

有一块片上存储区域的映射叫作特殊功能寄存器 (SFR) 空间,见 Table 7-1.

要注意并没有占用所有的地址,而没有使用的地址是在芯片上不可用的,读这些地址通常会返回

任意数据,而写操作会发生不可预料的结果。用户程序不应该对这些没有列出的地址进行写操作,

因为它们可能用于在将来的产品中引入新的特性。

Table 7-1. AT89LP213/214 SFR 映射和复位值

89ABCDEF

0F8H 0FFH

0F0H

0E8H

0E0H

0D8H 0DFH

0D0H

0C8H

0C0H P1M0

0B8H

0B0H

0A8H

0A0H AUXR1

98H

90H

88H

80H

B

0000 0000

SPSR

000x x000

ACC

0000 0000

PSW

0000 0000

IP

x000 0000

P3

xx11 1111

IE

0000 0000

SCON

0000 0000

P1

1111 1111

TCON

0000 0000

01234567

SPCR

0000 0000

SADEN

0000 0000

SADDR

0000 0000

SBUF

xxxx xxxx

TCONB

0010 0100

TMOD

0000 0000

SP

0000 0111

SPDR

xxxx xxxx

(2)

xxxx 0xxx

GPMOD

0000 0000

RL0

0000 0000

TL0

0000 0000

DPL

0000 0000

P1M1

xx00 0000

GPLS

0000 0000

RL1

0000 0000

TL1

0000 0000

DPH

0000 0000

GPIEN

0000 0000

RH0

0000 0000

TH0

0000 0000

GPIF

0000 0000

RH1

0000 0000

TH1

0000 0000

(2)

P3M0

WDTRST

(write-only)

P3M1

xx00 0000

IPH

x000 0000

WDTCON

0000 x000

ACSR

xx00 0000

CLKREG

0000 x000

PCON

0000 0000

0F7H

0EFH

0E7H

0D7H

0CFH

0C7H

0BFH

0B7H

0AFH

0A7H

9FH

97H

8FH

87H

Notes: 1. 最左边一列的所有 SFR 都是位可寻址的。

2. 当三态端口保险打开时,复位值为 xx11 1111B ,否则为 xx00 0000B。

3538A–MICRO–6/06

9

Page 10

8. 加强型 CPU

T

T

T

AT89LP213/214 使用一个加强型的 8051 CPU,它的运行速度是普通8051单片机的6到12倍。( 或

者说是 X2 型 8051 单片机速度的 3 到 6 倍 ). 速度的增加归功于下面两条因素。首先 ,CPU 每个时

钟周期就从代码存储器中取一条指令字节 .。其次 , CPU 使用一个二级流水线并行的取指令和执行

指令。这种基本的流水线操作理念使 CPU 的速度高达 1 MIPS 每 MHz。简单示例如图 Figure 8-1.

MCS-51 指令系统允许它的指令的长度可变。变化范围是 1 到 3 字节。在一个每字节单时钟取指令

的系统中,执行每一条指令至少需要和这条指令字节数一样多的机器时钟数 。 AT89LP213/214

中的大多数指令遵循如下规则 : 每一条指令的执行时间 (需要的时钟周期数)等于这条指令包含

的字节数 (有一些特例除外)。分支和调用需要一个额外的时钟周期以计算目标地址,并且某些

复杂的指令需要多个时钟周期。对于每一条指令的细节,请参见 59 页 “指令集摘要” 。 Figures

8-2 and 8-3 显示了一字节长和两字节长指令的情况。 .

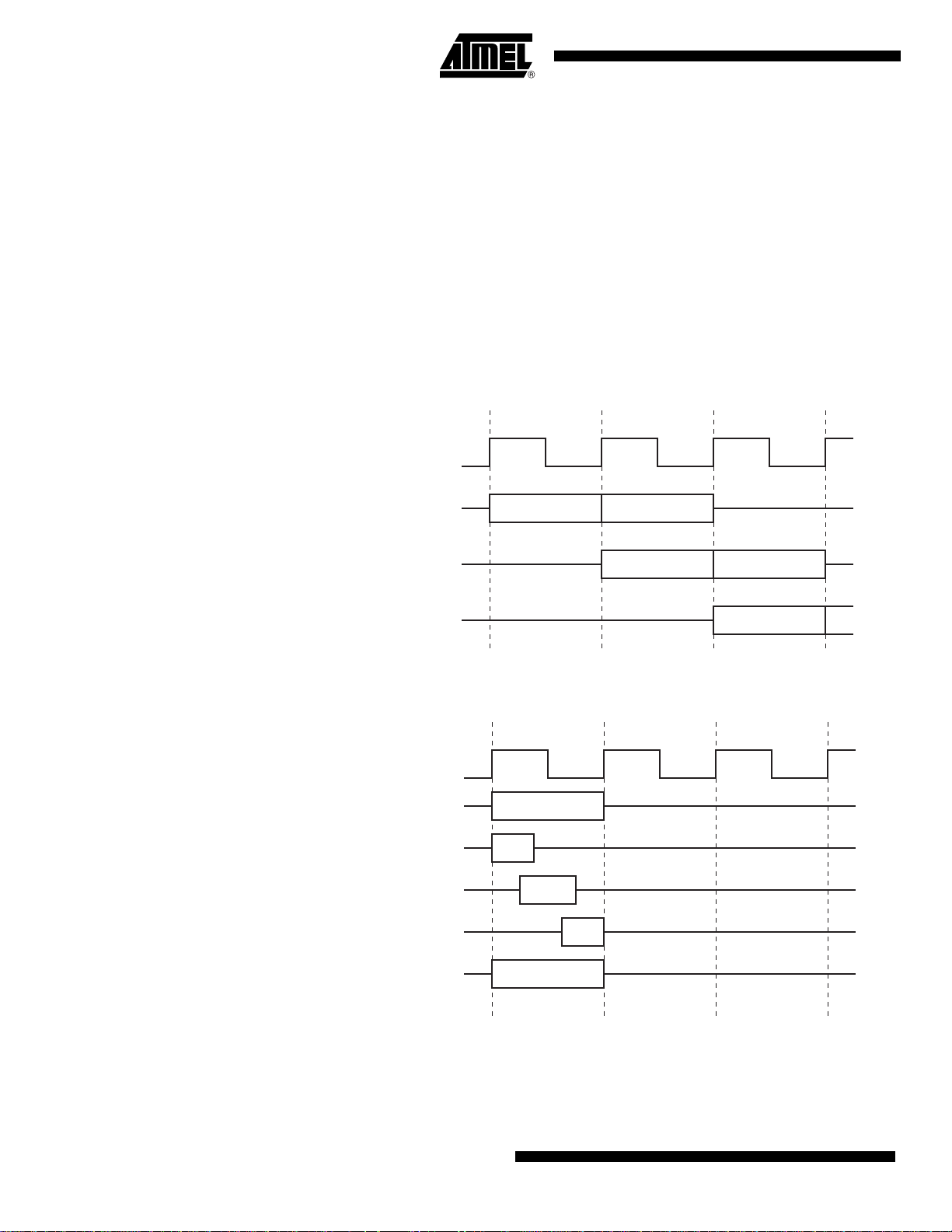

Figure 8-1. 取得和执行并行指令

System Clock

th

n

(n+1)

Instruction

th

Instruction

Fetch Execute

(n+2)th Instruction

Figure 8-2. 单周期 ALU 操作 ( 例 : INC R0)

T

System Clock

Total Execution Time

Register Operand Fetch

n

n+1

n+2

Fetch Execute

Fetch

1

T

2

T

3

10

ALU Operation Execute

Result Write Back

Fetch Next Instruction

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 11

AT89LP213/214 [Preliminary]

F

Figure 8-3. 两个周期的 ALU 操作 ( 例如 : ADD A, #data)

8.1 某些特殊指令的限制

AT89LP213/214 是 ATMEL 日益成长的微处理器家族的一款经济型性价比高的芯片。它包含 2K字节

的闪存程序存储器 . 他完全兼容于普通的 MCS-51 架构。可以使用 MCS-51 指令集编程。 然而在

使用某些特殊指令编程此芯片时,需要考虑某些特殊的情况。 所有关系到跳转或分支的指令都需

要考虑 AT89LP213/214 的闪存程序存储器的大小是 2K, 所以定义地址时,一定要注意不要超过这

个物理地址的极限。这就需要软件编程者多多注意。例如, LJMP 7E0H 是一条有效的指令,然而

LJMP 900H 就是一条无效的指令

System Clock

Total Execution Time

etch Immediate Operand

ALU Operation Execute

Result Write Back

Fetch Next Instruction

T

1

T

2

T

3

8.1.1 分支指令

只要编程时注意定义的分支地址在程序存储器尺寸 (AT89LP213/214 的地址范围从 000H 到

7FFH )范围以内,那么这些无条件分支命令 LCALL, LJMP, ACALL, AJMP, SJMP, 和 JMP

@A+DPTR 就可以正确的运行。 如果超出了它的物理地址的范围,将会造成无法预直的错误结

果。有条件分支命令例如 CJNE [...], DJNZ [...], JB, JNB, JC, JNC, JBC, JZ, 和 JNZ 等,情况与上

面的无条件分支命令相同。同样 ,如果超出了它的物理地址的范围,将会造成无法预直的错误结

果。 如果应用程序使用了中断,那么中断处理程序的入口地址同 8051 架构单片机的入口地址相

同。

8.1.2 MOVX 的相关指令 , 数据存储器

AT89LP213/214 包含 128 字节的内部数据存储器 . RAM 的存取地址如果超过 7FH 会返回无效的

数据。而且,堆栈的深度限制在 128 字节,与有效的 RAM 大小相同。堆栈指针也不可以指向的地

址大于 7FH. 这款芯片不支持外部数据存储器存取,也不支持外部程序存储器。 因此 , 命令 MOVX

[...] 在这款芯片上不能使用。

在通常的 8051 汇编程序中,即使我们写的语句违反了上面我们所说的这些限制,指令仍然可以集

合起来。所以,编程者必须知道芯片的物理特点和限制,以正确的使用命令。

.

3538A–MICRO–6/06

11

Page 12

9. 系统时钟

系统时钟直接有 3 个可选择的时钟源中的一个来产生。这 3 个时钟源分别是芯片内部的晶振,外

部时钟源和一个内部的 RC 震荡器。时钟源的选择是通过 Table 9-1 中的 Clock Source User Fuses

来设定的。并没有内部的时钟分频器对系统时钟分频得到 CPU 时钟,参见 “ 用户配置引脚 ” on page

69.

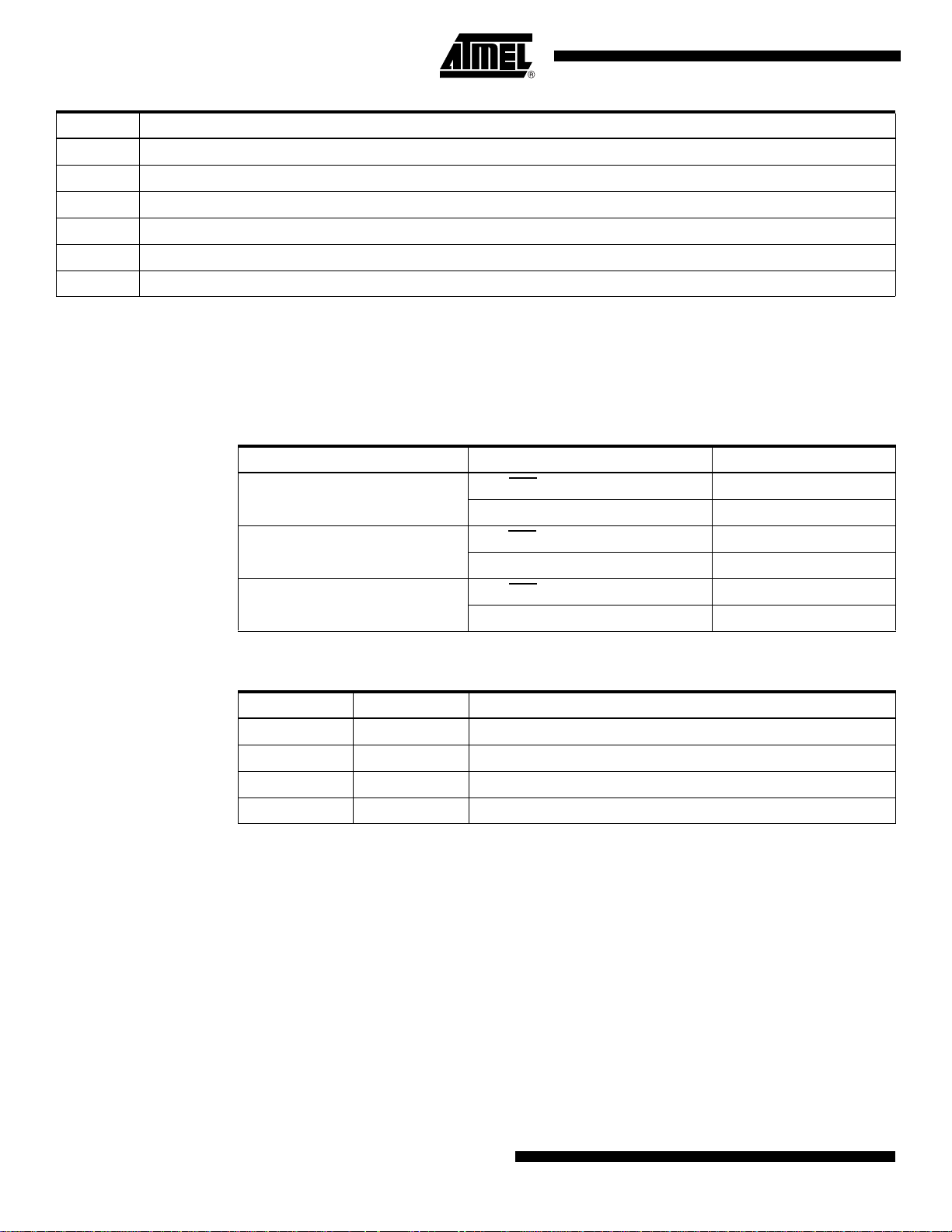

Table 9-1. 时钟源设定

9.1 晶振

9.2 外部时钟源

9.3 内部 RC 振荡器

Clock Source

Fuse 1

00晶振

01保留

1 0 XTAL1 上的外部时钟

11内部的 8 MHz RC 振荡器

当晶振被激活以后,内部的反向振荡放大器就被连接在 XTAL1 和 XTAL2 之间以连接一个外部的石

英晶振或者陶瓷振荡器。当使用晶振的时候,应该使 P3.2 和 P3.3 的输入或输出无效,XTAL2 不

可以在没有缓冲的情况下被用于驱动一个板级的时钟。

选择外部时钟会使振荡放大器无效并且允许 XTAL1 直接由时钟源来驱动。XTAL2 可以不连接,被用

做 P3.3 I/O 口,或者配置成为输出系统时钟的分开的版本。

AT89LP213/214 有一个内部的 RC 振荡器,频率范围在 8.0 MHz ±2.5%. 当它被激活作为时钟源

的时候, XTAL1 和 XTAL2 可分别作为 P3.2 和 P3.3 。 XTAL2 也可以 配置成为输出系统时钟的

分开的版本。 . 可以通过改变 RC Adjust Fuses 来调节振荡器的频率 . (See “ 用户配置引脚 ” on

page 69).

Clock Source

Fuse 0 选择的时钟源

9.4 系统时钟输出

12

AT89LP213/214 [Preliminary]

当 AT89LP213/214 被配置为使用外部时钟或内部 RC 振荡器的时候, XTAL2 (P3.3) 输出系统时钟

的 divided version 。可以通过设置 CLKREG 的 COE 位来激活此输出。两个 CDV 位决定了时钟的分

频数。 例如,当使用内部振荡器时,设定COE = “1” and CDIV = “00”将使P3.3的输出为3.950Mhz.

在使用时钟输出功能时,P3.3 必须设定为输出。

3538A–MICRO–6/06

Page 13

AT89LP213/214 [Preliminary]

Table 9-2.

CLKREG = 8FH 复位值 = 0000 0000B

不可位设定

Bit76543210

符号 Function

TPS3

TPS2

TPS1

TPS0

CDV1

CDV0

COE

CLKREG – 时钟控制寄存器

TPS3 TPS2 TPS1 TPS0 – CDV1 CDV0 COE

预脉冲计数器 . 预脉冲计数器从计数器 0。计数器 1,看门狗计数器中选择一个计数器。预脉冲计数器是一个 4 位二进制

的向下的计数器。当计数器计到 0 时,它会重载存储在 TPS 位中的值,从而给出分频的值。这个值的范围是从 1 到 16。

在默认情况下,每一个时钟,周期计数器都会计数。 (TPS = 0000B). 如果想配置计数器工作在通用的 8051 单片机情况下

(即每 12 个时钟周期计数),TPS 需要设定为 1011B.

时钟输出分频 . 决定了相对于系统时钟的始终输出频率。 .

CDIV1

00f/2

01f/4

10f/8

11f/16

时钟输出激活 . 设定 COE 以确定在 XTAL2 (P3.3)上输出的系统时钟的分频率。要使用此功能,必须选择内部 RC 振荡器

或者外部时钟源。 .

CDIV0 Clock Out Frequency

10. 复位

10.1 上电复位

在复位时,所有的 I/O 积存器都被设定为它们的初始值,芯片的管脚都是三态。程序从复位向量

0000H 开始执行。 AT89LP213/214 有五个复位源 : 上电复位 , 掉电复位 , 外部复位 , 看门狗复位 ,

和软件复位。

上电复位 (POR) 是由一个片上的检测电路产生的。检测级别是 1.4V. 当 Vcc 低于探测级别时,产

生一个上电复位。POR电路可以被用来触发一个复位或者在没有掉电探测器的情况下检测出供给电

源失败。POR 电路确保设备通过上电来复位。上电的顺序如图: Figure 10-1 on page 14. 当Vcc达

到了上电复位的阈值电压 V

,一个持续时间 t

POR

的初始化动作就开始了。初始化动作结束以

POR

后,启动定时器会决定设备在 Vcc 上升沿之后要保持在 POR 多长时间。当 Vcc 低于上电复位的阈

值电压时,POR 信号再一次被激活,没有任何的延迟。 上电复位 (例如冷复位)需要设定 PCON 中

的 POF 标志。通过保持 RST

脚低电平时间长过休息时间,内部产生的复位可以扩展到超过上电周

期。

3538A–MICRO–6/06

13

Page 14

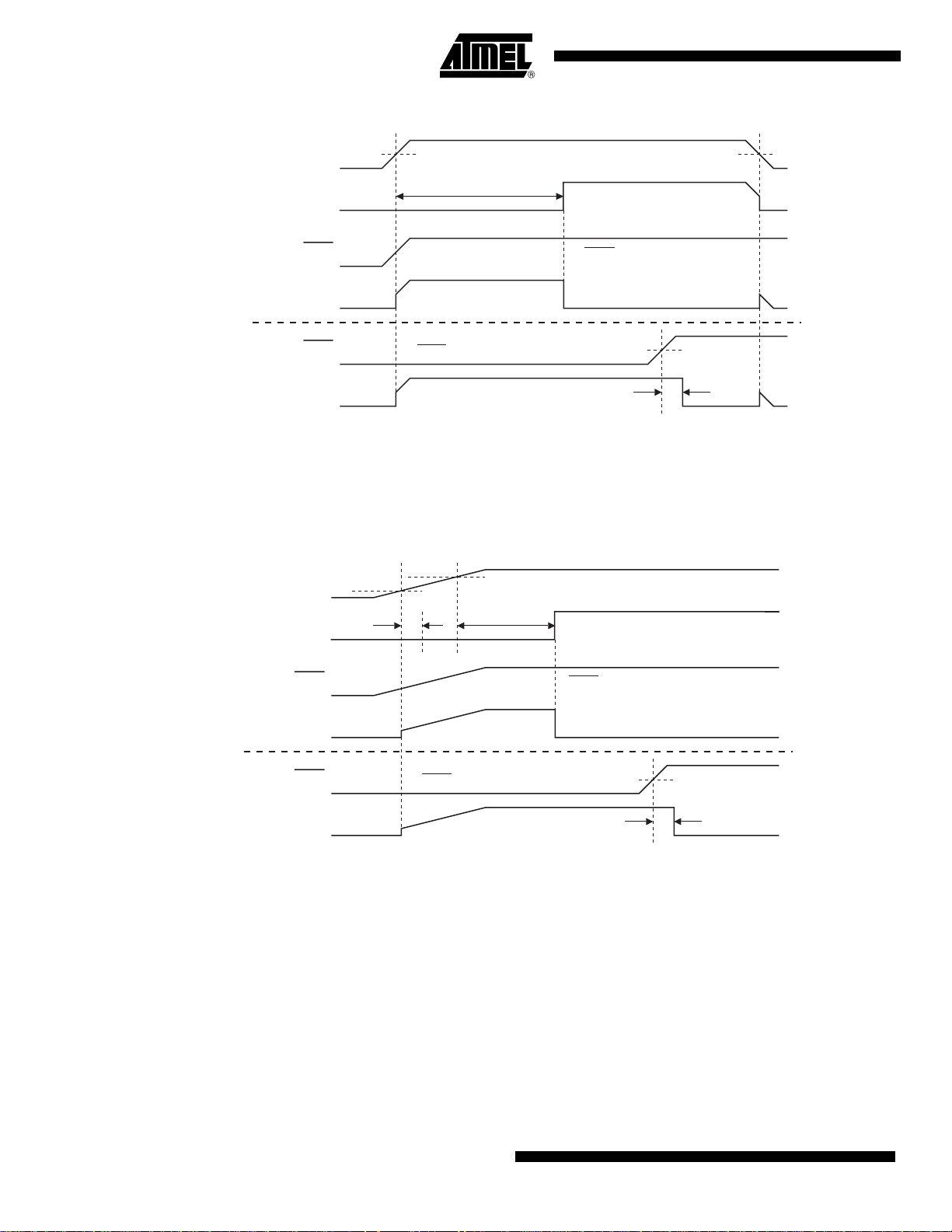

Figure 10-1. 上电复位时序 (BOD Disabled)

V

CC

V

POR

t

POR

+ t

SUT

V

POR

TIME-OUT

RST

(RST Tied to VCC)

INTERNAL

RESET

RST

INTERNAL

RESET

(RST Controlled Externally)

t

RHD

如果掉电探测器 (BOD) 也被激活, 那么直到 Vcc 达到如图 Figure 10-2 所示 的阈值电压 V

V

RH

,

BOD

启动定时器才开始计数。然而,如果在初始化完成之前,就出现这种情况,定时器必须首先等待

初始化完成再开始计数。

Figure 10-2. 上电复位时序 (BOD Enabled)

V

BOD

t

SUT

V

CC

TIME-OUT

t

POR

V

POR

RST

(RST Tied to VCC)

INTERNAL

RESET

V

RH

t

RHD

INTERNAL

RESET

Note: t

RST

近似等于 92 µs ± 5%.

POR

(RST Controlled Externally)

启动定时器的延迟依赖于时钟源 (Table 10-1),可以通过配置启动定时引线来设置这个延时。我们

设定启动延时时要注意给 Vcc 和可选时钟源提供足够的时间。启动定时引线同时也控制着掉电复

位后启动时间的长度,和在内部时控模式时下电后何时唤醒。

14

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 15

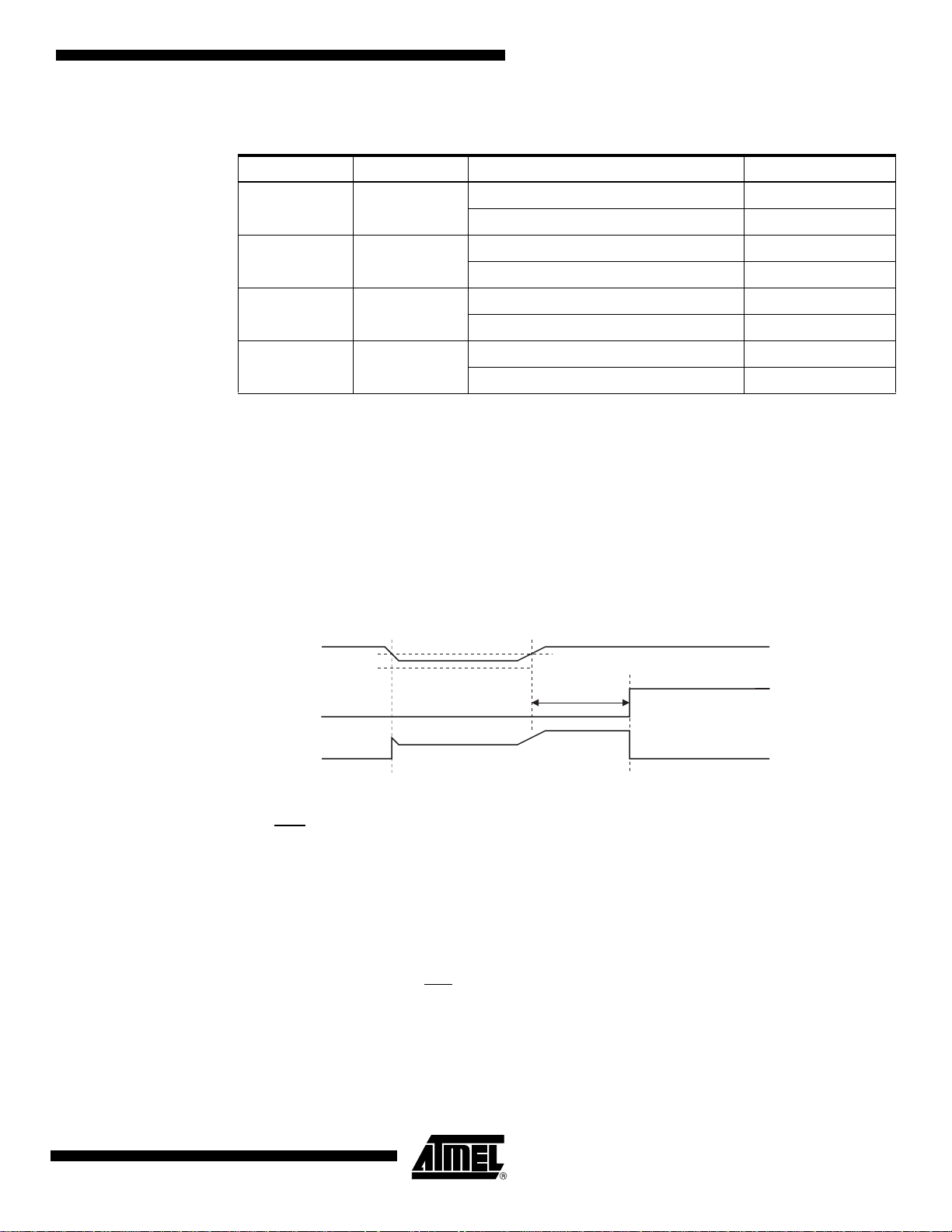

Table 10-1. 启动定时器设置

T

I

AT89LP213/214 [Preliminary]

10.2 掉电复位

SUT Fuse 1 SUT Fuse 0 时钟源 t

内部 RC/ 外部时钟 16 µs

00

晶振 1024 µs

内部 RC/ 外部时钟 512 µs

01

晶振 2048 µs

内部 RC/ 外部时钟 1024 µs

10

晶振 4096 µs

内部 RC/ 外部时钟 4096 µs

11

晶振 16384 µs

SUT (±

5%)

AT89LP213/214 有一个片上掉电探测电路 (BOD),它通过同一个固定的触发电平相比较以监控

Vcc 的情况。BOD 的触发电平是 2.2V。BOD 的作用是当系统在高速工作时,如果出现 Vcc 电压错

误,系统可以安全平稳的进入复位状态,而不会发生一些包括运行错误等的可能的错误。 BOD 的

时序如图 Figure 10-3. 当 V

减小到低于触发电平 V

CC

, 时,立即启动内部复位。当 Vcc 增加到

BOD

高于触发电平时,启动定时器在暂停周期满之后释放内部复位 (Table 10-1)。只有设置了 BOD 激活

引线之后才可以激活掉电探测器。 (See “ 用户配置引脚 ” on page 69).

10.3 外部复位

Figure 10-3. 掉电探测器复位

V

V

CC

V

POR

BOD

t

SUT

IME-OUT

NTERNAL

RESET

P1.3/RST 脚既可以作为一个低有效的复位输入,也可以作为一个通用的数字 I/O 口。当复位脚激

活引线被设置为 1 时,P1.3 脚的外部复位输入功能就被激活了。 (See “ 用户配置引脚 ” on page

69). 当清0 时, P1.3 可以被用做一个输入或者输出脚。当配置成复位输入时,要出发内部复位,管

脚必须至少保持在低电平 2 个时钟周期。

Note: 在上电时序中,引线选择总是无效的,因此,管脚总是执行着复位输入的功能。 与此管脚相连的外

部电路在上电时不可以将此管脚保持在低电平因为这将会导致芯片一直处于复位状态,除非将此管

脚拉高。 在上电延迟之后,这个输入脚或者执行一个外部复位输入功能或者是执行一个由引线位定

义的数字输入功能。只有上电复位时会使由复位引线位定义的选择项无效。而别的复位源不会使复

位引线位无效。 P1.3/RST

时,ISP 功能就被激活了。当复位脚被引线位设置无效时,可以在上电时通过将 P1.3 拉低来实现

ISP 功能。

也可以用做系统编程 (ISP)激活管脚。当外部复位脚被保持在低电平

3538A–MICRO–6/06

15

Page 16

10.4 看门狗复位

10.5 软件复位

11. 省电模式

11.1 空闲模式

当看门狗计数器溢出后,它将产生一个持续 16 个时钟周期的内部复位脉冲。看门狗复位也会设置

WDTCON 积存器的 WDTOVF 标志位。为了阻止看门狗复位,在看门狗溢出之前,必须将看门够

复位序列 1EH/E1H 写入到 WDTRST 中去。关于看门狗的操作细节请参照 . See “ 可编程看门狗

定时器 ” on page 55

可以通过软件写 5AH/A5H 到 WDRST 积存器中,使 CPU 产生一个内部的 16 个时钟周期的复位脉

冲。软件复位将会把 WDTCON 积存器中的 SWRST 位置 1。关于软件复位的详细信息请参见 .

See “ 软件复位 ” on page 55

AT89LP213/214 支持两种不同的低功耗模式:空闲模式和省电模式。这两种模式可以通过 PCON

来设定。

设定 PCON 的 IDL 位可以使芯片进入空闲模式。空闲模式下,内部 CPU 时钟停止工作。CPU 的状

态保持不变。包括 RAM, 堆栈指针,程序计数器,程序状态字和数字存储器。各个端口管脚的状态

保持在系统进入空闲模式时候的状态。空闲模式下,外部设备仍然运转,这样,当中断产生时,

它们就可以唤醒芯片。 定时器 , UART, SPI, 和 GPI 模块也会保持运转 . 在空闲模式下, 比较器或

者看们狗可以设定为工作状态或停止状态。任何中断或者复位都可以使系统结束空闲模式。当通

过中断结束空闲模式时,中断服务程序立即被执行。 之后的下一条指令 RETI 应该是使系统进入

空闲模式。

11.2 待机模式

设置 PCON 中的待机位 (PD)可以使系统进入待机模式。待机模式下振荡器停止工作,闪存掉电,

这样功耗就可以降到最低。此时只有上电电路保持有效。在待机模式下,电源供给电压可以减小

到保持 RAM 活动状态的电压。RAM 里面的内容会保持不变,但一旦 Vcc 降下来,我们无法保证 SFR

中的内容保持不变。可以通过外部复位,上电复位,或者某些特定的中断来结束待机状态。

11.2.1 待机模式下的中断恢复

可以通过三个外部中断来结束待机模式。当 XTAL1 或 XTAL2 没有被用于晶振或外部时钟的时候 可

以用来通过外部中断 INT0

INT0

或 INT1 来唤醒系统,中断必须被激活和配置成电平敏感模式。 当 RST 脚无效时,通用中

断 3 (GPI3)也可以用来唤醒系统。为了外结束待机模式, GPI3 必须被激活和配置为低电平探

测模式。

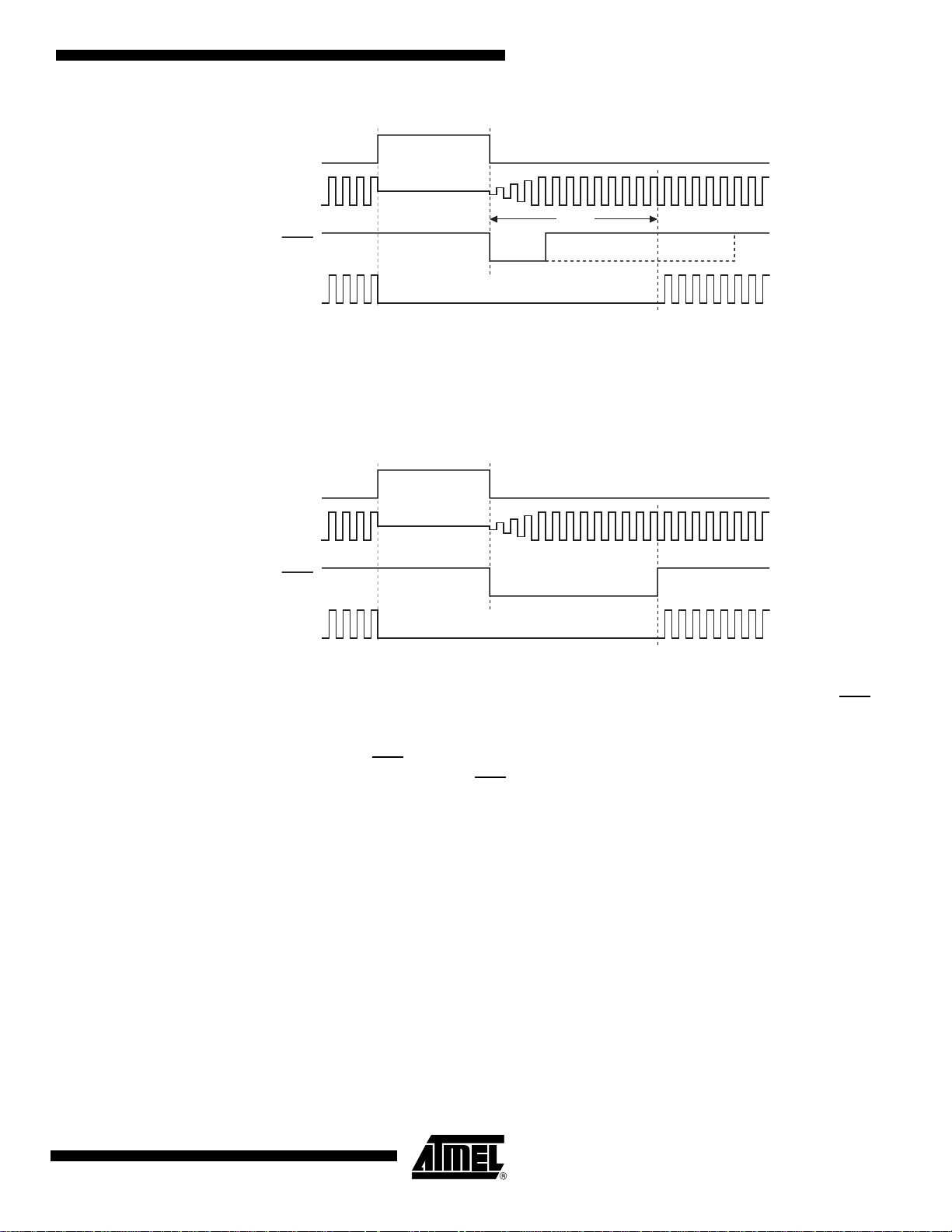

当通过中断结束待机模式时,两种不同的唤醒模式有效。当 PCON 中的 PWDEX 位是 0 时,唤醒周期

由如图 Figure 11-1 所示内部时控。在中断管脚的下降沿时结束待机模式,重启晶振,内部定时

器开始计数。直到定时器溢出,内部时钟才可以向 CPU 传送。溢出周期结束之后,开始调用中断

服务程序。溢出周期由启动计时引线来设定。 ( 参见 Table 10-1 on page 15). 在整个溢出周期,中

断引脚不需要一直保持低电平。

(P3.2) 和 INT1 (P3.3) 结束系统的待机状态。为了可以通过外部中断

16

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 17

AT89LP213/214 [Preliminary]

I

I

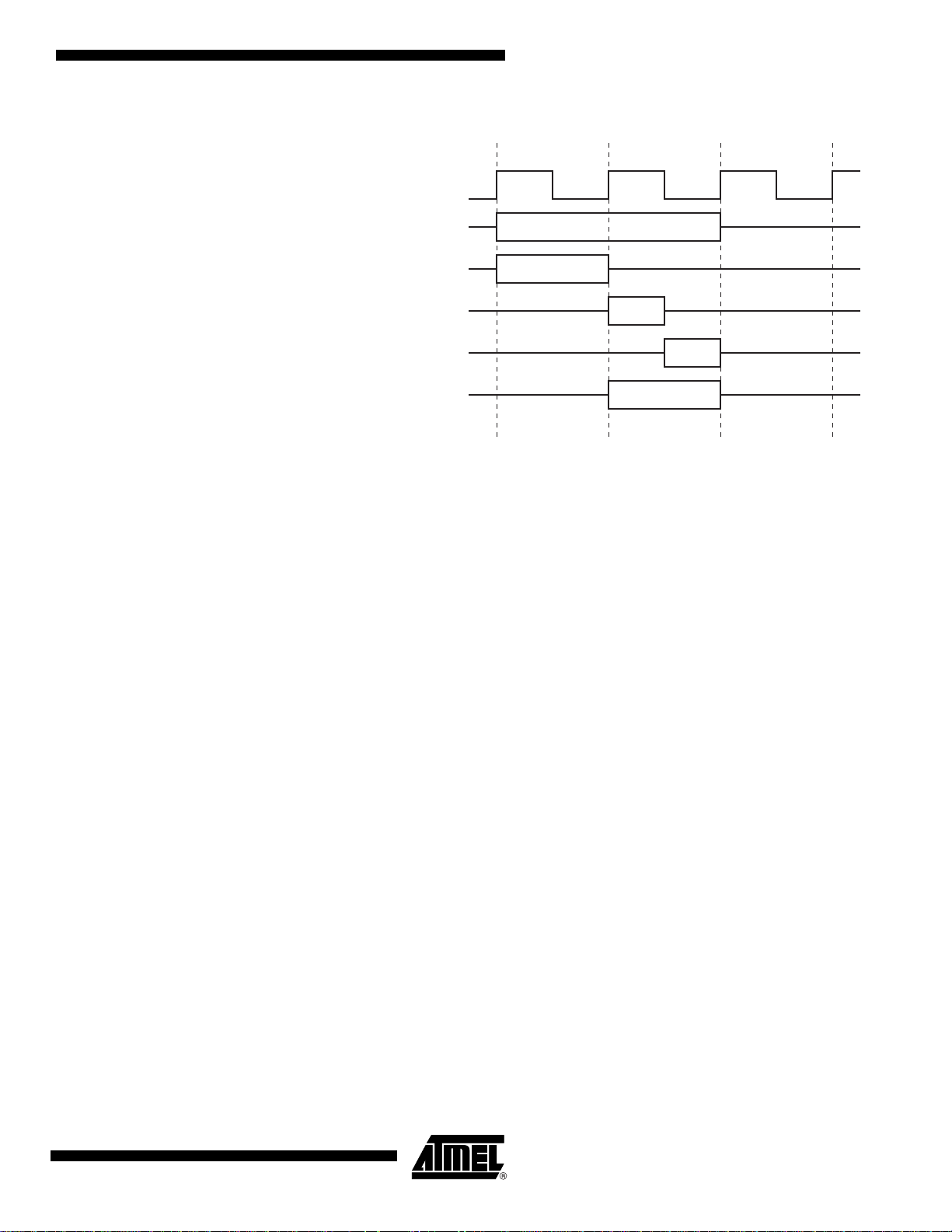

Figure 11-1. 待机模式下的中断恢复 (PWDEX = 0)

PWD

XTAL1

t

SUT

INT1

NTERNAL

CLOCK

当 PWDEX = “1” 时,唤醒周期表面上看起来是由中断所控制的。在中断管脚信号的下降沿,待机

模式结束并且重启振荡器。然而,直到如图 Figure 11-2 所示 的中断管脚信号的上升沿,内部时

钟才开始工作。 为了使选定的时钟源稳定,中断管脚的信号必须保持足够时间的低电平。中断管

脚信号的上升沿之后,系统调用中断服务程序。

Figure 11-2. 待机模式下的中断恢复 (PWDEX = 1)

PWD

XTAL1

NTERNAL

CLOCK

11.2.2 待机模式下的复位恢复

通过一个外部的复位来将系统从待机模式下唤醒和用 PWDEX = “0”. 的中断差不多。 在 RST

号的下降沿,结束待机状态,重启振荡器,如图 Figure 11-3 所示的内部定时器开始计数。直到这

个定时器溢出,内部时钟才对 CPU 起作用。 溢出周期由启动时间引线控制参见Table 10-1 on page

15 如果在溢出之前 RST

否则,芯片将保持复位状态一直到 RST

INT1

, 信

回到高电平状态,当内部时钟重启时,一个两周期的内部复位就产生了。

信号被拉高。

17

3538A–MICRO–6/06

Page 18

Figure 11-3. 待机模式下的服位恢复 .

I

I

PWD

XTAL1

RST

NTERNAL

CLOCK

NTERNAL

RESET

t

SUT

Tabl e 11 -1.

PCON = 87H 复位值 = 000X 0000B

不可位寻址

Bit76543210

符号 功能

SMOD1 双倍波特率位 . 在模式 1,2,3 下 UART 双倍波特率

SMOD0 祯错误选择 . 当 SMOD0 = 1, SCON.7 是 SM0. 当 SMOD0 = 1, SCON.7 是 FE (此处有误?)。注意无论 SMOD0 的状态

PWDEX 待机结束位 . 当 PWDEX = 1 时 , 待机模式下的唤醒由外部控制。当 PWDEX = 1 时 , 待机模式下的唤醒是内部时控的。

POF 关电标志 . 在上电时,POF 位被设置为 1 ( 例如: 冷重启 )。它可以通过软件来置位或重启,而不受 RST 或 BOD 的影响。 (

GF1, GF0 通用标志位

PD 待机位 . 该位 置位则系统进入待机模式 .

IDL 空闲模式位 . 该位置位则系统进入空闲模式

PCON – 电源控制寄存器

SMOD1 SMOD0 PWDEX POF GF1 GF0 PD IDL

如何,一个祯错误之后都要设成 FE..

例如热重启 ).

12. 中断

AT89LP213/214 提供了 7 个中断源 : 两个外部中断 , 两个定时器中断,一个串口中断,一个通用中

断,和一个模拟比较器中断。这些中断和系统复位在程序存储空间的开始处都各自有一个独立的

程序向量。通过设置中断激活寄存器 (IE)的一位可以使每一个中断源有效或失效。IE 寄存器也

包含一个全局的中断开关位 EA, 可以使所有的中断源无效。

每一个中断源(模拟比较器除外)都可以通过设置或清除中断优先级寄存器 IP 和 IPH 来独立的设

定它的中断优先级,一共有四个中断优先级。模拟比较器的中断被固定在最低优先级。一个在运

行的中断服务程序可以被一个比它优先级高的中断打断,但不可以被与它相同或更低的中断优先

级的中断打断。最高优先级的中断不可以被任何其它的中断源打断。如果在某条指令的最后同时

有两条不同中断优先级的中断请求,那么系统响应高优先级的中断。如果在某条指令的最后同时

有两条相同中断优先级的中断请求,则一个内部的查询将会来决定系统响应那一条中断。

18

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 19

AT89LP213/214 [Preliminary]

轮询序列是基于向量地址的,低向量地址的中断优先级高于高向量地址的中断。注意,轮询序列

只用于解决为响应的同优先级的中断 。

根据 TCON 寄存器的 IT0 和 IT1 位,外部中断 INT0

和 INT1 都可以是电平触发或边沿触发。实

际上产生这些中断的标志是 TCON 的 IE0 和 IE1 位。当服务例行程序是矢量时,只有当中断是边沿

触发时,硬件清除标志位才可以产生外部中断。如果中断是电平触发的,那么外部请求源 (而不

是片上硬件)控制请求标志。

定时器 0 和定时器 1 的中断由 TF0 和 TF1 产生,当各自的定时 / 计数寄存器溢出时置位 (除了定

时器 0 工作于方式 3)。当产生定时器中断时,如果服务例行程序是矢量的,则片上硬件清除产生

中断的标志位。

串行口中断是由 SCON 的 RI 和 TI 的或逻辑加上 SPSR 的 SPIF 产生的。如果服务例行程序是矢量

的,所有这些标志位不能由硬件清除。实际上,服务例行程序通常要检测 RI, TI, 或 SPIF 有没

有产生中断,这些位必须由软件清零。

GPIF 寄存器的八个标志位的或逻辑产生通用中断。如果服务例行程序是矢量的,所有这些标志位

都不能由硬件清零。服务例行程序必须检测中断是由哪位产生的,该位必须由软件清零。如果中

断是电平触发的,那么在软件清除标志位前,外部请求源必须保持中断信号。

ACSR 寄存器的 CF 位产生比较中断。如果服务例行程序是矢量的,这个标志位不能由硬件清除,而

必须由软件清除。

大多数产生中断的位可以由软件置位或清零,与由硬件置位和清零的效果相同。也就是说,可以

由软件产生中断和取消未响应的中断。SPI 中断标志位 SPIF 和通用中断标志位 GPIF 是两个例外。

这两个标志位只能由硬件置位,软件清除。

Table 12-1. 中断向量地址

12.1 中断响应时间

中断 源 向量地址

系统重启 RST or POR or BOD 0000H

外部中断 0 IE0 0003H

定时器 0 溢出 TF0 000BH

外部中断 1 IE1 0013H

定时器 1 溢出 TF1 001BH

串行口 RI or TI or SPIF 0023H

通用中断 GPIF 002BH

模拟比较器 CF 0033H

中断标志位可以在任何时钟周期由硬件置位。在进程中指令的最后一个时钟周期,中断控制器获

得标志位。如果在前述的周期中,一个标志位被置位,在轮询周期中会被发现,并且中断系统会

在适当的服务例行程序中产生 LCALL,作为下一条指令。在以下情况下中断不会被响应:相同优先

级或较高优先级的中断正在运行中;运行中的指令是 RETI 或者任何写入 IE, IP, 或 IPH 寄存器

的。这些情况中的任何一种会阻止对中断服务例行程序产生 LCALL。第二个条件确保如果在运行中

3538A–MICRO–6/06

19

Page 20

的指令是 RETI 或者任何访问 IE,IP 或 IPH 寄存器的,那么在中断矢量化前至少还可以执行一条

n

指令。轮询周期在每条指令的最后一个周期重复,选中的值是前述周期中存在的值。如果因为以

上原因一个激活的中断标志位没有被响应,且当上述原因消除后中断不再是激活的,那么这个中

断将不被响应。换一句话说,中断源一旦被激活但是没有被响应的不会被记录。每一个轮询周期

是新的。

如果请求被激活且满足被响应的条件,硬件子例行程序调用请求的服务例行程序,使其成为下一

条被执行的指令。调用程序本身需要四个周期。因此,在激活中断请求和开始执行第一条服务例

行程序的指令之间,至少要消耗五个完整的时钟周期。如果请求被前面所列的原因阻止了,那就

需要更长的响应时间。如果同级的中断源或者更高优先级的中断源在运行中,附加等待时间取决

于其他中断的服务例行程序。如果运行中的指令不是处于最后一个时钟周期,附加的等待时间不

会超过 3 个周期,因为最长也只有 4 个周期。如果运行中的指令是 RETI 或者访问 IE 或 IP 寄存

器,附加的等待时间不会超过 7 个周期 (结束运行中的指令最多需要 3 个周期,加上结束下一条

指令最多需要 4 个周期)。因此,在单个中断系统中,响应时间总是大于 5 个时钟周期而小于 13

个时钟周期。见图 12 - 1 和图 12 - 2。

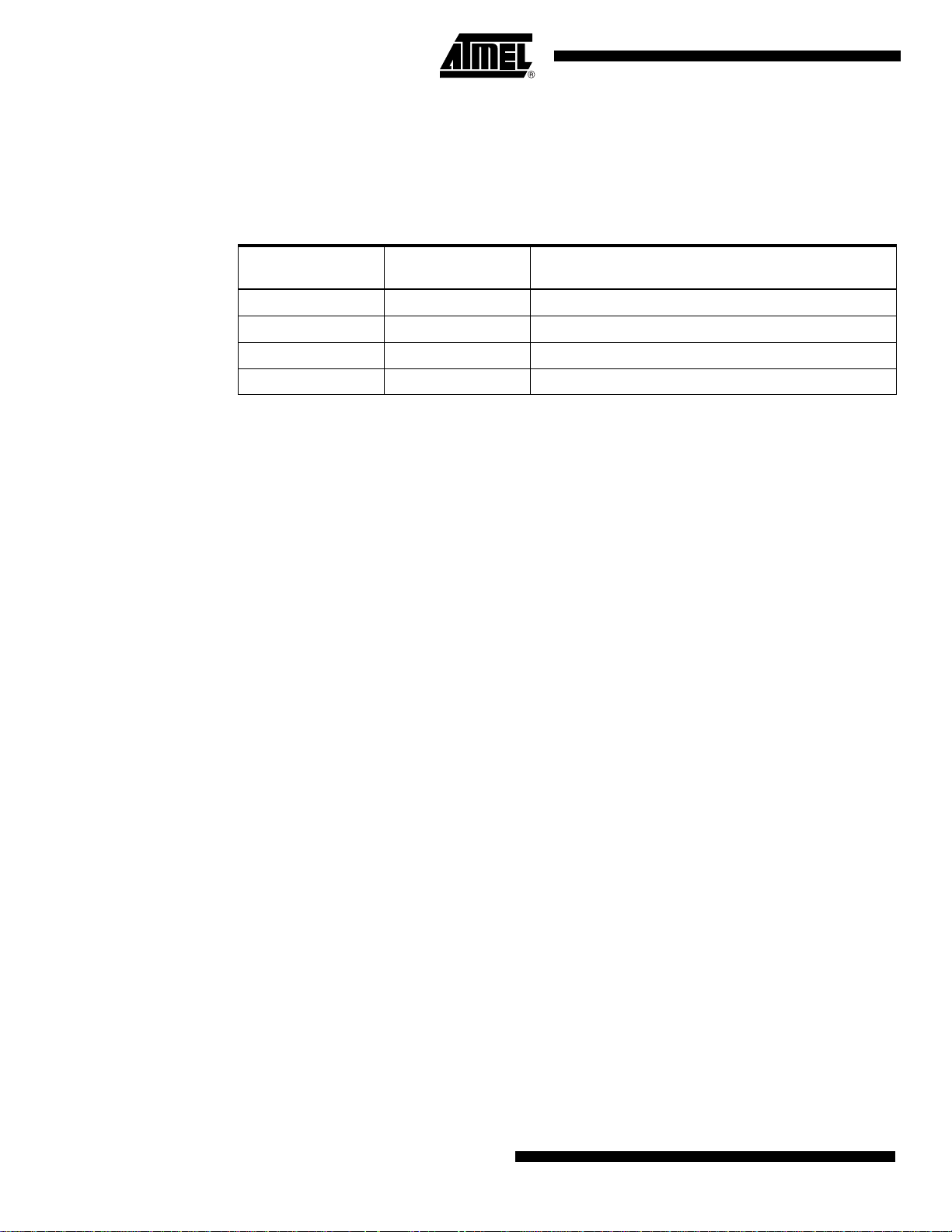

Figure 12-1. 最小中断响应时间

Clock Cycles

INT0

IE0

Instruction LCALL 1st ISR Instr.Cur. Instr.

15

Ack.

Figure 12-2. 最大中断响应时间

Clock Cycles

INT0

IE0

Instruction RETI 4 Cyc. Instr. LCALL 1st ISR I

113

Ack.

Table 12-2. IE – 中断允许寄存器

IE = A8H 复位值 = 0000 0000B

位可寻址

EA EC EGP ES ET1 EX1 ET0 EX0

Bit76543210

20

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 21

AT89LP213/214 [Preliminary]

符号 功能

EA 全部有效 / 失效 . 当 EA = 0 时,所有的中断失效 . 当 EA = 1 时 , 每个中断源通过设置 / 清除自己的使能位使中断有效 /

失效。

EC 比较器中断有效

EGP 通用中断有效

ES 串行口中断有效

ET1 定时器 1 中断有效

EX1 外部中断 1 有效

ET0 定时器 0 中断有效

EX0 外部中断 0 有效

.

Table 12-3. IP – 中断优先级寄存器

IP = B8H 复位值 = X000 0000B

位可寻址

–

位 76543210

–

PGP PS PT1 PX1 PT0 PX0

符号 功能

PGP 通用中断优先级低

PS 串行口中断优先级低

PT1 定时器 1 中断优先级低

PX1 外部中断 1 优先级低

PT0 定时器 0 中断优先级低

PX0 外部中断 0 优先级低

Table 12-4. IPH – 中断优先级高寄存器

IPH = B7H 复位值 = X000 0000B

不可位寻址

–

位 76543210

3538A–MICRO–6/06

–

PGH PSH PT1H PX1H PT0H PX0H

21

Page 22

符号 功能

PGH 通用中断优先级高

PSH 串行口中断优先级高

PT1H 定时器 1 中断优先级高

PX1H 外部中断 1 优先级高

PT0H 定时器 0 中断优先级高

PX0H 外部中断 0 优先级高

13. I/O 端口

AT89LP213/214 可以设置9到12个I/O引脚。有效的I/O引脚的精确数目取决于时钟和复位选择,如

表13-1所示。所有端口引脚 5V 的容限 , 也就是说可以被上拉或驱动到 5.5V, 即使工作在较低

的 V

Table 13-1. I/O 引脚配置

时钟源 复位选择 I/O 引脚数

外部晶体或振荡器

外部时钟

内部 RC 振荡器

CC,

如 3V

外部 RST

没有外部复位 10

外部 RST

没有外部复位 11

外部 RST

没有外部复位 12

引脚 9

引脚 10

引脚 11

.

13.0.1 准双向输出

.

Table 13-2. 端口 x, y 位配置模式

PxM0.y PxM1.y 端口模式

00准双向的

01推挽式输出

10只输入 ( 高阻抗 )

11开消耗输出

准双向输出模式的端口引脚功能与标准 8051 端口引脚相似。不需要重新配置端口,准双向的端口

就可以同时用作输入和输出 . 这是可行的,因为当端口输出一个逻辑高电平时,它被弱驱动,允

许外部设备把引脚电平拉低。当引脚低电平驱动时,强驱动使大电流减小。为了不同的目的,准

双向输出有 3 个上拉电阻 .

这 3 个上拉电阻中的一个叫做“极弱”上拉电阻,只要引脚的端口门限包含逻辑“1”,这个电阻

就是工作的。当引脚悬空时,这个极弱的上拉电阻产生极小的电流使引脚电平拉高 .

第二个上拉电阻叫做 “弱”上拉电阻,当引脚的端口门限包含逻辑 “1”且引脚本身是逻辑 “1”

电平时,这个电阻是工作的。这个上拉电阻提供准双向引脚输出为“1”的基本源电流。如果外部

设备把该引脚下拉为低电平,则这个弱上拉电阻关闭,只有极弱上拉电阻维持工作。 为了在这些

条件下使引脚电平下拉,外部设备不得不减小足够的电流抑制弱上拉电阻,并使端口引脚电平位

于输入门限电平以下。

22

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 23

AT89LP213/214 [Preliminary]

V

V

V

F

R

PWD

I

D

I

第三个上拉电阻是 “强”上拉电阻。这个上拉电阻的作用是,当端口门限由逻辑 “0”转换为逻

辑“1”时,可以加快准双向端口引脚的低电平到高电平的转换速度。当这种情况发生时,强上拉

电阻工作两个 CPU 周期,使端口电平迅速上拉。准双向端口配置如 Figure 13-1 所示 . 在下电时,

P1.3, P3.2 和 P3.3 的输入电流不是无效的 ( 见 Figure 13-3).

Figure 13-1. 准双向输出

13.0.2 只输入模式

1 Clock Delay

(D Flip-Flop)

CC

Strong

CC

Very

Weak

CC

Weak

Port

Pin

rom Port

egister

Input

Data

只输入端口配置如 Figure 13-2 所示 . 输出驱动是三态的 . 输入包括斯密特触发输入以提高对输入

噪声的抑制。在下电时, P1.3, P3.2 和 P3.3 的输入电路不是无效的 ( 见 Figure 13-3). 输入引脚可

以被安全的上拉到 5.5V ,即使工作在较低的 V

电平 ; 然而 , 斯密特触发器的输入门限是由 V

CC

CC

电平设置的,这一点必须考虑

Figure 13-2. I 只输入

nput

ata

Port

Pin

PWD

Figure 13-3. I P1.3, P3.2 和 P3.3 只输入

nput

Data

Port

Pin

13.0.3 开消耗输出

当端口门限包含逻辑“0”时,开消耗输出配置关闭多有的上拉,只驱动端口引脚的下拉电阻。为

了用作逻辑输出,在这种方式下端口配置必须要有外部上拉电阻,典型的是电阻与 V

相连。 这

CC

种模式的下拉电阻与准双向模式相同。开消耗配置如 Figure 13-4 所示 . 在下电时, P1.3, P3.2 和

P3.3 的输入电路不是无效的 ( 见 Figure 13-3). 开消耗引脚可以被安全的上拉到 5.5V ,即使工作在

较低的 V

3538A–MICRO–6/06

电平 ; 然而 , 斯密特触发器的输入门限是由 VCC 电平设置的,这一点必须考虑 .

CC

23

Page 24

13.0.4 推挽式输出

F

R

V

F

R

Figure 13-4. Open-Drain Output

Port

Pin

rom Port

egister

Input

Data

PWD

推挽式输出配置和开消耗与准双向输出模式有相同的下拉电阻结构,但是当端口门限包含逻辑

“1”时,提供持续的强上拉电阻。当端口输出需要更多的源电流时,采用推挽模式。推挽端口配

置如 Figure 13-5 所示 . 在下电时, P1.3, P3.2 和 P3.3 的输入电路不是无效的 ( 见 Figure 13-3).

Figure 13-5. 推挽式输出

CC

Port

Pin

13.1 端口 1 模拟功能

AT89LP213/214结合了模拟比较器 . 为了给出做好的模拟效果和最小化功率损耗,作为模拟功能的

引脚必须使他们的数字输出和数字输入无效 . 如 22 页 “端口配置”描述的,使端口引脚处于只输

入模式可以使端口引脚的数字输出无效。只要设置 ACSR 的CEN 位使模拟比较器有效,那么 P1.0

和 P1.1 的数字输入是无效的。 CEN 迫使 P1.0 和 P1.1 的 PWD

发电路无效 . 在复位后不管三端口得状态如何, P1.0 和 P1.1 总是默认为只输入模式 .

13.2 端口 读 - 修改 - 写

读引脚的状态还是读端口寄存器的状态取决于使用的指令。简单的读指令总是直接访问端口引脚

读 - 修改 - 写 指令 , 就是读到一个值,可能修改这个值 , 然后重新写回去 , 这个指令总是访问端口

寄存器 . 包括位写入指令,如 CLR 或 SETB ,它们实际上读了整个端口,修改单独的位,然后把

数据重新写回整个端口 . 如 Table 13-3 所示,列出了所有访问端口的读 - 修改 - 写指令 .

Table 13-3. 端口读 - 修改 - 写指令

助记符 指令 举例

ANL 逻辑 AND ANL P1, A

ORL 逻辑 OR ORL P1, A

rom Port

egister

Input

Data

PWD

输入为的电平 , 因此使斯密特触

XRL 逻辑 EX-OR XRL P1, A

24

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 25

13.3 端口选择功能

AT89LP213/214 [Preliminary]

Table 13-3. 端口读 - 修改 - 写指令

助记符 指令 举例

JBC 如果置位则跳转,同时清除该位 JBC P3.0, LABEL

CPL 补位 CPL P3.1

INC 递增 INC P1

DEC 递减 DEC P3

DJNZ 如果不是零则递减并跳转 DJNZ P3, LABEL

MOV PX.Y, C 把进位移动到端口 X 的 Y 位 MOV P1.0, C

CLR PX.Y 清除端口 X 的 Y 位 CLR P1.1

SETB PX.Y 设置端口 X 的 Y 位 SETB P3.2

AT89LP213/214 的大多数通用数字输入 / 输出引脚 与各种串行单元需要的输入 / 输出共享功能

Table 13-5 列出了端口引脚的选择功能. 选择功能以逻辑与的方式与引脚相连 . 为了使端口引脚的

选择功能有效 , 引脚相应的端口寄存器位必须为 “1” , 否则输入 / 输出总是为 “0” . 另外 , 在使

用前,每个引脚必须按照外设的要求配置成正确的输入 / 输出模式 . Table 13-4 给出了如何使通

用引脚配置为选择功能。

Table 13-4. 端口 x 引脚 y 选择功能配置

PxM0.y PxM1.y Px.y I/O 模式

00 1双向的 ( 内部上拉 )

01 1输出

10 X输入

11 1双向的 ( 外部上拉 )

Table 13-5. 端口引脚选择功能

配置位

端口引脚

P1.0 P1M0.0 P1M1.0

P1.1 P1M0.1 P1M1.1

P1.2 P1M0.2 P1M1.2 GPI2

P1.3 P1M0.3 P1M1.3 GPI3 RST

选择功能 注释PxM0.y PxM1.y

AIN0 只输入

GPI0

AIN1 只输入

GPI1

必须无效

3538A–MICRO–6/06

25

Page 26

Table 13-5. 端口引脚选择功能

配置位

端口引脚

P1.4 P1M0.4 P1M1.4

P1.5 P1M0.5 P1M1.5

P1.6 P1M0.6 P1M1.6

P1.7 P1M0.7 P1M1.7

P3.0 P3M0.0 P3M1.0 RXD

P3.1 P3M0.1 P3M1.1 TXD

P3.2 P3M0.2 P3M1.2 INT0 仅限于内部 RC 振荡器

P3.3 P3M0.3 P3M1.3

P3.4 P3M0.4 P3M1.4 T0

P3.5 P3M0.5 P3M1.5 T1

P3.6 not configurable CMPOUT 引脚与比较器输出相连

选择功能 注释PxM0.y PxM1.y

SS

GPI4

MOSI

GPI5

MISO

GPI6

SCK

GPI7

INT1

CLKOUT

仅限于 AT89LP214

仅限于内部 RC 振荡器或

外部时钟源

仅限于 AT89LP213

14. 性能增强型计时器计数器

AT89LP213/214 产品有两个16 位的计时计数器:计时器 0 和计时器 1。作为计时器,每一个时钟周

期寄存器增加一次。因此寄存器可以对时钟周期计数。因为每个时钟周期包括一个振荡周期,所

以计数频率就是振荡器频率。计时器频率可以通过可变频计时器从 1 到 16 改变。 (如表 9-2) .

两个计时器使用同一个分频器。

作为计数器,相应引脚 T0 或 T1 处有 1 到 0 的变化时寄存器就会相应的递增。每一个时钟周期都

会对外部输入进行采样。当采样值第一个周期为高电平,紧接着的那个周期为低电平,计数开始。

一旦检测到这种跳变,寄存器中的值就会刷新开始递增。因为进行这样的检测需要两个时钟周期,

所以最大的计数率也仅仅是振荡器频率的一半。对输入的信号没有约束,但信号必须确保检测到

的电平在变化之前至少保持了一个完整的时钟周期。在 AT89LP214 中, T0 和 T1 是不能通过引脚

输入的。但可以通过软件接换寄存器 3 中的 P3.4 和 P3.5 位来实现输入。

另外,计时器0和1就其功能来说有四种操作模式:可变宽度计时计数器,16 位自动重置计时计

数器、8 位自动重置计时计数器和分时计时计数器。可以通过特殊功能寄存器 TMOD 中的控制位 C/T

选择计时计数器功能。TMOD 中的 M1 和 M0 位用来选择操作模式。

14.1 模式 0 – 可变频计时计数器

两个计时器在模式 0 下都是可变频的 8 位计数器。分频器范围从 1 到 8 位,到底能变几位这要取

决于 TCONB 中的 PSC 位。这样计时器的范围就变成了 9 到 16 位。在标准 8051 模式 0 下的计时器

位数缺省值位13位。如图14-1所示。当计数器从全1变为全0时,中断标识符TF1会被置位。

计数输入是在 TR1=1 并且 GATE=0 或 INT1=1 有效的。给 GATE 置位使得外部输入 INT1 能够控制计

26

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 27

AT89LP213/214 [Preliminary]

INT1 Pin

pt

时器以便方便脉冲宽度测量。TR1 是特殊功能寄存器 TCON 中的控制位。GATE 是在 TMOD 中的。13

位寄存器是由TH1的8位和TL1中的低5位构成。TL1的高3位未定忽略。对TR1置位不会清零寄存器。

PSC

Mode 0: Time-out Period

Note: 在模式 0 下计时器 1 对 RH1/RL1 没有要求,可以用作临时存储寄存器。

256 2

------------------------------------------------------ -

Oscillator Frequency

Figure 14-1. 模式 0 下计时计数器:可变位数计数器

01+

×

TPS

1+()×=

OSC

T1 Pin

GATE

÷TPS

TR1

除了用 TR0、TF0 和 INT0 分别替代图 14 - 1 中相应的信号的情况,计时器 0 在模式 0 下的操作与

计时器 1 相同。这里有两种不同的 GATE 位,计时器 1 的是 TOMD.7,而计时器 0 则是 TOMD.3。 XTAL

振荡器使用 INT0

和 INT1 引脚 。它们只有在内部 RC 振荡器作系统时钟时实现 GATE 功能。

14.2 模式 1 – 16 位自动重置计时计数器

计时器在模式 1 下是 16 位自动重置。计时寄存器 16 位运行。16 位重置值放在高低重置寄存器 RH1

和 RL1 中。高低计时寄存器 TH1 和 TL1 相互配合完成计时。当收到时钟信号,计时器开始计数:

0000H、0001H、0002H……当 FFFFH 到 0000H 跳变时会发生溢出,这里还要注意计时寄存器是将

RH1和 RL1 中的值拿来重置并且 TCON 中的溢出标识位已经置位。如图 14 -2。重置缺省值为 0000H,

这样的 16 位计时器可与标准 8051 相比。模式 1 操作同样适应于计时计数器 0。

Mode 1: Time-out Period

C/T = 0

C/T = 1

Control

TL1

(8 Bits)

PSC1

TH1

(8 Bits)

65536

------------------------------------------------------ -

Oscillator Frequency

RH0RL

0{, }–()

TF1

TPS

Interru

1+()×=

3538A–MICRO–6/06

27

Page 28

Figure 14-2. 1 模式 1 下的计时计数器:16 位自动重置

INT1 Pin

pt

OSC

T1 Pin

GATE

14.3 模式 2 – 8 位自动重置计时计数器

模式 2 下的计时寄存器是自动重置的 8 位 (TL1)计数器。如图 14 - 3。TL1 溢出不仅要对 TF1 置

位,而且也要用 TH1 中的内容对 TL1 进行重置,这里的内容是预先用软件设置好的,而此时 TH1

内容并没有变化。模式 2 操作同样适合于计时计数器 0。

Mode 2: Time-out Period

Figure 14-3. 模式 2 下的计时器计数器:8 位自动重置

÷TPS

TR1

C/T = 0

C/T =1

Control

RL1

(8 Bits)

TL1

(8 Bits)

256

------------------------------------------------------ -

Oscillator Frequency

RH1

(8 Bits)

TH1

(8 Bits)

TH

0–()

Reload

TF1

TPS

Interru

1+()×=

Note: 在模式 2 下计时器 1 对 RH1/RL1 没有要求,可以用作临时存储寄存器。

14.4 模式 3 – 8 位分时计时器

模式 3 下的计时器 1 简单的说就是保持计数,相当于对 TR1 清零。模式 3 下的计时器 0 将 TL0 和

TH0独立,逻辑图如14-4所示。TL0用到计时器0的控制位:C/T, GATE, TR0, INT0 和 TF0。

TH0 用来对机器周期计数并且用到 TR1 和 TF1。因此 TH0 控制计时器 1 的中断。

模式 3 是为了满足额外 8 位计时计数器应用所需。从模式 3 下的计时器 0 看来,AT89LP213/214 产

品看起来好像就拥有了三个计时计数器;这种情况下,计时器 1 可以通过切换进出模式 3 来实现

关闭功能。这样看来计时器 1 仍然能作为波特率发生器的串口使用或任何不需要中断的应用。

OSC

T1 Pin

GATE

INT0 Pin

÷TPS

TR1

C/T = 0

C/T = 1

Control

TL1

(8 Bits)

TH1

(8 Bits)

Reload

TF1

Interrupt

28

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 29

AT89LP213/214 [Preliminary]

Figure 14-4. 模式 3 下的计时器计数器 0:两个 8 位计数器

÷TPS

T0 Pin

GATE

INT0 Pin

÷TPS

C/T = 0

C/T =1

Control

Control

(8 Bits)

(8 Bits)

Interrupt

Interrupt

Note: 在模式 3 下计时器 0 对 RH0/RL0 没有要求,可以用作临时存储寄存器。

.

Table 14-1. TCON – 计时器计数器控制寄存器

TCON = 88H 复位 值 = 0000 0000B

位选

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

位 76543210

标识符 功能

TF1 计时器 1 溢出标识,有硬件设置。当操作向量指向中断时对其清零。

TR1 计时器 1 运行控制位,通过软件置位或清零来实现计时计数器通断。

TF0 计时器 0 溢出标识,有硬件设置。当操作向量指向中断时对其清零。

TR0 计时器 0 运行控制位,通过软件置位或清零来实现计时计数器通断。

IE1 中断 1 标识。当检测到外部中断时通过硬件置位,中断运行完清零。

IT1 中断 1 类型控制位。通过软件置位清零来指定下降沿 / 低电平触发中断。

IE0 中断 0 标识。当检测到外部中断时通过硬件置位,中断运行完清零。

IT0 中断 0 类型控制位。通过软件置位清零来指定下降沿 / 低电平触发中断。

3538A–MICRO–6/06

29

Page 30

Table 14-2. TMOD: 计时计数器模式控制寄存器

TMOD = 88H 复位值 = 0000 0000B

无位选

GATE C/T M1 M0 GATE C/T M1 M0

76

计时器 1 计时器 0

Gate

C/T

M1 计时器 1 模式位 1 计时器 0 M1 位

M0 计时器 1 模式位 0 计时器 0 M0 位

门控制:当置位时,计时计数器只有在 INTx

引脚高电平和 TRx 控制引脚置位时才有效:当

清零时,计时器 x 在 TRx 控制位置位时都有效。

计时器或计数器选择:若清零则为计时器操作

(内部系统时钟输入); 若置位则为计数器操作

(Tx 引脚作为输入)

M1 M0 模式 操作模式

000

011

102

113

113(计时器 1)计时计数器 1 停止

543210

计时器 0 门位

计时器 0 计数记时选择位

9 到 16 位可变计时计数器

带有 1 到 8 位变长 THx 和 TLx 的 8 位计时计数器

16 位自动重置记时计数器

16 位计时计数器,THx 与 TLx 连带,无变长器。

8 位自动重置计时计数器

8 位自动重置计时计数器,THx 有重置值每次溢出时重置给 TLx。

分时计时计数器模式

(计时器 0)TL0 时由标准计时器 0 控制位控制的 8 位计时计数器。

TH0 时标准计时器 1 控制位控制的 8 位计时计数器。

30

计时器 SFR 作用 地址 位选

TCON 控制 88H 是

TMOD 模式 89H 否

TL0 计时器 0 低字节 8AH 否

TL1 计时器 1 低字节 8BH 否

TH0 计时器 0 高字节 8CH 否

TH1 计时器 1 高字节 8DH 否

TCONB 模式 91H 否

RL0 计时器 0 重置低字节 92H 否

RL1 计时器 1 重置低字节 93H 否

RH0 计时器 0 重置高字节 94H 否

RH1 计时器 1 重置高字节 95H 否

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 31

AT89LP213/214 [Preliminary]

0)

.

Table 14-3.

TCONB = 91H 复位值 = 0010 0100B

无位选

位 76543210

符号 功能

PWM1EN 在 T1 (P3.5)上将计时器 1 设置成脉冲宽度调制输出。

PWM0EN 在 T0 (P3.4)上将计时器 0 设置成脉冲宽度调制输出。

TCONB – 计时器计数器控制寄存器 B

PWM1EN PWM0EN PSC12 PSC11 PSC10 PSC02 PSC01 PSC00

PSC12

PSC11

PSC10

PSC02

PSC01

PSC00

模式 0 下计时器 1 的可变长器。TL1 可变位数为 PSC1+1.

在 AT89S2051 中复位后 PSC1=100B 使得 TL1 的 5 个位能够用于 13 位模式 0 的情况下。

模式 0 下计时器 0 的可变长器。TL0 可变位数为 PSC0+1.

在 AT89S2052 中复位后 PSC0=100B 使得 TL0 的 5 个位能够用于 13 位模式 0 的情况下。

14.5 脉宽调制

AT89LP213 中,可以通过置位 TCONB 中 PWM0EN 或 PWM1EN 分别将计时器0和1配置成8位异步脉冲

宽度调制器 (PWM)。在 PWM 模式下计时器引脚 T0 或 T1 输出产生的波形。在这种模式下 C/T 也必

须置 0。T0(P3.4) 和 T1(P3.5) 必须设置为输出模式。计时器溢出标识和中断将在 PWM 模式下继续

工作,计时器 1 仍可为 UART 口产生波特率。PWM 可以通过选择 TMOD 中的模式位来选择四种模式中

的任意一种。

图14-5给出了在PWM模式下计时器0输出的一种波形 。TH0 作为 8 位计数器使用而 RH0 存储 8

位比较值。当 TH0 为 00H 时,PWM 输出为高。当 TH0 中计数值累加到了 RH0 中的值时,PWM 输出置

低。 因此脉宽与 TH0 中的值一致。 为了防止毛刺产生 , 仅在 RH0 从 FFH 到 OOH 溢出时才写 RH0。将

RH0 置 00H 将会保持 PWM 输出为低。

Figure 14-5. 异步脉宽调制

Counter Value (TH0)

Compare Value (RH

14.5.1 模式 0 – 带有8位分频器的8位PWM

模式 0 下,TLx 作为算术分频器驱动 8 位计数器 THx.( 如图 14 - 6)TCONB 中的 PSCx 位控制分频器

的值。THx 溢出时,RHx 中的周期值转换给 OCRx,同时输出引脚置高。当 THx 中的计数与 OCRx 匹

配时,输出清零。接下来便是给输出频率和 PWM 模式 0 下计时器 0 的周期。PWM 模式下计时器 1 与

计时器 0 一致。

3538A–MICRO–6/06

PWM Output (T0)

31

Page 32

Mode 0:

INT1 Pin

f

Oscillator Frequency

------------------------------------------------------ -

out

256 2

1

PSC

01+

×

------------------ -×=

TPS

1+

Mode 0: Duty Cycle % 100

Figure 14-6. 计时器计数器 1PWM 模式 0

OSC

TR1

GATE

14.5.2 模式 1– 带有 8 位线性分频器的8位PWM

模式 1 下,TLx 利用 RLx 的 8 位自动重置实现线性分频 ( 如图 14 - 7)。TLx 溢出时将 RLx 中的值

置入 TLx 中。当 THx 溢出时,RHx 中的周期值转换给 OCRx,同时输出引脚置高。当 THx 中的计数

与 OCRx 匹配时,输出清零。接下来便是给输出频率和 PWM 模式 0 下计时器 0 的周期。PWM 模式下

计时器 1 与计时器 0 一致。

÷TPS

Control

PSC1

TL1

(8 Bits)

RH0

----------- -×=

256

RH1

(8 Bits)

OCR1

=

T1

TH1

(8 Bits)

32

Mode 1:

f

out

Mode 1: Duty Cycle % 100

AT89LP213/214 [Preliminary]

Oscillator Frequency

------------------------------------------------------ -

256 256

RL

0–()×

RH0

----------- -×=

256

------------------ -×=

TPS

1

1+

3538A–MICRO–6/06

Page 33

Figure 14-7. 计时器计数器 1PWM 模式 1

INT1 Pin

INT1 Pin

AT89LP213/214 [Preliminary]

RH1

(8 Bits)

14.5.3 模式 2 –8 位频率发生器

PWM模式2下,计时器0与8位自动重置计时器功能类似。与通常情况下模式2相同,但是在每次

TL0 溢出时输出引脚 T0 接换。(如图 14 - 8)PWM 模式 2 下的计时器 1 与计时器 0 一致。模式 2

下 PWM 可以输出频率可变的方波。THx 可作 8 位计数器。接下来便是给 PWM 模式 2 下计时器 0 的输

出频率。

GATE

OSC

TR1

Mode 2:

÷TPS

Control

f

out

RL1

(8 Bits)

TL1

(8 Bits)

Oscillator Frequency

------------------------------------------------------ -

2256

TH

0–()×

OCR1

TH1

(8 Bits)

------------------ -×=

TPS

=

T1

1

1+

Figure 14-8. PWM 模式 2 下的计时器计数器 1

Note: {RH0 和 RL0}/{RH1 和 RL1} 在 PWM 模式 2 下计时器 0/1 不做要求 ,可被用作临时存储寄存器。

14.5.4 模式 3 – 8 位分时 PWM

PWM 模式 3 下计时器 1 保持其值,与设置 TR = 1 时的效果相同。PWM 模式 3 下计时器 0 将 TL0 和

TH0 作为两个独立的 PWM 计数器使用,其方式与通常情况下的模式 3 类似。PWM 模式 3 下的计时器

0 工作情况如图 14 - 9 所示。只有在 PWM 模式 3 下计时器可变器工作时才可以改变输出频率。TL0

GATE

OSC

TR1

÷TPS

Control

TH1

(8 Bits)

TL1

(8 Bits)

T1

33

3538A–MICRO–6/06

Page 34

可以使用计时器 0 的控制位:GATE,TR0, INT0, PWM0EN 和 TF0。TH0 被锁存到,某个计时器功

I

TR1

能中并且使用 TR1,PWM1EN 和 TF1。RL0 为 TL0 提供周期频率,RH0 则为 TH0 提供周期频率。

PWM 模式 3 应用时需要一个 PWM 通道和两个计时器,或者两个 PWM 通道和一个额外的计时器或计数

器。对于 PWM 模式 3 下的计时器 0, AT89LP213 拥有三个计时器 / 计数器。当计时器 0 工作在 PWM

模式 3 下,计时器 1 可以通过通断控制来进入或退出模式 3。 在这种情况下,计时器 1 仍可以作为

串口的波特率产生器而无需任何中断。接下来便是给输出频率和 PWM 模式 3 下计时器 0 的周期。

Mode 3:

f

Oscillator Frequency

------------------------------------------------------ -

out

256

Mode 3, T0: Duty Cycle % 100

Mode 3, T1: Duty Cycle % 100

RL

--------- -×=

256

RH

--------- -×=

256

------------------ -×=

TPS

0

0

1

1+

Figure 14-9. PWM 模式 3 下的计时器计数器 0

RL0

(8 Bits)

OCR0

=

T0

TL0

(8 Bits)

RH0

(8 Bits)

OCR1

GATE

NT1 Pin

OSC

TR1

÷TPS

Control

=

T1

OSC

÷TPS

TH0

(8 Bits)

15. 外部中断

当 AT89LP213/214 被设置为使用内部 RC 振荡器时, XTAL1 and XTAL2 可能被用作 INT0 和

INT1

外部中断资源。 外部中断能够通过设置或清零寄存器 TCON 中 IT1 或 IT0位达到水平活性或阶

跃活性编程。如果 ITx = 0,外部中断 x 将会被 INTx

部中断将是边缘触发。 在这个模式中,如果 INTx

个周期为低电平,那么 TCON 中的中断请求标记 IEx 将被置位。标记位 IEx 开始请求中断。每当外

部中断引脚取样一个时钟周期,一个输入高或低电平将被持续至少两个振荡器周期,目的是为了

使取样顺利。 如果外部中断处于阶跃活性,那么外部资源将保持请求引脚高电平至少两个时钟周

引脚察觉到低电平时触发。如果 ITx = 1, 外

引脚中的连续样本表现为一个周期高电平而下一

34

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 35

AT89LP213/214 [Preliminary]

期,然后再将它置为低电平,时间也是至少两个时钟周期;这样,中断请求标记 IEx 才能被置位。

在边缘触发模式中,如果服务周期被需求,那么 IEx 将被 CPU 自动清除。如果外部中断处于水平

活性,那么外部资源将保持需求使能直到需求中断发生。然后,外部资源必须在中断服务程序完

全或另一个中断发生之前使请求无效。

16. 多用途中断

多用途中断 (GPI) 功能在端口 1 提供了 8 个可配置的外部中断。每个端口引脚都能探测到高 / 低

电平或正 / 负边缘。 GPIEN 寄存器挑选端口 1 中的位用于产生中断。 GPMOD 和 GPLS 寄存器确

定每个独立引脚的模式。 GPMOD 在水平灵敏和边缘触发模式之间进行选择。 GPLS 在水平模式

下的高 / 低和边缘模式下的正 / 负之间进行选择。端口 1 的引脚每个时钟周期都在采样。在水平

灵敏模式下,一个正确的水平面必须在产生中断前出现在两个连续的采样之间。在边缘触发模式

下,当两个采样之间评估值产生变化时,将会探测到一个阶跃。当一个中断条件在一个引脚被发

现,此时这个引脚使能,GPIF 寄存器中适当的标记被置位。GPIF 中的标记必须由软件清零。

.

Table 16-1. GPMOD – 多用途中断模式寄存器

GPMOD = 9AH 复位值 = 0000 0000B

没有可以设置地址的位

GPMOD7 GPMOD6 GPMOD5 GPMOD4 GPMOD3 GPMOD2 GPMOD1 GPMOD0

Bit76543210

GPMOD.x 0 = level-sensitive interrupt for P1.x

1 = edge-triggered interrupt for P1.x

Table 16-2. GPLS – 多用途中断水平选择寄存器

GPLS = 9BH 复位值 = 0000 0000B

没有可以设置地址的位

GPLS7 GPLS6 GPLS5 GPLS4 GPLS3 GPLS2 GPLS1 GPLS0

Bit76543210

GPMOD.x 0 = detect low level or negative edge on P1.x

1 = detect high level or positive edge on P1.x

3538A–MICRO–6/06

35

Page 36

.

Table 16-3.

GPIEN = 9CH 复位值 = 0000 0000B

没有可以设置地址的位

Bit76543210

.

GPIEN – 多用途中断使能寄存器

GPIEN7 GPIEN6 GPIEN5 GPIEN4 GPIEN3 GPIEN2 GPIEN1 GPIEN0

GPIEN.x 0 = interrupt for P1.x disabled

1 = interrupt for P1.x enabled

Table 16-4. GPIF – 多用途中断标记寄存器

GPIF = 9DH 复位值 = 0000 0000B

没有可以设置地址的位

GPIF7 GPIF6 GPIF5 GPIF4 GPIF3 GPIF2 GPIF1 GPIF0

Bit76543210

GPIF.x 0 = interrupt on P1.x inactive

1 = interrupt on P1.x active. 必须由软件清除 .

17. 连续分界面

36

AT89LP213/214 [Preliminary]

AT89LP214 上的连续分界面实现了通用异步接收器 / 发送器功能 (UART)。UART 具有以下特点:

• 全双工操作

• 8或9个数据位

• 错误侦查

• 自动地址识别下的多处理器传输模式

• 使用定时器 1 的波特率发生器

• 接收缓冲器或传输完全上的中断

3538A–MICRO–6/06

Page 37

AT89LP213/214 [Preliminary]

连续分界面是全双工的,这意味着它能够同时发送和接收信号。它同时也是一个接收缓冲器,这

意味着它能在前一个字节被接收寄存器读取之前接收第二个字节信息。(尽管如此,如果第二个字

节接收完成而第一个字节还没有被读取时,这两个字节中的一个将会丢失。 ) 连续端口接收和发

送寄存器都能访问特殊功能寄存器 SBUF。发送寄存器负责向 SBUF 中写入数据;而接收寄存器负责

从 SBUF 中读取数据。 连续端口能在以下四个模式中进行操作:

• 模式 0: 通过 RXD 实现连续数据的进入和退出。 TXD 输出变换时钟。8 个数据位是发送 / 接收。

波特率固定为振荡器频率的 1/2。

• 模式 1: 10 个位是发送(通过 TXD)或接收 (通过 RXD):1 个开始位 (0),8 个数据位,1 个停

止位 (1)。接收时,停止位变为特殊功能寄存器 SCON 中的 RB8。波特率基于定时器 1 可变。

• 模式 2: 11 个位是发送(通过 TXD)或接收(通过 RXD):1 个开始位 (0),8 个数据位,1 个可编

程的第 9 数据位,1 个停止位 (1)。发送时,第 9 数据位 (SCON 中的 TB8)可以被赋值 “0”

或 “1”。例如,奇偶位 (P,在 PSW 中)能够被移动至 TB8。接收时,当停止位被忽视时,

第 9 数据位将去特殊功能寄存器 SCON 中的 TB8。 波特率可编程设置为振荡器周期的 1/16 或

1/32

• 模式 3: 11 个位是发送 (通过 TXD)或接收(通过 RXD):1 个开始位 (0),8 个数据位,, a1个

可编程的第 9 数据位,1 个停止位 (1)。事实上,模式 3 与模式 2 除了波特率以外其余都一模

一样。模式 3 的波特率基于定时器 1 可变。

在所有的 4 种模式中,发送器能被将 SBUF 定义为目的寄存器的任何指令启动。 模式 0 中,当 RI =

0 且 REN = 1 时,开始接收。在其他模式中,当引入的启动位 REN=1 时,开始接收。

17.1 多处理器通信

模式 2 和模式 3 有一个多处理器通信模式。在这个模式中,9 个数据位用于接收,1 个停止位紧随

其后。第 9 个位去 RB8。然后产生一个停止位。端口仅在停止位接收时可以被编辑;只有当 RB8=1

时,连续端口中断才具备活性。通过设置 SCON 中的 SM2 位,能实现这一特点。

接下来的例子将会说明如何在多处理器通信中使用连续中断。当主处理器必须将一块数据传输给

其他处理器时,它首先发送一个地址位,用于鉴别目标处理器。这个地址位不同于数据位,因为

在地址位中第 9 位是 “1”,而在数据位中第 9 位是 “0”。当 SM2=1 时,没有处理器能够被数据

位阻止。然而,地址位可以中断所有的处理器。每个处理器都能检验接收字节并且鉴别它是否属

于地址位。地址处理器清除了它的 SM2 位,并且准备接收接下来的数据字节。处理器不能设置它

的 SM2 位,并且忽略数据字节。

SM2位在模式0中没有任何作用,但它可以用来检查模式1 中停止位的合法性。在模式1接收中,如

果 SM2=1, 那么除非收到一个有效的停止位,不然接收中断都具有活性。

Table 17-1. SCON – 连续端口控制寄存器

SCON 地址 = 98H 复位值 = 0000 0000B

可以设置地址的位

SM0/FE SM1 SM2 REN TB8 RB8 T1 RI

Bit7 6543210

(SMOD0 = 0/1)

(1)

3538A–MICRO–6/06

37

Page 38

符号 功能

FE

SM0 连续端口模式位 0, (SMOD0 must = 0 to access bit SM0)

SM1

SM2

REN 连续接收使能。由软件置位,由软件清零。

TB8 在模式 2 和模式 3 中传输第 9 数据位。由软件置位或清零。

RB8 在模式 2 和模式 3 中接收第 9 数据位。在模式 1 中,如果 SM2=0,RB8 将作为停止位被接收。在模式 0 中,RB8 不被使用。

TI

RI

Notes: 1. SMOD0 is 定位于 PCON.6.

取景错误位。当发现一个无效停止位时,接收器将它置位。FE 位不能被有效取景清零而只能被软件清零。 SMOD0 位必

须被设置为使能 FE 位。FE 的设置与 SMOD0 的规定无关。

连续端口模式位 1

osc

(2)

/2

/16

osc

SM0 SM1 Mode Description Baud Rate

0 0 0 shift register f

0 1 1 8-bit UART variable (Timer 1)

1 0 2 9-bit UART f

1 1 3 9-bit UART variable (Timer 1)

在模式 2 或 3 中,自动地址识别功能使能。当 SM2=1 时,除非接收到的第 9 位数据为 1,否则 RI 不能被置位。在模式 1

中,如果 SM2=1,除非接收到一个有效停止位,否则 RI 不能被激活,接收字节是一个赠与或广播地址。在模式 0 中,SM2

是0。

传输中断标志。无论处于哪种连续传输模式下,在模式 0 中,由 8 位时间硬件设置,在其他模式中,由地址位的开始状态

设置。必须由软件清零。

接收中断标志。在任何连续接收状态下 (除了 SM2),在模式 0 中,由 8 位时间的末尾设置;或者在其他模式下由停止位

时间的部分设置。必须由软件清零。

= 振荡器周期

2. f

osc

osc

/32 or f

17.2 波特率

模式 0 中,波特率是固定的,如下式所示:

模式 2 中,波特率由特殊功能寄存器中的 SMOD1 位的值决定。如果 SMOD1=0,那么波特率为振荡器

周期的 1/32。如果 SMOD1=1,那么波特率为振荡器周期的 1/16。 如下式所示:

17.2.1 利用定时器 1 产生波特率

在模式 1 和 3 中,定时器 1 的溢出率决定波特率。当定时器 1 是波特率发生器时,波特率由定时

器 1 的溢出率和 SMOD1 的值决定。如下式所示:

38

AT89LP213/214 [Preliminary]

Mode 0 Baud Rate

Mode 2 Baud Rate

Modes 1, 3

Baud Rate

SMOD1

2

-------------------- (Timer 1 Overflow Rate)×=

32

Oscillator Frequency

------------------------------------------------------ -=

SMOD1

2

-------------------- (Oscillator Frequency)×=

32

2

3538A–MICRO–6/06

Page 39

AT89LP213/214 [Preliminary]

在这个请求中,定时器 1 中断将被使无效。在 3 个连续模式下,定时器本身能被设置为任何定时

器或计数器运行。在最典型的应用程序中,它被设置为自动再装模式下的定时器运行。既然这样,

波特率由下式给出:

Modes 1, 3

Baud Rate

程序员可以通过设定定时器以 16 位自动再装定时器而获得非常低的波特率。既然这样,波特率由

下式给出:

Modes 1, 3

Baud Rate

Table 17-2 给出通常使用的波特率以及它们是如何从定时器 1 中获得的。

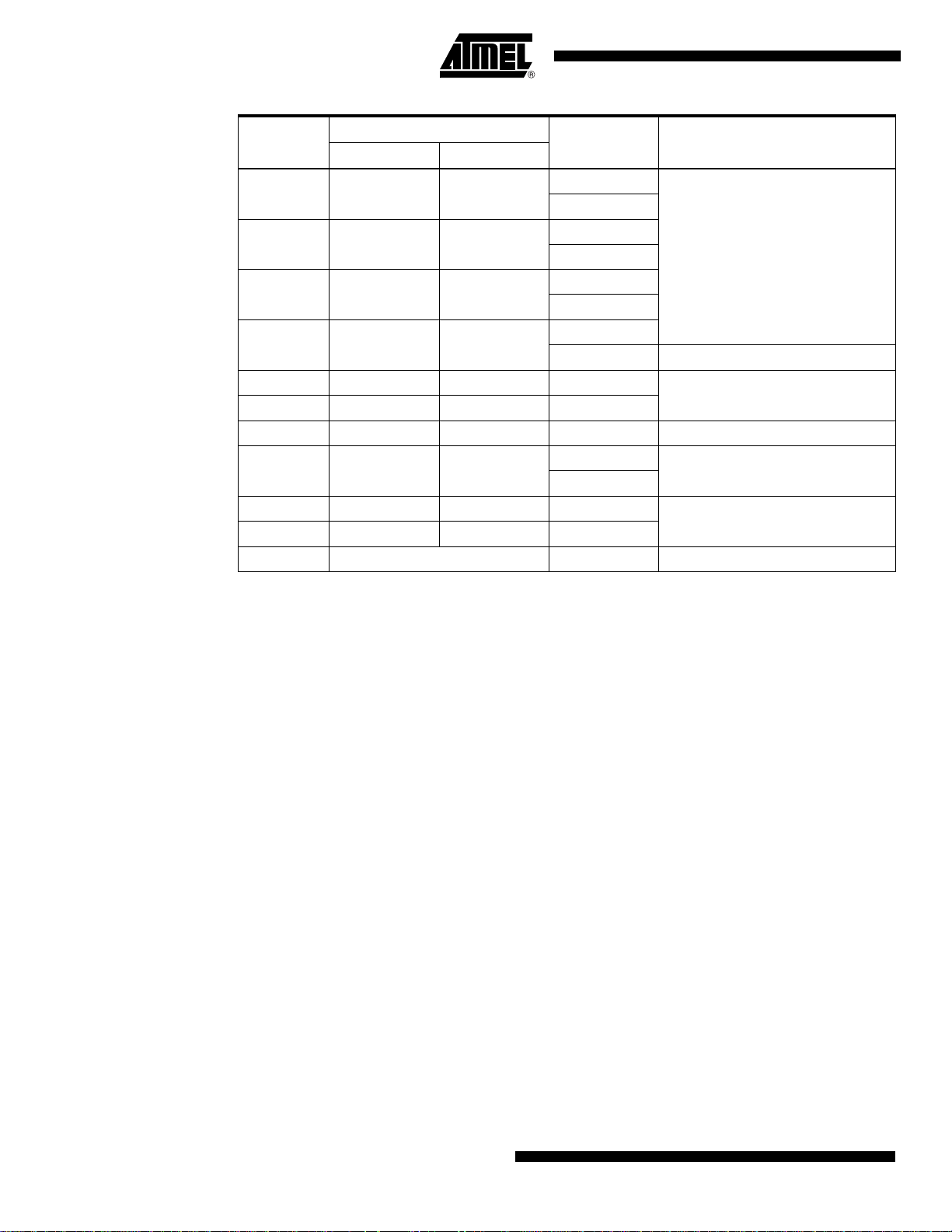

Table 17-2. 定时器 1 中常使用的波特率 (TPS = 0000B)

Baud Rate f

Mode 0: 1 MHz 2 X X X X

Mode 2: 375K 12 0 X X X

62.5K 12 1 0 2 F4H

19.2K 11.059 1 0 2 DCH

9.6K 11.059 0 0 2 DCH

4.8K 11.059 0 0 2 B8H

2.4K 11.059 0 0 2 70H

1.2K 11.059 0 0 1 FEE0H

137.5 11.986 0 0 1 F55CH

110 6 0 0 1 F958H

110 12 0 0 1 F304H

(MHz) SMOD1

OSC

SMOD1

2

--------------------

32

SMOD1

2

--------------------

32

Oscillator Frequency

------------------------------------------------------ -

256 TH1()–[]

Oscillator Frequency

------------------------------------------------------ -×

256

R

H1,RL1()–[]

C/T Mode Reload Value

1

------------------ -××=

TPS

1

------------------ -×=

TPS

Timer 1

1+

1+

17.3 关于模式 0 的更多内容

通过 RXD 实现连续数据进入和退出。TXD 输出变换时钟。8 个数据位用于发送。波特率固定为振荡

器周期的 1/2。 Figure 17-1 on page 40 显示了在模式 0 及关联定时状态下连续端口的单一化功能

图表。

发送器能被将 SBUF 定义为目的寄存器的任何指令启动。“向 SBUF 写入”信号等同于将 “1”置于

传输变换寄存器的第 9 位,并使 TX 控制模块开始传输。内部定时在“向 SBUF 写入”和 SEND 激活

中将机器周期流逝。

SEND 将交换寄存器的输出传送到P3.0的轮换功能输出线上,它也将变换时钟传送到P3.1 的轮换

功能输出线上。在变换时钟下降沿,传输轮换寄存器的内容将变换到右边的位置上。

当数据位向右变换时,“0”向左边移动。当数据字节中的 MSB 在变换寄存器的输出位置时,将第

9 个位置的最初部分置 1。这个控制标志 TX 控制时钟进行最后轮换,然后解除 SEND 并将 TI 置 1。

当 REN = 1 且 R1 = 0 时,开始接收。在下一个时钟周期,RX 控制单元将 11111110 写入接收轮

换寄存器并且在下一个时钟相位激活 RECEIVE i

RECEIVE 将轮换时钟设置到P3.1的轮换输出功能线上。在轮换时钟的下降沿,接收变换寄存器中

的内容向左移动。从右侧移位过来的数值来自于 P3.0 引脚在变换时钟上升沿的取样。

3538A–MICRO–6/06

39

Page 40

当数据位向右移动时,“1”向左移动。当将 “0”写入变换寄存器最右边的最初位置时,它标志

T

R

T

R

S

S

T

S

R

R

RX 控制时钟去进行一个最后的轮换。然后将 RECEIVE 清零并将 RI 置 1。

Figure 17-1. 连续端口模式 0

1/2 f

osc

INTERNAL BUS

“1“

INTERNAL BUS

WRITE TO SBUF

END

HIFT

XD (DATA OUT)

XD (SHIFT CLOCK)

I

40

WRITE TO SCON (CLEAR RI)

I

ECEIVE

HIFT

XD (DATA IN)

XD (SHIFT CLOCK)

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 41

17.4 关于模式 1 的更多内容

10 位传输 (通过 TXD)或接收 (通过 RXD):1 个开始位 (0),8 个数据位,1 个停止位。接收

时,停止位进入 SCON 中的 RB8。在 AT89LP214 中,波特率由定时器 1 的溢出率决定。 Figure 17-2

显示在传输和接收过程中,模式 1 和关联定时的连续端口的单一化功能图表。

发送器能被将 SBUF 定义为目的寄存器的任何指令启动。“向 SBUF 写入”信号等同于将 “1”置于

传输变换寄存器的第 9 位,并使 TX 控制模块开始传输。传输实际上从机器周期的 S1P1 开始。因

此,因此,位时间是同步的,而不是 “向 SBUF 写入”信号。

AT89LP213/214 [Preliminary]

当 SEND

之后,第一个轮转脉搏出现 1 位时间。

当数据位向右移动,“0”向左移动。当数据位的 MSB 在轮换寄存器的输出位置时,“1”写入第 9

位置的开头,所有位置向左移。这个控制标志 TX 控制单元去进行最后的轮换,然后解除 SEND

将TI置1。

当RXD探测到一个1至0的转变时,开始接收。为了达到这个目的,RXD以确定波特率的16被速

率取样。当探测到传输时,16 分频计数器立刻重启,输入轮换寄存器中写入 1FFH。16 分频计数器

通过引入的位时间重新设置。

16 分频计数器被分为 16 个位时间。在每个位时间的第 7、8、9 计数器状态下,位探测器取样 RXD

的值。接收的样本最少需要 3 个样本中的两个。这样可以拒绝噪声。为了拒绝错误位,如果接收

的第 1 位时间不为 0,那么接收电路重启,单元继续寻找 1 至 0 传输。如果开始位有效,它转变为

输入轮换寄存器。

当数据位向右移动时,“1”向左移动。当开始位到达轮换寄存器最左边的位置时,它标记 RX 控制

块去做最后的轮换,加载 SBUF 和 RB8,并将 RI 置 1。当且仅当满足下列条件时,产生加载 SBUF

和RB8并且将RI置1的信号。

如果这两个条件中的任何一个不满足,接收结构将不可挽回的丢失。如果两个条件同时满足,停

止位进入 RB8,8 个数据位写入 SBUF,并且 RI 被激活。此时,不论上述条件是否满足,单元都将

继续在RXD中寻找1至0的传输。

具有活性时,开始传输。1 位时间过后,DATA 被激活,它将传输轮换寄存器使能。在此

并

RI = 0 且

SM2 = 0, 或接收停止位 = 1

3538A–MICRO–6/06

41

Page 42

Figure 17-2. 连续端口模式 1

S

TI

TIMER 1

OVERFLOW

WRITE

RXD

TO

SBUF

SAMPLE

TRANSITION

DETECTOR

÷16

SERIAL

PORT

INTERRUPT

1-TO-0

÷2

= 0

SMOD1

= 1

MOD1

“1”

S

Q

D

CL

START

RX CLOCK

÷16

RX CLOCK

START

BIT

DETECTOR

INTERNAL BUS

SBUF

ZERO DETECTOR

SHIFT

TX CONTROL

TI

RI

RX CONTROL

INPUT SHIFT REG.

LOAD

SBUF

DATA

SEND

LOAD

SBUF

SHIFT

1FFH

(9 BITS)

TXD

SHIFT

TX

CLOCK

WRITE TO SBUF

SEND

DATA

SHIFT

TXD

TI

START BIT

RX

CLOCK

RXD

BIT DETECTOR SAMPLE TIMES

SHIFT

RECEIVE

RI

SBUF

READ

SBUF

INTERNAL BUS

D0 D1 D2 D3 D4 D5 D6 D7

÷16 RESET

START BIT

D0 D1 D2 D3 D4 D5 D6 D7

TRANSMIT

STOP BIT

STOP BIT

42

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 43

17.5 模式 2,3 介绍

AT89LP213/214 [Preliminary]

通过 TXD 进行 11 位数据的发送,通过 RXD 进行 11 位数据的接收。11 位数据包括:1 个起始位

(0),8 个数据位元 (LSB 在前),一个可编程的第 9 位数据位元,以及 1 个停止位 (1)。发送

时,第 9 位数据位元 (TB8 )可以被设置为 “0”或 “1”。接收时,第 9 位数据位元进入 SCON

的 RB8。模式 2 中,波特率可以编程设置为振荡频率的 1/16 或 1/32。模式 3 中,波特率可变,由

定时器 1 决定。

图 17-3 和 17-4 显示了模式 2,3 的串行端口功能图。接收部分与模式 1 完全相同,发送部分与模

式 1 的差别只在于发送移位寄存器的第 9 个数据位元。

通过使用 SBUF 作为目标寄存器的任何指令开始发送。信号 “写入 SBUF”同样将 TB8 载入发送移

位寄存的第 9 位,标志 TX 控制单元有一个发送的请求。发送实际开始于紧接着 16 分计数器的下

一次翻转机器周期的 S1P1。因此,位的时间是与 16 分计数器同步,而不是与 “写入 SBUF”信号

同步。

当 SEND 被激活时,开始发送,向 TXD 放入开始位。一个数据位的时间后,数据 DATA 激活,使发

送移位寄存器的输出的位到 TXD。之后产生第一个移位脉冲。第一次移位记录 “1”(停止位)进

入移位计时器第 9 位的时间。然后唯一的 “0”被计时。因此随着数据位向右移出,从左边进入的

“0”被计时。当 TB8 位于移位寄存器的输出位置时,停止位刚好在 TB8 的左边,在停止位的左边

都为 “0”。这种情况标志 TX 控制单元将做最后一次移位,然后解除 SEND 的激活并将 TI 置位。

这些发生在 “写入 SBUF”后 16 分计数器第 11 次翻转时。

RXD 检测到由 “1”到 “0”的跃迁后,开始接收过程。为了达到这个目的,RXD 以指定波特率的

16 倍的速率进行采样。检测到跃迁后,16 分计数器马上复位,“1FFH”写入输入移位寄存器中。

在每个位元时间的第 7,8,9 个计数器状态,位元检测器对 RXD 的值进行采样。公认的值至少存

在于 2/3 的采样值中。如果第一个位元时间接受的值不是 0,接收电路重启,并且该单元继续寻找

另一个 “1”到 “0”的跃迁。如果起始位有效,就将它移至输入移位寄存器,继续接受该帧剩余

部分。

随着数据位由右侧进入,“1”从左边移出。当起始位到达移位寄存器 (即模式 2,3 中的 9 位寄

存器)最左边位置时,标志着 RX 控制区将做最后一次移位,载入 SBUF 和 SB8,并重启 RI。只有

在最后一个移位脉冲产生时,在下列条件都满足的情况下,才会产生载入 SBUF 和 RB8,将 RI 置位

的信号:

1 . RI = 0

2 . SM2 = 0, 或接收到的第 9 个数据位元 = 1

如果上述两个条件之一不满足,接收到的帧会不可挽回的丢弃,并且 RI 不被置位。如果两者都满

足了,接收到的第 9 个数据位元进入 RB8,而前 8 个数据位元进入 SBUF。一个位元时间后,不管

上述条件是否满足,该单元继续寻找 RXD 输入中 “1”到 “0”的跃迁。

注意:接收到的停止位的值与 SBUF,RB8 或 RI 均无关。

3538A–MICRO–6/06

43

Page 44

Figure 17-3. 连续端口模式 2

CPU CLOCK

SMOD1

1

SMOD1 0

INTERNAL BUS

44

INTERNAL BUS

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 45

Figure 17-4. Serial Port Mode 3

TIMER 1

OVERFLOW

WRITE

TO

SBUF

SMOD1

= 0

÷2

SMOD1

= 1

TB8

D

CL

S

Q

ZERO DETECTOR

INTERNAL BUS

SBUF

AT89LP213/214 [Preliminary]

TXD

TX

CLOCK

WRITE TO SBUF

SEND

DATA

SHIFT

TXD

TI

START BIT

STOP BIT GEN

RX

CLOCK

STOP BIT

START

÷16

SERIAL

PORT

INTERRUPT

SAMPLE

1-TO-0

TRANSITION

DETECTOR

RXD

D0 D1 D2 D3 D4 D5 D6 D7 TB8

÷16 RESET

RX CLOCK

÷16

START

DETECTOR

TX CONTROL

RX CLOCK

RX CONTROL

BIT

READ

SBUF

TI

RI

LOAD

SBUF

SHIFT

DATA

SEND

LOAD

SBUF

SHIFT

1FFH

INPUT SHIFT REG.

(9 BITS)

SBUF

INTERNAL BUS

SHIFT

STOP BIT

TRANSMIT

BIT DETECTOR SAMPLETIMES

SHIFT

RECEIVE

RI

3538A–MICRO–6/06

RXD

START BIT

D0 D1 D2 D3 D4 D5 D6 D7 RB8

STOP

BIT

45

Page 46

17.6 帧错误检测

17.7 自动地址识别

除了它所有的通用模式外,UART 可以作为通过寻找丢失的停止位进行帧错误检测,并自动的地址

识别。当用于帧错误检测时,UART 在通信中寻找丢失的停止位。一个丢失的停止位会将 SCON 寄存

器的 FE 置位。FE 由 PCON.6 (SMOD0) 决定是作为 SCON.6 还是 SM0。如果 SMOD0 置位,那么 SCON.7

就作为 FE,此时 SCON.7 仅能由软件清零。当 SMOD0 清零,那么 SCON.7 作为 SM0。

自动地址识别具有一种特性,即利用硬件作出的比较使 UART 可以从大量连续字位中识别某些特定

地址。这种特性减少了依赖大量软件来检测通过连续端口的每一个连续地址。把 SM2 字位设置在

SCON 就可激活这种特性。在这种第 9 字位 UART 模式中,当接收到包含 “已知”地址或 “广播”

地址的字节时,模式 2 模式 3 和接受中断信号识标将自动激活。这种第 9 字位模式为了表明所接

受到的信息是地址而非数据,则要求第 9 个信息字位必须为 “1”。

第 8 字位模式也叫模式 1。在这种模式中,如果 SM2 被激活并且接受的信息在第 8 字位后有终端中

止的字位,不管是已知地址还是广播地址,接受中断信号识标将会设置为激活。

模式 0 是个备份寄存器模式,同时 SM2 就无任何作用。

利用自动地址识别的特性调用已知分端口的地址或地址群,就可以使主端口有选择性地连接一个

或多个分端口。所有的分端口都可以用 “广播”地址来连接起来。两种特殊功能的寄存器被用来

定义分端口地址 SADDR,和地址掩模 SADEN.SADEN 是来定义在 SADDR 中哪些字位将被用到,哪些则

无任何意义。逻辑上,SADEN 掩模和 SADDR 与门给出已知地址,主端口用已知地址来分配每个分端

口的地址。用已知地址可以识别多个分端口并且不和其他的混淆。下面的例子来说明这种配置具

有多功能性:

分端口 0 SADDR = 1100 0000

SADEN = 1111 1101

Given = 1100 00X0

分端口 1 SADDR = 1100 0000

SADEN = 1111 1110

Given = 1100 000X

在上面的例子中,SADDR 是同样的,SADEN 的数据用来区分两个分端口。分端口 0 需要一个 “0”

在 0 字位而不用考虑 1 字位,分端口 1 需要一个“0”在 1 字位而不用考虑 0 字位。对分端口 0 来

说只有唯一的地址 1100 0010,因为分端口 1 在 1 字位是 “0”。对分端口 1 来说也只有唯一的地

址 1100 0001,因为 “1”在 0 字位就不和分端口 0 重复了。用同一个地址即 0 字位 =0 (分端口

0)1 字位 =0 (分端口 1),两个分端口就可以被同时选择了。因此,两个分端口的地址都可以表

示成 1100 0000。

在一台更加复杂的系统中,用下面的方法就可以选择分端口1和2,而同时不包含分端0:

分端口 0 SADDR = 1100 0000

46

SADEN = 1111 1001

Given = 1100 0XX0

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 47

AT89LP213/214 [Preliminary]

分端口 1 SADDR = 1110 0000

SADEN = 1111 1010

Given = 1110 0X0X

分端口 2 SADDR = 1110 0000

SADEN = 1111 1100

Given = 1110 00XX

在上面例子中,三个端口之间的区别在于低端 3 位地址位的不同。端口 0 需要 0 字位 =0,就有唯

一的地址 1110 0110。端口 1 需要 1 字位 =0,就有唯一的地址 1110 0101。端口 2 需要 2 字位 =0,

就有唯一的地址 1110 0011。要选择端口0和1,就得用地址1110 0100,因为必须使 2 字位 =1 来

排除端口 2。

每一个分端口的广播地址是取 SADDR 和 SADEN 的逻辑 OR 获得的。在这个结果中所有的 0 被忽略。

大多数情况下,如果视忽略值为 1,广播地址则为 16 进制的 FF。

重设 SADDR (SFR 地址 0A9H)和 SADEN (SFR 地址 0B9H)后,所有地址位归置为 “0”。这就产

生了包含所有无意义字位的已知地址和包含所有无意义字位的广播地址。并有效地禁止自动寻址

模式,使微控制器使用不执行这个特性的标准 80C51 型 UART 驱动器。

18. 串行外设接口

串行外设接口可使高速同步数据在 AT89LP216 和外设元件或者多个 AT89LP216 元件之间传输。串

行外设接口特性如下:

* 双向,3 线同步数据传输

* 主、从操作方式

* 最大字位频率 =fosc/4

* LSB 或 MSB 优先数据传输

* 4 级可编程地址位的从模式

* 传输结束中断标识

* 存写冲突标识保护

* 双缓冲接受

* 双缓冲传输 (高级模式才有)

* 闲置模式唤醒

主、从 CPU 用 SPI 连接的方式如图 18-1 所示。接口的四个引脚分别是主进从出 (MISO),主

出从进 (MOSI),移位时钟 (SCK)和从属选择 ( )。SCK 引脚在主模式中是时钟输出,而在从

模式中是时钟输入。在 SPCR 中 MSTR 位决定了 MISO 和 MOSI 的方向。要注意到 MOSI 连接 MOSI,

MISO 连接 MISO。在主模式中, /P1.4 被忽略而只有可能作为一般的输入输出。在从模式中, 必须

置于低电平来选择单个元件作为从属。当 置于高电平时,从属的 SPI 端口无效并且 MOSI/P1.5 能

用于一般输出。

3538A–MICRO–6/06

47

Page 48

Figure 18-1. 主从连接

MSB LSB

SPI

Clock Generator

Master

8-Bit Shift Register 8-Bit Shift Register

MISO

MISO

MOSI MOSI

SCK

SS SS

SCK

V

CC

MSB LSB

Slave

SPI 有两种操作模式:标准模式 (无缓冲存写)和高级模式 (缓冲存写)。对主 CPU 的 SPI 数据

寄存器的存写触发 SPI 时钟寄存器,然后存写数据从 MOSI 引脚输出再输入到从 CPU 的 MOSI 的引

脚。当时钟寄存器等待下一个指定波长的满位槽时,传输经过一段初始延时就可触发。转移一个

字节后,SPI 时钟寄存器停止,同时设置传输中断位并把接受的字节传输到可读缓冲器中。如果要

同时设置 SPI 中断激活位和串口中断激活位,就需要中断(传输)。需要指出的是无论 SPDR 用可

写数据寄存器或可读数据寄存器,都取决于访问路径是可读还是可写。在标准模式下,由于可写

缓冲器是透明的 (并且对 SPDR 的存写路径会访问移位缓存器),所以在进行传输时任何向 SPDR

的存写都将导致和 WCOL 设置的存写冲突。但传输仍将正常完成,不过新字节是无效的所以必须再

重新写到 SPDR。

除可写缓冲器能控制传输下一字节外,高级模式类似于标准模式。SPDR的存写会占用可写缓冲器,

并告诉 WCOL 缓冲器已经满荷,以后任何的存写都将覆盖掉缓冲器。当缓冲字节加载到移位寄存器

开始传输时,硬件将会清除 WCOL。如果主 SPI 处于闲置状态,比如当前是第一个字节,在加载

SPDR 后,字节传输就会开始并且 WCOL 会被立即清除。在当前字节传输时,下一个字节也有可能被

写入到 SPDR。SPDR 中的加载激活标识 (LDEN)用来决定传输开始的时间。LDEN 取决于 SPI 传输

的前四位字位。每加载下一字节前,主 CPU 应当首先检测 LDEN 的设置和 WCOL 是否被清除。在高

级模式下,如果在传输完成后 WCOL 是设置的,比如若可以进行下一字节传输,SPI 会即时把缓存

字节加载到移位寄存器,重设 WCOL,进行不中断传输同时重新开始时钟发生器。只要 CPU 能保持

最大利用可写缓存,大量的字节就可以在最短时间间隔内传输出去。

Table 18-1. SPCR – SPI 控制寄存器

SPCR Address = E9H 复位值 = 0000 0000B

不可位寻址

SPIE SPE DORD MSTR CPOL CPHA SPR1 SPR0

Bit76543210

符号 功能

SPIE SPI 终端使能。它与寄存器 IE 中的 ES 位同时置位使能 SPI 中断。 SPIE = 0 时禁用 SPI 中断

SPE

SPI 使能。 SPI = 1 时,启用串行通道,分别连接 SS

SPI = 0 时禁用串行通道。

, MOSI, MISO 和 SCK 至管脚 P1.4, P1.5, P1.6, 和 P1.7。

DORD 数据顺序位。 DORD = 1 选择数据的 LSB。 DORD = 0 选择数据的 MSB。

MSTR 主 / 从选择位。当 MSTR = 1 时为主 SPI 模式。 MSTR = 0 时为从 SPI 模式。

48

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 49

符号 功能

时钟极性。当 CPOL = 1 时, SCK 在空闲时为高。

CPOL

当 CPOL = 0 并且不传输数据时,主设备的 SCK 为低。同时请参考 SPI 时钟状态和极性控制。

AT89LP213/214 [Preliminary]

CPHA

时钟相位。 CPHA 和 CPOL 位一起控制主从设备之间的数据和时钟的关系。 同时请参考 SPI 时钟状态和极性控制。

SPI 时钟频率选择。在主模式下,这两个位控制主设备的 SCK 频率,在从模式下这两位无效。SCK 频率和振荡器频率的关

系如下 :

SPR1

SPR0

SPR1

SPR0 SCK

00f

01f

10f

11f

OSC

OSC

OSC

OSC

/4

/8

/32

/64

Notes: 1. 设定时钟模式再启用 SPI: 先设置 SPCR 中除了 SPE 位的其他位,再设置 SPE 位。

2. 先使能主设备再使能从设备。

3. 如果没有装载新的数据的话,从设备会在下一个 Tx 时刻反馈给主设备信号。

Table 18-2. SPSR – SPI 状态寄存器

SPDR Address = EAH

不可位寻址

SPD7 SPD6 SPD5 SPD4 SPD3 SPD2 SPD1 SPD0

复位值 = 00H (after cold reset)

unchanged (after warm reset)

Bit76543210

Table 18-3. SPSR – SPI Status Register

SPSR Address = E8H 复位值 = 000X X000B

不可位寻址

SPIF WCOL

Bit76543210

LDEN – – SSIG DISSO ENH

3538A–MICRO–6/06

49

Page 50

符号 功能

SPI 中断标志。当串行传输完成时 SPIF 会被置位,如果此时 SPIE = 1 且 ES = 1,那么就会产生中断。通过读取 SPI 状态寄

SPIF

WCOL

LDEN

存器然后再读 / 写 SPI 数据寄存器可以将 SPIF 清零。

当 ENH = 0 时:WCOL 是写入冲突标志。如果在传输数据时向 SPI 数据寄存器中写入数据,将置位 WCOL。此时若读取

寄存器 SPDR 将得到错误的数值,且向 SPDR 写入数据也是无效的。通过读取 SPI 状态寄存器然后再读 / 写 SPI 数据寄

存器可以将 WCOL bit ( 和 SPIF 位 ) 清零。

当 ENH = 1 时: WCOL 在增强模式下作为 Tx 缓冲满标志。在增强模式下,当 WCOL = 1 时写入数据,将会覆盖已在 Tx

缓冲区内等待发送的数据。此时, WCOL 不再由 SPIF 的复位来清零,而是写入缓冲区的数据被装入移位寄存器时被清

零。

增强 SPI 模式下 Tx 缓冲区装载使能。

在 ENH 被置位的情况下,并且 LDEN = 1, WCOL = 0,此时向 Tx 缓冲区装载数据是安全的。在串行字节传输的前 0 - 3

位时 LDEN 为高, 4 - 7 位时 LDEN 为低。

SSIG

DISSO

ENH

从属选择忽略。如果 SSIG = 0, 如果 SS

,并且无论 SPE (SPCR.6) 是否置位,它都有效。 当 SSIG = 1 时, P1.4 可以用于通用 I/O 引脚。

SS

禁止从输出位

置位时,使得 MISO 管脚处于三态 , 能让多个从设备共用一个接口。通常传输的第一个字节是从设备的地址,只有被选

定的从设备才把它的 DISSO 位置零。

增强 SPI 模式选择位。当 ENH = 0 时, SPI 工作在普通模式下,没有写入数据缓冲

当 ENH = 1 时, SPI 工作在增强模式下,有写入数据缓冲。 Tx 缓冲区和寄存器 SPDR 公用一个地址。

(P1.4) 被拉低, SPI 将只工作于从属模式。当 SSIG = 1, SPI 忽略从属模式下的

50

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 51

Figure 18-2. SPI 移位寄存器图表

AT89LP213/214 [Preliminary]

7

Serial In

Transmit

Byte

8

2:1

MUX

8 8

Figure 18-3. SPI 结构图

Oscillator

Divider

÷4÷8÷32÷64

Serial Master Serial Slave

DQ

LATCH

CLK

8

Parallel Master

(Write Buffer)

DQ

LATCH

CLK

2:1

MUX

DQ

LATCH

CLK

Parallel Slave

(Read Buffer)

DQ

LATCH

CLK

S

M

M

MSB

8-bit Shift Register

LSB

S

Read Data Buffer

Write Data Buffer

Serial Out

Receive

Byte

8

MISO

P1.6

MOSI

P1.5

Select

SPR1

SPR0

SPI Control

WCOL

SPIF

SPI Status Register

SPI Clock (Mater)

SPI Interrupt

Request

MSTR

SPE

8

Internal

Data Bus

Clock

Clock

Logic

8

SPIE

SPE

DORD

MSTR

CPOL

CPHA

SPR1

SPR0

Pin Control Logic

S

M

MSTR

SPE

DORD

SCK

1.7

SS

P1.4

SPI Control Register

8

3538A–MICRO–6/06

51

Page 52

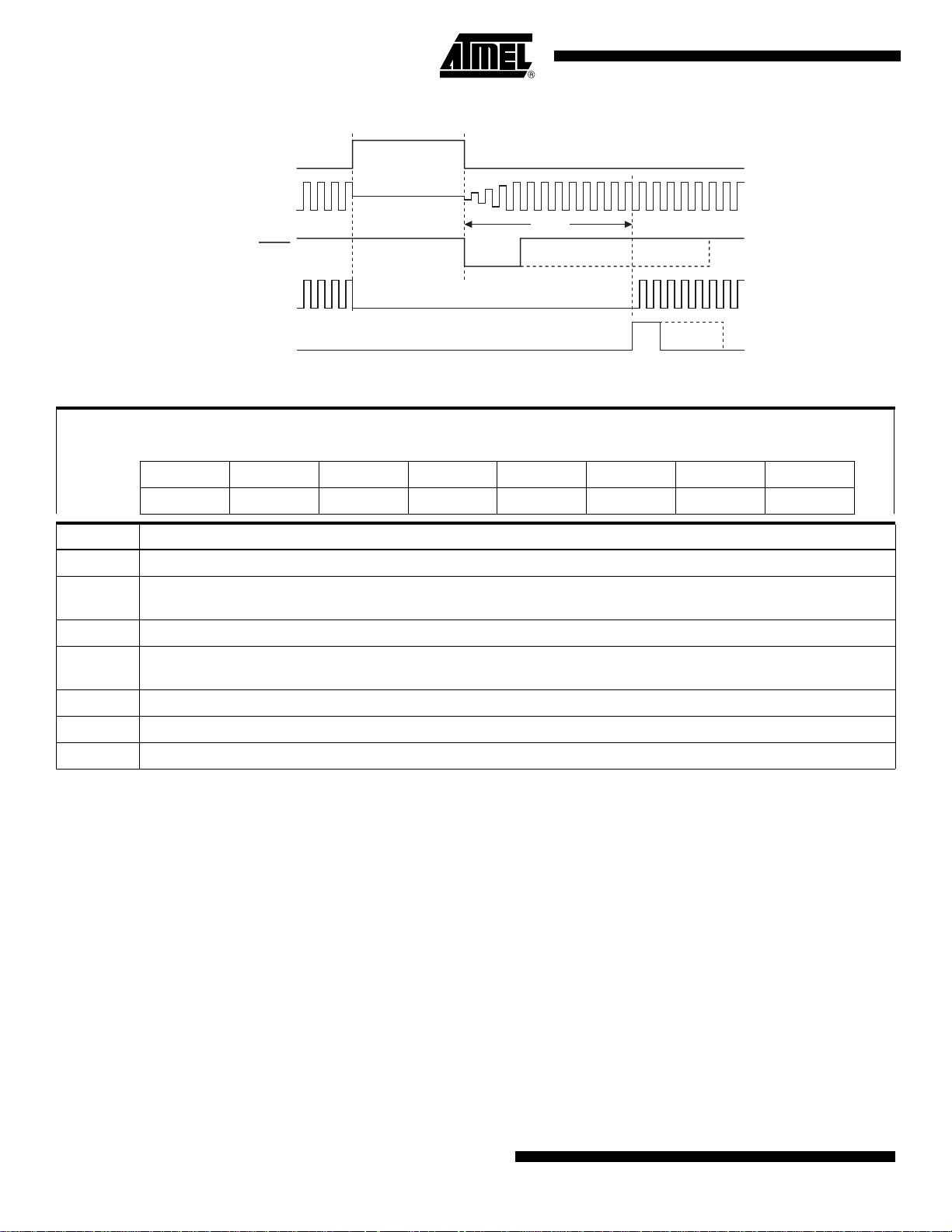

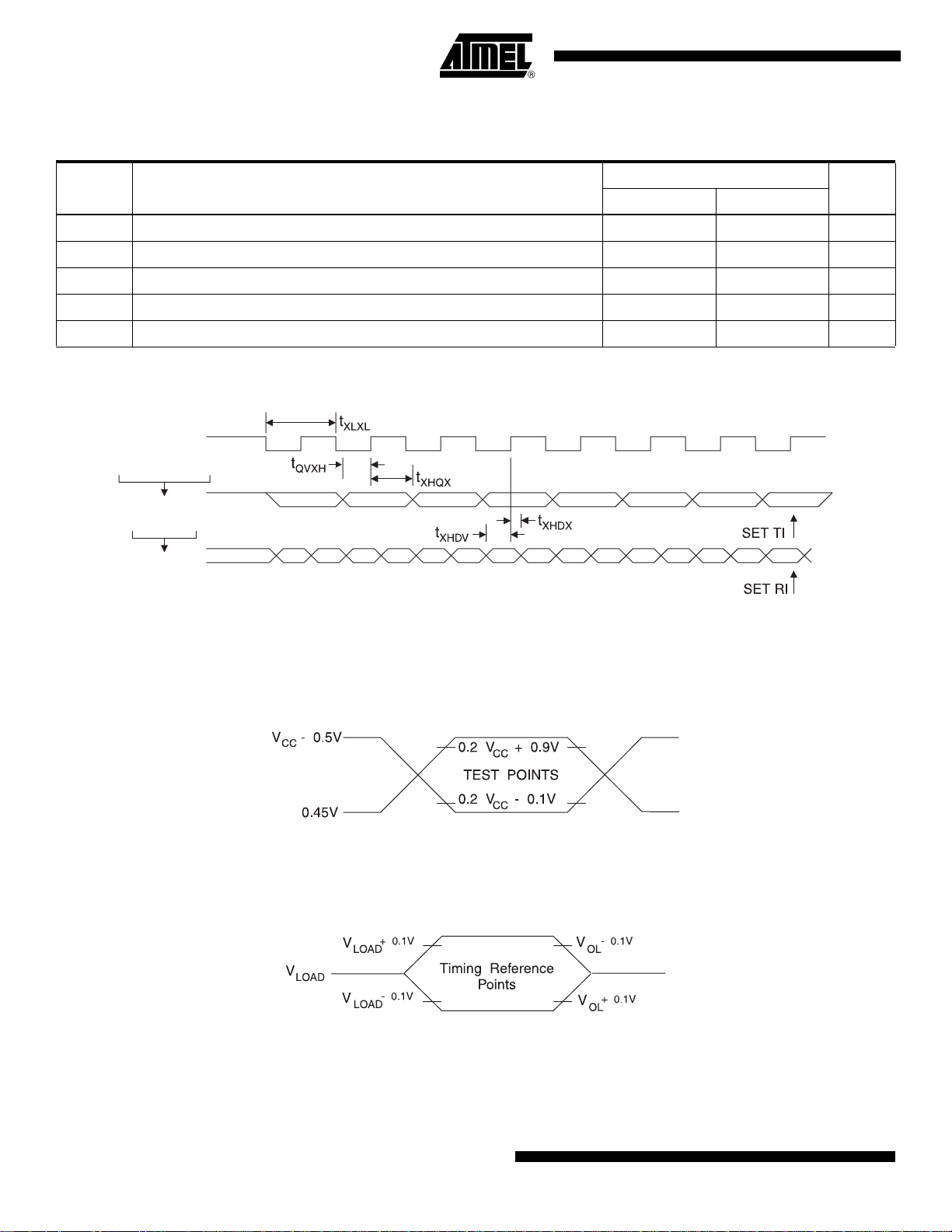

CPHA (Clock PHAse时钟相位), CPOL (Clock POLarity时钟极性),以 及 SPCR中的 SPR (Serial

P

eripheral clock Rate = baud rate串行外围时钟率=波特率)位控制SCK的形状及速度。当SPI 在

主模式下时,两个 SPR 位提供四个可能的时钟频率。在从模式下,只要 输入的 SCK 频率不超过

最大的位频率,SPI 将以它的频率工作。 至于串行数据,这里也有四种可能的 SCK 相位以及极性

组合。 CPHA 以及 CPOL 决定哪一个版本用于传输。 SPI 数据传输的版本见 Figures 18-4 and

18-5。为了避免 SCK 的短时脉冲干扰破坏接口,CPHA, CPOL,以及 SPR 在接口被使能时不应

被修正,并且主器件应该在从器件之前被使能 。

Figure 18-4. CPHA = 0 时 SPI 的转换波形图

Note: * 非定义但是正常的 MSB 特性被接受。

Figure 18-5. CPHA = 1 时 SPI 的转换波形

SCK CYCLE #

(FOR REFERENCE)

SCK (CPOL = 0)

SCK (CPOL = 1)

MOSI

(FROM MASTER)

MISO

(FROM SLAVE)

SS (TO SLAVE)

Note: * 非定义但是先前传输的正常的 LSB 特性。

1 2 3 4 5 6 7 8

MSB 6 5 4 3 2

MSB

*

65432

1 LSB

1 LSB

19. 模拟比较器

52

AT89LP213/214 [Preliminary]

AT89LP213/214 上提供一个单独的模拟比较器。模拟比较器有以下特性 :

3538A–MICRO–6/06

Page 53

• 比较器输出标志及中断

T

• 可选中断条件

• 硬件跳转模式

比较器操作是这样的,当正输入 AIN0 (P1.0]) 比负输入 AIN1 (P1.1) 大时输出逻辑 1。否则输出 0。

置位 ACSR 中的 CEN 位使能比较器。当比较器第一次被使能,比较器输出并且中断标志在 10 µs

中不一定稳定。相应的比较器在这一时间段不应该被使能, 而比较器中断标志必须在中断被使能

前清零以避免一个直接的中断服务。在使能比较器之前模拟输入应通过将 P1.0 以及 P1.1 置入仅

输入模式来置为三态。见 “ 端口 1 模拟功能 ” on page 24.

在多种输出值情况下,比较器可通过设置 ACSR 中的 CM 位来设定产生中断。无论何时只要比较

器输出与 CM 说明的情况匹配, ACSR 中的比较器中断标志 CF 被置位。标志位可能被软件选取

或被用于产生一个中断并且必须被软件清零。

19.1 含消抖的比较器中断

每个时钟周期比较器输出都被取样。模拟输入上的状态可能是这样的,比较器输出可能过度跳转。

当申请慢速移动模拟输入时这一情况尤其真实。有三种消抖模式被提供用于虑除这一噪声。在消

抖模式下,比较器使用 Timer 1 来调节它的采样时间。当相应的跳转发生时,比较器会等待直至

两个 Timer 1 溢出值在对输出重新取样前出现。如果新的采样适合预期的值,CF 被置位。否则,

事件被忽略。滤波器可以通过调整 Timer 1 的 time-out 周期来调谐。这是因为 Timer 1 是自由运

转的,消抖器必须等待两个溢出来保证采样延迟至少有一个 time-out 周期。因此,在最初的边缘

事件之后,中断可能在 1 到 2 个 time-out 周期之后发生见 Figure 19-1 on page 53。

AT89LP213/214 [Preliminary]

– 高或低等级

– 上升或下降边缘

– 输出跳转

在默认状态下空闲模式中比较器是被失效的。为了在空闲模式下允许比较器运行, ACSR 中的

CIDL 位必须被置位。当 CIDL 被置位,如果比较器中断被使能,比较器可以用于将 CPU 从空闲模

式中唤醒。在下电模式下比较器始终被失效。

Figure 19-1. 消抖下的负边沿

Comparator Out

imer 1 Overflow

CF

Start Compare

Start Compare

53

3538A–MICRO–6/06

Page 54

Table 19-1. ACSR – 模拟比较器控制 & 状态寄存器

ACSR = 97H 复位值 = XXX0 0000B

非位可寻址

––

Bit76543210

符号 功能

CIDL 比较器空闲使能。如果 CIDL = 1 比较器将在空闲模式下持续运作。如果 CIDL = 0 比较器在空闲模式下被下电。比较器

在下电模式下始终被关闭。

CF 比较器中断标志。当比较器输出遇到这样的情况,以 CM [2:0] 位说明并且 CEN 被置位,这一位置位。这一标志必须由

软件清零。中断可以通过置位 / 清零 IE 的 bit6 来使能 / 失效。

CEN 比较仪使能。置位这一位使能比较仪。清零这一位将迫使比较仪输出低电平并且防止置位 CF 引发进一步事件。当 CEN =

1 模拟输入输入引脚, P1.0 以及 P1.1,它们的数字输入失效。

CM [2:0] 比较仪中断模式

CIDL CF CEN CM3 CM1 CM0

CM2

000负 (低)电平

001正跳变

010套牢跳变

011负边缘跳变

100负沿

101套牢

110负边缘跳变

111正 (高)电平

Note: 1. Debouncing 模式要求使用定时器 1 来产生取样延迟。

CM1 CM0 中断模式

(1)

(1)

(1)

54

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 55

20. 可编程看门狗定时器

在定时器溢出前,如果软件未能定时供给,将触发一个系统复位,而可编程看门狗定时器 (WDT)

可以保护系统以免因此产生误操作。默认状态下 WDT 计 CPU 时钟周期。SFR WDTCON 中的预

置数分频位, PS0, PS1 以及 PS2 用来将看门狗定时器的周期设置为从 16K 到 2048K 时钟周期。

定时器预置数分频器同样可用于延长 time-out 周期 ( 见 Table 9-2 on page 13) 。在上电模式下

以及复位状态下 WDT 被失效。如果 WDT 计时结束而没有被服务,一个内部 RST 脉冲将被产生

来复位 CPU。可用 WDT 周期选择见 Table 20-1 。

Table 20-1. Watchdog Timer Time-out Period Selection

AT89LP213/214 [Preliminary]

WDT 预置数分频位

000 16K

001 32K

010 64K

011 128K

100 256K

101 512K

1 1 0 1024K

1 1 1 2048K

Note: 1. WDT 计时结束周期由系统时钟频率决定 .

Time-out Period

2

------------------------------------------------------ -

Oscillator Frequency

PS

14+()

TPS

1+()×=

(1)

周期

( 时钟周期 )PS2 PS1 PS0

看门狗定时器由 14 位定时器包含 7 位可编程预置数分频器组成。向 WDTRST 寄存器写队列

1EH/E1H可以使能定时器。 当 WDT被使能, WDTCON 中的 WDTEN 位将被置 1。为了避免 WDT

在溢出时产生复位,看门狗饲养队列必须在计时周期结束之前写入 WDTRST。为了喂养看门狗,

两条写指令必须被接连成功地执行。在两条写指令之间, SFR 读是被允许的,但是写不允许。指

令必须把 1EH 移动到 WDTRST 寄存器然后 1EH 到 WDTRST 寄存器。不正确的喂养或使能队列

将产生直接的看门狗复位。 喂养或使能看门狗定时器的程序队列如下:

20.1 软件复位

3538A–MICRO–6/06

MOV WDTRST, #01Eh

MOV WDTRST, #0E1h

通过对 WDTRST SFR 写软件复位队列 5AH/A5HA , AT89LP213/214 完成一个软件复位。 The

WDT不需要被使能以产生软件复位。 一个正常的软件复位会置位WDTCON中的SWRST标志。然

而,任何时候如果有错误的队列写到 WDTRST ( 例,除了 1EH/E1H 或 5AH/A5H),一个软件复

位将立即产生, SWRST 以及 WDTOVF 标志都会被置位。在这种方式下,一个故意的软件复位

和一个误操作产生的复位是有区别的。产生软件复位的程序队列如下:

55

Page 56

MOV WDTRST, #05Ah

MOV WDTRST, #0A5h

Table 20-2. WDTCON – 看门狗控制寄存器

WDTCON Address = A7H 复位值 = 0000 X000B

非位可寻址

PS2 PS1 PS0 WDIDLE

Bit76543210

符号 功能

PS2

PS1

PS0

WDIDLE 在空闲模式下失效 / 使能看门狗定时器。当 WDIDLE = 0 时, WDT 在空闲模式下持续计数。当 WDIDLE = 1 时, WDT

SWRST 软件复位标志。当通过对 WDTRST 写 5AH/A5H 队列产生一个软件复位时,它被置位。同样,当一个不正确的队列写到

WDTOVF 看门狗溢出标志。当 WDT 定时器溢出产生 WDT 复位时,它被置位。同样,当一个不正确的队列写到 WDTRST 中时,它必须

WDTEN 看门狗使能标志位。这一位是只读位,它反映了 WDT 的状态 (不管它是不是在运转)。任何复位之后 WDT 都被失效,并

看门狗定时器 (WDT) 的预置数分频器。当这所有三位都被清零时,看门狗定时器有一个 16K 时钟周期的常规周期。当这

所有三位都被置 1 时,这一常规周期为 2048K 时钟周期。

在空闲模式下冻结。

WDTRST 中时,它必须被软件清零。

被软件清零。

且必须通过写 1EH/E1H 到 WDTRST 来重新使能。

–

SWRST WDTOVF WDTEN

Table 20-3. WDTRST – 看门狗复位寄存器

WDTCON 地址 = A6H ( 只写 )

非位可寻址

––––––––

Bit76543210

WDT 通过写 1EH/E1H队列到 WDTRST SFR中被使能。通过读 WDTCON 中的 WDTEN 位可以核对目前的状态。为了阻止 WDT

复位器件,在 time-out 间隔期间同样的 1EH/E1H 队列必须被写到 WDTRST 中。通过写 5AH/A5H 队列到 WDTRST 中可以产

生一个软件复位。

56

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 57

21. 指令机摘要

AT89LP213/214 [Preliminary]

AT89LP213/214 是完全二进制的,与 MCS-51 指令集兼容。 AT89LP213/214 以及标准 8051 之间

的区别在于执行一条指令所需要的循环数。 AT89LP213/214 中的指令可能需要 1 个 , 2 个 , 3 个

或 4 个时钟周期来完成。 大多数指令的执行时间可以用 Table 21-1 来估算。 .

Table 21-1. 指令执行时间及例外

一般指令类型 循环数公式

大多数算法,逻辑,位及传输指令 # bytes

分支及调用 # bytes + 1

单字节间接 (i.e. ADD A, @Ri, etc.) 2

RET, RETI 4

MOVC 3

MOVX 4

MUL 2

DIV 4

INC DPTR 2

Clock Cycles

算法 Bytes

Hex Code8051 AT89LP

ADD A, Rn 1 12 1 28-2F

ADD A, direct 2 12 2 25

ADD A, @Ri 1 12 2 26-27

ADD A, #data 2 12 2 24

ADDC A, Rn 1 12 1 38-3F

ADDC A, direct 2 12 2 35

ADDC A, @Ri 1 12 2 36-37

ADDC A, #data 2 12 2 34

SUBB A, Rn 1 12 1 98-9F

SUBB A, direct 2 12 2 95

SUBB A, @Ri 1 12 2 96-97

SUBB A, #data 2 12 2 94

INC Rn 1 12 1 08-0F

INC direct 2 12 2 05

INC @Ri 1 12 2 06-07

INC A 2 12 2 04

DEC Rn 1 12 1 18-1F

DEC direct 2 12 2 15

DEC @Ri 1 12 2 16-17

DEC A 2 12 2 14

3538A–MICRO–6/06

57

Page 58

Table 21-1. 指令执行时间及例外 (Continued)

Clock Cycles

算法 Bytes

INC DPTR 1 24 2 A3

MUL AB 1 48 2 A4

DIV AB 1 48 4 84

DA A 1 12 1 D4

Clock Cycles

逻辑 Bytes

CLR A 1 12 1 E4

CPL A 1 12 1 F4

ANL A, Rn 1 12 1 58-5F

ANL A, direct 2 12 2 55

ANL A, @Ri 1 12 2 56-57

ANL A, #data 2 12 2 54

ANL direct, A 2 12 2 52

ANL direct, #data 3 24 3 53

ORL A, Rn 1 12 1 48-4F

Hex Code8051 AT89LP

Hex Code8051 AT89LP

ORL A, direct 2 12 2 45

ORL A, @Ri 1 12 2 46-47

ORL A, #data 2 12 2 44

ORL direct, A 2 12 2 42

ORL direct, #data 3 24 3 43

XRL A, Rn 1 12 1 68-6F

XRL A, direct 2 12 2 65

XRL A, @Ri 1 12 2 66-67

XRL A, #data 2 12 2 64

XRL direct, A 2 12 2 62

XRL direct, #data 3 24 3 63

RL A 1 12 1 23

RLC A 1 12 1 33

RR A 1 12 1 03

RRC A 1 12 1 13

SWAP A 1 12 1 C4

58

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 59

AT89LP213/214 [Preliminary]

Table 21-1. 指令执行时间及例外 (Continued)

数据传输

Bytes

MOV A, Rn 1 12 1 E8-EF

MOV A, direct 2 12 2 E5

MOV A, @Ri 1 12 2 E6-E7

MOV A, #data 2 12 2 74

MOV Rn, A 1 12 1 F8-FF

MOV Rn, direct 2 24 2 A8-AF

MOV Rn, #data 2 12 2 78-7F

MOV direct, A 2 12 2 F5

MOV direct, Rn 2 24 2 88-8F

MOV direct, direct 3 24 3 85

MOV direct, @Ri 2 24 2 86-87

MOV direct, #data 3 24 3 75

MOV @Ri, A 1 12 1 F6-F7

MOV @Ri, direct 2 24 2 A6-A7

MOV @Ri, #data 2 12 2 76-77

MOV DPTR, #data16 3 24 3 90

MOVC A, @A+DPTR 1 24 3 93

MOVC A, @A+PC 1 24 3 83

Clock Cycles

Hex Code8051 AT89LP

MOVX A, @Ri 1 24 4 E2-E3

MOVX A, @DPTR 1 24 4 E0

MOVX @Ri, A 1 24 4 F2-F3

MOVX @DPTR, A 1 24 4 F0

PUSH direct 2 24 2 C0

POP direct 2 24 2 D0

XCH A, Rn 1 12 1 C8-CF

XCH A, direct 2 12 2 C5

XCH A, @Ri 1 12 2 C6-C7

XCHD A, @Ri 1 12 2 D6-D7

CLR C 1 12 1 C3

CLR bit 2 12 2 C2

SETB C 1 12 1 D3

SETB bit 2 12 2 D2

CPL C 1 12 1 B3

CPL bit 2 12 2 B2

ANL C, bit 2 24 2 82

3538A–MICRO–6/06

59

Page 60

Table 21-1. 指令执行时间及例外 (Continued)

Clock Cycles

位操作 Bytes

ANL C, bit 2 24 2 B0

ORL C, bit 2 24 2 72

ORL C, /bit 2 24 2 A0

MOV C, bit 2 12 2 A2

MOV bit, C 2 24 2 92

分支

Bytes

JC rel 2 24 3 40

JNC rel 2 24 3 50

JB bit, rel 3 24 4 20

JNB bit, rel 3 24 4 30

JBC bit, rel 3 24 4 10

JZ rel 2 24 3 60

JNZ rel 2 24 3 70

SJMP rel 2 24 3 80

Clock Cycles

Hex Code8051 AT89LP

Hex Code8051 AT89LP

ACALL addr11 2 24 3

LCALL addr16 3 24 4 12

RET 1 24 4 22

RETI 1 24 4 32

AJMP addr11 2 24 3

LJMP addr16 3 24 4 02

JMP @A+DPTR 1 24 2 73

JMP @A+PC

CJNE A, direct, rel 3 24 4 B5

CJNE A, #data, rel 3 24 4 B4

CJNE Rn, #data, rel 3 24 4 B8-BF

CJNE @Ri, #data, rel 3 24 4 B6-B7

DJNZ Rn, rel 2 24 3 D8-DF

DJNZ direct, rel 3 24 4 D5

NOP 1 12 1 00

BREAK

Note: 1. 漏掉的指令是这一套指令系统的扩展部分。

(1)

(1)

2– 3A573

2– 2A500

11,31,51,71,9

1,B1,D1,F1

01,21,41,61,8

1,A1,C1,E1

60

AT89LP213/214 [Preliminary]

3538A–MICRO–6/06

Page 61

22. 片上调试系统

A

22.1 物理接口