查询AT80C51SND1C-7HTIL供应商

1. Features

• MPEG I/II-Layer 3 Hardwired Decoder

– Stand-alone MP3 Decoder

– 48, 44.1, 32, 24, 22.05, 16 kHz Sampling Frequency

– Separated Digital Volume Control on Left and Right Channels (Software Control

using 31 Steps)

– Bass, Medium, and Treble Control (31 Steps)

– Bass Boost Sound Effect

– Ancillary Data Extraction

– CRC Error and MPEG Frame Synchronization Indicators

• Programmable Audio Output for Interfacing with Common Audio DAC

– PCM Format Compatible

–I2S Format Compatible

• 8-bit MCU C51 Core Based (F

• 2304 Bytes of Internal RAM

• 64K Bytes of Code Memory

– AT89C51SND1C: Flash (100K Erase/Write Cycles)

– AT83SND1C: ROM

• 4K Bytes of Boot Flash Memory (AT89C51SND1C)

– ISP: Download from USB (standard) or UART (option)

• External Code Memory

– AT80C51SND1C: ROMless

• USB Rev 1.1 Controller

– Full Speed Data Transmission

• Built-in PLL

– MP3 Audio Clocks

–USB Clock

• MultiMedia Card

• Atmel DataFlash

• IDE/ATAPI Interface

• 2 Channels 10-bit ADC, 8 kHz (8-true bit)

– Battery V ol tage Monitoring

– Voice Recording Controlled by Software

• Up to 44 Bits of General-purpose I/Os

– 4-bit Interrupt Keyboard Port for a 4 x n Matrix

–SmartMedia® Software Interface

• 2 Standard 16-bit Timers/Counters

• Hardware Watchdog Timer

• Standard Full Duplex UART with Baud Rate Generator

• Two Wire Master and Slave Modes Controller

• SPI Master and Slave Modes Controller

• Power Management

– Power-on Reset

– Software Programmable MCU Clock

– Idle Mode, Power-down Mode

• Operating Conditions:

–3V, ±10%, 25 mA Typical Operating at 25°C

– Temperature Range: -40°C to +85 °C

• Packages

– TQFP80, BGA81, PLCC84 (Development Board)

–Dice

®

Interface Compatibility

®

SPI Interface Compatibility

= 20 MHz)

MAX

Single-Chip

Flash

Microcontroller

with MP3

Decoder and

Human Interface

AT83SND1C

AT89C51SND1C

AT80C51SND1C

Rev. 4109H–8051–01/05

AT8xC51SND1C

2. Description The AT8xC51SND1C a re fully in tegrated sta nd-alone har dwired MPEG I/II-Layer 3

decoder with a C51 microcontroller core handling data flow and MP3-player control.

The AT89C51SND1C includes 64K Bytes of Flash memory and allows In-System Pro-

gramming through an embedded 4K Bytes of Boot Flash memory.

The AT83SND1C includes 64K Bytes of ROM memory.

The AT80C51SND1C does not include any code memory.

The AT8xC51SND1C include 2304 Bytes of RAM memory.

The AT8xC51SND1C provides the necessary features for human interface like timers,

keyboard port, serial or parallel interface (USB, TWI, SPI, IDE), ADC input, I

and all external memory interface (NAND or NOR Flash, SmartMedia, MultiMedia,

DataFlash cards).

3. Typical

Applications

•MP3-Player

• PDA, Camera, Mobile Phone MP3

• Car Audio/Multimedia MP3

• Home Audio/Multimedia MP3

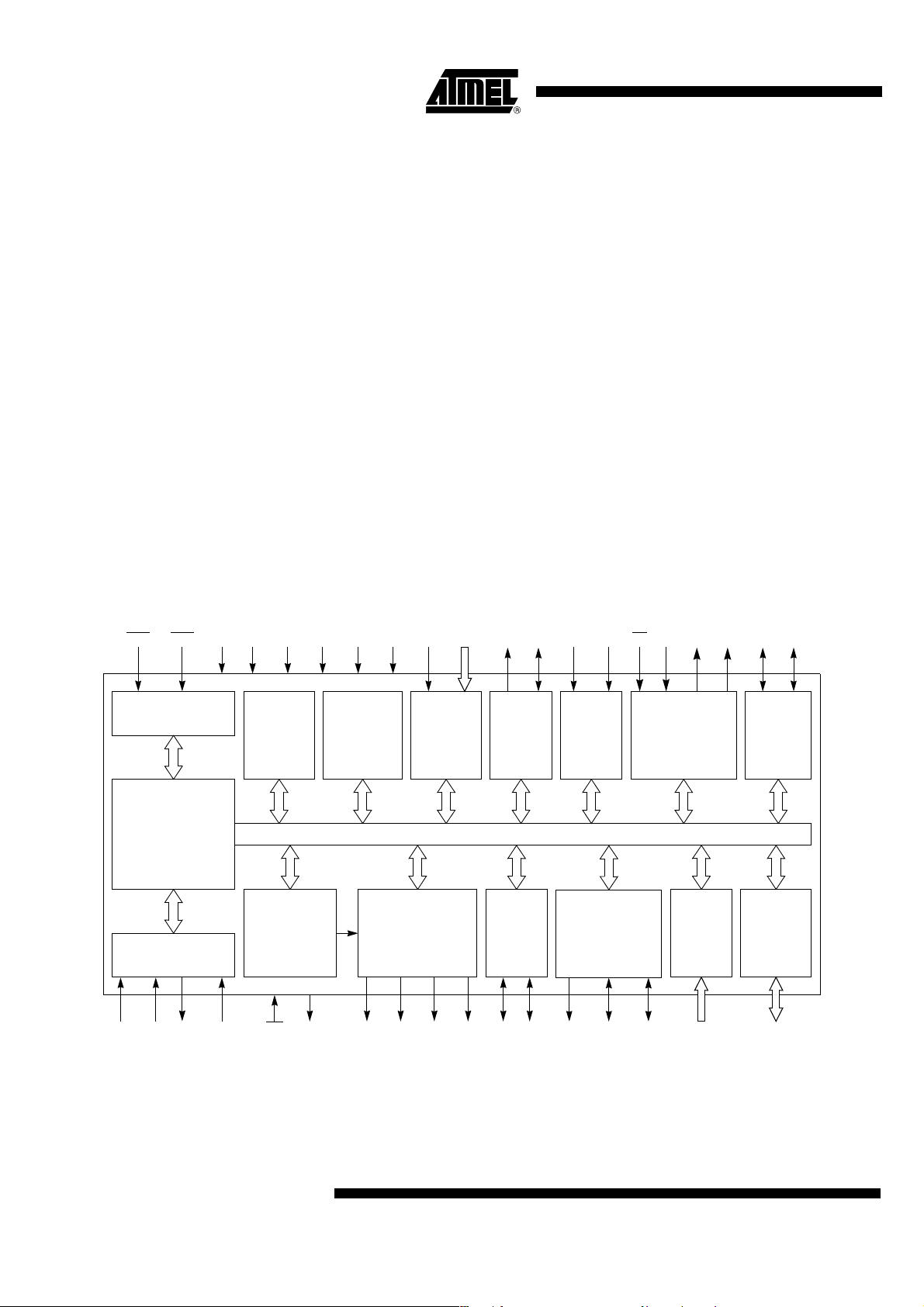

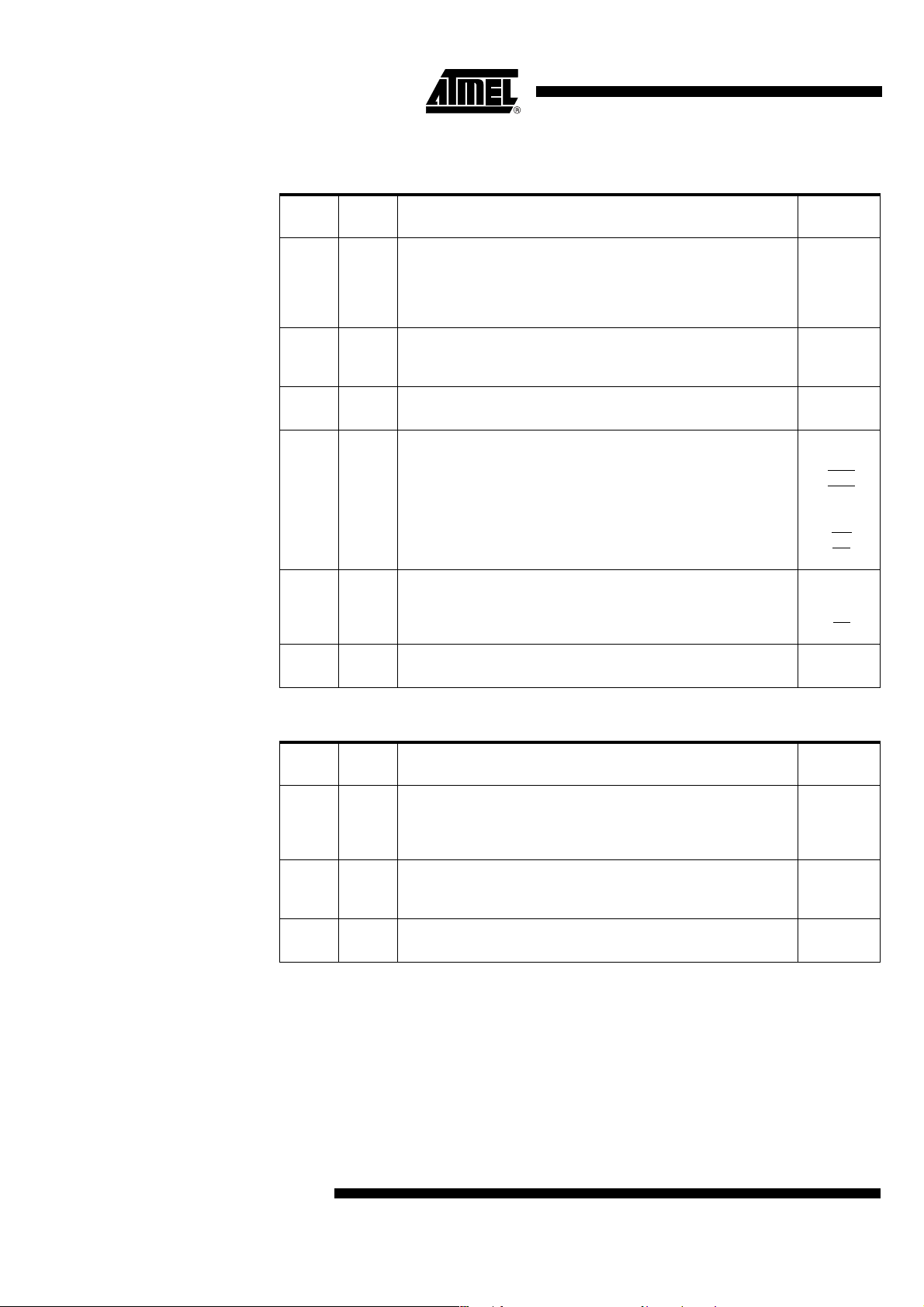

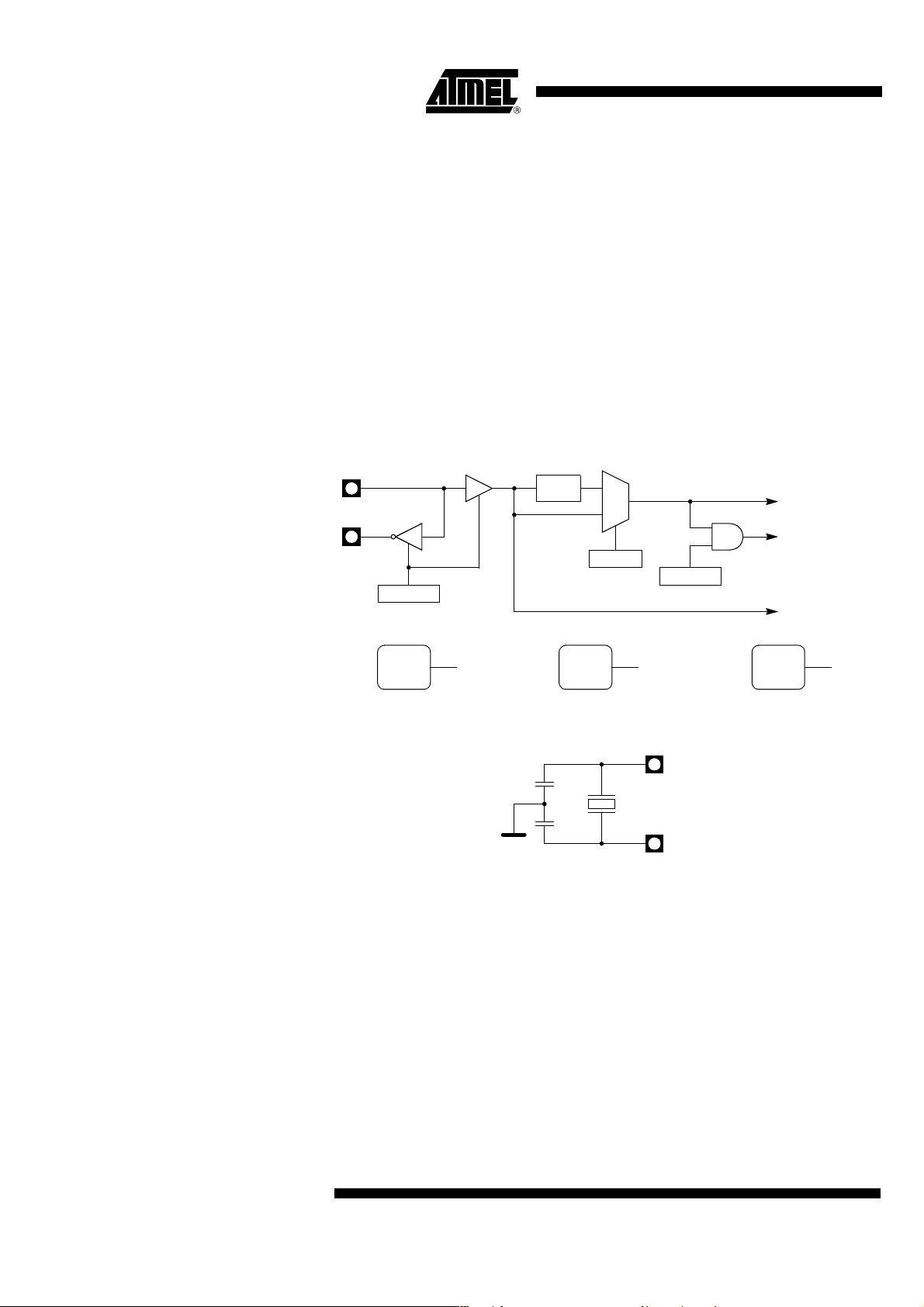

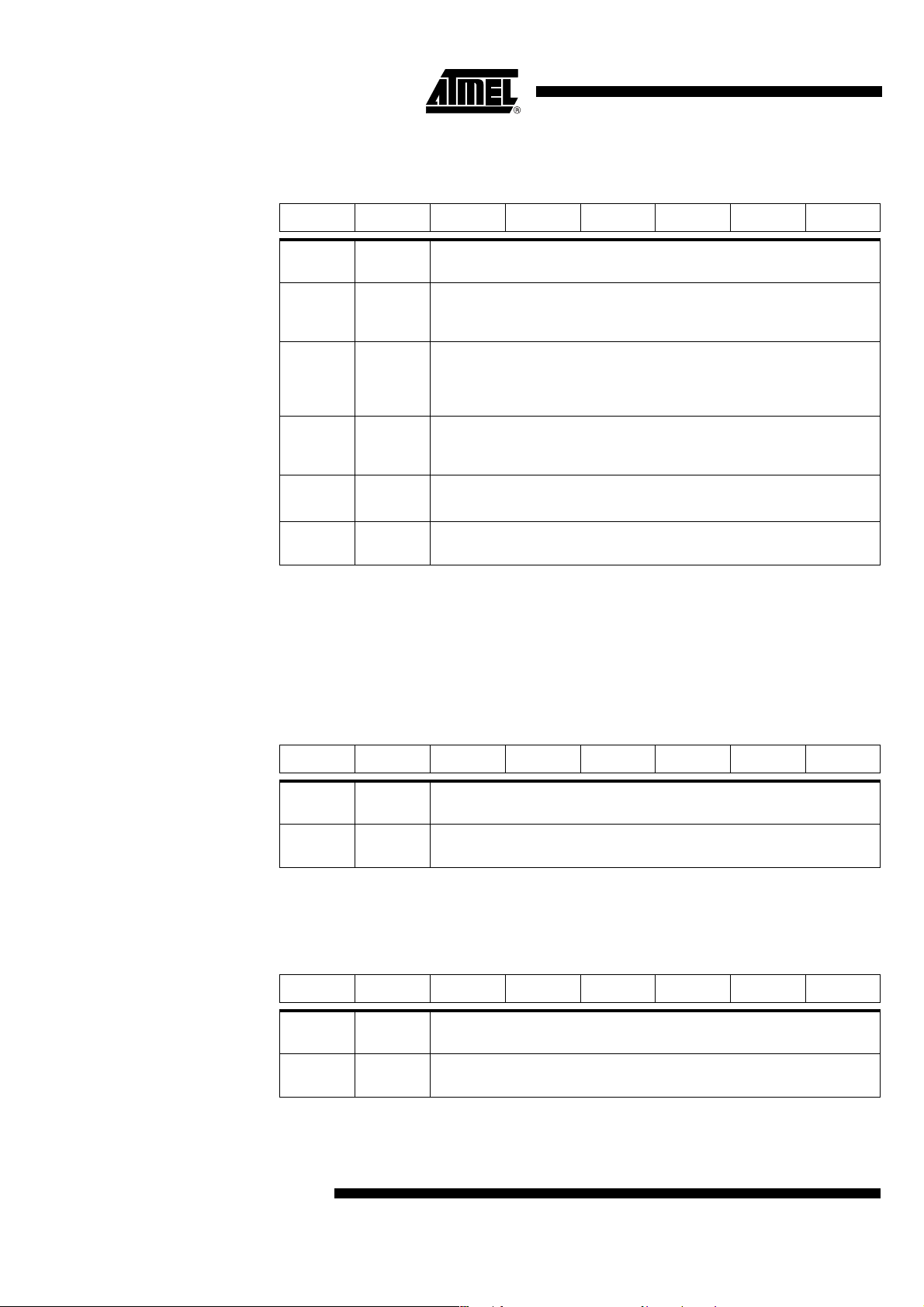

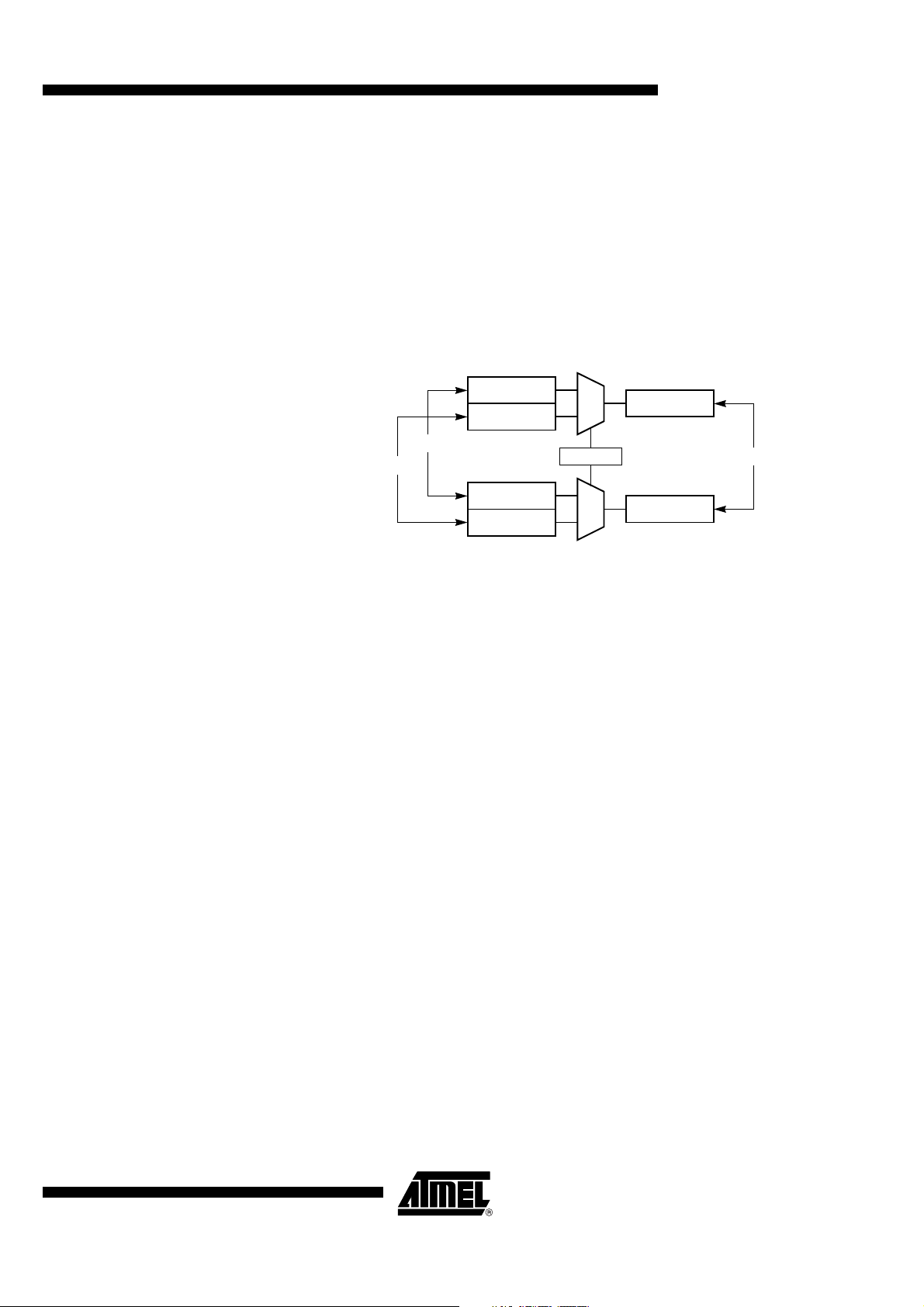

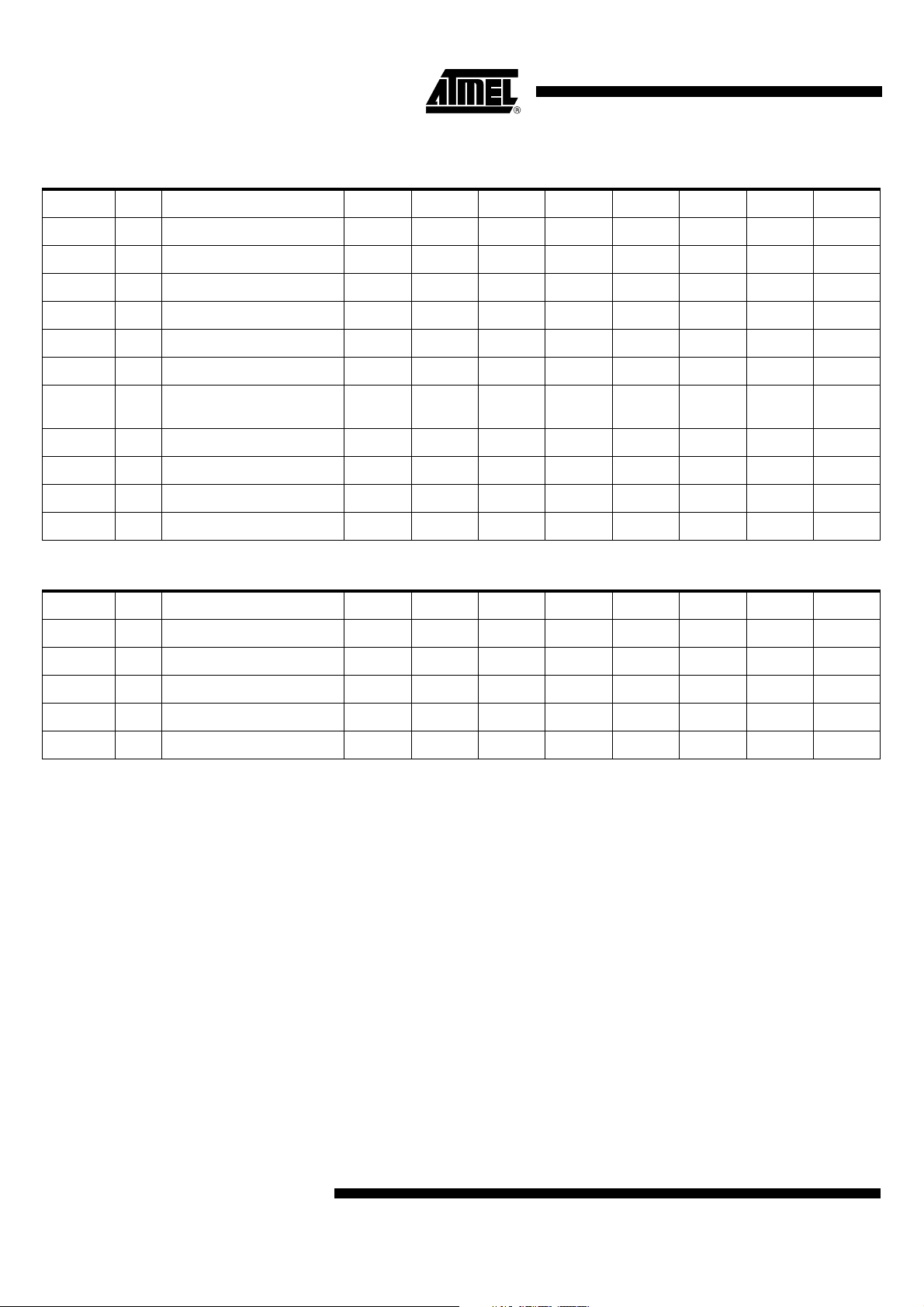

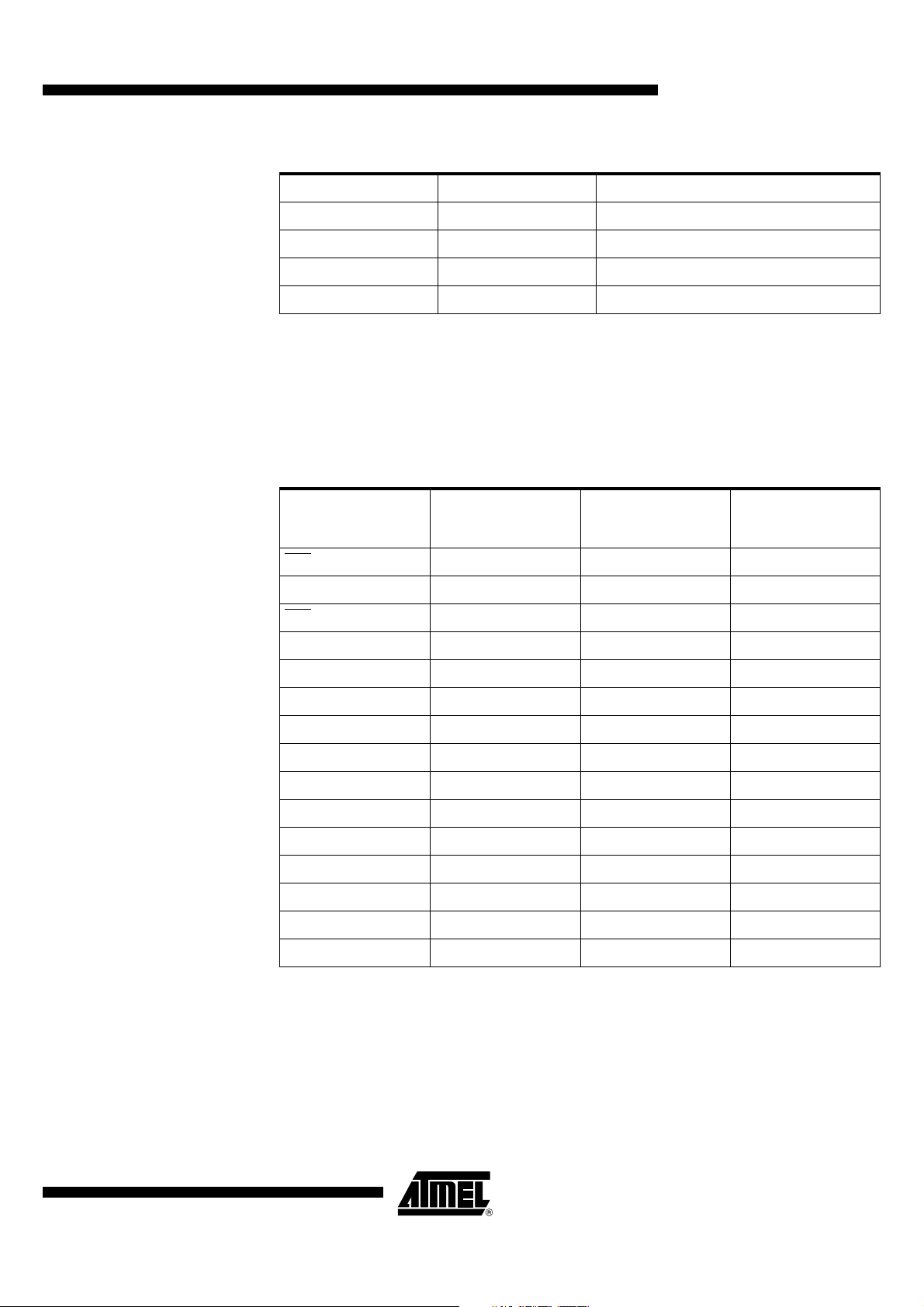

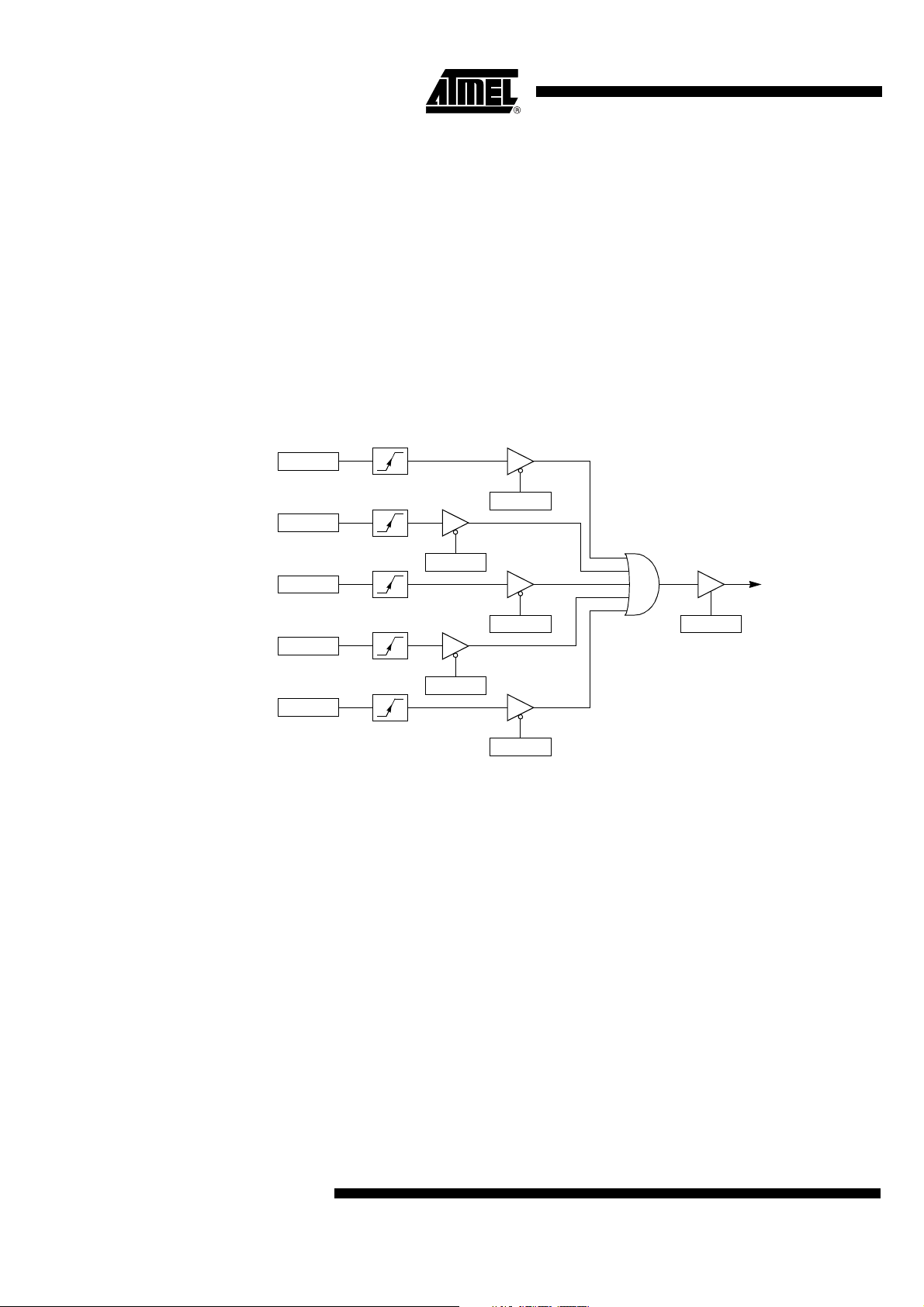

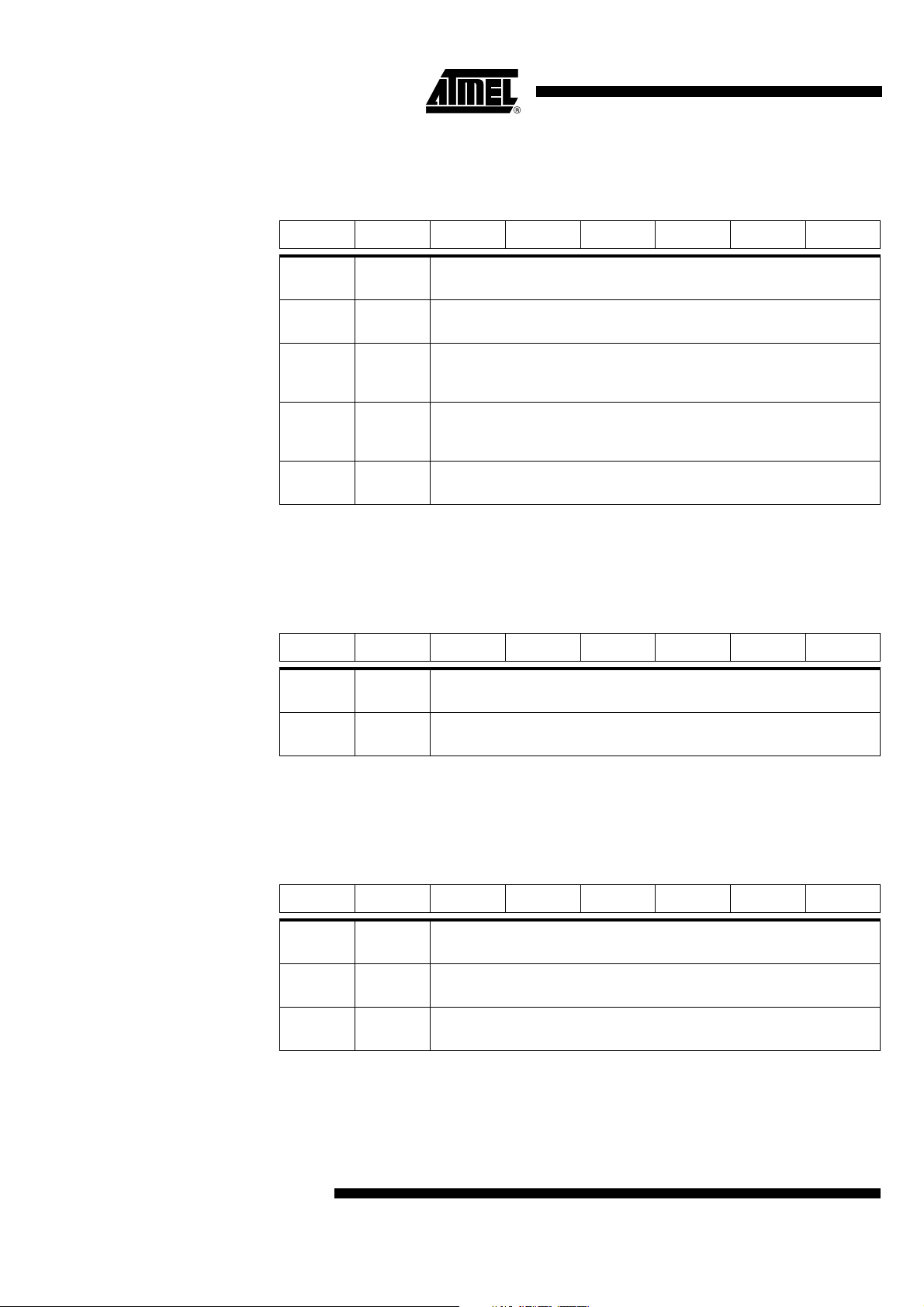

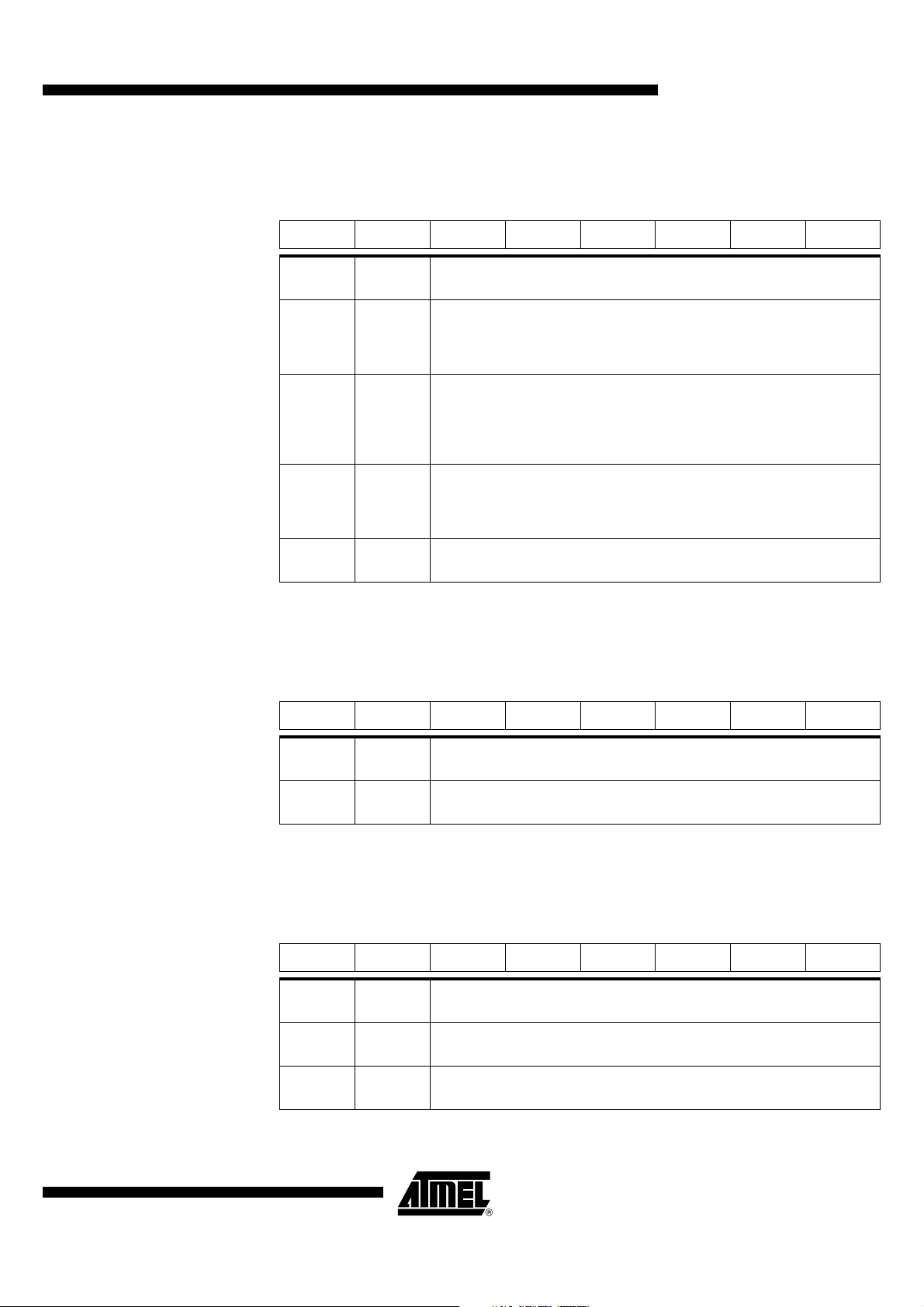

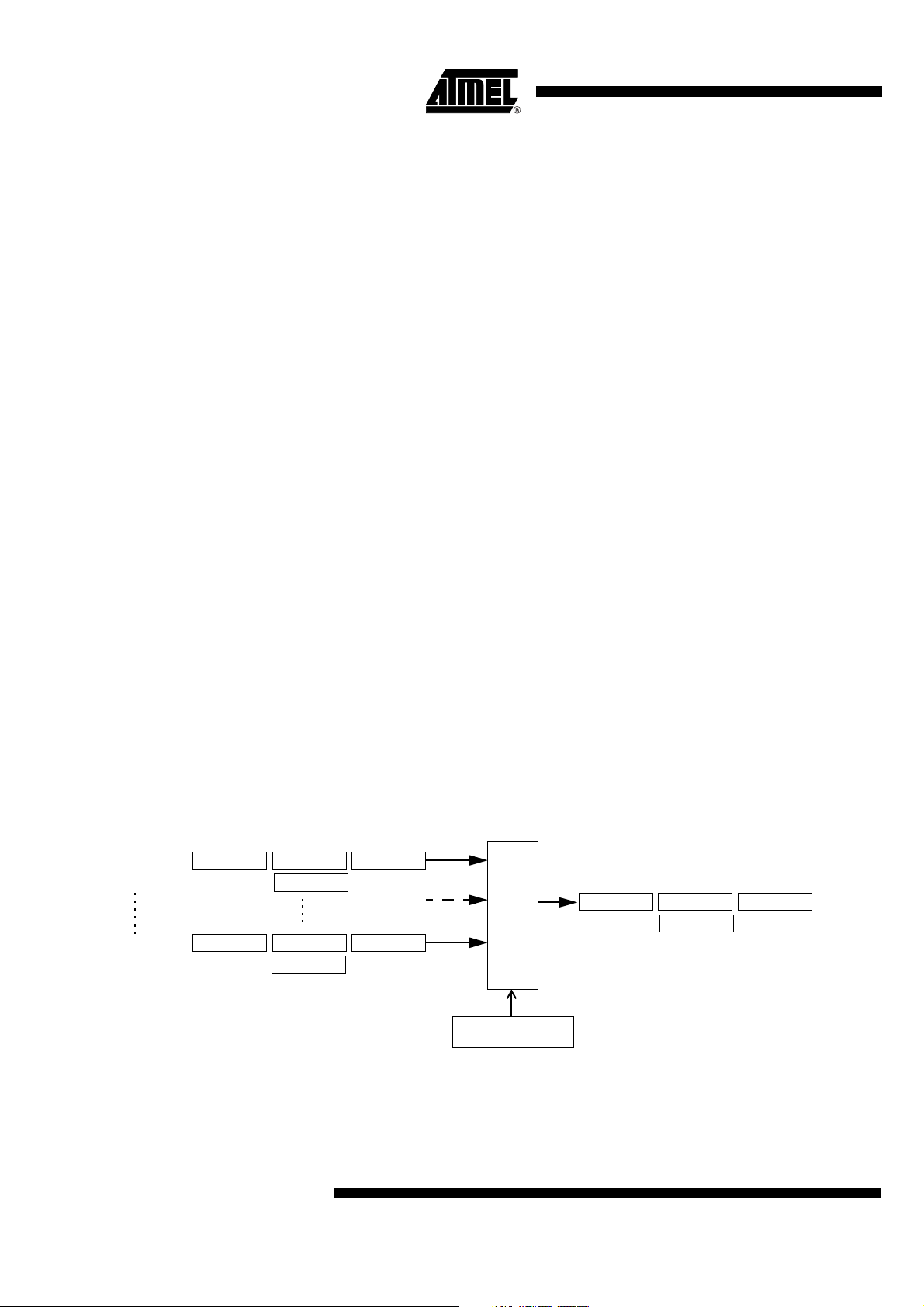

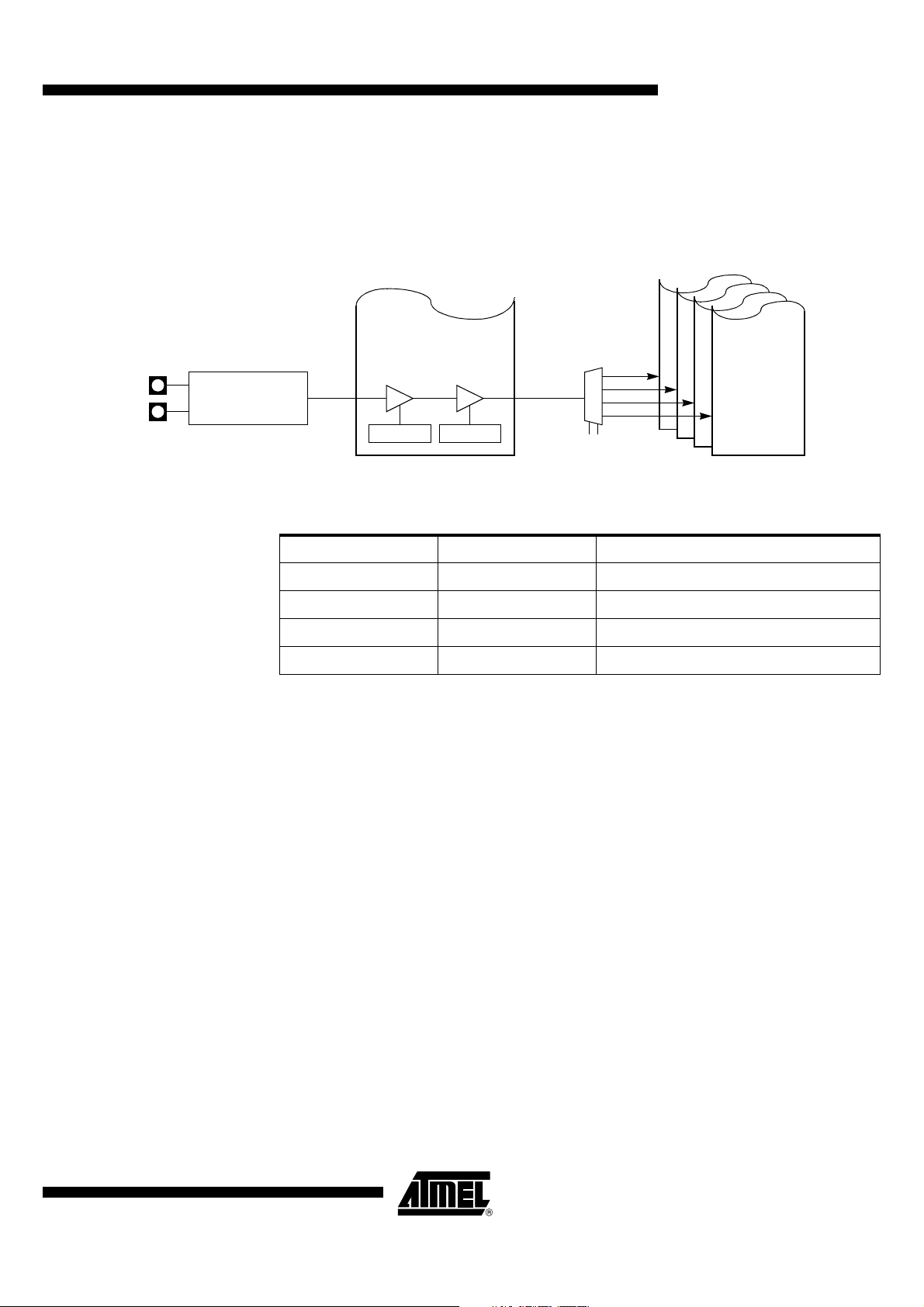

4. Block Diagram

Figure 1. AT8xC51SND1C Block Diagram

INT0 INT1 MOSIMISO

33

Interrupt

Handler Unit

VSSVDD

RAM

2304 Bytes

UVSSUVDD

AVSSAVDD

Flash

ROM

64 KBytes

Flash Boot

4 KBytes

AIN1:0

AREF

10-bit A to D

Converter

2

S output,

SCK

RXDTXD

33 33444411

UART

and

BRG

T1T0

Timers 0/1

Watchdog

SS

SPI/DataFlash

Controller

SCL SDA

TWI

Controller

C51 (X2 Core)

Clock and PLL

Unit

FILT X2X1

RST

MP3 Decoder

Unit

ISP

ALE

Audio Interface

8-Bit Internal Bus

I2S/PCM

DSELDCLK SCLKDOUT

USB

Controller

D+ D-

MCLK

MMC

Interface

MDAT

MCMD

Keyboard

Interface

1

KIN3:0

I/O

Ports

IDE

Interface

P0-P5

1 Alternate function of Port 1

3 Alternate function of Port 3

4 Alternate function of Port 4

2

4109H–8051–01/05

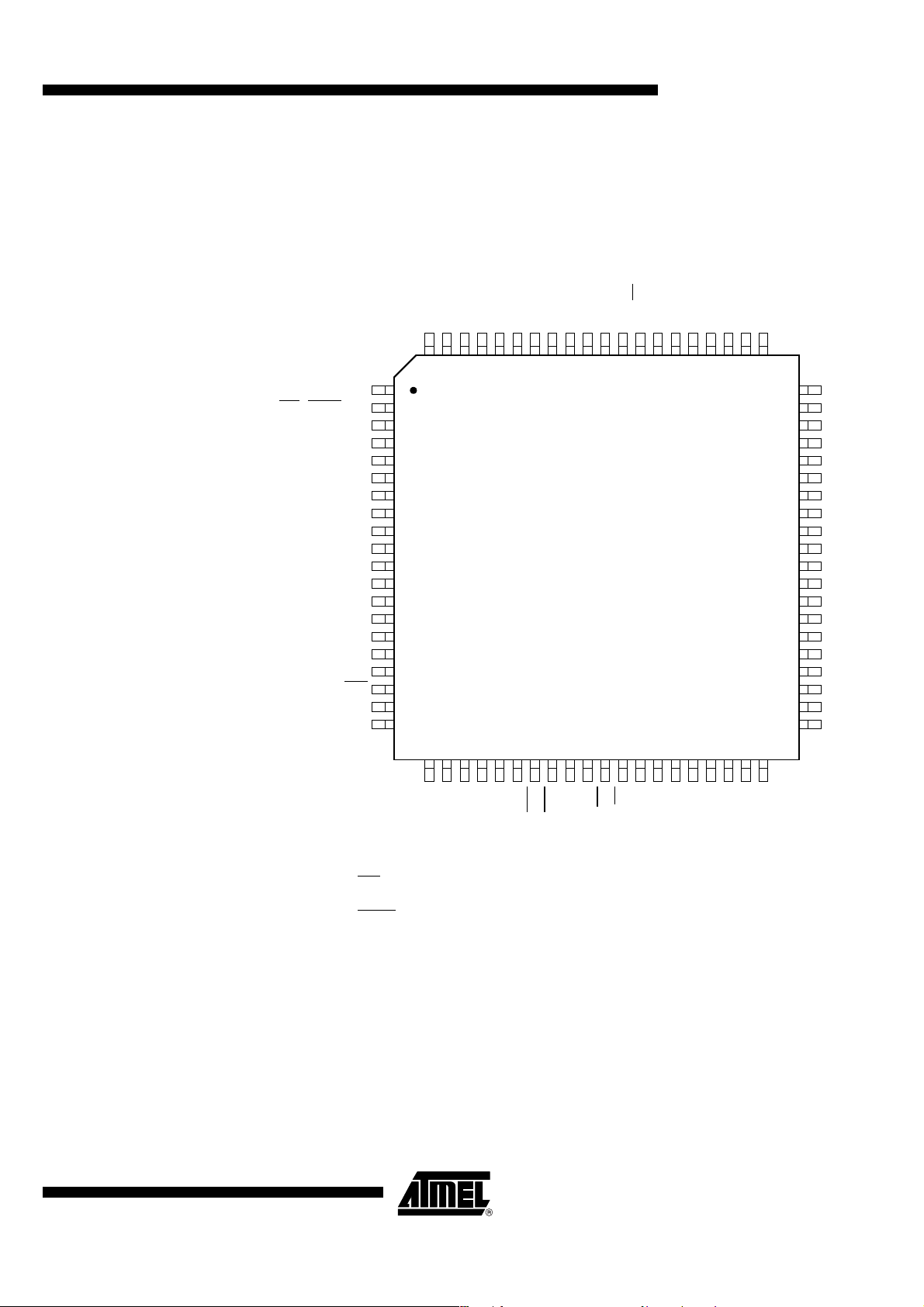

5. Pin Description

0

1

2

4

3

5

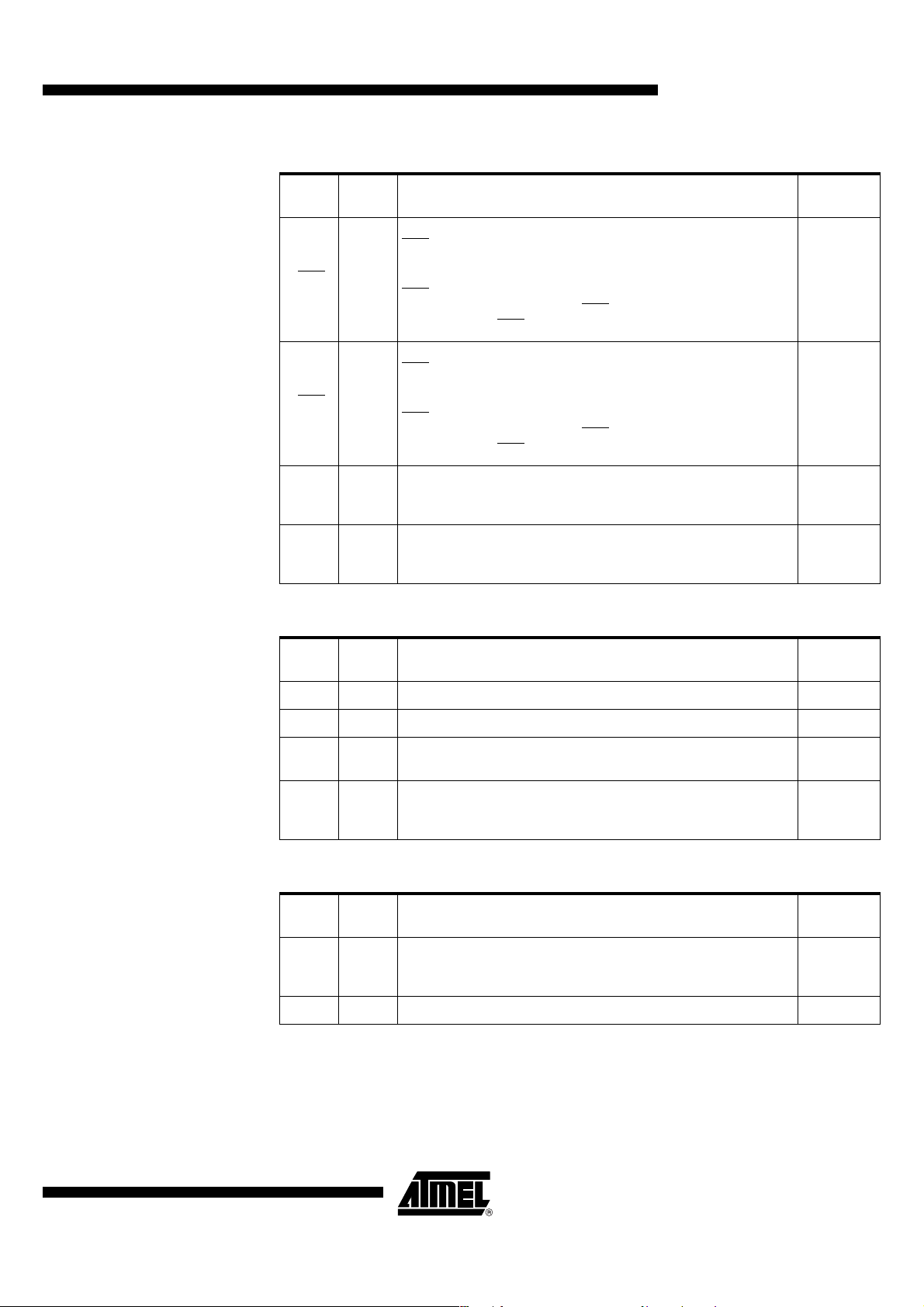

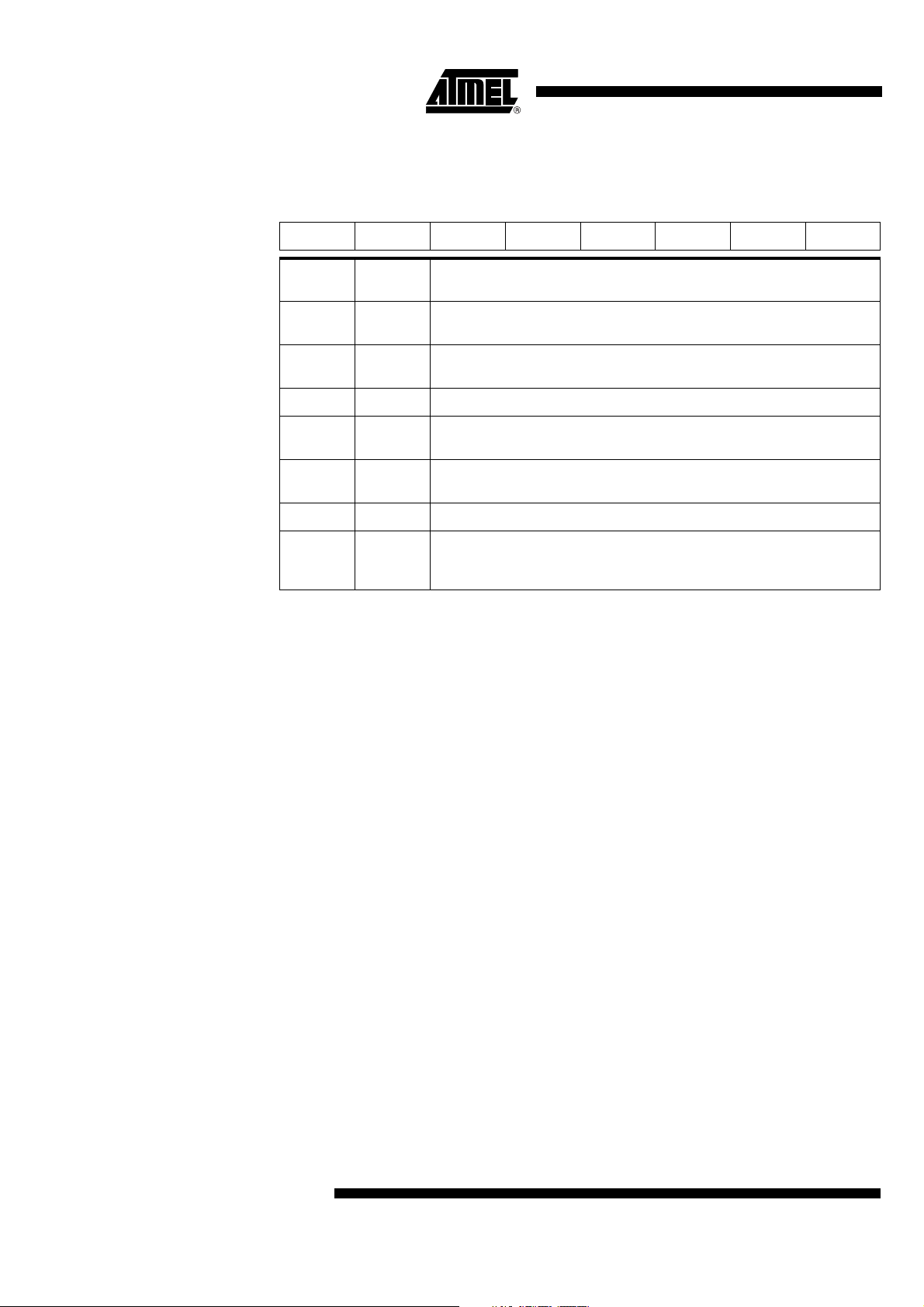

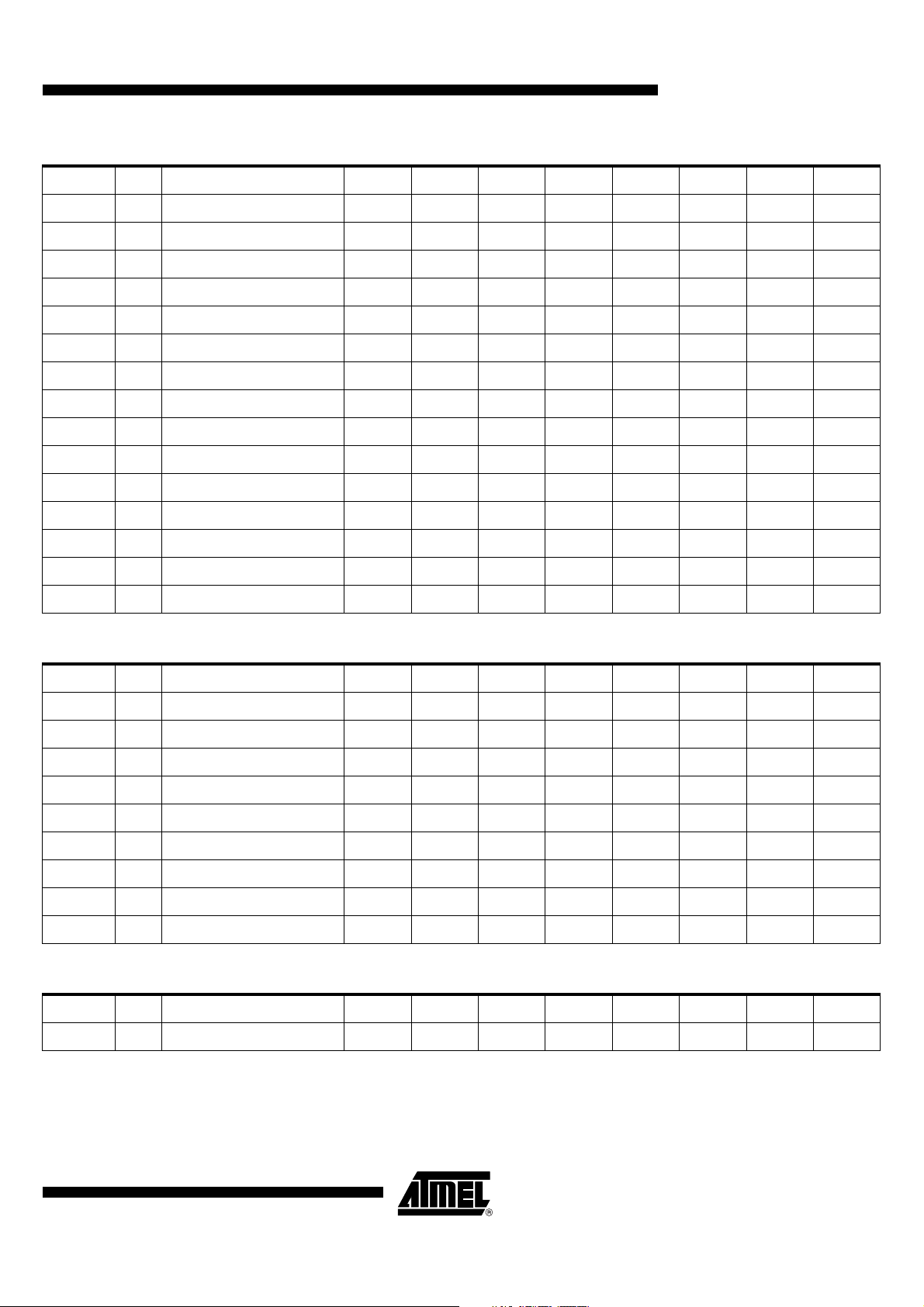

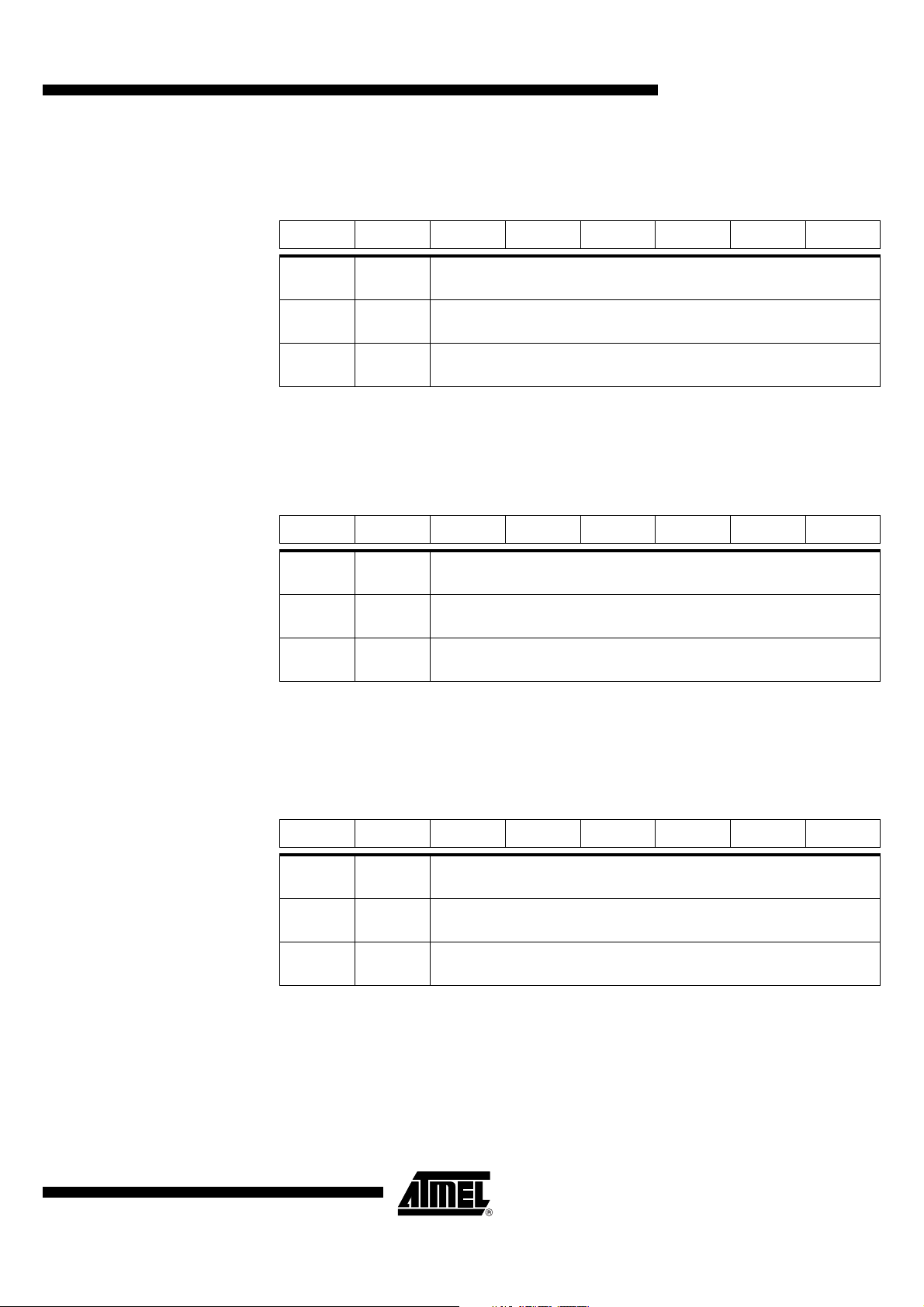

5.1 Pinouts

Figure 1. AT8xC51SND1C 80-pin QFP Package

ALE

1

/PSEN2/NC

ISP

P1.0/KIN0

P1.1/KIN1

P1.2/KIN2

P1.3/KIN3

P1.4

P1.5

P1.6/SCL

P1.7/SDA

VDD

PVDD

FILT

PVSS

VSS

X2

X1

TST

UVDD

UVSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

P0.3/AD3

P0.4/AD4

P0.5/AD5

VSS

VDD

717069

72

P0.6/AD6

P5.1

80

P5.0

79

P0.0/AD0

78

P0.1/AD1

77

P0.2/AD2

76

75

74

73

AT89C51SND1C-RO (FLASH)

AT83SND1C-RO (ROM)

AT80C51SND1C-RO (ROMLESS)

AT8xC51SND1C

P0.7/AD7

P4.3/SS

P4.2/SCK

67

68

P4.1/MOSI

66

P4.0/MISO

65

P2.0/A8

64

P2.1/A9

63

P4.7

62

P4.6

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

P4.5

P4.4

P2.2/A1

P2.3/A1

P2.4/A1

P2.5/A1

P2.6/A1

P2.7/A1

VSS

VDD

MCLK

MDAT

MCMD

RST

SCLK

DSEL

DCLK

DOUT

VSS

VDD

4109H–8051–01/05

21222324252627

D-

D+

VSS

VDD

P3.0/RXD

Notes: 1. ISP pin is only available in AT89C51SND1C product.

Do not connect this pin on AT83SND1C product.

2. PSEN pin is only available in AT80C51SND1C product.

28

302932

P3.4/T0

P3.3/INT1

P3.5/T1

P3.1/TXD

P3.2/INT0

31

P3.6/WR

33

34353637383940

AVSS

AVDD

P3.7/RD

P5.3

P5.2

AIN1

AIN0

AREFP

AREFN

3

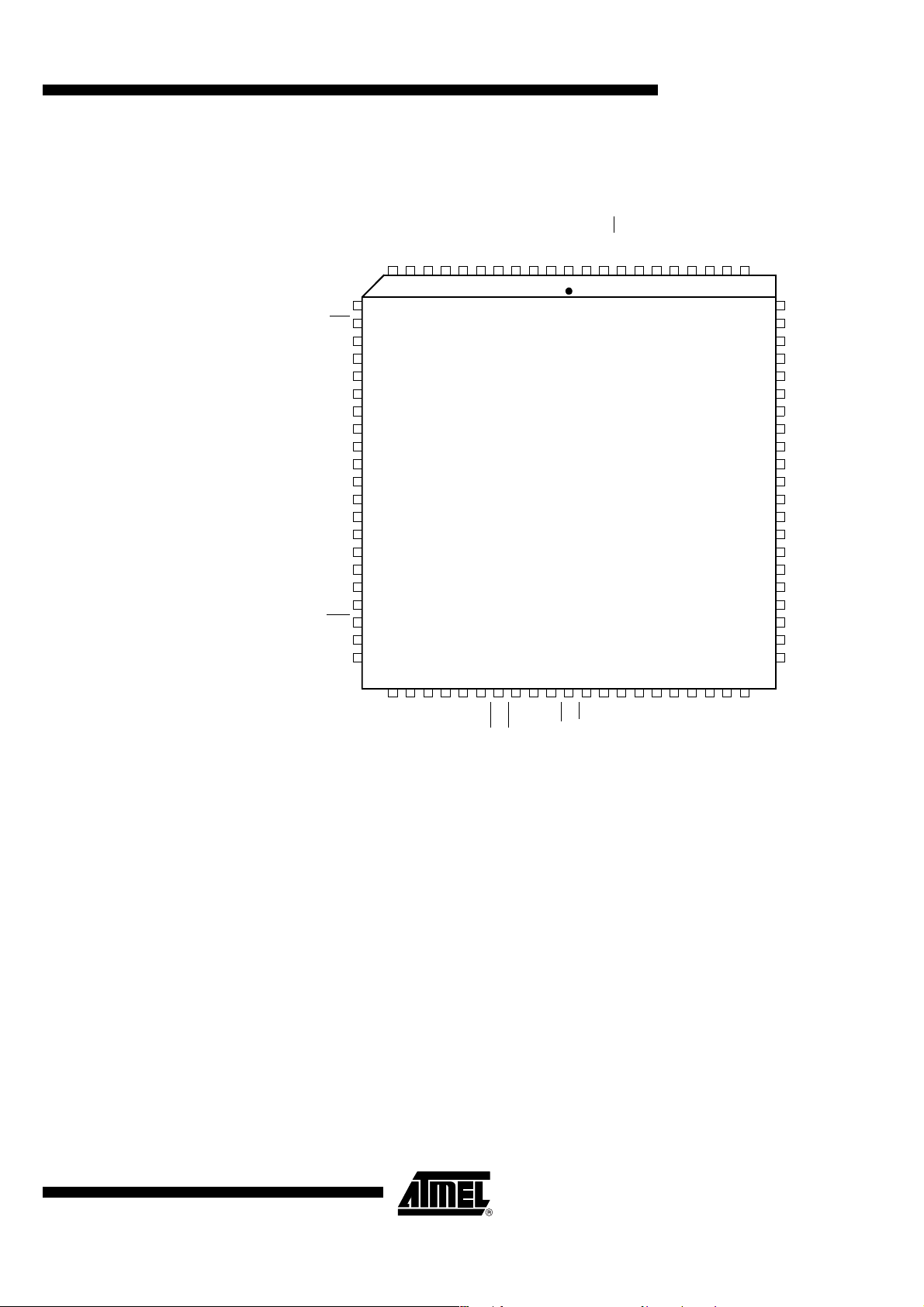

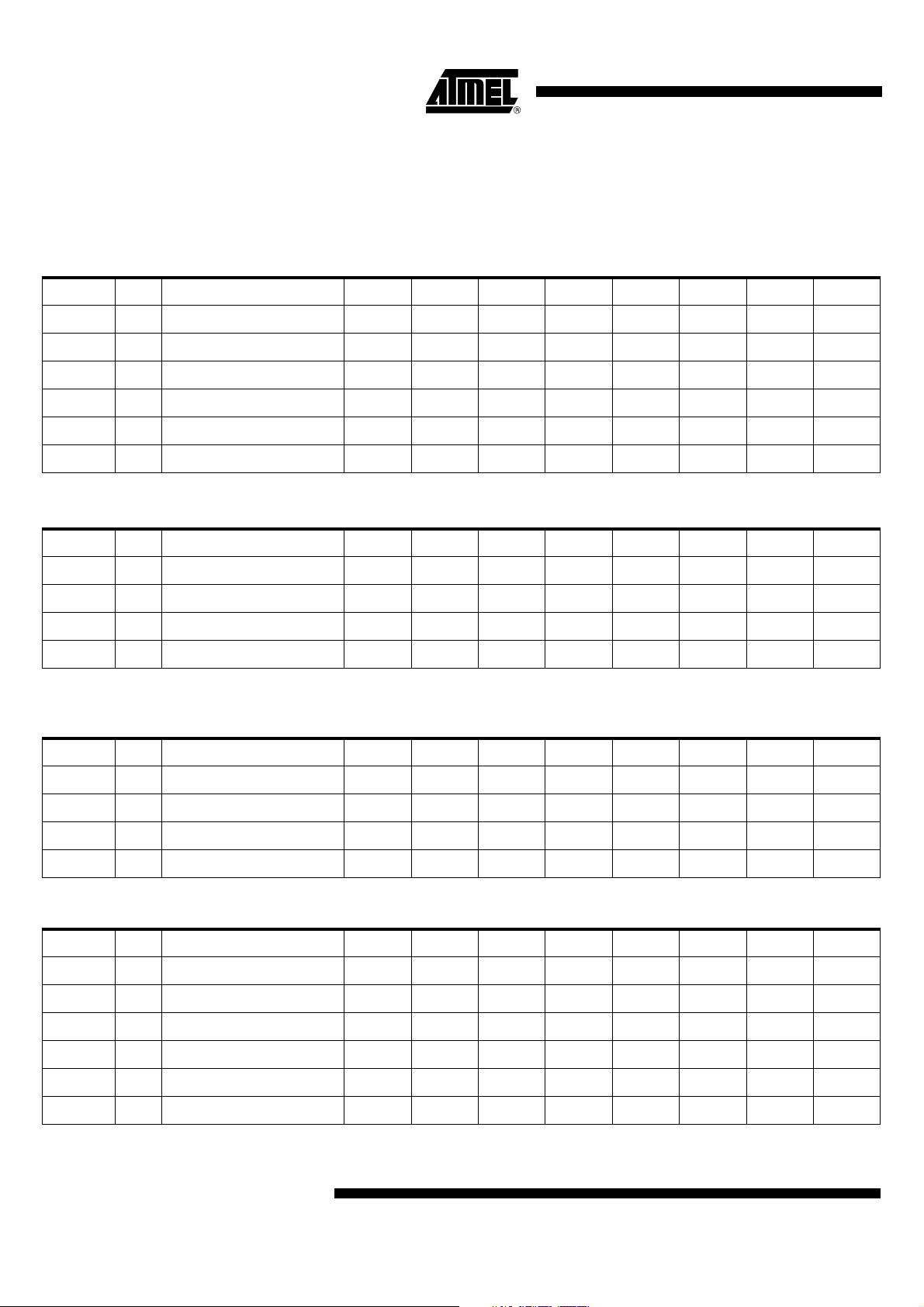

AT8xC51SND1C

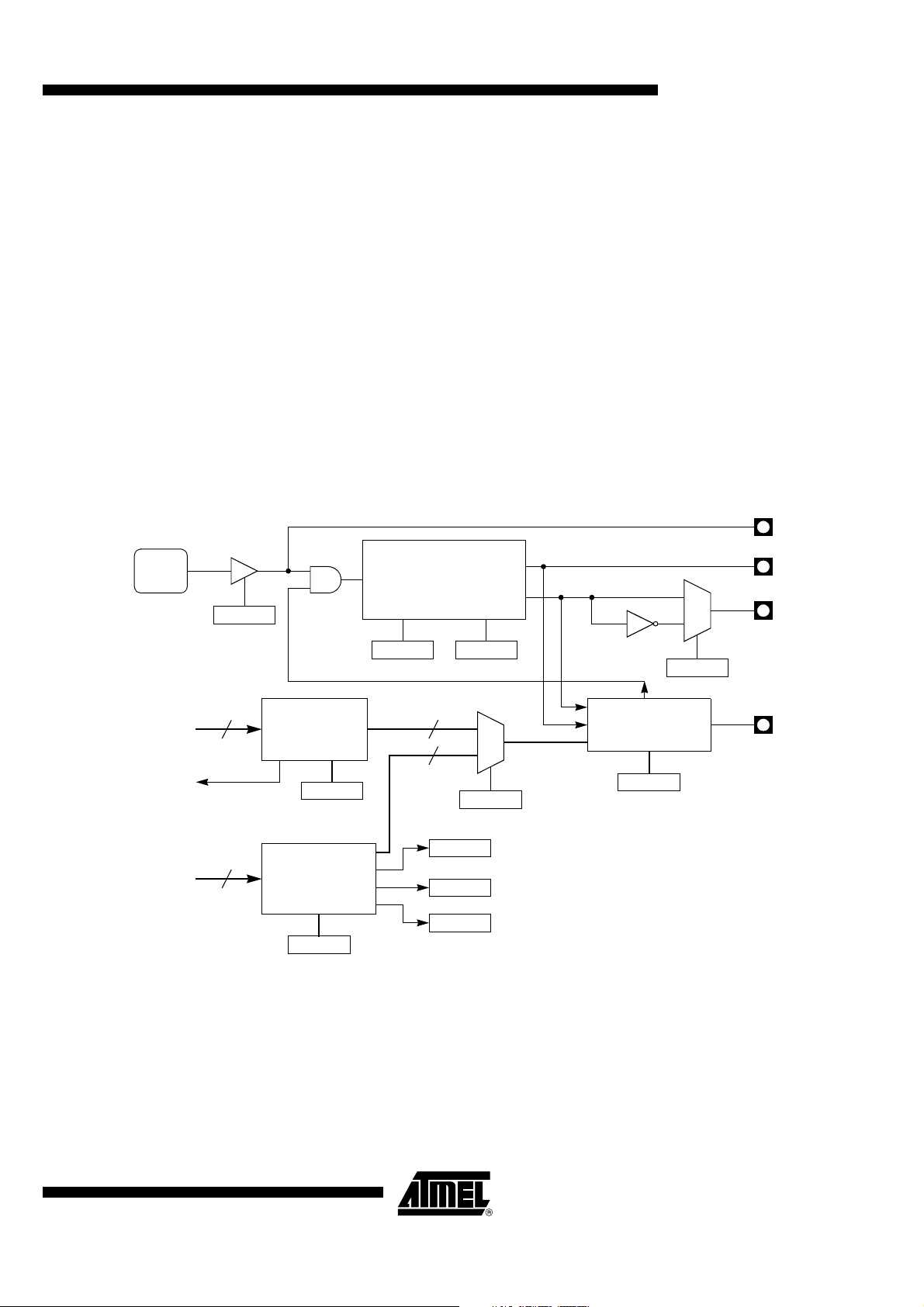

Figure 2. AT8xC51SND1C 81-pin BGA Package

C

B

A

D

E

F

G

H

J

P4.6

P4.4

P2.5/

A13

P2.4/

A12

VDD

RST

DSEL

DCLK

89765432

P2.0/

P4.7

P2.2/

P2.6/

A14

P2.3/

A11

MCMD

SCLK

VSS

P4.0/

MISO SCK AD2

P4.1/

MOSI

P2.1/

A9A10

P4.5

VSS

MCLK

DOUT

AIN1

P4.2/

P4.3/

SS

P0.6

P0.7/

AD7 AD5

P2.7/

A15

MDAT

P5.3

AVSS

VDD

P0.1/

VSS

P0.5/

AVDD

P3.7/

AIN0

RD

P0.2/

P0.4/

AD4 AD0AD1

P5.1

P1.6/

SCL SDA

FILT

P3.4/

T0

P3.5/

T1

P3.3/

INT1

P0.3/

AD3A8

P0.0/

P1.0/

KIN0

P1.7/

PVDD

UVSS

VDD

P3.1/

TXD

P5.0

ISP

PSEN

NC

P1.3/

KIN3

P1.5

X1

PVSS

TST

D-

1

ALE

1

/

2

P1.1

P1.2/

KIN2

P1.4

VDD

X2

VSS

UVDD

VDD

P5.2

AREFP

AREFN

P3.6/

WR

P3.2/

INT0

P3.0/

RXD

Notes: 1. ISP pin is only available in AT89C51SND1C product.

Do not connect this pin on AT83SND1C and AT80C51SND1C product.

2. PSEN

pin is only available in AT80C51SND1C product.

VSS

D+

4

4109H–8051–01/05

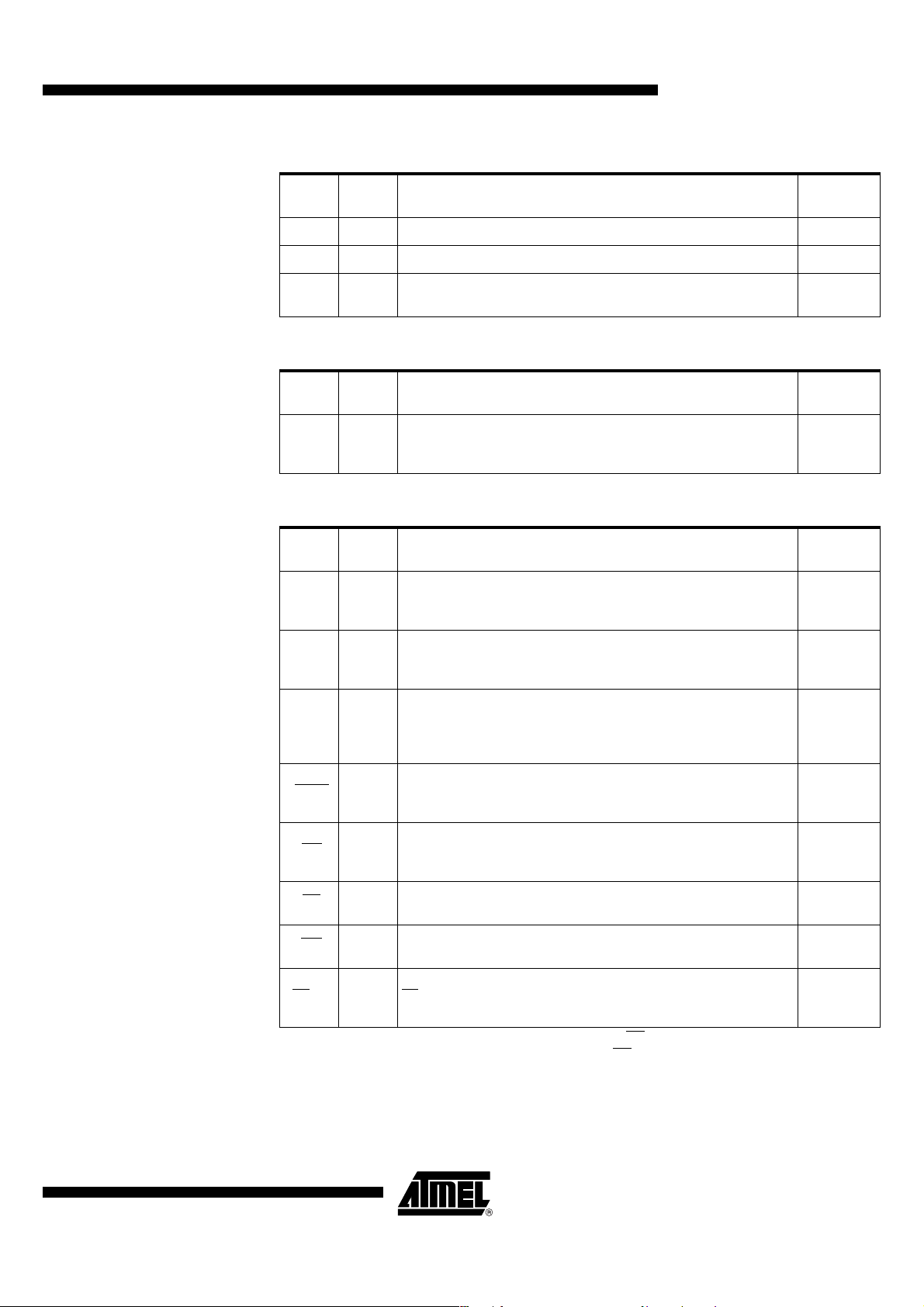

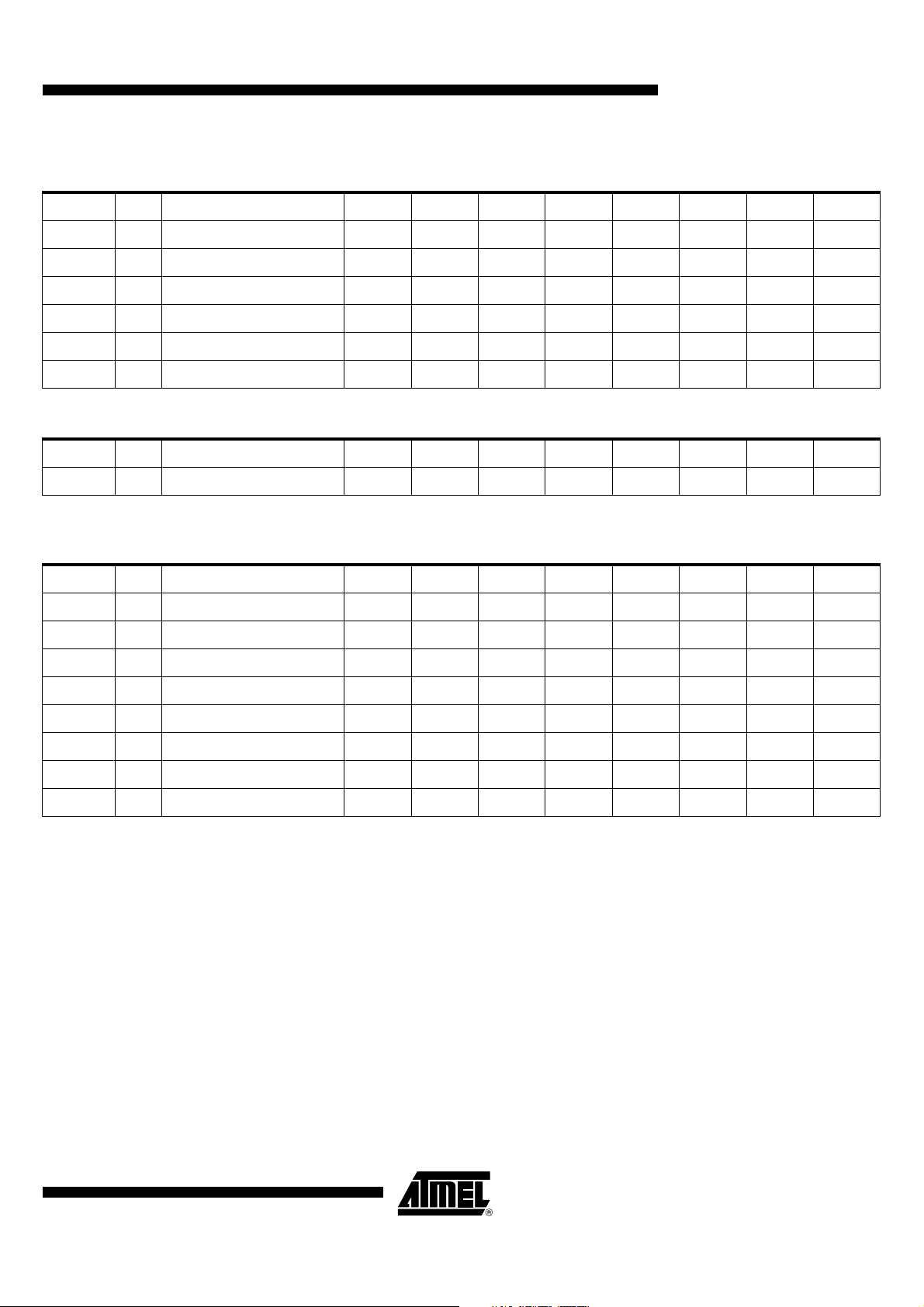

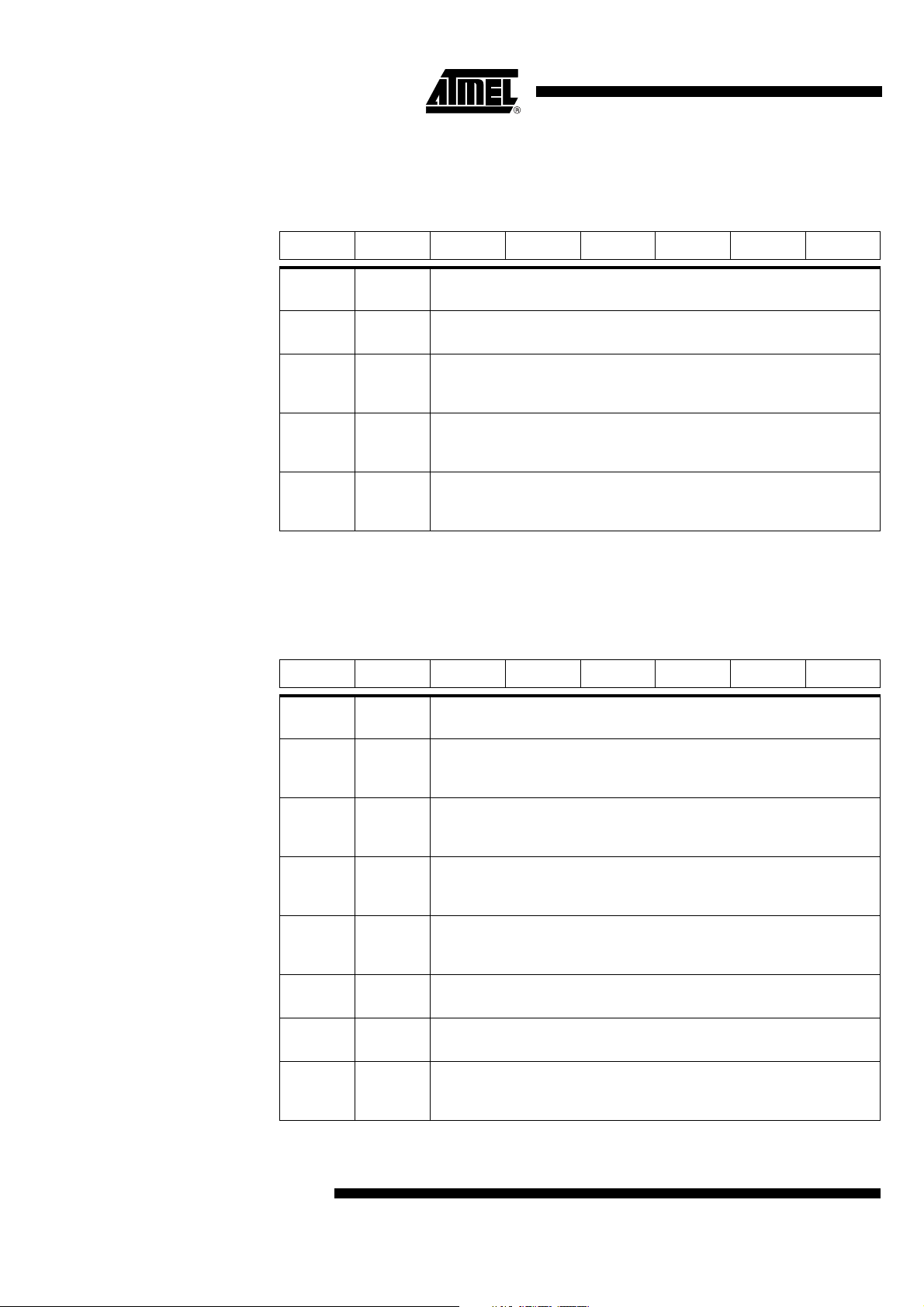

Figure 3. AT8xC51SND1C 84-pin PLCC Package

AT8xC51SND1C

ALE

ISP

P1.0/KIN0

P1.1/KIN1

P1.2/KIN2

P1.3/KIN3

P1.4

P1.5

P1.6/SCL

P1.7/SDA

VDD

PAVDD

FILT

PAVSS

VSS

X2

NC

X1

TST

UVDD

UVSS

NC

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

3334353637

P5.1

10

P0.3/AD3

P0.4/AD4

P0.5/AD5

VSS

VDD

P0.2/AD2

P0.1/AD1

P5.0

P0.0/AD0

432

5

6

7

8

9

P0.6/AD6

1

84838281807978

AT89C51SND1C-SR (FLASH)

3839404142

43

444546474849505152

P4.3/SS

P0.7/AD7

P4.2/SCK

P2.0/A8

P4.0/MISO

P2.1/A9

77

P4.7

76

P4.6

75

53

NC

74

73

P4.5

7271P4.4

P2.2/A10

70

P2.3/A11

69

P2.4/A12

68

P2.5/A13

67

P2.6/A14

66

P2.7/A15

65

VSS

64

VDD

MCLK

63

MDAT

62

MCMD

61

60

RST

59

SCLK

58

DSEL

57

DCLK

56

DOUT

55

VSS

54

VDD

P4.1/MOSI

D+

D-

VSS

VDD

P3.4/T0

P3.5/T1

P3.0/RXD

P3.1/TXD

P3.3/INT1

P3.2/INT0

P3.6/WR

P3.7/RD

AVSS

AVDD

AREFP

AIN1

AIN0

AREFN

NC

P5.2

P5.3

4109H–8051–01/05

5

AT8xC51SND1C

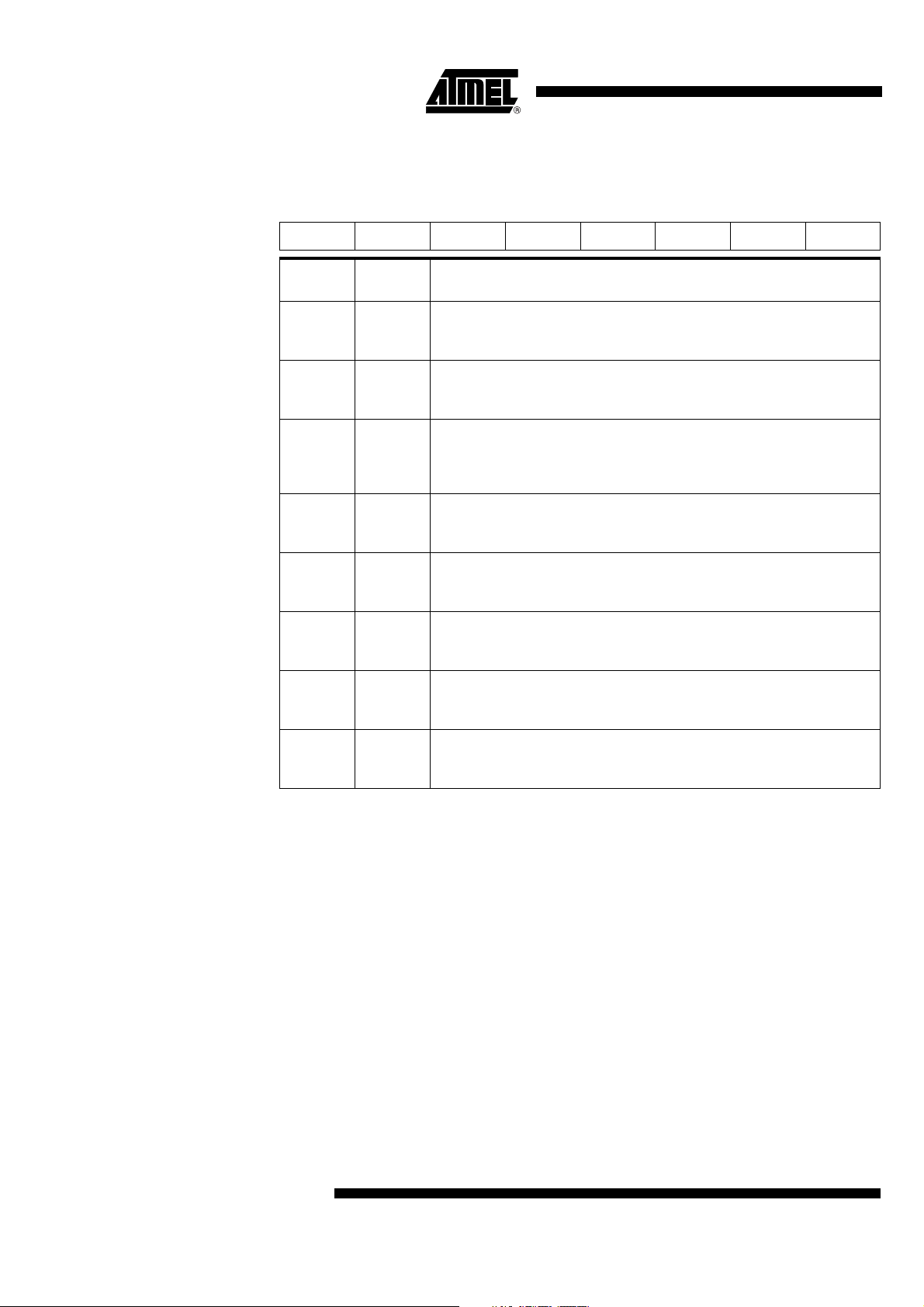

5.2 Signals All the AT8xC51SND1C signals are detailed by functionality in Table 3 to Table 16.

Table 3. Ports Signal Description

Signal

Name Type Description

Port 0

P0.7:0 I/O

P1.7:0 I/O

P2.7:0 I/O

P3.7:0 I/O

P4.7:0 I/O

P0 is an 8-bit open-drain bidirectional I/O port. Port 0 pins that have 1s

written to them float and can be used as high impedance inputs. To

avoid any parasitic current consumption, floating P0 inputs must be

polarized to V

Port 1

P1 is an 8-bit bidirectional I/O port with internal pull-ups.

Port 2

P2 is an 8-bit bidirectional I/O port with internal pull-ups.

Port 3

P3 is an 8-bit bidirectional I/O port with internal pull-ups.

Port 4

P4 is an 8-bit bidirectional I/O port with internal pull-ups.

DD

Alternate

Function

AD7:0

or VSS.

KIN3:0

SCL

SDA

A15:8

RXD

TXD

INT0

INT1

T0

T1

WR

RD

MISO

MOSI

SCK

SS

P5.3:0 I/O

Port 5

P5 is a 4-bit bidirectional I/O port with internal pull-ups.

Table 4. Cloc k Si gna l Desc r ipt ion

Signal

Name Type Description

Input to the on-chip inverting oscillator amplifier

X1 I

X2 O

FILT I

To use the internal oscillator, a crystal/resonator circuit is connected to

this pin. If an external oscillator is used, its output is connected to this

pin. X1 is the clock source for internal timing.

Output of the on-chip inverting oscillator amplifier

To use the internal oscillator, a crystal/resonator circuit is connected to

this pin. If an external oscillator is used, leave X2 unconnected.

PLL Low Pass Filter input

FILT receives the RC network of the PLL low pass filter.

-

Alternate

Function

-

-

-

6

4109H–8051–01/05

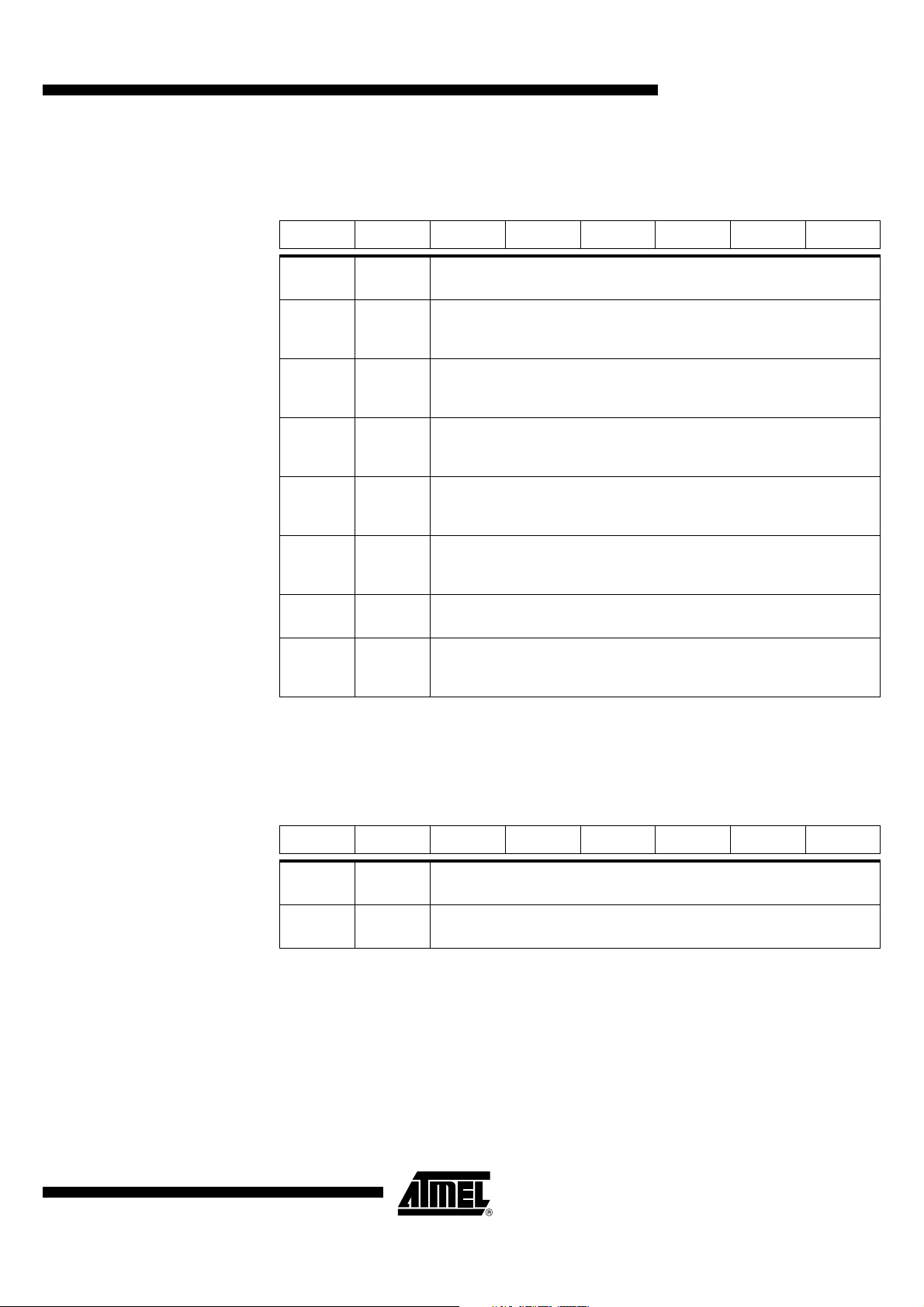

Table 5. Timer 0 and Timer 1 Signal Description

AT8xC51SND1C

Signal

Name Type Description

Timer 0 Gate Input

serves as external run control for timer 0, when selected by

INT0

GATE0 bit in TCON register.

INT0

INT1

T0 I

T1 I

I

External Interrupt 0

input sets IE0 in the TCON register. If bit IT0 in this register is set,

INT0

bit IE0 is set by a falling edge on INT0

by a low level on INT0

Timer 1 Gate Input

serves as external run control for timer 1, when selected by

INT1

GATE1 bit in TCON register.

I

External Interrupt 1

INT1

input sets IE1 in the TCON register. If bit IT1 in this register is set,

bit IE1 is set by a falling edge on INT1

by a low level on INT1

Timer 0 External Clock Input

When timer 0 operates as a counter, a falling edge on the T0 pin

increments the count.

Timer 1 External Clock Input

When timer 1 operates as a counter, a falling edge on the T1 pin

increments the count.

.

.

Table 6. Audio Interface Signal Description

Alternate

Function

P3.2

. If bit IT0 is cleared, bit IE0 is set

P3.3

. If bit IT1 is cleared, bit IE1 is set

P3.4

P3.5

Signal

Name Type Description

DCLK O DAC Data Bit Clock -

DOUT O DAC Audio Data -

DSEL O

SCLK O

DAC Channel Select Signal

DSEL is the sample rate clock output.

DAC System Clock

SCLK is the oversampling clock synchronized to the digital audio data

(DOUT) and the channel selection signal (DSEL).

Table 7. USB Controller Signal Description

Signal

Name Type Description

D+ I/O

D- I/O USB Negative Data Upstream Port -

USB Positive Data Upstream Port

This pin requires an external 1.5 KΩ pull-up to V

operation.

for full speed

DD

Alternate

Function

-

-

Alternate

Function

-

4109H–8051–01/05

7

AT8xC51SND1C

Table 8. MutiMediaCard Interface Signal Description

Signal

Name Type Description

MCLK O

MCMD I/O

MDAT I/O

MMC Clock output

Data or command clock transfer.

MMC Command line

Bidirectional command channel used for card initialization and data

transfer commands. To avoid any parasitic current consumption,

unused MCMD input must be polarized to V

MMC Data line

Bidirectional data channel. To avoid any parasitic current consumption,

unused MDAT input must be polarized to V

Table 9. UART Signal Description

Signal

Name Type Description

Receive Serial Data

RXD I/O

TXD O

RXD sends and receives data in serial I/O mode 0 and receives data in

serial I/O modes 1, 2 and 3.

Transmit Serial Data

TXD outputs the shift clock in serial I/O mode 0 and transmits data in

serial I/O modes 1, 2 and 3.

DD

or VSS.

DD

Alternate

Function

-

-

or VSS.

-

Alternate

Function

P3.0

P3.1

Table 10. SPI Controller Signal Description

Signal

Name Type Description

MISO I/O

MOSI I/O

SCK I/O

SS

SPI Master Input Slave Output Data Line

When in master mode, MISO receives data from the slave peripheral.

When in slave mode, MISO outputs data to the master controller.

SPI Master Output Slave Input Data Line

When in master mode, MOSI outputs data to the slave peripheral.

When in slave mode, MOSI receives data from the master controller.

SPI Clock Line

When in master mode, SCK outputs clock to the slave peripheral. When

in slave mode, SCK receives clock from the master controller.

SPI Slave Select Line

I

When in controlled slave mode, SS

Table 11. TWI Controller Signal Description

Signal

Name Type Description

TWI Serial Clock

SCL I/O

When TWI controller is in master mode, SCL outputs the serial clock to

the slave peripherals. When TWI controller is in slave mode, SCL

receives clock from the master controller.

enables the slave mode.

Alternate

Function

P4.0

P4.1

P4.2

P4.3

Alternate

Function

P1.6

8

SDA I/O

TWI Serial Data

SDA is the bidirectional Two Wire data line.

P1.7

4109H–8051–01/05

Table 12. A/D Converter Signal Description

AT8xC51SND1C

Signal

Name Type Description

AIN1:0 I A/D Converter Analog Inputs -

AREFP I Analog Positive Voltage Reference Input -

AREFN I

Analog Negative Voltage Reference Input

This pin is internally connected to AVSS.

Table 13. Keypad Interface Signal Description

Signal

Name Type Description

KIN3:0 I

Keypad Input Lines

Holding one of these pins high or low for 24 oscillator periods triggers a

keypad interrupt.

Table 14. External Access Signal Description

Signal

Name Type Description

Address Lines

A15:8 I/O

Upper address lines for the external bus.

Multiplexed higher address and data lines for the IDE interface.

Alternate

Function

-

Alternate

Function

P1.3:0

Alternate

Function

P2.7:0

AD7:0 I/O

ALE O

PSEN

ISP

RD

WR

(1)(2)

EA

Address/Data Lines

Multiplexed lower address and data lines for the external memory or the

IDE interface.

Address Latch Enable Output

ALE signals the start of an external bus cycle and indicates that valid

address information is available on lines A7:0. An external latch is used

to demultiplex the address from address/data bus.

Program Store Enable Output (AT80C51SND1C Only)

I/O

This signal is active low during external code fetch or external code

read (MOVC instruction).

ISP Enable Input (AT89C51SND1C Only)

I/O

This signal must be held to GND through a pull-down resistor at the

falling reset to force execution of the internal bootloader.

Read Signal

O

Read signal asserted during external data memory read operation.

Write Signal

O

Write signal asserted during external data memory write operation.

External Access Enable (Dice Only)

I

EA must be externally held low to enable the device to fetch code from

external program memory locations 0000h to FFFFh.

Notes: 1. For ROM/Flash Dice product versions: pad EA must be connected to VCC.

2. For ROMl ess Dice product versions: pad EA

must be connected to VSS.

P0.7:0

-

-

-

P3.7

P3.6

-

4109H–8051–01/05

9

AT8xC51SND1C

Table 15. System Signal Description

Signal

Name Type Description

Reset Input

Holding this pin high for 64 oscillator periods while the oscillator is

running resets the device. The Port pins are driven to their reset

conditions when a voltage lower than V

RST I

TST

oscillator is running.

This pin has an internal pull-down resistor which allows the device to be

reset by connecting a capacitor between this pin and V

Asserting RST when the chip is in Idle mode or Power-Down mode

returns the chip to normal operation.

Test Input

I

Tes t mode entry signal. This pin must be set to V

Table 16. Power Signal Description

Signal

Name Type Description

VDD PWR

VSS GND

AVDD PWR

Digital Supply Voltage

Connect these pins to +3V supply voltage.

Circuit Ground

Connect these pins to ground.

Analog Supply Voltage

Connect this pin to +3V supply voltage.

is applied, whether or not the

IL

.

DD

.

DD

Alternate

Function

-

-

Alternate

Function

-

-

-

AVSS GND

PVDD PWR

PVSS GND

UVDD PWR

UVSS GND

Analog Ground

Connect this pin to ground.

PLL Supply voltage

Connect this pin to +3V supply voltage.

PLL Circuit Ground

Connect this pin to ground.

USB Supply Voltage

Connect this pin to +3V supply voltage.

USB Ground

Connect this pin to ground.

-

-

-

-

-

10

4109H–8051–01/05

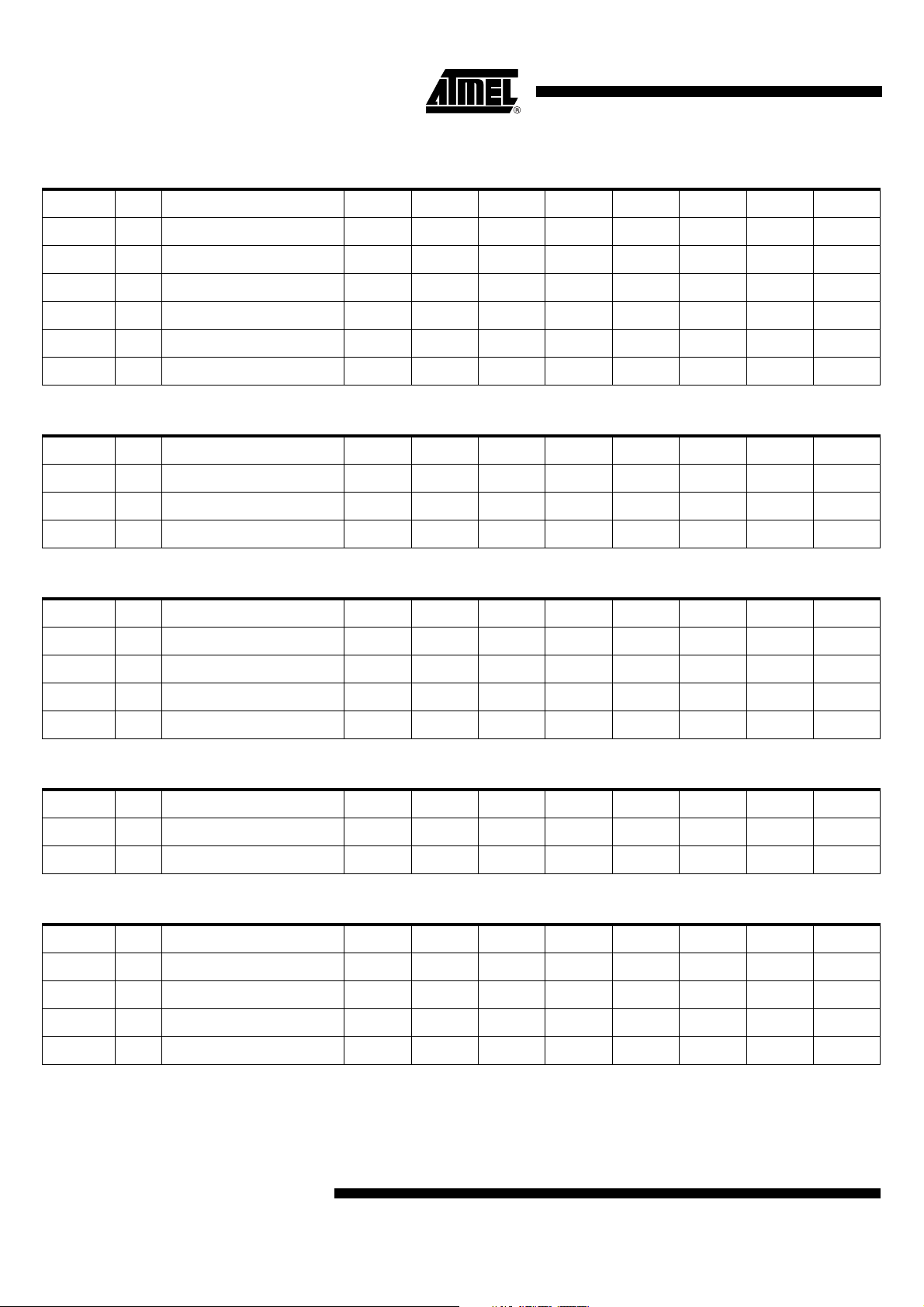

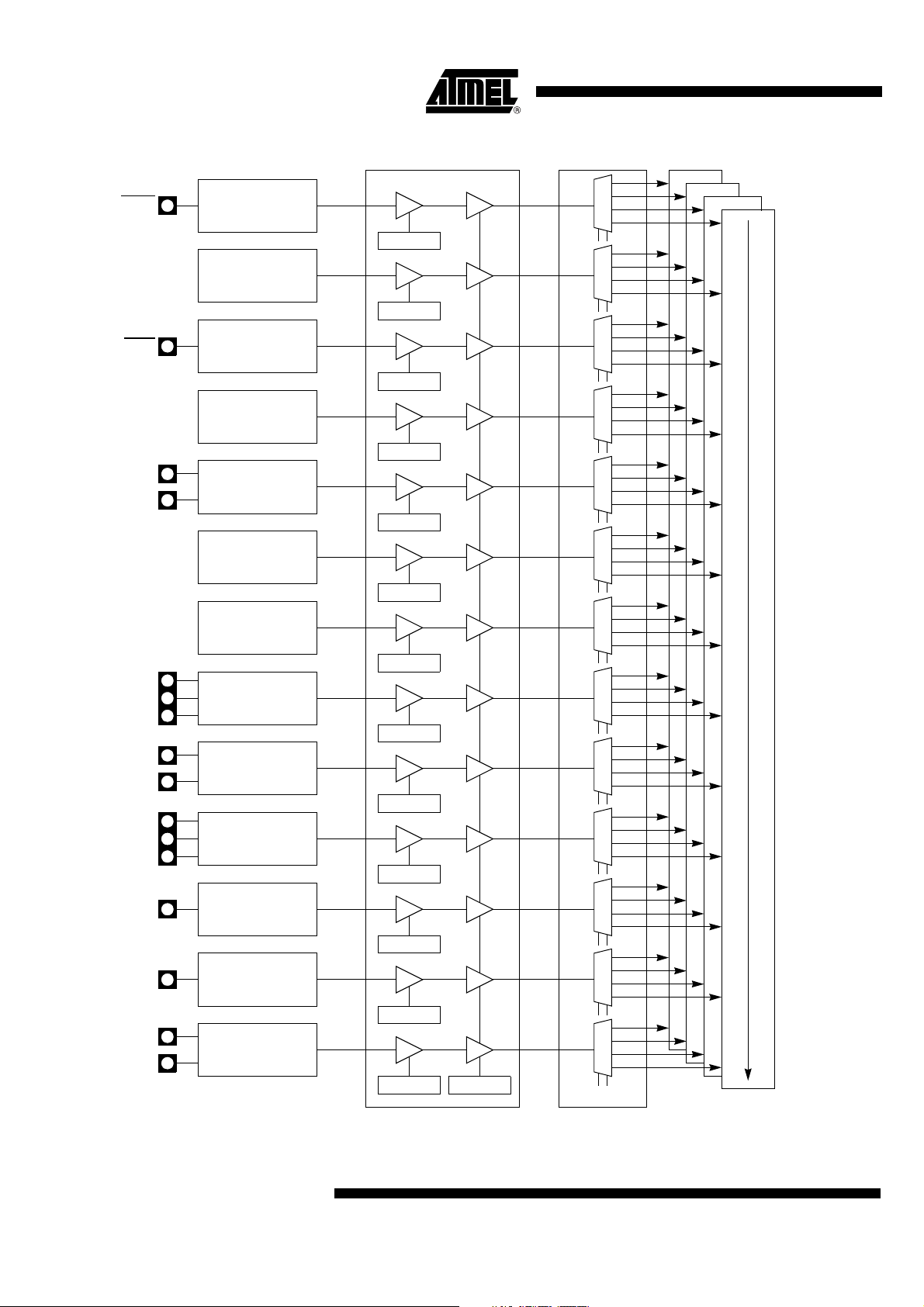

AT8xC51SND1C

VSS

VDD

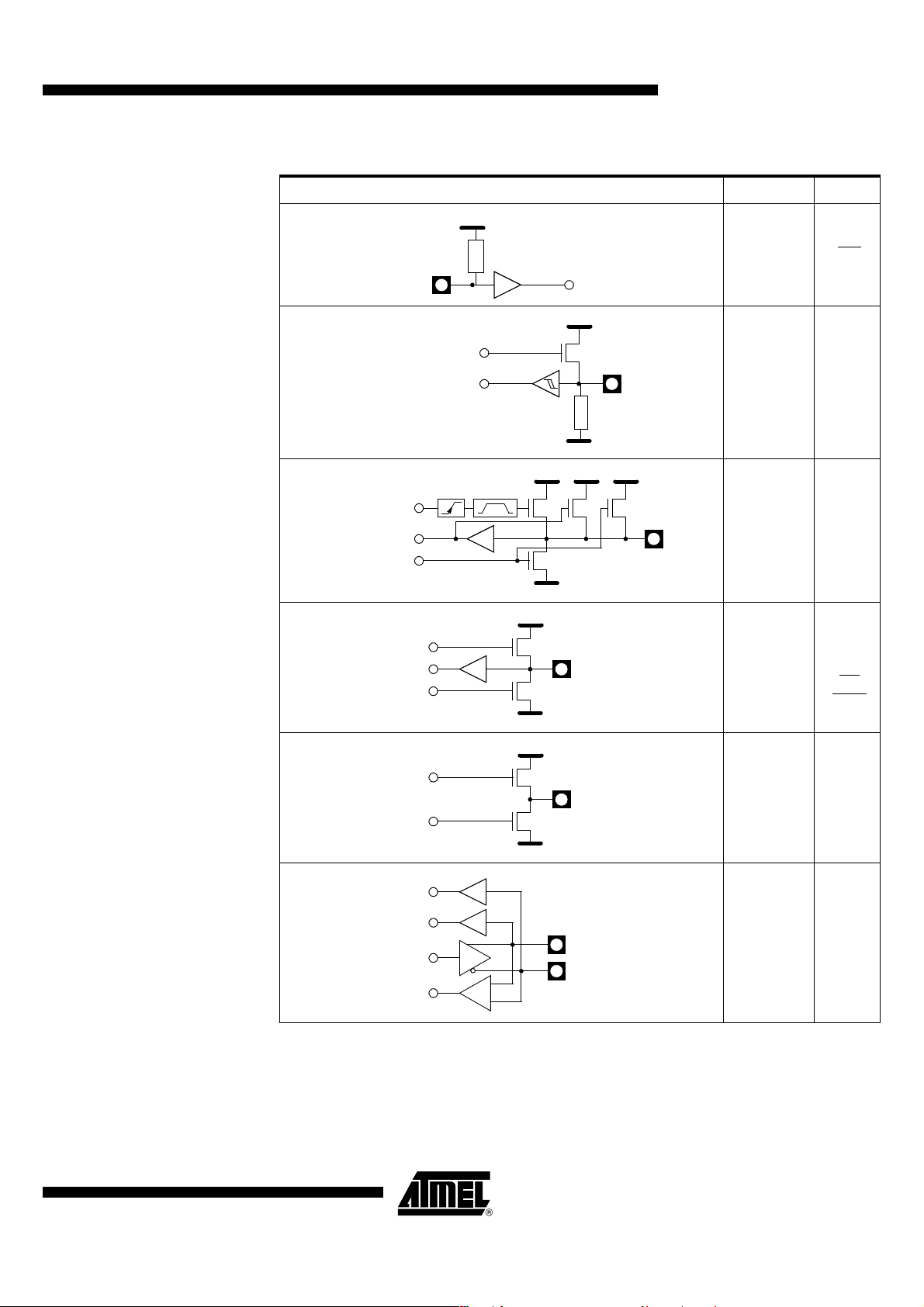

5.17 Internal Pin

Structure

Table 18. Detailed Internal Pin Structure

(1)

Circuit

VDD

TST

R

Watchdog Output

VDD VDD

P

1

N

VSS

Latch Output

2 osc

periods

Type Pins

Input TST

P

Input/Output RST

RST

R

VDD

(2)

P

P

3

2

Input/Output

P1

P2

(3)

P3

P4

P53:0

VDD

P0

P

Input/Output

N

VSS

VDD

MCMD

MDAT

ISP

PSEN

ALE

SCLK

P

N

VSS

D+

Output

Input/Output

DCLK

DOUT

DSEL

MCLK

D+

D-

D-

Notes: 1. For information on resistors value, input/output levels, and drive capability, refer to

the Section “DC Characteristics”, page 184.

2. When the Two Wire controller is enabled, P

, P2, and P3 transistors are disabled

1

allowing pseudo open-drain structure.

3. In Port 2, P1 transistor is continuously driven when outputting a high level bit address

(A15:8).

4109H–8051–01/05

11

AT8xC51SND1C

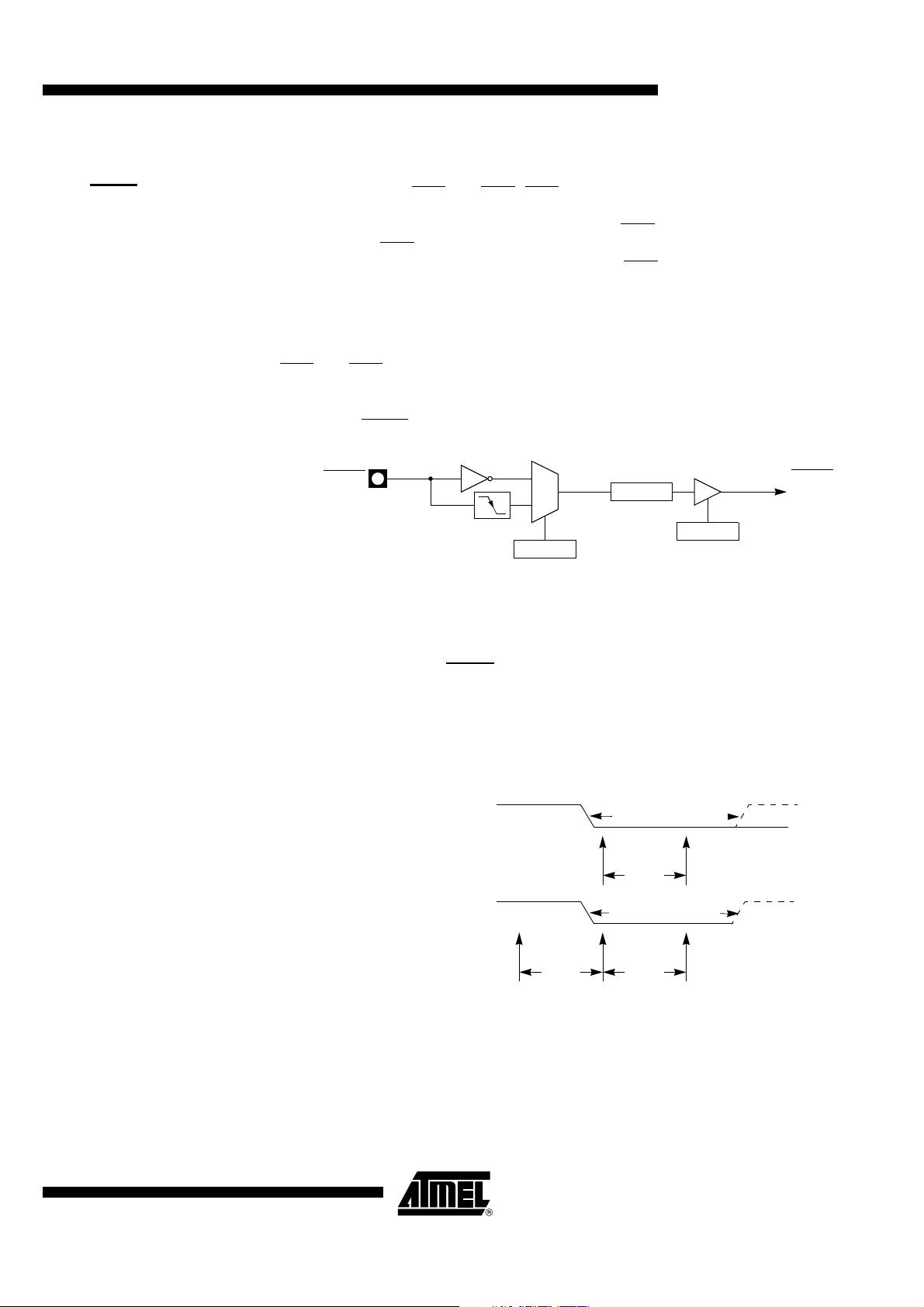

6. Clock Controller The AT8xC51SND1C clock controller is based on an on-chip osci llator feeding an on-

chip Phase Lock Loop (PLL). All internal clocks to the peripherals and CPU core are

generated by this controller.

6.1 Oscillator The AT8xC51SND1C X1 and X2 pins are the input and the output of a single -stage on-

chip inverter (see Figure 4) that can be configured with off-chip components such as a

Pierce oscillator (see Figure 5). Value of capacitors and crystal characteristics are

detailed in the Section “DC Characteristics”, page 163.

The oscillator outputs three different clocks: a clock for the PLL, a clock for the CPU

core, and a clock for the per ipherals as shown in Figu re 4. These clocks are either

enabled or disabled, de pendin g on th e power red uctio n mode as detailed in the sec tion

“Power Management” on page 48. The peripheral clock is used to generate the Timer 0,

Timer 1, MMC, ADC, SPI, and Port sampling clocks.

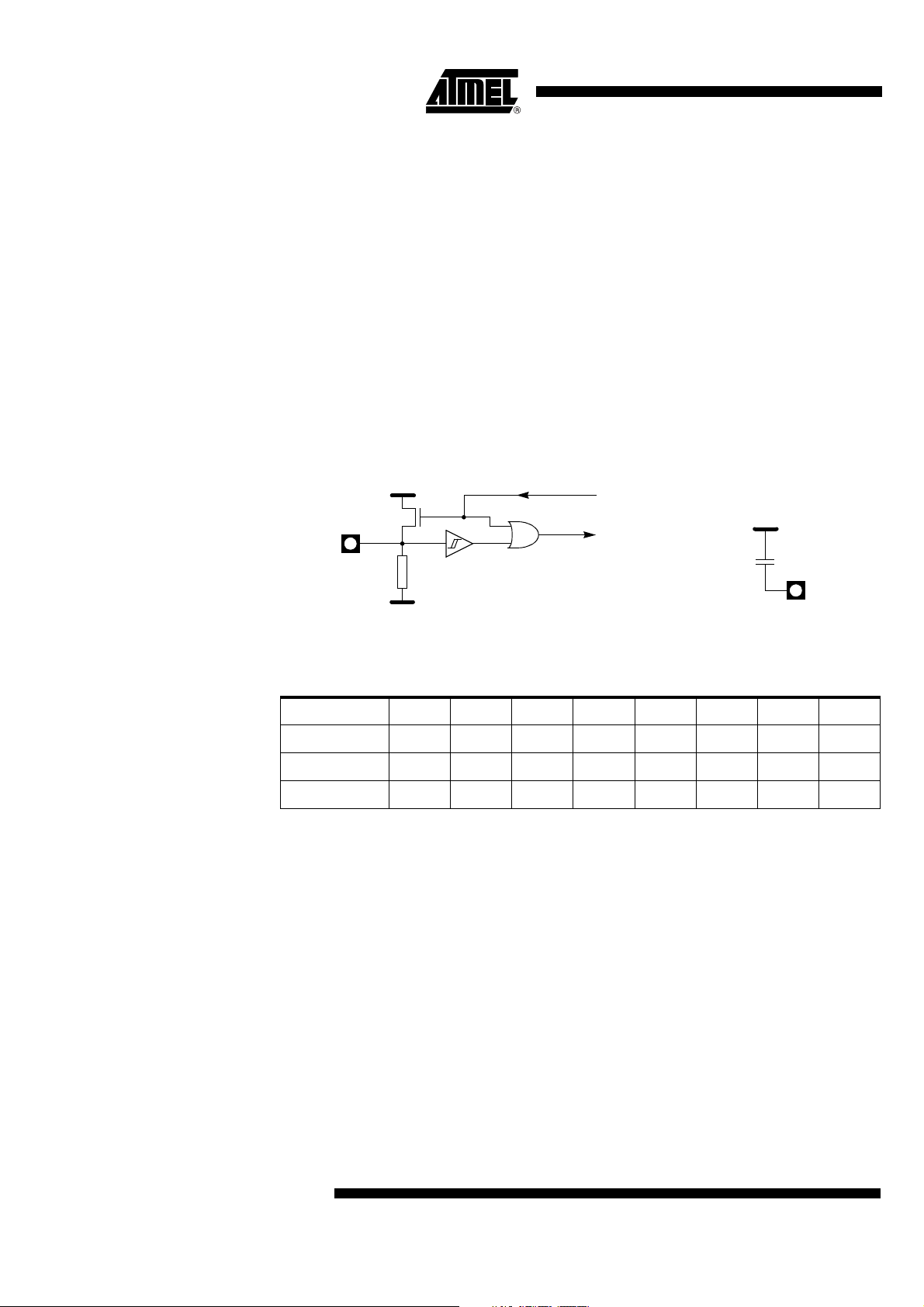

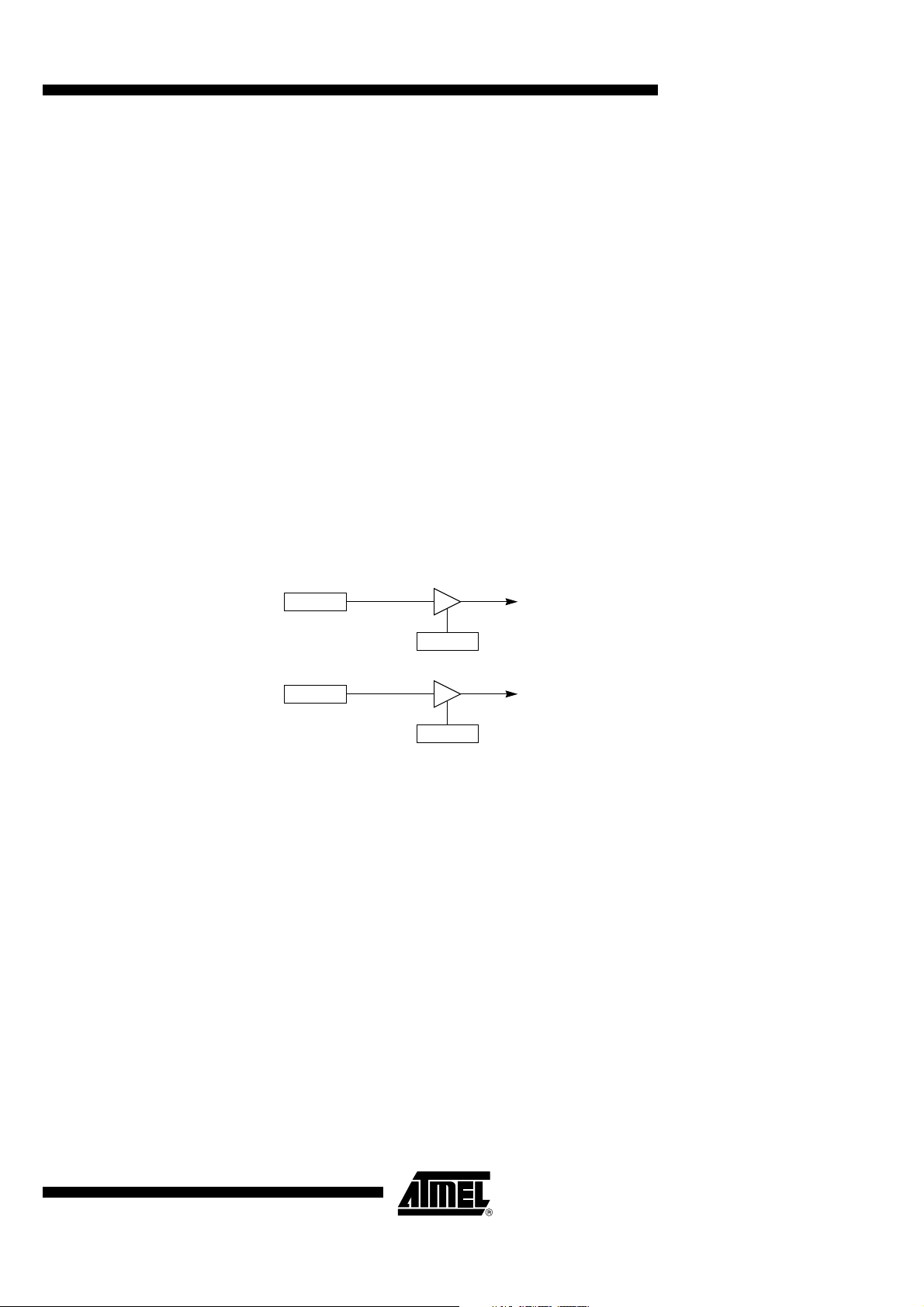

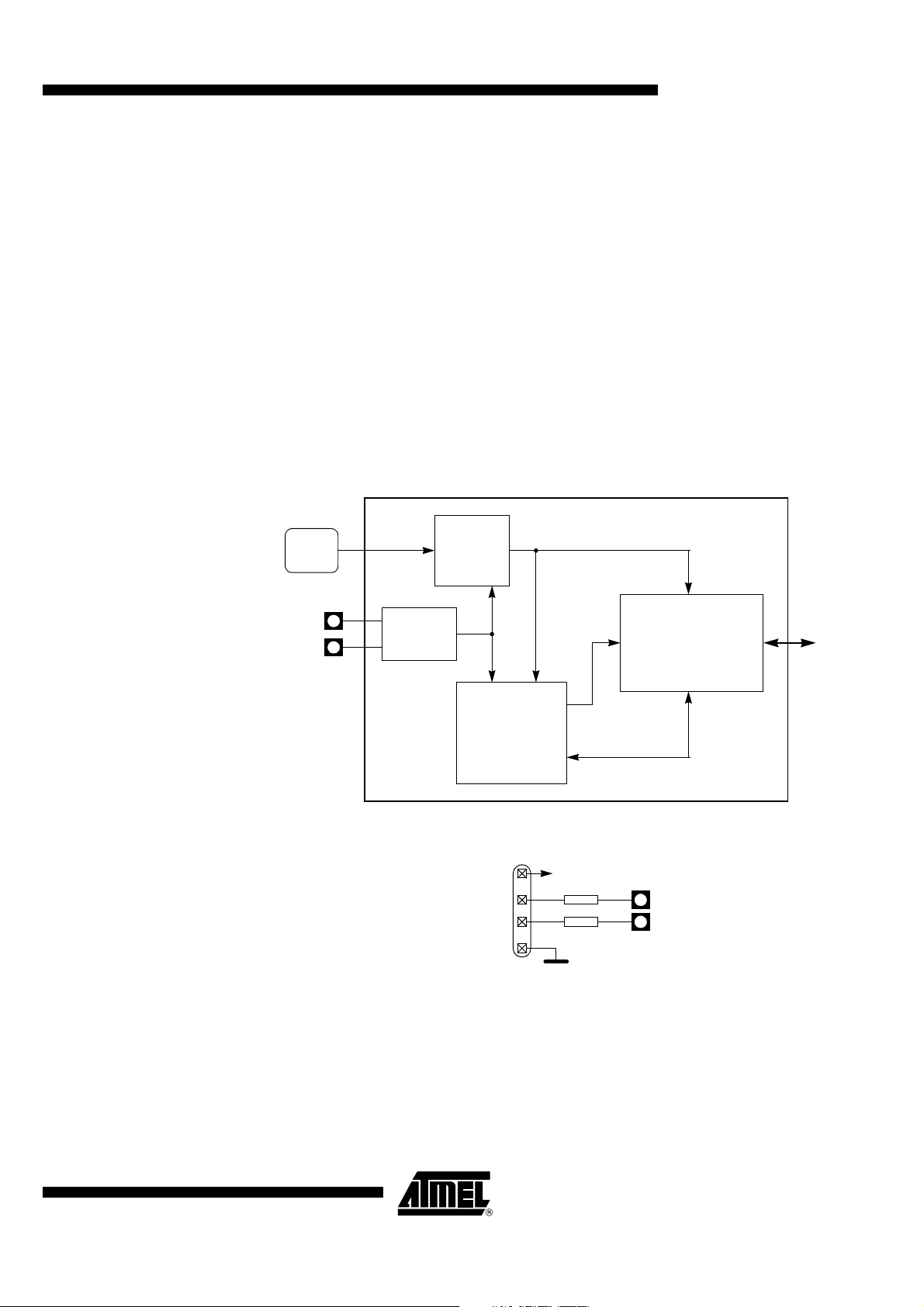

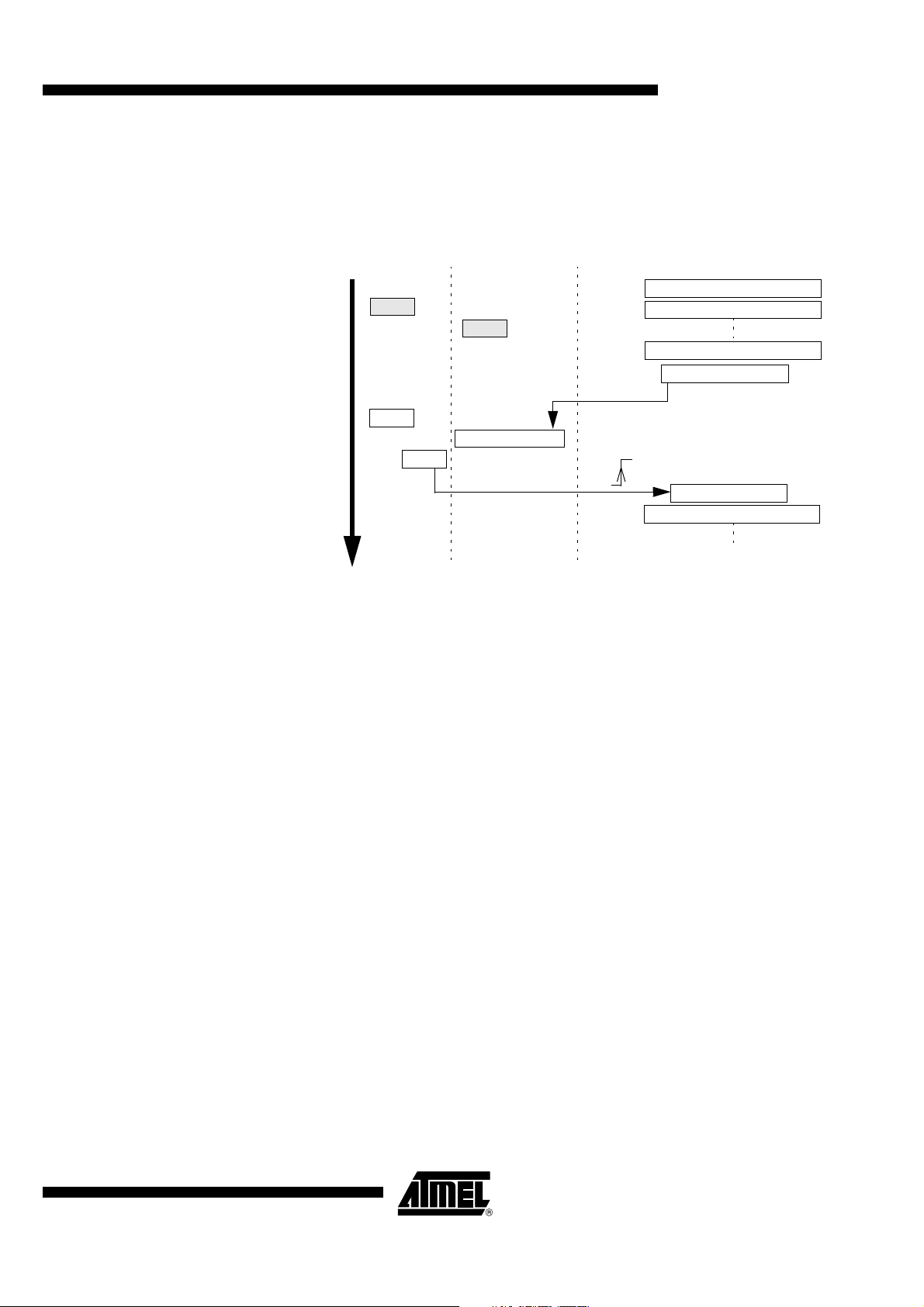

Figure 4. Oscillator Block Diagram and Symbol

CKCON.0

CPU

0

1

X2

Peripheral

Clock

CPU Core

Clock

IDL

PCON.0

Oscillator

Clock

OSC

CLOCK

Oscillator Clock Symbol

X1

X2

PD

PCON.1

PER

CLOCK

Peripheral Clock Symbol

÷ 2

CLOCK

CPU Core Clock Symbol

Figure 5. Crystal Connection

X1

C1

Q

C2

VSS

X2

6.2 X2 Feature Unlike standard C51 products that require 12 oscillator clock periods per machine cycle,

the AT8xC51SND1C need only 6 oscillator clock periods per machine cycle. This feature called the “X2 feature” can be enabled using the X2 bit

and allows the AT8x C51SND1C to operate in 6 or 12 oscillator cloc k periods per

machine cycle. As shown in Figure 4, both CPU and peripheral clocks are affected by

this feature. Figure 6 shows the X2 mode switching waveforms. After reset the standard

mode is activated. In standard mode the CPU and peripheral clock frequency is the

oscillator frequency divided by 2 while in X2 mode, it is the oscillator frequency.

(1)

in CKCON (see Table 5)

12

Note: 1. The X2 bit reset value depends on the X2B bit in the Hardware Security Byte (see

Table 12 on page 24). Using the AT89C51SND1C (Flash Version) the system can

boot either in standard or X2 mode depending on the X2B value. Using AT83SND1C

(ROM Version) the system always boots in standard mode. X2B bit can be changed

to X2 mode later by software.

4109H–8051–01/05

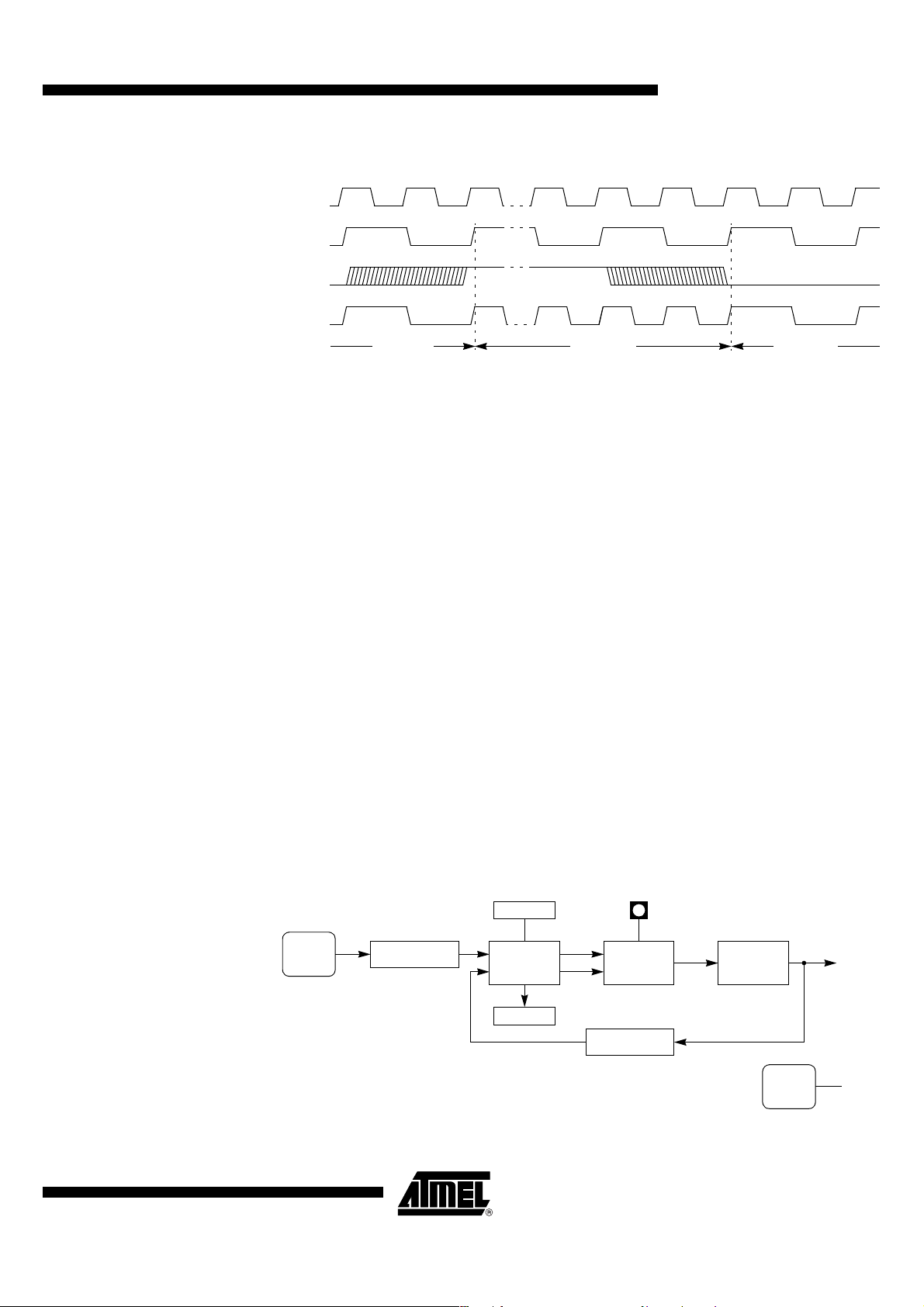

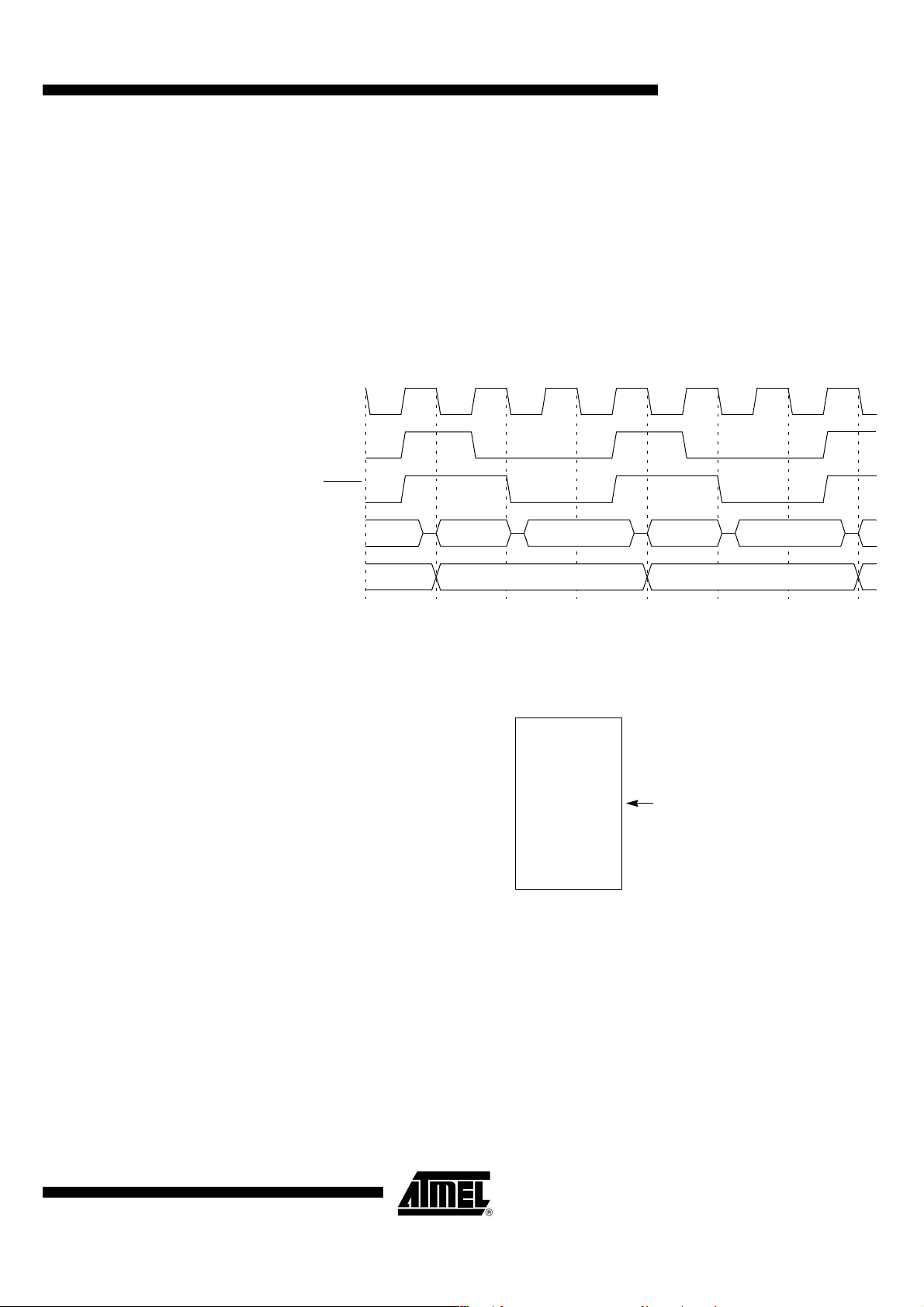

Figure 6. Mode Switching Waveforms

k

X1

X1 ÷ 2

X2 Bit

Clock

AT8xC51SND1C

STD Mode STD Mode

Note: 1. In order to prevent any incorrect operation while operating in X2 mode, user must be

aware that all peripherals using clock frequency as time reference (timers, etc.) will

have their time reference divided by 2. For example, a free running timer generating

an interrupt every 20 ms will then generate an interrupt every 10 ms.

X2 Mode

(1)

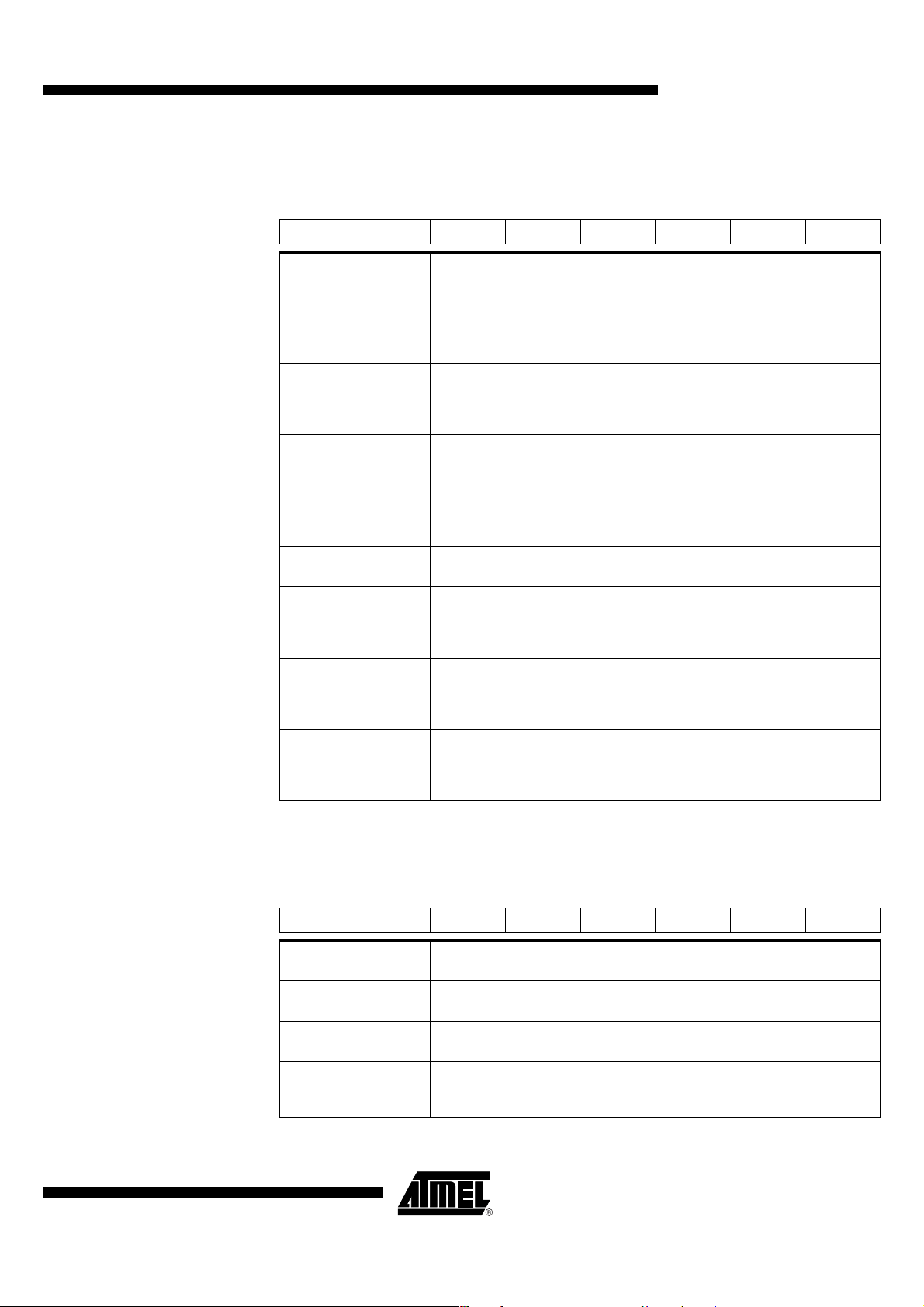

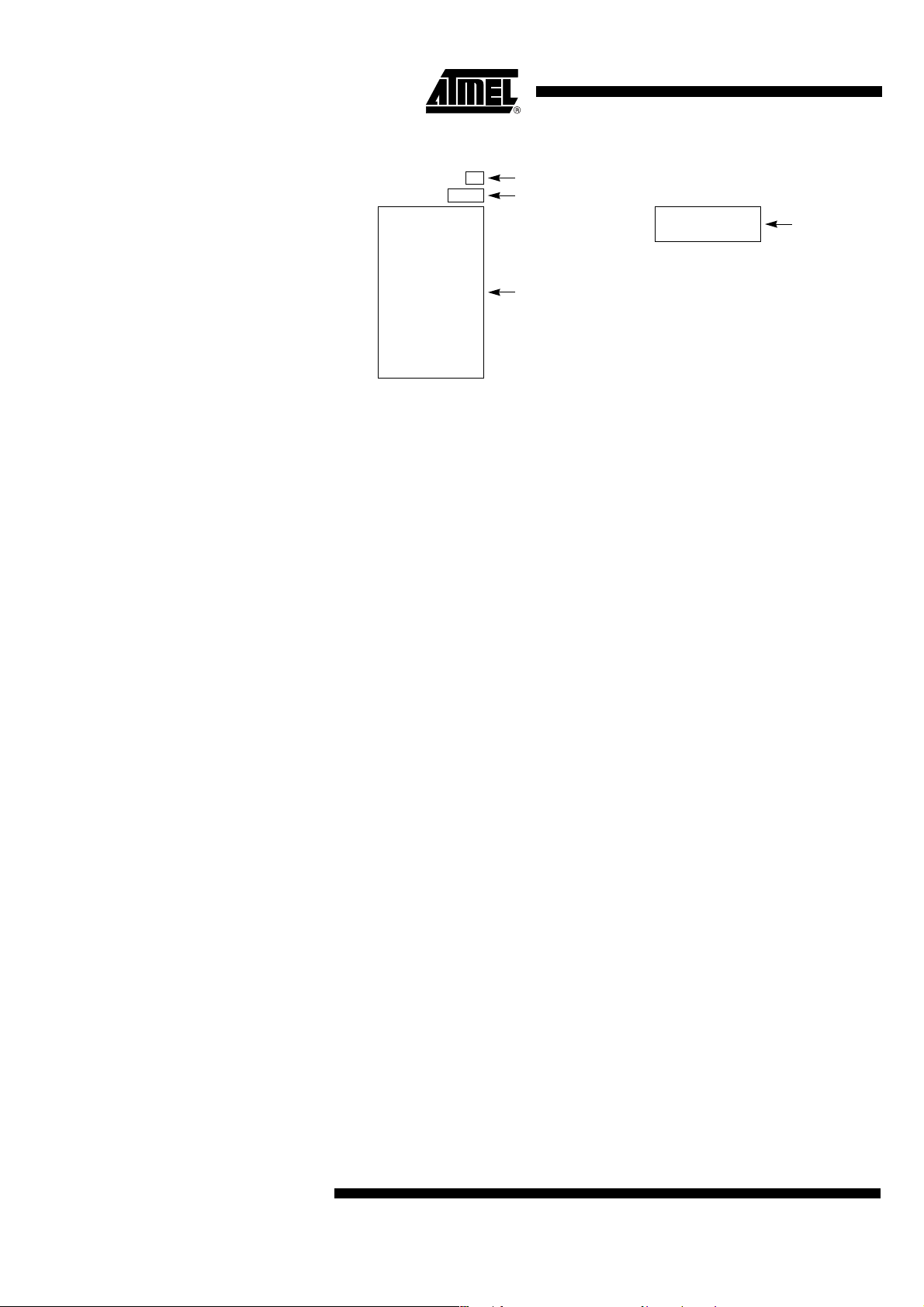

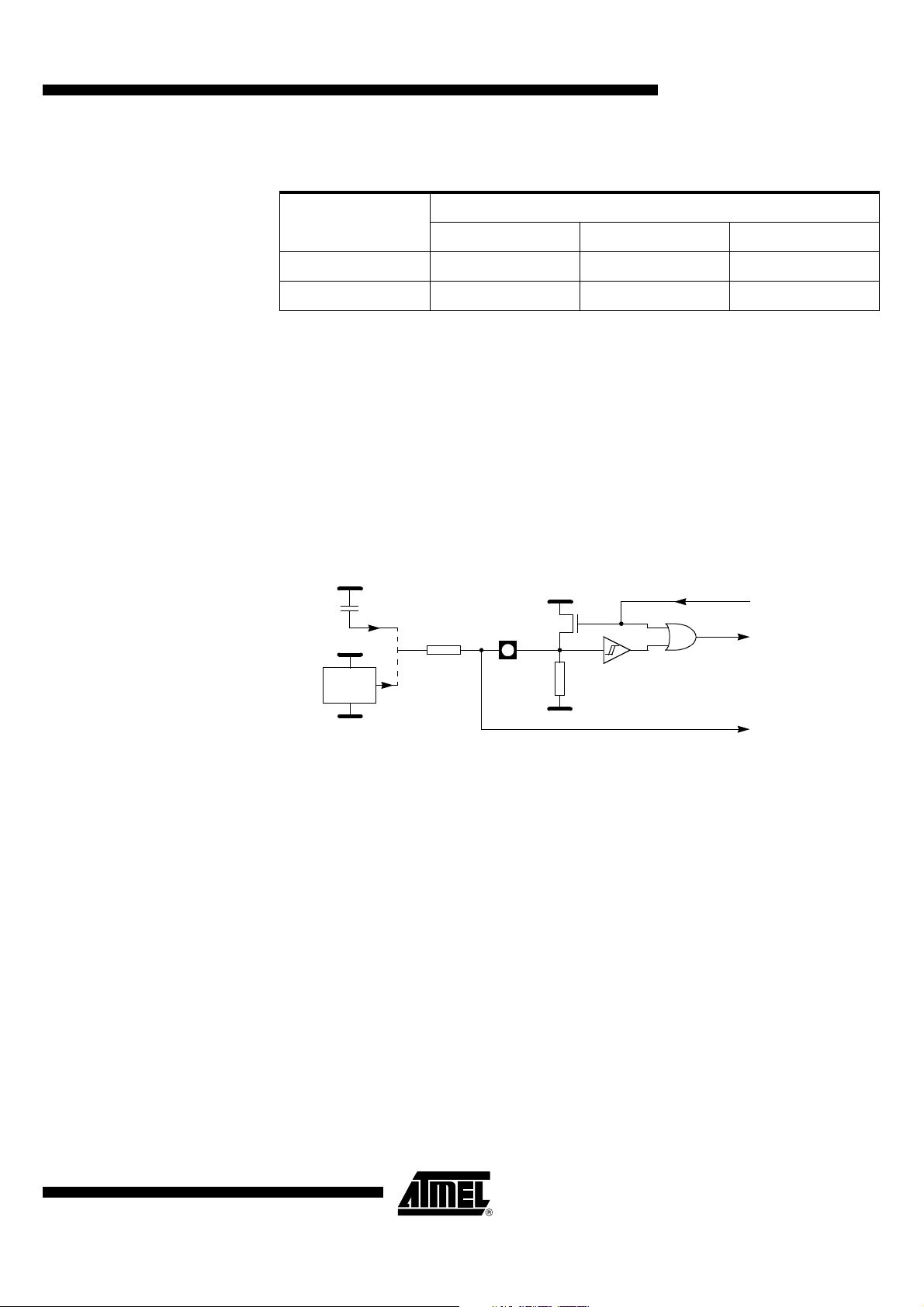

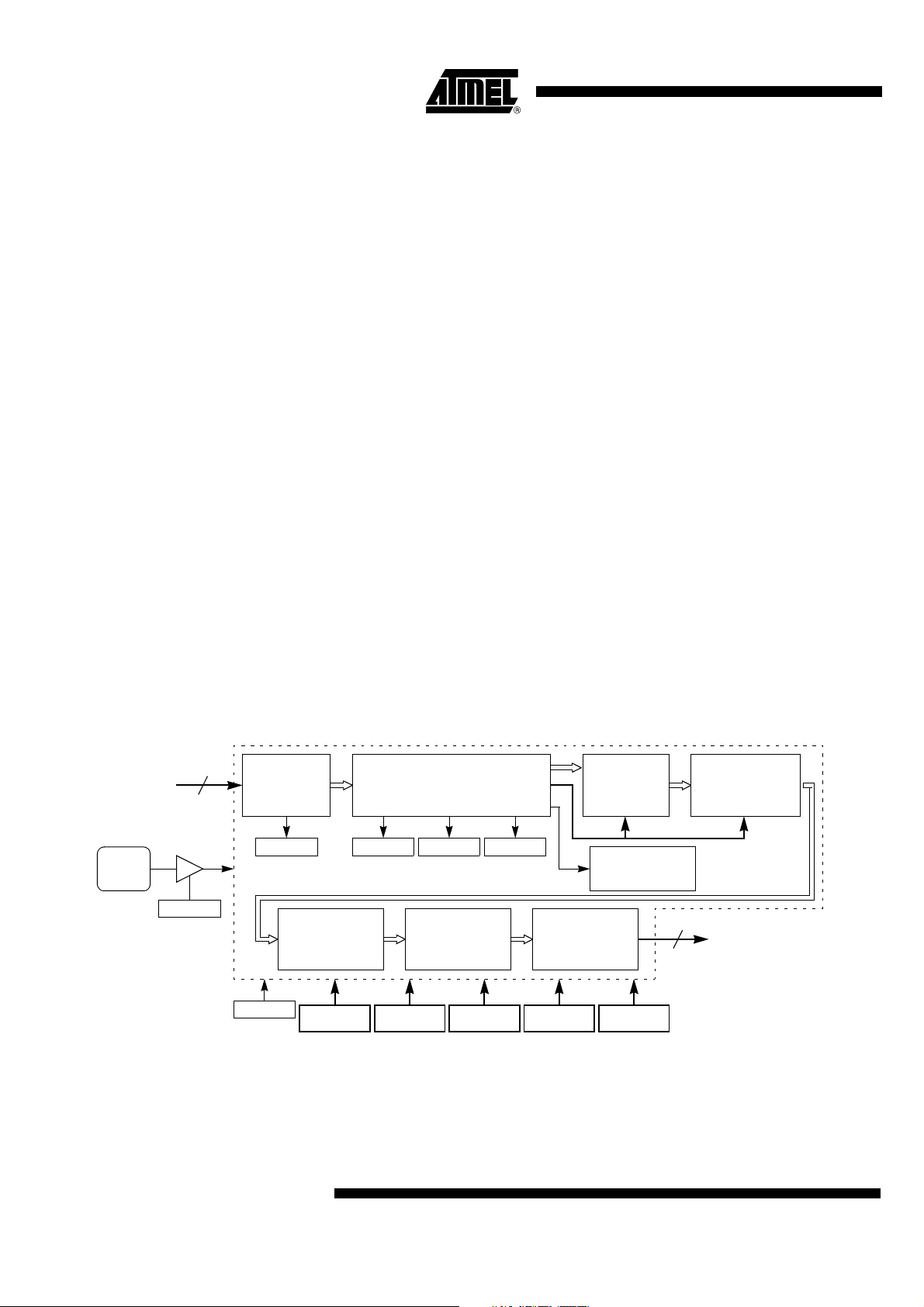

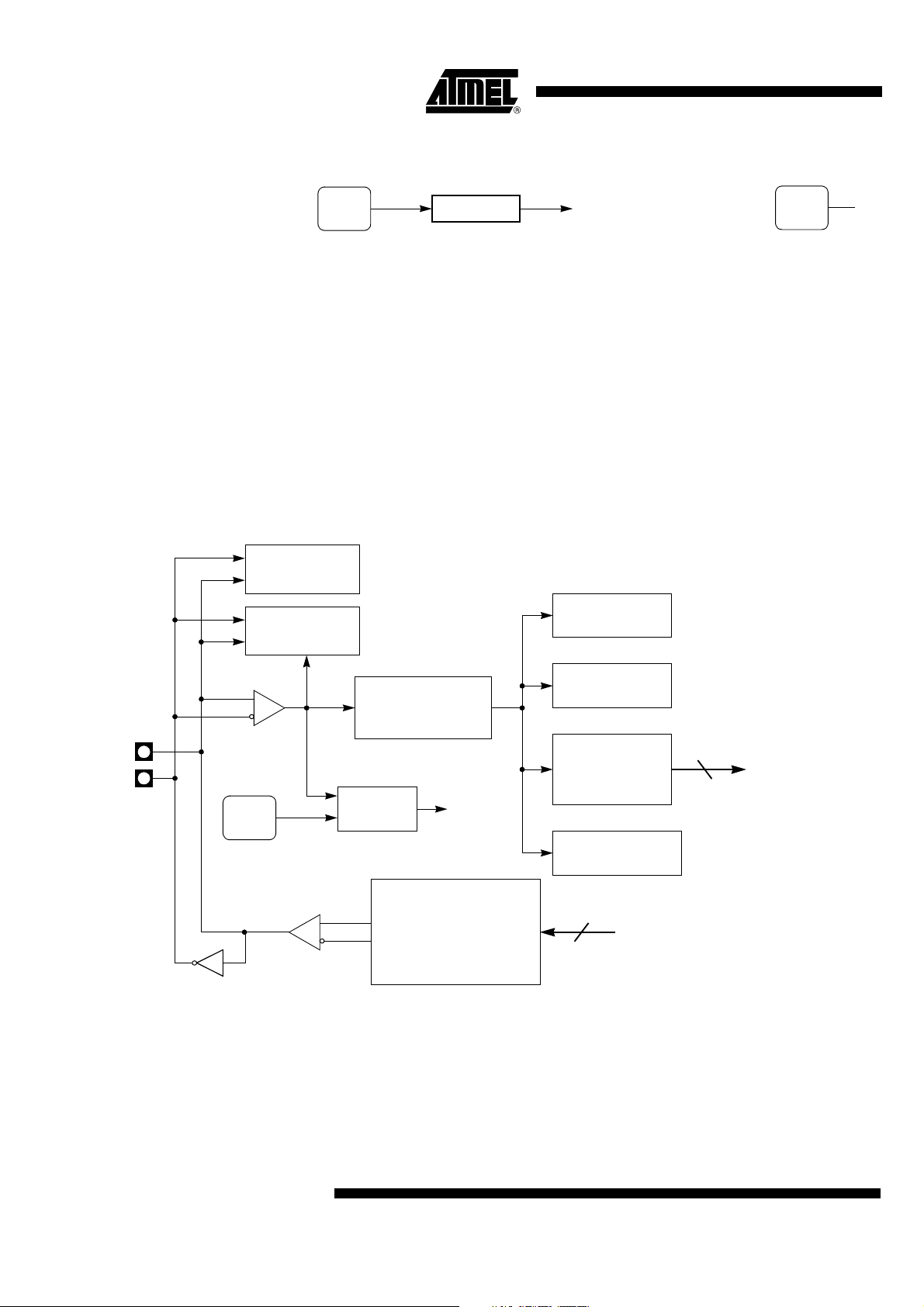

6.3 PLL

6.3.1 PLL Description The AT8xC51SND1C PLL is us ed to generate internal hi gh frequency clo ck (the PLL

Clock) synchronized with an ex ternal low-frequency (the O scillator Clock). The P LL

clock provides the MP3 decoder, the audi o interface, and the USB interface cl ocks.

Figure 7 shows the internal structure of the PLL.

The PFLD block is the Phase Frequency Comparator and Lock Detector. This block

makes the comparison between the reference clock coming from the N divider and the

reverse clock coming from the R divider and generates some pulses on the Up or Down

signal dependin g on the edge posi tion of the r everse c lock. The P LLEN bit in PLLCO N

register is used to enab le the c lock gene ratio n. When the PLL is l ocked, th e bit PL OCK

in PLLCON register (see Table 6) is set.

The CHP block is the Charge Pump that generates the voltage reference for the VCO by

injecting or extracting charges from the exter nal filte r connected on PFILT pin (see

Figure 8) . Value of the filter components are detailed in the Section “DC

Characteristics”.

4109H–8051–01/05

The VCO block is the Voltage Controlled Oscillator controlled by the voltage V

duced by the charge pump. It generates a square wave signal: the PLL clock.

Figure 7. PLL Block Diagram and Symbol

PFILT

R divider

R9:0

CHP

Vref

VCO

PLL

CLOCK

PLL Clock Symbol

OSC

CLOCK

N divider

N6:0

PLLclk

PLLCON.1

PLLEN

Up

PFLD

Down

PLOCK

PLLCON.0

OSCclk R 1+()

-----------------------------------------------=

×

N1+

ref

PLL

Cloc

pro-

13

AT8xC51SND1C

Figure 8. PLL Filter Connection

FILT

R

C1

VSS

C2

VSS

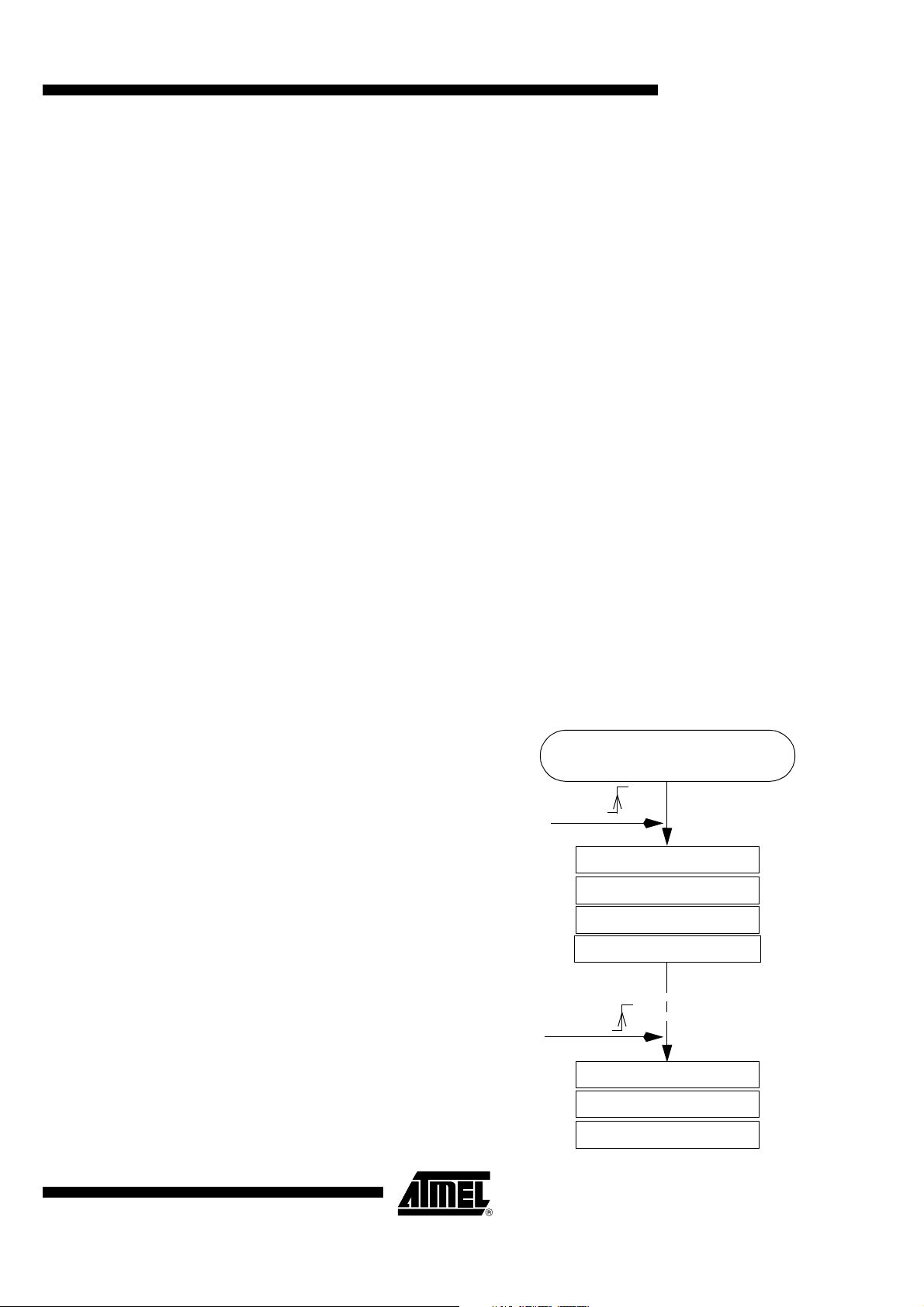

6.3.2 PLL Programming The PLL is progra mmed u sing the flo w sho wn in Figure 9. As s oon as c lock g enera tion

is enabled, the user must wait until the lo ck indic ator is set to ens ure the cl ock output is

stable. The PLL clock fr equenc y will dep end on MP 3 deco der cloc k and au dio int erfac e

clock frequencies.

Figure 9. PLL Programming Flow

PLL

Programming

Configure Dividers

N6:0 = xxxxxxb

R9:0 = xxxxxxxxxxb

Enable PLL

PLLRES = 0

PLLEN = 1

PLL Locked?

PLOCK = 1?

14

4109H–8051–01/05

6.4 Registers Table 5. CKCON Register

CKCON (S:8Fh) – Clock Control Register

76543210

TWIX2 WDX2 - SIX2 - T1X2 T0X2 X2

AT8xC51SND1C

Bit

Number

7TWIX2

6WDX2

5-

4SIX2

3-

2T1X2

1T0X2

0X2

Bit

Mnemonic Description

Two-Wire Clock Control Bit

Set to select the oscillator clock divided by 2 as TWI clock input (X2

independent).

Clear to select the peripheral clock as TWI clock input (X2 dependent).

Watchdog Clock Control Bit

Set to select the oscillator clock divided by 2 as watchdog clock input (X2

independent).

Clear to select the peripheral clock as watchdog clock input (X2 dependent).

Reserved

The values read from this bit is indeterminate. Do not set this bit.

Enhanced UART Clock (Mode 0 and 2) Control Bit

Set to select the oscillator clock divided by 2 as UART clock input (X2

independent).

Clear to select the peripheral clock as UART clock input (X2 dependent)..

Reserved

The values read from this bit is indeterminate. Do not set this bit.

Timer 1 Clock Control Bit

Set to select the oscillator clock divided by 2 as timer 1 clock input (X2

independent).

Clear to select the peripheral clock as timer 1 clock input (X2 dependent).

Timer 0 Clock Control Bit

Set to select the oscillator clock divided by 2 as timer 0 clock input (X2

independent).

Clear to select the peripheral clock as timer 0 clock input (X2 dependent).

System Clock Control Bit

= F

= F

PER

OSC

=

Clear to select 12 clock periods per ma chine cycle (STD m ode, F

/2).

F

OSC

Set to select 6 clock periods per machine cycle (X2 mode, F

CPU

= F

CPU

PER

).

4109H–8051–01/05

Reset Value = 0000 000Xb (AT89C51SND1C) or 0000 0000b (AT83SND1C)

Table 6. PLLCON Register

PLLCON (S:E9h) – PLL Control Register

76543210

R1 R0 - - PLLRES - PLLEN PLOCK

Bit

Number

7 - 6 R1:0

5 - 4 -

3 PLLRES

Bit

Mnemonic Description

PLL Least Significant Bits R Divider

2 LSB of the 10-bit R divider.

Reserved

The values read from these bits are always 0. Do not set these bits.

PLL Reset Bit

Set this bit to r e set the PLL.

Clear this bit to free the PLL and allow enabling.

15

AT8xC51SND1C

Bit

Number

2-

1 PLLEN

0PLOCK

Bit

Mnemonic Description

Reserved

The value read from this bit is always 0. Do not set this bit.

PLL Enable Bit

Set to enable the PLL.

Clear to disable the PLL.

PLL Lock Indicator

Set by hardware when PLL is locked.

Clear by hardware when PLL is unlocked.

Reset Value = 0000 1000b

Table 7. PLLNDIV Register

PLLNDIV (S:EEh) – PLL N Divider Register

76543210

- N6N5N4N3N2N1N0

Bit

Number

7-

6 - 0 N6:0

Bit

Mnemonic Description

Reserved

The value read from this bit is always 0. Do not set this bit.

PLL N Divider

7 - bit N divider.

Reset Value = 0000 0000b

Table 8. PLLRDIV Register

PLLRDIV (S:EFh) – PLL R Divider Register

76543210

R9 R8 R7 R6 R5 R4 R3 R2

Bit

Number

7 - 0 R9:2

Bit

Mnemonic Description

PLL Most Significant Bits R Divider

8 MSB of the 10-bit R divider.

Reset Value = 0000 0000b

16

4109H–8051–01/05

AT8xC51SND1C

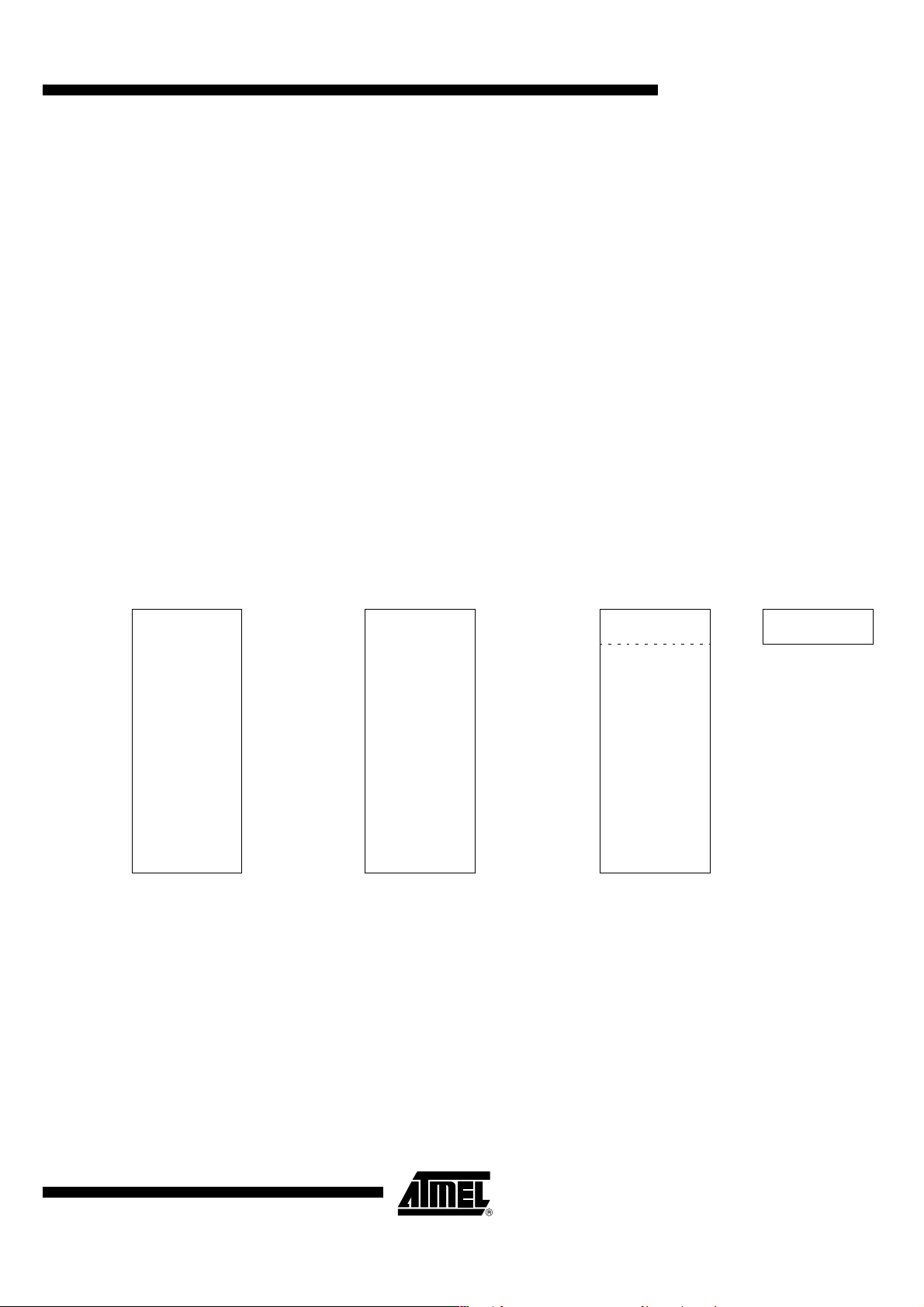

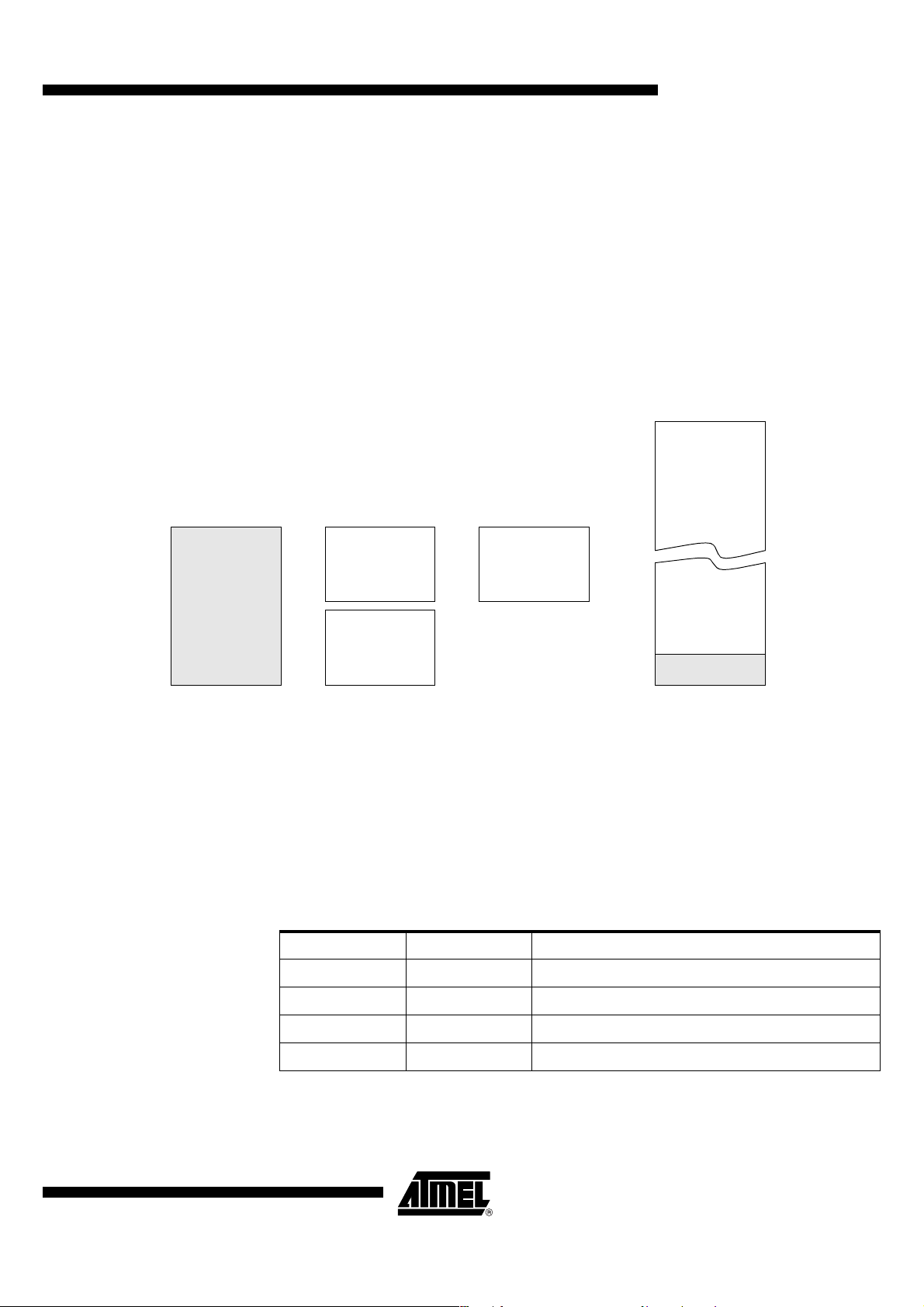

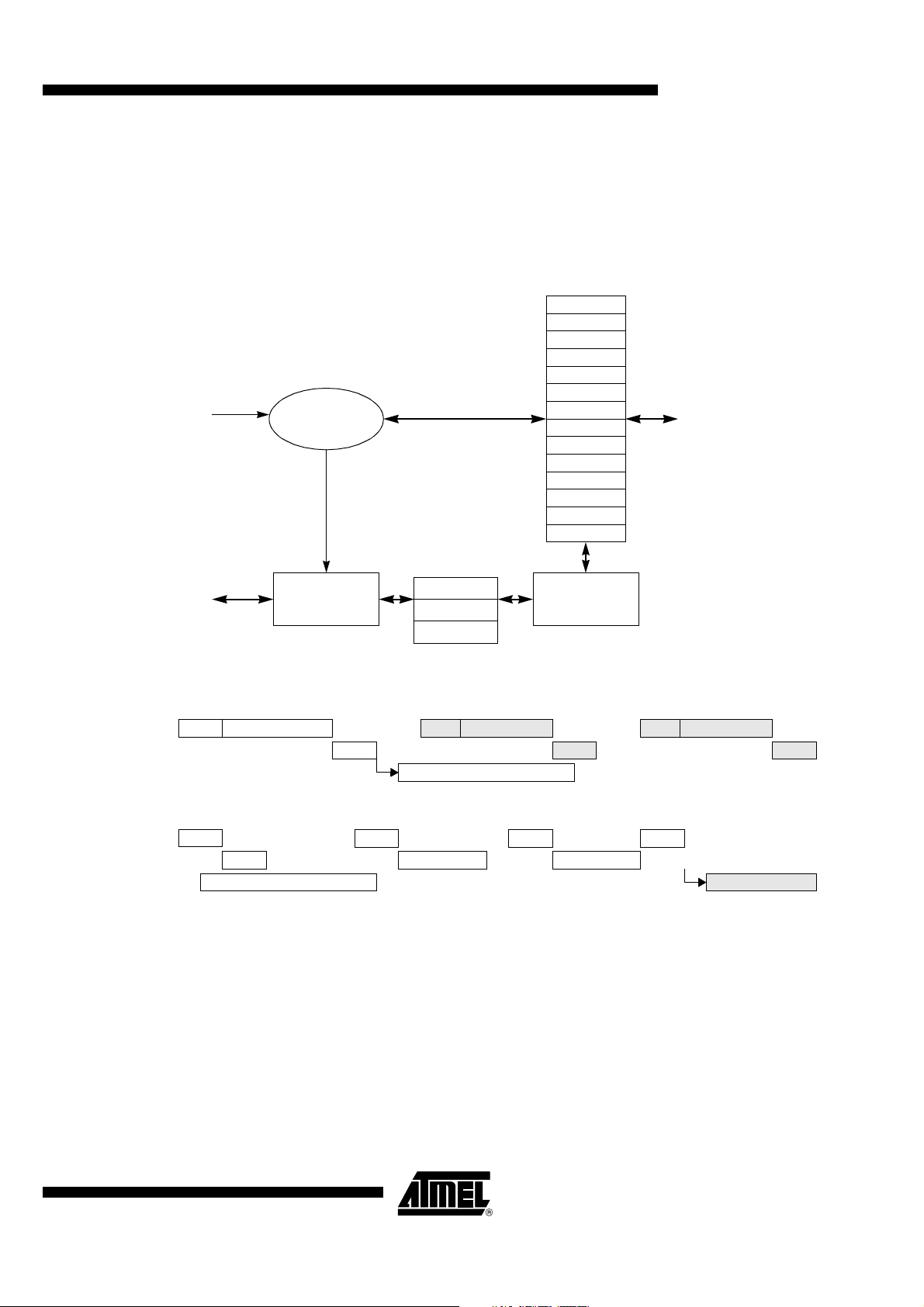

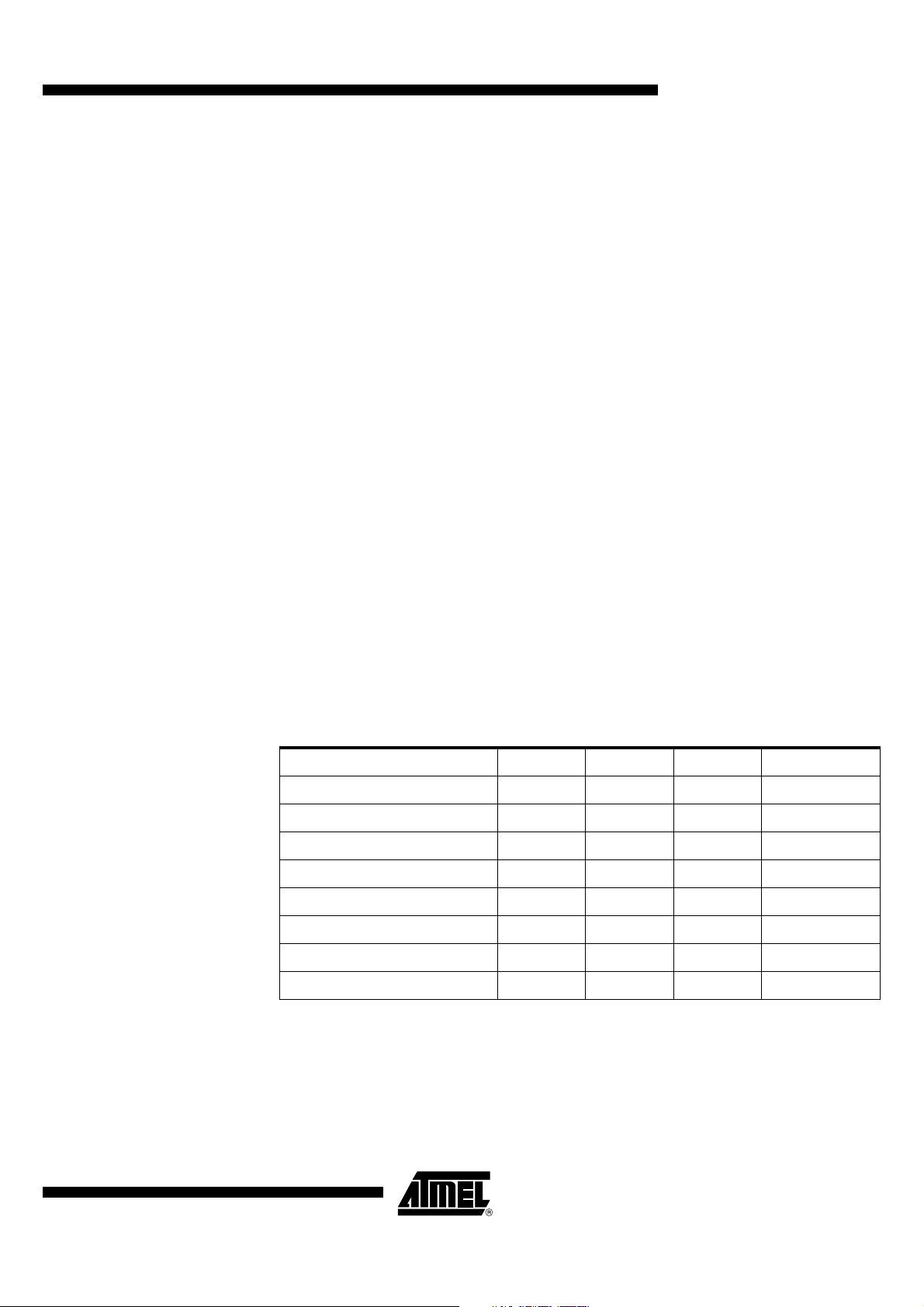

7. Program/Code

Memory

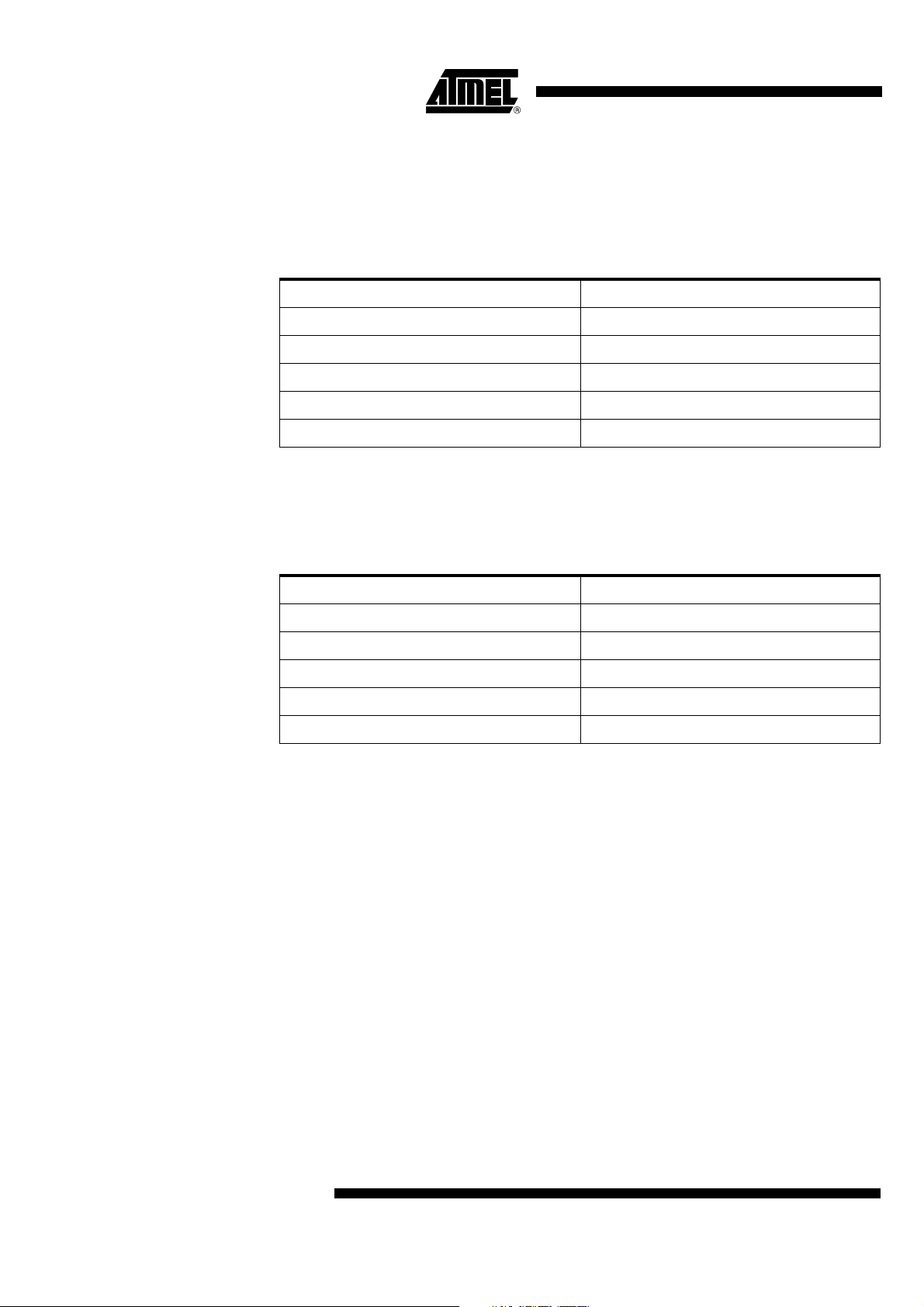

The AT8xC51SND1C execute up to 64K Bytes of program/code memory. Figure 10

shows the split of internal and external program/code memory spaces depending on the

product.

The AT83SND1C pr odu ct prov id es the i ntern al program/code memor y i n ROM memory

while the AT89C51SND1C product provides it in Flash memory. These 2 products do

not allow external code memory executio n. External code memory execution is

achieved using the AT80C51SND1C product which does not provide any internal program/code memory.

The Flash memory increa ses EP ROM and ROM func tional ity by in-cir cui t electric al erasure and programming. The high voltage needed for programming or erasing Flash cells

is generated on-chip using the standard V

charge pump. Thus, the AT89C51SND1C can be programmed using only one voltage

and allows In-application software programming. Hardware programming mode is also

available using common programming tools. See the application note ‘Programming

T89C51x and AT89C51x with Device Programmers’.

The AT89C51SND1C implements an additional 4K Bytes of on-chip boot Flash memory

provided in Fla sh memor y. Thi s bo ot memo ry is deli vered p rogr ammed with a stand ard

boot loader so ftware allowi ng In-System Programm ing (ISP). It also con tains som e

Application Prog rammin g Interface r outines named API ro utines allo wing In Appl icatio n

Programming (IAP) by using user’s own boot loader.

Figure 10. Program/Code Memory Organization

voltage, made possible by the internal

DD

FFFFh

0000h

AT80C51SND1C

64K Bytes

External Code

FFFFh

0000h

64K Bytes

Code ROM

AT83SND1C

FFFFh

F000h

0000h

AT89C51SND1C

64K Bytes

Code Flash

FFFFh

F000h

4K Bytes

Boot Flash

4109H–8051–01/05

17

AT8xC51SND1C

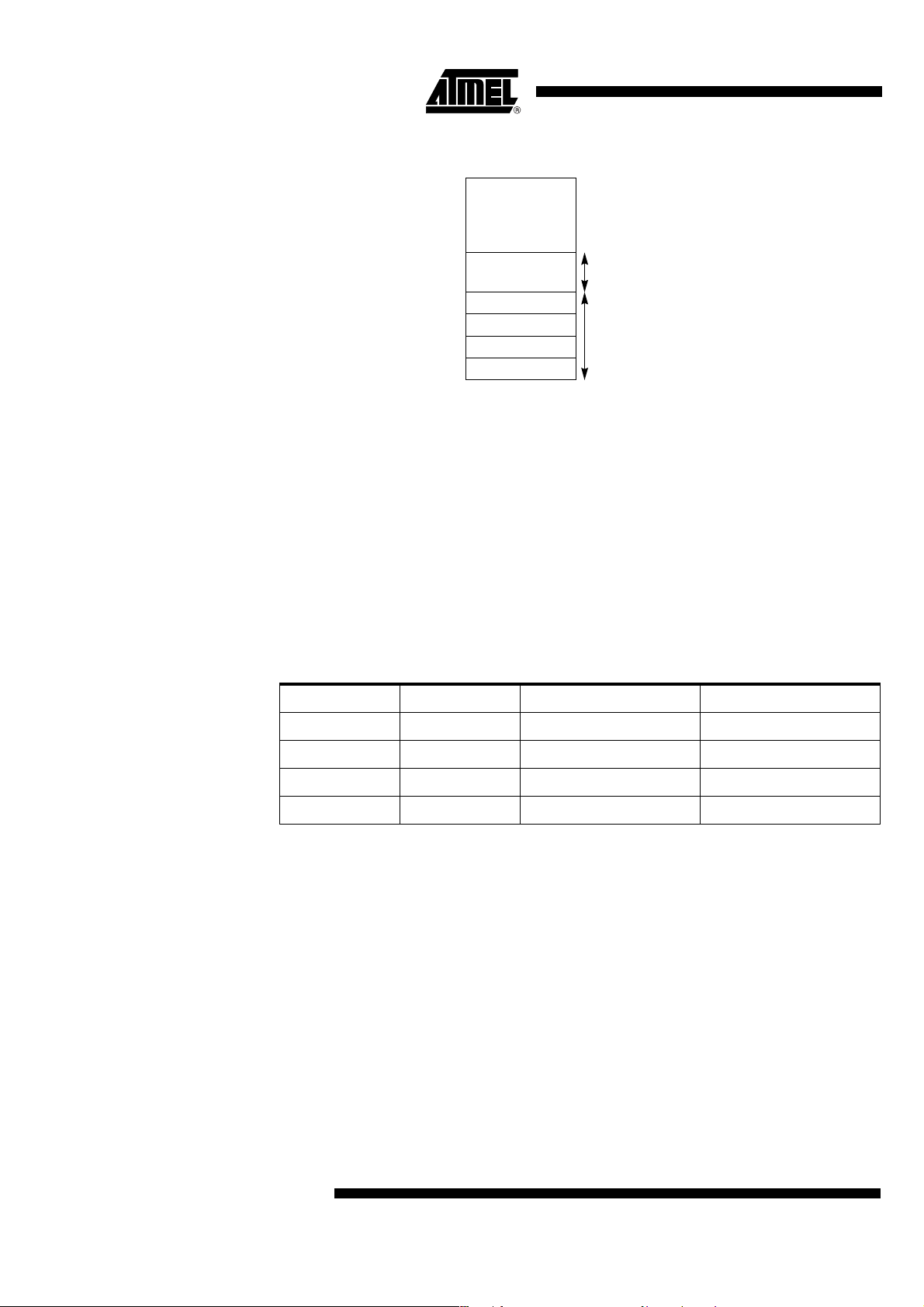

7.1 ROMLESS Memory

r

Architecture

As shown in Figure 11 the AT80C51SND1C external memory is composed of one

space detailed in the following paragraph.

Figure 11. AT80C51SND1C Memory Architecture

FFFFh

64K Bytes

Use

External Memory

0000h

7.1.1 User Space This space is composed of a 64K By tes co de (Fla sh, EE PROM, EP ROM…) me mory . It

contains the user’s application code.

7.1.2 Memory Interface The external memory interface comprises the external bus (port 0 and port 2) as well as

the bus control signals (PSEN

, and ALE).

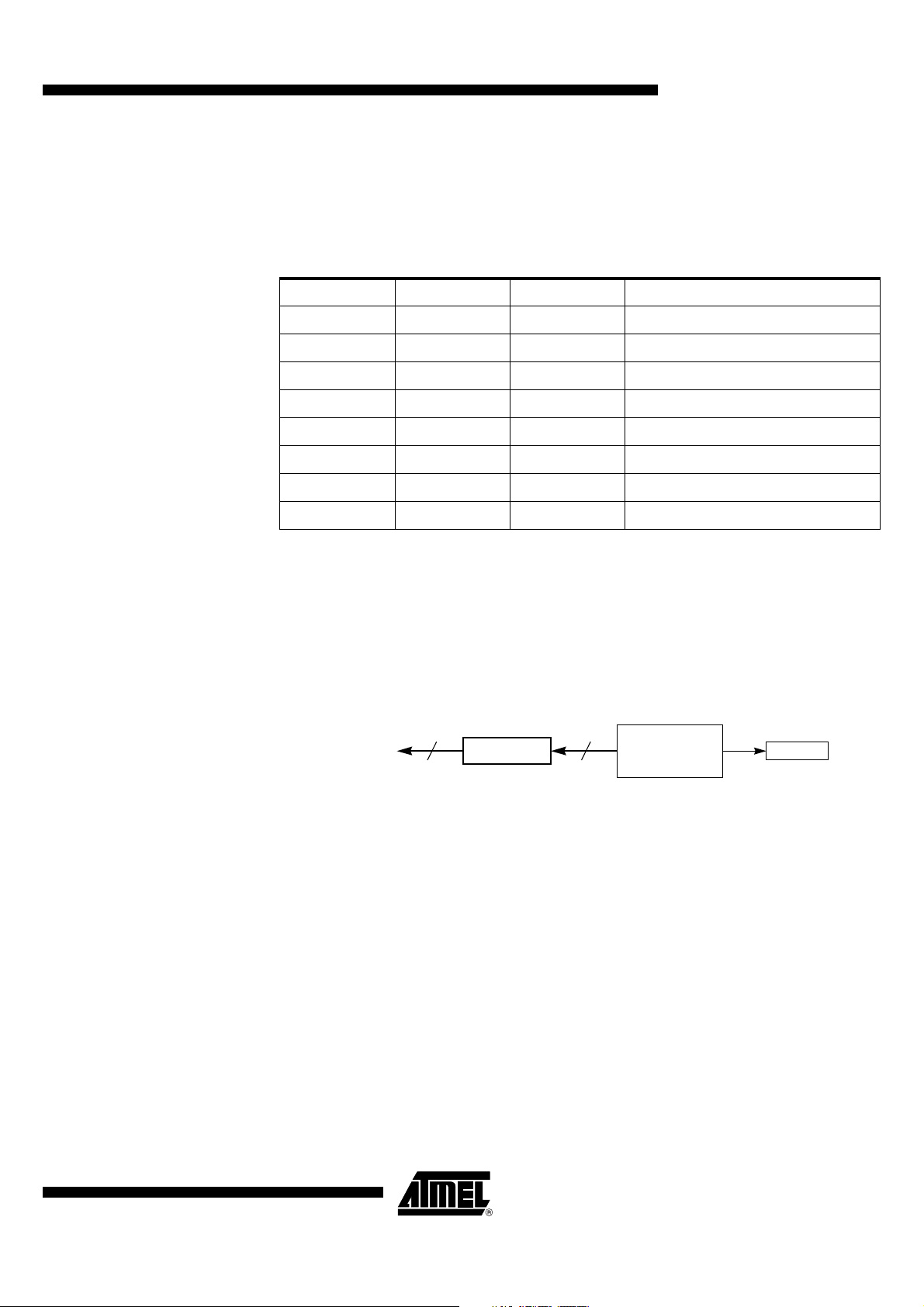

Figure 12 s hows the structure of the external address bus. P0 carries address A7:0

while P2 carries address A15:8. Data D7:0 is multiplexed with A7:0 on P0. Table 12

describes the external memory interface signals.

Figure 12. External Code Memory Interface Structure

AT80C51SND1C

AD7:0

A15:8

Latch

A7:0

P2

ALE

P0

Table 2. External Code Memory Interface Signals

Signal

Name Type Description

A15:8 O

AD7:0 I/O

ALE O

Address Lines

Upper address lines for the external bus.

Address/Data Lines

Multiplexed lower address lines and data for the external memory.

Address Latch Enable

ALE signals indicates that valid address information are available on lines

AD7:0.

Flash

EPROM

A15:8

A7:0

D7:0

OEPSEN

Alternate

Function

P2.7:0

P0.7:0

-

18

Program Store Enable Output (AT80C51SND1C Only)

O

PSEN

This signal is active low during external code fetch or external code read

(MOVC instruction).

4109H–8051–01/05

-

AT8xC51SND1C

7.2.1 External Bus Cycles This section describes the bus cycles th e A T8 0C5 1SN D1C e xe cu tes to f etc h c od e (se e

Figure 13) in the external program/code memory.

External memory cycle takes 6 CPU clock periods. This is equivalent to 12 oscillator

clock periods in standard mode or 6 oscillator clock periods in X2 mode. For further

information on X2 mode see section “Clock “.

For simplicity, the accompanying figure depicts the bus cycle waveforms in idealized

form and does not provide precise timing information.

For bus cycling parameters refer to the ‘AC-DC parameters’ section.

Figure 13. External Code Fetch Waveforms

CPU Clock

ALE

PSEN

7.3 ROM Memory

Architecture

P0

P2

D7:0

PCL

PCHPCH

As shown in Figure 14 the AT83SND1C ROM memory is composed of one space

detailed in the following paragraph.

PCLD7:0 D7:0

PCH

Figure 14. AT83SND1C Memory Architecture

FFFFh

64K Bytes

ROM Memory

0000h

User

7.3.1 User Space This space is composed of a 64K Bytes ROM memory programmed during the manufacturing process. It contains the user’s application code.

7.4 Flash Memory

Architecture

4109H–8051–01/05

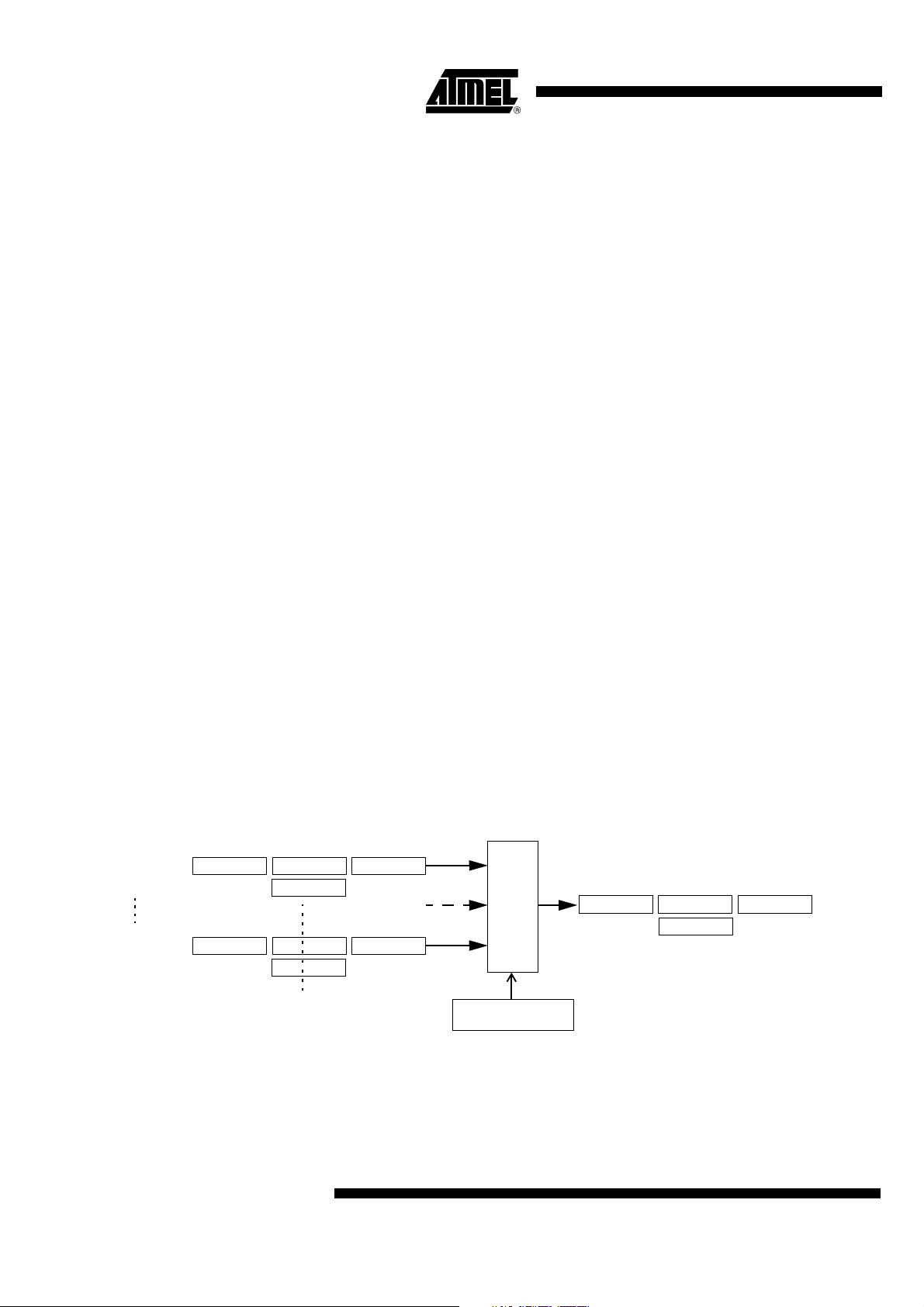

As shown in Figure 15 the AT89C51 SND1C Flas h memor y is compos ed of four spac es

detailed in the following paragraphs.

19

AT8xC51SND1C

Figure 15. AT89C51SND1C Memory Architecture

0000h

t

Hardware Security

FFFFh

64K Bytes

Flash Memory

Extra Row

User

FFFFh

F000h

4K Bytes

Flash Memory

Boo

7.4.1 User Space This space is composed of a 64K Bytes Flash memory organized in 512 pages of 128

Bytes. It contains the user’s application code.

This space can be read or written by both software and hardware modes.

7.4.2 Boot Space This space is composed of a 4K B ytes F l ash memory. It contains t he b oot lo ader f or InSystem Programming and the routines for In Application Programming.

This space can only be read or wr itt en by hardwa re mode using a par all el progr am min g

tool.

7.4.3 Hardware Security Space This space is composed of one Byte: the Hardware Security Byte (HSB see Table 12)

divided in 2 separ ate n ibble s. The MSN conta ins the X2 mo de con figur ation bit an d the

Boot Loader Jump Bit as detailed in Section “Boot Memory Execution”, page 21 and can

be written by software while the LS N co nta ins the l oc k system lev el to pro tec t the memory content against piracy as detailed in Section “Hardware Security System”, page 21

and can only be written by hardware.

7.4.4 Extra Row Space This space is composed of 2 Bytes:

• The Software Boot Vector (SBV, see Table 13).

This Byte is used by the software boot loader to build the boot address.

• The Software Security Byte (SSB, see Table 14).

This Byte is used to lock the execution of some boot loader commands.

20

4109H–8051–01/05

AT8xC51SND1C

7.5 Hardware Security

System

7.7 Boot Memory

Execution

The AT89C51SND1C implem ents three lock bits LB2:0 in the LSN of HSB ( see

Table 12) providing three lev els of secur ity for us er’s p rogr am as descr ibed in Tabl e 12

while the A T83SND1C is always set in read disabled mode.

Level 0 is the level of an erased part and does not enable any security feature.

Level 1 locks the hardware programming of both user and boot memories.

Level 2 locks also hardware verifying of both user and boot memories

Level 3 locks also the external execution.

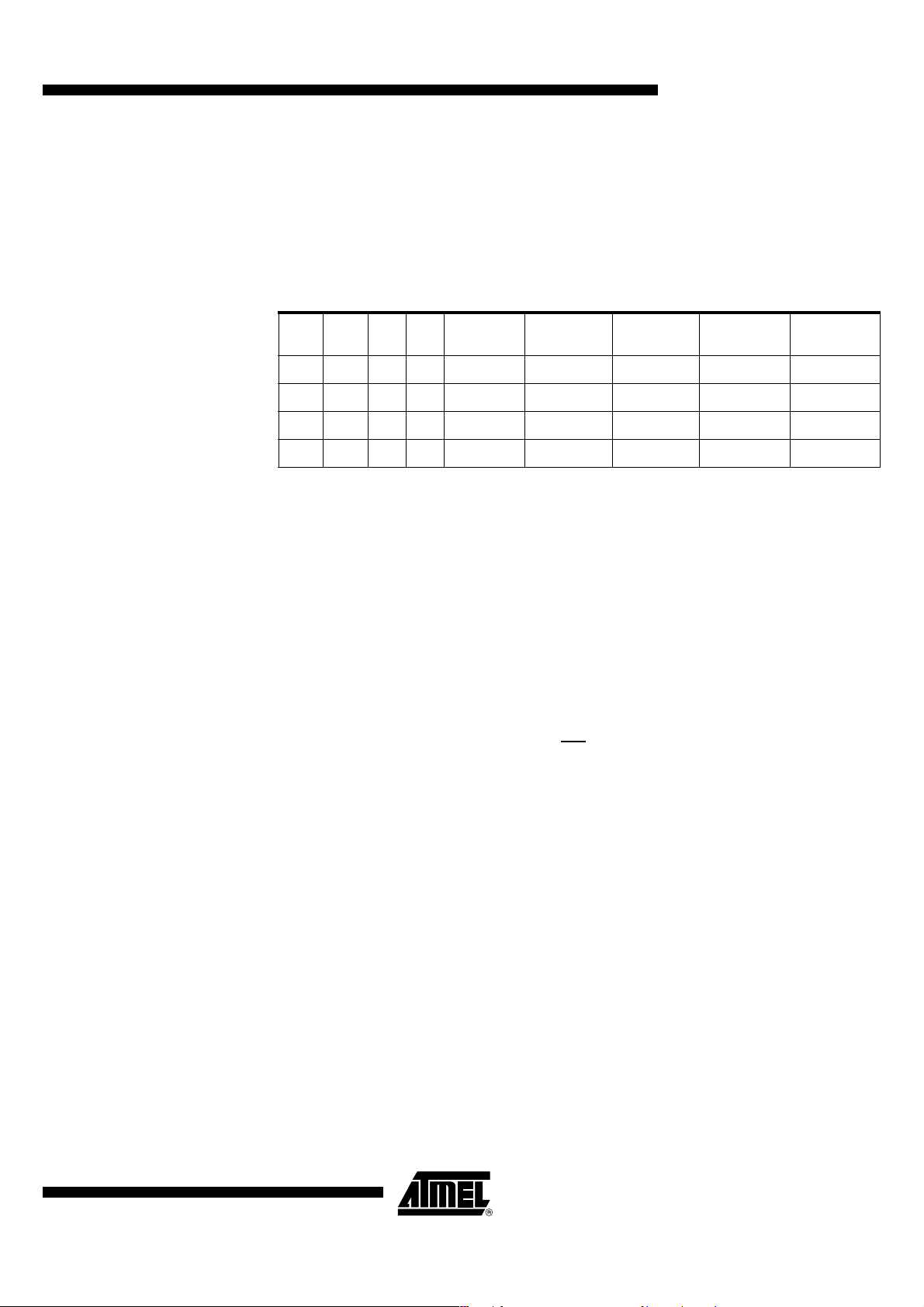

Table 6. Lock Bit Features

Level LB2

0 U U U Enable Enable Enable Enable Enable

1 U U P Enable Enable Enable Disable Enable

2 U P X Enable Enable Disable Disable Enable

(3)

3

Notes: 1. U means unprogrammed, P means programmed and X means don’t care (pro-

(2)

LB1 LB0

P X X Enable Dis able Disable Disable Enable

grammed or unprogrammed).

2. LB2 is not implemented in the AT8xC51SND1C products.

3. AT89C51SND1C products are delivered with third level programmed to ensure that

the code programmed by software using ISP or user’s boot loader is secured from

any hardware piracy.

(1)

Internal

Execution

External

Execution

Hardware

Verifying

Hardware

Programming

Software

Programming

As internal C51 code space is limited to 64K Bytes, some mechanisms are implemented

to allow boot memory to be mapped in the code space for ex ecution at addre sses from

F000h to FFFFh. The boot memory is enabled by setting the ENBOOT bit in AUXR1

(see Figure 10). The three ways to set this bit are detailed in the following sections.

7.7.1 Software Boot Mapping The software way to set ENBOOT consists in writing to AUXR1 from the user’s software. This enables boot loader or API routines execution.

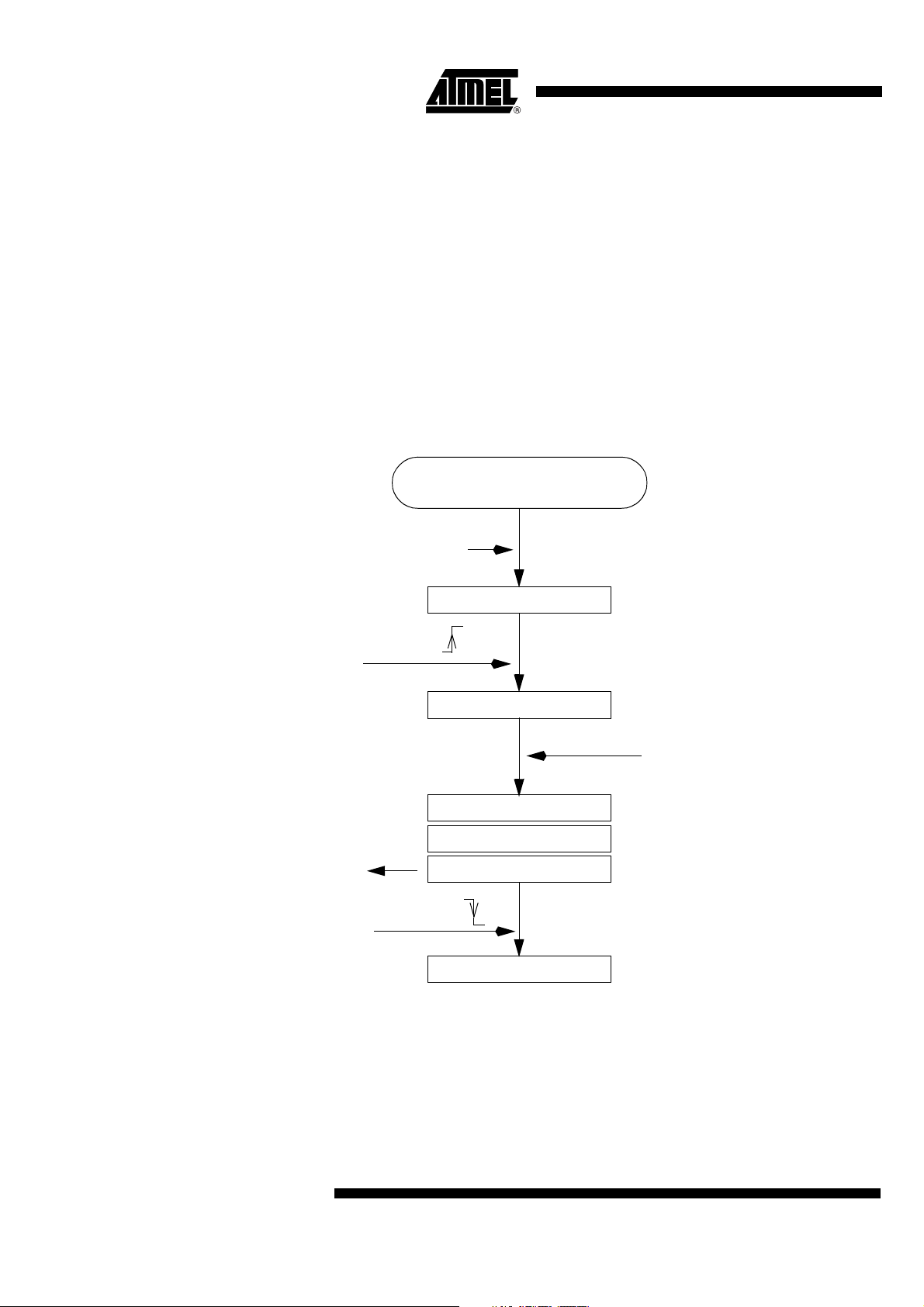

7.7.2 Hardware Condition

Boot Mapping

The hardware condition is based on the ISP

pin. When driving this pin to low level, the

chip reset sets ENBOOT and for ce s the res et vector to F000 h ins te ad of 00 00h i n order

to execute the boot loader software.

As shown in Figure 16 the hardware condition always allows in-system recovery when

user’s memory has been corrupted.

7.7.3 Programmed Condition

Boot Mapping

The programmed con dition is based on the Boot Loader Ju mp Bit (BLJB) in HSB. As

shown in Figure 16 when this bit is programmed (by hardware or software programming

mode), the chip reset set ENBOOT and forces the reset vec tor to F000h instead of

0000h, in order to execute the boot loader software.

4109H–8051–01/05

21

AT8xC51SND1C

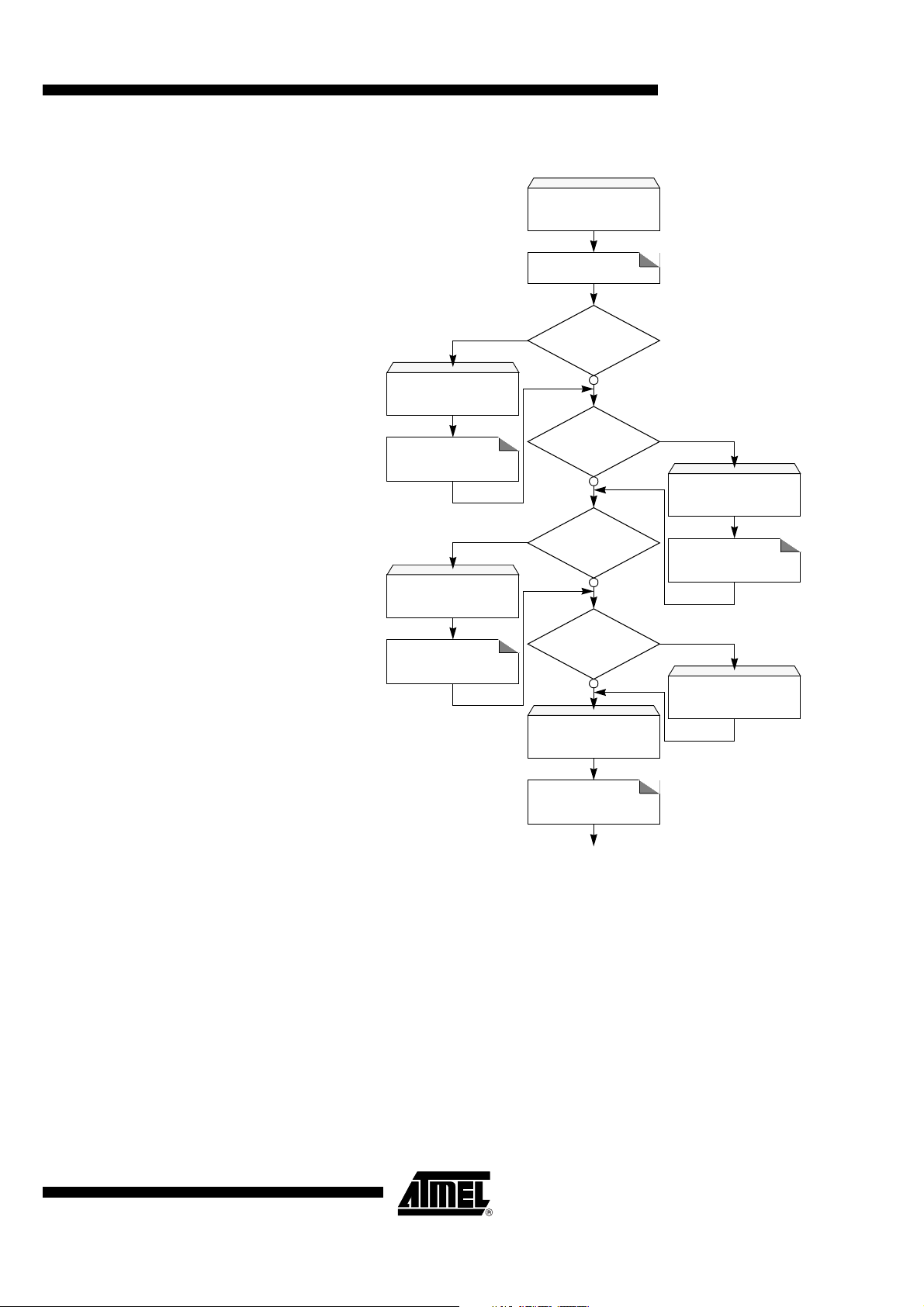

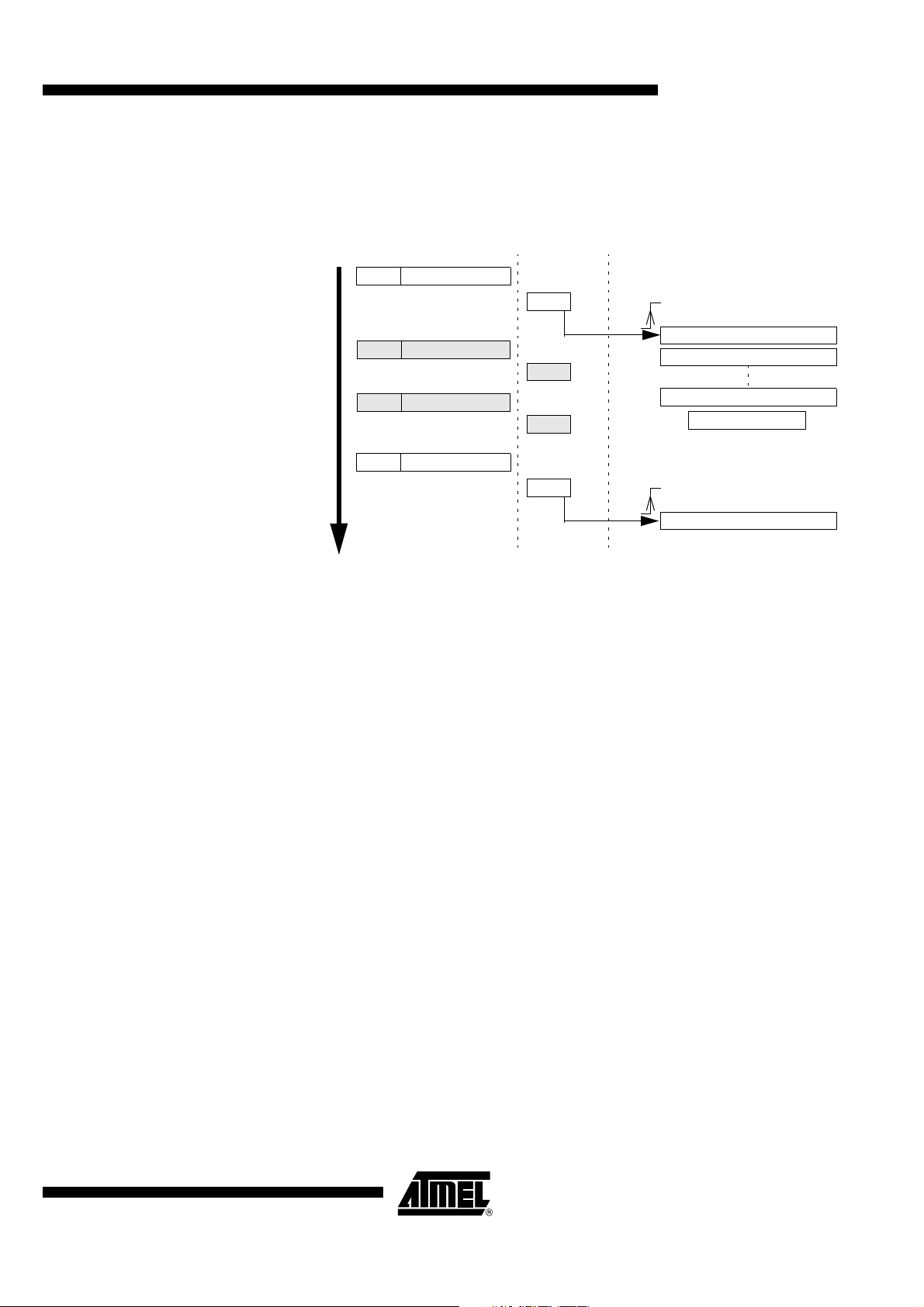

Figure 16. Hardware Boot Process Algorithm

RESET

Hard Cond?

ISP = L?

HardwareSoftware

7.8 Preventing Flash

Corruption

Process Process

Standard Init

ENBOOT = 0

PC = 0000h

FCON = F0h

User’s

Application

Prog Cond?

BLJB = P?

Prog Cond Init

ENBOOT = 1

PC = F000h

FCON = F0h

Atmel’s

Boot Loader

Hard Cond Init

ENBOOT = 1

PC = F000h

FCON = 00h

The software process (boot loader) is detailed in the “Boot Loader Datasheet”

Document.

See Section “Reset Recommendation to Prevent Flash Corruption”, page 49.

22

4109H–8051–01/05

7.9 Registers Table 10. AUXR1 Register

AUXR1 (S:A2h) – Auxiliary Register 1

76543210

- - ENBOOT - GF3 0 - DPS

AT8xC51SND1C

Bit

Number

7 - 6 -

5 ENBOOT

4-

3GF3

20

1-Reserved for Data Pointer Extension.

0DPS

Bit

Mnemonic Description

Reserved

The value read from these bits are indeterminate. Do not set these bits.

Enable Boot Flash

Set this bit to map the boot Flash in the code space between at addresses F000h

1

to FFFFh.

Clear this bit to disable boot Flash.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

General Flag

This bit is a general-purpose user flag.

Always Zero

This bit is stuck to logic 0 to allow INC AUXR1 instruction without affecting GF3

flag.

Data Pointer Select Bit

Set to select second data pointer: DPTR1.

Clear to select first data pointer: DPTR0.

Reset Value = XXXX 00X0b

Note: 1. ENBOOT bit is only ava il abl e in AT89C51SND1C product.

4109H–8051–01/05

23

AT8xC51SND1C

7.11 Hardware Bytes Table 12. HSB Byte – Hardware Security Byte

76543210

X2B BLJB - - - LB2 LB1 LB0

Bit

Number

7X2B

6BLJB

5 - 4 -

3-

2 - 0 LB2:0

Bit

Mnemonic Description

X2 Bit

(1)

Program this bit to start in X2 mode.

Unprogram (erase) this bit to start in standard mode.

Boot Loader Jump Bit

Program this bit to execute the boot loader at address F000h on next reset.

(2)

Unprogram (erase) this bit to execute user’s application at address 0000h on

next reset.

Reserved

The value read from these bits is always unprogrammed. Do not program these

bits.

Reserved

The value read from this bit is always unprogrammed. Do not program this bit.

Hardware Lock Bits

Refer to for bits description.

Reset Value = XXUU UXXX, UUUU UUUU after an hardware full chip erase.

Note: 1. X2B initializes the X2 bit in CKCON during the reset phase.

2. In order to ensure boot loader activation at first power-up, AT89C51SND1C products

are delivered with BLJB programmed.

3. Bits 0 to 3 (LSN) can only be programmed by hardware mode.

Table 13. SBV Byte – Software Boot Vector

76543210

ADD15 ADD14 ADD13 ADD12 ADD11 ADD10 ADD9 ADD8

Bit

Number

7 - 0 ADD15:8

Bit

Mnemonic Description

MSB of the user’s boot loader 16-bi t address location

Refer to the boot loader datasheet for usage information (boot loader dependent)

Reset Value = XXXX XXXX, UUUU UUUU after an hardware full chip erase.

Table 14. SSB Byte – Software Security Byte

76543210

SSB7SSB6SSB5SSB4SSB3SSB2SSB1SSB0

Bit

Number

7 - 0 SSB7:0

Bit

Mnemonic Description

Software Security Byte Data

Refer to the boot loader datasheet for usage information (boot loader dependent)

Reset Value = XXXX XXXX, UUUU UUUU after an hardware full chip erase.

24

4109H–8051–01/05

AT8xC51SND1C

8. Data Memory The AT8xC51SND1C provides data memory access in 2 different spaces:

1. The internal space mapped in three separate segments:

– The lower 128 Bytes RAM segment

– The upper 128 Bytes RAM segment

– The expanded 2048 Bytes RAM segment

2. The external space.

A fourth internal segment is available but dedicated to Special Function Registers,

SFRs, (addresses 80h to FFh) accessible by direct addressing mode. For information

on this segment, refer to the Section “Special Function Registers”, page 32.

Figure 17 shows the internal and external data memory spaces organization.

Figure 17. Internal and External Data Memory Organization

FFFFh

64K Bytes

External XRAM

7FFh FFh

00h

2K Bytes

Internal ERAM

EXTRAM = 0

80h 80h

7Fh

00h

Upper

128 Bytes

Internal RAM

Indirect Addressing

Lower

128 Bytes

Internal RAM

Direct or Indirect

Addressing

FFh

Direct Addressing

Special

Function

Registers

0800h

0000h

EXTRAM = 1

8.1 Internal Space

8.1.1 Lower 128 Bytes RAM The lower 128 Bytes of RAM (see Fi gure 18) are accessible from address 00h to 7Fh

using direct or indirect address ing modes. T he lowest 32 Bytes are grouped in to 4

banks of 8 regis ters (R0 to R7 ). 2 bits RS0 and RS1 in PSW re gister (see Table 8)

select which bank is in use accord ing to Table 2. T his al lows m ore eff icient us e of cod e

space, since register instructions are shorter than instructions that use direct addressing, and can be used for context switching in interrupt service routines.

Table 2. Register Bank Selection

RS1 RS0 Description

0 0 Register bank 0 from 00h to 07h

4109H–8051–01/05

0 1 Register bank 1 from 08h to 0Fh

1 0 Register bank 2 from 10h to 17h

1 1 Register bank 3 from 18h to 1Fh

The next 16 Bytes above the register banks form a block of bit-addressable memory

space. The C51 instruction set includes a wide selection of single-bit instructions, and

the 128 bits in this area can be directly addressed by these instructions. The bit

addresses in this area are 00h to 7Fh.

25

AT8xC51SND1C

Figure 18. Lower 128 Bytes Internal RAM Organization

7Fh

30h

20h

18h

10h

08h

00h

2Fh

Bit-Addressable Space

(Bit Addresses 0-7Fh)

1Fh

17h

4 Banks of

8 Registers

0Fh

R0-R7

07h

8.2.1 Upper 128 Bytes RAM The upper 128 Bytes of RAM are accessible from address 80h to FFh using only indirect

addressing mode.

8.2.2 Expanded RAM The on-chip 2K Bytes of expa nded RAM (E RAM ) are acces s ible fr om a ddr ess 0 000h to

07FFh using i ndirect ad dressing mode thro ugh MOVX in structio ns. In this a ddress

range, EXTRAM bit in AUXR register (see Table 9) is used to select the ERAM (default)

or the XRAM. As shown in Figure 17 when EXTRAM = 0, the ERAM is selected and

when EXTRAM = 1, the XRAM is selected (see Section “External Space”).

The ERAM memo ry can be resiz ed using XRS1: 0 bits in AUXR re gister to dynam ically

increase external access to the XRAM space. Table 3 details the selected ERAM size

and address range.

Table 3. ERAM Size Selection

XRS1 XRS0 ER AM Size Add ress

0 0 256 Bytes 0 to 00FFh

0 1 512 Bytes 0 to 01FFh

1 0 1K Byte 0 to 03FFh

1 1 2K Bytes 0 to 07FFh

Note: Lower 128 Bytes RAM, Upper 128 Bytes RAM, and expanded RAM are made of volatile

memory cells. This means that the RAM content is indeterminate after power-up and

must then be initialized properly.

26

4109H–8051–01/05

AT8xC51SND1C

8.4 External Space

8.4.1 Memory Interface The external memory interface comprises the external bus (port 0 and port 2) as well as

the bus control signals (RD

Figure 19 s hows the structure of the external address bus. P0 carries address A7:0

while P2 carri es addre ss A15:8. Data D7:0 is multi plexed with A7:0 on P0. Table 5

describes the external memory interface signals.

Figure 19. External Data Memory Interface Structure

, WR, and ALE).

AT8xC51SND1C

AD7:0

A15:8

Latch

A7:0

P2

ALE

P0

WR

Table 5. External Data Memory Interface Signals

Signal

Name Type Description

A15:8 O

AD7:0 I/O

ALE O

RD

Address Lines

Upper address lines for the external bus.

Address/Data Lines

Multiplexed lower address lines and data for the external memory.

Address Latch Enable

ALE signals indicates that valid address information are available on lines

AD7:0.

Read

O

Read signal output to external data memory.

RAM

PERIPHERAL

A15:8

A7:0

D7:0

OERD

WR

Alternate

Function

P2.7:0

P0.7:0

-

P3.7

WR

O

Write signal output to external memory.

P3.6

Write

8.5.1 Page Access Mode The AT8xC51SND1C impl ement a fea ture call ed Page A ccess tha t disables the outpu t

of DPH on P2 wh en execut ing MO VX @DP TR instru ction. P age Ac cess is enable by

setting the DPHDIS bit in AUXR register.

Page Access is useful when application uses both ERAM and 256 Bytes of XRAM. In

this case, software modifies intensively EXTRAM bit to select access to ERAM or XRAM

and must save it if used in interrupt service routine. Page Access allows external access

above 00FFh address with out generating DP H on P2. Thus ERAM is accessed u sing

MOVX @Ri or MOVX @DPTR with DPTR < 0100h, < 0200h, < 0400h or < 0800h

depending on the XRS1:0 bits value. The n XRAM is a ccessed us ing MOVX @ DPTR

with DPTR ≥ 0800h regardless of XRS1:0 bits valu e while ke eping P2 fo r general I/O

usage.

27

4109H–8051–01/05

AT8xC51SND1C

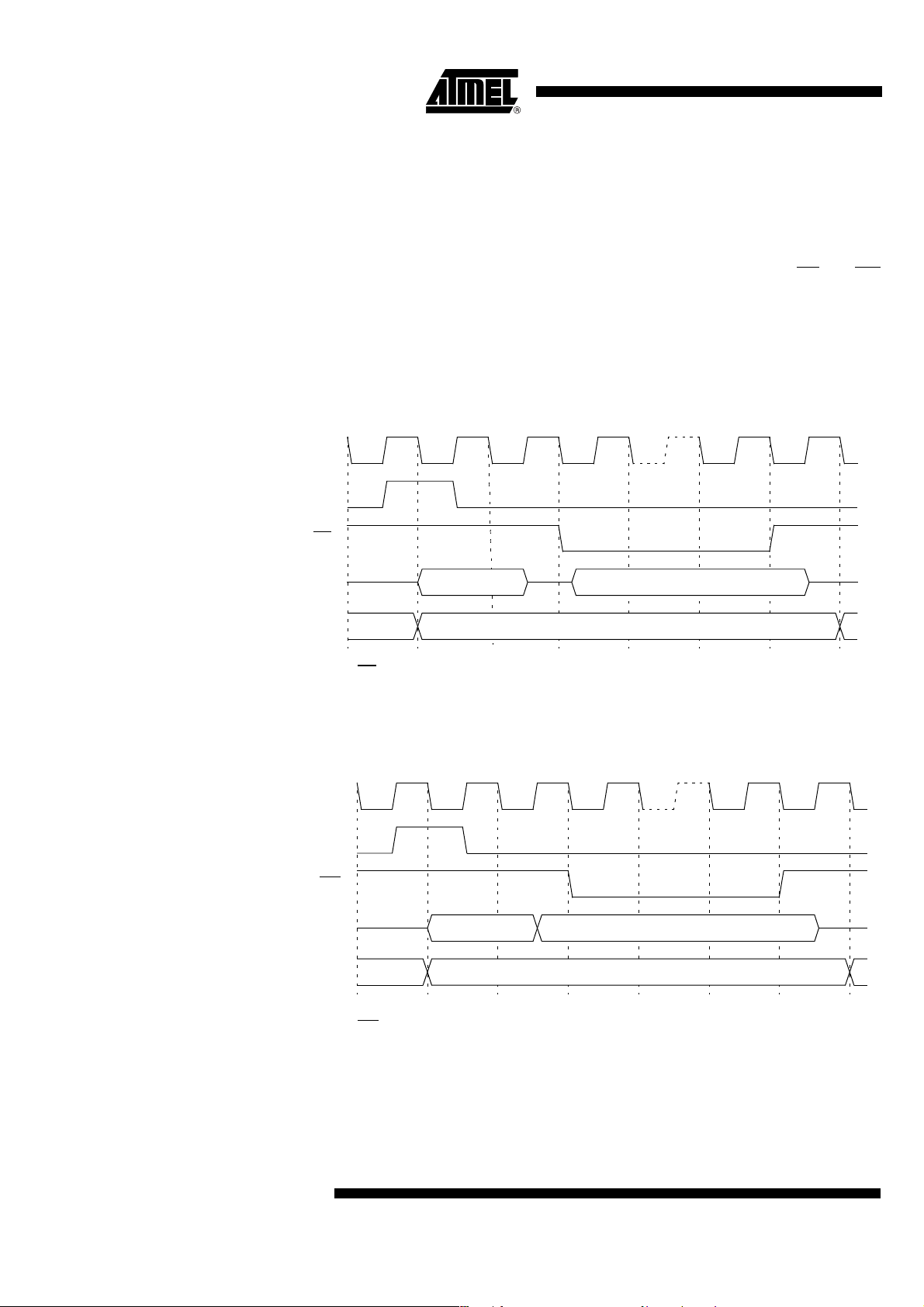

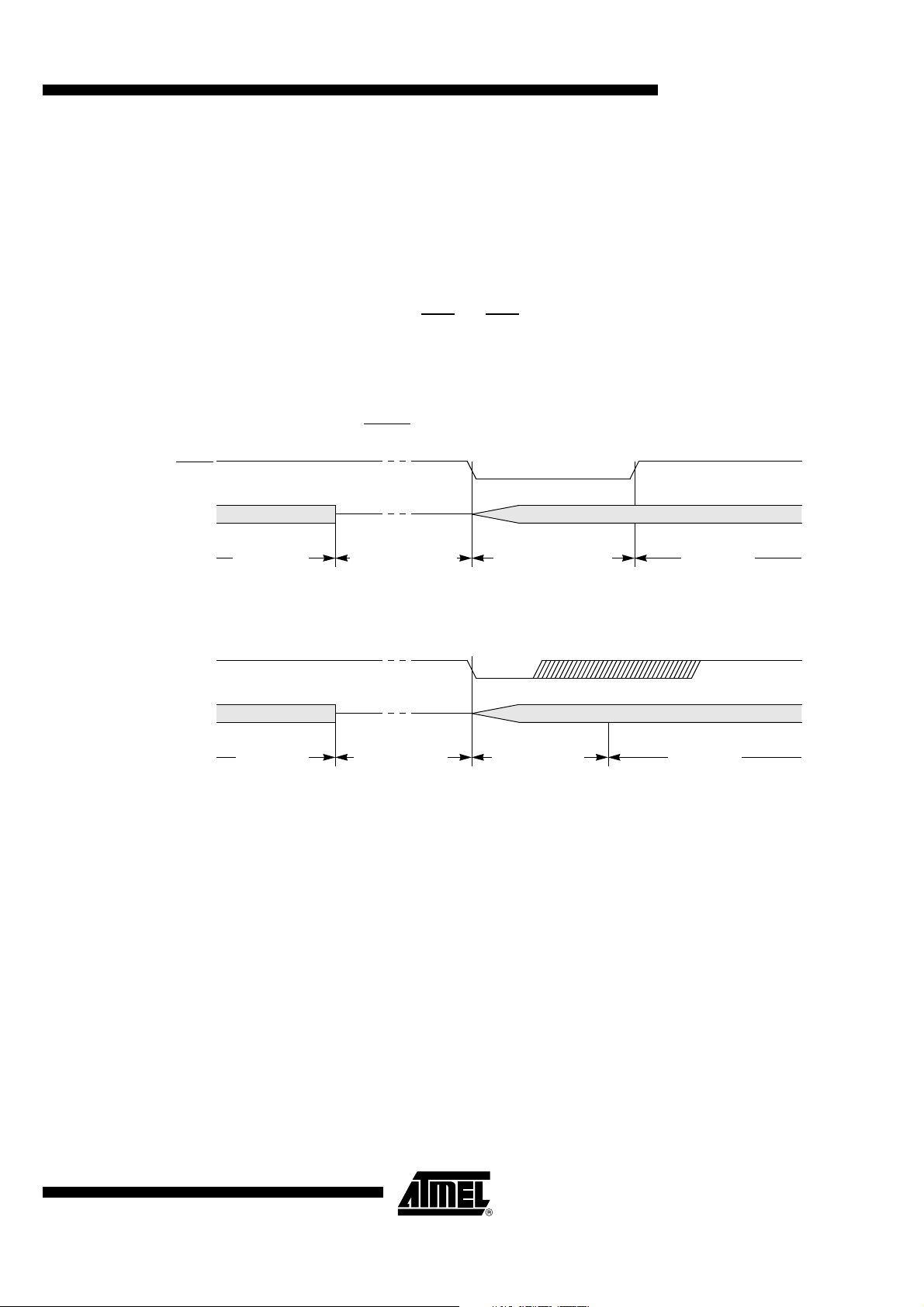

8.5.2 External Bus Cycles This section describes the bus cycles the AT8xC51SND1C executes to read (see

Figure 20), and write data (see Figure 21) in the external data memory.

External memory cycle takes 6 CPU clock periods. This is equivalent to 12 oscillator

clock period in standard mode or 6 oscillator clock periods in X2 mode. For further information on X2 mode, refer to the Section “X2 Feature”, page 12.

Slow peripherals can be acc essed b y stretc hing th e read and write cycles . This is done

using the M0 bit in AUXR reg ister. S etting t his bi t changes the widt h of the RD

and WR

signals from 3 to 15 CPU clock periods.

For simplicity, Figure 20 and Figure 21 depict the bus cycle waveforms in idealized form

and do not provide precis e timing in forma tion. For bus cycl e timing p aramet ers refe r to

the Section “AC Characteri stics”.

Figure 20. External Data Read Waveforms

CPU Clock

ALE

(1)

RD

P0

P2

Notes: 1. RD signal may be stretched using M0 bit in AUXR register.

P2

2. When executing MOVX @Ri instruction, P2 outputs SFR content.

3. When executing MOVX @DPTR instruction, if DPHDIS is set (Page Access Mode),

P2 outputs SFR content instead of DPH.

DPL or Ri D7:0

DPH or P2

(2),(3)

Figure 21. External Data Write Waveforms

CPU Clock

ALE

(1)

WR

P0

P2

Notes: 1. WR signal may be stretched using M0 bit in AUXR register.

2. When executing MOVX @Ri instruction, P2 outputs SFR content.

3. When executing MOVX @DPTR instruction, if DPHDIS is set (Page Access Mode),

P2

P2 outputs SFR content instead of DPH.

DPL or Ri D7:0

DPH or P2

(2),(3)

28

4109H–8051–01/05

AT8xC51SND1C

8.6 Dual Data Pointer

8.6.1 Description The AT 8xC51S ND1C impl ement a s econd da ta point er for spe eding up code execu tion

and reducing code size in case of intensive usage of external memory accesses.

DPTR0 and DPTR1 ar e seen by the CPU as DPTR and a re access ed using t he SFR

addresses 83h and 84h that are the DPH and DPL addresses. The DPS bit in AUXR1

register (see Table 10) is us ed to selec t whether DPTR is th e data poin ter 0 or the data

pointer 1 (see Figure 22).

Figure 22. Dual Data Pointer Implementation

DPL0

DPL1

DPTR0

DPTR1

DPH0

DPH1

0

1

DPS

0

1

DPL

AUXR1.0

DPH

DPTR

8.6.2 Application Software can take advantage of the additional data pointers to both increase speed and

reduce code size, for example, block operations (copy, compare, search …) are well

served by using one data poi nter as a “so urce” p ointer and the other one as a “des tination” pointer.

Below is an example of block move implementation using the 2 pointers and coded in

assembler. T he latest C compi ler also takes ad vantage of this fe ature by provid ing

enhanced algorithm libraries.

The INC instruction is a short (2 Bytes) and fast (6 CPU clocks) way to manipulate the

DPS bit in the AUXR 1 reg ister. H owever , note that th e INC i nstruc tion do es no t direc tly

force the DPS bit to a particular state, but simply toggles it. In simple routines, such as

the block move exa mple, o nly the f act that DP S is tog gled i n the pr oper s equenc e matters, not its actual value. In other words, the block move routine works the same whether

DPS is '0' or '1' on entry.

4109H–8051–01/05

; ASCII block move using dual data pointers

; Modifies DPTR0, DPTR1, A and PSW

; Ends when encountering NULL character

; Note: DPS exits opposite of entry state unless an extra INC AUXR1 is added

AUXR1 EQU 0A2h

move: mov DPTR,#SOURCE ; address of SOURCE

inc AUXR1 ; switch data pointers

mov DPTR,#DEST ; address of DEST

mv_loop: inc AUXR1 ; switch data pointers

movx A,@DPTR ; get a Byte from SOURCE

inc DPTR ; increment SOURCE address

inc AUXR1 ; switch data pointers

movx @DPTR,A ; write the Byte to DEST

inc DPTR ; increment DEST address

jnz mv_loop ; check for NULL terminator

end_move:

29

AT8xC51SND1C

8.7 Registers Table 8. PSW Register

PSW (S:8Eh) – Program Status Word Register

76543210

CY A C F0 RS1 RS0 OV F1 P

Bit

Number

7CY

6AC

5F0User Definable Flag 0

4 - 3 RS1:0

2OV

1F1User Definable Flag 1

0P

Bit

Mnemonic Description

Carry Flag

Carry out from bit 1 of ALU operands.

Auxiliary Carry Flag

Carry out from bit 1 of addition operands.

Register Bank Select Bits

Refer to Table 2 for bits description.

Overflow Flag

Overflow set by arithmetic operations.

Parity Bit

Set when ACC contains an odd number of 1’s.

Cleared when ACC contains an even number of 1’s.

Reset Value = 0000 0000b

30

4109H–8051–01/05

AT8xC51SND1C

Table 9. AUXR Register

AUXR (S:8Eh) – Auxiliary Control Register

76543210

- EXT16 M0 DPHDIS XRS1 XRS0 EXTRAM AO

Bit

Number

7-

6EXT16

5M0

4 DPHDIS

3 - 2 XRS1:0

1EXTRAM

0AO

Bit

Mnemonic Description

Reserved

The value read from this bit is indeterminate. Do not set this bit.

External 16-bit Access Enable Bit

Set to enable 16-bit access mode during MOVX instructions.

Clear to disable 16-bit access mode and enable standard 8-bit access mode

during MOVX instructions.

External Memory Access Stretch Bit

Set to stretch RD

Clear not to stretch RD

DPH Disable Bit

Set to disable DPH output on P2 when executing MOVX @DPTR instruction.

Clear to enable DPH output on P2 when executing MOVX @DPTR instruction.

Expanded RAM Size Bits

Refer to Table3 for ERAM size description.

External RAM Enable Bit

Set to select the external XRAM when executing MOVX @Ri or MOVX @DPTR

instructions.

Clear to select the internal expanded RAM when executing MOVX @Ri or MOVX

@DPTR instructions.

ALE Output Enable Bit

Set to output the ALE signal only during MOVX instructions.

Clear to output the ALE signal at a constant rate of F

or WR signals duration to 15 CPU clock periods.

or WR signals and set duration to 3 CPU clock periods.

/3.

CPU

4109H–8051–01/05

Reset Value = X000 1101b

31

AT8xC51SND1C

9. Special Function

Registers

The Special Function Registers (SFRs) of the AT8xC51SND1C derivatives fall into the

categories detailed in Table 1 to Table 17. The rela tive address es of these SFRs are

provided together with their reset values in Table 18. In this table, the bit-addressable

registers are identified by Note 1.

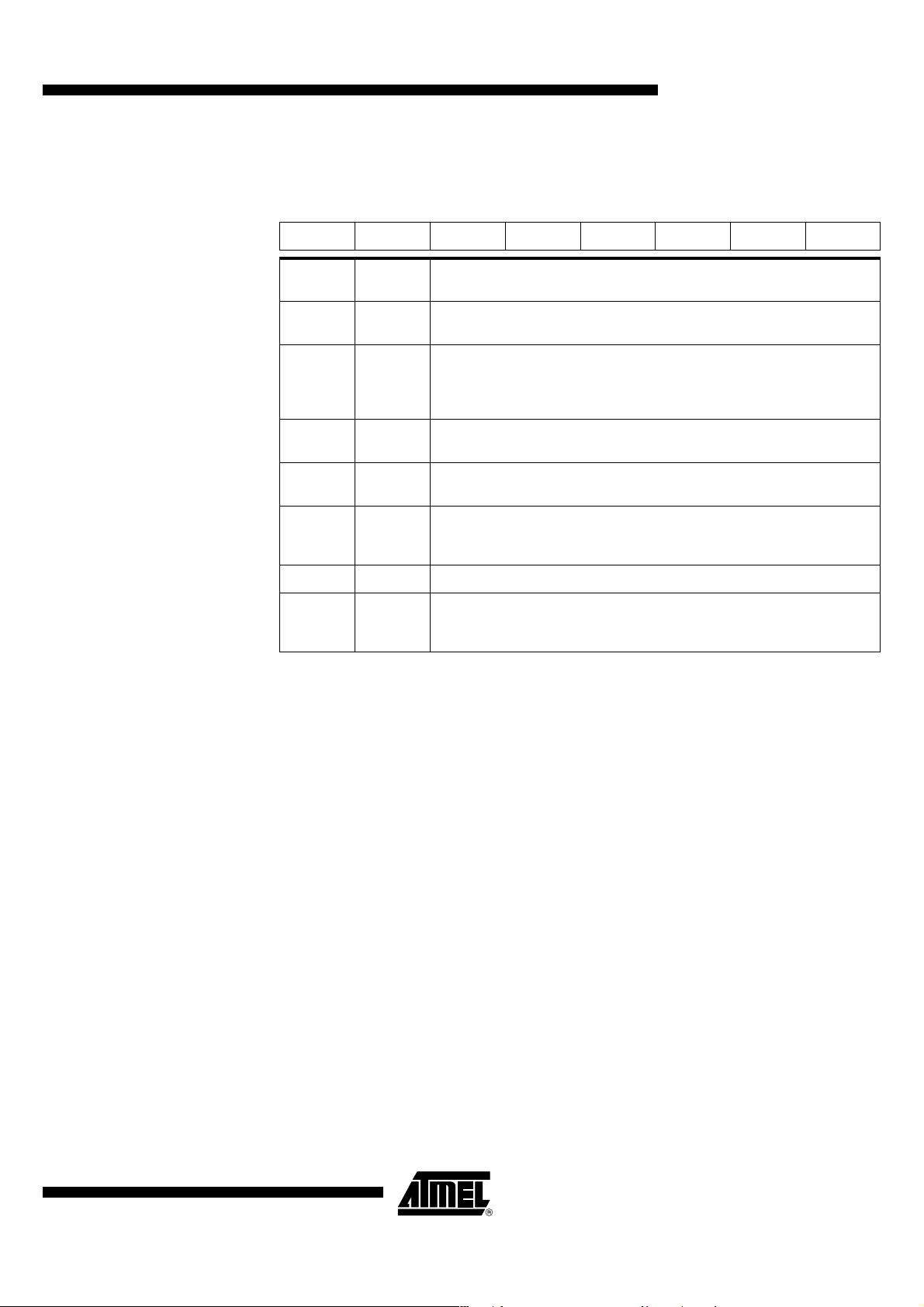

Table 1. C51 Core SFRs

MnemonicAddName 76543210

ACC E0h Accumulator

B F0h B Register

PSW D0h Program Status Word CY AC F0 RS1 RS0 OV F1 P

SP 81h Stack Pointer

DPL 82h Data Pointer Low Byte

DPH 83h Data Poi nter High Byte

Table 2. System Management SFRs

MnemonicAddName 76543210

PCON 87h Power Control SMOD1 SMOD0 - - GF1 GF0 PD IDL

AUXR 8Eh Auxiliary Register 0 - EXT16 M0 DPHDIS XRS1 XRS0 EXTRAM AO

AUXR1 A2h Auxiliary Register 1 - - ENBOOT

(1)

-GF30 -DPS

NVERS FBh Version Number NV7 NV6 NV5 NV4 NV 3 NV2 NV1 NV0

Note: 1. ENBOOT bit is only available in AT89C51SND1C product.

Table 3. PLL and System Clock SFRs

MnemonicAddName 76543210

CKCON8FhClock Control -------X2

PLLCON E 9 h PLL Control R1 R0 - - PLLRES - PLLEN PLOCK

PLLNDIV EEh PLL N Divider - N6 N5 N4 N3 N2 N1 N0

PLLRDIV EFh PLL R Divider R9 R8 R7 R6 R5 R4 R3 R2

Table 4. In terrupt S F Rs

MnemonicAddName 76543210

IEN0 A8h Interrupt Enable Control 0 EA EAUD EMP3 ES ET1 EX1 ET0 EX0

IEN1 B1h Interrupt Enable Control 1 - EUSB - E KB EADC ESPI EI2C EMMC

IPH0 B7h Interrupt Priority Control High 0 - IPHAUD IPHMP 3 IPHS IPHT1 IPHX1 IPHT0 IPHX0

IPL0 B8h Interrupt Priority Control Low 0 - IPLAUD I PLM P3 IPLS IPLT1 IPLX1 IPLT0 IPLX0

IPH1 B3h Interrupt Priority Control High 1 - IPHUSB - IPHKB IPHADC IPHSPI IPHI2C IPHMMC

IPL1 B2h Interrupt Priority Control Low 1 - IPLUSB - IPLKB IPLADC IPLSPI IPLI2C IPLM MC

32

4109H–8051–01/05

AT8xC51SND1C

Table 5. Port SFRs

MnemonicAddName 76543210

P0 80h 8-bit Port 0

P1 90h 8-bit Port 1

P2 A0h 8-bit Por t 2

P3 B0h 8-bit Por t 3

P4 C0h 8-bit Port 4

P5D8h4-bit Port 5 ----

Table 6. Flash Memory SFR

MnemonicAddName 76543210

(1)

FCON

Note: 1. FCO N register is only available in AT89C51SND1 C product.

D1h Flash Control FPL3 FPL2 FPL1 FPL0 FPS FMOD1 FMOD0 FBUSY

Table 7. Timer SFRs

MnemonicAddName 76543210

TCON 88h Timer/Counter 0 and 1 Control TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

TMOD 89h Timer/Counter 0 and 1 Modes GATE1 C/T1# M11 M01 GATE0 C/T0# M10 M00

TL0 8Ah Timer/Counter 0 Low Byte

TH0 8Ch Timer/Counter 0 High Byte

TL1 8Bh Timer/Counter 1 Low Byte

TH1 8Dh

WDTRST A6h Watchdog Timer Reset

WDTPRG A7h Watchdog Timer Program -----WTO2WTO1WTO0

Timer/Counter 1 High Byte

4109H–8051–01/05

33

AT8xC51SND1C

Table 8. M P3 Decode r SFRs

MnemonicAddName 76543210

MP3CON AAh MP3 Control MPEN MPBBST CRCEN MSKANC MSKREQ MSKLAY MSKSYN MSKCRC

MP3STA C8h MP3 Status MPANC MPREQ ERRLAY ERRSYN ERRCRC MPFS1 MPFS0 MPVER

MP3STA1 AFh MP3 Status 1 - - - MPFREQ MPBREQ - - MP3DAT ACh MP3 Data MPD7 MPD6 MPD5 MPD4 MPD3 MPD2 MPD1 MPD0

MP3ANC ADh MP3 Ancillary Data AND7 AND6 AND5 AND4 AND3 AND2 AND1 AND0

MP3VOL 9Eh MP3 Audio Volume Control Left - - - VOL4 VOL3 VOL2 VOL1 VOL0

MP3VOR 9Fh

MP3BAS B4h MP3 Audio Bass Control - - - BAS4 BAS3 BAS2 BAS1 BAS0

MP3MED B5h MP3 Audio Medium Control - - - MED4 MED3 MED2 MED1 MED0

MP3TRE B6h MP3 Audio Treble Control - - - TRE4 TRE3 TRE2 TRE1 TRE0

MP3CLK EBh MP3 Clock Divider - - - MPCD4 MPCD3 MPCD2 MPCD1 MPCD0

MP3 Audio Volume Control

Right

- - - VOR4 VOR3 VOR2 VOR1 VOR0

Table 9. Audio Interface SFRs

MnemonicAddName 76543210

AUDCON0 9Ah Audio Control 0 JUST4 JUST3 JUST2 JUST1 JUST0 POL DSIZ HLR

AUDCON1 9Bh Audio Control 1 SRC DRQEN MSREQ MUDRN - DUP1 DUP0 A UDE N

AUDSTA 9Ch Audio Status SREQ UDRN AUBUSY ----AUDDAT 9Dh Audio Data AUD7 A UD6 AUD5 AUD4 AUD3 AUD2 AUD1 AUD0

AUDCLK ECh Audio Clock Divider - - - AUCD4 AUCD3 AUCD2 AUCD1 AUCD0

34

4109H–8051–01/05

AT8xC51SND1C

Table 10. USB Controller SFRs

MnemonicAddName 76543210

USBCON BCh USB Global Control USBE SUSPCLK SDRMWUP - UPRSM RMWUPE CONFG FADDEN

USBADDR C6h USB Address FEN UADD6 UADD5 UADD4 UADD3 UADD2 UADD1 UADD0

USBINT BDh USB Global Interrupt - - WUPCPU EORINT SOFINT - - SPINT

USBIEN BEh USB Global Interrupt Enable - - EWUPCPU EEORINT ESOFINT - - ESPINT

UEPNUMC7hUSB Endpoint Number ------EPNUM1EPNUM0

UEPCONX D4h USB Endpoint X Control EPE N NAKIEN NAKOUT NAKIN DTG L EPDIR EPTYPE1 EPTYPE0

UEPSTAX CEh USB Endpoint X Status DIR RXOUTB1 STALLRQ TXRDY STLCR C RXSETUP RXOUTB0 TXCMP

UEPRSTD5hUSB Endpoint Reset -----EP2RSTEP1RSTEP0RST

UEPINTF8hUSB Endpoint Interrupt -----EP2INTEP1INTEP0INT

UEPIEN C2h USB Endpoint Interrupt Enable -----EP2INTEEP1INTEEP0INTE

UEPDATX CFh USB Endpoint X FIFO Data FDAT7 FDAT6 FDAT5 FDAT4 FDAT3 F DAT2 FDAT1 FDAT0

UBYCTX E2h USB Endpoint X Byte Counter - BYCT6 BYC T5 BYCT4 BYCT3 BYC T2 BYCT1 BYCT0

UFNUML BAh USB Frame Number Low FNUM7 FNUM6 FNUM5 FNUM4 FNUM3 FNUM2 FNUM1 FNUM0

UFNUMH BBh USB Frame Number High - - CRCOK CRCERR - FNUM10 FNUM9 FNUM8

USBCLKEAhUSB Clock Divider ------USBCD1USBCD0

Table 11. MMC Controller SFRs

MnemonicAddName 76543210

MMCON0 E4h MMC Control 0 DRPTR DTPTR CRPTR CTPTR MBLOCK DFMT RFMT CRCDIS

MMCON1 E5h MMC Control 1 BLEN3 BLEN2 BLEN1 BLEN0 DATDIR DATEN RESPEN CMDEN

MMCON2 E6h MMC Control 2 MMCEN DCR CCR - - DATD1 DATD0 FLOWC

MMSTA DEh MMC Control and Status - - CBUSY CRC16S DATFS CRC7S RESPFS CFLCK

MMINT E7h MMC Interrupt MCBI EORI EOCI EOFI F2FI F1FI F2EI F1 EI

MMMSK DFh MMC Interrupt Mask MCBM EORM EOCM EOFM F2FM F1FM F2EM F1EM

MMCMD DDh MMC Command MC7 MC6 MC5 MC4 MC3 MC2 MC1 MC0

MMDAT DCh MMC Data MD7 MD6 MD5 MD4 MD3 MD2 MD1 MD0

MMCLK EDh MMC Clock Divider MMCD7 MMCD6 MMCD5 MMCD4 MMCD3 MMCD2 MMCD1 MMCD0

Table 12. IDE Interface SFR

MnemonicAddName 76543210

DAT16H F9h High Order Data Byte D15 D14 D13 D12 D11 D10 D9 D8

4109H–8051–01/05

35

AT8xC51SND1C

Table 13. Serial I/O Port SFRs

MnemonicAddName 76543210

SCON 98h Serial Control FE/SM0 SM1 SM2 REN TB8 RB8 TI RI

SBUF 99h Serial Data Buffer

SADEN B9h Slave Address Mask

SADDR A9h Slave Address

BDRCON 92h Baud Rate Control BRR TBCK RBCK SPD SRC

BRL 91h Baud Rate Reload

Table 14. SPI Controller SFRs

MnemonicAddName 76543210

SPCON C3h SPI Control SPR2 SPEN SSDIS MSTR CPOL CPHA SPR1 SPR0

SPSTAC4hSPI Status SPIFWCOL-MODF---SPDAT C5h SPI Data SPD7 SPD6 SPD5 SPD4 SPD3 SPD2 SP D1 SPD0

Table 15. Two Wire Controller SFRs

MnemonicAddName 76543210

SSCON 93h Synchronous Serial Control SSCR2 SSPE SSSTA SSSTO SSI SSAA SSCR1 SSCR0

SSSTA 94h Synchronous Serial Status SSC4 SSC3 SSC2 SSC1 SSC0 0 0 0

SSDAT 95h Synchronous Serial Data SSD7 SSD6 SSD5 SSD4 SSD3 SSD2 SSD1 SSD0

SSADR 96h Synchronous Serial Address SSA7 SSA6 SSA5 SSA4 SSA3 SSA2 SSA1 SSGC

Table 16. Keyboard Interface SFRs

MnemonicAddName 76543210

KBCON A3h Keyboard Control KINL3 KINL2 KINL1 KINL0 K INM3 KINM2 KINM1 KINM0

KBSTA A4h Keyboard Status KPDE - - - KINF3 KINF2 KINF1 KIN F0

Table 17. A/D Controller SFRs

MnemonicAddName 76543210

ADCON F3h ADC Control - ADIDL ADEN ADEOC ADSST - - ADCS

ADCLK F2h ADC Clock Divider - - - ADCD4 ADCD3 ADCD2 ADCD1 ADCD0

ADDLF4hADC Data Low Byte ------ADAT1ADAT0

ADDH F5h ADC Data High Byte ADAT9 ADAT8 ADAT7 ADAT6 ADAT5 ADAT4 ADAT3 ADAT2

36

4109H–8051–01/05

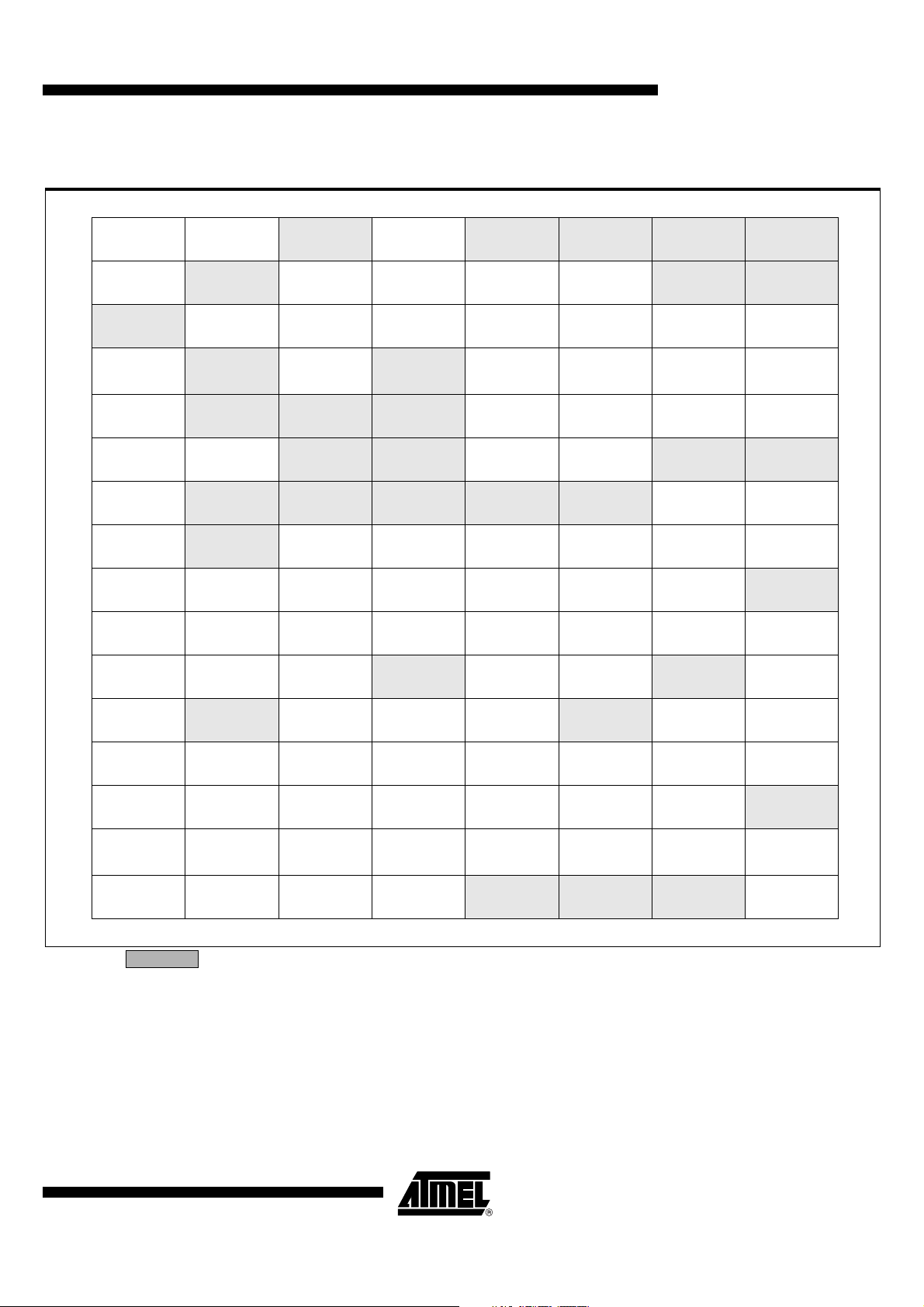

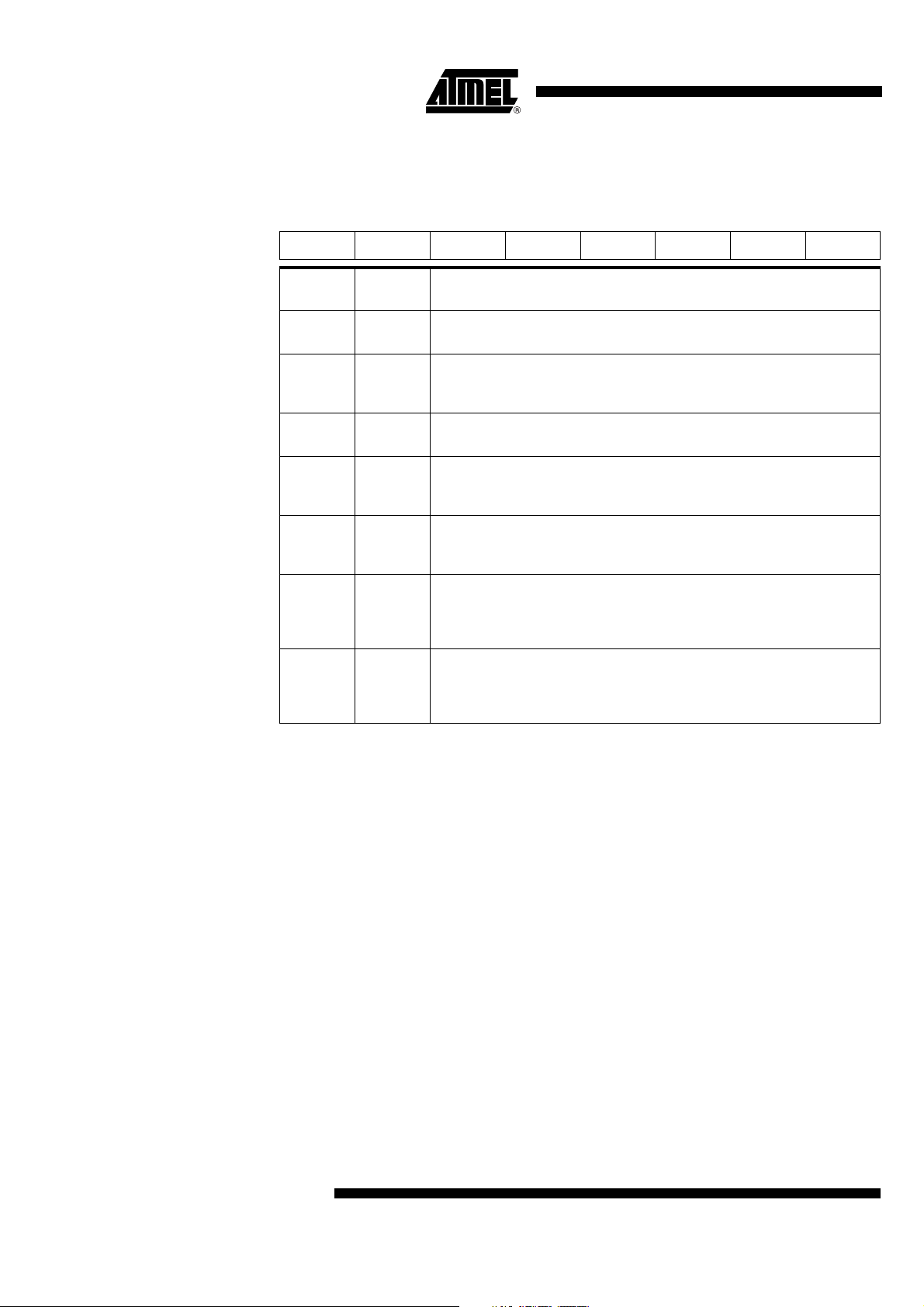

Table 18. SFR Addresses and Reset Values

0/8 1/9 2/A 3/B 4/C 5/D 6/E 7/F

AT8xC51SND1C

F8h

F0h

E8h

E0h

D8h

D0h

C8h

C0h

B8h

B0h

A8h

A0h

UEPINT

0000 0000

(1)

B

0000 0000

(1)

ACC

0000 0000

(1)

P5

XXXX 1111

(1)

PSW

0000 0000

MP3STA

0000 0001

(1)

P4

1111 1111

(1)

IPL0

X000 0000

(1)

P3

1111 1111

(1)

IEN0

0000 0000

(1)

P2

1111 1111

(1)

DAT16H

XXXX XXXX

PLLCON

0000 1000

(3)

FCON

1111 0000

SADEN

0000 0000

IEN1

0000 0000

SADDR

0000 0000

(4)

ADCLK

0000 0000

USBCLK

0000 0000

UBYCTLX

0000 0000

UEPIEN

0000 0000

UFNUML

0000 0000

IPL1

0000 0000

MP3CON

00111111

AUXR1

XXXX 00X0

NVERS

XXXX XXXX

ADCON

0000 0000

MP3CLK

0000 0000

SPCON

0001 0100

UFNUMH

0000 0000

IPH1

0000 0000

KBCON

0000 1111

(2)

ADDL

0000 0000

AUDCLK

0000 0000

MMCON0

0000 0000

MMDAT

1111 1111

UEPCONX

1000 0000

SPSTA

0000 0000

USBCON

0000 0000

MP3BAS

0000 0000

MP3DAT

0000 0000

KBSTA

0000 0000

ADDH

0000 0000

MMCLK

0000 0000

MMCON1

0000 0000

MMCMD

1111 1111

UEPRST

0000 0000

SPDAT

XXXX XXXX

USBINT

0000 0000

MP3MED

0000 0000

MP3ANC

0000 0000

PLLNDIV

0000 0000

MMCON2

0000 0000

MMSTA

0000 0000

UEPSTAX

0000 0000

USBADDR

0000 0000

USBIEN

0001 0000

MP3TRE

0000 0000

WDTRST

XXX XXXX

PLLRDIV

0000 0000

MMINT

0000 0011

MMMSK

1111 1111

UEPDATX

XXXX XXXX

UEPNUM

0000 0000

IPH0

X000 0000

MP3STA1

0100 0001

WDTPRG

XXXX X000

FFh

F7h

EFh

E7h

DFh

D7h

CFh

C7h

BFh

B7h

AFh

A7h

98h

90h

88h

80h

SCON

0000 0000

(1)

P1

1111 1111

(1)

TCON

0000 0000

(1)

P0

1111 1111

SBUF

XXXX XXXX

BRL

0000 0000

TMOD

0000 0000

SP

0000 0111

AUDCON0

0000 1000

BDRCON

XXX0 0000

TL0

0000 0000

DPL

0000 0000

AUDCON1

1011 0010

SSCON

0000 0000

TL1

0000 0000

DPH

0000 0000

AUDSTA

11000000

SSSTA

1111 1000

TH0

0000 0000

AUDDAT

1111 1111

SSDAT

1111 1111

TH1

0000 0000

0/8 1/9 2/A 3/B 4/C 5/D 6/E 7/F

Reserved

Notes: 1. SFR registers with least significant nibble address equal to 0 or 8 are bit-addressable.

2. NVERS reset value de pends on the silic on ver sion: 10000100 for AT89C51SND1C product and 00000001 for AT83SND1C

product.

3. FCON register is only available in AT89C51SND1C product.

4. FCON reset value is 00h in case of reset with hardware condition.

5. CKCON reset value depends on the X2B bit (programmed or unprogrammed) in the Hardware Byte.

4109H–8051–01/05

MP3VOL

0000 0000

SSADR

1111 1110

AUXR

X000 1101

MP3VOR

0000 0000

CKCON

0000 000X

PCON

00XX 0000

9Fh

97h

8Fh

(5)

87h

37

AT8xC51SND1C

10. Interrupt System The AT8xC51 SND1C, l ike other contro l-orie nted co mput er archit ectur es, em ploy a pr o-

gram interrupt method. This operation branches to a subroutine and performs some

service in r e spo ns e t o th e in te rr u pt. Wh en t h e su br ou ti ne co m pl e tes, ex ec ut i on r es um es

at the point where the interrupt occurred. Interrupts may occur as a result of internal

AT8xC51SND1C activity (e.g., timer overflow) or at the initiation of electrical signals

external to the microcontroller (e.g., keyboard). In all cases, interrupt operation is pro-

grammed by the system designer, who determines priority of interrupt service relative to

normal code execution and other interrupt service routines. All of the interrupt sources

are enabled or disabled by the system designer and may be manipulated dynamically.

A typical interrupt event chain occurs as follows:

• An internal or external device initiates an interrupt-request signal. The

AT8xC51SND1C, latches this event into a flag buffer.

• The priority of the flag is compared to the priority of other interrupts by the interrupt

handler. A high priority causes the handler to set an interrupt flag.

• This signals the instruction execution unit to execute a context switch. This context

switch breaks the current flow of instruction sequences. The execution unit

completes the current instruction prior to a save of the program counter (PC) and

reloads the PC with the start address of a software service rou tine.

• The software service routine executes assigned tasks and as a final activity

performs a RETI (return from interrupt) instruction. This instruction signals

completion of the interrupt, resets the interrupt-in-progress priority and reloads the

program counter. Program operation then continues from the original point of

interruption.

Table 1. In terr upt Sy st em Signal s

10.2 Interrupt System

Priorities

Signal

Name Type Description

External Interrupt 0

INT0

INT1

KIN3:0 I

I

See section "External Interrupts", page 41.

External Interrupt 1

I

See section “External Interrupts”, page 41.

Keyboard Interrupt Inputs

See section “Keyboard Interface”, page 182.

Alternate

Function

P3.2

P3.3

P1.3:0

Six interrupt register s ar e use d to cont rol t he int er rupt sy st em. 2 8- bit regi st er s are use d

to enable separately the inte rrupt source s: IEN0 and IE N1 registers (s ee Table 7 and

Table 8).

Four 8-bit registers are used to establish the priority level of the different sources: IPH0,

IPL0, IPH1 and IPL1 registers (see Table 9 to Table 12).

Each of the interrupt sources on the AT8xC51SND1C can be individually programmed

to one of four priority levels. This is accomplished by one bit in the Interrupt Priority High

registers (IPH0 and IPH1) and one bit in the Interrupt Priority Low registers (IPL0 and

IPL1). This prov ides each interrupt source fo ur possib le priorit y levels accordin g to

Table 3.

38

4109H–8051–01/05

AT8xC51SND1C

Table 3. Priority Levels

IPHxx IPLxx Priority Level

0 0 0 Lowest

011

102

1 1 3 Highest

A low-priority i nterrupt is always in terrupted by a higher priority interrupt b ut not by

another interrupt o f low er o r equ al p riority. Highe r pr iorit y in terrupt s are se rviced befor e

lower priority interrupts. The response to simultaneous occurrence of equal priority interrupts is determined by an inter nal hard ware pol ling s equence deta iled in Table 4. Thus ,

within each priority level there is a second priority structure determined by the pollin g

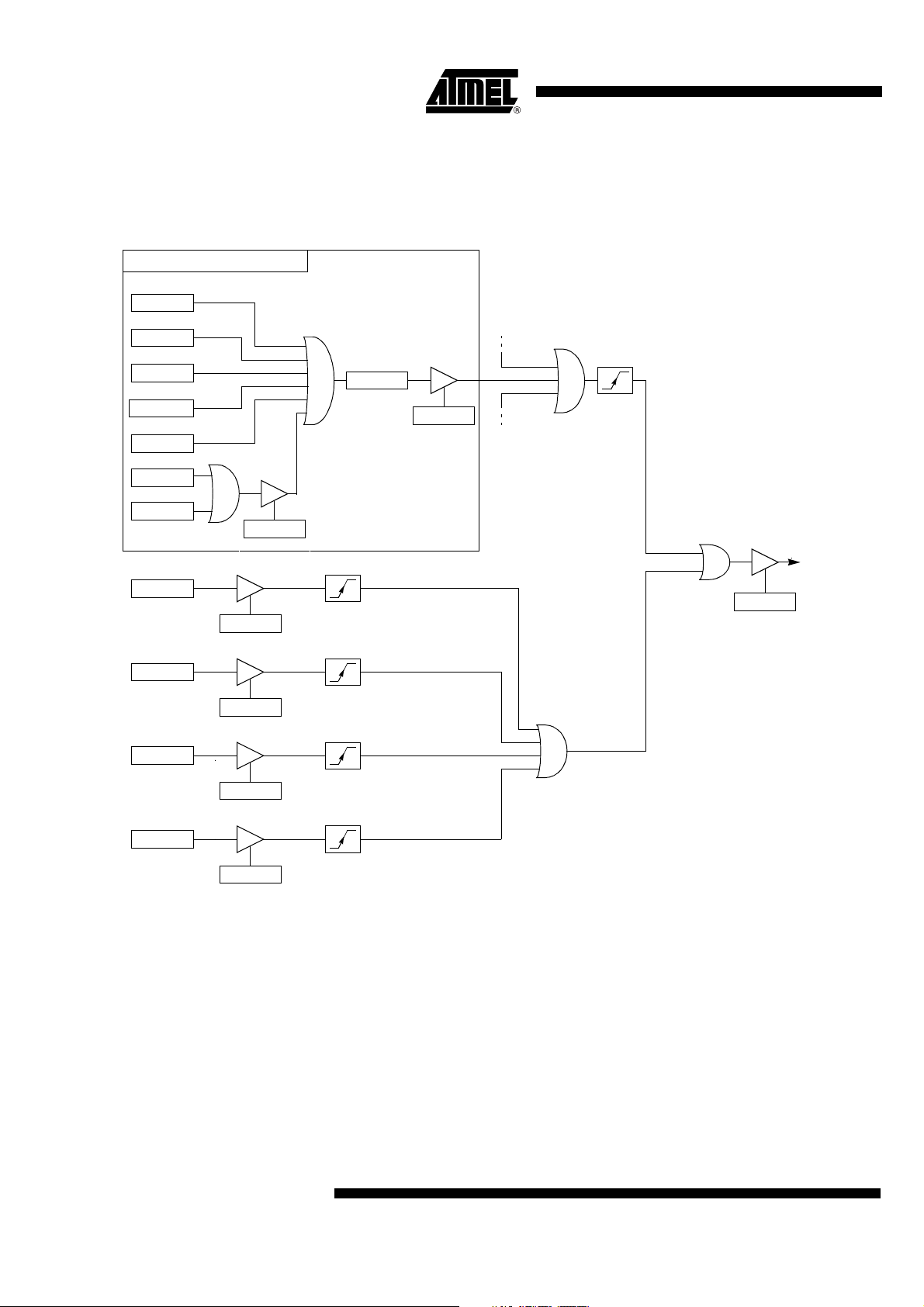

sequence. The interrupt control system is shown in Figure 23.

Table 4. Priority within Same Level

Interrupt Name Priority Number

INT0

Timer 0 1 C:000Bh H

INT1

Timer 1 3 C:001Bh H

Serial Port 4 C:0023h S

MP3 Decoder 5 C:002Bh S

Audio Interface 6 C:0033h S

MMC Interface 7 C:003Bh S

Two Wire Controller 8 C:0043h S

SPI Controller 9 C:004Bh S

A to D Converter 10 C:0053h S

Keyboard 11 C:005Bh S

Reserved 12 C:0063h USB 13 C:006Bh S

Reserved 14 (Lowest Priority) C:0073h -

0 (Highest Priority) C:0003h H if edge, S if level

2 C:0013h H if edge, S if level

Interrupt Address

Vectors

Interrupt Request Flag

Cleared by Hardware

(H) or by Software (S)

4109H–8051–01/05

39

AT8xC51SND1C

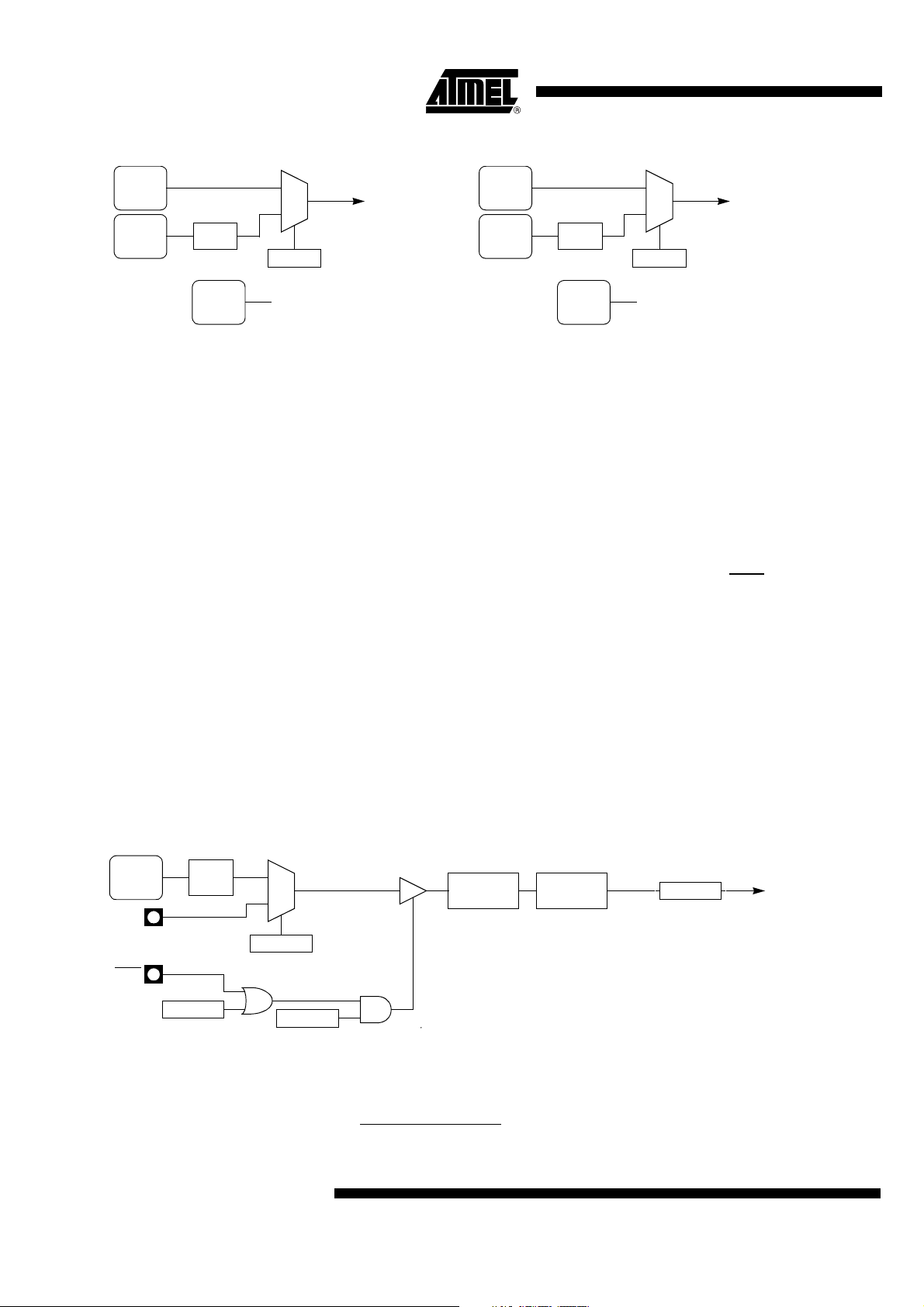

Figure 23. Interrupt Control System

Highest

ts

INT0

INT1

TXD

RXD

MCLK

MDAT

MCMD

SCL

SDA

SCK

SI

SO

AIN1:0

KIN3:0

D+

D-

External

Interrupt 0

Timer 0

External

Interrupt 1

Timer 1

Serial

Port

MP3

Decoder

Audio

Interface

MMC

Controller

TWI

Controller

SPI

Controller

A to D

Converter

Keyboard

USB

Controller

00

01

10

11

EX0

IEN0.0

ET0

IEN0.1

EX1

IEN0.2

ET1

IEN0.3

ES

IEN0.4

EMP3

IEN0.5

EAUD

IEN0.6

EMMC

IEN1.0

EI2C

IEN1.1

ESPI

IEN1.2

EADC

IEN1.3

EKB

IEN1.4

EUSB

IEN1.6

Interrupt Enable Lowest Priority Interrupts

EA

IEN0.7

00

01

10

11

00

01

10

11

00

01

10

11

00

01

10

11

00

01

10

11

00

01

10

11

00

01

10

11

00

01

10

11

00

01

10

11

00

01

10

11

00

01

10

11

00

01

10

11

IPH/L

Priority Enable

Priority

Interrup

40

4109H–8051–01/05

AT8xC51SND1C

t

t

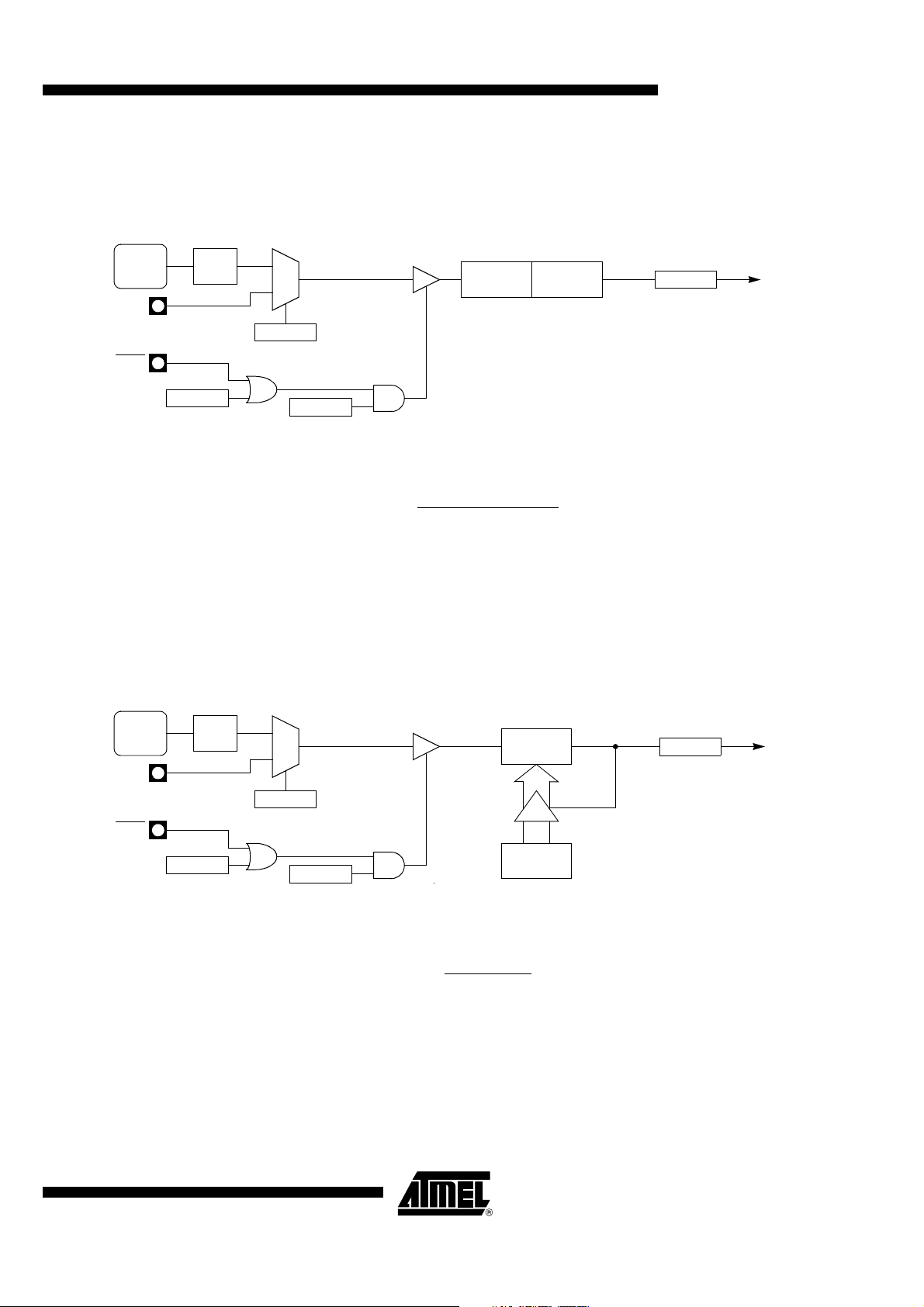

10.5 External Interrupts

10.5.1 INT1:0 Inputs External interrupts INT0 and INT1 (INTn, n = 0 or 1) pins may each be programmed to

be level-triggered or edge-triggered, dependent upon bits IT0 and IT1 (ITn, n = 0 or 1) in

TCON register as shown i n Figure 24 . If ITn = 0 , INTn

pin. If ITn = 1, INTn

is negative-edge trig ger ed . E xte rnal int er ru pts ar e ena ble d wi th b its

EX0 and EX1 (EXn, n = 0 or 1) in IEN0. Events on INTn

in TCON register. If the interrupt is edge-triggered, the request flag is cleared by hardware when vectoring to the interrupt service routine. If the interrupt is level-triggered, the

interrupt service routine must clear the request flag and the interrupt must be deasserted before the end of the interrupt service routine.

INT0

and INT1 inputs provide b oth t he cap ability t o exit from P ower-do wn mode o n low

level signals as detailed in section “Exiting Power-down Mode”, page 50.

is triggered by a low level at the

set the interrupt request flag IEn

Figure 24. INT1:0

INT0/1

Input Circuitry

0

1

IT0/1

TCON.0/2

IE0/1

TCON.1/3

EX0/1

IEN0.0/2

INT0/1

Interrup

Reques

10.5.2 KIN3:0 Inputs External interrupts KIN0 to KIN3 provide the capability to connect a matrix keyboard. For

detailed information on these inputs, refer to section “Keyboard Interface”, page 182.

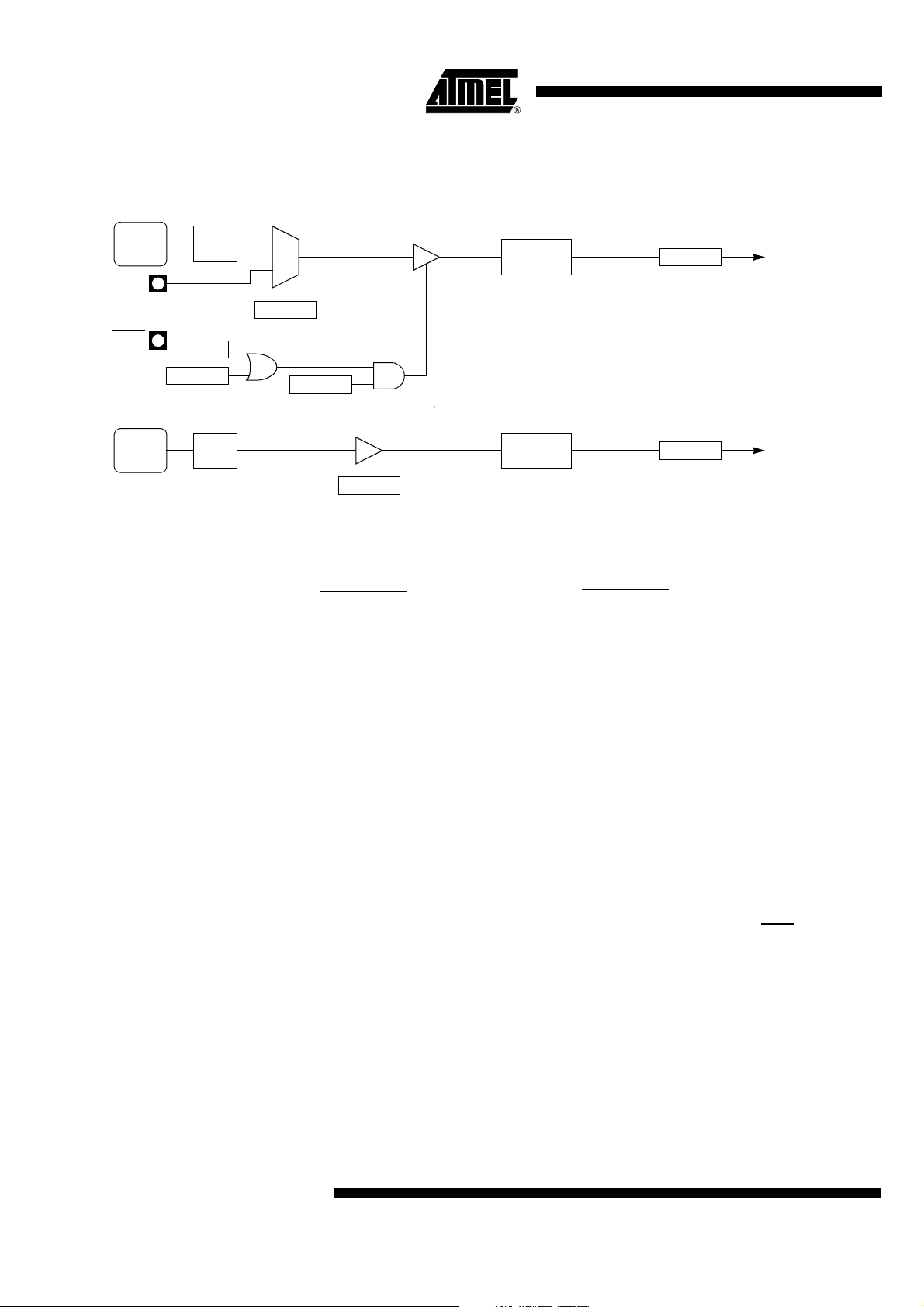

10.5.3 Input Sampling Ex ternal i nterrupt pi ns (INT1:0

and KIN3:0) are sampled once per peripheral cycle (6

peripheral clock periods) (see Figure 25). A le ve l- tr ig gered interrupt pin held low or hig h

for more than 6 peripheral clock periods (12 oscillator in standard mode or 6 oscillator

clock periods in X2 mode) guar antees detectio n. Edge-trigger ed external i nterrupts

must hold the request pin low for at least 6 peripheral clock periods.

Figure 25. Minimum Pulse Timings

Level-Triggered Interrupt

> 1 Peripheral Cycle

1 cycle

4109H–8051–01/05

Edge-Triggered Interrupt

> 1 Peripheral Cycle

1 cycle 1 cycle

41

AT8xC51SND1C

10.6 Registers Table 7. IEN0 Regi st er

IEN0 (S:A8h) – Interrupt Enable Register 0

76543210

EA EAUD EMP3 ES ET1 EX1 ET0 EX0

Bit

Number

7EA

6 EAUD

5EMP3

4ES

3ET1

2EX1

1ET0

Bit

Mnemonic Description

Enable All Interrupt Bit

Set to enable all interrupts.

Clear to disable all interrupts.