ATMEL AT48802-16QI, AT48802-16QC Datasheet

SpreadSpectrum

Signal

Processor

Integrated

Circuit

Preliminary

Features

0624A

Two Independent PN (Pseudo -Random Noise) Generators

•

Programmable R7 (128) to R13 (8 ,1 92 ) PN Sequence Lengths

•

Programmable Tau-Di ther Amplitude

•

Programmable PN Phase Adj ustment to 1/16 Chip

•

Correlation Acqui si tio n Interface

•

Programming Register Control

•

Microcontroller Com patible Bus Interface

•

Patent-Pending Fre qu en cy Dive rsity

•

Low Speed Link Data Path for Supe rvisory and Setup Func tio ns

•

Description

The AT48802 Spread-Spectrum Signal Processor (SSSP) chip from Atmel handles

all PN code generation, synchronization, and handshaking required for either station

(handset or base station) of a time division duplex direct sequence spread-spectrum

cordless telephone. The AT48802 supports RF spreading and despreading for the

best rejection of interference. In conjunction with a single-chip microcontroller, the

circuit performs the following functions:

• Generates a pseudo-random sequence for spreading the transmitted signal.

• Generates a pseudo-random sequence for despreading in the receiver.

• Generates a sliding phase PN for acquiring synchronization with an incoming

signal.

• Controls receive signal strength measurement timing for correlation peak

detection.

• Operates a tau-dither tracking loop, with adaptive threshold, to maintain

synchronization with the incoming signal.

• Controls transmit keying antenna switching for time-division duplexing.

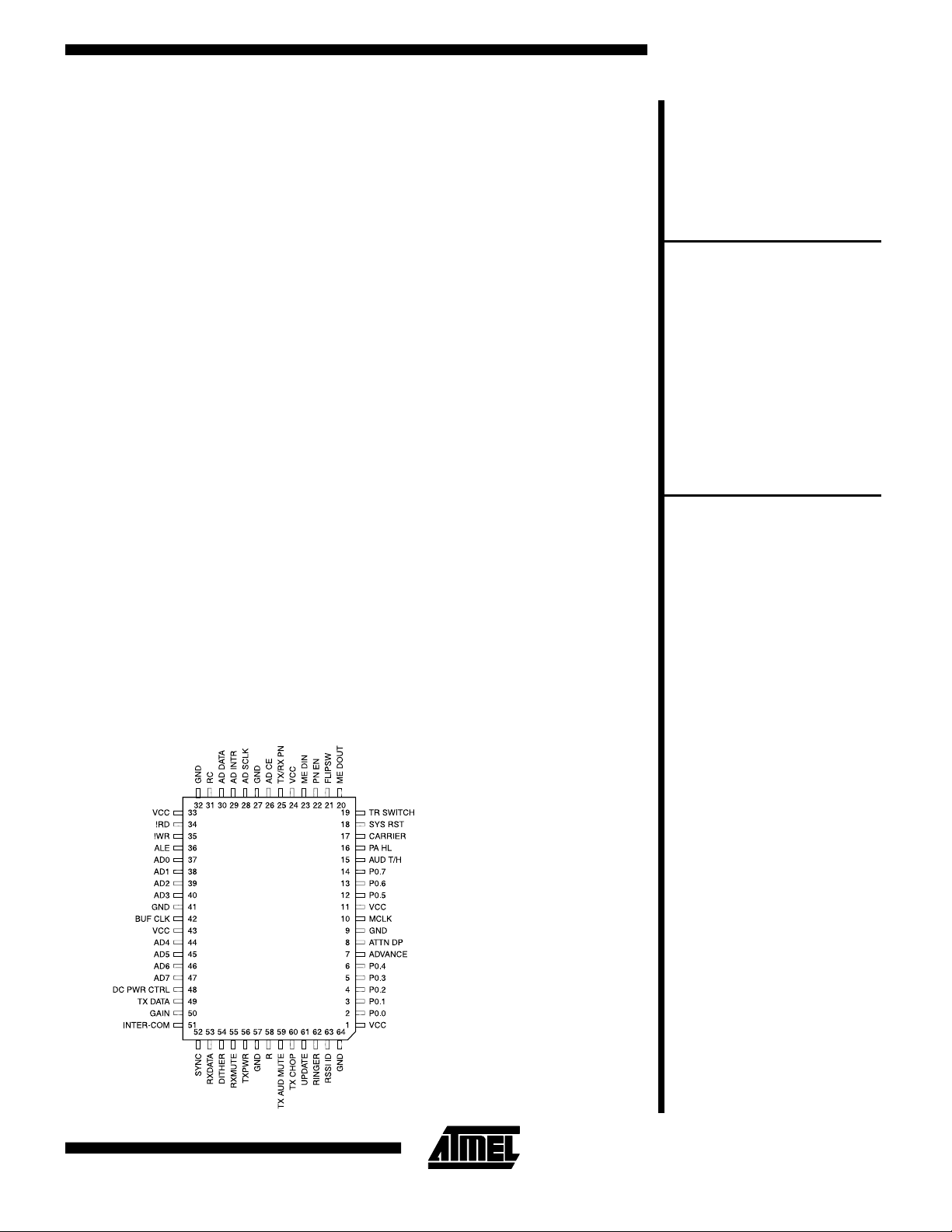

AT48802

Pin Configuration

(continued)

64 Lead PQFP

2-1

Description (Continued)

• Controls receive audio or data sampling time and

duration.

• Controls wake-up and sleep functionality for remote

battery operated handset.

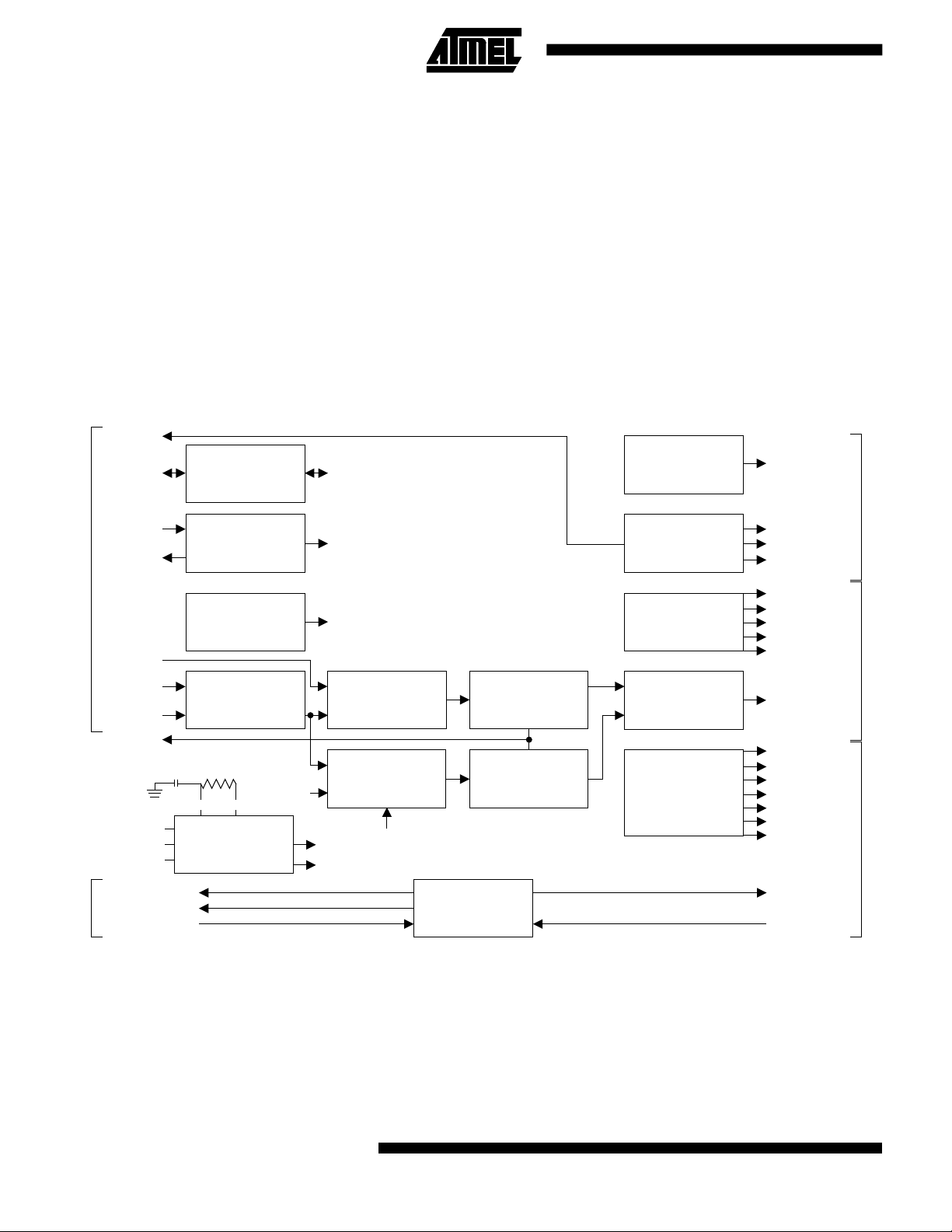

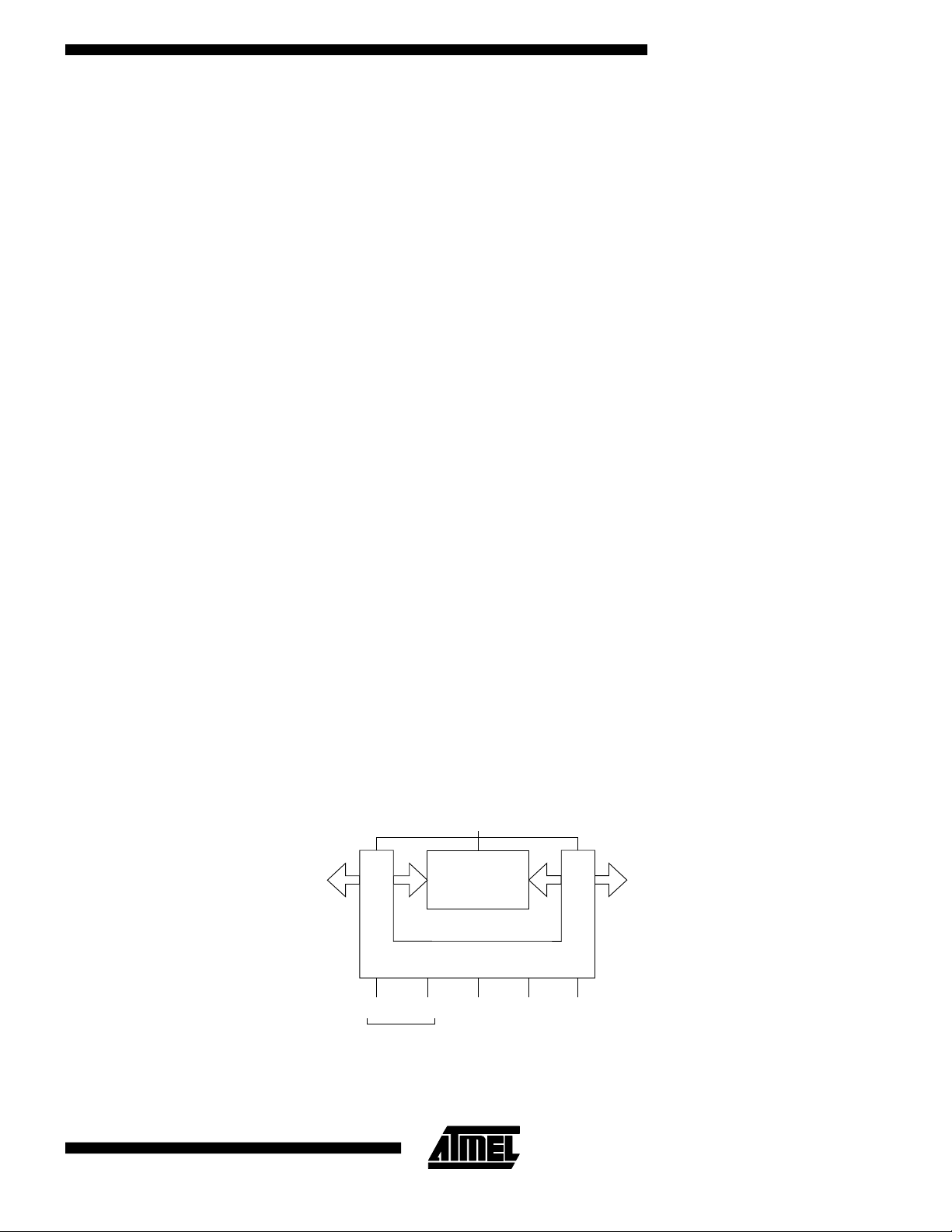

Block Diagram

AD INTR

BUS

MCLK

BUF CLK

µC

DITHER

UPDATE

ADVANCE

SYNC

* External Components

FLIPSW

INTERCOM

DC PWR CTRL

RX DATA

CARRIER DET

µC

TX DATA

BUS

INTERFACE

CLOCK

TIMING AND

SYNC GENERATOR

TDD

CONTROL

CHIP

PHASE

CONTROL

300K*

1000 pF

RC R

SLEEP/

WAKE

CONTROLS

MASTER

ALL BLOCKS

ALL BLOCKS

ALL BLOCKS

TAU

DITHER

GENERATOR

MUX

CLK

INTERNAL Ckts

I/Os

INTERNAL

The AT48802 unique spread-spectrum architecture capitalizes on the benefits of long range, signal-to-noise improvements, multi-path protection, and privacy. This design employs proven analog FM modulation to achieve the

lowest possible system cost yet the highest processing

gain and sound quality. The chip is a fully static design.

DATA

PATH

RECEIVE

PN

GENERATOR

TRANSMIT

PN

GENERATOR

RSSI

TIMING

A/D

INTERFACE

RF

CONTROLS

MUX AND

DIVERSITY

CONTROL

AUDIO

CONTROLS

RSSI D/I

A/D CLOCK

A/D DATA

A/D CE

TX PWR

TR SW

GAIN

PN EN

PA HI/LO

TX RX PN

TX AUD MUTE

RX MUTE

TX CHOP

AUD T/H

AUX T/H

RINGER

ATTN DP

ME DOUT

ME DIN

RSSIRSSI

RF

AUDIO AND LINE

2-2 AT48802

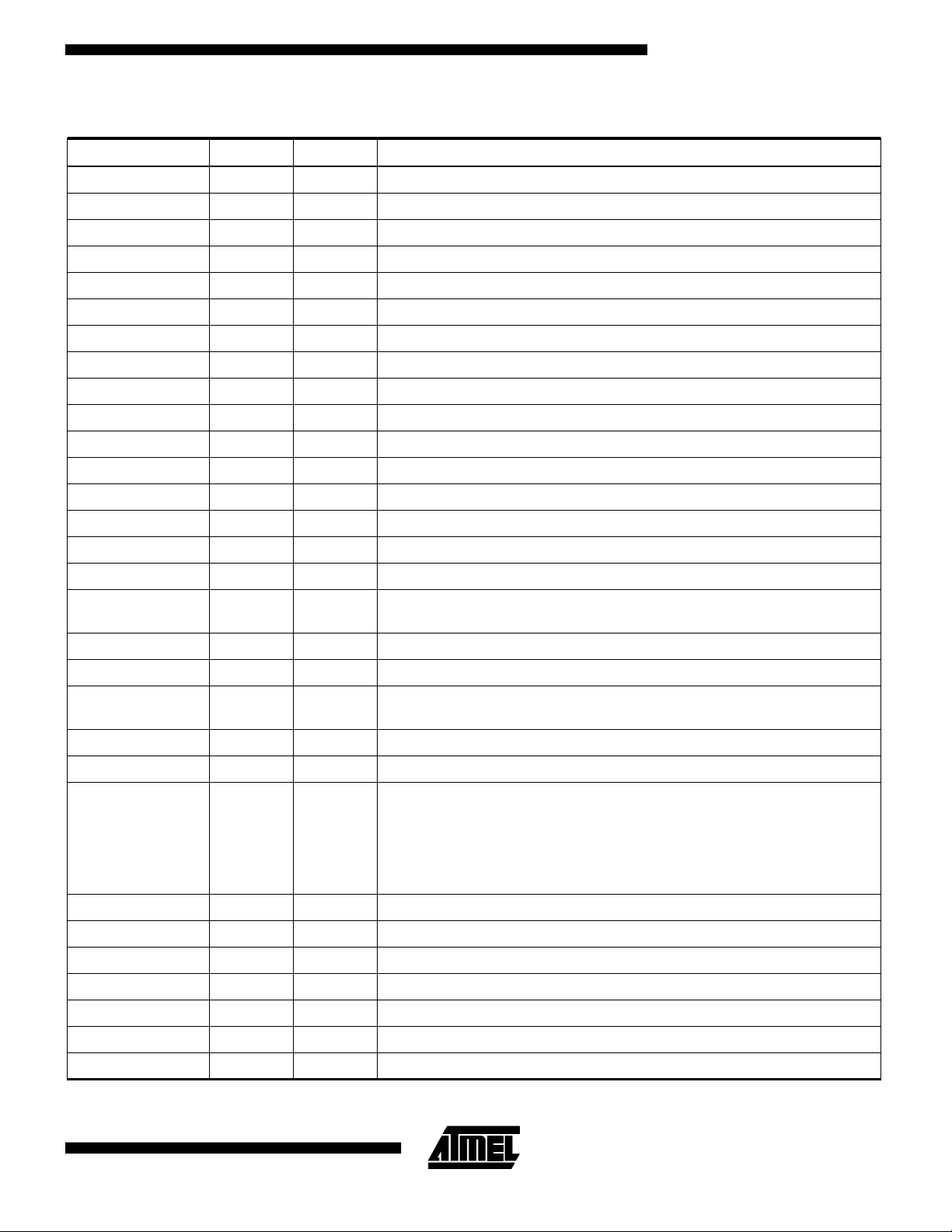

AT48802

Pin Description

Name Pin# I/O/T Description

AD CE 26 O Chip enable for external A/D converter, true = low.

AD DATA 30 I 8 bit serial input for external A/D.

AD INTR 29 O Interrupt to controller to read A/D data, true = high.

AD SCLK 28 O Clock for A/D converter.

ADVANCE 7 I Advance or retard the chip phase. High = advance.

AD0 37 I/T General purpose bi-directional port for microcontroller interface.

AD1 38 I/T General purpose bi-directional port for microcontroller interface.

AD2 39 I/T General purpose bi-directional port for microcontroller interface.

AD3 40 I/T General purpose bi-directional port for microcontroller interface.

AD4 44 I/T General purpose bi-directional port for microcontroller interface.

AD5 45 I/T General purpose bi-directional port for microcontroller interface.

AD6 46 I/T General purpose bi-directional port for microcontroller interface.

AD7 47 I/T General purpose bi-directional port for microcontroller interface.

ALE 36 I Address Latch Enable for port AD. Down edge latches.

ATTN DP 8 O Can drive dial pulse relay or other function.

AUD T/H 15 O Driver for audio track and hold.

BUF CLK 42 O

CARRIER 17 O Internal data path, high = carrier present.

DC PWR CTRL 48 O Can control a V

DITHER 54 O

FLIPSW 21 I A programmable transition on this pin will cause the chip to wake-up.

GAIN 50 O May be used to control RF receive gain.

9

27

GND

INTERCOM 51 I A programmable transition on this pin will cause the chip to wake-up.

MCLK 10 I High speed clock input to chip.

ME DIN 23 I Internal data path input from RF module.

ME DOUT 20 O Internal data output to RF module.

32

41

57

64

I DC power return = 0 Volts

Replica of MCLK high speed clock input, for driving microcontroller

clock input.

switch to turn on and off the other circuits.

CC

Indicates whether the tau-dither state is retarded or not retarded. High

= retarded.

P0.0 2 O General purpose output port.

P0.1 3 O General purpose output port.

P0.2 4 O General purpose output port.

(continued)

2-3

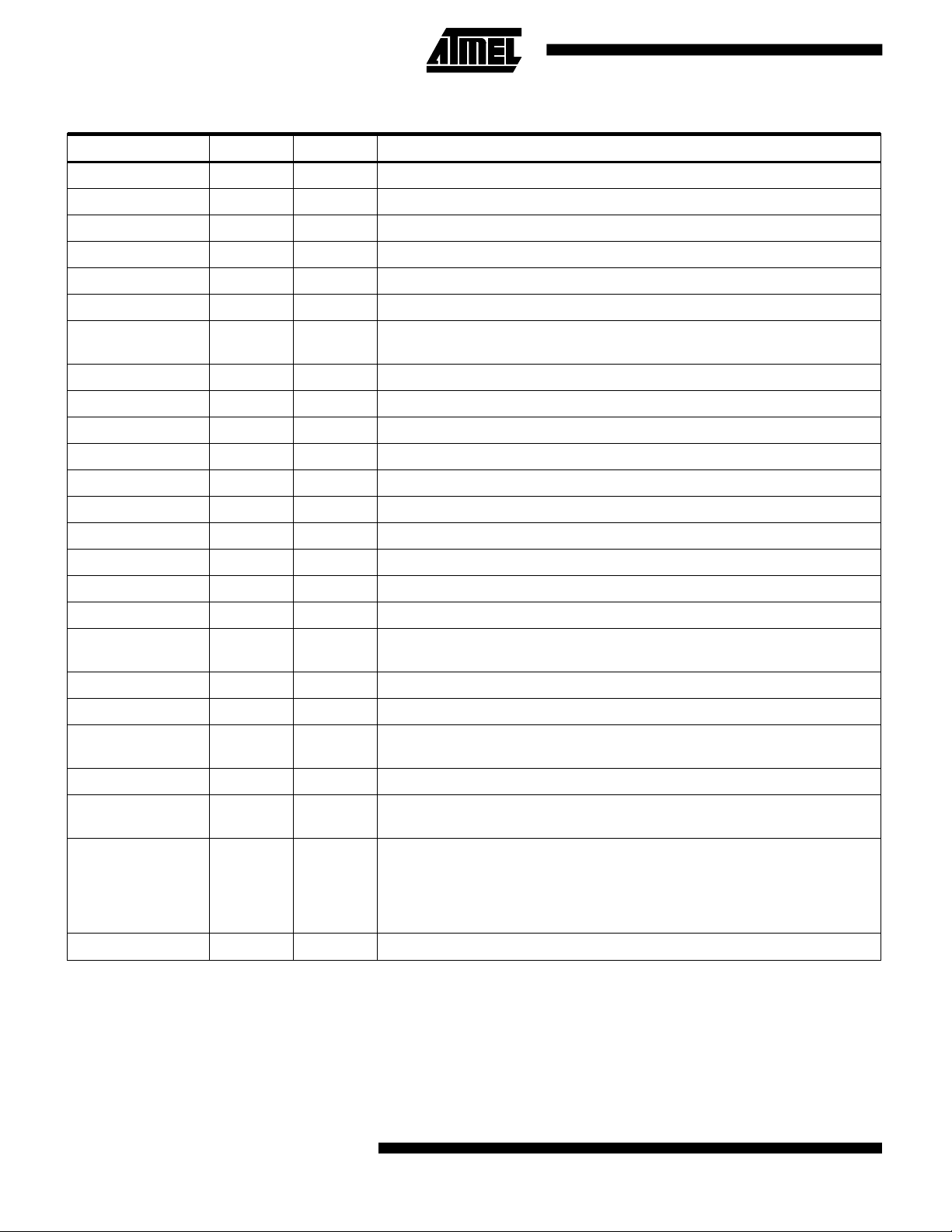

Pin Description (Continued)

Name Pin# I/O/T Description

P0.3 5 O General purpose output port.

P0.4 6 O General purpose output port.

P0.5 12 O General purpose output port.

P0.6 13 O General purpose output port.

P0.7 14 O General purpose output port.

PA HL 16 O May be used to control a switch which controls the RF transmit power.

PN EN 22 T

R 58 O Low speed clock oscillator for sleep control.

RC 31 I Low speed clock oscillator for sleep control.

!RD 34 I Read strobe input for port AD, low = true.

RINGER 62 O Ring control output.

RSSI ID 63 O RSSI integrate/dump control.

RX DATA 53 O Internal data path output to microcontroller.

RX MUTE 55 O Mute receive audio.

SYNC 52 T PN epoch sync for receive, transmit or both.

SYS RST 18 I Not a user control. Hold high always.

TR SWITCH 19 O Controls state of RF module transmit/receive switch.

TX CHOP 60 O

TX DATA 49 I Internal data path input from microcontroller.

TX AUD MUTE 59 O For disconnecting transmit audio when data must be transmitted.

TX PWR 56 O

TX/RX PN 25 T Pseudo-noise sequence to RF module.

For controlling whether the RF module runs on spread-spectrum or

narrowband.

Controls switch to disconnect audio from RF module modulation input

during receive part of TDD.

Turns on RF module transmit power during transmit part of TDD, and

off during receive part of TDD.

UPDATE 61 I

1

11

V

CC

!WR 35 I Write strobe for Port AD. Low = true.

2-4 AT48802

24

33

43

Causes chip phase control to step the phase. Used in conjunction with

ADVANCE pin 7.

DC power input = +V

CC

Volts.

AT48802

Time Division Duplex Architecture

The AT48802 processor supports a Time Division Duplex

(TDD) mode of operation where the transceiver transmits

information during one time period and receives during an

alternating time period. This architecture has the benefit of

optimizing the frequency channel utilization as the transmit and receive frequencies can be equal to or close to

one another, without spreading at two frequencies that are

wide apart. The chip generates all TDD signals , (including

those signals that account for time delays through the RF

transceiver) that are necessary to implement a full-duplex

voice communication system. All internal timing is derived

from a master external clock. The chip is fully static and

can work at any clock frequency less than 20 MHz. In all

the following discussions the clock rate is assumed to be

15.360 MHz which is available from the companion RF

module.

The 15.360 MHz master clock is internally divided down to

a 7.5 kHz TDD rate, alternating between transmit cycle

and receive cycle. That is, the transmit and r eceiv e cycles

last for 66.67µs.

Sleep Mode and Battery Functionality

In most battery applications it is necessary to power down

one end of the communication link except when a call is to

be made. The sleep mode circuits of the AT48802 control

this function.

The sleep mode circuits consist of a timer which runs from

a low frequency (4 kHz) RC oscillator and a set of latches

to interact with the rest of the chip which runs from the high

frequency clock input. The sleep mode circuits also can

also disable and protect the I/O’s of the high frequency

circuits. The protected mode is such that the outputs are

three-stated and the input is floating. In addition, the sleep

control section has a DC power control output which can

be used to shutdown external circuits V

The chip should always be connected to V

CC

.

CC

in order for

the sleep mode to be usable; the sleep mode circuits are

alive and running as long as V

is applied, however their

CC

power drain is extremely small.

The sleep circuits will wake-up the chip, and other circuits

if desired, in any one of three ways.

1. Time-out from the 4 kHz Oscillator will happen about

2 seconds (one half cycle of divided by 214 ) after going to sleep. Then the remote set could, for example,

briefly listen for an incoming call using narrowband reception (which has little or no acquisition time), and

listen for a predetermined tone with a very narrowband filter. For different wake-up periods the value of

the C can be changed.

2. If the INTERCOM input is activated. The edge sense

is programmable at R6 b7.

3. If the FLIPSW input is activated. The edge sense is

programmable at R11 b7.

When the chip wakes up it stores information about the

reason for wake-up in the I/O Registers at R14 b0-2 so the

microprocessor can respond in a suitable way. The edge

sense for FLIPSW and INTERCOM are programmed at

R14 b4-5. (Note: Throughout this document “Rx by”

means Register x bit y; x is hexadecimal.)

Once the chip is awake, only the microprocessor can put

it back into sleep mode. It does this through the bus port

at R0 b7. The OPERATE bit must be set before the command to STANDBY can be recognized. If the chip is

awake and the user activates the INTERCOM or FLIPSW

inputs, then the microprocessor can sense these actions

at R14 b4-5.

Figure 1. Sleep Mode Arrangement

High Speed I/Os

Sleep Mode Circuits

C

Low

Clock

Speed

R

V

CC

High Speed

Processing

Circuits

DC Power CTRL

FLIPSW

High Speed I/Os

(Operate/!Standby

and Wake 0, Wake 1)

INTERCOM

2-5

PN Code Generation

The AT48802 contains two independently programmable

pseudo-random noise (PN) generators. One is used for

transmit and the other is for receive. They are 13-stage

linear feedback shift registers clocked at f(master clock) /

16, or the “chip rate”, normally 960 kHz (based on a 15.36

MHz master clock). Each can be programmed to operate

with lengths of 7 to 13-stages PN (8,192 bit code sequence length). These lengths are actually linear maximal

lengths plus one to simplify the internal circuitry. The long

code length has the benefit of having many different maximal-length codes available for co-location operation in

similar spread-spectrum equipment with minimum mutual

interference, thus allowing efficient use of frequency channels. For example, there are over 600 maximal-length sequences available for R13 PN, and over 300 for R11 PN.

Each maximal-length code can be considered a unique

user channel.

The “Mask” bit in each PN register controls the counter

sequence by setting feedback tap weights to either 0 or 1.

The Transmit PN Generator (Tx PN) output and the Receive PN Generator (Rx PN) output are time division multiplexed precisely by the 50% duty-cycle TX PWR signal.

That is, during the transmit cycle, only the Tx PN codes

are outputted at the TX/RX PN pin. Conversely during the

receive cycle, only the Rx PN codes are outputted. There

is no prohibition against using the same code for transmit

and receive. The shift register taps are set at R2 b0-4 and

R1 b0-7 for receive, and R4 b0-4 and R3 b0-7 for transmit.

For definition purposes the end of the link which is initiating the link is the MASTER, and the end which is responding is the SLAVE. This means, e.g., for a cordless phone,

if you are calling out then the handset becomes the MASTER and the base station is the SLAVE. If someone is

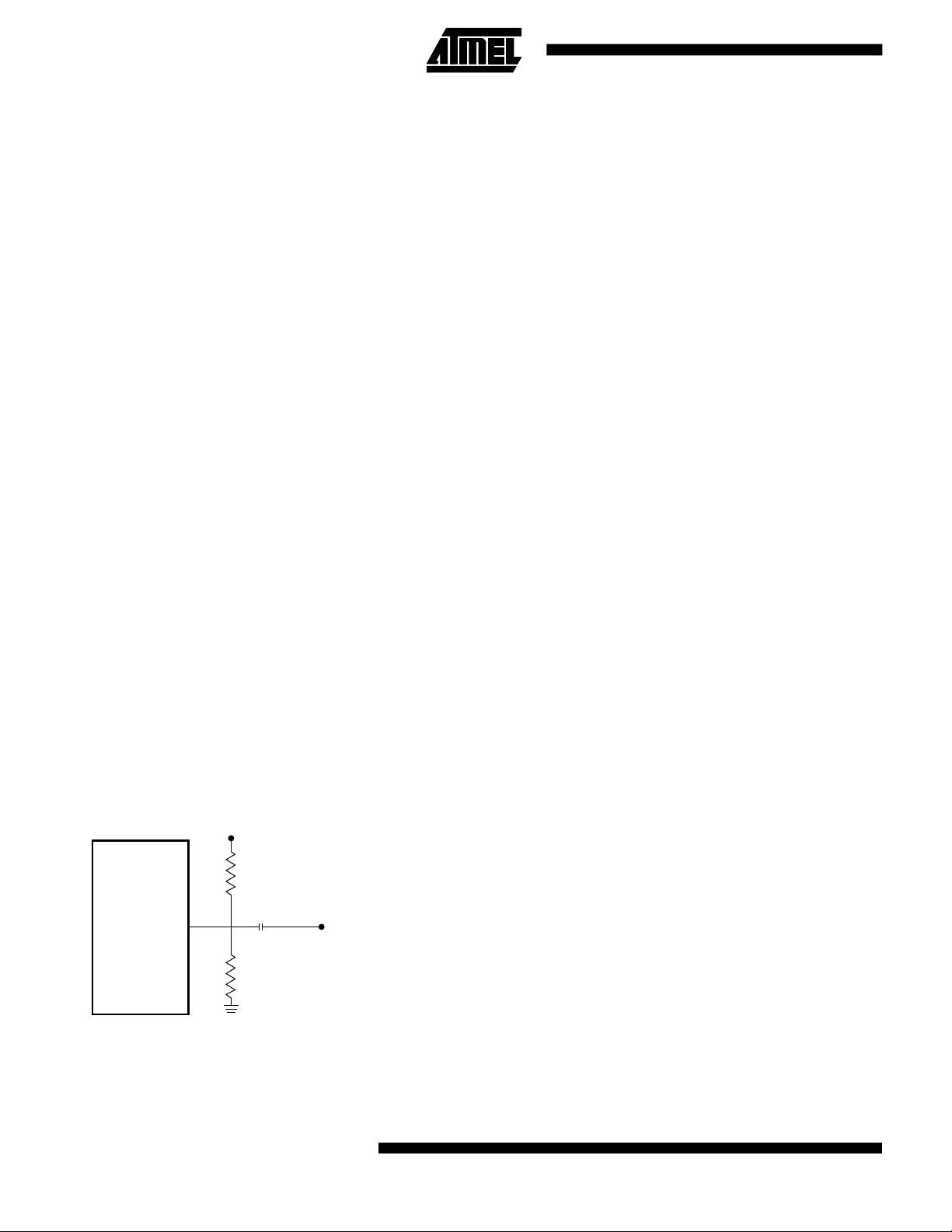

Figure 2. PN Coupling for Spectral Control

V

CC

AT48802

470

TX_RX_PN

0.1 uF

R is chosen to make the immediate

R

value of PN output equal to V /2

To RF Circuit

CC

calling you, then the base station is the MASTER (because it is initiating the radio link) and the handset is the

SLAVE. This function is set at R0 b6.

If the chip is the MASTER, then the transmit PN generator

is clocked from the clock generator and the receive PN

generator is clocked from the chip phase control (through

the tau-dither generator). If the chip is the SLAVE, then

both PN generators are clocked from the chip phase control. Therefore the MASTER transmit has independent timing and the SLAVE locks both PN generators, via the chip

phase control, to the receive signal. Finally, the MASTER

receive PN uses the chip phase control to lock to its received signal from the SLAVE. In this way one can see the

outline of an acquisition process.

The AT48802 PN spectral control feature enables the radio frequency transmit spectrum to easily meet the FCC

requirement that out-of-band energy in a 100 kHz bandwidth be at least 20dB below in-band maximum energy in

the same bandwidth. By this means one can achieve more

spreading and more widely spaced frequency channels

with less output filtering and still meet the requirements.

The TX RX PN output is three-stated for one MCLK (master clock, the 15.36 MHz input ) at each transition. By

means of external pull resistors, this makes the PN voltage waveform rest at V

/2 for 60 ns on every transition.

CC

The objective is that the RF transmit power should go to

zero during these periods. This introduces a spectral

notch at 7.5 MHz on each side of center. If this waveform

is faithfu lly preserved by the spreading mixer and subsequent amplifiers then the RF transmit spectrum will

have nulls near ±7.5 MHz. This reduces the normal PN

lobes which might otherwise exceed allowed amplitude. A

particular application may or may not need this feature; for

example, if only one frequency channel is being used, and

it is in the center of the band, then depending on the output

filter one may not have this problem. In such a case a simple lowpass filter may be used from the PN generator output to the RF module PN input.

A force-load function is provided for initializing the PN generator to ensure the transmit and receive PN generator

coefficients can be loaded into the counters without locking up during the first-time loading after a power up cycle.

This is common among multiple feedback PN counters.

The force-load bit can be set by a logic 1 to the FLO AD bit

in the control register (Register 0, bit 1).

The Transmit PN and the Receive PN counters can be

synchronized by asserting a logic 1 to the PN RESET bit

in the control register (Register 0, bit 0). The PN OUT

function at R0 b5 turns on the PN when set.

2-6 AT48802

AT48802

Frequency Diversity Impr oves

Signal-to-Noise Rati o

Built into the AT48802 is an exclusive frequency diversity

function, which enhances protection from PN noise due to

imperfect correlation. The chip encodes the PN code sequence such that when spread, the information is modulated and transmitted redundantly in two side lobes. That

is, the red undant information is contained in two main

lobes with a null at the carrier instead of the classical single lobe spreading spectra. The spreading bandwidth also

doubles, effectively doubling the spreading chip rate. This

has the benefit of increased processing gain and greatly

reducing the residual PN noise near the carrier after correlation. The frequency diversity can be user enabled by

setting the BW (Band-Width) bit high in the PN register

(Register 2, bit 7 for Receive PN, and Register 4, bit 7 for

Transmit PN). The transmit and receive PN generators are

set independently.

Chip Phase and Tau-Dither Control

The chip phase control circuit enables the user to step the

chip phase in either direction by amounts from 1/16 to 8/16

chip per update. The size of the step is set in R5 b0-2, the

step direction is controlled by the ADVANCE line, and the

command to do a step is by pulsing the UPDATE line. The

maximum allowed update rate is MCLOCK/32.

The tau-dither circuit is used to assist in the tracking a correlation peak. This is done as follows. When the locally

generated receive PN is a good match to the incoming signal at RF, then the RF signal is accurately despread and

the signal energy is gathered into a narrow spectral region

around the carrier. If a narrow IF filter is used to filter this

signal, then when the chip phase match to the incoming

signal is good then the most possible power will get

through the narrow IF filter; when the chip phase is advanced or retarded from the best place, then the signal

power in a narrow band will fall. The tau-dither circuits,

when activated, step the PN chip phase back and forth by

a settable amount at a rate of TDD/2. If one looks at the

RF module RSSI (receive signal strength indicator) by using the A/D converter interface, then when the PN phase

is, on the average, optimum then the alternating output of

RSSI will show small variation at a rate of TDD/2. If the

peak is not centered, then the RSSI variation at TDD/2

measured through the A/D converter interface, will become larger because one phase of tau-dither will produce

less RSSI than the other. Now one can track the peak by

using the microprocessor to close this control loop which

has as an input to the RSSI variation at TDD/2 measured

through the A/D converter interface and has output using

the UPDATE and ADVANCE controls. The control loop

should null the TDD/2 signal.

The available tau-dither amounts are 1/16 chip peak-topeak, to 15/16 chip peak-to-peak, set at R5 b3-5. Dither

on/off is controlled via R0 b4 (track = high = dither on ).

The tau-dither phase is actually only a retard or no retard

with respect to the chip phase when tau-dither is off, this

is a detail which the control system designer may need.

If the tau-dither amplitude is changed it will not take affect

until the receive PN code is reloaded. The DITHER output

of the chip tells the microprocessor whether the dither

phase is retarded (High) or not retarded. High is retarded.

RSSI Interface

The purpose of this circuitry is to provide an interface to a

serial A/D converter and an integrate/dump filter, if desired. The interface is synchronized to TDD. The data from

the A/D converter is converted to parallel and loaded to

the register at R8 b0-7. The RSSI function provides an integrated/dump command output with timing completely

adjustable throughout the TDD cycle and also completely

adjustable for pulse width, except the hardware will not allow the timing of RSSI ID to conflict with the A/D converter

command. This allows optimum filtering of the RSSI signal

if desired. The adjustable timing is necessary to allow for

different RF designs with different amounts of delay in the

IF filter. The sense of the RSSI ID output, that is, which

way is integrate and which way is dump, is controlled via

RC b6-7

RSSI ID timing is set via RC b0-5 for delay and RD b0-5

for pulse width. The smallest step is MCLK/32 = 2 us for a

15.36 MHz clock. The 5 bits allow adjustment over a range

of TDD/2. In order to get the other half TDD cycle, one

must invert the RSSI ID bits at RC b6-7, which will invert

the waveform.

Figure 3 shows the A/D converter timing for a converter

such as the Linear Technology LTC 1196 National Semiconductor ADC0831 or similar.

2-7

Loading...

Loading...