Datasheet AT45D011-XI, AT45D011-XC, AT45D011-SI, AT45D011-SC, AT45D011-JI Datasheet (ATMEL)

...

Features

•

Single 4.5V - 5.5V Supply

•

Serial Interface Arch itec ture

•

Page Program Operation

– Single Cycle Reprogram (Erase and Program)

– 512 Pages (264 Bytes/Page) Main Memory

•

Optional Page and Block Erase Operations

•

One 264-Byte SRAM Data Buffer

•

Internal Program and Control Timer

•

Fast Page Program Time – 7 ms Typical

µµµµ

•

120

s Typical Page to Buffer Transfer Time

•

Low-Power Dissipation

– 15 mA Active Read Current Typical

µµµµ

–10

A CMOS Standby Current Typical

•

15 MHz Max Clock Frequency

•

Hardware Data Protection Feature

•

Serial Peripheral Interface (SPI) Compatible – Modes 0 and 3

•

CMOS and TTL Compatible Inputs and Outputs

•

Commercial and Industrial Temperature Ranges

1-Megabit

5.0-volt Only

Serial

DataFlash

®

Description

The AT45D011 is a 5.0- volt only, serial interfac e Fl as h m emo ry s ui table for in-system

reprogramming. Its 1,081,344 bit s of memory are organized as 512 pag es of 264

bytes each. In additi on to the mai n memory, the AT45D 011 also co ntains on e SRAM

data buffer o f 26 4 byte s. U nlik e c onven tiona l Fl ash m em ories tha t are acc essed ra ndomly with multiple ad dres s l in es and a pa rall el inte r fac e, th e Dat aFla sh uses a serial

interface to sequentially access its data. The si mple serial inter face facilitates hard-

(continued)

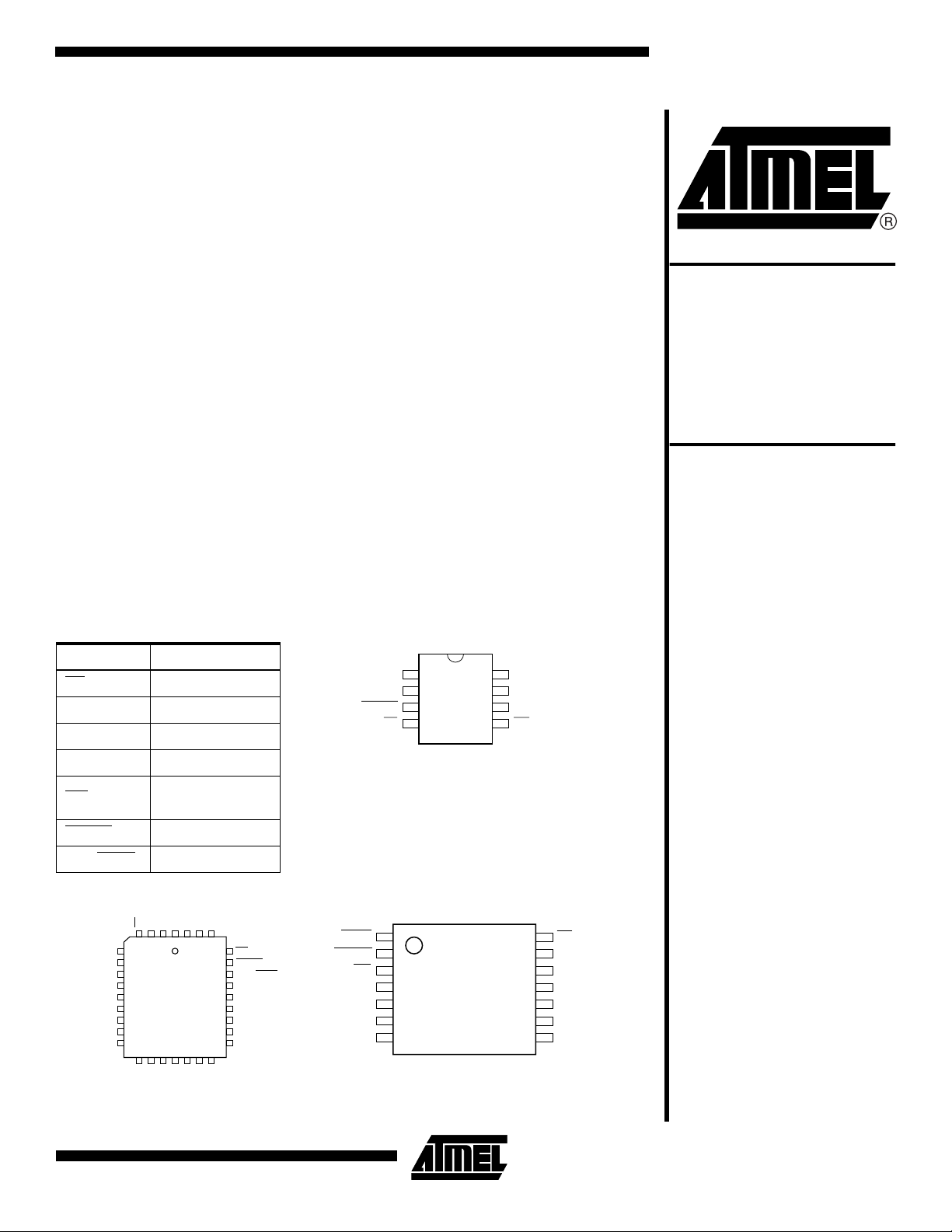

Pin Configurations

Pin Name Function

CS

SCK Serial Clock

SI Serial Input

SO Serial Output

WP

RESET Chip Reset

RDY/BUSY Ready/Busy

SCK

SI

SO

NC

NC

NC

NC

NC

NC

Note: PLCC package pins 16

and 17 are DON’T CONNECT

Chip Select

Hardware Page

Write Protect Pin

PLCC

CSNCNC

GND

432

5

6

7

8

9

10

11

12

13

1

14151617181920

NCNCDCDCNCNCNC

VCCNCNC

323130

29

28

27

26

25

24

23

22

21

WP

RESET

RDY/BUSY

NC

NC

NC

NC

NC

NC

SI

SCK

RESET

CS

RDY/BUSY

RESET

WP

VCC

GND

SCK

SO

SOIC

1

2

3

4

TSSOP Top View

Type 1

1

2

3

4

5

6

7

SO

8

GND

7

VCC

6

WP

5

14

CS

13

NC

12

NC

11

NC

10

NC

9

NC

8

SI

AT45D011

Preliminary

AT45DB011

Preliminary 16Megabit 2.7-volt

Only Serial

DataFlash

Rev. 1123A–08/98

1

ware layout, increases system reli ability, mini mizes sw itching noise, and reduces package size and active pin count.

The device is optimized for use in many commercial and

industrial applications where high density, low pin count,

low voltage, and low power are essential. Typical applications for the DataFlash are digital voice storage, image

storage, and data storage. The device operates at clock

frequencies up to 15 MHz with a typica l activ e read cu rrent

consumption of 15 mA.

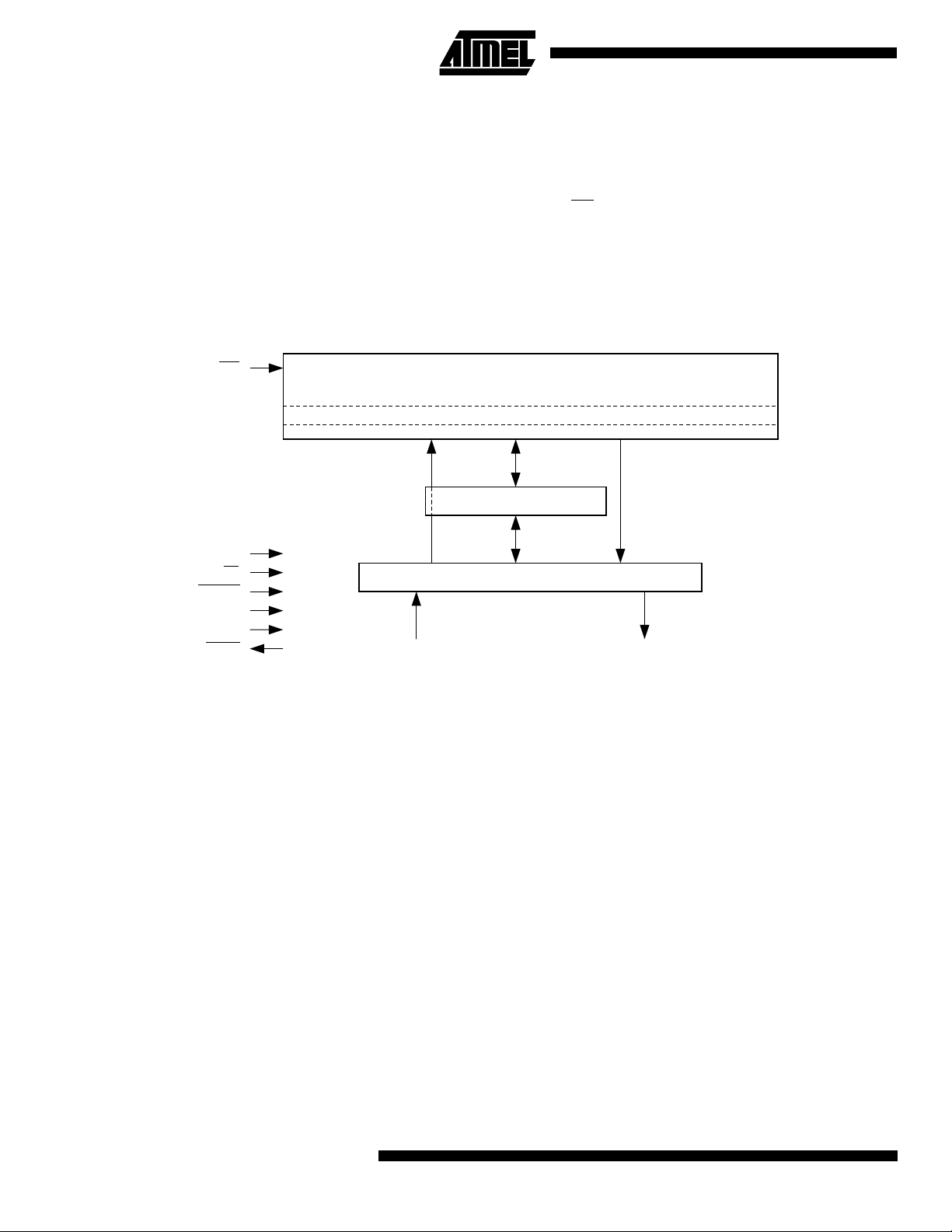

Block Diagram

To allow for simple in-system reprogrammability, the

AT45D011 does not require high input voltages for programming. The devi ce operate s from a s ingle po wer supply, 4.5V to 5.5V, for both the program and read

operations. The AT45D011 is enabled through the chip

select pin (CS

) and accessed via a three-wire interface

consisting of the Serial Input (SI), Serial Output (SO), and

the Serial Clock (SCK).

All programming cycles are self-timed, and no separate

erase cycle is required before programming.

WP

PAGE (264 BYTES)

BUFFER (264 BYTES)

SCK

CS

RESET

V

CC

GND

RDY/BUSY

Memory Array

To provide optimal flexibility, the memory array of the

AT45D011 is divided into three levels of granularity comprising of sectors, bl ocks, and page s. The Memory Arch itecture Diagram illustrates the breakdown of each level and

FLASH MEMORY ARRAY

I/O INTERFACE

SOSI

details the number of pages per sector and block. All pr ogram operations to the DataFlash occur on a page by page

basis; however, the optional erase operations can be performed at the block or page level.

2

AT45DB011

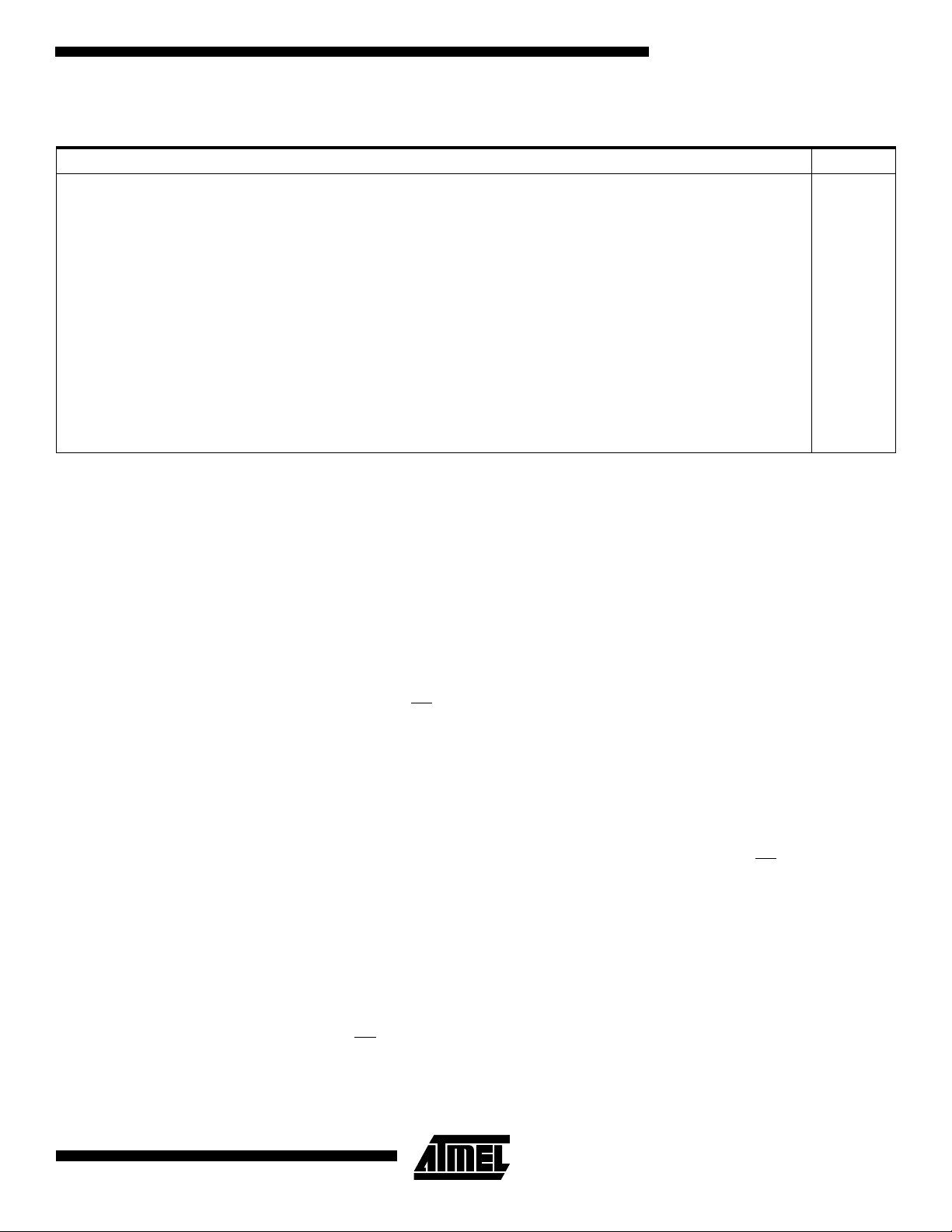

Memory Architecture Diagram

AT45DB011

SECTOR ARCHITECTURE

SECTOR 0 = 2112 BYTES (2K + 64)

SECTOR 1 = 65,472 BYTES (62K + 1984)

SECTOR 2 = 67,584 BYTES (64K + 2K)

SECTOR 0

BLOCK ARCHITECTURE PAGE ARCHITECTURE

8 Pages

BLOCK 0

BLOCK 1

PAGE 14

PAGE 15

PAGE 16

PAGE 17

PAGE 18

PAGE 509

PAGE 510

PAGE 511

Page = 264 bytes

SECTOR 1SECTOR 2

BLOCK 0

BLOCK 1

BLOCK 2

BLOCK 3

BLOCK 29

BLOCK 30

BLOCK 31

BLOCK 32

BLOCK 33

BLOCK 34

BLOCK 61

BLOCK 62

BLOCK 63

Block = 2112 bytes

(2K + 64)

PAGE 0

PAGE 1

PAGE 6

PAGE 7

PAGE 8

PAGE 9

(256 + 8)

Device Operation

The device operation is controlled by instructions from the

host processor. The l is t o f in st ru cti on s a nd thei r as so ci ated

opcodes are contained in T able 1 and Table 2. A valid

instruction starts with the falling edge of CS

appropriate 8-bit opcode and the desired buffer or main

memory address loc ati on. Whi le the CS

the SCK pin controls the loading of the opcode and the

desired buffer or main memory address location through

the SI (serial input) pin. All instructions, addresses, and

data are transferred with the most significant bit (MSB) first.

Read

By specifying the appropriate opcode, data can be read

from the main memory or from the data buffer.

MAIN MEMORY PAGE READ:

the user to read data directly from any one of the 512

pages in the main memory, bypassing the data buffer and

leaving the contents of the buffer unchanged. To start a

page read, the 8-bit opcode, 52H, is followed by 24

address bits and 32 don’t care bits . In the AT45D011, the

first six address bits are reserved for larger density devices

(see Notes on page 10), the next nine address bits (PA8PA0) specify the page address, and the next nine address

bits (BA8-BA0) specify the starting byte address within the

page. The 32 don’t care bits which follow the 24 address

A main memory read allows

followed by the

pin is low, toggl in g

bits are sent to initialize the read operation. Following the

32 don’t car e bit s, ad diti onal puls es o n SCK res ult i n se ria l

data being output on the SO (serial output) pin. The CS

pin

must remain low during the loading of the opcode, the

address bits, and the reading of data. When the end of a

page in main memory is reached during a m ain memory

page read, the device will continue reading at the beginning

of the same page. A low to high transition on the CS

pin will

terminate the read operation and tri-state the SO pin.

BUFFE R RE AD:

Data can be read from the data buffer

using an opcode of 54H. To perform a buffer read, the eight

bits of the opcode m ust be foll owed by 15 don ’t care bits,

nine address bits, and eight don't care bits. Since the buffer

size is 264-bytes, nine address bits (BFA8-BFA0) are

required to specify the firs t b yte of data to be re ad f ro m th e

buffer. The CS

pin must remain low during the loading of

the opcode, the address bits, the don’t care bits, and the

reading of data. When the end of the buf fer is rea ched, the

device will continue reading back at the beginning of the

buffer. A low to high t ransi tion on th e CS

pin will ter minat e

the read operation and tri-state the SO pin.

MAIN MEMORY PAGE TO BUFFER TRANSFER:

A page

of data can be tran sf er re d f rom t he main memory to buf fer .

An 8-bit opcode of 53H is followed b y the si x res er ve d b its,

nine address bits (PA 8-PA0) which specify the page in

3

main memory that is to be transferred, and nine don’t care

bits. The CS

pin must be low while toggling the S CK pin t o

load the opcode , the ad dress bi ts, and the don’t care b its

from the SI pin. The tran sfer of the pag e of data from th e

main memory to the buffer wi ll beg in when the CS

pin transitions from a low to a h igh state. During t he transfer of a

page of data (t

), the status register can be read to deter-

XFR

mine whether the transfer has been completed or not.

MAIN MEMORY PAGE TO BUFFER COMPARE:

A page of

data in main memor y can be compa red to the da ta in the

buffer. An 8-bit opcode of 60H is followed by 24 address

bits consisting of the six reserved bits, nine address bits

(PA8-PA0) which specify the page in the main memory that

is to be compared to the buffer, and nine don’t care bits.

The loading of the opcode and the address bits is the same

as described previously. The CS

pin must be low while toggling the SCK pin to load the opcode, the address bits, and

the don't care bits from the SI pin. On the low to high transition of the C S

pin, the 264 bytes in the selected main memory page will be co mpared wi th the 2 64 by tes in the buf fer.

During this time (t

), the status register will indicate that

XFR

the part is busy. On completion of the compare operation,

bit 6 of the status register is updated with the result of the

compare.

Program

BUFFER WRITE:

into the data buffer. To load data into the buffer, an 8-bit

opcode of 84H is followed by 15 don’t care bits and nine

address bits (BFA 8-BFA0). T he nine addre ss bits spe cify

the first byte in the buffer to be written. The data is ente red

following the address bits. If the end of the data buffer is

reached, the device wil l w ra p arou nd b ac k to the beg inn in g

of the buffer. D ata wi ll con tinue to be loaded i nto t he bu ffer

until a low to high transition is detected on the CS

BUFFER TO MAIN MEMORY PAGE PROGRAM WITH

BUILT-IN ERASE:

grammed into the main me mory. An 8-bit opcode of 83H is

followed by the six rese rved bits, nine ad dress bits (PA 8PA0) that specify the page in the main memory to be written, and nine additional don ’t car e bits. When a low to high

transition occurs on the CS

selected page in main memory to all 1s and then program

the data stored in the buffer into the spe cified page in the

main memory. Both the erase and the programming of the

Data can be shif ted in from the SI pi n

pin.

Data written into the buffer can be pro-

pin, the part will first erase the

page are internally self timed and should take place in a

maximum time of t

. During this time, the status register

EP

will indicate that the part is busy.

BUFFER TO MAIN MEMORY PAGE PROGRAM WITHOUT BUILT-IN ERASE:

A previously erased page within

main memory ca n be program med w ith th e co ntents of th e

buffer. An 8-bit opcode of 88H is followed by the six

reserved bits, nine address bits (PA8-PA0) that specify the

page in the main me mor y to be written, and nine addi ti ona l

don’t care bits. When a lo w to high tran sitio n occurs on the

pin, the part will program the data stored in the buffer

CS

into the specified pag e in the main memory. It is nec es sary

that the page in main memory that is being programmed

has been previously er ased. The pr ogram ming of the pag e

is internally self timed and should take place in a maximum

time of t

. During this time, the status register will indicate

P

that the part is busy.

PAGE ERASE:

The optional Page Erase comma nd can b e

used to individually er ase any page in the main memory

array allowing the Buffer to Main Memory Page Program

without Built-In Erase command to be utilized at a later

time. To perform a P age E rase , an op co de of 8 1H must be

loaded into the device, followed by six reser ved bits, nine

address bits (PA8 -PA0), and ni ne don’t c are bits. The nine

address bits are used to specify whi ch page of the memo ry

array is to be erased. Wh en a low to hig h transiti on occu rs

on the CS

pin, the part will erase the selected page to 1s.

The erase operation is internally self-timed and should take

place in a maximum time of t

. During this time, the status

PE

register will indicate that the part is busy.

BLOCK ERASE:

A block of eight pages can be erased at

one time allowing the Buffer to Main Me mory Page Program without Built-In Erase command to be utilized to

reduce programming times when writing large amounts of

data to the device. To perform a Block Erase, an opcode of

50H must be loaded into the device, followed by six

reserved bits, six address bits (PA8-PA3), and 12 don’t

care bits. The six address bits are used to specify which

block of eight pages is to be erased. When a low to high

transition occurs on the CS

pin, the part will erase the

selected block o f eigh t pages to 1s. The er ase oper ation is

internally self -timed an d should tak e place in a max imum

time of t

. During this time, the stat us re giste r will in dica te

BE

that the part is busy.

4

AT45DB011

AT45DB011

Block Erase Addressing

PA8 PA7 PA6 PA5 PA4 PA3 PA2 PA1 PA0 Block

000000XXX0

000001XXX1

000010XXX2

000011XXX3

•

•

•

111100XXX60

111101XXX61

111110XXX62

111111XXX63

MAIN MEMORY PAGE PROGRAM:

combination of the Buffer Write and Buffer to Main Memory

Page Program with Built-In Erase ope rations. Data is first

shifted into the buffer from the SI pin and then programmed

into a specified page in the main memo ry. An 8-bi t opcode

of 82H is followed by the six reserved bits and 18 address

bits. The ni ne most si gnificant address b its (PA8-P A0)

select the page in the main memory wher e data is to be

written, and the next n ine ad dr ess bits (BFA8-BFA0) sel ect

the first byte in the buffer to be written. After all address bits

are shifted in, the part will take data fro m the SI pin an d

store it in the data buffer. If the end of the buffer is reached,

the device will wrap around back to the beginning of th e

buffer. When there is a low to high transition on the CS

the part will first erase the selected page in main memory to

all 1s and then program the data stored in the buffer into

the specified page in the main memory. Both the erase and

the programming of the page are internally self timed and

should take place in a maximum of time t

time, the status register will indicate that the part is busy.

AUTO PAGE REWRITE:

ple bytes within a page or mu ltiple pag es of data are mod ified in a random fashion. This mode is a combination of two

operations : Main Mem ory Page to B uffer Tran sfer and

Buffer to Main Memory Page Program with Built-In Erase.

A page of data is first transf erred fr om the main me mory to

the data buffer, and th en t he sa me data ( from the buffer) is

programmed back into its original page of main memory.

An 8-bit opcode of 58H is followed b y the si x r ese r ved bi ts,

nine address bits (PA8-PA0) that specify the page in main

memory to be re writte n, and n ine a ddi tio nal d on’ t care bits.

When a low to high transition occurs on the CS

will first transfer da ta from the p age i n main memory to th e

buffer and then program the data from the buffer back into

same page of main memory. The operation is internally

•

•

•

•

•

•

•

•

•

This operation is a

EP

This mode is only needed if multi-

•

•

•

pin,

. During this

pin, the part

•

•

•

•

•

•

•

•

•

•

•

•

self-timed and s hould t ake pl ace in a maxi mum ti me of t

During this time, the status register w ill indicate that th e

part is busy.

If a sector is programmed or reprogrammed sequentially

page by page, then the programming algorithm shown in

Figure 1 is recommended. Otherwise, if multiple bytes in a

page or several pa ges are programmed randoml y i n a se ctor, then the programming algorithm shown in Figure 2 is

recommended.

STATUS REGISTER:

The status register can be used to

determine the device’s ready/busy status, the result of a

Main Memory Page to Buffer Compa re operation, or the

device density. To read the status register, an opcode of

57H must be loaded in to th e d ev ice. A fte r the las t b it of th e

opcode is shifted in, the eig ht bits of the status register,

starting with the MSB (bit 7), will be shifted out on the SO

pin during the next eight clock cycles. The five most-significant bits of the status register will contain device infor mation, while the remaining three least-significant bits are

reserved for future use and will have undefined values.

After bit 0 of the status register has been shifted out, the

sequence will repeat itse lf (as long as CS

remains lo w an d

SCK is being toggled ) startin g again wit h bit 7. The data in

the status register is constantly updated, so each repeating

sequence will output new data.

Ready/busy status is indicated using bit 7 of the status register. If bit 7 is a 1, th en the device is not bus y and is re ady

to accept the next comman d. If bit 7 i s a 0, then the devic e

is in a busy state. The user can continuously poll bit 7 of the

status register by stopping SCK once bit 7 has been output.

The status of bit 7 will continue to b e o utp ut o n the SO pi n,

and once the device is no longer busy, the state of SO will

change from 0 to 1. There are eight operations which can

cause the device to be in a busy state: Main Memo ry Page

•

•

•

.

EP

5

to Buffer Transfer, Main Memory Page to Buffer Compare,

Buffer to Main Memory Page Program with Built-In Erase,

Buffer to Main Memory Page Program without Built-In

Erase, Page Erase, Block Erase, Main Memory Page Program, and Auto Page Rewrite.

The result of the mos t recent Ma in Memor y Page to B uffer

Compare opera tion is indic ated using bi t 6 of the status

register. If bit 6 is a 0, then the data in the main memory

page matches the data in the buffer. If bit 6 is a 1, then at

least one bit of the data in the main memory page does not

match the data in the buffer.

The device density is indicate d using bits 5, 4, and 3 of the

status register. For the AT45D011, the three bits are 0, 0,

and 1. The decimal value of these three binary bits does

not equate to th e dev ice d ensi ty; th e thr ee b its re presen t a

combinational code r elating to di ffering den sities of Ser ial

DataFlash devices, allowing a total of eight different density

configurations.

HARDWARE PAGE WRITE PROTECT:

If the WP

pin is

held low, the first 256 pages of the main memory cannot be

reprogrammed. The only way to reprogram the first 256

pages is to first dri ve the prot ect pin high and then us e the

program commands previo usly mentioned. T he WP

pin is

internally pulled high; therefore, in low pin count applications, connection of the WP

pin is not necessary if this pin

and feature will not be utilized. However, it is recommended that the WP

pin be driven high externally when-

ever possible.

RESET

:

A low state on the reset pin (RESET

) will terminate

the operation in progress and reset the internal state

machine to an idle state. The device will remain in the reset

condition as long as a low level is pr esent on the RESE T

pin. Normal operation can resume once the RESET pin is

brought back to a high level.

The device incorporates an internal power-on reset circuit,

so there are no restrictions on the RESET

power-on sequences. The RESET

pin is also internally

pin during

pulled high; therefore, in low pin count applications, connection of the RESET

pin is not necessary if this pin and

feature will not be utilized. However, it is recommended

that the RESET

pin be driven high externally whenever

possible.

READY/BUSY

:

This open dra in output pin will be dri ven

low when the device is busy in an internally self-timed operation. This pin, which is normally in a high state (through an

external pull-up resistor), will be pulled low during programming operations, compare operations, and during page-tobuffer transfers.

The busy status indic at es that the Flas h m emo ry a rray an d

the buffer cannot be accessed.

Power On/Reset State

When power is first applied to the device, o r w hen recovering from a reset conditio n, the device will defau lt to SPI

mode 3. In addition, the SO pin will be in a high im peda nc e

state, and a high to low transition on the CS

required to start a valid instruction. The SPI mode will be

automatically select ed on ever y falling ed ge of CS

pling the inactive clock state.

pin will be

by sam-

Status Register Format

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

RDY/BUSY

COMP001XXX

Absolute Maximum Ratings*

Temperature Under Bias................................-55°C to +125°C

Storage Temperature..................................... -65°C to +150°C

All Input Voltages

(including NC Pins)

with Respect to Ground...................................-0.6V to +6.25V

All Output Voltages

with Respect to Ground.............................-0.6V to V

+ 0.6V

CC

*NOTICE: Stresses beyond those listed under “Absolute

Maximum Ratings” may cause permanent damage to the dev ice . This is a s tress rating only an d

functional oper ation of the de vi ce at these or any

other conditions beyond those indicated in the

operational sections of this specification is not

implied. Exposure to absolute maximum rating

conditions f or e xtended periods ma y af fect de vice

reliability .

6

AT45DB011

AT45DB011

DC and AC Operating Range

AT45D011

Operating Temperature (Case)

V

Power Supply

CC

(1)

Note: 1. After power is applied and VCC is at the minimum specified data sheet value, the system should wait 20 ms before an oper-

ational mode is started.

DC Characteristics

Symbol Parameter Condition Min Typ Max Units

I

SB

Standby Current CS, RESET, WP = VIH,

all inputs at CMOS levels

Com. 0°C to 70°C

Ind. -40°C to 85°C

4.5V to 5.5V

10 20 µA

I

CC1

Active Current,

Read Operation

I

CC2

Active Current,

Program/Erase Operation

I

LI

I

LO

V

IL

V

IH

V

OL

V

OH1

V

OH2

Input Load Current VIN = CMOS levels 10 µA

Output Leakage Current V

Input Low Voltage 0.8 V

Input High Vo ltage 2.0 V

Output Low Voltage IOL = 2.1 mA 0.45 V

Output High Voltage IOH = -400 µA2.4 V

Output High Voltage IOH = -100 µA; V

f = 15 MHz; I

V

= 5.5V

CC

= 0 mA;

OUT

15 25 mA

VCC = 5.5V 25 50 mA

= CMOS levels 10 µ A

I/O

= 4.5V 4.2 V

CC

7

AC Characteristics

DEVICE

UNDER

TEST

30 pF

Symbol Parameter Min T yp Max Units

f

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

SCK

WH

WL

CS

CSS

CSH

CSB

SU

H

HO

DIS

V

XFR

EP

P

PE

BE

RST

REC

SCK Frequency 15 MHz

SCK High Time 30 ns

SCK Low Time 30 ns

Minimum CS High Time 250 ns

CS Setup Time 250 ns

CS Hold Time 250 ns

CS High to RDY/BUSY Low 200 ns

Data In Setup Time 10 ns

Data In Hold Time 15 ns

Output Hold Time 0 ns

Output Disable Time 20 ns

Output Valid 25 ns

Page to Buffer Transfer/Compare Time 120 200

Page Erase and Programming Time 10 20 ms

Page Programming Time 7 15 ms

Page Erase Time 6 10 ms

Block Erase Time 7 15 ms

RESET Pulse Width 10

RESET Recovery Time 1

s

µ

s

µ

s

µ

Input Test Waveforms and

Measurement Levels

2.4V

AC

DRIVING

LEVELS

8

0.45V

tR, tF < 5 ns (10% to 90%)

AT45DB011

AC

2.0

MEASUREMENT

0.8

LEVEL

Output Test Load

AC Waveforms

Two different timing diagrams are shown b elo w. W av efo r m

1 shows the SCK signal being low when C S

to-low transition, and Waveform 2 shows the SCK signal

being high when C S

makes a high-to-low transition. Both

waveforms show valid timing diagrams. The setup and hold

Waveform 1 – Inactive Clock Polarity Low

CS

makes a high-

AT45DB011

times for the S I signal are referenced t o the low-to -high

transition on the SCK signal.

Waveform 1 shows timing that is also compatible with SPI

Mode 0, and Waveform 2 shows tim ing that is compatibl e

with SPI Mode 3.

tCS

tWH tWL tCSH

tV

VALID IN

SCK

HIGH IMPEDANCE

SO

SI

tCSS

Waveform 2 – Inactive Clock Polarity High

CS

SCK

SO

tCSS

HIGH Z

tWL tWH tCSH

tV

tHO tDIS

VALID OUT

tHO tDIS

VALID OUT

tHtSU

tHtSU

HIGH IMPEDANCE

tCS

HIGH IMPEDANCE

SI

VALID IN

9

Reset Timing (Inactive Clock Polarity Low Shown)

CS

SCK

RESET

tREC tCSS

tRST

SO

HIGH IMPEDANCE HIGH IMPEDANCE

SI

Command Sequence for Read/Write Operations (Except Status Register Read)

SI CMD 8 bits

MSB

Reserved for

larger densities

Notes: 1. “r” designates bits reserved for larger densities.

2. It is recommended that “r” be a logical “0”.

3. For densities larger than 1M bit, the “r” bits become the most significant Page Address bit for the appropriate density.

Page Address

(PA8-PA0)

8 bits

8 bits

Byte/Buffer Address

(BA8-BA0/BFA8-BFA0)

LSBr r r r r r X X X X X X X X X X X X X X X X X X

10

AT45DB011

AT45DB011

Write Operations

The following block diagram and waveforms illustrate the various write sequences available.

FLASH MEMORY ARRAY

PAGE (264 BYTES)

BUFFER TO

MAIN MEMORY

PAGE PROGRAM

BUFFER (264 BYTES)

MAIN MEMORY PAGE

BUFFER

WRITE

I/O INTERFACE

SI

PROGRAM THROUGH

BUFFER

Main Memory Page Program through Buffer

CS

SI

CMD n n+1 Last Byte

r ···r , PA8-7

PA6-0, BFA8

BFA7-0

Buffer Write

CS

SI

CMD X

X···X, BFA8

BFA7-0

n

Buffer to Main Memory Page Program

(Data from Buffer Programmed into Flash Page)

Starts self-timed erase/program operation

CS

· Completes writing into buffer

· Starts self-timed erase/program operation

· Completes writing into buffer

n+1

Last Byte

SI

Each transition represents

8 bits and 8 clock cycles

CMD PA6-0, X X

r ···r , PA8-7

n = 1st byte written

n+1 = 2nd byte written

11

Read Operations

The following block diagram and waveforms illustrate the various read sequences available.

FLASH MEMORY ARRAY

PAGE (264 BYTES)

MAIN MEMORY

PAGE TO

BUFFER

BUFFER (264 BYTES)

BUFFER

READ

I/O INTERFACE

SO

MAIN MEMORY

PAGE READ

Main Memory Page Read

CS

BA7-0 X X X X

n n+1

SO

SI

CMD

r ···r , PA8-7

PA6-0, BA8

Main Memory Page to Buffer Transfer (Data from Flash Page Read into Buffer)

Starts reading page data into buffer

CS

SO

SI

CMD PA6-0, X X

r ···r , PA8-7

Buffer Read

CS

SI

SO

Each transition represents

8 bits and 8 clock cycles

CMD

X···X, BFA8

X

BFA7-0

X

n n+1

n = 1st byte read

n+1 = 2nd byte read

12

AT45DB011

AT45DB011

Detailed Bit-Level Read Timing – Inactive Clock Polarity Low

Main Memory Page Read

CS

SCK

SI

SO

Buffer Read

CS

SCK

SI

SO

tSU

tSU

12345 60 61 62 63 64 65 66 67

COMMAND OPCODE

0

10

10

XXX

HIGH-IMPEDANCE

12345 36 37 38 39 40 41 42 43

XX

tV

DATA OUT

D

7

MSB

D

COMMAND OPCODE

0

10

HIGH-IMPEDANCE

10

XXX

XX

tV

DATA OUT

D

7

MSB

D

D

6

5

D

6

5

Status Register Read

CS

SCK

tSU

SI

SO

12345 7891011 12 16 17

0

COMMAND OPCODE

10

10

HIGH-IMPEDANCE

6

111

tV

STATUS REGISTER OUTPUT

D

D

7

MSB

D

6

5

D

1

D

D

0

LSB MSB

7

13

Detailed Bit-Level Read Timing – Inactive Clock Polarity High

Main Memory Page Read

CS

SCK

SI

SO

Buffer Read

CS

SCK

SI

SO

12345 61 62 63 64 65 66 67

tSU

COMMAND OPCODE

0

10

10

XXX

XX

tV

HIGH-IMPEDANCE

12345 37 38 39 40 41 42 43

tSU

COMMAND OPCODE

0

10

10

XXX

XX

tV

HIGH-IMPEDANCE

D

MSB

D

MSB

7

7

DATA OUT

D

D

6

5

DATA OUT

D

D

6

5

68

44

D

4

D

4

Status Register Read

CS

SCK

SI

SO

14

12345 7891011 12 17 18

tSU

0

AT45DB011

COMMAND OPCODE

10

10

HIGH-IMPEDANCE

6

111

tV

D

MSB

STATUS REGISTER OUTPUT

D

D

7

6

D

5

4

D

D

0

LSB MSB

D

7

6

AT45DB011

Table 1

Main Memory

Page Read

52H 54H 53H 60H 84H

00001

11110

00010

11100

00000

01001

10100

00100

rXrrX

rXrrX

rXrrX

rXrrX

rXrrX

rXrrX

PA8 X PA8 PA8 X

PA7 X PA7 PA7 X

PA6 X PA6 PA6 X

PA5 X PA5 PA5 X

PA4 X PA4 PA4 X

PA3 X PA3 PA3 X

PA2 X PA2 PA2 X

PA1 X PA1 PA1 X

PA0 X PA0 PA0 X

BA8 BFA8 X X BFA8

BA7 BFA7 X X BFA7

BA6 BFA6 X X BFA6

BA5 BFA5 X X BFA5

BA4 BFA4 X X BFA4

BA3 BFA3 X X BFA3

BA2 BFA2 X X BFA2

BA1 BFA1 X X BFA1

BA0 BFA0 X X BFA0

XX

XX

XX

XX

XX

XX

XX

XX

•

•

•

X (64th bit)

Buffer

Read

Main Memory Page

to Buffer Transfer

Opcode

Main Memory Page

to Buffer Compare

Buffer

Write

X (Don’t Care)

r (reserved bits)

15

Table 2

Buffer to

Main Memory

Page Program

with Built-In Erase

83H 88H 81H 50H 82H 58H 57H

111 0100

000 1011

000 0000

000 1011

010 0010

000 0001

100 0101

101 0001

rrr rrr

rrr rrr

rrr rrr

rrr rrr

rrr rrr

rrr rrr

PA8 PA8 PA8 PA8 PA8 PA8

PA7 PA7 PA7 PA7 PA7 PA7

PA6 PA6 PA6 PA6 PA6 PA6

PA5 PA5 PA5 PA5 PA5 PA5

PA4 PA4 PA4 PA4 PA4 PA4

PA3 PA3 PA3 PA3 PA3 PA3

PA2 PA2 PA2 X PA2 PA2

PA1 PA1 PA1 X PA1 PA1

PA0 PA0 PA0 X PA0 PA0

X X X X BFA8 X

X X X X BFA7 X

X X X X BFA6 X

X X X X BFA5 X

X X X X BFA4 X

X X X X BFA3 X

X X X X BFA2 X

X X X X BFA1 X

X X X X BFA0 X

Buffer to

Main Memory

Page Program

without Built- In

Erase

Page

Erase

Block

Erase

Opcode

Main Memory

Page Program

Through Buffer

Auto Page

Rewrite

Through Buffer

Status

Register

16

X (Don’t Care)

r (reserved bits)

AT45DB011

AT45DB011

Figure 1.

Algorithm for Programming or Reprogramming of the Entire Array Sequentially

START

provide address

and data

BUFFER WRITE

(84H)

MAIN MEMORY PAGE PROGRAM

(82H)

BUFFER to MAIN

MEMORY PAGE PROGRAM

(83H)

END

Notes: 1. This type of algorithm is used for applicat ion s in which the enti re array is p rog rammed sequentially, filling th e a r r ay page-b y-

page.

2. A page can be written using either a Main Memo ry Pa ge Prog r am op erat ion or a Buffer Write operatio n f ol lo we d b y a Bu ff er

to Main Memory Page Program operation.

3. The algorithm above shows the programming of a single page. The algorithm will be repeated sequentially for each page

within the entire array.

17

Figure 2.

Algorithm for Randomly Modifying Data

START

provide address of

page to modify

MAIN MEMORY PAGE

to BUFFER TRANSFER

MAIN MEMORY PAGE PROGRAM

(82H)

ADDRESS POINTER

(53H)

Auto Page Rewrite

(58H)

INCREMENT PAGE

If planning to modify multiple

bytes currently stored within

a page of the Flash array

BUFFER WRITE

(84H)

BUFFER to MAIN

MEMORY PAGE PROGRAM

(83H)

(2)

(2)

END

Notes: 1. T o pr eserve data integrity, each page of a DataFlash

sector must be updated/rewritten at least once

within every 10,000 cumu lati ve page erase /pro gram

operations within that sector.

2. A Page Address Pointer must be maintained to indi-

cate which page is to be rewritten. The Auto Page

Rewrite command must use the address specified

by the Page Address Pointer.

3. Other algorithms can be used to rewrite portions of

the Flash arra y. Low power applic ations ma y choose

to wait until 10,000 cumulative page erase/program

operations have accumulated before rewr iting all

pages of the sector. See application note AN-4

(“Using Atmel’s Serial DataFlash”) for more details.

18

AT45DB011

Sector Addressing

PA2-

PA8 PA7 PA6 PA5 PA4 PA3

000000X 0

0XXXXXX 1

1XXXXXX 2

PA0 Sector

Ordering Information

I

CC

f

(MHz)

SCK

15 25 0.02 AT45D011-JC

15 25 0.02 AT45D011-JI

(mA)

Ordering Code Package Operation RangeActive Standby

AT45D011-SC

AT45D011-XC

AT45D011-SI

AT45D011-XI

32J

8S2

14X

32J

8S2

14X

AT45DB011

Commercial

(0°C to 70°C)

Industrial

(-40°C to 85°C)

32J

8S2

14X

Package Type

32-Lead, Plastic J-Leaded Chip Carrier (PLCC)

8-Lead, 0.210" Wide, Plastic Gull Wing Small Outline (EIAJ SOIC)

14-Lead, 0.170" Wide, Plastic Thin Shrink Small Outline Package (TSSOP)

19

Packaging Information

32J

, 32-Lead, Plastic J-Leaded Chip Carrier (PLCC)

Dimensions in Inches and (Millimeters)

JEDEC STANDARD MS-016 AE

.045(1.14) X 45°

.032(.813)

.026(.660)

.050(1.27) TYP

PIN NO.1

IDENTIFY

.553(14.0)

.547(13.9)

.300(7.62) REF

.430(10.9)

.390(9.90)

AT CONTACT

POINTS

.453(11.5)

.447(11.4)

.495(12.6)

.485(12.3)

.025(.635) X 30° - 45°

.595(15.1)

.585(14.9)

.022(.559) X 45° MAX (3X)

.012(.305)

.008(.203)

.530(13.5)

.490(12.4)

.021(.533)

.013(.330)

.030(.762)

.015(3.81)

.095(2.41)

.060(1.52)

.140(3.56)

.120(3.05)

8S2

, 8-Lead, 0.210" Wide, Plastic Gull Wing Small

Outline (EIAJ SOIC)

Dimensions in Inches and (Millimeters)

.020 (.508)

.012 (.305)

PIN 1

0

REF

8

.213 (5.41)

.205 (5.21)

.050 (1.27) BSC

.212 (5.38)

.203 (5.16)

.013 (.330)

.004 (.102)

.035 (.889)

.020 (.508)

.330 (8.38)

.300 (7.62)

.080 (2.03)

.070 (1.78)

.010 (.254)

.007 (.178)

14X

, 14-Lead, 0.170" Wide, Thin Shrink Small

Outline Package (TSSOP)

Dimensions in Millimeters and (Inches)*

INDEX MARK

4.50 (.177)

4.30 (.169)

1.20 (.047) MAX

0.20 (.008)

0.09 (.004)

.650 (.026) BSC

0

REF

8

5.10 (.201)

4.90 (.193)

0.30 (.012)

0.19 (.007)

0.75 (.030)

0.45 (.018)

PIN

1

0.15 (.006)

0.05 (.002)

*Controlling dimension: millimeters

6.50 (.256)

6.25 (.246)

SEATING

PLANE

20

AT45DB011

Loading...

Loading...