ATMEL AT27LV520-90XI, AT27LV520-90TI, AT27LV520-90TC, AT27LV520-90SC, AT27LV520-90CI Datasheet

...

1

512K (64K x 8)

Multiplexed

Addresses/

Outputs

Low Voltage

OTP EPROM

AT27LV520

Features

•

8-Bit Multiplexed Addresses/Outputs

•

Fast Read Access Time - 90 ns

•

Dual Voltage Range Operation

– Low-Voltage Power Supply Range, 3.0V to 3.6V, or

– Standard 5V

±±±±

10% Supply Range

•

Low Power CMOS Operation

–20

µµµµ

A max. Standby for ALE = VIH and VCC = 3.6V

– 29 mW max. Active at 5 MHz for VCC = 3.6V

•

20-Lead TSSOP Package

•

High Reliability CMOS Technology

– 2,000V ESD Protection

– 200 mA Latchup Immunity

•

Rapid™ Programming Algorithm - 50

µµµµ

s/byte (typical)

•

CMOS and TTL Compatible Inputs and Outputs

– JEDEC Standard for LVTTL

•

Integrated Product Identification Code

•

Commercial and Industrial Temperature Range

Description

The AT27LV520 is a low- power, high- perfor mance 524,28 8-bit one-ti me pro gram mable read only mem ory (OTP EP RO M) o rg ani zed 64K by 8 bi ts . It in co rpor ates l atche s

for the 8 lower order address bits to multiplex with the 8 data bits. This minimizes system chip count, reduces cost, and simplifies the design of multiplexed bus systems. It

requires only one power supply in the range of 3.0V to 3.6V for normal read mode

operation, making it ideal for fast, portable systems using battery power. Any byte can

be accessed in less than 90 ns.

The AT27LV520 is av ai la ble i n 173 m il , 2 0-pi n TS SO P , 3 00 mi l, 20 -p in S OIC a nd 28 pin TSOP, one-time programmable (OTP) plastic packages.

Rev. 0911B-B–01/98

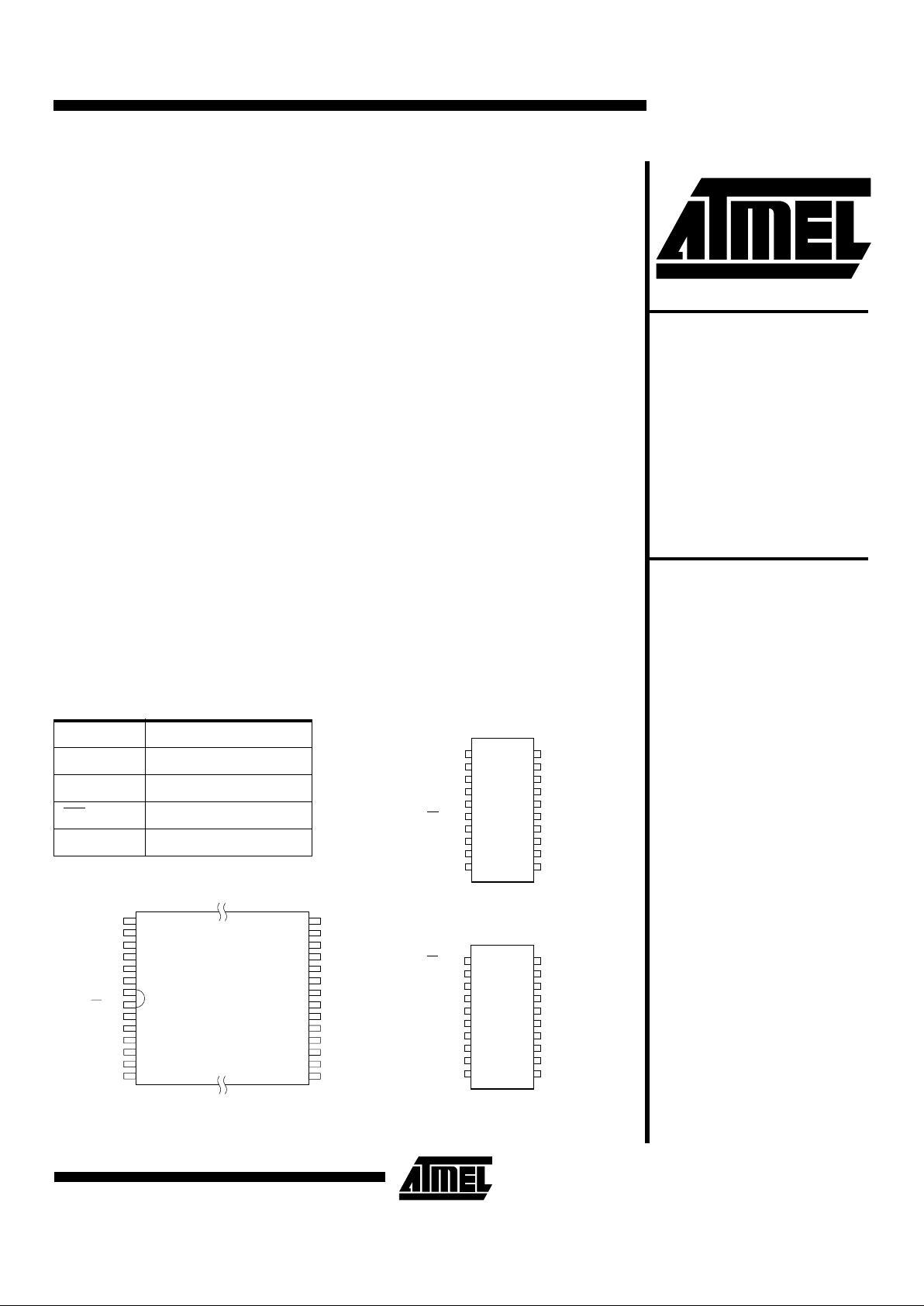

Pin Configurations

Pin Name Function

A8 - A15 Addresses

AD0 - AD7 Addresses/Outputs

OE

/V

PP

Output Enable/V

PP

ALE Address Latch Enable

TSSOP Top View

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

A10

A12

A14

ALE

VCC

OE/VPP

A15

A13

A11

A9

A8

AD1

AD3

AD5

AD7

GND

AD6

AD4

AD2

AD0

(continued)

TSOP Top View

22

23

24

25

26

27

2

3

4

5

6

7

21

20

19

18

17

16

15

14

13

12

11

10

9

8

A10

NC

NC

A12

A14

ALE

VCC

OE/VPP

A15

A13

A11

NC

NC

A9

A8

NC

NC

AD1

AD3

AD5

AD7

GND

AD6

AD4

AD2

NC

NC

AD0

28

1

SOIC Top View

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

OE/VPP

A15

A13

A11

A9

AD0

AD2

AD4

AD6

GND

VCC

ALE

A14

A12

A10

A8

AD1

AD3

AD5

AD7

AT27LV520

2

Atmel’s innovativ e design techniques provide fas t speeds

that rival 5V parts while keep ing the low pow er consum ption of a 3.3V supply. At V

CC

= 3.0V, any byte can be

accessed in less than 90 ns. With a typical power dissipation of only 18 mW at 5 MHz and V

CC

= 3.3V, the

AT27LV520 consumes less than one fifth the power of a

standard 5V EPROM. Standby mode is acheived by asserting ALE high. Standby mode supply current is typically less

than 1 µA at 3.3V.

The AT27LV520 operating with V

CC

at 3.0V produces TTL

level outputs that are compatible with standard TTL logic

devices operating at V

CC

= 5.0V. The device is also capable of standard 5-volt operation making it ideally suited for

dual supply range systems or card products that are pluggable in both 3-volt and 5-volt hosts.

Atmel’s AT27LV520 has additional features to ensure high

quality and efficient production use. The Rapid

™

Programming Algorithm reduces the time required to program the

part and guarantees reliable programming. Programing

time is typically only 50 µs/byte. The Integrated Product

Identification Code electronic ally identif ies the devic e and

manufacturer. This feature is used by industry standard

programming equipment to select the proper programming

algorithms and voltages. The AT27LV520 programs exactly

the same way as a standard 5V AT27C520 and uses the

same programming equipment.

System Considerations

Switching under active conditions may produce transient

voltage excursions. Unless accomm odated by the sy stem

design, these transient s may exceed data sheet li mits,

resulting in device non-conformance. At a minimum, a 0.1

µF high frequency, low inherent inductance, ceramic

capacitor should be ut iliz ed for eac h dev ice. This capacito r

should be connected between the V

CC

and Ground terminals of the device, as close to the device as possible. Additionally, to stabilize the supply voltage level on printed circuit boards with larg e EPROM array s, a 4.7 µF bulk electrolytic capacitor should be utilized, again connected

between the V

CC

and Ground terminals. This capaci tor

should be positioned as close as possible to the point

where the power supply is connected to the array.

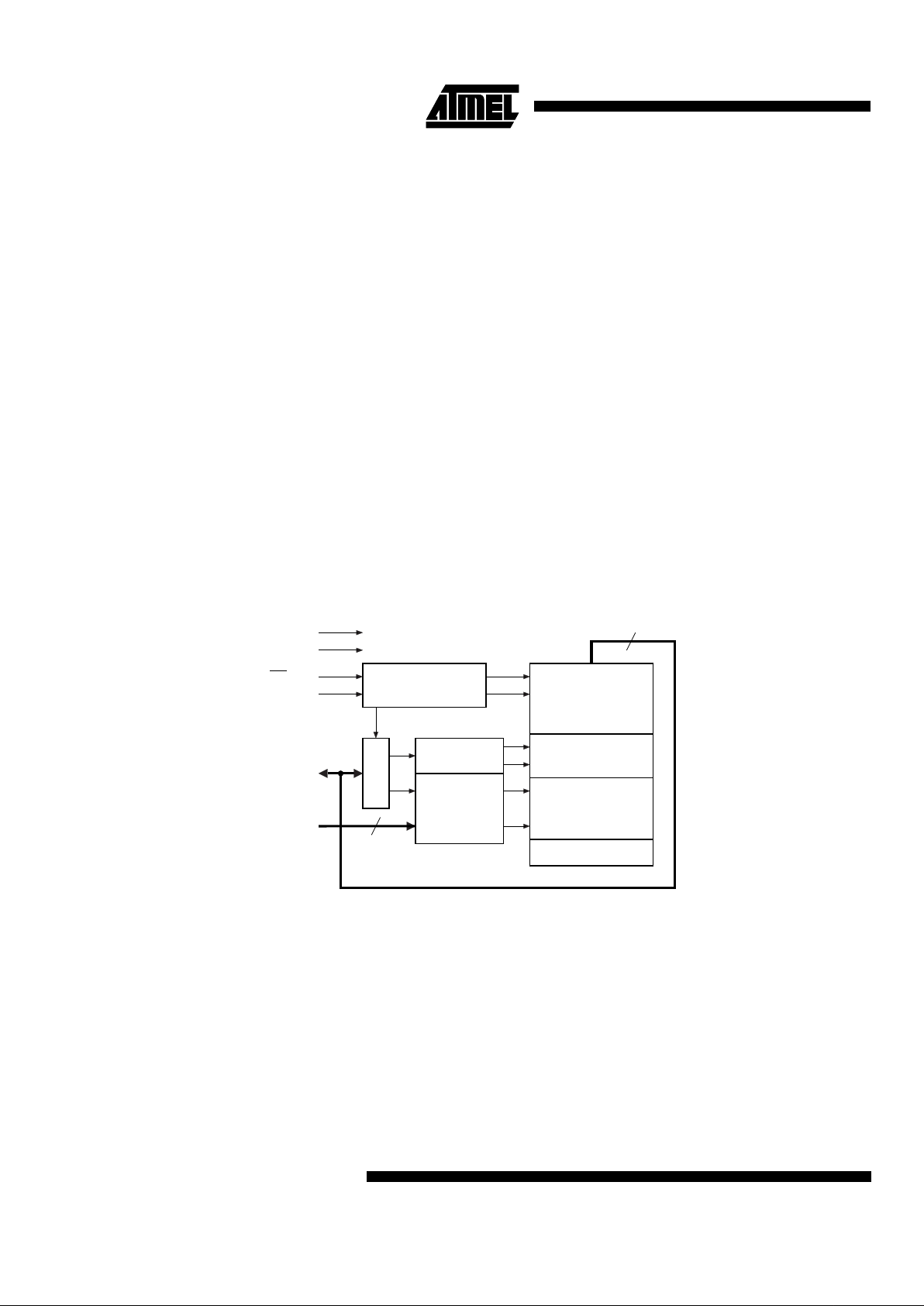

Block Diagram

OE, ALE, AND

PROGRAM LOGIC

Y DECODER

X DECODER

Y-GATING

CELL MATRIX

IDENTIFICATION

OUTPUT

BUFFERS

V

CC

GND

OE/VPP

LATCHES

ALE

AD7 - AD0

A15 - A8

8

8

AT27LV520

3

Absolute Maximum Ratings*

Temperature Under Bias................................ -55°C to +125°C

*NOTICE: Stresses beyond those l isted under “A bsolute

Maximum Ratings” may cause permanent damage to the dev ice. This is a stress ratin g only an d

functional oper ati on of the device at thes e or any

other conditions beyond those indicated in the

operational sections of this specification is not

implied. Exposure to absolute maximum rating

conditions f or extende d periods may af fect de vice

reliability.

Note: 1. Minimum voltage is -0.6V DC which may under-

shoot to -2.0V for pulses of less than 20 ns. Maximum output pin voltage is V

CC

+ 0.75V DC

which may overshoot to +7.0V for pulses of less

than 20 ns.

Storage Te mperature..................................... -65°C to +150°C

Voltage on Any Pin with

Respect to Ground ........................................-2.0V to +7.0V

(1)

Voltage on A9 with

Respect to Ground .....................................-2.0V to +14.0V

(1)

VPP Supply Voltage with

Respect to Ground ......................................-2.0V to +14.0V

(1)

Operating Modes

Notes: 1. X can be VIL or V

IH.

2. Read, output disable, and standby modes require 3.0V ≤ VCC ≤ 3.6V, or 4.5V ≤ VCC ≤ 5.5V.

3. Refer to Programming Characteristics.

4. V

H

= 12.0 ± 0.5V.

5. Two identifier bytes ma y be se lecte d. All A8 - A15 inp uts are hel d lo w (VIL), except A9 which is set to VH and A8 which is toggled low (V

IL

) to select the Manufacturer’s Identification byte and high (VIH) to select the Device Code byte.

Mode/Pin ALE OE/V

PP

A8 - A15 AD0 - AD7

Read

(2)

V

IL

V

IL

Ai D

OUT

Output Disable

(2)

VIL/V

IH

V

IH

X

(1)

High Z/A0 - A7

Standby V

IH

V

IH

Ai A0 - A7

Address Latch Enable

(2)

V

IH

V

IH

XA0 - A7

Rapid Program

(3)

V

IH

V

PP

Ai D

IN

Product Identification

(4)

V

IL

V

IL

A9 = V

H

(5)

A8 = VIH or V

IL

A10 - A15 = V

IL

Identification Code

Loading...

Loading...