ATMEL AT25P1024W1-10SI-2.7, AT25P1024W1-10SI-1.8, AT25P1024W1-10SI, AT25P1024W1-10SC-2.7, AT25P1024W1-10SC-1.8 Datasheet

...

Features

•

Serial Peripheral Interface (SPI) Compatible

•

Supports SPI Modes 0 (0,0) and 3 (1,1)

•

2.1 MHz Clock Rate

•

128-Byte Page Mode Only for Write Operations

•

Low Voltage and Standard Voltage Operation

– 5.0 (VCC = 4.5V to 5.5V)

– 2.7 (VCC = 2.7V to 5.5V)

– 1.8 (VCC = 1.8V to 3.6V)

•

Block Write Protection

– Protect 1/4, 1/2, or Entire Array

•

Write Protect (WP) Pin and Write Disable Instructions for

Both Hardware and Software Data Protection

•

Self-Timed Write Cycle (5 ms Typical)

•

High Reliability

– Endurance: 100,000 Write Cycles

– Data Retention: >40 Years

– ESD Protection: >3000V

•

20-Pin JEDEC SOIC and 8-Pin Leadless Array Package

SPI Serial

EEPROMs

1M (131,072 x 8)

AT25P1024

Description

The AT25P1024 provi des 1,048 ,576 bits of s erial ele ctrically erasabl e program mable

read only memory (EEPROM) organized as 131,072 words of 8 bits each. The device

is optimized for u se in m any ind ustri al and comm erci al a pplic atio ns w here low pow er

and low voltage operatio n are ess ential. The AT25P 1024 is av ailab le in spac e savin g

20-pin JEDEC SOIC and 8-pin leadless array (LAP) packages.

(continued)

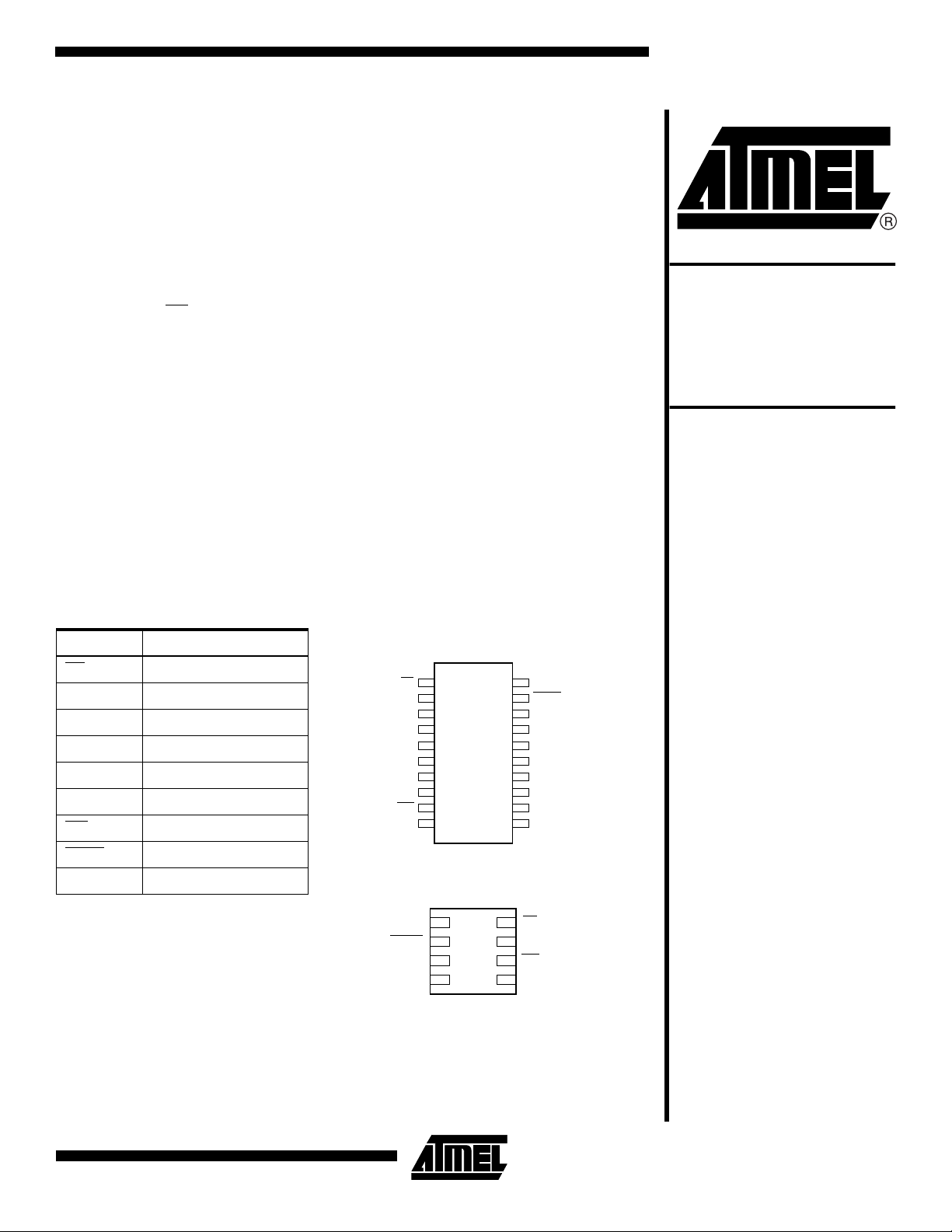

Pin Configurations

Pin Name Function

CS

Chip Select

SCK Serial Data Clock

SI Serial Data Input

SO Serial Data Output

GND Ground

VCC Power Supply

WP

Write Protect

HOLD Suspends Serial Input

NC No Connect

CS

SO

NC

NC

NC

NC

NC

NC

WP

GND

VCC

HOLD

SCK

SI

20-Lead SOIC

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

8-Pin LAP

8

7

6

5

1

2

3

4

VCC

HOLD

NC

NC

NC

NC

NC

NC

SCK

SI

CS

SO

WP

GND

Preliminary

Bottom View

Rev. 1082C–08/98

1

The AT25P1024 is enabled through the Chip Select pin

) and accessed via a 3-wire interface consisting of

(CS

Serial Data Input (SI), Serial Data Output (SO), and Serial

Clock (SCK). All progr amming cycle s are co mpletely s elftimed, and no separate ERASE cycle is required before

WRITE.

BLOCK WRITE protection is enabled by programming the

status register with top ¼, top ½ or entire array of write protection. Separate program enable and program disable

instructions are provided for additional data protection.

Hardware d ata protection is pr ovided via the WP

tect against inadvertent write attempts to the status register. The HOLD

communication without resetting the serial sequence.

pin may be used to suspend any serial

pin to pro-

Block Diagram

Absolute Maximum Ratings*

Operating Temperature..................................-55°C to +125°C

Storage Temperature .....................................-65°C to +150°C

Voltage on Any Pin

with Respect to Ground.................................... -1.0V to +7.0V

Maximum Operating Voltage...........................................6.25V

DC Output Current........................................................5.0 mA

*NOTICE: Stresses beyond those listed under “Absolute Maxi-

mum Ratings” ma y cause permanent d amage to th e

device. This is a stress rating only and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of this specif ic ati on is n ot im pl ie d. Ex pos ure to

absolute maximum rating conditions for extended

periods may affect device reliability.

131,072 x 8

2

AT25P1024

AT25P1024

Pin Capacitance

(1)

Applicable over recommended operating range from TA = 25°C, f = 1.0 MHz, VCC = +5.0V (unless otherwise noted).

Test Conditions Max Units Conditions

C

OUT

C

IN

Output Capacitance (SO) 8 pF V

Input Capacitance (CS, SCK, SI, WP, HOLD)6pFV

OUT

IN

= 0V

= 0V

Note: 1. This parameter is characterized and is not 100% tested.

DC Characteristics

Applicable over recommended operating range from: TAI = -40°C to +85°C, VCC = +1.8V to +5.5V,

= 0°C to +70°C, VCC = +1.8V to +5.5V (unless otherwise noted).

T

AC

Symbol Parameter Test Condition Min Typ Max Units

V

CC1

V

CC2

V

CC3

I

CC1

I

CC2

I

SB1

I

SB2

I

SB3

I

IL

I

OL

(1)

V

IL

(1)

V

IH

V

OL1

V

OH1

V

OL2

V

OH2

Note: 1. V

Supply Voltage 1.8 3.6 V

Supply Voltage 2.7 5.5 V

Supply Voltage 4.5 5.5 V

Supply Current VCC = 5.0V at 1 MHz, SO = Open Read 2.0 5.0 mA

Supply Current VCC = 5.0V at 2 MHz, SO = Open Write 4.0 7.0 mA

Standby Current VCC = 1.8V, CS = V

Standby Current VCC = 2.7V, CS = V

Standby Current VCC = 5.0V, CS = V

Input Leakage VIN = 0V to V

CC

CC

CC

CC

-3.0 3.0

0.1 3.0

0.2 3.0

2.0 7.0

Output Leakage VIN = 0V to VCC, TAC = 0°C to 70°C-3.0 3.0

Input Low Voltage -0.6 V

x 0.3 V

CC

Input High Voltage VCC x 0.7 VCC + 0.5 V

Output Low Voltage

Output High Voltage IOH = -1.6 mA VCC - 0.8 V

4.5V ≤ V

≤ 5.5V

CC

Output Low Voltage

Output High Voltage IOH = -100 µAVCC - 0.2 V

1.8V ≤ V

and VIH max are reference only and are not tested.

IL

≤ 3.6V

CC

I

= 3.0 mA 0.4 V

OL

I

= 0.15 mA 0.2 V

OL

µ

A

µ

A

µ

A

µ

A

µ

A

3

AC Characteristics

Applicable over recommended operating range from TA = -40°C to +85°C, VCC = As Specified,

= 1 TTL Gate and 100 pF (unless otherwise noted).

C

L

Symbol Parameter Voltage Min Max Units

f

SCK

SCK Clock Frequency

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

0

0

0

2.1

1.0

0.5

MHz

t

t

t

t

t

t

t

t

RI

FI

WH

WL

CS

CSS

CSH

SU

Input Rise Time

Input Fall Time

SCK High Time

SCK Low Time

CS High Time

CS Setup Time

CS Hold Time

Data In Setup Time

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

2.7 - 5.5

1.8 - 3.6

200

400

800

200

400

800

250

500

1000

100

250

1000

150

250

1000

30

50

100

2

2

s

µ

2

2

2

s

µ

2

ns

ns

ns

ns

ns

ns

4.5 - 5.5

t

H

Data In Hold Time

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

t

HD

Hold Setup Time

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

t

CD

Hold Hold Time

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

t

V

Output Valid

2.7 - 5.5

1.8 - 3.6

4.5 - 5.5

t

HO

Output Hold Time

2.7 - 5.5

1.8 - 3.6

4

AT25P1024

50

50

100

100

100

400

200

300

400

0

0

0

0

0

0

200

400

800

ns

ns

ns

ns

ns

Loading...

Loading...