Features

• Serial Peripheral Interf ace (SPI) Compatible

• Supports SPI Modes 0 (0,0) and 3 (1,1)

• 20 MHz Clock Rate

• Byte Mode and 256-byte Page Mode for Program O perations

• Sector Architecture:

– T w o Sectors with 32K Bytes Each (512K)

– Four Sectors with 32K Bytes Each (1M)

– 128 Pages per Sector

• Product Identification Mode

• Low- voltag e O p e r a tion

– 2.7 (V

• Sector Write Protection

• Write Protect (WP) Pin and Write Disable Instructions for

both Hardware and Software Data Protection

• Self-timed Program Cycle (60 µs/Byte Typical)

• Self-timed Sector Era se Cycle (1 second/Sector Typical)

• Single Cycle Repr ogramming (Erase and Program) f or Status Register

• High Reliability

– Endurance: 10,000 W rite Cycles Typical

• 8-lead JEDEC SOIC

= 2.7V to 3.6V)

CC

SPI Serial

Memory

512K (65,536 x 8)

1M (131,072 x 8)

AT25F512

Description

The AT25F512/1024 provides 524,288/1,048,576 bits of serial reprogrammable Flash

memor y or ganized as 6 5,536/ 131,0 72 wo rds of 8 bits each. The device is o ptimi zed

for use in many industrial and commercial applications whe re low-power and low-voltage operation are essential. The AT25F512/1024 is available in a space-saving 8-lead

JEDEC SOIC package.

The AT25F512/1024 is enabled through the Chip Selec t pin (CS

3-wire interface consisting of Serial Data Input (SI), Serial Data Output (SO), and

Seria l Cl ock (S C K ) . All w r it e c ycles are completely sel f- t im e d.

BLOCK WRITE prote ction for top 1/4, top 1/2 or the entire memory array (1M) or

entire memor y array (512K) is enabled by program ming the stat us regist er. Separate

write enable and write disable instructions are provided for additional data protection.

Hardware data protection is provided via the WP

write attempts to the status register. The HOLD

pin to protect against inadvertent

pin may be used to suspend any serial

communication without resetting the serial sequence.

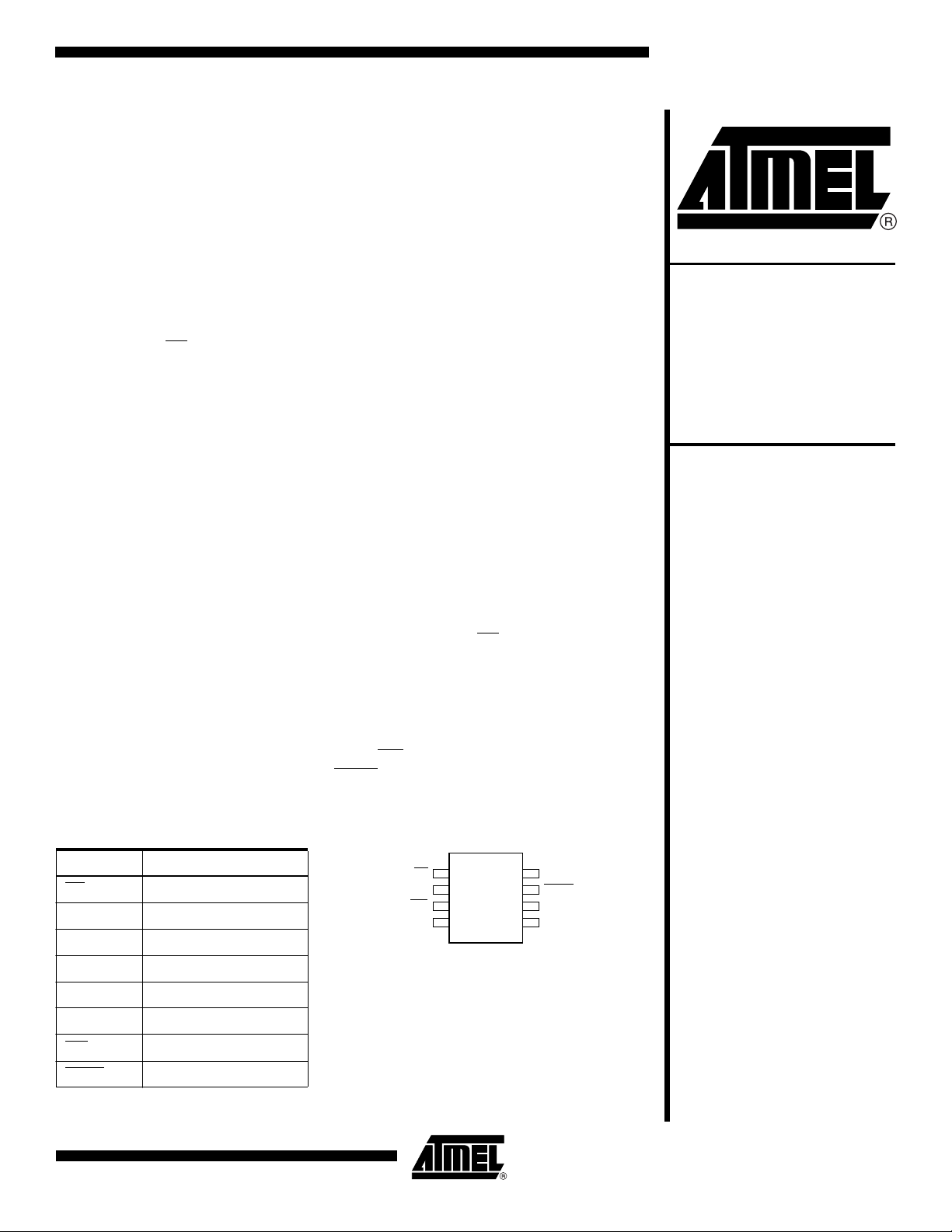

Pin Configurations

Pin Name Function

CS

SCK Seria l Da ta Cl ock

SI Serial Data Input

Chip Select

8-lead SOIC

CS

SO

WP

GND

) and accessed via a

1

2

3

4

8

7

6

5

VCC

HOLD

SCK

SI

AT25F1024

SO Serial Data Output

GND Ground

VCC Power Supply

WP

HOLD

Write Protect

Suspends Serial Input

Rev. 1440M–SEEPR–7/03

1

Absolute Maximum Ratings*

Operating Temperature.................................... -40°C to +85°C

Storage Temperature........... .......................... -65°C to +150°C

Voltage on Any Pin

with Resp e c t to Gr o und ............. ............... .. ... .... -1 . 0V to +7 .0 V

Maximum Operating Voltage .......................................... 6.25V

DC Output Current........................................................ 5.0 mA

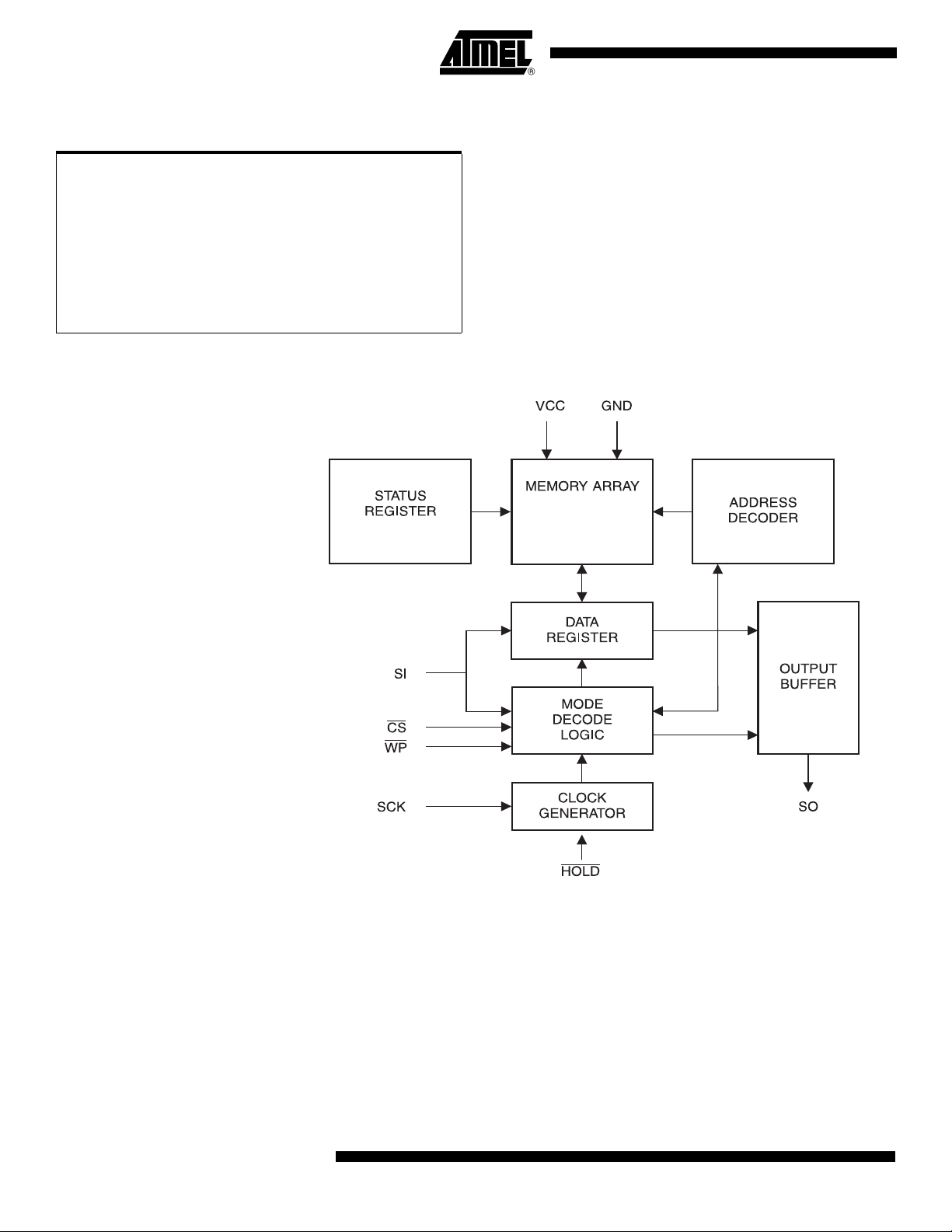

Block Diagram

*NOTICE: Stresses beyond those listed under “Ab solute

Maximum Ratings” may cause permanent damage to the device . This i s a stress rat ing only and

functional operation of the device at these or any

other conditions beyond those indi cated in the

operational sections of this specification is not

implied. Exposure to absolute maximum rating

conditions f or extended periods may affect

device reli a bi lit y.

65,536 x 8

or

131,072 x 8

2

AT25F512/1024

1440M–SEEPR–7/03

AT25F512/1024

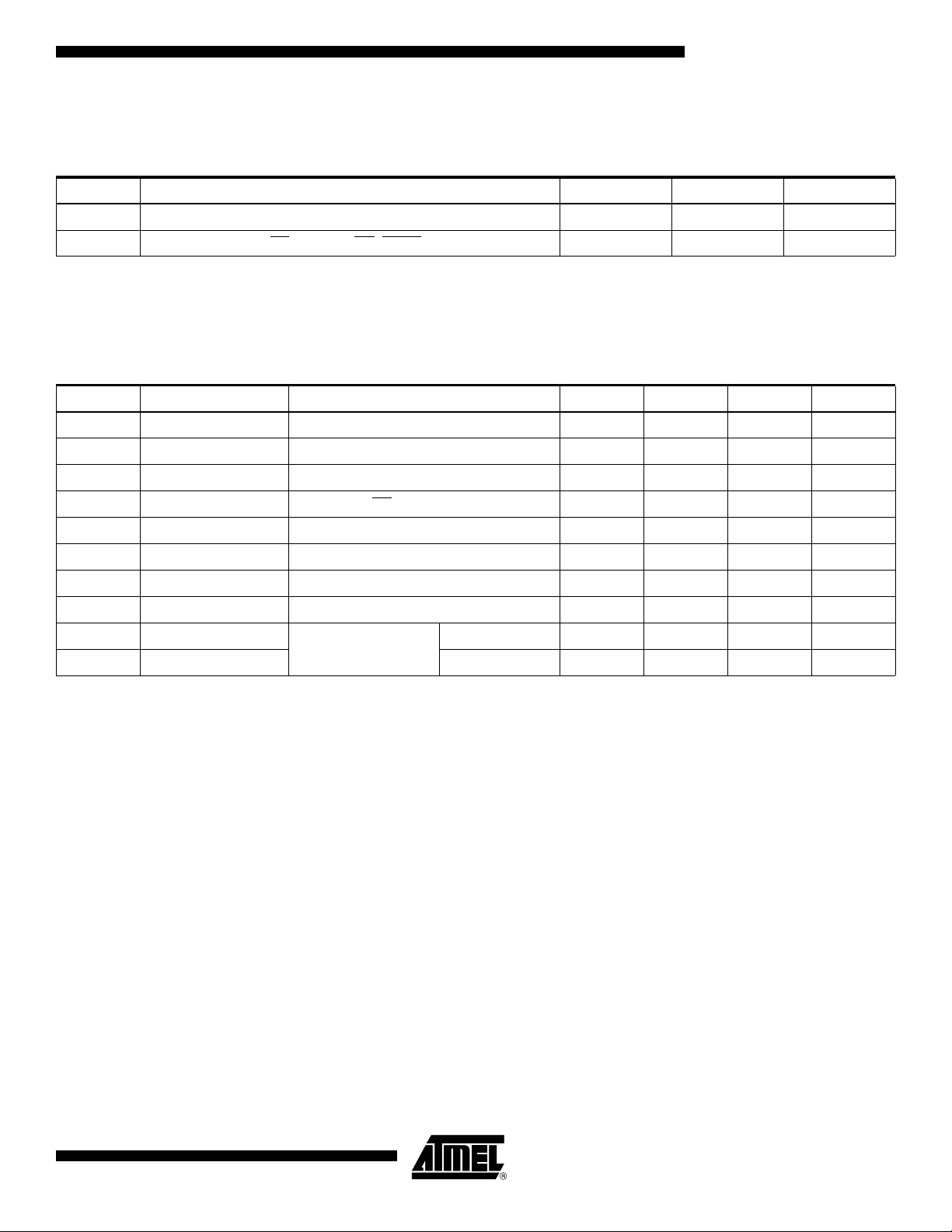

Pin Capacitance

(1)

Applicable over recommended operating range from TA = 25°C, f = 1.0 MHz, VCC = +3.6V (unless otherwise noted).

Symbol T est Conditions Max Units Conditions

C

OUT

C

IN

Output Capacitance (SO) 8 pF V

Input Capacit ance (CS, SCK, SI, WP, HOLD)6pFV

OUT

IN

= 0V

= 0V

Note: 1. This parameter is characterized and is not 100% tested.

DC Characteristics

Applicable over recommended operating range from: TAI = -40°C to +85°C, VCC = +2.7V to +3.6V,

T

= 0°C to +70°C, VCC = +2.7V to +3.6V (unless otherwise noted).

AC

Symbol Parameter Test Condition Min Typ Max Units

V

CC

I

CC1

I

CC2

I

SB

I

IL

I

OL

(1)

V

IL

(1)

V

IH

V

OL

V

OH

Note: 1. V

Supply Voltage 2.7 3.6 V

Supply Current VCC = 3.6V at 20 MHz, SO = Open Read 10.0 15.0 mA

Supply Current VCC = 3.6V at 20 MHz, SO = Open Write 15.0 30.0 mA

Standby Current VCC = 2.7V, CS = V

Input Leakage VIN = 0V to V

CC

CC

-3.0 3.0 µA

2.0 10.0 µA

Output Leakage VIN = 0V to VCC, TAC = 0°C to 70°C -3.0 3.0 µA

Input Low Voltage -0.6 V

x 0.3 V

CC

Input High Voltage VCC x 0.7 VCC + 0.5 V

Outp u t Lo w Voltag e

Output High Voltage IOH = -100 µA VCC - 0.2 V

2.7V ≤ V

and VIH max are reference only and are not tested.

IL

≤ 3.6V

CC

I

= 0.15 mA 0.2 V

OL

1440M–SEEPR–7/03

3

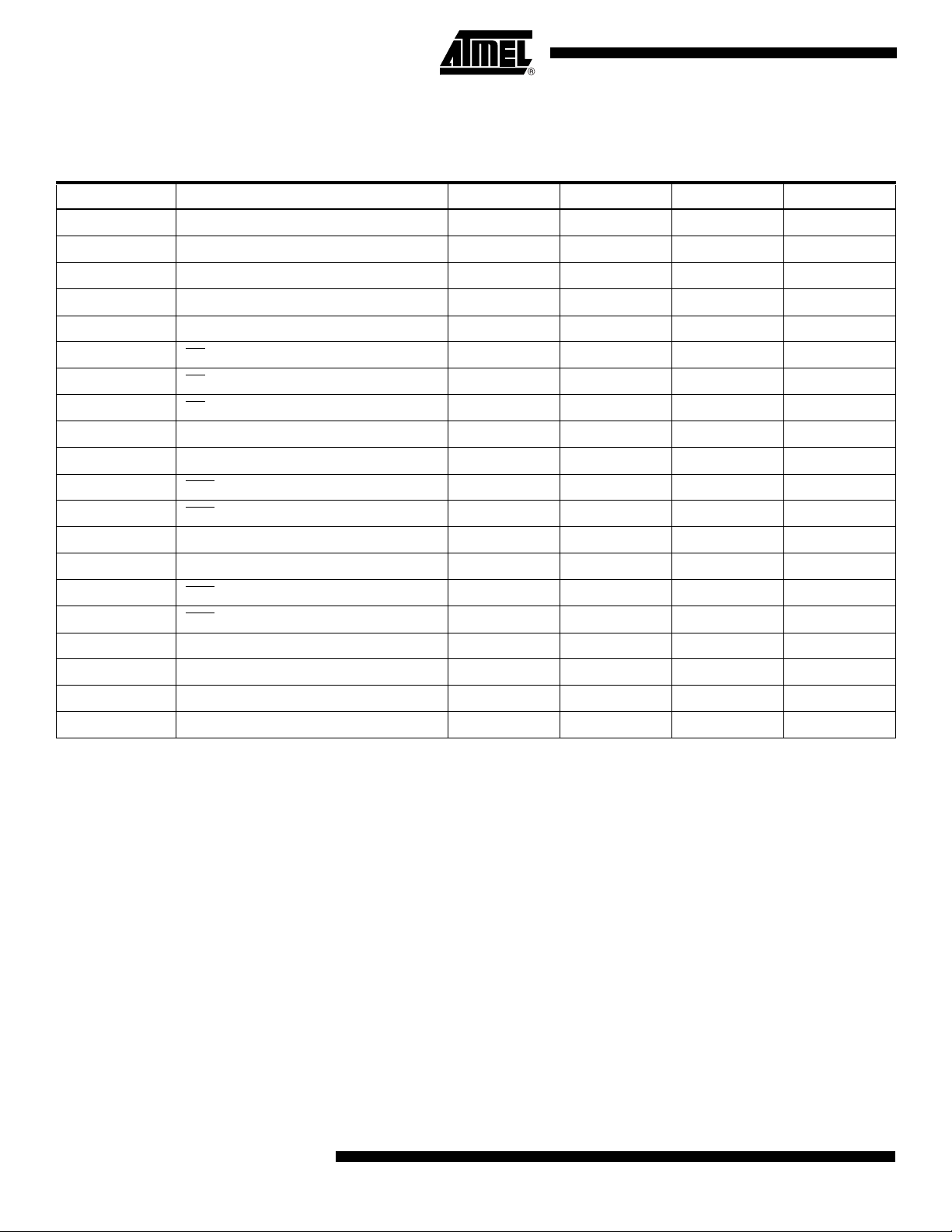

AC Characteristics

Applicable over recommended operating range from TAI = -40°C to +85°C, VCC = +2.7V to +3.6V

C

= 1 TTL Gate and 30 pF (unless otherwise noted).

L

Symbol Parameter Min Typ Max Units

f

SCK

t

RI

t

FI

t

WH

t

WL

t

CS

t

CSS

t

CSH

t

SU

t

H

t

HD

t

CD

t

V

t

HO

t

LZ

t

HZ

t

DIS

t

EC

t

BPC

Endurance

(2)

SCK Clock Frequency 0 20 MHz

Input Rise Time 20 ns

Input Fall Time 20 ns

SCK High Time 20 ns

SCK Low Time 20 ns

CS High Time 25 ns

CS Setup Time 25 ns

CS Hold Time 25 ns

Data In Setup Time 5 ns

Data In Ho ld Ti me 5 ns

Hold Setup Time 15 ns

Hold Time 15 ns

Output Valid 20 ns

Output Hold Time 0 ns

Hold to Output Low Z 200 ns

Hold to Output High Z 200 ns

Output Disable Time 100 ns

Erase Cycle Time per Sector 1.1 s

Byte Program Cycle Time

(1)

Notes: 1. The programming time f or n bytes will be equal to n x t

2. Thi s parameter is characteri zed at 3.0V, 25°C and is not 100% tested.

3. One write cycle consists of erasing a sector, followed by programming the same sector.

BPC

60 100 µs

10K Write Cycles

(3)

.

4

AT25F512/1024

1440M–SEEPR–7/03

AT25F512/1024

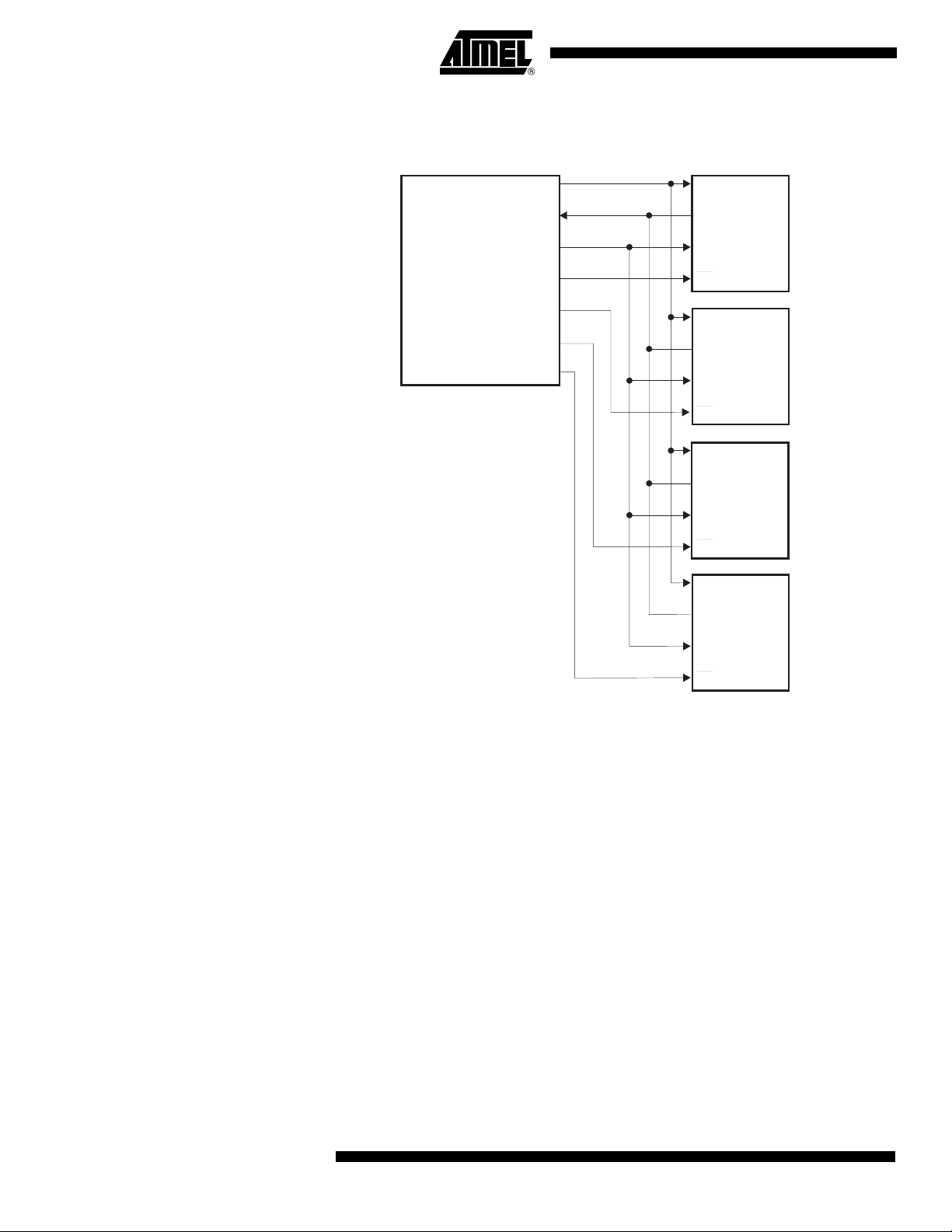

Serial Interface

Description

MASTER: The device that generates the serial clock.

SLAVE: Because the Serial Clock pin (SCK) is always an input, the AT25F512/1024

always operates as a slave.

TRANSMITTER/RECEIVER: The AT25F512/1024 has separate pins designated for

data transmission (SO) and reception (SI).

MSB: The Most Significant Bit (MSB) is the first bit transmitted and received.

SERIAL OP-CODE: After the device is selected with CS

received. This byte contains the op-code that defines the operations to be performed.

INVALID OP-CODE: If an invalid op-code is received, no data will be shifted into the

AT25F512/1024, and the serial output pin (SO) will remain in a high impedance state

until the falling edge of CS

communication.

CHIP SELECT: The AT25F512/1024 is selected when the CS

device is not selecte d, data wil l not be accepted via the S I pin, and the serial output pi n

(SO) will remain in a high impedance state.

HOLD: The HOLD

AT25F 512/1024. When t he device i s selecte d and a serial sequ ence is un derway,

HOLD

can be used to paus e the serial communication with the master device without

resett ing th e s erial sequ en ce. To pa use, th e HOLD

SCK pin is low. To resume serial communication, the HOLD

SCK pin is low (SCK ma y still toggle duri ng HOLD

while the SO pin is in the high impedance state.

pin is used in conjunction with the CS pin to s elect th e

is detecte d again. This will rein itialize the seri al

going l o w , th e f ir s t byte will be

pin is low. When the

pin mu st be brou gh t low whil e the

pin is brought high while the

). Inputs to the SI pin will be i gnored

WRITE PROTECT: The 25F512 /1024 h as a write loc kout feature that ca n be activa ted

by asserting the write protect pin (WP

sectors will be RE AD only. The write protect pin will allow no rma l read/writ e opera tions

when held high. When the WP

the status register are inhibited. WP

the status register. If the internal status register w rite cycle has already b een initiated,

WP

going low will have no effect o n any write ope ratio n to the stat us register. The WP

pin function is blocked when the WPEN bit in the status register is “0”. This will allow the

user to install the AT25F512/1024 in a system with the WP

able to write to the status register. All WP

is set to “1”.

is brought low and WPEN bit is “1”, all write operations to

). When the lockout feature is activated, locked-out

going low while CS is still low will interrupt a write to

pin tied to ground and still be

pin functions are enabled when the WPEN bit

1440M–SEEPR–7/03

5

SPI Serial Interface

MASTER:

MICROCONTROLLER

DATA OUT (MOSI)

DATA IN (MISO)

SERIAL CLOCK (SPI CK)

SS0

SS1

SS2

SS3

SLAVE:

AT25F512/1024

SI

SO

SCK

CS

SI

SO

SCK

CS

SI

SO

SCK

CS

SI

SO

SCK

CS

6

AT25F512/1024

1440M–SEEPR–7/03

Loading...

Loading...