Datasheet AT24CS256W-10SI-2.7, AT24CS256W-10SI-1.8, AT24CS256W-10SI, AT24CS256W-10SC-2.7, AT24CS256W-10SC-1.8 Datasheet (ATMEL)

...

Features

•

One-Time Programmable (OTP) Feature

•

Low-Voltage and Standard-Voltage Operation

– 5.0 (VCC = 4.5V to 5.5V)

– 2.7 (VCC = 2.7V to 5.5V)

– 1.8 (VCC = 1.8V to 3.6V)

•

Internally Organized 16,384 x 8 and 32,768 x 8

•

2-Wire Serial Interface

•

Schmitt Trigger, Filtered Inputs for Noise Suppression

•

Bidirectional Data Transfer Protocol

•

1 MHz (5V), 400 kHz (2.7V) and 100 kHz (1.8V) Compatibility

•

Write Protect Pin for Hardware and Software Data Protection

•

64-Byte Page Write Mode (Partial Page Writes Allowed)

•

Self-Timed Write Cycle (5 ms typical)

•

High Reliability

– Endurance: 100,000 Write Cycles

– Data Retention: 40 Years

– ESD Protection: >4000V

•

Automotive Grade and Extended Temperature Devices Available

•

8-Pin JEDEC PDIP and 8-Pin JEDEC and EIAJ SOIC Packages

2-Wire Serial

EEPROMs

with Permanent

Software Write

Protect

Description

The AT24CS128/256 provides 131,072/262,144 bits of serial electrically erasable and

programmable read onl y mem ory ( EEPROM ) organi zed as 16,384/ 32,768 w ords of 8

bits each. The device’s cascadable feature allows up to 4 devices to share a common

2-wire bus. The device also features a one-time programmable 2048 bit array, which

once enabled, becomes r ead -only and can not be ove rwritten. If not enabled, the OTP

section will function as part of the normal memory array. The device is optimized for

use in many industri al and comm erc ial appli catio ns wher e low power and low v oltag e

operation are essential. The devices are available in space-saving 8-pin JEDEC PDIP

(AT24CS128/256), 8-pin EIAJ (AT24CS128/256), 8-pin JEDEC SOIC (AT24CS128)

packages. In addition, the en tire family is available in 5.0V (4.5V to 5.5V), 2.7 V (2.7V

to 5.5V) and 1.8V (1.8V to 3.6V) versions.

Pin Configurations

Pin Name Function

A0 to A2 Address Inputs

SDA Serial Data

SCL Serial Clock Input

WP Write Protect

A0

A1

A2

GND

8-Pin PDIP

1

2

3

4

8-Pin SOIC

8

VCC

7

WP

6

SCL

5

SDA

128K (16,384 x 8)

256K (32,768 x 8)

AT24CS128

AT24CS256

with Permanent

Software Write

Protect

Advanced

Information

A0

A1

A2

GND

1

2

3

4

VCC

8

WP

7

SCL

6

SDA

5

Rev. 1152A–09/98

1

Absolute Maximum Ratings*

Operating Temperature.................................. -55°C to +125°C

Storage Temperature.....................................-65°C to +150°C

Voltage on Any Pin

with Respect to Ground.....................................-1.0V to +7.0V

Maximum Operating Voltage........................................... 6.25V

DC Output Current........................................................5.0 mA

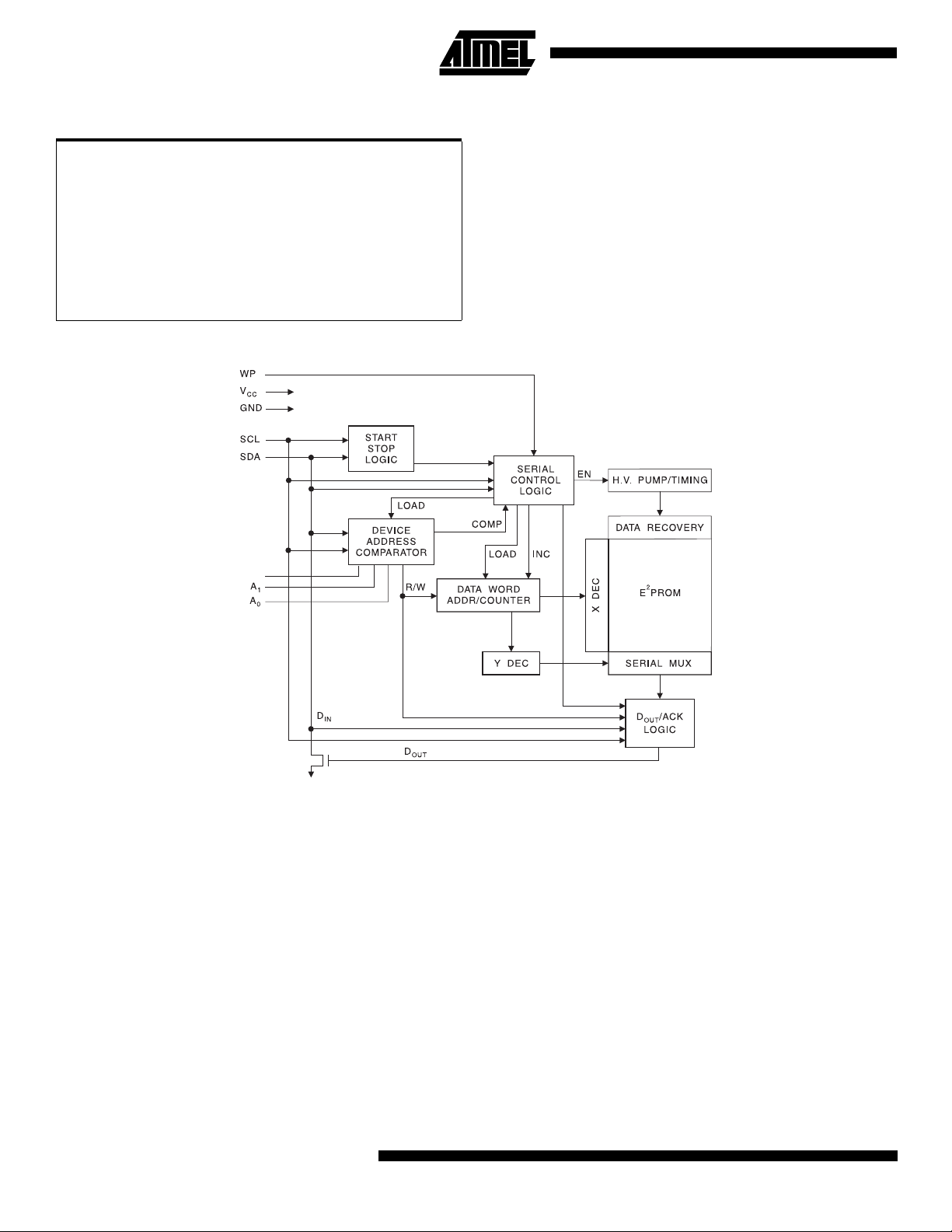

Block Diagram

A

2

*NOTICE: Stresses beyond those listed under “Absolute

Maximum Ratings” may cause permanent damage to the dev ice . This is a stress ra ting onl y and

functional oper ati on of the device at these or an y

other conditions beyond those indicated in the

operational sections of this specification is not

implied. Exposure to absolute maximum rating

conditions f or exten ded periods may af fect de vice

reliability.

Pin Description

SERIAL CLOCK (SCL):

edge clock data into each EEPROM device and negative

edge clock data out of each device.

SERIAL DATA (SDA):

serial data transfer. This pin is open-drain driven and may

be wire-ORed with any number of other open-drain or open

collector devices.

DEVICE/PAGE ADDRESSES (A2, A1, A0):

A0 pins are device address inputs that are hardwired or left

not connected for hardware compatibility with AT24C32/64.

When the pins are hardwired, as many as four 128K/256K

devices may be addres sed on a sing le bus syst em (devic e

addressing is discussed in detail under the Device

Addressing section). When the pins are not hardwired, the

2

AT24CS128/256

The SCL input is used to positive

The SDA pin is bidirectional for

The A1 and

default A

and A0 are zero. The A2 device address input is

1

a “don’t care” input.

WRITE PROTECT (WP):

The write protect input, when tied

to GND, allows normal write operations. Wh en WP is tied

high to V

, all write operat ions to the memory are inhib-

CC

ited. If left unconnected, WP is interna lly pulled down to

GND. Switching WP to V

prior to a write op eration cre-

CC

ates a soft ware write protect function.

Memory Organization

AT24CS128/256, 128K/2 56K SERIAL EEPROM:

128K/256K is internal ly organ ized as 25 6/51 2 pages of 64bytes each. Random word addressing requires a 14/15-bit

data word address.

The

AT24CS128/256

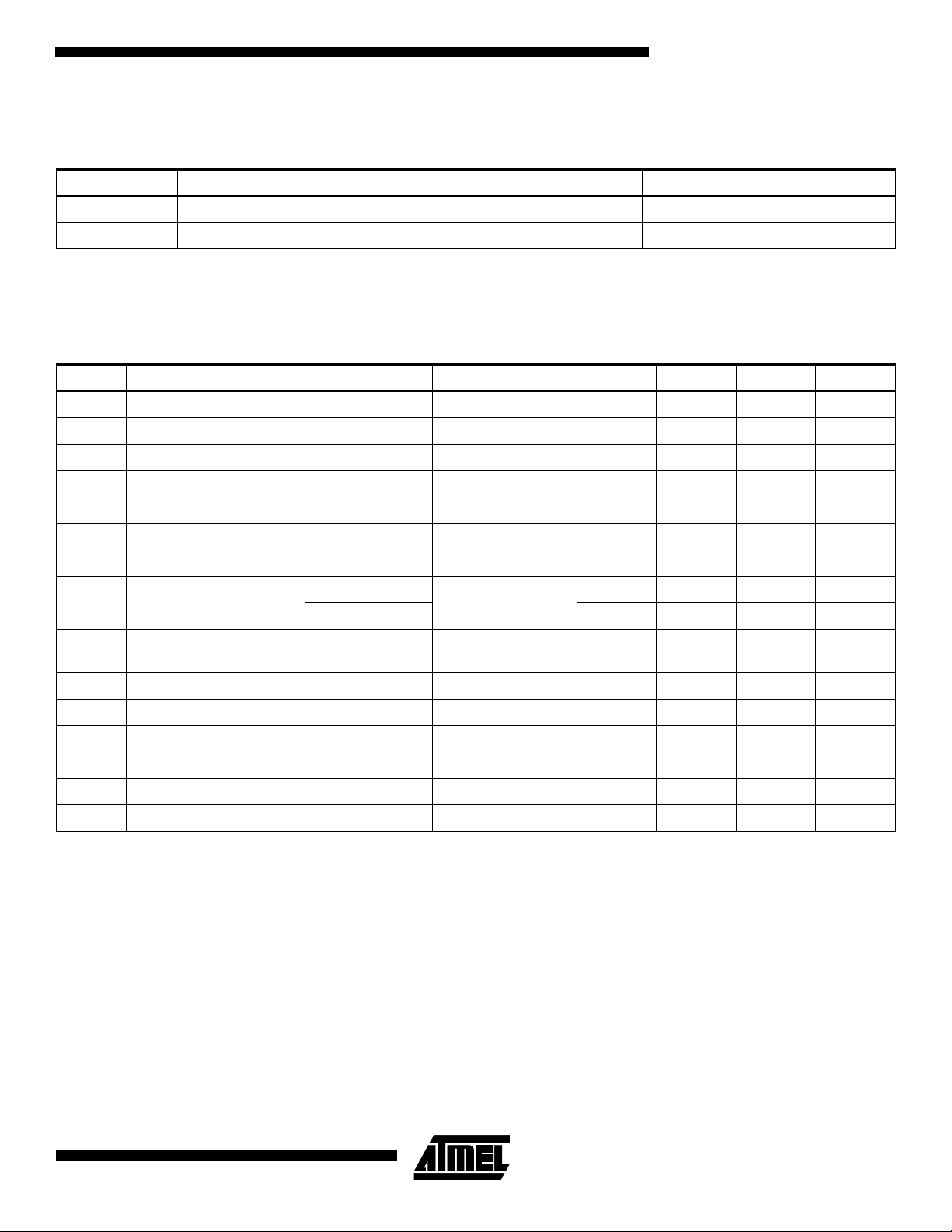

Pin Capacitance

(1)

Applicable over recommended operating range from TA = 25°C, f = 1.0 MHz, VCC = +1.8V.

Symbol Test Condition Max Units Conditions

C

I/O

C

IN

Input/Output Capacitance (SDA) 8 pF V

I/O

= 0V

Input Capacitance (A0, A1, SCL) 6 pF VIN = 0V

Note: This parameter is characterized and is not 100% tested.

DC Characteristics

Applicable over recommended operating range from: T

= +1.8V to +5.5V (unless otherwise noted).

V

CC

Symbol Parameter Test Condition Min Typ Max Units

V

V

V

I

I

I

I

CC1

CC2

CC3

CC1

CC2

SB1

SB2

Supply Voltage 1.8 3.6 V

Supply Voltage 2.7 5.5 V

Supply Voltage 4.5 5.5 V

Supply Current VCC = 5.0V READ at 400 kHz 1.0 2.0 mA

Supply Current VCC = 5.0V WRITE at 400 kHz 2.0 3.0 mA

= 1.8V

V

Standby Current

(1.8V option)

Standby Current

(2.7V option)

CC

V

= 3.6V 2.0

CC

V

= 2.7V

CC

VCC = 5.5V 5.0

= -40°C to +85°C, VCC = +1.8V to +5.5V, TAC = 0°C to +70°C,

AI

0.2

= VCC or V

V

IN

SS

0.5

= VCC or V

V

IN

SS

µ

A

µ

A

I

I

I

V

V

V

V

SB3

LI

LO

IL

IH

OL2

OL1

Standby Current

(5.0V option)

Input Leakage Current VIN = V

Output Leakage Current V

Input Low Level

Input High Level

(Note:)

(Note:)

Output Low Level VCC = 3.0V IOL = 2.1 mA 0.4 V

Output Low Level VCC = 1.8V IOL = 0.15 mA 0.2 V

= 4.5 - 5.5V VIN = VCC or V

V

CC

OUT

Note: VIL min and VIH max are reference only and are not tested

CC or VSS

= V

CC or VSS

SS

5.0

0.10 3.0

0.05 3.0

µ

µ

µ

-0.6 VCC x 0.3 V

VCC x 0.7 VCC + 0.5 V

A

A

A

3

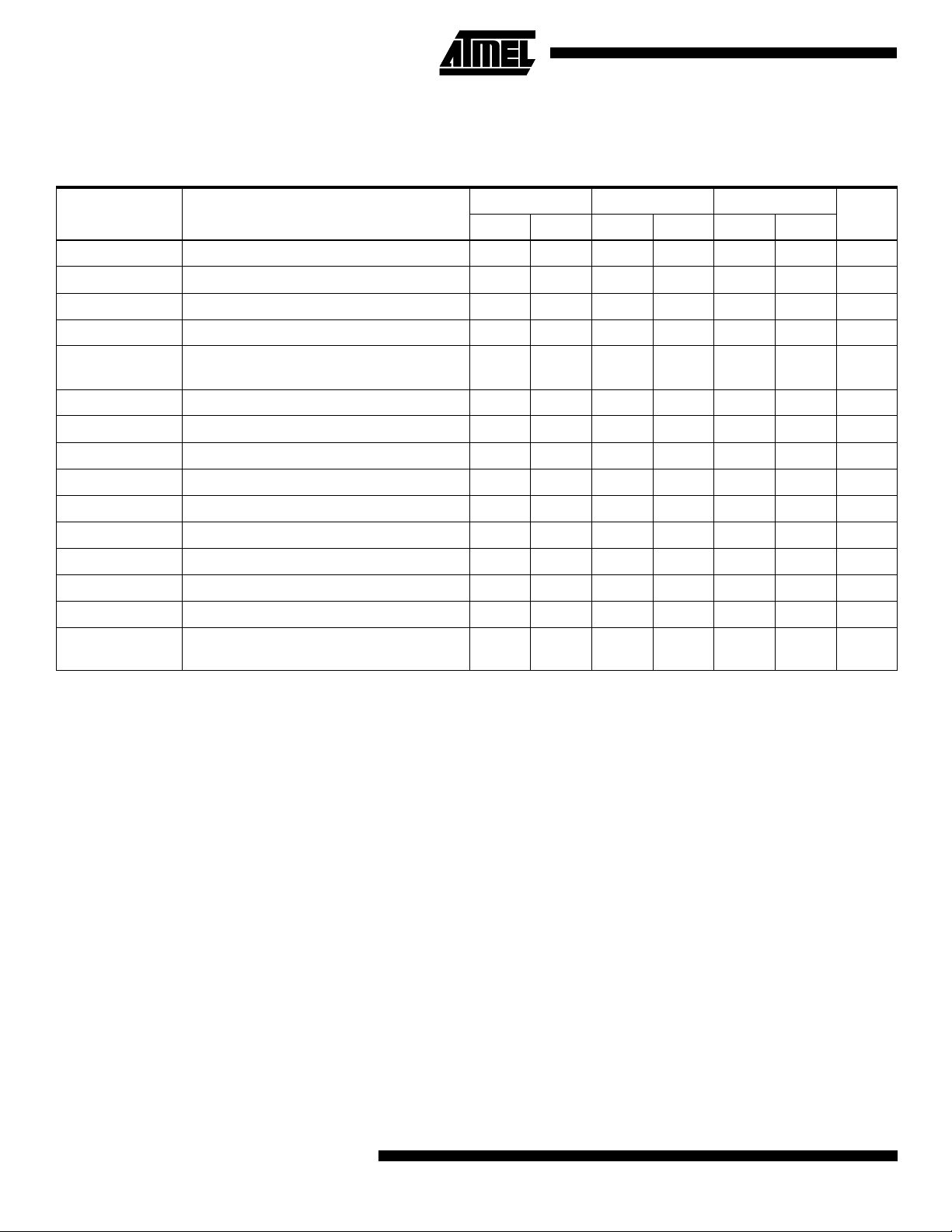

AC Characteristics

Applicable over recommended operating ran ge fro m TA = -40°C to +85°C, VCC = +1.8V to +5.5V, CL = 100 pF (unless otherwise noted). Test conditions are listed in Note 2.

1.8-volt 2.7-volt 5.0-volt

Symbol Parameter

f

SCL

t

LOW

t

HIGH

t

AA

t

BUF

t

HD.STA

t

SU.STA

t

HD.DAT

t

SU.DAT

t

R

t

F

t

SU.STO

t

DH

t

WR

Endurance

(1)

Clock Frequency, SCL 400 1000 1000 kHz

Clock Pulse Width Low 1.3 0.6 0.6 µs

Clock Pulse Width High 1.0 0.4 0.4 µs

Clock Low to Data Out Valid 0.1 0.9 0.05 0.55 0.05 0.55 µs

Time the bus must be free before a new

transmission can start

(1)

Start Hold Time 0.6 0.25 0.25 µs

Start Set-up Time 0.6 0.25 0.25 µs

Data In Hold Time 0 0 0 µs

Data In Set-up Time 100 100 100 ns

Inputs Rise Time

Inputs Fall Time

(1)

(1)

Stop Set-up Time 0.6 0.25 0.25 µs

Data Out Hold Time 50 50 50 ns

Write Cycle Time 20 10 10 ms

5.0V, 25°C, Page Mode 100K 100K 100K

Notes: 1. This parameter is characterized and is not 100% tested.

2. AC measurement conditions:

(connects to VCC): 1.3KΩ (2.7V, 5V), 10KΩ (1.8V)

R

L

Input pulse voltages: 0.3V

to 0.7V

CC

CC

Input rise and fall times: ≤50ns

Input and output timing reference voltages: 0.5V

CC

UnitsMinMaxMinMaxMinMax

1.2 0.5 0.5 µs

0.3 0.3 0.3 µs

300 100 100 ns

Write

Cycles

Device Operation

CLOCK and DATA TRANSITIONS:

mally pulled h ig h w ith an external devi ce . D ata on the SDA

pin may chan ge only dur ing SC L lo w ti me p eri ods (re fer to

Data Validity timing diagram). Data changes during SCL

high periods will indicate a start or stop condition as defined

below.

START CONDITION:

A high-to-low transition of SDA with

SCL high is a start condition which must precede any other

command (refer to Start and Stop Definition timing diagram).

STOP CONDITION:

A low-to-high transition of SDA with

SCL high is a stop condition. After a read sequence, the

stop command will place the EEPROM in a standby power

mode (refer to Start and Stop Definition timing diagram).

4

AT24CS128/256

The SDA pin is nor-

ACKNOWLEDGE:

All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words.

The EEPROM sends a zero during the ninth clock cycle to

acknowledge that it has received each word.

STANDBY MODE:

The AT24CS128/256 features a low

power standby mode which is enabled: a) upon power-up

and b) after the r ecei pt of the STOP bit and the completi on

of any internal operations.

MEMORY RESET:

After an interruption in protocol, power

loss or system reset, any 2-wire part can be reset by following these steps: (a) Clock up to 9 cycles, (b) look for SDA

high in each cycle while SCL is high and then (c) create a

start condition as SDA is high.

AT24CS128/256

Bus Timing (SCL: Serial Clock, SDA: Serial Data I/O)

Write Cycle Timing (SCL: Serial Clock, SDA: Serial Data I/O)

SCL

SDA

Note: 1. The write cycle time tWR is the time from a valid stop condition of a write sequence to the end of the internal clear/write

cycle.

8th BIT

WORD n

ACK

STOP

CONDITION

(1)

t

WR

START

CONDITION

5

Data Validity

Start and Stop Definition

Output Acknowledge

6

AT24CS128/256

AT24CS128/256

Device Addressing

The 128K/256K EEPROM re qui re s an 8- bit devi c e add re ss

word following a start condition to enable the chip for a read

or write operation (refer to Figure 1). The device address

word consists of a manda tory one , zero sequence for th e

first five most significant bits as shown. This is common to

all 2-wire EEPROM devices.

The 128K/256K uses the two devic e add re ss bits A1, A0 to

allow as many as four devices on the same bus. These bits

must compare to their corresponding hardwired input pins.

The A1 and A0 pins use an internal proprietary circuit that

biases them to a lo gic low co nditio n if the pi ns are al lowed

to float.

The eighth bit of the device address is the read/write operation select bit. A read operation is initiated if this bit is high

and a write operation is initiated if this bit is low.

Upon a compare of the device address, the EEPROM will

output a zero. If a compare is not made, the device will

return to a standby state.

DATA SECURITY:

data protection scheme that allows the user to write protect

the whole memory when the WP pin is at V

The AT24CS128/256 has a hardware

.

CC

Write Operations

BYTE WRITE:

word addresses following the device address word and

acknowledgment. U pon receipt of this address, the

EEPROM will again respond with a zero and then clock in

the first 8-bit data word. Following r eceipt of the 8-bit data

word, the EEPROM will output a zero. The addressing

device, such as a microcontroller, then must terminate the

write sequence with a s top condition. At thi s time the

EEPROM enters an in ternall y-tim ed write cyc le, t

nonvolatile memory. All inputs are disabled during this write

cycle and the EEPROM will not respond until the write is

complete (refer to Figure 2).

PA GE WRIT E:

byte page writes.

A page write is initiated the same way as a byte write, but

the microcontroller doe s not send a stop conditi on a fter th e

first data word is clocked in. Instead, after the EEPROM

acknowledges receipt of the first data word, the microcontroller can transmit up to 63 more data words. The

EEPROM will respond with a zero after each data word

received. Th e microcontr oller must ter minate the pag e

write sequence with a stop condition (refer to Figure 3).

The data word address lower 6 bits are internally incremented following the rece ipt of each data word. The hig her

data word address bits ar e not incremen ted, retaini ng the

memory page row location. When the word address, internally generated, reaches the page boundary, the following

byte is placed at the beginning of the same page. If more

A write operation requires two 8-bit data

, to the

WR

The 128K/256K EEPROM is capabl e of 64-

than 64 data words are transmitted to the EEPROM, the

data word address will “roll over” an d previous data will be

overwritten. The addr ess “rol l ov er” durin g wri te is fro m the

last byte of the current page to the first byte of the same

page.

ACKNOWLEDGE POLLING:

write cycle has started and the EEPROM inpu ts are disabled, acknowledge polling can be initia ted. This invol ves

sending a start condition followed by the device address

word. The read/write bit is repres entative of the oper ation

desired. Only if the internal wri te cycle has c ompleted will

the EEPROM respond with a zero, allowing the read or

write sequence to continue.

Once the internally-time d

OT P Description/Operation

The OTP feature provides the user with a 2048-bit (256 x 8)

security section, which once programmed and enabled,

becomes read-on ly and data cannot be ch anged or ove rwritten. The OTP sectio n i s loc ated in the u ppe r 2 K sec tio n

of the memory array in the AT24CS128/256. If not enabled,

the OTP section wi ll f unc tio n as pa rt of the n ormal m emo ry

array.

To enable the OTP section:

1. Inputs must be connected:

A2 = Don’t Care, A1 and A0 = V

2. Initiate the programming sequence:

START 1010 1100 11xx xxxx xxxx xxxx xxxx xxxx STOP

Once enabled, previously written data cannot be changed.

The status of the OTP section can only be confirmed by initiating a programming sequence to the OTP section and

verifying by a read command. The use of the write protect

(WP) feature can be utilized with or without enabling the

OTP function.

or GND

CC

Read Operations

Read operations are initiated the same way as write operations with the exception that the read/write select bit in the

device address word is set to one. There are t hree read

operations: current address read, random address read

and sequential read.

CURRENT ADDRESS REA D:

address counter maintains the last addr ess accessed during the last read or write operation, incremented by one.

This address stays valid between operations as long as the

chip power is maintained. T he address “roll over” during

read is from the last by te of the last me mory page, to th e

first byte of the first page.

Once the device address with the read/wr ite select b it set

to one is clocked in and acknowledged by the EEPROM,

the current address data word is s erially clo cked out. The

microcontroller does not r espond with an input zero but

does generate a following stop condition (refer to Figure 4).

The internal data word

7

RANDOM READ:

write sequence to l oad in t he data word addr ess. On ce the

device address word and data word address are clocked in

and acknowledge d by the EE PROM, the microcontroller

must generate another start condition. The microcontroller

now initiates a current address read by sending a device

address with the read/write select bit high. The EE PROM

acknowledges the device address and serially clocks out

the data word. The microcontroller does not respond with a

zero but does generate a following stop condition (refer to

Figure 5).

A random read requires a “ dummy ” byte

SEQUENTIAL READ:

either a current address read or a random address read.

After the microcontroller receives a data word, it responds

with an acknowledge. As long as the EEPROM receives an

acknowledge, it will continue to increment the data word

address and serially clock out sequential data words. When

the memory address limit is reached, the data word

address will “roll over” and the sequential read will continue. The sequential r ead operation is terminated when

the microcontroller does not respond with a zero but does

generate a following stop condition (refer to Figure 6).

Sequential reads are initiated by

Figure 1.

Figure 2.

Figure 3.

Device Address

Byte Write

Page Write

(* = DON’T CARE bit)

(† = DON’T CARE bit for the 128K)

8

AT24CS128/256

AT24CS128/256

Figure 4.

Figure 5.

(* = DON’T CARE bit)

(† = DON’T CARE bit for the 128K)

Current Address Read

Random Read

Figure 6.

Sequential Read

9

AT24CS128 Ordering Information

tWR (max)

(ms)

10 3000 5.0 1000 AT24CS128-10PC

10 1500 0.5 400 AT24CS128-10PC-2.7

20 800 0.2 100 AT24CS128-10PC-1.8

ICC (max)

(µµµµA)

3000 5.0 1000 AT24CS128-10PI

1500 0.5 400 AT24CS128-10PI-2.7

800 0.2 100 AT24CS128-10PI-1.8

ISB (max)

(µµµµA)

f

MAX

(kHz) Ordering Code Package Operation Range

AT24CS128N-10SC

AT24CS128W-10SC

AT24CS128N-10SI

AT24CS128W-10SI

AT24CS128N-10SC-2.7

AT24CS128W-10SC-2.7

AT24CS128N-10SI-2.7

AT24CS128W-10SI-2.7

AT24CS128N-10SC-1.8

AT24CS128W-10SC-1.8

AT24CS128N-10SI-1.8

AT24CS128W-10SI-1.8

8P3

8S1

8S2

8P3

8S1

8S2

8P3

8S1

8S2

8P3

8S1

8S2

8P3

8S1

8S2

8P3

8S1

8S2

Commercial

(0°C to 70°C)

Industrial

(-40°C to 85°C)

Commercial

(0°C to 70°C)

Industrial

(-40°C to 85°C)

Commercial

(0°C to 70°C)

Industrial

(-40°C to 85°C)

Package Type

8P3 8-Lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)

8S1 8-Lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)

8S2 8-Lead, 0.200" Wide, Plastic Gull Wing Small Outline (EIAJ SOIC)

Options

Blank Standard Operation (4.5V to 5.5V)

-2.7 Low-Voltage (2.7V to 5.5V)

-1.8 Low-Voltage (1.8V to 3.6V)

10

AT24CS128/256

AT24CS256 Ordering Information

tWR (max)

(ms)

10 3000 5.0 1000 AT24CS256-10PC

10 1500 0.5 400 AT24CS256-10PC-2.7

20 800 0.2 100 AT24CS256-10PC-1.8

ICC (max)

(µµµµA)

3000 5.0 1000 AT24CS256-10PI

1500 0.5 400 AT24CS256-10PI-2.7

800 0.2 100 AT24CS256-10PI-1.8

ISB (max)

(µµµµA)

f

MAX

(kHz) Ordering Code Package Operation Range

AT24CS256W-10SC

AT24CS256W-10SI

AT24CS256W-10SC-2.7

AT24CS256W-10SI-2.7

AT24CS256W-10SC-1.8

AT24CS256W-10SI-1.8

AT24CS128/256

8P3

8S2

8P3

8S2

8P3

8S2

8P3

8S2

8P3

8S2

8P3

8S2

Commercial

(0°C to 70°C)

Industrial

(-40°C to 85°C)

Commercial

(0°C to 70°C)

Industrial

(-40°C to 85°C)

Commercial

(0°C to 70°C)

Industrial

(-40°C to 85°C)

Package Type

8P3 8-Lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)

8S2 8-Lead, 0.200" Wide, Plastic Gull Wing Small Outline (EIAJ SOIC)

Options

Blank Standard Operation (4.5V to 5.5V)

-2.7 Low-Voltage (2.7V to 5.5V)

-1.8 Low-Voltage (1.8V to 3.6V)

11

Packaging Information

AT24CS128/256

8P3,

8-Lead, 0.300" Wide,

Plastic Dual Inline Package (PDIP)

Dimensions in Inches and (Millimeters)

JEDEC STANDARD MS-001 BA

.400 (10.16)

.355 (9.02)

PIN

1

.280 (7.11)

.240 (6.10)

.037 (.940)

.300 (7.62) REF

.210 (5.33) MAX

SEATING

PLANE

.150 (3.81)

.115 (2.92)

.012 (.305)

.008 (.203)

.070 (1.78)

.045 (1.14)

.027 (.690)

.100 (2.54) BSC

.015 (.380) MIN

.022 (.559)

.014 (.356)

.325 (8.26)

.300 (7.62)

0

REF

15

.430 (10.9) MAX

8S1

, 8-Lead, 0.150" Wide,

Plastic Gull Wing Small Outline (JEDEC SOIC)

Dimensions in Inches and (Millimeters)

.020 (.508)

.013 (.330)

.244 (6.20)

.228 (5.79)

.068 (1.73)

.053 (1.35)

.010 (.254)

.007 (.203)

PIN 1

0

8

.157 (3.99)

.150 (3.81)

.050 (1.27) BSC

.196 (4.98)

.189 (4.80)

.010 (.254)

.004 (.102)

REF

.050 (1.27)

.016 (.406)

8S2,

8-Lead, 0.200" Wide,

Plastic Gull Wing Small Outline (EIAJ SOIC)

Dimensions in Inches and (Millimeters)

.020 (.508)

.012 (.305)

PIN 1

0

8

.213 (5.41)

.205 (5.21)

.050 (1.27) BSC

.212 (5.38)

.203 (5.16)

.013 (.330)

.004 (.102)

REF

.035 (.889)

.020 (.508)

.330 (8.38)

.300 (7.62)

.080 (2.03)

.070 (1.78)

.010 (.254)

.007 (.178)

12

Loading...

Loading...