Page 1

Bit Error Rate Test Set

packetBERTTM PB200

This product is discontinued.

View alternative products

CHARACTERISTICS

GENERATOR

.

packetBERT PB200

Features

Specs

Clock -

External clock input:

Frequency: DC to 200 MHz.

Amplitude: 0.5 to 5.0 V p-p.

Connector: BNC.

Termination select: 50 Ohm to -2 V, +3 V, AC or GND.

Input range: ECL, TTL, PECL compatible.

Threshold resolution: 10 mV step.

External clock reference input:

Frequency: 10 MHz, ±100 ppm maximum.

Amplitude: 0.5 to 2.0 V p-p, AC coupled.

Termination: 50 Ohm.

Connector: BNC.

Internal synthesized clock source:

Frequency: 1 Hz to 200 MHz.

Resolution: 1 Hz.

Accuracy: 10 ppm.

BURST clock:

Programmable gap: 16 Kbits maximum, 8-Bit resolution.

Pattern Generator -

PRBS: 2

Programmable word: 256 Kbits maximum, 8-Bit resolution.

Mark density: PRBS 2

Mixed mode frame: 256 Kbits maximum, 8-Bit resolution.

Error injection:

Error: Single, Rate, External (TTL).

Field select: Overhead, payload or both.

Error rates: Error rate of 10

Outputs -

Data and clock outputs:

Format: NRZ.

Configurations: Differential (True/Complement).

Source impedance: 50 Ohm.

Connector: BNC.

Amplitude: 0.5 V to 2.0 V, 10 mV step.

N

- 1, N = 31, 23, 15, 11, 10, 9, 7.

10

1 (1/8, 1/4, 1/2, 3/4, 7/8).

-n

, n = 3, 4, 5, 6, 7.

Page 2

Offset, 50 Ohm to GND: -2.0 V to +1.8, 10 mV step

(termination to 50 Ohm will increase the range for PECL).

Data delay range: ±1.0 ns, 20 ps resolution.

Rise/fall time: 300 ps typical, 500 ps maximum (20 to 80%).

Pattern sync output:

Signal level: 250 mV

into 50 Ohm load.

p-p

Auxiliary -

Data inhibit input: ECL, 50 Ohm to -2 V, BNC.

Clock disable input: ECL, 50 Ohm to -2 V, BNC.

ANALYZER

Data and Clock -

Data and clock inputs:

Clock input: External or internal from generator.

Data polarity: True/invert selectable.

Input mode select: Single-ended or differential.

Termination select: 50 Ohm to -2 V, +3 V, AC or GND.

Input range: ECL, TTL, PECL compatible.

Threshold resolution: 10 mV step.

Threshold resolution: 10 mV step.

Synchronization -

Auto search: Clock and data threshold, clock and data timing

skew, data pattern and polarity.

Measurements -

Frequency: 1 Hz to 200 MHz.

Bit errors: Window, Totalize, Timed Test, Simultaneous 1's, 0's

and All Errors.

BER test field: Overhead, payload or both.

Propagation delay: Up to 128 Kbits.

Eye-width: Up to 32 ns.

Reference Data Patterns -

Identical to Pattern Generator but independent.

Startup delay: 0 to 64 Kbits programmable.

Auxiliary Signals (BNC Connectors) -

Error count inhibit input: ECL, 50 Ohm to -2 V.

Error detect output: RZ, TTL, 50 Ohm source.

Analyzer clock disable: ECL, 50 Ohm to -2 V.

Data delay output: ECL, 50 Ohm source.

Common Characteristics

Pattern -

Controls: Start/Stop, Pause/Resume or Single Step.

Save/Load:

Floppy disk: 3.5 in.

Internal storage: 2 Mbits.

Pattern Editor Software requires PC running Windows 3.1 or

above.

Remote Interface -

Page 3

GPIB: IEEE 488.2 compatible.

RS-232C: DB9 connector.

Parallel printer: DB25 connector.

Monitor: DB15, VGA Analog Output.

Environmental -

Operating temperature: 5 to 40°C.

Storage temperature: -10 to 60°C.

Meets European Community EMC Directive 89/336/EEC for

electromagnetic compatibility.

Safety -

UL1244, CSA231, EN61010-1, IEC61010-1.

Power -

AC line: 100 to 120 V AC, 200 to 240 V AC.

Power consumption: 300 W maximum.

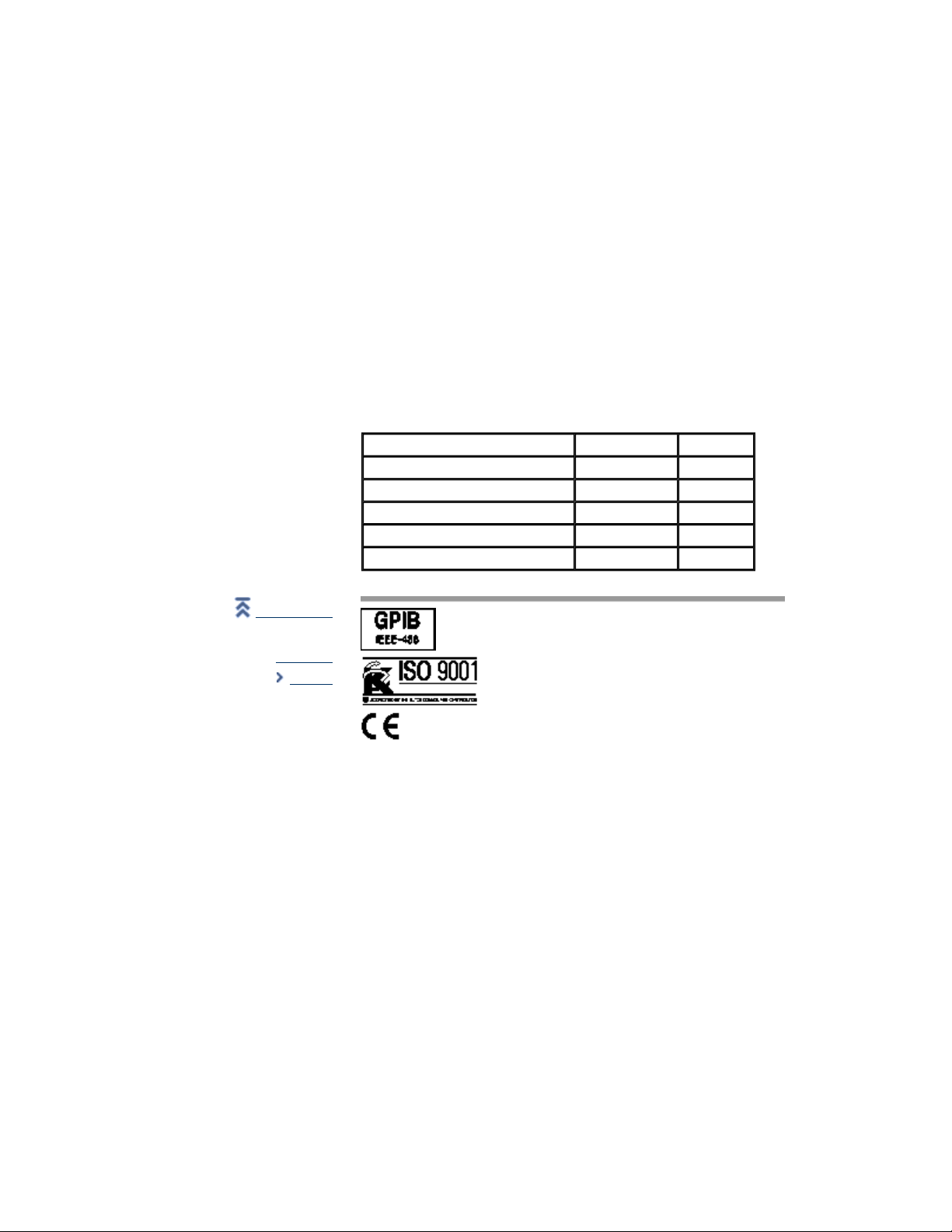

Physical Characteristics

Dimensions mm in.

Height 203.2 8

Width 355.6 14

Depth 508 20

Weight kg lbs.

Net 13.6 30

Top of Page

Features

Specs

49A-10733-3p350, 06/1997, 09/01/1999

Product(s) complies with IEEE Standard 488.2-

1987.

Tektronix Measurement products are

manufactured in ISO registered facilities.

Loading...

Loading...