Page 1

Agilent Technologies

8110A 150 MHz Pulse Generator

Technical Specifications

Flexible pulses or patterns for digital

designs

Key Features

· 150 MHz Timing

· 2 ns Variable Transitions

· 10 Vpp (20 Vpp) into 50 Ω

· 10 ps Resolution

· 0.1% Frequency Accuracy

· 4 kbit Pattern per Channel

· 3 and 4 Level Signals

· 1 or 2 Output Channels

· SCPI Programming Commands

· Small Size

· Graphic Display

Agilent Technologies

8110A 150 MHz Pulse Generator

The Agilent 8110A 150 MHz Pulse

Generator is a test instrument

that provides sufficient speed and

performance for testing designs to

their limits; testing under realworld conditions to verify the

proper function of the design.

· pulses, digital patterns and

multilevel waveforms for testing

current logic technologies

(CMOS, TTL, LVDS, ECL, etc.)

· credible measurements

· easy set-up and operation

· upgrade capability

Real World Pulses

With the pattern feature and the

the optional second channel of

the Agilent 8110A, real world s

ignals, like reflections, distorted

pulses, or three or even four-level

signals can be simulated.

Pattern Based Timing

The Agilent 8110A simulates all

the clock and data signals needed

to test digital designs. Conditions

such as extended delays can be

generated using pattern based

timing features.

Clean Pulses

The Agilent 8110A generates

clean pulses with 10 ps

resolution, low jitter and good

pulse performance across all

operating temperatures or

settings. Parameters and trigger

modes can be changed without

generating unwanted pulses, so

that reliable measurements are

guaranteed.

Page 2

2

High Accuracy

Excellent accuracy over a wide

temperature range guarantees

repeatable measurement results.

Frequency accuracy, jitter,

resolution and range can be enhanced

further when the Agilent 8110A is

used with the internal phase locked

loop (PLL) of the Agilent 81106A as

pulse period source.

Delay Calibration

Systematic delays caused by cables,

connections and adapters can be

compensated when the Agilent

81107A is installed. It offers enough

additional delay range to compensate

for 5 m of BNC cable.

External Clock or Reference

Frequency

1

An external synthesizer or system

clock can be used as clock source at

the clock input of the Agilent 8110A

to achieve the frequency accuracy

and required. This

feature is ideal for simulating

digital control signals

synchronously to the clock of the

microprocessor.

Up to 10 channels in parallel

2

Up to 4 Agilent 8110As can be slaved

to a master, so that 10

synchronous channels can be

programmed independently. With the

Agilent 81107A multichannel deskew

installed, the propagation delay of the

set-up can be

compensated, and all other output

channels zeroed to the reference

channel.

Smooth Integration into Automated

Test Systems

The Agilent 8110A can be smoothly

integrated into automated test

systems, ensuring:

· low integration costs

· low costs of ownership

All Digital Waveforms

The waveform and trigger

flexibility of the Agilent 8110A make

it a universal digital

stimulus for any automated test system.

Reliable Measurements

Accuracy is specified over the whole

temperature range that exists in a

test rack. Setting check and built-in

diagnostics allow you to monitor the

correct operation of the Agilent

8110A in an automated test system.

Easy Rack Integration

The small size of the Agilent 8110A

saves valuable rack space. Rear panel

connectors and rack mount kits are

optional.

Reduced Programming

Investment

The local user interface eases the

transition from manual to

automated measurements and from

the R&D bench to

automated manufacturing test. All

parameters of the Agilent 8110A are

programmable via GPIB. SCPI

(Standard Commands for

Programmable Instruments)

facilitates the standardization of test

programs.

Low Cost of Ownership

The proven hardware reliability of

Agilent test and measurement products results in high uptime of test

systems and low maintenance costs.

The Agilent 8110A offers a 3 year

standard warranty.

Easy Set-up and Operation

View all timing parameters for both

channels at a glance. Timing and

level parameters can be entered in

any format, e.g. period as frequency.

The alternative graphic display shows

the timing relationship of all pulse

parameters on both channels

graphically, making setting up the

pulse generator easy - no extra

oscilloscope is required.

Pulses and patterns can be set up

quickly using the convenient

cursor keys, knob and data entry

keys. You can even use the Autoset

Key to resolve all timing conflicts.

Memory Card

Settings can be stored

permanently either internally or on

the memory card for duplication in

another test set-up.

1

only with the Agilent 81106A PLL/External Clock

2

only with the Agilent 81107A Multichannel Deskew

Page 3

3

Specifications

Specifications describe the instrument's warranted performance. Non-warranted values are described as typical. All specifications apply

after a 30 minute warm-up phase with 50 Ω source/load resistance and separate channels. All specifications are valid from 0°C to 55°C

ambient temperature.

Timing Characteristics

Measured at 50% amplitude at fastest transitions in continuous mode and 50 Ω source impedance.

Burst Count: 2 to 65536 (single or

double pulses).

Delay: delay, phase or % of period.

Fixed delay: 34 ns typical

Double pulse and delay:

mutually exclusive.

Duty cycle: set between 0.1% and

94.0% (subject to width limits.

99.9% with overprogramming).

Repeatability: is typ. four times

better than accuracy.

Transition times: leading/ trailing edge

or % of width. Leading and trailing

edges are independent within one of

the following

overlapping segments

(1:20 ratio): 2 ns (3 ns) - 20 ns,

10 ns - 200 ns, 100 ns - 2 ms,

1µs - 20 µs, 10 µs - 200 µs,

100 µs - 2 ms, 1 ms - 20 ms,

10 ms - 200 ms.

Overprogramming: values can be

entered exceeding the specified

range.

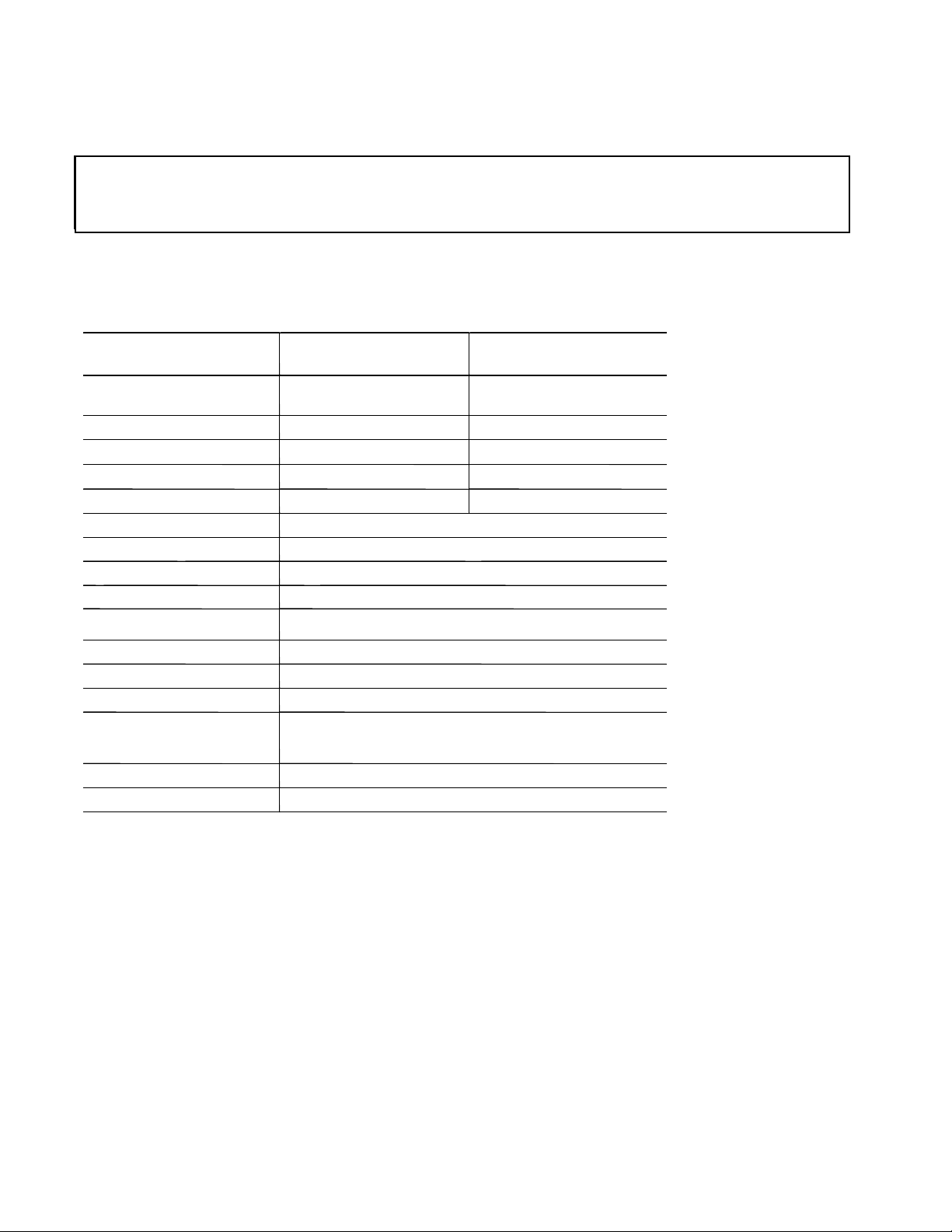

Mainframe

Output module

Agilent 8110A

Agilent 81103A

Agilent 8110A

Agilent 81103A with 81106A PLL

Frequency range

1 Hz to 150 MHz

1 mHz to 150 MHz

Timing resolution

3 digits, 10 ps best case

4 digits, 10ps best case

RMS jitter (period, width, delay)

0.03% + 25 ps

0.003% + 20 ps

Period range

6.65 ns to 999 ms

6.65 ns to 999 s

Accuracy

± 5% ± 100ps

± 0.1%

Width range

3.30ns to (period 3.3

ns), maximum 999ms

Accuracy

± 5% ± 250 ps

Add. variable delay range

[1]

0.00

ns to (period 6.6

ns), maximum 999

ms

Accuracy

± 5% ± 1 ns

Double pulse delay range

6.65ns to (period - width - 3.3 ns), maximum 999 ms

Min. period

13.3

ns (75 MHz)

Accuracy

± 5% ± 250 ps

Transition time range (10/90)

2.00 ns to 200 ms variable

Minimum

(with overprogramming)

≤

2.0 ns for levels within ± 5

V window.

< 2.5 ns for all levels

1.4 ns typ. for ECL levels (20/80)

Accuracy

± 10 % ± 200 ps

Linearity

3% typ. for transitions > 100 ns

Notes:

[1] Additional 0

ns to 28

ns delay range with the Agilent 81107A Multichannel

Page 4

4

Level/Pulse Performance Characteristics

Level parameters: voltage or

current, high or low level, offset or

amplitude.

On/off: relays connect/disconnect

output (HiZ)

Load compensation: the actual load

value can be entered (for loads ≠ 50 Ω

to display actual output values.

Normal/complement: selectable.

Limit: programmable high and low lev-

els can be limited to protect the

device-under-test.

Channel Addition

If the instrument is equipped with 2 output modules, channel 2 can be added to channel 1 internally. In this case the

second output is disabled. 2, 3 an 4 level signals can be generated.

separate channels channel addition (at output channel1)

Channel 1 Channel 2 Channel 1 Channel 2

source impedance 50 Ω 1 ΚΩ 48 Ω 500 Ω

accuracy typ. ± 1%

voltage (50 Ω load)

amplitude 100 mV to 10.0 V 200 mV to 20.0V 0 V to 19.5 V

[1]

0 V to 20.0 V

(doubles into open)

high level -9.90 V to + 10.0 V -18.8 V to 19.0 V -19.3 V to + 19.5 V -20.0 V to 20.0 V

low level -10.0V to +9.90 V -19.0V to +18.8 V -19.5 V to + 19.3 V -20.0 V to + 20.0 V

level accuracy

± (1% ampl + 50 mV) ± (1% ampl + 100 mV) - -

resolution 10mV 20 mV 10 mV 20 mV

current (into short)

amplitude - 4 mA to 400 mA - 0 mA to 800 mA

high level -396 mA to 400 mA - -792 mA to + 800 mA

low level - -400 mA to + 396 mA - -800 mA to + 792 mA

minimum transition 2.0 ns

[2]

2.5 ns 7.5 ns typ. 2.5 ns typ. 7.5 ns typ. 30 ns typ. 30 ns typ.

minimum period 6.65 ns 24 ns typ. 24 ns typ. 90 ns typ.

minimum width 3.3 ns 12 ns typ. 3.5 ns typ 12 ns typ. 45 ns typ. 45 ns typ.

delay accuracy ± (5% + 1 ns) - - - - add. fixed delay (typical) 0 - ---+ 0.6 ns typ. +0.6 ns typ.

Max. external voltage ± 25 V

Short circuit current ± 400 mA max.

Dynamic Crosstalk < 0.1% typ.

Baseline noise 8 mV RMS typ.

Overshoot/preshoot/ringing ± 5% of amplitude ± 20 mV

Settling Time 30 ns typical

Note:

[1] max. amplitude of bipolar signals is limited to values between 10 Vpp (-0.2 V/+ 10.3 V peak levels) and 14 Vpp (- 7 V/+ 7 V peak levels).

[2] for levels within ±5 V window.

Page 5

5

Pattern Mode

Pattern length:

4 kbit/channel and

strobe output.

Output format: RZ (return to zero),

NRZ (non-return to zero), DNRZ

(delayed non-return to zero).

Random pattern:

PRBS 2^(n-1) n = 7,8,...,12

Trigger Modes

Continuous:

continuous pulses,

double pulses, bursts (single or

double pulses) or patterns.

External triggered: each active input

transition (rising, falling or both)

generates a single or double pulse,

burst or pattern.

External gated: the active input level

(high or low) enables pulses, double

pulses, bursts or patterns. The last

single/double pulse, burst or pattern

is always

completed.

External width: the pulse shape

can be recovered. Period and width of

an external input signal is maintained. Delay, levels and transitions

can be set.

Manual: simulates an external input

signal.

Internal triggered (only with Agilent

81106A): internal PLL replaces an

external trigger source. Pulses, double

pulses, bursts or patterns can be set.

Inputs and Outputs

External input

used for trigger, gate or external

width.

Input impedance: 50 Ω /10 kΩ selec-

table.

Threshold: - 10 V to + 10 V.

Max. input voltage: ± 15 Vpp.

Sensitivity

::

≤ 300 mVpp typical.

Transitions: < 100 ns.

Frequency: dc to 150 MHz

Min. pulsewidth: 3.3 ns.

Strobe output and trigger output

Level:

TTL or ECL selectable.

Output impedance: 50 Ω typical.

Strobe output: user-defined, 16 kbit pat-

tern (NRZ) when in pattern mode.

Max. external voltage: - 2 V/+7 V.

Transition times: 2 ns typical.

Pattern: 4096 bits NRZ in pattern

mode.

Delay from external input to strobe

output:

in pattern mode same as for

trigger output.

Trigger Output

Level: TTL or ECL selectable

Output impedance: 50 Ω typical

Trigger pulse width: typically 50% of

period

Maximum external voltage: -2 V/+7 V

Transition times: 2 ns typical

Delay from external input to trigger

output:

l8.5 ns typical

Agilent 81106A PLL/External Clock

for the Agilent 8110A

Can be retrofitted without

recalibration. Useful for

applications which require a phase

locked loop (PLL) or an external

clock:

Locking to an external frequency

reference: the internal PLL is locked

to the 5 MHz or 10 MHz frequency at

the PLL reference input.

High accuracy: the output period is

determined by the internal PLL.

Period accuracy, range, resolution,

and jitter are improved as shown in

the diagram. Asynchronous triggering possible.

Internal triggered burst: the internal

PLL replaces an external trigger

source.

External clock: the output period is

determined by signal at clock input.

Frequency accuracy can be increased

by using a precise external clock.

Trigger synchronously to external

clock:

the output period is

synchronous to the signal at clock

input. The signal at external input is

used for arming.

Period

Range: 6.65 ns to 999 s

Accuracy: ±0.1%

Resolution: 4 digits, 10ps best case

RMS-jitter: 0.003% + 20ps

Stability: 50 ppm/year typical

Trigger Modes

Standard trigger modes and:

Internal triggered: pulses, double

pulses, bursts or patterns

Figure 1

Clock Input/ PLL Reference Input to

be used as:

a) external system clock input pulse

frequency = input

frequency,

b) 5 MHz or 10 MHz frequency reference input for internal PLL.

Frequency can be measured. Rear

panel BNC connector.

Input impedance: 50 Ω or 10 kΩ

selectable

Threshold: -10 V to +10 V

Maximum input voltage: ±15 V

Input transitions:<100 ns

Input Frequency: dc to 150 MHz

Minimum Pulse width: 3.3 ns

Input sensitivity: -300 mVpp typical

Delay from clock input to trigger

output:

22 ns typical

Agilent 8110A

Clock

Input

PLL

Ref

Input

External

Input

Internal Oscillator

Agilent 81106A

PLL

Continuous

Pulse Period

Trigger Signal

Page 6

6

Agilent 81107A Multichannel Deskew

for the Agilent 8110A

Can be retrofitted without

recalibration. Supports two

output channels. The

multichannel deskew can be used for

two applications:

Up to 10 channels: compensates delay

between external input and trigger

outputs when using up to five

8110As synchronously.

Delay calibration: compensates for

measurement system delays or pretrigger delays of oscilloscopes.

Variable range: 0 ns to 28 ns

Additional fixed delay: 6.5 ns typical

Resolution: 10 ps

User Interface

Overprogramming:

all parameters can

be overprogrammed

(exceeding specifications) to fully

exploit the hardware limits.

Setting check: warning messages indi-

cate potentially conf licting parameters due to inaccuracy.

Error messages indicate

conflicting parameters.

Help key: displays a context-

sensitive message.

Autoset key: resolves all timing con-

flicts.

Non-volatile memory: current

setting is saved on power-down.

Up to nine user settings and one fixed

default setting can be stored in the

instrument.

Clear memory: clears all nine user set-

tings.

Memory card: 320 settings can be

stored on a 1 MB PCMCIA card

(MS-DOS).

Remote Control

Operates according to IEEE

standard 488.2, 1987 and SCPI

1992.0.

Function Code: SH1, AH1, T6, L4, SR1,

RL1, PP0, DC1, DT1, C0.

Programming times: all checks and

display off.

General

Operating temperature:

0°C to +55°C.

Storage temperature:

-40°C to +70°C.

Humidity: 95% r.h. up to 40°C ambi-

ent temperature.

EMC: conforms to EN50082-1,

EN 55011, Class A.

Noise emission: 5.7 bel typical.

Battery: Lithium CR2477-N.

Safety: IEC1010, CSA1010.

Power requirements:

100-240 Vac, ± 10%, 50-60 Hz;

100-120 Vac, ± 10%, 400 Hz.

Power consumption:

300 VA max.

Max. dimensions (H * W * D):

89 mm * 426 mm * 521 mm.

Weight: 9.2 kg net, 13.8 kg

shipping.

Recalibration period:

one year recommended.

Warranty: three years standard.

ASCII command Typ. exec. time

One parameter

or mode

30 ms typ.

Recall setting 250 ms typ.

16 k pattern transfer 600 ms typ.

Page 7

7

Ordering Information - 8110A

The minimum order must include the 8110A mainframe and one 81103A output channel. A second output channel, the 81106A PLL/external clock or the

81107A multichannel deskew are optional. All configurations are available from the factory. Alternatively, additional modules can be ordered later and fitted by

the user or an Agilent service facility.

Qty per MainframeCategory

min max

Description Number

Mainframe

[1]

1 150 MHz Pulse Generator Mainframe Agilent 8110A

Modules

1 2 10 V/2 ns Output Channel Agilent 81103A

0 1 PLL/External Clock Agilent 81106A

0 1 Multichannel Deskew Agilent 81107A

All options are orderable with the mainframes.

Accessories

Opt UN2

Rear Panel Connectors

Opt 1CP Rack Mount and Handle Kit (5062-3975)

Opt 1CN Handle Kit (5062-3988)

Opt 1CM Rack Mount Kit (5062-3974)

Opt 1CR Rack Slide Kit (1494-0060)

Opt UFJ 1 MB SRAM Memory Card

Agilent 15104A Pulse Adder/Splitter

Language options

Opt ABD

German Localization (08110-91112)

Opt ABF French Localization (08110-91212)

Opt ABZ Italian Localization (08110-91312)

Opt ABE Spanish Localization (08110-91412)

Opt ABJ Japanese Localization (08110-91512)

Opt AB0 Chinese Localization (08110-91612)

Additional documentation options

Opt 0B2

Additional English Operating Manual

(08110-91012)

Opt 0BW Service Manual (08110-91021)

08110-91031 Service Documentation (Component Level)

Support Options

Opt 1BP MIL Std. 45662A Calibration with Test Data

Opt W32 3 Year Customer Return Calibration Coverage

Opt W34 3 Year MIL Calibration Service

Opt W50 5 Year Customer Return Repair Coverage

Opt W52 5 Year Customer Return Calibration Coverage

Opt W54 5 Year MIL Calibration Service

Page 8

Related Agilent Literature

· Agilent Family of Pulse/Pattern

Generators, brochure,

p/n 5980-0489E

Agilent Technologies'

Test and Measurement Support,

Services, and Assistance

Agilent Technologies aims to maximize the value

you receive, while minimizing your risk and

problems. We strive to ensure that you get the

test and measurement capabilities you paid for

and obtain the support you need. Our extensive

support resources and services can help you

choose the right Agilent products for your

applications and apply them successfully. Every

instrument and system we sell has a global

warranty. Support is available for at least five

years beyond the production life of the product.

Two concepts underlay Agilent's overall support

policy: "Our Promise" and "Your Advantage."

Our Promise

Our Promise means your Agilent test and

measurement equipment will meet its advertised

performance and functionality. When you are

choosing new equipment, we will help you with

product information, including realistic

performance specifications and practical

recommendations from experienced test

engineers. When you use Agilent equipment, we

can verify that it works properly, help with

product operation, and provide basic measurement assistance for the use of specified

capabilities, at no extra cost upon request. Many

self-help tools are available.

Your Advantage

Your Advantage means that Agilent offers a wide

range of additional expert test and measurement

services, which you can purchase according to

your unique technical and business needs. Solve

problems efficiently and gain a competitive edge

by contracting with us for calibration, extra-cost

upgrades, out-of-warranty repairs, and on-site

education and training, as well as design, system

integration, project management, and other

professional services. Experienced Agilent

engineers and technicians worldwide can help

you maximize your productivity, optimize the

return on investment of your Agilent instruments

and systems, and obtain dependable

measurement accuracy for the life of those

products.

By internet, phone, or fax, get assistance with

all your test & measurement needs

Online assistance:

www.agilent.com/find/assist

Phone or Fax

United States:

(tel) 1 800 452 4844

Canada:

(tel) 1 877 894 4414

(fax) (905) 206 4120

Europe:

(tel) (31 20) 547 2000

Japan:

(tel) (81) 426 56 7832

(fax) (81) 426 56 7840

Latin America:

(tel) (305) 267 4245

(fax) (305) 267 4286

Australia:

(tel) 1 800 629 485

(fax) (61 3) 9272 0749

New Zealand:

(tel) 0 800 738 378

(fax) 64 4 495 8950

Asia Pacific:

(tel) (852) 3197 7777

(fax) (852) 2506 9284

Product specifications and descriptions in this

document subject to change without notice.

Copyright © 2000 Agilent Technologies

Printed in Germany 10/2000

5980-1212E

For more information, please visit us :

www.agilent.com/find/pulse_generator

Loading...

Loading...