Page 1

LIST

OF

SECTION

SECTION

TABLE

OF CONTENTS

ILLUSTRATIONS

ONE--INTRODUCTION

Main

Conponents

Case

design

Differences

from

520l1040ST

TWO..THEORY

OF OPERATION

Overview

Main

Systen

Microprocessing

unit

GIue

Main

Menory

Direct

l4enory

Access

MFP Interrupt

Control

Audio/Video

subsystem

Video

Shifter

Video Display

Menory

GIue

Memory Control-Ler

Sound

Synthesizer

Video Interface

Input/output

subsystens

MIDI

Intelligent

Keyboard

Parallel Interface

RS232

Interface

Disk Drive

Interface

Hard

Disk

Interface

Systen Startup

System Errors

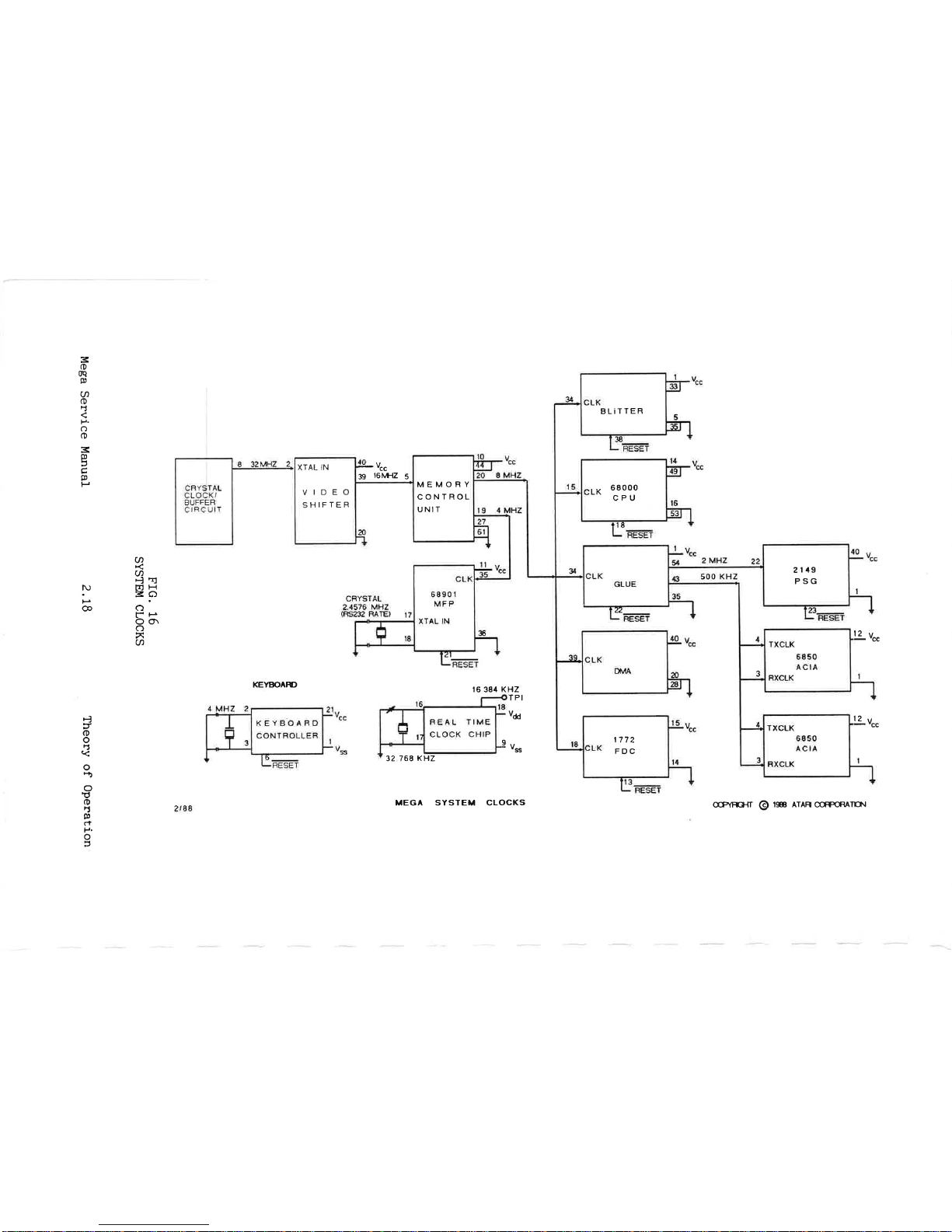

Functional

block

diagran

Systen

clock

diagra-m

t.2

t.2

I.5

2.t

2.2

2.2

2.2

2.3

2.3

2.4

2.5

2.5

2.5

2.6

2.6

2.6

2.6

2.8

2.8

2.9

2.70

2.Lt

2.L2

2.L3

2.t4

2.15

2.L6

2.t7

11

Mega

Service

Manua1

i.1

Table

of Contents

Page 2

SECTION

THREE--TESTING

THE

MBGA

Overview

Test equipnent

Test Configuration

Trouble-Shooting

a

dead

unit

ST

Diagnostic

Cartridge

Power-up

RAM test

ROM

test

Color test

Keyboard

test

MIDI test

RS232 test

Audio test

Tining test

DMA test

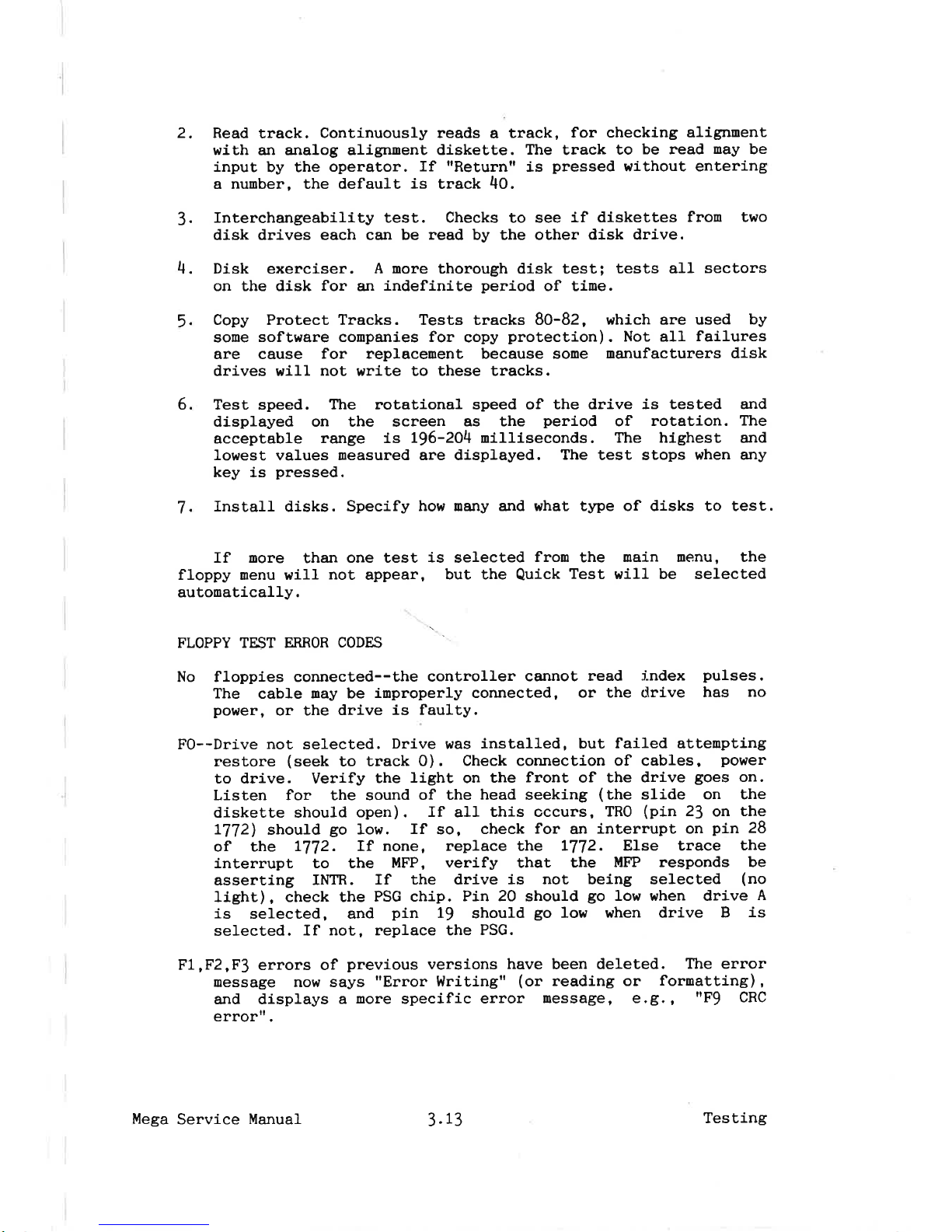

Floppy

Disk test

Printer/Joystick

test

High

Res

Monitor

Blitter test

Clock

test

Expansion

port

test

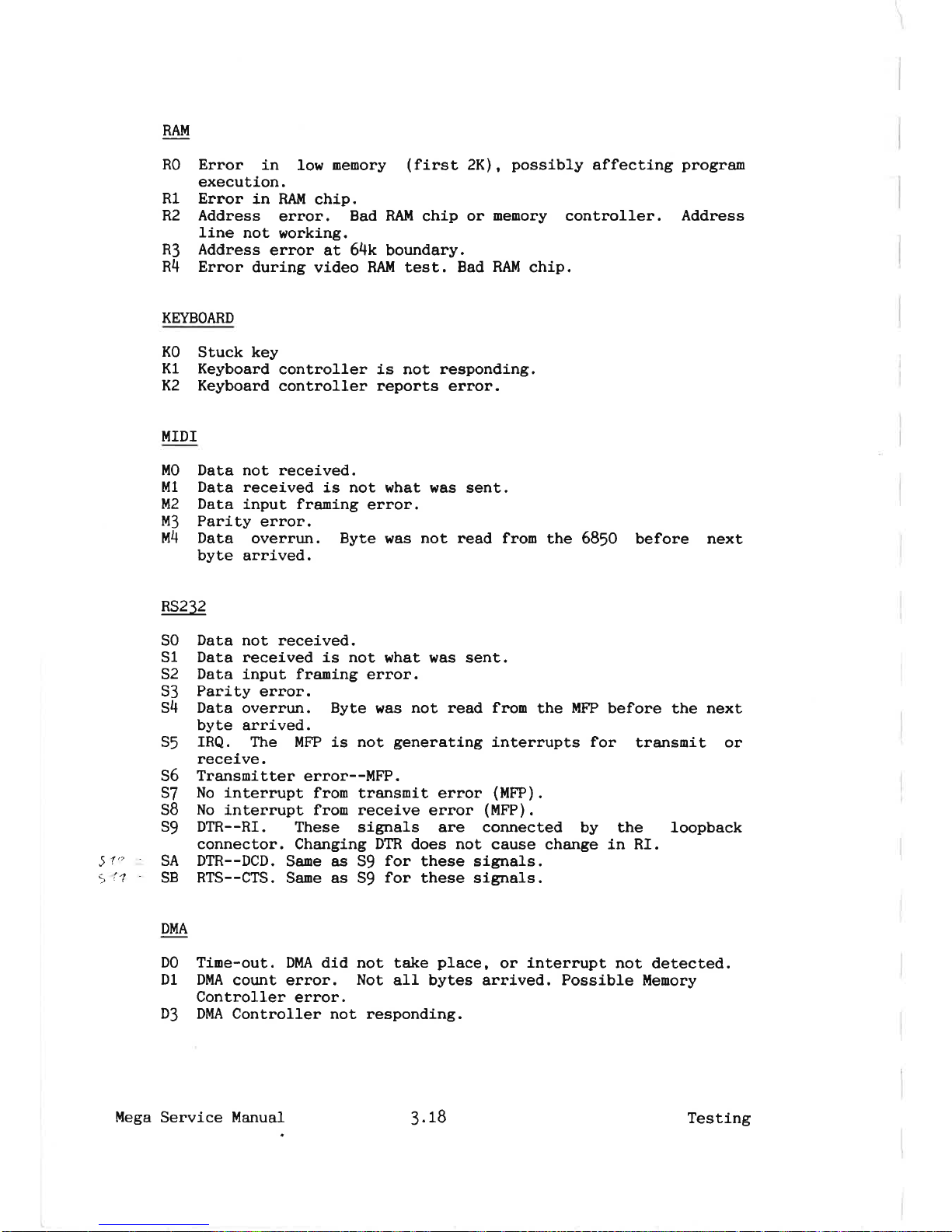

Error

Codes

Quick

Reference

SECTION

FOUR--DISASSBMBLY/ASSEMBLY

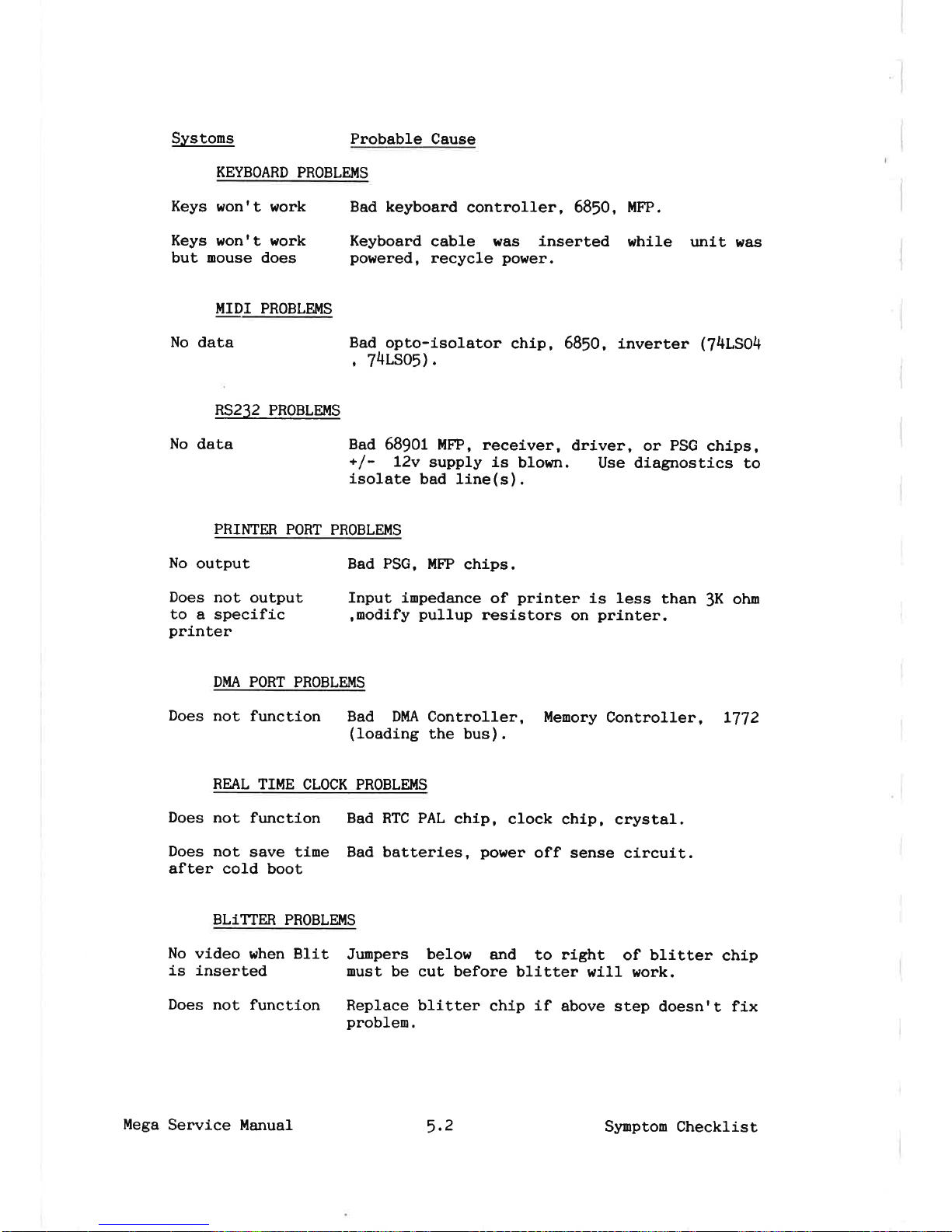

SECTION

FIVE-.SYMPTOM

CHECKLIST

Display

problems

Disk

Drive

Problens

Keyboard

problens

MIDI

problems

R5232

problens

Printer

Problems

Hard

Disk

Problens

Real

Time

Clock

Problens

Blitter

Problens

3.1

3.1

3.2

3.2

3.4

3.4

3.6

3.7

3.7

3.9

3.9

3.

10

3.

11

3.r7

3.r2

3.

13

3.t5

3.16

3.L6

3.L7

3.r7

3.18

5.t

5.L

5.2

5.2

5.2

5.2

5.2

5.2

5.2

í.2

Mega Service

Manual

Table of

Contents

Page 3

SECTION

SIX.-DIAGNOSTIC

FLOIlICHARTS

SECTION

SEVEN..PARTS

LIST AND

ASSEMBLY

DRAWINGS

SECTION

EIGHT-.SCHEMATICS

AND

SILKSCREEI'I

SECTION

NINE--GLOSSARY

Mega

Service

Manual

i.3

Tab1e of

Contents

Page 4

LIST OF

ILLUSTRATIONS

FIG 1

MEGA

COMPUTER

FIG

2 BATTERY COMPARTMEI.IT

FIG

3

BACK PANEL

FIG 4

I,EM

SIDE

PANEL

FIG

5

TOP

OF

KEYBOARD

FIG

6

BOTTOM OF

KEYBOARD

FIG

7

MEGA MOUSE

FrG

I

t{oNrron

poRr

FIG

9

MIDI PORTS

FrG

10 MoUSE/JOY

PoRTS

FIG

11 PRINTER

PORT

FrG 12

RS232 PoRT

FIG 13

EXTERNAL

FLOPPY

PORT

FIG 14 EXTERNAL

HARD DISK

PORT

FrG 15

FLJNCTTONAL

BLoCK

DTAGRAM

FIG

16

SYSTEM

CLOCKS

1.1

L.2

1.3

r.3

1.4

1.4

1.5

2.7

2.8

2.9

2.LO

2.tL

2.L2

2.L3

2.16

2.r7

Mega Service

Manual

11 List

of

Illustrations

Page 5

SECTION ONE

INTRODUCTION

The Mega

2

and

Mega

4 are Motorola

MC68000 nicroprocessor based

conputers with

sinilar

architectures

to the

520ST/

1040ST line. They

are

styled as

a

nain CPU

unit

with a detached

keyboard. The Mega 2 has

2 negabytes

of RAM,

the Mega 4 contains 4 negabytes. Both the Viega

2

and

Mega

4 have

a built-in 1 Megabyte

(720K

fornatted)

3,5

inch floppy

disk

drive,

and an internal switching

power

supply with built-in

cooling fan.

Since the

onty difference between

the

Mega 2

and

Mega

4 is the

size

of its RAM,

this

nar¡ual

will

use

'

Mega

'

as a

generic

tern

which

refers

to both

products.

Power Light

Disk

Drive

Drive Busy Light

FIG. 1

COMPUTER SYSTEM

Mega

Service

Manua1

ItIEGA

1.1

Introduction

Page 6

The main

components

of

the

Mega 2 and

Mega

4 are:

CPU

Main board assembly

Disk drive

Power supply

& cooling

fan

RF Shield

(upper

and

lower)

CPU

Plastic case

(upper

and

lower)

KEYBOARD

Keyboard assembly

Interface board

assembly

Keyboard

Plastics

(upper

and

lower)

MOUSE

Mouse board assembly

Mouse Plastics

(upper

and

lower)

CASE

DESIGN

shows

the

CPU

portion

and figure

7

shows the

o

o

o

o

o

o

o

o

o

o

Figures

1

thru 4

keyboard

portion,

Battery

Housing

of the

IUEGA,

5

ar¡d

6

mouse.

shows

the

Cover

--

size AA Batteries

+

Top

of

Computer

(+)(-)

FIG. 2

BATTERY COMPARTMENT

Mega

Service

Manual

r.2

Introduction

Page 7

On/Off

lo

Power

Js

Frc.

3

BACK PANEL

FIG. 4

LEFT SIDE PANEL

loppy

I

Printer

Midi

ln

Cartridge

Keyboard

Mega

Service

Manual 1.3

Introduction

Page 8

Function

Keys

I

¡oyst¡Jx

Port

I

FIG.

5

TOP OF KEYBOARD

Arrow

Keys

Bottom

of

Keyboard

Calculator

Keypad

Computer

Jack

V

I

MouseiJoystick

FIG.

5

BOTTOM OF KEYBOARD

Mega

Service

Manual

1

.ll

Introduction

Page 9

Clicking

Left Mouse

Button

Right

Mouse

Button

FrG.

7

MEGA

UOUSE

Differences

fron

520ST/1040ST

o

New version of

T0S

o More

nenory requiring

74LS243

buffers on

MAD lines

o

ReaI

tine

clock chip

& support circuit,

o

Graphics Co-Processor

(BITtsLiT)

o

Internal expansion

connector

& support circuit

o

Cooling

fan

o

New

case

styling with

detached

keyboard

Mega

Service

Manual

r.5 Introducti.on

Page 10

Page 11

SECTION

T!{O

THEORY OF OPERATION

OVERVIEW

The Mega 2 and

Mega 4 share a coruDon architecture,

using the sa.ne

LSI

chip set,

and case styling.

Ttre only difference

is the addition

of

one

ba¡rk of

2 Mega-bytes of

RAM, for a total of 4

Mega-bytes of

RAM

on

the Mega 4.

Ttre hardware can be considered

as consisting of

a

nain

systen

(central processing

unit ar¡d

support chips)

a¡rd several

Input/Output subsystens

.

Main

System

o

Mc680o0 running at SMltz

o

192 Kbyte Read Only

Memory

o

2

or 4

Mega-byte

Randon Access Menory

o

Direct Menory

Access

support

o Systen

tining and

Bus control

o

Interrupt control

Audio/Video Subsystem

o

Bit Mapped video display,

using

l2k

bytes of

RAM, relocatable

anywhere

in nenory.

There

are

three display

nodes available:

a.

32O

x 200

pixel,

16

color

palette

îron

jL2

selectÍons

b. 640

x 200

pixel,

4

color

palette

fron

!12

selections

c. 640

x

400

pixet,

nonochrone

o

BITBLiT

support

o

Monitor

interface analog:

RGB, Monochrone

o

Audio output:

programmable

sound chip

with

J

voices

Input/Output Subsystens

o

Intelligent

Keyboard

with

2

button

mouse/ioystick interface

o

Parallel

printer

interface

(Centronics)

o

RS-232C serial

interface

o

DMA

Port & connector

for

external

drive

o

Hard disk

drive

interface &

Laser

Printer

o

Musical

instrunent

network connunication

:

Musical

Instrunent

Digital

Interface

(MIDI).

o

ReaI

Time Clock with

battery

backup

o

ROM

Port

Mega

Service

ManuaL

2.7

Theory of Operation

Page 12

MAIN

SYSTEM

The

main system

includes

the

microprocessing

unit,

main

nemory

(ROM

and

RAM)

,

systen

control,

intepupt

control,

and

general

purpose

DMA controller.

MicroProcessing

Unit

The

Mega uses

the

Motorola

MC68000

16 bit

external/32

bj-t

internal

data

bus,

Z4 Uit

address

bus

nicroprocessor,

running

at

I

Mflz.

Glue

Glue

(naned

because

it holds

the

systen

together)

is

such an

important

component

that

it

is

involved

in nearly

every

operation

in

thè

computer.

The

functions

nay be

sumnarÍzed

as

follows:

Clock

dividers--

takes

ttre

I

Mtlz clock

and outputs

2

Mllz and

500

KHz clocks.

Video

tining--

B-Lank,

DE

(Display

Enable),

Jlsync:

gnd Hsync

are

use¿

to

generãtlsignals

for

the

video

display.

There

is a

Ìead/Write

register

in Gtue

wfrich

nay be

written

to

configUre

for

50

or

60 Hz

operation

(done

by

the

Operating

System).

Interrupt

priority--

interrupts

fron the

MFP

and video

tining

are

codeffisofpriorityonoutputsIP11andÍPL2tothe

68000.

These

leve1s

correspond

to

no

interrupts,

MFP

interrupts,

VSYNC

interrupt,

HSYNC

interruPt.

Signa]

and

Bus

qlbitration--

Glue

decodes

addresses

to

generate

crrip

,

DMA

Controller,

Progranmable

Sound

Genàrator,

Memory

Controller,

and

ROMs.

It

receives

signals

from the

MFP,

DMA,

Menory

Controller,

to

synchronize

data

transfer.

It arbitrates

the

bus

during

DMA transfers

to

prevent

CPU and

DMA

devices

from

interfering

with

each

other

(see

DMA

below)

'

IlleEal

condition

detectiq4--Glue

asserts

Bus

Error

(BERR)

if

writing

to

ROM,

writing

byte

writing

to

system

DeII¡ory

when

the

processor

is

in user

mode.

AIso occurs

if a

device

does

not

respond within

the

required tine

linit.

For example,

the

CPU

tries to

read

from

nemory

and

the

Memory

Controller

does

not

assert

DTACK.

certain

conditions

are

violated,

such

as

sized

data

to

a word sized

register,

or

Mega Service

Ma¡rual

2.2

Theory

of

Operation

Page 13

Main

Menory

Main

menory

consists

of L92 kbytes

of ROM

and

one

or

two

banks

(2

Mega-byte

each) of d¡manic RAM.

rn

addition,

the

cartridge

sLot alrows

access

to 128 Kbytes

of

ROM.

All

nenory is

directly

addressable.

The

components

of

the

ne¡nory

systen

are:

ROM,

RAM,

RAM

buffers, Menory

controller,

a¡¡d

Glue. Tt¡e

Operating

System resides

nostly

in

ROM,

wíth

optional

segnents loaded

fron

disk into RAM.

R.{M is

organized

as

16

bit

words

and

nay

be

accessed 16

bits

at a

tine

or

8 bits

at a tine.

Even nunbered

addresses refer

to the high

I

bits

of a word

and odd addresses

refer

to the low

I bits. RAIII

ís made

up

of

1 Megabit

X 1

chips; in

the Mega 2

there

are 16

chips,

giving

z

Mbytes,

while in

the Mega

4 there is

a¡r additional

bank

of L6

chips,

giving

two tines

the

nemory,

or 4 Mbytes.

BAM menory

nap:

000008-000800

Systen nenory

(priveliged

access)

000800-1FFFFF

low

bank

200000-3FFFFF

high

bank

(Mega

4 only)

Note:

the

first

8 bytes

of ROM are napped

into

addresses

O-7.

These

are reset

vectors

which the

68000 uses

on start-up.

The

Operating

Systen is located

in

two

lMeg

x

I

ROM

chips

in

current

versions

(192k).

Menory

Controller--takes

addresses fron

the address

bus and

converts

to Row Address

Strobe

(RAS)

and Column

Address

Strobe

(CAS).

All

RAIì|

accesses

are controlled

by this Atari

proprietary

chip,

which

is

progrannable

for

up to 4

Megabytes

of

nenory.

Tt¡e

Operating

System

determines how

nuch Eernory

is

present

and

prograns

the

Menory

Controller

at

poner-up.

Ttre Memory

Controller refreshes

the

dynanic

RAMs,

loads

the Video Shifter

with display

data,

and

gives

or

receives

data

during direct nernory

access

(DMA).

Glue--decodes

addresses for RAM

a¡rd ROM

a¡rd asserts

output

signals

to

enable these devices

(also

decodes

addresses for

nost

hardware

registers

to

provide

chip selects,

as well as nany

other

functions.

See Glue

description

above.

).

Direct Menory Access

Direct

menory

access is

provided

to

support both low

speed

(25O

to

500

Kilobits/sec)

and

high

speed

(up

to 8

Megabits/sec)

Sbit device

controllers.

The floppy

disks transfer

data via low

speed

DMA

and the

hard

disk

(or

other devices on the hard

disk

port)

transfer

at high

speed.

For DlvlA

to take

place,

the

Menory

Controller

is

given

the

address

of

where to tal<e data

fron

or

put

data

in

RAM,

the

DMA

Controller

is

set up

(which

channel,

high

speed or low

speed, and how

many

bytes)

and the

peripheral

is

given

a

comnand to send

or

receive

data. The

entire block of data

(the

size

must

be

given

to

the

DMA

Controller

and

the

peripheral

before the

operation

starts)

is

then

transferred

to or

from menory

without intervention

by the CPU.

Mega

Service Manual

2.3

Theory

of Operation

Page 14

For

exanple,

in a

transfer

of

a

sector

fron

the

floppy

to

nenory'

the

floppy

conúro1ler

will

signal

the

DItlA,

Controller

that

a

byte

is

ready

by

asserti"á

ponO,

tn"

óue chip

will

read

the

byte

ar¡d

signal

Ci".l

Glüe

will

signal

the

Menory

Controller,

-and

the

Menory

Controller

will

read

the

byte

fron

the

DMA

Óontrotler

a¡rd

place

it

in

the

address

which

was

set

up

previously.

The

DMA

Controller

will

then

wait

for the

next

byte

fron

thè

floppy

controller,

and

the

process

wítl

repeat

until

Itr"

äpecified

number

ôr

uyt"s

has

been

transferred'

Tra¡rsfers

from

nenory

to

fJ-oppy

are

sinilár.

The

floppy

initiates

every

transfer

by

requesting

data

on

FDRQ.

At

high

speed

(hard

disk

port),

there

is

a

difference:

as

a

byte

is

ready

to

transfer

to

or

fron

the

DMA chip,

the

DMA

Controller

will

assert

ACK

to

tel

tne

peripheral

know

the

byte

ís

avaÍlable

or

has been

reaa.

The

DMA

Controller

can

store

up

to

l2

bytes

in

internal

De¡rory'

This

is

,r."."".ry

if the

68000

is using

the

bus,

and

the

DMA

nust

wait

to

transfer

to

ä.roty.

Data

nay

be

input

fron

the

port

without

being

lost

or

slowing

down

the

tra¡¡sfer

speed'

MFP

InterruPt

Control

The

68901

MFP

handles

up

to

16

interrupts.

Currently

all

but

one

are

used.

Each

interrupt

can

be

nasked

off

or

disabled

by

progrernning

ñ;

MFp.

Th;8

inputs

äre

also

directly

readable

by

the

CPU.

When

the

MFp

receives

an

inlerrupt

input,

or

generates

an

interrupt

internally,

if the

interrupt

is enatled,-MFPlyf

witt

be

driven

low.

When

the

CPU

is

ready

to

respond,

it

signals

interrupt

acknowledge

(Fco-2ìigh and

vltlA

Iow)

and

GIue

*nilI

."""tt

r¡cr

(interrupt

acknowledge).

The

MFP

will

assert

DTACK

and

put

a

vector

number

on

the

data

bus,

which

the

cPU

will

read

and

use

lo

calculate

the

address

of

the

interrupt

routine'

The

interrupts

controlted

by

the

MFP

are:

nonochrone

monitor

derecr

(MONOMOÑI-,--R5232

(including

CTS,

999,

RI),

disk

(FDINT

a¡rd

HDINT),

parallef'óort

gÚSV,

display

enable

(DE,

equals

start

of

display

iine),'S'giO

IRQs

ior

keyboard

and

MIDI

data,

and

MFP timers.

ñoi árr

l/O

operations

use

interrupts.

The

CPU can

also

poll

the

MFp

while

waitini

for

an

operation

to

conplete.

The

MFP

has

four

timers,

used

by

tñe

Operating

System

for

event

tining

and

used

by

the

RS232

port

for

transnit

and

receive

clocks'

Mega

Service

ltlanual

2.4

Theory

of

OPeration

Page 15

AUDIO/VIDEO

SUBSYSTEM

The

video

subsysten

consists

of

the video display nenory,

the

Menory

controller,

Glue,

a

graphics

control chip

(video

shifter),

a

graphics

processing

unit

(BImLiT)

,

and a discrete

section

to drive

the

video

output.

The audio

subsysten

consists

of

a

Progra.mnable

Sound

Generator

chip with a transistor

output

anplifier.

Video

Shifter

There

are 16

color

palette

registers

Ín

the shifter.

AII 16

are

nay

be used in

row resorution,

4

nay

be used

in

high

resolution,

a¡¡d

only

one

is

used in high resorution

(actuarly,

onry bit

0

of

register

0

is

used

for inverse/nornal

video). Each

palette

is

progr¡mmed

for

8

Ievels

of intensity

of red,

blue,

and

green,

so

there

are 8 x

I x I

=

112

colors

possible.

For

a

given

pixel,

the coror

which is

displayed

is

taken fron

the

palette

referred

to by

getting

infornation

from

each

logical

plane (see

description

of

video

dispray menory

betow). The

shifter

will

output the red,

green,

and

blue

levers

specified

by

that

palette;

note

there are three

outputs for

each color. Each

output is

either

on or off. Thus,

the nu¡nber

of

possible

output levels

is

Z to

the

lrd

power

=

$. The

three

outputs

are sr¡nmed

through

a resistor

network

to

proportion

the voltage level

to

give

I equal

steps. In

monochrome

node,

the

color

palettes

are bypassed

a¡rd there is

a

separate

output.

Video Display

Menory

Display

nemory

is

part

of nain nenory

with

the

physical

screen

origin

located

at the top left

corner

of the

screen.

Display

Eenory

is

configured as 1, 2,

or

4

(nigh,

nediun,

or

1ow

resolution)

Iogical

planes

interwoven

by 16 bit

words into

contiguous

nemory

to forn

one

32

Kilobyte

physical

plane

starting

at a 256 byte

half

page

boundary. The

starting address of display

Eer¡ory is

placed

in

the Menory

Controller's

Video

Base

Address

register

by

the Operating

Systen

or

application. The Menory

Controller

will load

display

infornation

into

the video

Shifter 16

uits

at a tine,

and the Video

Shifter

wirl

decode this infornation

to

generate

a seriar

dispray

strean. rn

nonochrone

mode,

each bit represents

1

pixer

on or off. rn

color,

bits

are conbined fron

each

plane

to

generate

the comect level

of red,

green,

and blue.

For

exanple, in

low resolution

(4

ptanes)

4 words

are

loaded

into

the

Video Shifter for

each

word

(16

pixels

displayed

on the

screen. Tt¡e

Video

Shifter

conbines

bit 0 from

each word

to forn

a four

bit

nunber

(0-15),

and takes the

color

from

the

palette

referenced

by that

nunber

(e.s.

0101=5,

use color from

palette

register

!)

a¡rd

outputs

those revers,

then takes

bit

1 fron

each

plane

and outputs

the coror

from

the

palette

referenced

by those four

bits,

etc.

Mega

Service ManuaÌ 2.5

Theory

of Operation

Page 16

G1ue

GIue

provides

tining

control

to

the

Menory

Controller,

video

output,

and

monitor/RF output.

VSYNC

input

to

the

Menory

Controller

causes

the

starting

address

of

the

display

nenory

to be

reloaded

into

the

address

counter

during

vertical

blanking.

DISPLAY

EI{ABLE

(DE)

tells

the

Memory

Controller

a¡¡d

Video

ShÍfter

that

a display

line

ís being

scanned

anâ

data

shoutd

be

loaded

into

the

Vídeo

Shifter.

BLANK shuts

off

the

video

output

fron the

Video

Shifter

during

periods

when

the

scan

is

not

in a

dilplayable

part

of

the

screen.

VSYNC

and

HSYNC

both

go

to

the

monitor

output

a¡rd

RF

modulator.

These

signals

synchronize

the

nonitor

or

T.V.

vertical

a¡rd

horizontal

sweep

to

the

display

sigPal.

Menory

Controller

In addition

to

the

inputs

from

Glue

nentioned

above,

there

are two

output

control

signals

associated

with

video.

DCYC

strobes

data

from

display

nenory

lñto tne

Video

Shifter.

CMPCS

(color

nap select)

is

active-only

when

changing

the color

attributes

in

the

color

palettes.

Sound

SYnthesizer

The

yM2149

Progranmable

Sound

Generator

(PSG)

produces

nusic

synthesis,

sound

effects,

and audio

feedback

(e.g.

alarns

a¡rd

key

"ii"t

"¡.

The clock

input

ís

2 MHz; the

frequency

response

range

is

30

Hz to

tZJ

KHz,

There are

three

sound

channels

output

fron

the

chip,

which

are

míxed and

sent

to the

nonitor

speaker.

The

pSG

is also

used

in

the

system

for

various

f/O

functions

relating to

printer

port,

disk

drive,

and

RS232.

This

Iocation

r.s

to

Atari

Blitter

a

DMA device

that

moves

block

of

nenory

data

fron a source

a destination

location

through

a

given

logic

operation.

Single

or

multiple

word

increments

and

decrenents

are

provided

for

transfer

to destination.

There are

16

possible logic operation

rules

associated

with

the

merging

of

source

a¡rd

destination

data.

In

addition,

with

the

16 wõrd

patterns ran a¡rd

three

L6 bit

end-nask

registers,

the

blit can

also

be

used to

perforn

operations

such

as area

seãd

filling,

pattern

filling,

brush

line

drawing,

text

and

graphic

transformations,

etc.

For

more infornation,

please

refer

to

the

user

nanual

which

is

included

in the

Developer

Kit.

Mega

Service

Manual

2.6

Theory of

Operation

Page 17

Real

Tine

Clock

with

Battery Backup

Ttris

device has

counters for

Time

and Calendar

buÍIt-in. Clock

data

are expressed with BCD

code. The

lower four

address

and data

Iines

are

used to

program

the device

and access

the clock

through

signal lines

RTCCS, RTCRD, RTCh¡R

which

generated

fron

a decoder. A

RESET

line is

also

provided

to reset

the chip when

the system is reset.

The

naín clock supplied to

the devÍce is

a

32.768

l<hz

oscillator

which

will

be adjusted by a trimmer condenser

so that it

will output

through

the CLKOIJII

line

a standard

clock signal

of

16.384 Xfrz.

In

addition, a

JV

battery backup ca¡¡ be used

to

keep

the clock running

during

power

down.

For nore

detail,

please

refer

to

the application na¡rual

fron

the

nanufacturer

(RICOH

part

number RP5C15)

Mega

Service Manual 2.7

Theory

of Operation

Page 18

Video

Interface

The

th¡o

types

of

interface

are

provided in the

Megas

are

a¡alog

RGB a¡rd

nonochrone.

The

presence

of

a

nonochrone

nonitor

ís detected

by

the

MONOMQN

input

(when

â

nonochrone

nonitor

is connected,

it

will

be

Iow).

The

possible

disPlays

are:

Monochrome:

single

enitter

foltower

a.nplifier

driving

the output

of

the

Video

Shifter.

RGB:

resistor

network

sums

colors

each

have an

output.

Monitor

Inputs:

outputs

for each

color.

Ttre

three

emitter

follower

a.mplifier

to

drive

Hsync--TTL

level,

negative,

3.3

k ohn.

Vsync--TIL

Ievel,

negative,

3.3

k ohn.

Monochrone--digital

1.0V

P-P'

J!

ohn.

R,G,B--analog

0-1.OV

P-P'

75

ohn.

Audio--1V.

P-P,

1k ohn.

û

Monitor

1

-

Audio

Out

2

-

ComPosite

SYnc

3

-

General

PurPose

OutPut

4

-

Monochrome

Detedt

5

-

Audio

ln

6

-

Green

7-Red

I

-

Plus

12-Voll

Pullup

9

-

Horizontal

SYnc

FIG.

8

MONITOR

PORT

10 - Blue

11

-

Monochrome

12

-

Vertical

Sync

13

-

Ground

Mega Service

Manual

2.8

Theory

of

Operation

Page 19

rNPUT/oUTPUT

SUBSYSTEMS

Musical

Instrument

Connunication

The

Musical

Instrunent

Digital

Interface

(MIDI)

allows

the

integration

of

the

Mega

with

nusiõ

sysnthesizers'

sequencers'

drun boxes

and

other

devices

fossessing

MIDI

interfaces.

HiSh

speed

(3L'25

Kilobaud)

as¡rnchronous

current

loop

serial

communication

of

keyboard

"rrd

ptog"an ilfornation

is

provided

by

two

ports, MIDI

gUT

and

MIDI

IN

(MIDI

oUT

also

supports

the

optionat

ttlt¡t

ntnu

port)

.

MIDI

specifies

thar

data

co.rsi"f'ãi

8

A.t.

bits

preceded by

one

start

bit

a¡rd

followed

by

one

stoP

bit.

Connunication

takes

place

via

a

6850

nCfe.

The

CPU

reads

and

writeJ-to

l[ã-OóiO

in

response

to

interrupts

which

are

passed

fron

the

6850

to

the

MFP

interrupt

controller.

Ttre

systen

is

interfaced

to the

outside

via

trdo

inverters

on

the

tra¡rsnit

side

a¡rd

an

LED/photo-

transistor

chip

on

the

input

side.

The

input

signal

is routed

around

through

two

inverters

to

the

output

connector

where

it

is called

II{IDI

THRU

in

order

to

allow

chaining

of

nultiple

devices

on the

MIDI

bus'

Js

J¡

Midi

Out

1

-

THRU

Transmit

Data

2

-

Shield

Ground

3

-

THRU

LooP

Return

4

-

OUT

Transmit

Data

5

-

OUT

LooP

Return

Midi

ln

1

-

Not

Connected

2

-

Not

Connected

3

-

Not Connected

4

-

lN

Receive

Data

5

-

lN

LooP

Return

FIG.

9

MIDI

PORTS

Mega

Service

Manual

2.9

Theory

of

OPer'ttion

Page 20

Intelligent Keyboard

The

keyboard

trarismits

nake/break

key scan codes,

ASCII

codes,

nouse data,

joystick

data,

in response

to external

events, and

tine-

of-day data

(year,

month, day,

hour, minute,

second)

in response

to

requests by the

CPU. Comnunication is

controlled

on the

nain

board by

a

6850 device

a¡rd

on

the keyboard assenbly by the

lMHz

8 bit

HD6301

Microconputer Unit.

The HD6301 has internal RAM

and

RoM. Included in

ROM are self-test diagnostics which are

perforned

at

poh'er-up

and

whenever the

RESET

connand

is

sent over

the serial connunication

line

by the CPU.

The MC6850 is read

a¡¡d written to

by the CPU in response to

interrupts

which are

passed

to

the

CPU by Èhe

MFP interrupt

controller.

The 2 Button Mouse is

a¡r opto-mechanical

device with the

following

characteristics: a resolution of

100

counts/inch,

a

mæ<imun

velocity of

10 inches/second

and a

naxinum

pulse phase

error of

50

percent.

The

joystick/nouse

port

has inputs

for

up, down,

left, ríght, right

button,

Ieft

button.

The right

button

equals the

joystick

trigger, a.nd the

left

button

is

wired to the second

joystick

port

trigger.

The

joystick

has

four

directions

(up,

down, etc. ) and

one trigger.

Mouse/Joystick

1

-

Up/XB

2

-

Down/XA

3 - Left/YA

4 - Right/YB

5

-

Not

Connected

6

-

Fire/Left

Bulton

7-

+sVDC

I

-

Ground

9

-

Joyl

Fire/Right

Bulton

1-up

2

-

Down

3 - Lefl

4

-

Right

5

-

Reserved

6

-

Fire

Button

7-

+SVDC

8

-

Ground

9

-

Not

Connected

FIG.

10

MOusE/JoY

PoRT

v

Joystick

3

Mega

Service Manual

2.ro

Theory

of

Operation

Page 21

Parallel

Interface

The

parallel

port

is

prinarily

intended

as

a Centronics

type

printer

interface,

but

can also

be used as a

general

purpose

r/0

port.

centronics

STROBE

and

BUSY

are

supported. BUSY

is read

by the MFp

chip.

Data

and strobe

signals

are output

by the YM2149

psc

chíp.

Not

all

Centronics

printers

are compatible

with

this

port.

The

current

loading

on

the data lines

should

not

exceed 2.3 mA.

(TtrÍs

corresponds

to

a

2.2k

ohn resistor

pull-up

on the

printer

side.

)

Ttre

port

can

be

programned

to

be

read

directly

by the CPU,

with

Gtue

chip

select.

input

or output.

The

PSG

chip

is

doing

address

decode

to

provide

ç

Printer

1

-

STROBE

Output

2-Dala0

3-Data1

4-Dala2

5-Data3

6-Data4

7-Data5

8-Dala6

9-Dala7

aaaaaaaaaaaaa

aaaaaaaaaaaa

?5 .r¡

2l :2 l!

2f

19

16

rr 16

!5

10

-

Not

Connected

11

-

BUSY

lnput

12-17

-

Not

Connected

18-25

-

Ground

FIG. 11

PRINTER PORT

Mega

Service Manual

2.17

Theory

of Operation

Page 22

RS232C Interface

The

RS232C

interface

provides

asynchronous

serial

connt¡¡¡ication

with

five

handshake control

signals:

Reguest to

Send

a¡rd

Data

Terninal

Ready are

output

by the

PSG chip;

Clear to

Send,

Data

Carrier

Detect,

and

Ring

Detect are

input to the

MFP

chip.

The

MFP

contains

a

USART

(Universal

Synchronous/Asynchronous

Receiver/Tra¡rsnitter)

which

handles

data

transmission

and

reception.

The

2.4576

MHz clock

to

the

MFP

is

divided by the

tiner

D

(pin

16) output

of

the

MFP

to

provide

the

basic

clock

for receiver

and

transnitter.

Data

rate of

50

to

19200

bits

per

second

are

supported.

f488 tine drivers

and

1489

line receivers

with

+/-

I2v. supply

meet the

EIA

RS232C

standard

for electrical

interface.

\

Modem

1

-

Protective

Ground

2

-

Transmitted

Data

3

-

Received Data

4

-

Requesl

to

Send

5 - Clear

lo Send

6

-

Not Connected

7 - Signal

Ground

8

-

Data

Carrier

RePeat

9-19

-

Not Connected

'¡

aaaaaaaaaaaaa

aaaaaaaaaaaa

2t

20

-

Data

Terminal Ready

21

-

Not Connected

22

-

Ring lndicator

23-25

-

Not

Connected

FIG.

T2

RS232

PoRT

Mega Service

Manuaf

2.L2

Theory of

Operation

Page 23

Disk Drive

Interface

The Mega

conputers

have

a

built-in floppy

disk controller

(a

lrJestern

Digital

L772) and

logic for

selecting

up to

trr¡o single

or

double sided drives. The Mega has one built-in

floppy disk

drive a¡rd

provision

for

one external disk drive. The hlestern Digital WDt772

Controller

services both drives. Drive

and side selection

is

done

by

outputs

on the

YM2149 PSG

chip. The CPU reads

a¡rd writes

to the

L772

through

the

DMA

Controller,

Tl:e 1772

Ínterrupts

the CPU on

the

INTR

Iine, via

the

MFP interrupt

controller. Tl:re L772

accepts

high

level

comnands, such as

seek,

fornat

track,

write

sector,

read

sector,

etc.

and

passes

data to the

DMA Controller

(see

DMA

controller under

Main

Systen,

above,

for

details

on DMA

tra¡rsfer).

The L772 ínbemupts the

CPU

when the operation

is

conplete.

The

CPU

is

freed fron

nuch

of the

overhead of disk I/0.

I

Floppy

tlsk

1 - Read Dala

2-Side0Select

3

-

Logic Ground

4 - lndex

Pulse

5-Drive0Select

6-DrivelSelect

7 - Logic

Ground

I

-

Motor

On

9 - Direction

ln

10

-

Step

FrG.

L3

EXTERNAL

FLOPPY

11

-

Write Data

12

-

Write

Gale

13

-

Track

00

14

-

Write

Protecl

PORT

Mega

Service Manual

2.13 Theory of Operation

Page 24

DMA

Port;

Hard

Disk

Interface

The

hard

disk

drive

interface

is

provided through

the

DMA

controller;

the

hard

disk

controller

is off-board

and is

board

a¡rd

is sent

conna¡¡ds

via an

SCSI-like

(SnaII

Conputer

System

Interface)

command

paraneter

block.

Data

is transferred

via

DMA.

l,Jriting

to

the externâI

controller

causes

HDCS

(Hard

Disk

Chip

Se]ect)

to

go

low and

CAl

to

go

high.

DMA tra¡¡sfers

are

controlled

by

the

external

device.

fJhen

data

is available,

or

the

device

is

ready to

accept

data,

HDRQ will

be

driven

high by

the

external

controller.

The

DMA chip

nust

respond

within

2!0

nanoseconds

with

ACK

(}ow)

to

acknowledge

that

data

is on the

bus

or

has

been

read

fron the bus-

The

Memory

Cóntroller

feeds

data

to

or accepts

data

fron the

DMA

Controller.

Transfers

can

take

place

at

up

to

1 Mbyte/second.

a

Had

Disk

1-Data0

2-Dala1

3-Data2

4-Data3

5-Data4

6-Data5

7-Data6

8-Data7

9

-

Chip

Select

10

-

lnterruPt

Request

11 - Ground

1

2

-

Reset

FIG. 14

EXTERNAL

HARD DISK

aaaaaaaaaa

aaaaaaaaa

13

-

Ground

14

-

Acknowledge

'15

-

Ground

16

-

A1

17

-

Ground

18

-

Read/Write

19

-

Data

Request

PORT

Mega

Service

Manual

2.r4

Theory of

Operation

Page 25

SYSTEM

STARTUP

After

a

RESET

(power-up

or reset

button) the

68000 will

start

executÍng at

the address

pointed

to by

locations

4-J, which is RoM

(GIue

maps

8 bytes of ROM

at

FC0000-J

into

the addresses

0-7).

Location

000004

points

to the start

of the operating

systen code in ROM

(FCOOOO-

FEFFFF).

The following

sequence is

then executed:

1. Perforn

a

reset instruction

(outputs

a

reset

pulse).

2. Read

the

longword

at cartridge

address

F40000. If

the

data

read

is a

"nagic

nunber",

execute fron

the cartridge

(diagnostic

cartridge tal<es over here). If not,

continue.

3.

Check for

a warn start

(see

if RAM locations

vrere

previ.ously

written), initialÍze

the nenory

controller,

and continue

running

the application which

was

running

before

the reset if

it

was a warm start.

Initialize

the

PSG

chip, deselect

disk drives.

Initialize

color

palettes

a¡rd set screen

address.

If not

a

h,arn start, zero De[¡ory.

Set up operating system variables in RAM.

Set up exception

vectors.

Initialize MFP.

Set screen

resolutÍon.

11. Attempt

to boot

floppy;

attenpt to boot

hard

disk;

run

progran

if

succeeded.

SYSTEM

ERRORS

The 68000 has a feature calted

exception

processing,

which takes

place

when an Ínterrupt or bus error is indicated

by external

logic,

or

when the CPU detects an emor

internally,

or

when certain

types of

instrtrctions

are executed.

An exception

wiII cause the CPU to fetch a

vector

(address

to a

routine)

fron

RAM

and start

processing

at the

routine

pointed

to by

the vector. E:<ception vectors

are

initialized

by

the

operating system.

Those exceptions whích

do

not have legitimate

occurrences

(interrupts

being legitimate) have

vectors

pointing

to a

general purpose

routine which wiII

display some

nunber

of bonbs

showing

on

the screen

(nushroon

clouds in

older versions of disk loaded

operating

systen).

The number of

bonbs equals the

nunber

of the

exception

which occurred.

4.

5.

6.

7.

8.

9.

10.

Mega

Service

ManuaL 2.15 Theory

of Operation

Page 26

System

errors

nay or ¡nay

files

from disk wiII cause the

Verify the diskette and

disk

computer.

not

be

recoverable.

Errors

in

loading

system to crash,

necessitating

a

reset.

drive before

attempting

to repair

the

NUMBER OF BOMBS

AND MEANINGS

(No.

26,28,30, ana 64-79 wiII

not bomb, as

they are

legitinate.

)

2 Bus

Error.

Glue asserted bus error

or

CPU detected an error.

]

Address Error. Processor attenpted

to access word or

long word

sized data on an odd

address.

IIIegaI

Instruction.

Processor fetched an

instruction from

ROM

or

RAM which nas not a

legal instruction.

Zero

Divide. Processor was asked

to

perforn

a

division by zeto.

Chk

Instruction. This is a

legal instruction,

if

software uses

this,

it nust

install

a

handler.

Trapv

Instruction.

See

Chk

instruction.

Privilege Víolation. CPU

was in user

mode, tried to

access

a

location in

supervisor

address space.

Trace. If

trace

bit

is

set

in

the

status

register, the CPU will

execute

this exception after every

instruction. Used to debug

sofuware.

10 Line 1010 Ernulator.

CPU read

pattern

1010 as an

instruction.

Provided to allow user to

emulate

his own

instructions.

11 Line 1111 Emu1ator. See

Line 1010

Emulator.

12-23 Unassigned, shouLd

be

no

occurrence.

24

Spurious

Interrupt.

Bus

error

during

interrupt

processing.

25-3L Autovector

Interrupt.

Even nunbered

vectors are used, others

should

have

no

occurrence.

32-63

TRAP

Instruction.

The CPU read

instruction

which forced except-

ion

processing.

64-lg MFP

interrupts.

BO-255 User

interrupts.

Note: If

you

have an emor

nessage such

as

"T0S

ERROR

35",

then the

possible

errors are:

1- The

file in

progress

is

bad.

2- The

total

number of

folders

in

the sysLem

has

exceeded

the 4O-folder

linit. However, there

is

a

program

which

can be used to

extend this

limitation on

folders.

3-

No ha¡rdles left or

too

nany

open

files.

5

6

7

B

9

Mega

Service

Manual

2.L6

Theory of Operation

Page 27

=

o

æ

p)

Ø

o

ts.

o

o

3

p

Þ

P

JOYSTICK

I

MOUSE

KEYBOAFD

MIDI

DMA

R5232

PORT

VIDEO/AUDIO

CONNECTOF

I

rk

TXD

r20vAc

+lzvDc(1

6 A)

+

sVDC(3 0 A)

OUT IN THRU

¡lf

VSYNC

*

HSYNC

*

41

d

z

c)

Ê

H

o

z

tr.

,71

fE'

F-r

t.c)

o.

C)

i(P

\tl

tt

H

c)

7

Þ

=

MONO

MON

v

P

\¡

CONTROL BUS

32MHZ

Ê

J

o

o

ìt

o

H)

o

ì5

o

õ

Þ

cl

P.

o

t(

MoNo

RGB

*

VIDEO

DISPLAY

MEMOFY DATA BUS

DRAM CONTROL

niEMORY

CONTBOLLER

t^IT

2t88

MEGA FUNCTlONAL BLOCK

DIAGRAM

coPyRtGHT

@

1988 ATARI CORPORAIION

Page 28

3

o

æ

ID

Ø

o

ÈJ

ts.

o

o

=

e

)

ç

çD

ts

(t)

U)

F]E

rTJ

H

=G)

c)

t-P

oo\

C)

x

Ø

P

P

Õ

a:

o

o

7t

o

H)

O

ìd

o

4

ID

a?

P,

o

39

16Àitlz

5

KEYBOAÐ

12v

!3v""

ccPlFEHr

@

ls ATAR COFFOFA'IÛ\¡

t6 38¿t KHZ

TPI

vdd

o

t

Va"

32 768

KHZ

MEGA SYSTEM CLOCKS

BL¡TÏER

MEMORY

CONTROL

UNIT

XTAL

IN

VIDEO

SHIFTER

LK

68ooo

CPU

21 49

PSG

1772

FDC

Page 29

SECÎION

THREE

TESTING

OVERVIEI{¡

Ttris

section

pertains

to the test

equipment, diagnostic

software,

and test

procedures

used to verify

correct operation and

repair

the

Mega/ST

computers.

Tt¡e

diagnostic cartridge

should be

used if

possible.

If

the unit

gives

no

display

or

R5232

output

when

running

the cartridge,

see

rrTroubleshooting

a Dead

Unit'r

below.

Since

the

level

of

conplexity

in

the Mega/ST

systen is

high,

it

shouldn't

be expected

that this docunent

can

cover all

possible

problens

or

pinpoint

the causes; rather,

the intent

here is

to

give

a

systematic

approach which

a

technician

can use to narrolt

down

a

problen

to Íts nost

likely

source. Experience

in

troubleshooting

conputer

systems

is

assumed. Knowledge

of the

68000

processor

nay

be helpful. Economics

witl

be arì ínportant

consideration;

due

to the

low

cost

of the

Mega/ST

conputer line,

little

tine can be

justified

in

troubleshooting

down

to the

component

level

when

it

may be

cheaper to

exchange the

entire

sub-assembly. Many

of

the

¡nore

expensive

(and

critical) cotrponents

naybe

socketed,

naking

verification

and

replacenent

faster.

TEST EQUIPMEI.¡T

The following

equipnent will

computer:

be needed

to test the Mega/ST

i

Atari

SCl224 RGB Monitor

(or

sinilar)

i

Atari

SM124

Monochrone

Monitor

(or

siniJ-ar)

r

Atari

SF354 or

SF314

Floppy Disk

Drive

I

Mega/ST

Port Test Fixture

I

Mega

Expansion Test

Fixture

(Mega

only)

*

RS232

Loop-Back

Connector

t

MIDI Loop-Back

Cable

ì

Mega/ST

Test

Diagnostic

Cartridge

(Revision

4.0)

t

Diskettes

(2)

I

RS232

ternirral

(or

Mega in

tff52

enulator node)

In

addition,

the following

itens

will

be necessary

to

troubleshoot

and

repair

failed

computers:

r

0scilloscope

(100MHz

Recconmended)

*

Digital Multimeter,

1l

FS

(or

better)

*

Snall

Ha¡rd

Tool,

& Soldering

lron

*

Spare Parts

Mega

Service Manual

3.1

Testing

Page 30

TEST CONFIGI.JRATION

With the

power

switch

off,

Ínstall

the

Diagnostic

Cartridge

(IMPORTAI.IT--if

the

cartridge

does

not

have

the

plastic

enclosure,

BE SURE

THE

CARTRIDGE

IS

INSTALLED

WITH

THE CHIPS

FACINC

DOIW)

.

Connect

cables

fron test

fixture

into the

hard

disk

port,

parallel

port,

and

joystick

/

nouse

ports.

The

ioystick

cables

should

be

plugged

in so that,

if the

fixture

ports

were

directly

facing the

cornputer

ports,

the

cables

would

not be

crossed.

PIug the

R5232

and

MIDI

loopback

connectors

into their

ports.

PIug

the

color

nonitor

into the

nonitor

output

(a

nonochro¡ne can

be used

instead)

Power on the

unit. Some

tests

will

be

run autonatícally;

in

a

few seconds the

nenu screen

should

appear.

If

the

screen appeArs,

skip

down to

"

Mega/ST

Diagnostic

Cartridge

",

below.

If

not, read

next section

"Troubleshooting

a

Dead Unitrr.

If the unit

is being used

as

a terninal

for a

host computer,

it should

be disconnected

fron the

host before using

the

diagnostic;

otherwise,

the

host

nay think

soneone

is logging

oD,

and will send

nessages which

will act

like

keystrokes

input to the

diagnostic.

TROIJBLESHOOTING

A

DEAD UNIÎ

In the event

that

the

systen

is correctly

configured

and

pclwered

a¡¡d

no display

appears,

this

is the

procedure

to

use

for

determining

the

problen.

This assr¡nes

elementary

steps

have

been

taken,

such as

checking

the

LED in the

forward

left corner

of

the

compu+,er

to verify

the

unit

is

powered

and

naking sure

the

nonitor

is working.

1. Connect a

dumb terninal

to

the

RS232

port

of

the unit

under

test

(IJ.U.T.

).

You can

use an

Mega/ST

running the

l/T52

terminal

emulator

program--see

the

owner's

nanual

for

setting

up

tÆ52.

The

cable

should connect

pin

2

(serial

out)

of the U.U.T

to

pi.n

3

(serial

in) of the

terminal,

a¡rd

vice versa.

Connect

pin

7

(sround)

to

pin

7.

The terminal

should

be set up

for

9600

bps,

I

bits of data,

1 stop bit,

no

parity

(this

is

the

default

condition

for

the

VT)2 enulator).

Insert the

Diagnostic

Cartridge

into the U.U.T.,

8¡¡d

power

on

the unit.

If

the

Diagnostic

Cartridge

messages

appear

on

the

display of

the terninal,

use

the

diagnostic

to troubleshoot

tire

computer.

If not, the

conputer

will

have to be

disassenbled

to

iroubleshoot.

Refer

to

"Diagnostic

Cartridge"

below

for information on

using

the cartrÍdge.

If no activity

is

seen

on

the

RS232

port

or

display,

continue

with

(2)

next

page.

Mega

Service

Manual

3.2

Testing

Page 31

2. Disassenble

the conputer

so that the

printed

circuiÈ board is

exposed

(see

Section 4,

Disassenbly).

Power up the conputer.

Using

a¡¡

oscilloscope,

verify

the SMHz clock

to

the

68000

CPU

(pin

15).

Replace oscillator if necessary.

Tt¡en check

pin

17

(HALT)

of the

68000 CPU.

It

should be a

TIL

high. If so,

go

on ro

I

below. If

not,

the CPU

is halted. The

reasons may

be:

(1)

bad

reset

circuit,

(2)

doubte bus error,

3)

bad CPU.

Check

(1)

bV observing signal

on

input

of the tn¡o

inverters

on

the

HALT line. Check

(2)

by

observing

pín

22

of the CPU

(BERR)

as the unÍt

is

powered

on. It

should be

high

always.

If

there

are

logic low

pulses,

some

conponent is malfunctioning

a¡¡d

Glue is

generating

the error.

Verify the clocks to GIue a¡rd Menory Controller

and

replace

these

conponents

to verify then

(if

socketed).

If

still failing,

the CPU

is

unable

to

read ROM or there is a

conponent wlr-leh is not

responding

to a

read or write

by

the CPU,

probably

the

MFP

68901

or DMA Controller. The

MFP

should respond to

an

MFPCS

with DTACK.

The DMA

chip should

respond

to

FCS

by asserting RDY. There is

no

way

to check

(3)

other

than by elinination

of the other

two

possÍbilities,

although a

hot CPU

(too

hot

to touch for nore

than

a

second)

strongly

indicates

a bad

CPIJ.

3.

If

the CPU

is not halted, it

should be reading instructions

f'ron ROM

(cartridge,

if installed)

and data a¡¡d address lines will

be toggling.

(If

not, replace CPU. ) At this

point,

there

is

the

possibility

that both

the video

and

RS232

subsystems are failing.

Verify the output of the

MFP

chip

(pin

8)

while

powering

on the

unit with

the cartridge

installed. If

data

is

being sent. trace it

through the 1488 driver.

Note

that

+

a¡rd

-

12v. is required for

RS232.

If

all

looks

good,

there nay be sonething

wrong with the

connection

to the

terninai.

Verify also the output

of the

Video Shifter.

If

using an RGB

nonitor,

check the outputs to the sunnirrg

resistors

(if

external)

for R,

G, a¡¡d

B. Note

that

if BLANK is not

going

high, no

picture

will be

possible.

If using nonochrone,

check output

pin

30.

AIso

check

the

input

to the

MFP,

pin

29, M0N0M0N. Note

that

if

the CPU

does

not

read a low on this signal on

power-up,

Ít will

cause

RGB

output

on the Video Shifter.

If

the

Video Shifter

is outputti.ng a signal, but

the

picture

is unreadable,

there

is

probably

a

problen

with screen RArY. The

cartridge should be used to diagnose this

problen,

with

the

RS232

terminal

as a

display

device.

Mega

Service Manual

3.3

Testing

Page 32

MEGA/ST

DIAGNOSTIC CARTRIDGE

The

diagnostic cartridge

is used to detect a¡rd isolate

conponent failures

in

the conputers

(52O/LO4O

and Mega). There

are

several

revisions;

this docunent

refers to

revision

4.0. Users of

earlier

versions

should

refer to the appropriate

Troubleshooting

Guide. This section

gives

a brief

guide

to use with a description

of each test, error codes

or

pass/fail

criteria, and

recommendations

on

repaír.

Power-up

The

diagnostic

program perforns

several tests on

power-up.

In

particular,

the

nessage

"Testing

MFP, GIue tining,

Video will

appear,

a¡rd the screen will appear scrambled

for a few

seconds

before the

menu is

printed.

The screen will

turn

red

(dark

background in nonochrone)

if

a¡r emor occurs

in

the

initial

testing, with a

message indicating

the

failure. The lowest

2

Kbytes of RAIü is tested on

power-up;

if

a

locatíon fails,

the

error wiII be

printed

to the

R5232

device.

It is

assumed that

if

RAM is failing,

Lhe

screen nay not be

readable

a¡¡d

program

execution will

fail

because there

is no

stack

or

system variables.

The

progra¡n

will continue to test

RAM and

print

emors, but

no

screen will be displayed

(the

screen

¡nay turn

red).

Repair RAM.

If

the

keyboard fails, it will

be

inactivated. The

user nust

connect

a

terninal to the

R5232

port.

The

diagnostic

progra¡n

looks

for keystrokes fron

the

RS232

device.

If

the display

is

unreadable,

the

RS232

terminal should be

used.

All nessages

are

printed

to the

R5232

port

as

weII

as the

screen.

Test Menu

The normaL

screen will be dark blue

with white letters. The

test title and

revision nunber

are displayed at the

top,

with the

anount of

RAM

and

keyboard

controller

revision below, and a test

menu

below that.

To

select tests, the user types the

keys

corresponding to those tests, and then the

return key. Many

iterations of the test or tests chosen ca¡r be

run

by typing

in

the

nunber

of cycles

just

before typing RETURN. Typing a zeto will

cause the test sequence to

run continuously. To

stop a cycle

before

completion,

hit the

escape

key

(there

nay

be sone delay

in

sone tests before

the

test

stops). As

each cycle conpletes, the

total

numbers of cycles will be

displayed

on the screen.

Mega

Service

Manual

3.4

Testing

Page 33

MAIN

MENU

Mega

and

4u

nnu

ST

Field

Service

Diagnostic

Test

Rev'

4'0

o

1987,

Atari

CorPoration--

Keyboard

revisioi-V----6O

n"

0S

Version

2

USA

NTSO

c

S

D

H

R

K

A

F

G

L

X

0

z

E

B

V

?

RAI{

Test

0

0'S'

ROltls

Keyboard

M

MIDI

Audio

T

Timing

Fioppy

Oisk

P

Printer/JoY

Ports

Graphics

chiP

(Blitter)

ReaI-tine

clock

Expansion

connector

Run

AII

Tests

iun

rnternal

tests

(R,o'c'K'A'T'L'G)

Exanine/ModifY

nenory

Set

RS2l2

rate

iãÀgr"

iia"o

outPut--5o/6o

Hz

Help

Enter

letter(s),

and

REIURN

ons

will

be

highlighted

if

these

e.

These

should

be

Present

in

tion

requires

the

exPansÍon

test

quires disassemblY)

'

If

these

ishted,

the

test

wirl

check

for

hrough

all

the

tests

except

for

seleðtion

sequences

through

RAM'

tests.

Selection

'E'

enables

the

or

hardware

registers'

The

'B'

e

baud

rate

on

the

RS232

Port'

Pressing

the

up

arrovJ

increases

it'

pressing

the

down

arrovr¡

decreases

it.

Pressing

'?'

or

the

HELP

key

brings

up

a

brief

synopsis

of

the

cartridge

functions.

After

a

test

or

series

of

tests

conpletes'

the

pass/fail

status

arrA

er"ãr-".po"t,

if

any,

will

be

displayed'

Press

the

space

bar

to

return

to

the

nenu'

If

nultiple

tests

are

selected'

the

sequence

can

be

halted

before

completion

by

pres"ins-ihã

BéC

tey.

Át

ttte

conpletion

of

the

current

test,

the

sequen"å

"iff

hali,

with

the

options

of

either

continuini

or

returning

to

the

nenu'

In

some

cases

there

will

be

"

"or,"id"iabte

delay

Uãfore

the

current

test

conpletes

and

rhe

keysr"oL"

i"-ããlãðt"0.

iup-lã

i

minutes

with

4

meg

of

RAM'

)

CoIor

Serial

Port

DMA

Port

High

resolution

Mega

Service

Manual

3.5

Testing

Page 34

Sumnary of

Tests

RAM TEST

RAM is tested

in

three stages:

low

2 kbytes,

niddle

(up

to

64t¡, a¡rd

fron

64t

to top.

The test

patterns

used

are: all ls, all

0s, a counting

pattern

(data=low

word of

the address)

'

reverse

counting

pattern (data=conplenent

of address

low

word).

The

counÈing

pattern

is copied

fron the top

and

botton of a

J2

Kbyte

buffer

into

the current

J2

Kbytes

of

video

RAM, then shifts video

RAM

to a

new

area,

verifies

the

pattern,

and

repeats

the test,

until the top of

RAM

is reached.

Finally, addressing at 64t

boundaries

is

checked

by writÍng

unique

pattern

in last 216

bytes

of

each

64t Utoct.

If an error occurs,

the error

code

is displayed, followed by

the address, data

written,

data

read, and the bits which did

not

agree.

E.g.:

"

R2 45603E W:603E

R:613c bad bits:

1,8".

In

units

having nore than one ba¡rk

(i.e.,

1040ST, MEGA4)

the

address as

well as the bit

position

nust be used to find the

correct chip.

The following table