Page 1

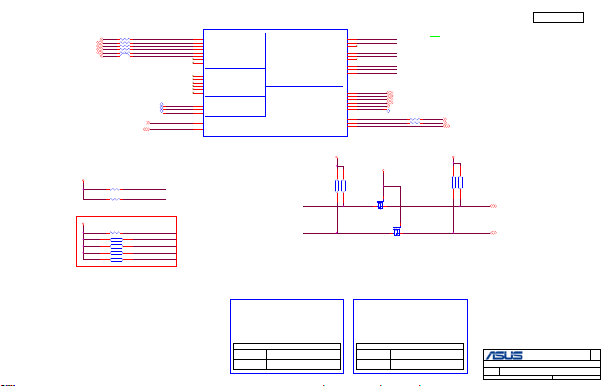

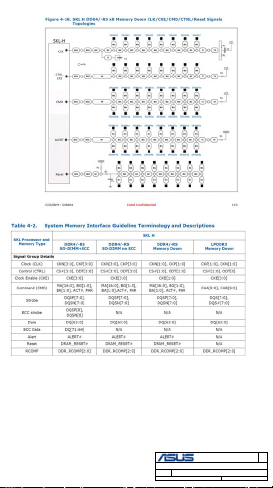

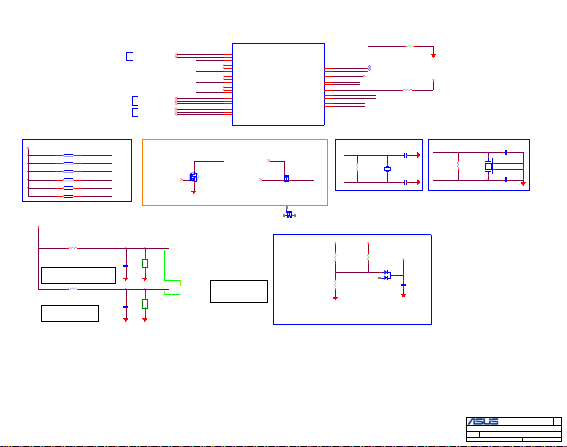

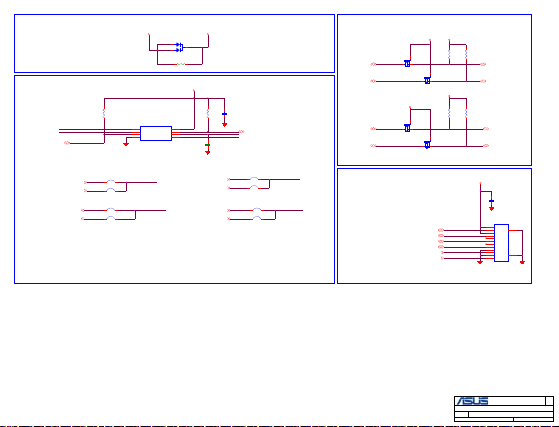

SYSTEM PAGE REF.

PAGE

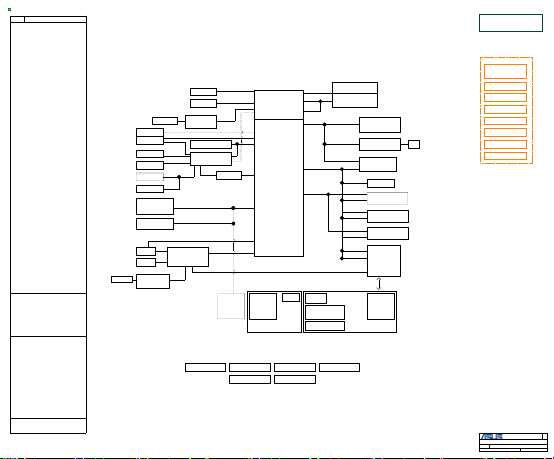

001_Block Diagram

002_System Setting

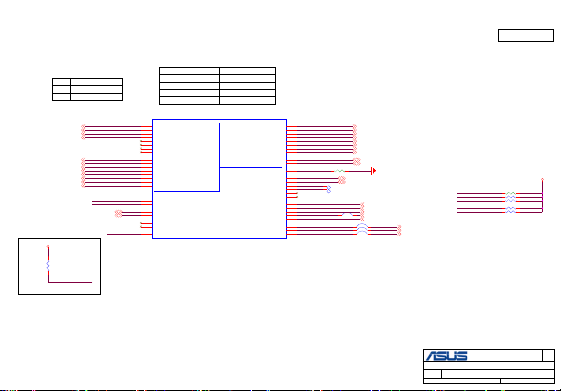

003_CPU_DISPLAY

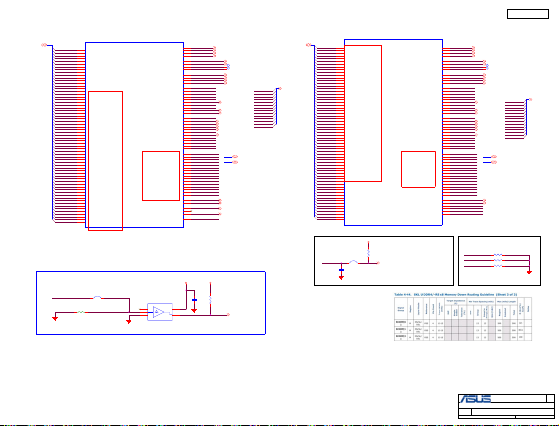

004_CPU_DDR3

005_CPU_LPC,SPI,SMB,CLINK

006_CPU_POEWR

007_

008_CPU_MISC,JTAG

009_CPU_CFG,RSVD

010_CPU_POWER_CAP

011_

012_

013_DDR3L_TERMINATION

014_DDR3L_ON-BOARD_A(1)

015_DDR3L_ON-BOARD_A(2)

016_DDR3L SO-DIMM_B

017_

018_

019_DDR3L_CA_DQ_VOLTAGE

020_CPU_PCH_CSI2,EMMC

021_CPU_PCH_CGPIO, LPIO, MISC

022_CPU_PCH_AUDIO,SDIO,SDXC

023_CPU_PCH_PCIE,USB,SATA

024_CPU_PCH_CLOCK SIGNALS,RTC

025_CPU_PCH_SYS_POWER

026_CPU_PCH_POEWR,GND

027_CPU_PCH_POEWR,GND

028_PCH-SPI ROM,OTH

029_

030_KBC_IT8995E/AX

031_KB, TouchPad & FingerPrint

032_RST_Reset Circuit

033_LAN_RTL8111GUX-CG

034_LAN RJ45

035_

036_AUD_CODEC ALC3288

037_AUD_Smart Amp. 5766L & SKP

038_

039_

040_

041_

042_

043_

044_

045_eDP_LVDS

046_

047_eDP to VGA & CRT D-SUB

048_HDMI-type A

049_

050_FAN_Thermal Sensor

051_SATA_ODD & HDD B to B CONN.

052_USB 3.0 port1/port2

053_MINICARD(WLAN)

054_SSD_key M

055_USB 3.1 MB Type-C

056_

057_DSG_Discharge

058_PRO_Protect

059_Power & LID

060_DC_DC & BAT IN

061_

062_

063_

064_DB_SATA HDD

065_ME_Conn & Skew Hole

066_DB_IO_USB & CR & LED & JACK

067_

068_IO_FPC_CONN.

069_EMI

070_VGA_nVIDIA_N16V/S_PCIE

071_VGA_nVIDIA_N16V/S_FB-IF

072_VGA_nVIDIA_N16V/S_FB-DDR3

073_VGA_nVIDIA_N16V/S_VDD

074_VGA_nVIDIA_N16V/S_DISPLAY

075_VGA_nVIDIA_N16V/S_ROM,XTAL

076_VGA_nVIDIA_N16V/S_GPIO

077_VGA_nVIDIA_N16V/S_POWER

078_VGA_

079_VGA_

080_PW_SKYLAKE-U (1)

081_PW_SKYLAKE-U (2)

082_PW_

083_PW_+1.0VSUS/+1.8VSUS

084_PW_

084_PW_

086_PW_+1.2V/+VTT/+2.5V

087_PW_+3VADSW/+5VSUS

088_PW_LOAD SWITCH

089_PW_CHARGER

090_PW_PROTECTION

091_PW_+NVVDD (1)

092_PW_

093_PW_+FBVDDQ

094_PW_

095_PW_

096_PW_

097_PW_

098_PW_

099_PW_FLOW CHART

100_Power On Timing--AC mode

101_Power On Timing--DC mode

102_History

Content

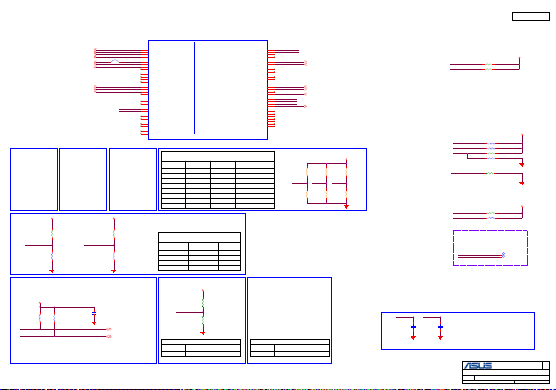

X542UN/URV SCHEMATIC Revision 1.0

(N16:DGPU = Nvidia N16S-GMR, 930MX)

(N17:DGPU = Nvidia N17S-G1, MX150)

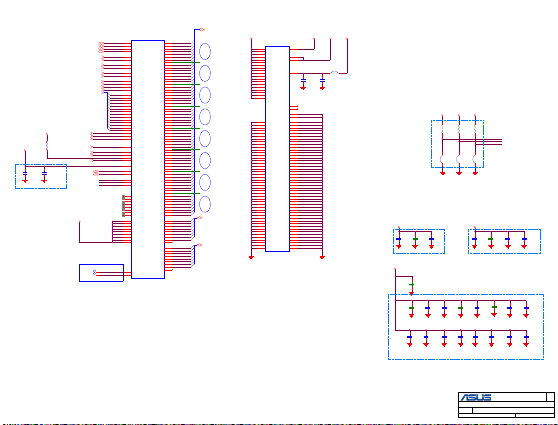

eDP

eDP Panel

Page 45

DDI_2

DDI_2

HDMI type A

DDI_1

Page 48

DDI to VGA

D-SUB

Page 47

RTD2166-VAS-CG

Finger Print

Touchpad

Keyboard

Charger

CPU

Thermal Sensor

DIMM

Thermal Sensor

M.2 SSD

INT. DMIC

Page 45

INT. AMIC

Page 45

SMART AMP

Speaker L/R

Page 37

TI_TAS5766L

Page 47

PS2

Debug Conn.

Page 31

EC

Page 31

SMB0

IT8995E

Page 88

SPI SPI

SMB1

Page 50

Page 14

SATA_2

Gen3

Page 54

SATA_1

ODD

Gen3

Page 51

Audio Codec

ALC3288

Page 36

I2S

Page 37

CPU XDP

KabeLaker-R-U

SML1

DDI_1

2 lans

SPI

I2C1

LPC

Page 28

Page 30

PCH

SPI ROM

Wildcat_Point

W25Q64FVSSIQ

Page 28

SATA

iSST

Azalia

HDA

HP & MIC

SATA_0

Gen3

20 Pin

20 Pin

BtoB Conn.

BtoB Conn.

To HDD DB.

To MB

Page 64

Page 52

Discharge Circuit

Page 57

Page 7

Reset Circuit

Page 32

Non Connected Standby

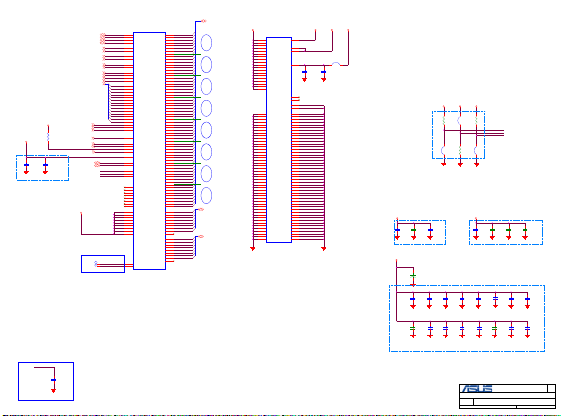

DDR4 so-dimm

DDR4

2100MHz

DDR4 so-dimm

DDR4

CPU

2100MHz

Page 13~15, 19

SMB

Page 3~9

PCIE

PCIE_1~4

USB 2.0

MCP

USB 3.0

Page 20~28

HDD

Audio Jack

SATA_1

CardReader

AU6465RB63-GCF-GR

USB 2.0 Conn.

HDD DB.

DC & BATT. Conn.

PWM Fan

Page 60

Skew Holes

Page 65

Nvidia

930M/1040

N16V-GMR1

Page 70~ 79

PCIE_5

GigaLAN

RJ45

RTL8402

Page 34

Page 33

PCIE_6

WLAN + BT

USB 2.0_8

Page 53

USB 2.0_6

CMOS Camera

Page 45

USB 3.0_1

USB 3.0 Standard Conn.

USB 2.0_1

Port 1

Page 52

USB 3.0_4

USB 3.0 Type-A

USB 2.0_3

Port 2

Page 53

USB 3.0_2

USB 3.0_3

USB 3.1 Type-C

USB 2.0_2

Page 55

USB 2.0_3

30 Pin

FPC Conn.

USB 2.0_4

To IO BD.

Page 68

FPC

30 Pin

FPC Conn.

To MB

USB 2.0_7

Page 66

USB 2.0_4

IO DB.

Page 50

BLOCK DIAGRAM

Power

+VCCGT

+VCCCORE

+VCCSA

+1.0VSUS / +1.8VSUS

+1.35V / +0.675VS

+3VADSW/+5VSUS

Load Switch

Charger

+NVVDD

+FBVDDQ

BOM

Project Name

Title :

Block Diagram

Size

Dept.:

NB2_RD1_EE1

Custom

Date: Sheet

Tuesday, June 20, 2017

Page 80 & 81

Page 83

Page 86

Page 87

Page 88

Page 89

Page 91

Page 93

Rev

R1.0X542UN/URV

Engineer:

Andy_Tang

102

of

1

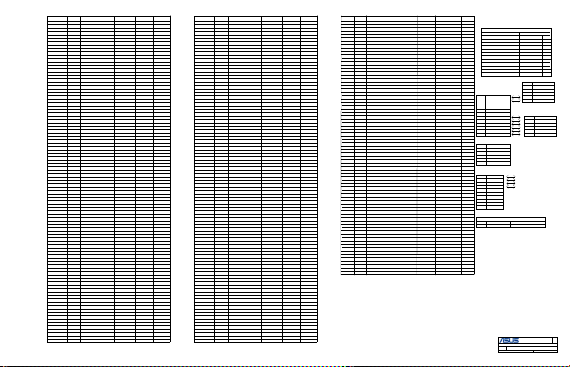

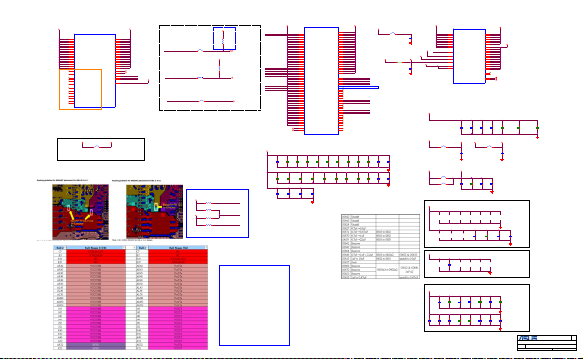

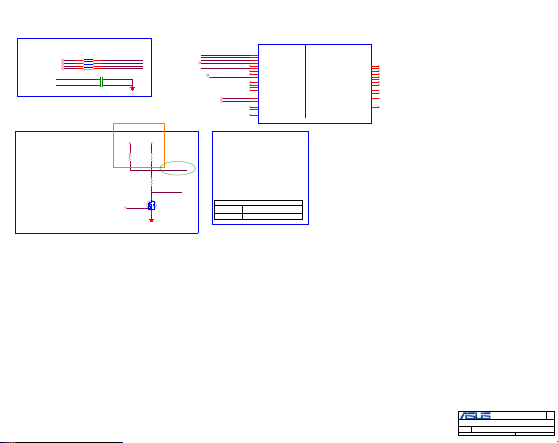

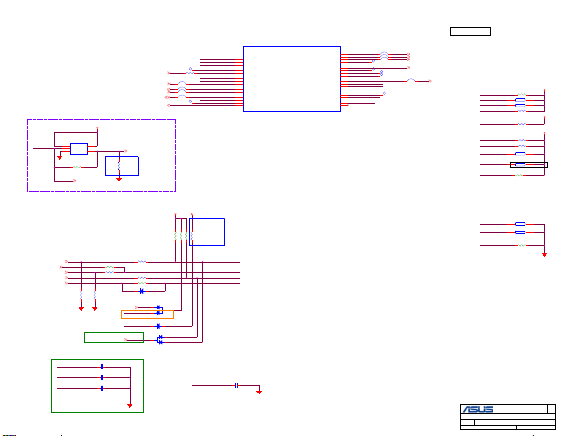

Page 2

PCH_CPT

GPIO

綠色:

新增function

紅色:

待再確認

藍色:

額外標示

灰色:

預留不上件

For FingerPrint

For FingerPrint

For FingerPrint

For FingerPrint

For FingerPrint

For FingerPrint

Int.& Ext

Power on

PCH_IBEX GPIO

Signal NameUse As

RC_IN#

Native1

GPP_A0

LPC_AD0

Native1

GPP_A1

LPC_AD1

Native1

GPP_A2

LPC_AD2

Native1

GPP_A3

LPC_AD3

Native1

GPP_A4

LPC_FRAME#

Native1

GPP_A5

INT_SERIRQ

Native1

GPP_A6

NA

GPO

GPP_A7

PM_CLKRUN#

Native

GPP_A8

CLK_KBCPCI_PCH

Native1

GPP_A9

CLK_DEBUG

Native

GPP_A10

NA

GPP_A11

GPO

NA

GPP_A12

GPO

SUSWARN#

Native1

GPP_A13

PCH_SUS_STAT#

Native1

GPP_A14

PCH_SUSACK#

Native1

GPP_A15

NA

GPP_A16

GPO

NA

GPP_A17

GPO

NA

GPP_A18

GPO

NA

GPP_A19

GPO

NA

GPP_A20

GPO

NA

GPP_A21

GPO

NA

GPP_A22

GPO

NA

GPP_A23

GPO

VCCPRIM_VID0

GPP_B0

Native

VCCPRIM_VID1

GPP_B1

Native

NA

GPP_B2

GPO

NA

GPP_B3

GPO

NA

GPP_B4

GPO

CK_REQ_P0#

GPP_B5

Native

CK_REQ_P1#

GPP_B6

Native

CK_REQ_P2#

GPP_B7

Native

CK_REQ_P3#

GPP_B8

Native

CK_REQ_P4#

GPP_B9

Native

CK_REQ_P5#

GPP_B10

Native

MPHY_PWREN

GPP_B11

Native

PCH_SLP_S0#

GPP_B12

Native

PLT_RST#

GPP_B13

Native

NA

GPP_B14

GPO

FP_GSPI0_CS#

GPP_B15

GPO

FP_GSPI0_CLK

GPP_B16

GPO

FP_GSPI0_MISO

GPP_B17

GPO

FP_GSPI0_MOSI

GPP_B18

GPI

BT_ON/OFF#

GPP_B19

GPO

GPU_EVENT#

GPP_B20

GPO

DGPU_FB_CLAMP_GPIO

GPP_B21

GPI

NA

GPP_B22

GPO

SML1ALERT#

Native

GPP_B23

SMB_CK

GPP_C0

Native

SMB_DATA

GPP_C1

Native

NA

GPP_C2

GPO

SML0_CK

GPP_C3

Native

SML0_DATA

GPP_C4

Native

NA

GPO

GPP_C5

SML1_CK

GPP_C6

Native

SML1_DATA

GPP_C7

Native

NA

GPP_C8

GPO

NA

GPP_C9

GPO

NA

GPP_C10

GPO

NA

GPP_C11

GPO

DIMM_SEL0

GPP_C12

GPI

DIMM_SEL1

GPP_C13

GPI

DIMM_SEL2

GPP_C14

GPI

NA

GPP_C15

GPO

NA

GPP_C16

GPO

NA

GPP_C17

GPO

I2C1_SDA_TCH_PAD

GPP_C18

Native

I2C1_SCL_TCH_PAD

GPP_C19

Native

DGPU_PWROK

GPP_C20

GPI

GPU_RST#

GPP_C21

GPO

DGPU_PWR_EN#

GPP_C22

GPO

N/A

GPP_C23

GPO

N/A

GPP_D0

GPO

N/A

GPP_D1

GPO

N/A

GPP_D2

GPO

N/A

GPP_D3

GPO

N/A

GPP_D4

GPO

SATA_ODD_PWRGT

GPP_D5

GPO

SATA_ODD_DA#

GPP_D6

GPI

FP_RST#

GPP_D7

GPI

FP_INT#

GPP_D8

GPO

PCB_ID0

GPI

GPP_D9

PCB_ID1

GPI

GPP_D10

N/A

GPP_D11

GPO

N/A

GPP_D12

GPO

TOUCHPAD_INTR#

GPP_D13

GPI

WLAN_LED_R

GPP_D14

GPO

N/A

GPP_D15

GPO

N/A

GPP_D16

GPO

N/A

GPP_D17

GPO

N/A

GPP_D18

GPO

N/A

GPP_D19

GPO

N/A

GPP_D20

GPO

N/A

GPP_D21

GPO

N/A

GPP_D22

GPO

Power

Pull up / down

Default States

NA

NA

DGPU

NA

GLAN

WLAN

NA

DIMM & TP

DIMM & TP

PCH_IBEX GPIO

EXT PU 10K

+3VS

GPP_D23

PU at EC

GPP_E0

GPP_E1

For SSD +3VS

GPP_E2

GPP_E3

EXT PU 10K

EXT PU 8.2K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 10KNANA

EXT PU 10K

EXT PU 10K

EXT PU 20K

Check PU can be removed?

EXT PU 49.9K

EXT PU 49.9K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PD 10K

EXT PU 10K +3VSG

EXT PU 150K

EXT PU 2.2K

EXT PU 2.2K

EXT PU 2.2K

EXT PU 2.2K

EXT PU 2.2K

EXT PU 2.2K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 4.7K

EXT PU 4.7K

EXT PU 10K

EXT PD 10K

EXT PU 10K +3VS

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PD 10K

EXT PD 10K

EXT PU 10K +3VS

EXT PU 10K

EXT PD 10K

EXT PU 10K

EXT PU 10K

EXT PD 10K

EXT PU 10K

GPP_E4

+3VS

GPP_E5

GPP_E6

+3VS

GPP_E7

GPP_E8

GPP_E9

GPP_E10

GPP_E11

GPP_E12

+3VSUS

GPP_E13

GPP_E14

GPP_E15

GPP_E16

GPP_E17

GPP_E18

GPP_E19

GPP_E20

GPP_E21

GPP_E22

GPP_E23

+3VS

GPP_F0

+3VS

GPP_F1

GPP_F2

GPP_F3

GPP_F4

+3VS

GPP_F5

+3VS

GPP_F6

+3VS

GPP_F7

+3VS

GPP_F8

+3VS

GPP_F9

+3VS

GPP_F10

+3VSUS

GPP_F11

GPP_F12

GPP_F13

GPP_F14

+3VS

GPP_F15

+3VS

GPP_F16

+3VS

GPP_F17

+3VS

GPP_F18

GPP_F19

+3VSG

GPP_F20

PD at DGPU

GPP_F21

GPP_F22

+3VSUS

GPP_F23

+3VSUS

GPP_G0

+3VSUS

GPP_G1

GPP_G2

+3VSUS

GPP_G3

+3VSUS

GPP_G4

GPP_G5

+3VSUS

GPP_G6

+3VSUS

GPP_G7

GPD0

GPD1

GPD2

+3VSUS

GPD3

+3VSUS

GPD4

+3VSUS

GPD5

GPD6

GPD7

GPD8

GPD9

+3VS

GPD10

+3VS

+3VS

GPD11

PU at DGPU

+3VSUS

+3VS

PU at ODD

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

at LED

+3VSUS

Use As Signal Name

N/A

GPO

N/A

GPO

N/A

GPO

MSATA_MPCIE_DET#

GPI

N/A

GPO

SATA0_DEVSLP

GPO

SATA1_PHYSLP

GPO

SATA2_DEVSLP

GPO

N/A

GPO

SATA_LED#

NATIVE

USB_OC_1_2# EXT PU 10K

NATIVE

USB_OC_3_4#

GPI

USB_OC_5_6#

GPI

USB_OC_7_8#

GPI

DDPB_HPD_PCH

NATIVE

HDMI_HP

NATIVE

EXT_SMI# EXT PU 10K

GPO

EXT_SCI#

GPI

EDP_HPD_CON

NATIVE

DDPB_SCL_PCH

NATIVE

DDPB_SDA_PCH

NATIVE

DDPC_SCL_PCH

NATIVE

DDPC_SDA_PCH

NATIVE

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

N/A

GPO

SDIO_CMD

GPO

SDIO_D0

GPO

SDIO_D1

GPO

SDIO_D2

GPO

SDIO_D3

GPO

SDIO_CD#

GPO

SDIO_CLK

GPO

SDIO_WP

GPO

PM_BATLOW_R#

Native

ME_AC_PRESENT_PCH

Native

PCH_GPD2#

GPI

PM_PWRBTN#

Native

PM_SUSB#

Native

PM_SUSC#

Native

PM_SLP_A_R#

Native

WLAN_ON#

GPO

SUS_CK

Native

PCH_SLP_WLAN#

Native

SLP_S5#

Native

LAN_PWREN

Native

Power on

Int.& Ext

Default States

Pull up / down

EXT PU 10K

REF: UX390 no PU

EXT PU 10K

HDD

EXT PU 10K

NA +3VS

EXT PU 10K

SSD

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PU 10K

EXT PD 100K PD at DDI to VGA

EXT PU 1M

EXT PU 10K

EXT PD 100K

EXT PU 10K +3VS

EXT PU 10K

EXT PU 10K

EXT PU 2.2K

EXT PU 2.2K

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

EXT PU 8.2K

EXT PU 100K

EXT PU 10K

EXT PU 10K

EXT PD 100K

EXT PD 100K PD at EC

N/A

EXT PU 10K

EXT PD 1K

N/A

N/A

N/A

Signal Name

Pin Name

Config

Power

EC

PWR_LED

IT8995

GPA0

O

CHG_LED#

GPIO

GPA1

OD

GPA2

OD

FAN_PWM_GPU(N/A)

GPA3

Alt

CLICK_WAKE#/WLAN_WAKE#_EC(N/A)

GPA4

O

FAN0_PWM

GPA5

Alt

+3VS

+3VS

+3VS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VA_DSW

+3VA_DSW

+3VA_DSW

+3VSUS

+3VA_DSW

KB_LED_PWM

GPA6

Alt

OS_LED# (N/A)

GPA7

O

GPB0

Alt

LID_SW#

GPB1

I

(N/A)

GPB2

OD

PWR_SW#

GPB3

I

PS_ON

GPB4

O

A20GATE (N/A)

GPB5

O

GPB6

OD

(N/A)

PU at HDMI conn

GPC0

O

GPC1

Alt

GPC2

Alt

PD at LVDS conn

GPC3

O

GPC4

I

GPC5

I

BAT1_IN_OC#

GPC6

Alt

PU at HDMI conn

(N/A)

PU at HDMI conn

I

GPC7

PCH_SLP_S0#

I

GPD0

ME_AC_PRESENT

O

GPD1

BUF_PLT_RST#

Alt

GPD2

EXT_SCI#

OD

GPD3

EXT_SMI#

OD

GPD4

OP_SD#

O

GPD5

FAN0_TACH

Alt

GPD6

(N/A)

Alt

GPD7

GPE0

O

SUSC_EC#

GPE1

O

1.2V_ON

GPE2

O

(N/A)

GPE3

O

(N/A)

GPE4

O

GPE5

I

CAP_LED#

GPE6

OD

GPE7

OD

O

GPF0

O

GPF1

Alt

GPF2

Alt

GPF3

Alt

GPF4

Alt

GPF5

PECI_EC

Alt

GPF6

PCH_SPI_OV

O

GPF7

DGPU_LIMIT

GPG0

O

PCH_SUSACK#

GPG1

O

PWRLIMIT_EC#

GPG2

I

(N/A)

GPG6

O

PM_CLKRUN#

Alt

GPH0

SMB3_CLK

N/A

Alt

GPH1

SMB3_DAT

N/A

Alt

GPH2

O

GPH3

DPWROK_EC

O

GPH4

PM_PWROK

O

GPH5

PM_SYSPWROK

O

GPH6

LCD_BACKOFF#

O

GPH7

PM_SLP_SUS#

GPI0

I

3VSUS_PWRGD

GPI1

I

ALL_SYSTEM_PWRGD

PD at EC

GPI2

I

IMVP8_PWRGD

GPI3

I

3VA_DSW_PWRGD

GPI4

I

ME_SusPwrDnAck_EC

GPI5

I

A/D_MAX_POWER

GPI6

Alt

MB_MAX_POWER

GPI7

Alt

EC_WAKE_SCI

N/A

I

GPJ0

O

GPJ1

REST_AMP#

Alt

For Smart Amp.

GPJ2

PCH_SUS_STAT#

N/A

O

GPJ3

AMP_SLEEP#

Alt

For Smart Amp.

GPJ4

EC_GPJ5

N/A

I

GPJ5

N/A

I

GPJ6

N/A

OGPJ7

*1: EC config GPI; Function output

Power

Ext Pull up / down

Default status

Design IP Source:

LOW

EXT 10K PU

+3VA_EC

HIGH

SM_BUS ADDRESS :

EXT 10K PUCHG_FULL_LED#

+3VA_EC

EXT 10K PU +3VA_EC

EXT 10K PU

EXT 4.7K PUSMB1_DAT

EXT 10K PUPM_PWRBTN#

EXT 10K PDDGPU_FB_CLAMP_GPIO

EXT 100K PDPM_SUSC#

EXT 10K PD

EXT 100K PD

EXT 10K PU +3VS

EXT 10K PU +3VS

EXT 10K PU

EXT 10K PU

EXT 10K PDSUSB_EC#

EXT 10K PD

EXT 100K PDPM_SUSB#

EXT 1K PUTHRO_CPU#

EXT 10K PU/ 1M PD5VSUS_ON

EXT 100K PU

EXT 4.7K PU +3VSTP_CLK

EXT 8.2K PU

EXT 10K PDPM_RSMRST#

EXT 10K PD

EXT 100K PD

EXT 10K PD

EXT 10K PU/ 100K PD +3VA_EC

EXT 10K PU +3VS

EXT 10K PU +3VS

EXT 100K PU +3VA_DSW

EXT 0 PD

EXT 100K PU/93.1K PD +3VACC

+3VA_ECEXT 10K PU

+3VAEXT 10K PUAC_IN_OC#

+3VAEXT 10K PU

+3VA

+3VSEXT 10K PU

+3VSEXT 10K PURC_IN#

+3VA_ECEXT 4.7K PUSMB1_CLK

+3VA_EC

+3VSUS

PCI Express

PCIE 1

PCIE 2

+3VA_DSWEXT 100K PU

PCIE 3

PCIE 4

PCIE 5

PCIE 6

+3VS

+3VS

PCIE 9

PCIE 10

PCIE 11

PCIE 12

PCI CLK

+VCCSTG

+3VA_EC

+3VA_ECVSUS_ON

+3VA_ECEXT 4.7K PUSMB0_CLK

+3VA_ECEXT 4.7K PUSMB0_DATA

+3VSEXT 4.7K PUTP_DAT

USB Port

USB 1

USB 2

USB 3

USB 4

+3VA_ECEXT 100K PU

USB 5

USB 6

+3VS

USB 7

USB 8

USB 9

USB 10

Device Identification

CPU Thermal Senser

1st

2nd

+3VA_ECEXT 100K PU3VADSW_ON

+3VS

PCH Master

SM-Bus Device

EC Master (SMB1)

SM-Bus Device

CPU Thermal Sensor 90h

DGPU

GLAN

WLAN

SSD PCIE3

SSD PCIE2

SSD PCIE1

SSD PCIE0 SSD SATA

DGPUx4

CLK0

CLK1

SSD

CLK2

CLK3

LAN

CLK4

WLAN

CLK5

USB 2.0 Port

USB 2.0 Port

USB 2.0 Port

USB 2.0 Port

CAMERA

CARD READER

WLAN/BT

06G023123010

NCT7717U

BOM

Title :

System Setting

Size

Dept.:

NB2_RD1_EE1

D

Date: Sheet of

Tuesday, June 20, 2017

SM-Bus Address

SM-Bus Address

9AhDIMM TEMP.

USB3 Port

USB3_1

USB 3.0 Port 0

USB3_2

USB 3.1 Type C

USB3_3

USB 3.1 Type C

USB3_4

USB 3.0 Port 1

SATA Port

SATA 0

HDD

SATA 1

ODD / 2nd HDD

SATA 2

USB 3.0 Port 0

USB 3.1 Type C

USB 3.0 Port 1

USB 2.0

Project Name

Rev

R1.0X542UN/URV

Engineer:

Andy_Tang

102

2

HIGH

LOW

LOW

LOW

HIGH

HIGH

HIGH

HIGH

LOW

HIGH

HIGH

LOW

HIGH

LOW

LOW

LOW

HIGH

HIGH

HIGH

HIGH

LOW

HIGH

LOW

HIGH

HIGH

HIGH

HIGH

LOW

LOW

HIGH

HIGH

LOW

HIGH

HIGH

LOW

HIGH

HIGH

LOW

LOW

HIGH

HIGH

HIGH

HIGH

LOW

LOW

LOW

HIGH

HIGH

LOW

HIGH

HIGH

HIGH

HIGH

LOW

LOW

LOW

HIGH

HIGH

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

LOW

HIGH

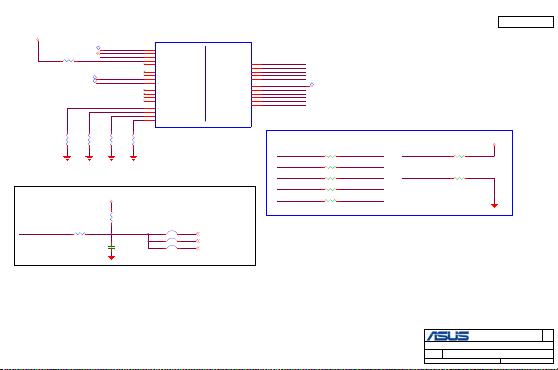

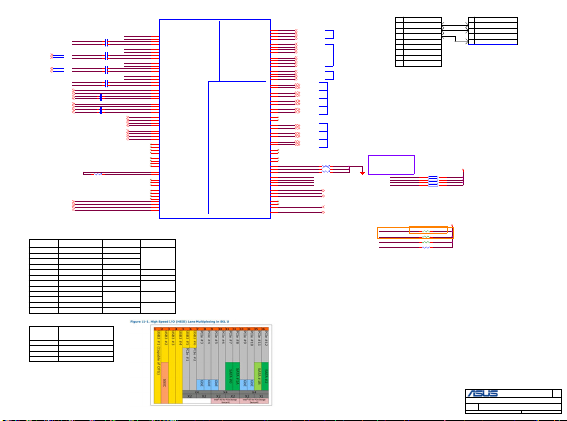

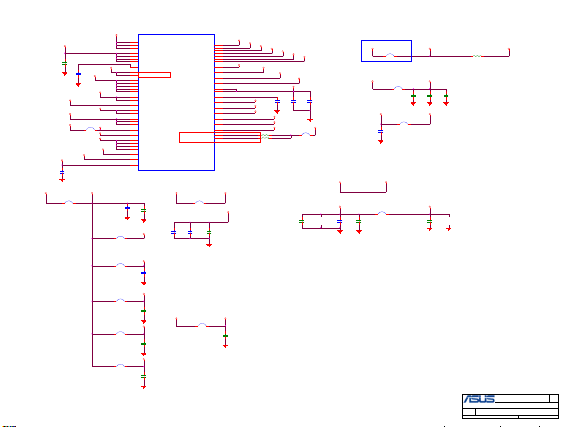

Page 3

Main Board

Display Port

B VGA

CHDMI

VGA_LANE0_DN47

VGA_LANE0_DP47

VGA_LANE1_DN47

VGA_LANE1_DP47

HDMI_DATA2N_PCH48

HDMI_DATA2P_PCH48

HDMI_DATA1N_PCH48

HDMI_DATA1P_PCH48

HDMI_DATA0N_PCH48

HDMI_DATA0P_PCH48

HDMI_CLKN_PCH48

HDMI_CLKP_PCH48

PDG#543016 DDI1 mapping DDPB

DDI2 mapping DDPC

+VCCIO_CPU

R0301

24.9Ohm

1%

12

EDP_COMP

COMPENSATION PU FOR DP

ASUS P/NIntel Version

U0301A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

SKL-ULT

pre-ES

C47

DDI

DISPLAY SIDEBANDS

EDP_TXN[0]

C46

EDP_TXP[0]

D46

EDP_TXN[1]

C45

EDP_TXP[1]

A45

EDP_TXN[2]

B45

EDP_TXP[2]

A47

EDP_TXN[3]

B47

EDP_TXP[3]

E45

EDP_AUXN

EDP

F45

EDP_AUXP

B52

EDP_DISP_UTIL

G50

DDI1_AUXN

F50

DDI1_AUXP

E48

DDI2_AUXN

F48

DDI2_AUXP

G46

DDI3_AUXN

F46

DDI3_AUXP

L9

GPP_E13/DDPB_HPD0

L7

GPP_E14/DDPC_HPD1

L6

GPP_E15/DDPD_HPD2

N9

GPP_E16/DDPE_HPD3

L10

GPP_E17/EDP_HPD

R12

EDP_BKLTEN

R11

EDP_BKLTCTL

U13

EDP_VDDEN

DP_UTIL

DDI2_AUX_DN

DDI2_AUX_DP

EXT_SMI#

EXT_SCI#_X1

EDP_HPD_CON

LCD_BACKEN_PCH_X1

L_BKLTCTL_PCH_X1

L_VDDEN_PCH_X1

R0302 0Ohm@

1

1

SL0304

12

T0301

T0302

SL0301

SL0302

SL0303

EDP_TXN0 45

EDP_TXP0 45

EDP_TXN1 45

EDP_TXP1 45

EDP_TXN2 45

EDP_TXP2 45

EDP_TXN3 45

EDP_TXP3 45

EDP_AUXN 45

EDP_AUXP 45

DDPB_AUXN_PCH 47

DDPB_AUXP_PCH 47

DDPB_HPD_PCH 47

HDMI_HP 48

EXT_SMI# 30

21

EXT_SCI# 30

0402

EDP_HPD_CON 45

0402

0402

0402

21

21

21

eDP_HDP

L_BKLT_EN 45

EDP_BRIGHTNESS 45

L_VDDEN_PCH 45

BOM

Title :

Size

Dept.:

Custom

Date: Sheet

Tuesday, June 20, 2017

VGA

CPU_DISPLAY

EDP_HPD_CON

EXT_SMI#

EXT_SCI#_X1

DDPB_SCL_PCH

DDPB_SDA_PCH

NB2_RD1_EE1

Project Name

R0303 10KOhm@

12

R0305 10KOhm

12

R0306 10KOhm

12

R0304 10KOhm

12

R0307 10KOhm

12

Engineer:

Joach_Wang

3

+3VS

Rev

R2.0X542UA/UV

102

of

EDPA

DDPB_SCL_PCH

DDPB_SDA_PCH

DDPC_SCL_PCH48

DDPC_SDA_PCH48

EDP_COMP

Page 4

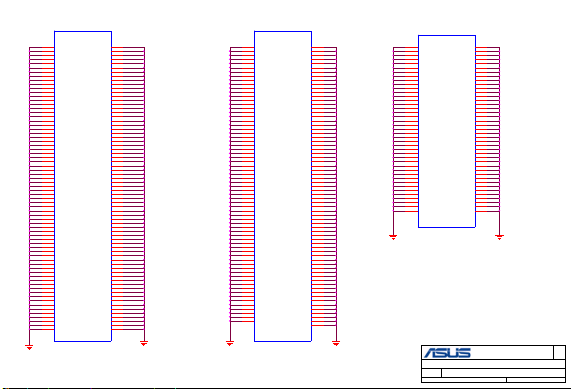

M_A_DQ[63:0]16

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

DDR_VTT_CTRL:

SystemMemoryPowerGateControl:

DisablestheplaormmemoryVTTregulator

inC8anddeeperandS3.

Ref:544924_544924_Skylake_EDS_Vol_1_Rev0.9.pdfP.120

2016/10/11 X542UA_#32, Modify 0401 circuit follow X456U P14. U1405

2017/01/19 X542UA_#11, R0404 modify PU to +3VS & RES 200K

VTT Enable

DDR_VTT_CTRL

R0407 0Ohm@

12

512M x 8bit x 8

For On Board (A)

U0301B

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU

8

6

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DD

_DQ[61]/DDR1_DQ[45]

R0

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKL-ULT

IL/NIL

REV=<REV>

21

SL0409

0402

DDR_PG_CTRL_RR

DDR0_MA[5]

DDR0_MA[9]

DDR0_MA[6]

DDR0_MA[8]

DDR0_MA[7]

DDR0_BA[2]

DDR0_MA[12]

DDR0_MA[11]

DDR0_MA[15]

DDR0_MA[14]

DDR0_MA[13]

DDR0_CAS#

DDR0_WE#

DDR0_RAS#

DDR0_BA[0]

DDR0_MA[2]

DDR0_BA[1]

DDR0_MA[10]

DDR0_MA[1]

DDR0_MA[0]

DDR CH - A

U0401

1

NC

2

A

34

GND

74AUP1G07GW

/DDR0_CAA[0]/DDR0_MA[5]

/DDR0_CAA[1]/DDR0_MA[9]

/DDR0_CAA[2]/DDR0_MA[6]

/DDR0_CAA[3]/DDR0_MA[8]

/DDR0_CAA[4]/DDR0_MA[7]

/DDR0_CAA[5]/DDR0_BG[0]

/DDR0_CAA[6]/DDR0_MA[12]

/DDR0_CAA[7]/DDR0_MA[11]

/DDR0_CAA[8]/DDR0_ACT#

/DDR0_CAA[9]/DDR0_BG[1]

/DDR0_CAB[0]/DDR0_MA[13]

/DDR0_CAB[1]/DDR0_MA[15]

/DDR0_CAB[2]/DDR0_MA[14]

/DDR0_CAB[3]/DDR0_MA[16]

/DDR0_CAB[4]/DDR0_BA[0]

/DDR0_CAB[5]/DDR0_MA[2]

/DDR0_CAB[6]/DDR0_BA[1]

/DDR0_CAB[7]/DDR0_MA[10]

/DDR0_CAB[8]/DDR0_MA[1]

/DDR0_CAB[9]/DDR0_MA[0]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

IL/NIL

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

5

VCC

Y

AU53

AT53

AU55

AT55

BA56

BB56

M_A_CKE0

AW56

M_A_CKE1

AY56

M_A_CKE2

M_A_CKE3

AU45

AU43

AT45

AT43

BA51

BB54

M_A_A5

BA52

M_A_A9

AY52

M_A_A6

AW52

M_A_A8

AY55

M_A_A7

AW54

BA54

M_A_A12

BA55

M_A_A11

AY54

AU46

AU48

M_A_A13

AT46

AU50

AU52

AY51

AT48

M_A_A2

AT50

BB50

M_A_A10

AY50

M_A_A1

BA50

M_A_A0

BB52

M_A_A3

M_A_A4

AM70

AM69

M_A_DQS#0

AT69

M_A_DQS0

AT70

M_A_DQS#1

BA64

M_A_DQS1

AY64

M_A_DQS#2

AY60

M_A_DQS2

BA60

M_A_DQS#3

BA38

M_A_DQS3

AY38

M_A_DQS#4

AY34

M_A_DQS4

BA34

M_A_DQS#5

BA30

M_A_DQS5

AY30

M_A_DQS#6

AY26

M_A_DQS6

BA26

M_A_DQS#7

M_A_DQS7

AW50

AT52

AY67

AY68

BA67

AW67

DDR_VTT_CTRL

DDR0_Vref_DQ - Not in use in DDR4 ,

DDR1_Vref_DQ = DDR4_CA_ch1 ,

DDR_Vref_CA = DD4_CA_ch0

+1.2V

12

C0402

0.1UF/16V

+3VS

12

M_A_CLK_DDR#0 16

M_A_CLK_DDR0 16

M_A_CLK_DDR#1 16

M_A_CLK_DDR1 16

M_A_CKE0 16

M_A_CKE1 16

1

1

M_A_CS#0 16

M_A_CS#1 16

M_A_ODT0 16

M_A_ODT1 16

M_A_BG0 16

M_A_ACT# 16

M_A_BG1 16

M_A_CAS# 16

M_A_WE# 16

M_A_RAS# 16

M_A_BA0 16

M_A_BA1 16

M_A_ALERT# 16

M_A_PAR 16

SA_DIMM_VREFCA 18

SB_DIMM_VREFCA 18

R0404

200KOhm

T0403

T0402

M_A_DQS[7:0] 16

M_A_DQS#[7:0] 16

DDR_PG_CTRL 86

For SO-DIMM (B)

Main Board

U0301C

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

DRAMRST#

IL/NIL

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF

1

7

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DD

_DQ[62]

R1

AN21

DDR1_DQ[63]

SKL-ULT

REV=<REV>

SL0401

21

0402

12

C0401

100PF/50V

/EMI

2017/02/06 X542UA_R1.1 #26, EMI solution

GND

AN45

DDR1_CKN[0]

M_B_CLK_DDR#0 17

AN46

DDR1_CKN[1]

M_B_CLK_DDR#1 17

AP45

DDR1_CKP[0]

M_B_CLK_DDR0 17

AP46

DDR1_CKP[1]

M_B_CLK_DDR1 17

AN56

DDR1_CKE[0]

M_B_CKE0 17

AP55

M_B_CKE0

DDR1_CKE[1]

M_B_CKE1 17

1

AN55

T0401

M_B_CKE1

DDR1_CKE[2]

1

AP53

T0404

M_B_CKE2

DDR1_CKE[3]

M_B_CKE3

BB42

DDR1_CS#[0]

M_B_CS#0 17

AY42

DDR1_CS#[1]

M_B_CS#1 17

BA42

DDR1_ODT[0]

M_B_ODT0 17

AW42

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

AY48

AP50

M_B_A5

BA48

M_B_A9

BB48

M_B_A6

AP48

M_B_A8

AP52

M_B_A7

AN50

AN48

M_B_A12

AN53

M_B_A11

AN52

BA43

AY43

M_B_A13

AY44

AW44

BB44

AY47

BA44

M_B_A2

AW46

AY46

M_B_A10

BA46

M_B_A1

BB46

M_B_A0

BA47

M_B_A3

M_B_A4

AH66

AH65

M_B_DQS#0

AG69

M_B_DQS0

AG70

M_B_DQS#1

AR66

M_B_DQS1

AR65

M_B_DQS#2

AR61

M_B_DQS2

AR60

M_B_DQS#3

AT38

M_B_DQS3

AR38

M_B_DQS#4

AT32

M_B_DQS4

AR32

M_B_DQS#5

AR25

M_B_DQS5

AR27

M_B_DQS#6

AR22

M_B_DQS6

AR21

M_B_DQS#7

M_B_DQS7

AN43

AP43

AT13

AR18

DRAMRST#

AT18

SM_RCOMP_0

AU18

SM_RCOMP_1

SM_RCOMP_2

DDR4 COMPENSATION SIGNALS

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

PDG #543016 P.181

BOM

Title :

Size

C

Date: Sheet

Tuesday, June 20, 2017

M_B_BG0 17

M_B_ACT# 17

M_B_BG1 17

M_B_CAS# 17

M_B_WE# 17

M_B_RAS# 17

M_B_BA0 17

M_B_BA1 17

R0403 121Ohm 1%

R0402 80.6Ohm 1%

R0406 100Ohm 1%

CPU_DDR3

Dept.:

NB2_RD1_EE1

M_B_ODT1 17

M_B_ALERT# 17

M_B_PAR 17

12

12

12

M_B_DQS[7:0] 17

M_B_DQS#[7:0] 17

Project Name

M_B_A[13:0] 17

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

Rev

R2.0X542UA/UV

Engineer:

Joach_Wang

102

of

4

DDR3L/LPDDR3/DDR4DDR3L/LPDDR3/DDR4

DDR1_MA[5]

/DDR1_CAA[0]/DDR1_MA[5]

/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[9]

/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[6]

/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[8]

/DDR1_CAA[4]/DDR1_MA[7]

DDR1_MA[7]

/DDR1_CAA[5]/DDR1_BG[0]

DDR1_BA[2]

/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[12]

/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[11]

/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[15]

/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[14]

DDR1_MA[13]

/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#

/DDR1_CAB[1]/DDR1_MA[15]

/DDR1_CAB[2]/DDR1_MA[14]

DDR1_WE#

DDR1_RAS#

/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]

/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]

/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]

/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]

/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]

/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]

/DDR1_CAB[9]/DDR1_MA[0]

IL/NIL

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR CH - B

+1.2V

12

R0401

470Ohm

1%

DDR4_DRAMRST# 16,17

EMI

M_B_DQ[63:0]17

M_A_A[13:0] 16

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

Page 5

SPI_CLK_SPI_228

SPI_SO_SPI_228

SPI_SI_SPI_228

PCH_SPI_DQ228

PCH_SPI_DQ328

SPI_CS#0_SPI_228

+3VS

+3VSUS

12

R0503 15Ohm

12

R0510 15Ohm

12

R0509 15Ohm

12

R0539 15Ohm

12

R0540 15Ohm

21

SL0501

0402

2017/02/02 X542UA_R1.1 #24, 0ohm modify to SL

2016/10/20 X542UA_#50, Add SPI for FingerPrint

RC_IN#30

INT_SERIRQ30

R0522 8.2KOhm

12

12

R0519 10KOhm

12

R0508 150KOHM

34

RN0501B

2.2KOhm

12

RN0501A

2.2KOhm

34

RN0502B

2.2KOhm

12

RN0502A

2.2KOhm

SMB_CK_S3 16,17,47

TO DIMM / VGA

SMB_DATA_S3 16,17,47

Main Board

U0301E

SPI - FLASH

AV2

SPI0_CLK

AW3

SPI_CLK_SPI_2_X1

SPI0_MISO

AV3

SPI_SO_SPI_2_X1

SPI0_MOSI

AW2

SPI_SI_SPI_2_X1

SPI0_IO2

AU4

PCH_SPI_DQ2_X1

SPI0_IO3

AU3

PCH_SPI_DQ3_X1

SPI0_CS0#

AU2

SPI_CS#0_SPI_2_X1

SPI0_CS1#

AU1

SPI0_CS2#

SPI - TOUCH

M2

GPP_D1/SPI1_CLK

M3

GPP_D2/SPI1_MISO

J4

GPP_D3/SPI1_MOSI

V1

GPP_D21/SPI1_IO2

V2

GPP_D22/SPI1_IO3

M1

GPP_D0/SPI1_CS#

C LINK

1

G3

T0502

CL_CLK

1

G2

CL_CK

T0501

CL_DATA

1

G1

CL_DATA

T0503

CL_RST#

CL_RST#

AW13

GPP_A0/RCIN#

AY11

GPP_A6/SERIRQ

INT_SERIRQ

SKL-ULT

REV=<REV>

PM_CLKRUN#

INT_SERIRQ

SML1ALERT#

SML1_CK

SML1_DATA

SML0_CK

SML0_DATA

SMBUS, SMLINK

GPP_B23/SML1ALERT#/PCHHOT#

LPC

GPP_A5/LFRAME#/ESPI_CS#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

SMB_CK

SMB_DATA

2016/10/27 X542UA_#58, Remove GPP_C2/GPP_C5 & remove R0506/R0507

R7

GPP_C0/SMBCLK

R8

SMB_CK

GPP_C1/SMBDATA

R10

SMB_DATA

GPP_C2/SMBALERT#

R9

GPP_C3/SML0CLK

W2

SML0_CK

GPP_C4/SML0DATA

W1

SML0_DATA

GPP_C5/SML0ALERT#

W3

GPP_C6/SML1CLK

V3

SML1_CK

GPP_C7/SML1DATA

AM7

SML1_DATA

SML1ALERT#

AY13

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

+3VSUS +3VS

RN0503A

2.2KOhm

LPC_AD0 28,30

BA13

LPC_AD1 28,30

BB13

LPC_AD2 28,30

AY12

LPC_AD3 28,30

BA12

LPC_FRAME# 28,30

BA11

T0506

1

2016/10/27 X542UA_R1.0 #53, Remove PCH_SUS_STAT# & reserve test point for measure

PCH_SUS_STAT#

12

AW9

R0512 33Ohm

12

AY9

CLK_KBCPCI_PCH_X1

R0514 22Ohm

AW11

CLK_TPMPCI_PCH_X1

PM_CLKRUN#

+12VS

34

12

RN0503B

2.2KOhm

2

61

Q0501A

EM6K1-G-T2R

5

34

Q0501B

EM6K1-G-T2R

Transport Layer Security (TLS) C onfidentiality

SMB_CK_S3

SMB_DATA_S3

TO DIMM / VGA / TP

CLK_KBCPCI_PCH 30

CLK_DEBUG 28

PM_CLKRUN# 30

RN0504A

2.2KOhm

12

34

RN0504B

2.2KOhm

GPP_C5: weak internal pull down

PU

SPI BUS

LPC is selected for EC (Default)

PD

GPP_C2: weak internal pull down

PU Enable

Disable Intel ME TLS ipher suite

( no confodentiality)(Default)

PD

BOM

Project Name

Title :

CPU_LPC,SPI,SMB,CLINK

Size

Dept.:

NB2_RD1_EE1

Custom

Date: Sheet

Tuesday, June 20, 2017

Rev

R2.0X542UA/UV

Engineer:

Joach_Wang

102

of

5

Page 6

+VCCCORE +VCCCORE

U0301L

CPU POWER 1 OF 4

A30

G32

VCC_A30

VCC_G32

A34

G33

VCC_A34

VCC_G33

A39

G35

VCC_A39

VCC_G35

A44

G37

VCC_A44

VCC_G37

AK33

G38

VCC_AK33

VCC_G38

AK35

G40

VCC_AK35

VCC_G40

AK37

G42

VCC_AK37

VCC_G42

AK38

J30

VCC_AK38

VCC_J30

AK40

J33

VCC_AK40

VCC_J33

AL33

J37

VCC_AL33

VCC_J37

AL37

J40

VCC_AL37

VCC_J40

AL40

K33

VCC_AL40

VCC_K33

AM32

K35

VCC_AM32

VCC_K35

AM33

K37

VCC_AM33

VCC_K37

AM35

K38

VCC_AM35

VCC_K38

AM37

K40

VCC_AM37

VCC_K40

AM38

K42

VCC_AM38

VCC_K42

G30

K43

VCC_G30

VCC_K43

K32

E32

RSVD_K32

VCC_SENSE

E33

VSS_SENSE

AK32

RSVD_AK32

B63

VIDALERT#

AB62

A63

VCCOPC_AB62

VIDSCK

P62

D64

VIDSOUT

VCCOPC_P62

V62

VCCOPC_V62

G2

STG_G20

VCC

H63

VCC_OPC_1P8_H63

G61

VCC_OPC_1P8_G61

REV=<REV>

AC63

VCCOPC_SENSE

AE63

VSSOPC_SENSE

AE62

VCCEOPIO_1

AG62

VCCEOPIO_2

AL63

VCCEOPIO_SENSE

AJ62

VSSEOPIO_SENSE

SKL-ULT

CPU W/OPC

+VCCIO +VCCSTG

21

SL0630

0.04A

0603

Volume Segment

+VCCIO is supplied +1.0VS (shared with +VCCSTG)

+1.0V_VCCST

R1.0-3

R0606

SVID DATA

100Ohm

1%

12

21

SL0609

P_SVID_DATA_50OHM_X2 80

0402

P_SVID_DATA_X3

20151230 LAUOYUT 此3組訊號請將 SVID ALERT 擺中間

+1.0V_VCCST

R0605

SVID ALERT

0

P_SVID_ALERT#_X3

P_SVID_CLK_X3

P_SVID_DATA_X3

P_VCCCORE_VCCSENSE_50OHM 80

P_VCCCORE_VSSSENSE_50OHM 80

+VCCSTG

56Ohm

12

12R0604 220Ohm

P_SVID_ALERT#_X3 U42_CORE_1_U22_GTx

P_SVID_CLK_X3

P_SVID_ALERT#_50OHM_X2 8 0

SVID CLOCK

21

SL0617

P_SVID_CLK_50OHM_X2 80

0402

2016/10/07 X542UA_R1.0 #27, Add R0601/R0602/R0607/R0608 for U42 & U22 Option

2016/10/17 X542UA_R1.0 #47, Modify R0602/R0607/R0608 from 0603 to 0805 for intel suggestion

2017/03/16 X542UA_R2.0 #01, JP0601/02/03/04 change to RSE R0607/08/09/10 (special RES)

KBL-R U42 & U22 co-lay, 在CPU 下方

+VCCGT

1 pin

/U22

12R0607 0Ohm

RES 0 OHM 1/2W(0805) JUMPER

U42_RSVD_U22_GT

10114-00193000

/U22

12

R0608 0Ohm

RES 0 OHM 1/2W(0805) JUMPER

10114-00193000

10 pin

+VCCCORE

U42_CORE_2_U22_GT

/U42

12

R0609 0Ohm

RES 0 OHM 1/2W(0805) JUMPER

10114-00193000

12 pin

/U42

12

R0610 0Ohm

RES 0 OHM 1/2W(0805) JUMPER

U42_CORE_1_U22_GTx

10114-00193000

5A

5A

JP鋼板測試, 共20顆 PR remove

+VCCGT +VCCGT +1.2V

U0301M

CPU POWER 2 OF 4

N70

VCCGT56

A48

N71

VCCGT1

VCCGT57

A53

U42_CORE_2_U22_GT

U42_CORE_2_U22_GT

U42_CORE_2_U22_GT

U42_CORE_2_U22_GT

U42_CORE_2_U22_GT

U42_CORE_2_U22_GT

U42_CORE_2_U22_GT

U42_CORE_2_U22_GT

U42_CORE_2_U22_GT

U42_CORE_2_U22_GT

U42_RSVD_U22_GT

P_VCCGT_VCCSENSE_50OHM80

P_VCCGT_VSSSENSE_50OHM80

2016/12/05 X542UA_R1.0 #96,VCORE sense & VCCGT sense modify

CPU - VCCGT DECAPS- Underneath the package

+VCCGT

31A 2+2

12

12

12

R63

VCCGT2

VCCGT58

A58

R64

VCCGT3

VCCGT59

A62

R65

VCCGT4

VCCGT60

A66

R66

VCCGT5

VCCGT61

AA63

R67

VCCGT6

VCCGT62

AA64

R68

VCCGT7

VCCGT63

AA66

R69

VCCGT8

VCCGT64

AA67

R70

VCCGT9

VCCGT65

AA69

R71

VCCGT10

VCCGT66

AA70

T62

VCCGT11

VCCGT67

AA71

U65

VCCGT12

VCCGT68

AC64

U68

VCCGT13

VCCGT69

AC65

U71

VCCGT14

VCCGT70

AC66

W63

VCCGT15

VCCGT71

AC67

W64

VCCGT16

VCCGT72

AC68

W65

VCCGT17

VCCGT73

AC69

W66

VCCGT18

VCCGT74

AC70

W67

VCCGT19

VCCGT75

AC71

W68

VCCGT20

VCCGT76

J43

W69

VCCGT21

VCCGT77

J45

W70

VCCGT22

VCCGT78

J46

W71

VCCGT23

VCCGT79

J48

Y62

VCCGT24

VCCGT80

J50

VCCGT25

J52

VCCGT26

J53

AK42

VCCGT27

VCCGTX_AK42

J55

AK43

VCCGT28

VCCGTX_AK43

J56

AK45

U42_CORE_1_U22_GTx

VCCGT29

VCCGTX_AK45

J58

AK46

U42_CORE_1_U22_GTx

VCCGT30

VCCGTX_AK46

REV=<REV>

J60

AK48

U42_CORE_1_U22_GTx

VCCGT31

VCCGTX_AK48

K48

AK50

U42_CORE_1_U22_GTx

VCCGT32

VCCGTX_AK50

K50

AK52

U42_CORE_1_U22_GTx

U42_RSVD_U22_GTx, U42 & U22 無使用

VCCGT33

VCCGTX_AK52

K52

AK53

VCCGT34

VCCGTX_AK53

K53

AK55

VCCGT35

VCCGTX_AK55

K55

AK56

VCCGT36

VCCGTX_AK56

K56

AK58

VCCGT37

VCCGTX_AK58

K58

AK60

VCCGT38

VCCGTX_AK60

K60

AK70

VCCGT39

VCCGTX_AK70

L62

AL43

VCCGT40

VCCGTX_AL43

L63

AL46

U42_CORE_1_U22_GTx

VCCGT41

VCCGTX_AL46

L64

AL50

U42_CORE_1_U22_GTx

VCCGT42

VCCGTX_AL50

L65

AL53

U42_CORE_1_U22_GTx

VCCGT43

VCCGTX_AL53

L66

AL56

VCCGT44

VCCGTX_AL56

L67

AL60

VCCGT45

VCCGTX_AL60

L68

AM48

VCCGT46

VCCGTX_AM48

AM50

L69

U42_CORE_1_U22_GTx

V

VCCGT47

CCGTX_AM50

L70

AM52

U42_CORE_1_U22_GTx

VCCGT48

VCCGTX_AM52

L71

AM53

U42_CORE_1_U22_GTx

VCCGT49

VCCGTX_AM53

M62

AM56

VCCGT50

VCCGTX_AM56

N63

AM58

VCCGT51

VCCGTX_AM58

N6

4

AU58

VCCGT52

VCCGTX_AU58

N66

AU63

VCCGT53

VCCGTX_AU63

N67

BB57

VCCGT54

VCCGTX_BB57

N69

BB66

VCCGT55

VCCGTX_BB66

J70

AK62

VCCGT_SENSE

VCCGTX_SENSE

AL61

J69

VSSGTX_SENSE

VSSGT_SENSE

SKL-ULT

12

12

12

12

C0601

10UF/6.3V

12

C0628

1UF/6.3V

@

12

C0640

1UF/6.3V

12

12

12

12

C0608

C0610

C0611

C0604

C0620

C0609

C0607

10UF/6.3V

10UF/6.3V

10UF/6.3V

10UF/6.3V

10UF/6.3V

10UF/6.3V

10UF/6.3V

@

@

@

C0629

1UF/6.3V

@

C0613

1UF/6.3V

@

@

@

@

12

12

12

12

12

12

C0630

C0632

C0652

C0631

C0643

1UF/6.3V

1UF/6.3V

1UF/6.3V

1UF/6.3V

1UF/6.3V

@

@

@

@

@

12

12

C0656

C0667

1UF/6.3V

1UF/6.3V

2017/01/23 X542UA_R1.1 #19, VccSA Caps modify in list

21

+VDDQ_CPU_CLK

12R0633 0Ohm

@

12

C0615

10UF/6.3V

+1.0V_VCCST

+VCCSTG

+VCCPLL_OC

+1.0V_VCCPLL

12

C0663

1UF/6.3V

+VCCSA

+VCCSA

Simulation team suggestio n

For X542U

+VCCSA

U0301N

CPU POWER 3 OF 4

AU23

VDDQ_AU23

AU28

VDDQ_AU28

AU35

VDDQ_AU35

AU42

VDDQ_AU42

BB23

VDDQ_BB23

BB32

VDDQ_BB32

BB41

VDDQ_BB41

BB47

VDDQ_BB47

BB51

VDDQ_BB51

AM40

VDDQC

+VDDQ_CPU_CLK

A18

VCCST

A22

VCCSTG_A22

AL23

VCCPLL_OC

K20

VCCPLL_K20

K21

VCCPLL_K21

SKL-ULT

REV=<REV>

+1.2V

CPU - VDDQ DECAPS- Place close to the package

2A

12

C0662

10UF/6.3V

+VCCST

+1.0V_VCCST

21

SL0634

120mA 120mA

0603

12

C0616

1UF/6.3V

+VCCIO_CPU+VCCIO

CPU - VCCIO DECAPS- Place close to the package

21

SL0601

3.1A

0805

12

C0619

21SL0603

0805

1UF/6.3V

CPU - VCCSA DECAPS- Underneath the package

5.1A

CPU - VCCSA DECAPS- Place close to the package

12

C0639

22UF/6.3V

nbs_c0805_h57_000s

5.1A

@

12

12

C0627

C0624

C0612

4.7UF/6.3V

1UF/6.3V

10UF/6.3V

12

nbs_c0603_h37_000s

nbs_c0603_h37_000s

@

12

12

12

C0633

C0641

C0661

C0625

1UF/6.3V

1UF/6.3V

4.7UF/6.3V

2.2UF/10V

12

nbs_c0603_h37_000s

AK28

VCCIO1

AK30

VCCIO2

AL30

VCCIO3

AL42

VCCIO4

AM28

VCCIO5

AM30

VCCIO6

AM42

+VCCSA

VCCIO7

AK23

VCCSA1

AK25

VCCSA2

G23

VCCSA3

G25

VCCSA4

G27

VCCSA5

G28

VCCSA6

J22

VCCSA7

J23

VCCSA8

J27

VCCSA9

K23

VCCSA10

K25

VCCSA11

K27

VCCSA12

K28

VCCSA13

K30

VCCSA14

AM23

VCCIO_SENSE

AM22

VSSIO_SENSE

H21

VSSSA_SENSE

P_VCCSA_VSSSENSE_50O HM 80

H20

VCCSA_SENSE

P_VCCSA_VCCSENSE_50O HM 80

12

12

12

12

12

C0618

10UF/6.3V

12

C0605

1UF/6.3V

@

12

C0635

10UF/6.3V

nbs_c0603_h37_000s

C0634

4.7UF/6.3V

12

nbs_c0603_h37_000s

@

C0665

4.7UF/6.3V

12

nbs_c0603_h37_000s

12

@

@

@

C0614

C0606

C0658

C0603

C0648

22UF/6.3V

22UF/6.3V

22UF/6.3V

10UF/6.3V

10UF/6.3V

nbs_c0603_h39_000s

nbs_c0603_h39_000s

nbs_c0603_h39_000s

+1.0V_VCCPLL+VCCST

21

SL0602

0603

12

C0602

1UF/6.3V

12

12

C0621

C0622

1UF/6.3V

1UF/6.3V

12

12

12

C0655

C0637

C0657

0.47UF/6.3V

1UF/6.3V

1UF/6.3V

@

@

@

C0642

C0645

C0644

4.7UF/6.3V

4.7UF/6.3V

4.7UF/6.3V

12

12

12

nbs_c0603_h37_000s

nbs_c0603_h37_000s

nbs_c0603_h37_000s

12

12

C0670

C0671

C0669

1UF/6.3V

0.47UF/6.3V

4.7UF/6.3V

12

nbs_c0603_h37_000s

BOM

Project Name

Rev

R2.0X542UA/UV

Title :

CPU_POEWR

Size

Dept.:

Engineer:

NB2_RD1_EE1

Joach_Wang

D

Date: Sheet of

102

6

Tuesday, June 20, 2017

+1.2V

SL0610

0603

+1.2V

nbs_r0603_h24_000s

12

12

12

C0626

C0659

C0617

C0660

10UF/6.3V

10UF/6.3V

10UF/6.3V

10UF/6.3V

@

@

12

12

12

C0638

C0636

C0666

C0654

1UF/6.3V

1UF/6.3V

1UF/6.3V

@

1UF/6.3V

@

+VCCIO_CPU

Page 7

+1.0V_VCCST

12

R0802 1KOhm1%

CPU SIDEBAND SIGNALS

H_PROCHOT_D#

PECI_EC30

T0803

T0804

R0813

49.9Ohm

1%

12

R0808

12

499OHM

1

T0801

1

1

R0812

49.9Ohm

1%

12

H_CATERR#

PECI_EC

H_PROCHOT_D#

THERMTRIP#

XDP_BPM2

XDP_BPM3

R0811

49.9Ohm

1%

12

+VCCSTG

12

R0809

1KOhm

H_PROCHOT_D#_R

12

C0801

43PF/50V

D63

A54

C65

C63

A65

C55

D55

B54

C56

BA5

AY5

AT16

AU16

H66

H65

R0810

49.9Ohm

1%

12

@

U0301D

CATERR#

PECI

PROCHOT#

THERMTRIP#

SKTOCC#

CPU MISC

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

A6

GPP_E3/CPU_GP0

A7

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

SKL-ULT

REV=<REV>

20150108

Checking

SL0801~0803 near device side

21

0402

21

0402

21

0402

SL0802

SL0801

SL0803

JTAG

OD

THRO_CPU# 30

IMVP8_VRHOT# 80

PWRLIMIT#_CPU 89

B61

PROC_TCK

D60

XDP_TCLK_CPU

PROC_TDI

A61

XDP_TDI_CPU

PROC_TDO

C60

XDP_TDO_CPU

PROC_TMS

B59

XDP_TMS_CPU

PROC_TRST#

XDP_TRST_CPU#

B56

PCH_JTAG_TCK

D59

PCH_JTAG_TCK

PCH_JTAG_TDI

A56

PCH_JTAG_TDI

PCH_JTAG_TDO

C59

PCH_JTAG_TDO

PCH_JTAG_TMS

C61

PCH_JTAG_TMS

PCH_TRST#

A59

PCH_TRST#

JTAGX

XDP_TCK_JTAGX

20160218 X541UV

R0803,R0804,R0805,R0807,R0 814,R0820,R0806 unstuff

XDP_TDI_CPU PCH_JTAG_TDI

XDP_TDO_CPU PCH_JTAG_T DO

XDP_TMS_CPU PCH_JTAG_TMS

XDP_TRST_CPU# PCH_TRST#

1

T0802

@

12

R0803 0Ohm

12

R0804 0Ohm@

12

R0805 0Ohm@

12

R0807 0Ohm@

12

R0814 0Ohm@

R0820 51Ohm

XDP_TDO_CPUXDP_TCLK_CPU XDP_TCK_JTAGX

R0806 51Ohm

XDP_TCLK_CPU

BOM

Title :

Size

Dept.:

B

Date: Sheet

Tuesday, June 20, 2017

@

12

@

12

CPU_MISC,JTAG,CLK

NB2_RD1_EE1

Main Board

+VCCSTG

Project Name

Engineer:

Joach_Wang

8

Rev

R2.0X542UA/UV

102

of

Page 8

CFG STRAPS

CFG4

CFG0

CFG4

R0902

49.9Ohm

1%

12

12

R0901 1KOhm

U0301S

E68

CFG[0]

B67

CFG[1]

D65

CFG[2]

D67

CFG[3]

E70

CFG[4]

C68

CFG4

CFG[5]

D68

CFG[6]

C67

CFG[7]

F71

CFG[8]

G69

CFG[9]

F70

CFG[10]

G68

CFG[11]

REV=<REV>

H70

CFG[12]

G71

CFG[13]

H69

CFG[14]

G70

CFG[15]

E63

CFG[16]

F63

CFG[17]

E66

CFG[18]

F66

CFG[19]

E60

CFG_RCOMP

E8

ITP_PMODE

AY2

RSVD_AY2

AY1

RSVD_AY1

D1

RSVD_D1

D3

RSVD_D3

K46

RSVD_K46

K45

RSVD_K45

AL25

RSVD_AL25

AL27

RSVD_AL27

C71

RSVD_C71

B70

RSVD_B70

F60

RSVD_F60

A52

RSVD_A52

BA70

RSVD_TP_BA70

BA68

RSVD_TP_BA68

J71

RSVD_J71

J68

RSVD_J68

F65

VSS_F65

G65

VSS_G65

F61

RSVD_F61

E61

RSVD_E61

SKL-ULT

01 NOTE

RESERVED SIGNALS-1

STALL RESET SEQUENCE

AFTER PCU PLL LOCK

UNTIL DE-ASSERTEDNO STALL STALL

eDP ENABLEDISABLE ENABLE

RSVD_TP_BB68

RSVD_TP_BB69

RSVD_TP_AK13

RSVD_TP_AK12

RSVD_TP_AW71

RSVD_TP_AW70

PROC_SELECT#

F6

E3

C11

B11

A11

D12

C12

F52

X0901

24Mhz

4

2

CPU_CFG,RSVD

Dept.:

NB2_RD1_EE1

Main Board

XTAL24_IN_U42

C0903

/U42

12

27PF/50V

C0904

/U42

12

27PF/50V

GND

Project Name

Rev

R2.0X542UA/UV

Engineer:

Joach_Wang

102

9

U0301T

SPARE

BB68

BB69

AK13

AK12

BB2

RSVD_BB2

BA3

RSVD_BA3

AU5

TP5

AT5

TP6

D5

RSVD_D5

D4

RSVD_D4

B2

RSVD_B2

C2

RSVD_C2

B3

RSVD_B3

A3

RSVD_A3

AW1

RSVD_AW1

E1

RSVD_E1

E2

RSVD_E2

BA4

RSVD_BA4

BB4

RSVD_BB4

A4

RSVD_A4

C4

RSVD_C4

BB5

TP4

A69

RSVD_A69

B69

RSVD_B69

AY3

RSVD_AY3

D71

RSVD_D71

C70

RSVD_C70

C54

RSVD_C54

D54

RSVD_D54

AY4

TP1

BB3

TP2

AY71

VSS_AY71

AR56

ZVM#

AW71

AW70

AP56

R0905

@

MSM#

C64

+1.0V_VCCST

12

100KOhm

AW69

AW68

AU56

AW48

C7

U12

XTAL24_OUT_U42

U11

H11

12

12

C0901

C0902

1UF/6.3V

1UF/6.3V

@

@

2016/10/05 X542UA_R1.0 #01, Add 24MHz parts for KBL-R U42

XTAL 24MHz

XTAL24_IN_U42

XTAL24_OUT_U42

2nd source:

0402

SL0901

07009-00062000 (未測)

07009-00063200 (未測)

21

0402

SL0902

21

RSVD_AW69

RSVD_AW68

RSVD_AU56

RSVD_AW48

RSVD_C7

RSVD_U12

RSVD_U11

RSVD_H11

REV=<REV>

SKL-ULT

12

R0903

1MOhm

/U42

/U42

07009-00063100

BOM

Title :

Date: Sheet of

RSVD_F6

RSVD_E3

RSVD_C11

RSVD_B11

RSVD_A11

RSVD_D12

RSVD_C12

RSVD_F52

13

Size

Custom

Tuesday, June 20, 2017

Page 9

CPU - VCC DECAPS- Underneath the package

+VCCCORE

28A 2+2

CAP above 22UF move to PWR page

12

12

C1030

C1028

C1031

1UF/6.3V

1UF/6.3V

2.2UF/10V

@

CAP above 22UF move to PWR page

12

12

CPU - VCC DECAPS- Place close to the package

+VCCCORE

Simulation team suggestion

For X542U

+VCCCORE

5.1A

12

12

12

nbs_c0603_h37_000s

12

nbs_c0603_h37_000s

12

C1058

C1059

C1060

C1069

10UF/6.3V

10UF/6.3V

10UF/6.3V

10UF/6.3V

nbs_c0603_h37_000s

nbs_c0603_h37_000s

nbs_c0603_h37_000s

12

12

C1073

C1074

C1071

10UF/6.3V

10UF/6.3V

10UF/6.3V

nbs_c0603_h37_000s

nbs_c0603_h37_000s

12

12

C1037

C1038

2.2UF/10V

2.2UF/10V

BOM

Project Name

Rev

Title :

CPU_POWER_CAP

Size

Dept.:

NB2_RD1_EE1

C

Date: Sheet

Tuesday, June 20, 2017

R2.0X542UA/UV

Engineer:

Joach_Wang

102

of

10

12

C1057

10UF/6.3V

nbs_c0603_h37_000s

12

C1070

10UF/6.3V

nbs_c0603_h37_000s

12

C1036

C1034

1UF/6.3V

2.2UF/10V

@

2017/01/23 X542UA_R1.1 #20, VCCCORE Caps modify in list

Page 10

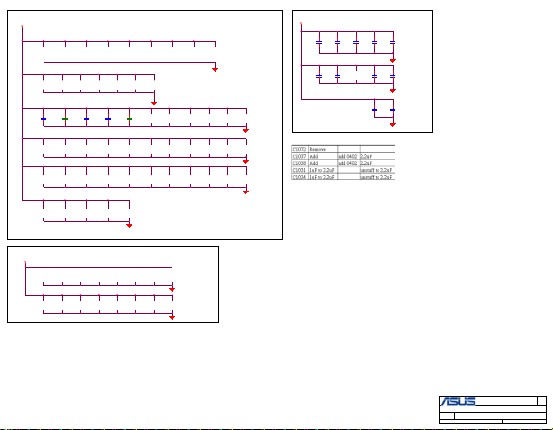

<Variant Name>

Project Name

Title :

DDR4_TERMINATION_A

Size

Dept.:

C

Date: Sheet

Tuesday, June 20, 2017

Rev

R2.0X542UA/UV

Engineer:

Joach_Wang

102

of

13

Page 11

2016/11/23 X542UA_#86, Add SO-DIMM (ChA), remove P13, P14 & P15 DRAM

+1.2V

M_A_WE#4

M_A_CAS#4

M_A_RAS#4

R1605

M_A_ACT#4

M_A_VREFCA

240Ohm

12

M_A_PAR4

M_A_ALERT#4

DDR4_DRAMRST#4,17

12

12

C1617

C1612

SMB_DATA_S35,17,47

0.1UF/10V

2.2UF/10V

SMB_CK_S35,17,47

GND GND

Place close to SO-DIMM

J1601A

137

M_A_CLK_DDR04

CK0_T

139

M_A_CLK_DDR#04

CK0_C

138

M_A_CLK_DDR14

CK1_T

140

M_A_CLK_DDR#14

CK1_C

109

M_A_CKE04

CKE0

110

M_A_CKE14

CKE1

149

M_A_CS#04

S0*

157

M_A_CS#14

S1*

155

M_A_ODT04

ODT0

161

M_A_ODT14

ODT1

115

M_A_BG04

BG0

113

M_A_BG14

BG1

150

M_A_BA04

BA0

145

M_A_BA14

BA1

M_A_A[13:0]4

144

A0

133

M_A_A0

A1

132

M_A_A1

A2

131

M_A_A2

A3

128

M_A_A3

A4

126

M_A_A4

A5

127

M_A_A5

A6

122

M_A_A6

A7

125

M_A_A7

A8

121

M_A_A8

A9

146

M_A_A9

A10_AP

120

M_A_A10

A11

119

M_A_A11

A12

158

M_A_A12

A13

151

M_A_A13

A14_WE*

156

A15_CAS*

152

A16_RAS*

114

ACT*

143

PARITY

116

ALERT*

134

EVENT*

108

M_A_DIMM0_EVENT#

RESET*

164

VREFCA

254

SDA

253

SCL

166

SA2

260

M_A_DIMM0_SA2

SA1

256

M_A_DIMM0_SA1

SA0

M_A_DIMM0_SA0

92

CB0_NC

91

CB1_NC

101

CB2_NC

105

CB3_NC

88

CB4_NC

87

CB5_NC

100

CB6_NC

104

CB7_NC

+1.2V

12

DM0*/DBI0*

33

D

M1*/DBI1*

54

DM2*/DBI2*

75

DM3*/DBI3*

178

DM4*/DBI4*

199

DM5*/DBI5*

220

DM6*/DBI6*

241

DM7*/DBI7*

96

DM8*/DBI8*

For ECC

162

1

T1601

S2*/C0

165

1

T1602

M_A_DIMM0_S2

S3*/C1

M_A_DIMM0_S3

DDR4_DIMM_260P

12002-00083500

2nd source:

12002-00082100

12002-00082000

'EVENT_N': INDICATES THERMAL EVENT ON DIMM.

NON-ECC DIMM: NOT CONNECTED

EVENT# ON ECC DIMM: KEEP A PULL UP IF NO PIN IN PCH

2016/12/05 X542UA_R1.0 #98, DDR SWAP

2016/12/07 X542UA_R1.0 #A3, DDR SWAP

M_A_DQ[63:0] 4

SWAP

8

DQ0

7

M_A_DQ0

DQ1

20

M_A_DQ1

DQ2

21

M_A_DQ2

D0

DQ3

4

M_A_DQ3

DQ4

3

M_A_DQ5

DQ5

16

M_A_DQ4

DQ6

17

M_A_DQ6

DQ7

28

M_A_DQ7

DQ8

29

M_A_DQ12

DQ9

41

M_A_DQ8

DQ10

42

M_A_DQ10

D1

DQ11

24

M_A_DQ14

DQ12

25

M_A_DQ13

DQ13

38

M_A_DQ9

DQ14

37

M_A_DQ11

DQ15

50

M_A_DQ15

DQ16

49

M_A_DQ17

DQ17

62

M_A_DQ21

DQ18

63

M_A_DQ16

D2

DQ19

46

M_A_DQ23

DQ20

45

M_A_DQ18

DQ21

58

M_A_DQ20

DQ22

59

M_A_DQ19

DQ23

70

M_A_DQ22

DQ24

71

M_A_DQ28

DQ25

83

M_A_DQ29

DQ26

84

M_A_DQ31

D3

DQ27

66

M_A_DQ25

DQ28

67

M_A_DQ24

DQ29

79

M_A_DQ27

DQ30

80

M_A_DQ30

DQ31

174

M_A_DQ26

DQ32

173

M_A_DQ35

DQ33

187

M_A_DQ37

DQ34

186

M_A_DQ38

D4

DQ35

170

M_A_DQ34

DQ36

169

M_A_DQ32

DQ37

183

M_A_DQ36

DQ38

182

M_A_DQ39

DQ39

195

M_A_DQ33

DQ

4

0

194

M_A_DQ56

DQ41

207

M_A_DQ60

DQ42

208

M_A_DQ63

D7

DQ43

191

M_A_DQ62

DQ44

190

M_A_DQ61

DQ45

203

M_A_DQ57

DQ46

204

M_A_DQ58

DQ47

216

M_A_DQ59

DQ48

215

M_A_DQ44

DQ49

228

M_A_DQ45

DQ50

229

M_A_DQ47

D5

DQ51

211

M_A_DQ46

DQ52

212

M_A_DQ41

DQ53

224

M_A_DQ40

DQ54

225

M_A_DQ42

DQ55

237

M_A_DQ43

DQ56

236

M_A_DQ52

DQ57

249

M_A_DQ48

DQ58

250

M_A_DQ51

D6

DQ59

232

M_A_DQ55

DQ60

233

M_A_DQ53

DQ61

245

M_A_DQ49

DQ62

246

M_A_DQ54

DQ63

M_A_DQ50

M_A_DQS[7:0] 4

13

DQS0_T

34

M_A_DQS0

DQS1_T

55

M_A_DQS1

20161207 swap

DQS2_T

76

M_A_DQS2

DQS3_T

179

M_A_DQS3

DQS4_T

200

M_A_DQS4

DQS5_T

221

M_A_DQS7

DQS6_T

242

M_A_DQS5

DQS7_T

97

M_A_DQS6

DQS8_T

M_A_DQS#[7:0] 4

11

DQS0_C

32

M_A_DQS#0

DQS1_C

53

M_A_DQS#1

20161207 swap

DQS2_C

74

M_A_DQS#2

DQS3_C

177

M_A_DQS#3

DQS4_C

198

M_A_DQS#4

DQS5_C

219

M_A_DQS#7

DQS6_C

240

M_A_DQS#5

DQS7_C

95

M_A_DQS#6

DQS8_C

20161205 swap

20161205 swap

20161205 swap

20161205 swap

20161205 swap

20161207 swap

20161207 swap

20161207 swap

J1601B

163

VDD19

160

VDD18

159

VDD17

154

VDD16

153

VDD15

148

VDD14

147

VDD13

142

VDD12

141

VDD11

136

VDD10

135

VDD9

130

VDD8

129

VDD7

124

VDD6

123

VDD5

118

VDD4

117

VDD3

112

VDD2

111

VDD1

251

VSS1

247

VSS2

243

VSS3

239

VSS4

235

VSS5

231

VSS6

227

VSS7

223

VSS8

217

VSS9

213

VSS10

209

VSS11

205

VSS12

201

VSS13

197

VSS14

193

VSS15

189

VSS16

185

VSS17

181

VSS18

175

VSS19

171

VSS20

167

VSS21

107

VSS22

103

VSS23

99

VSS24

93

VSS25

89

VSS26

85

VSS27

81

VSS28

77

VSS29

73

VSS30

69

VSS31

65

VSS32

61

V

57

VSS34

51

VSS35

47

VSS36

43

VSS37

39

VSS38

35

VSS39

31

VSS40

27

VSS41

23

VSS42

19

VSS43

15

VSS44

9

VSS45

5

VSS46

1

VSS47

DDR4_DIMM_260P

GND GND

+2.5V+1.2V

+3VS

+VTT

258

VTT

259

VPP2

257

VPP1

SL1604

255

21

VDDSPD

NP_NC1

NP_NC2

MT1

MT2

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VS

7

S7

VSS78

VSS79

VSS80

3

SS3

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

2017/02/02 X542UA_R1.1 #24, 0ohm modify to SL

0402

12

12

C1628

C1627

0.1UF/10V

2.2UF/10V

GND GND

263

264

261

262

252

248

244

238

234

230

226

222

218

214

210

206

202

196

192

188

184

180

176

172

168

106

102

98

94

90

86

82

78

72

68

64

60

56

52

48

44

40

36

30

26

22

18

14

10

6

2

+VTT

nbs_c0603_h37_000s

12

12

C1603

10UF/6.3V

10UF/6.3V

nbs_c0603_h37_000s

Place close to SO-DIMM Socket

(+VTT Pin)

+1.2V

12

+

CE1601

330UF/2V

11020-0035Z000

@

GND

12

C1606

10UF/6.3V

nbs_c0603_h37_000s

12

C1616

0.1UF/16V

/EMI

2017/02/06 X542UA_R1.1 #26, EMI solution

2017/02/02 X542UA_R1.1 #24, 0ohm modify to SL

2017/03/16 X542UA_R2.0 #03, Modify SA0 to pull down

@

12

21

0402

Place close to SO-DIMM

GND GND GN D

12

C1622

C1619

0.1UF/16V

/EMI

@

GND GNDGNDGND GNDGNDGND

Place close to SO-DIMM Socket (VDD Pin)

12

12

C1618

10UF/6.3V

@

GNDGNDGND GND

nbs_c0603_h37_000s

nbs_c0603_h37_000s

12

12

C1605

0.1UF/16V

/EMI

GNDGNDGND GND GNDGNDGNDGND

+3VS+3VS+3VS

R1602

R1601

R1609

@

@

0Ohm

0Ohm

0Ohm

12

12

M_A_DIMM0_SA2

M_A_DIMM0_SA1

M_A_DIMM0_SA0

21

21

SL1601

SL1602

SL1603

0402

0402

WRITE ADDRESS: 0X

+2.5V

nbs_c0603_h37_000s

12

12

C1608

10UF/6.3V

nbs_c0603_h37_000s

Place close to SO-DIMM Socket

(+VPP Pin)

2017/02/06 X542UA_R1.1 #26, EMI solution2017/02/06 X542UA_R1.1 #26, EMI solution

12

12

C1626

C1613

C1614

10UF/6.3V

10UF/6.3V

10UF/6.3V

@

GND

GND

nbs_c0603_h37_000s

nbs_c0603_h37_000s

nbs_c0603_h37_000s

12

12

12

C1621

0.1UF/16V

C1625

C1611

/EMI

1UF/6.3V

1UF/6.3V

BOM

Title :

DDR3_ON-BOARD_B_L32

Size

Dept.:

NB2_RD1_EE1

C

Date: Sheet of

Tuesday, June 20, 2017

12

12

C1615

C1607

0.1UF/16V

C1604

0.1UF/16V

/EMI

10UF/6.3V

/EMI

@

12

12

12

C1610

C1620

C1602

10UF/6.3V

10UF/6.3V

10UF/6.3V

/EMI

@

GNDGND

nbs_c0603_h37_000s

nbs_c0603_h37_000s

12

12

C1624

0.1UF/16V

C1609

C1623

/EMI

1UF/6.3V

1UF/6.3V

Project Name

Rev

R2.0X542UA/UV

Engineer:

Joach_Wang

102

16

Page 12

2016/11/16 X542UA_#78, Remove R1709

M_B_VREFCA

12

C1704

0.1UF/10V

GND GND

Place close to SO-DIMM

(3895.00 3358.00)

EMI

DDR4_DRAMRST#