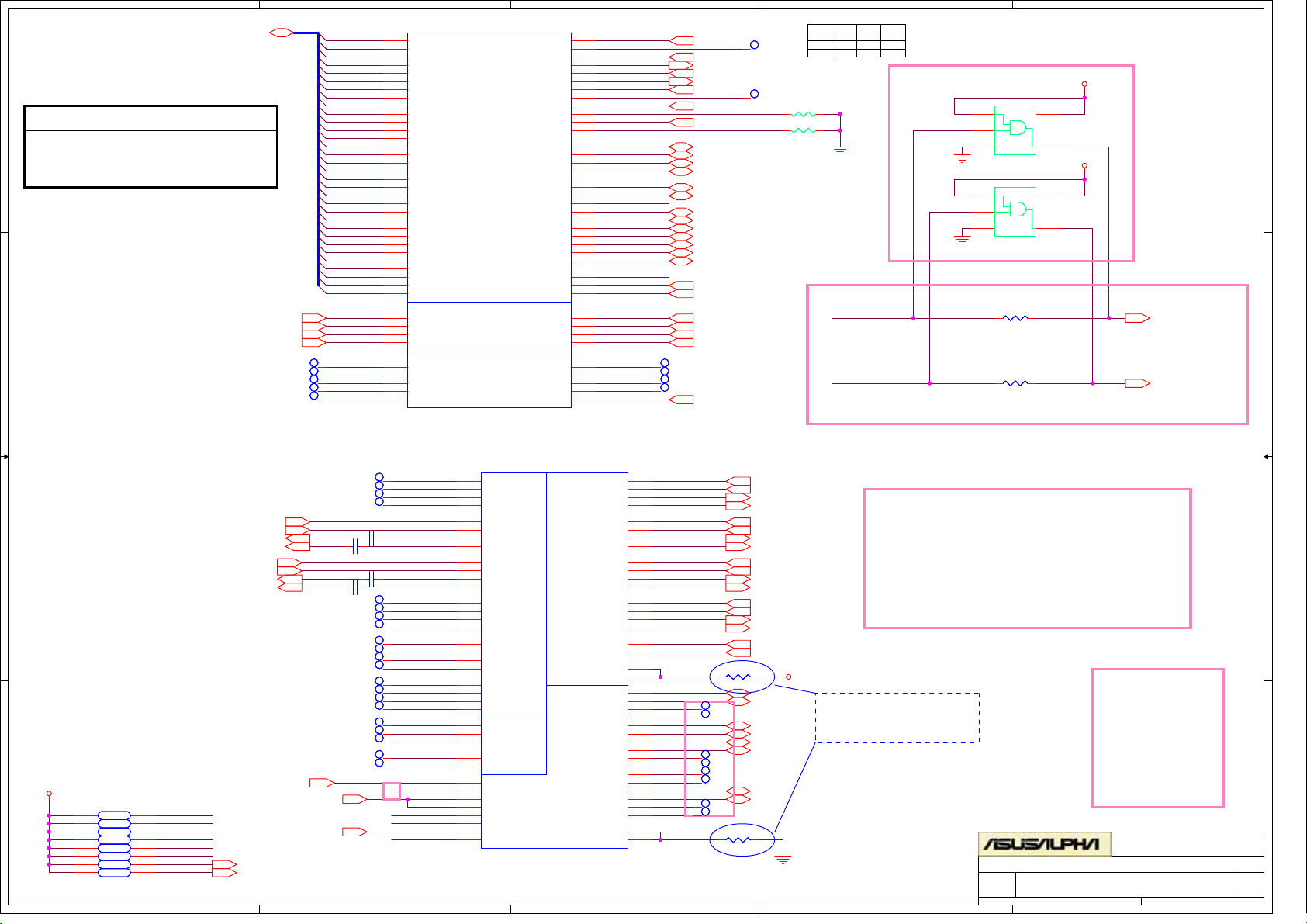

Asus Teresa, Satellite Pro L40 Schematic

5

4

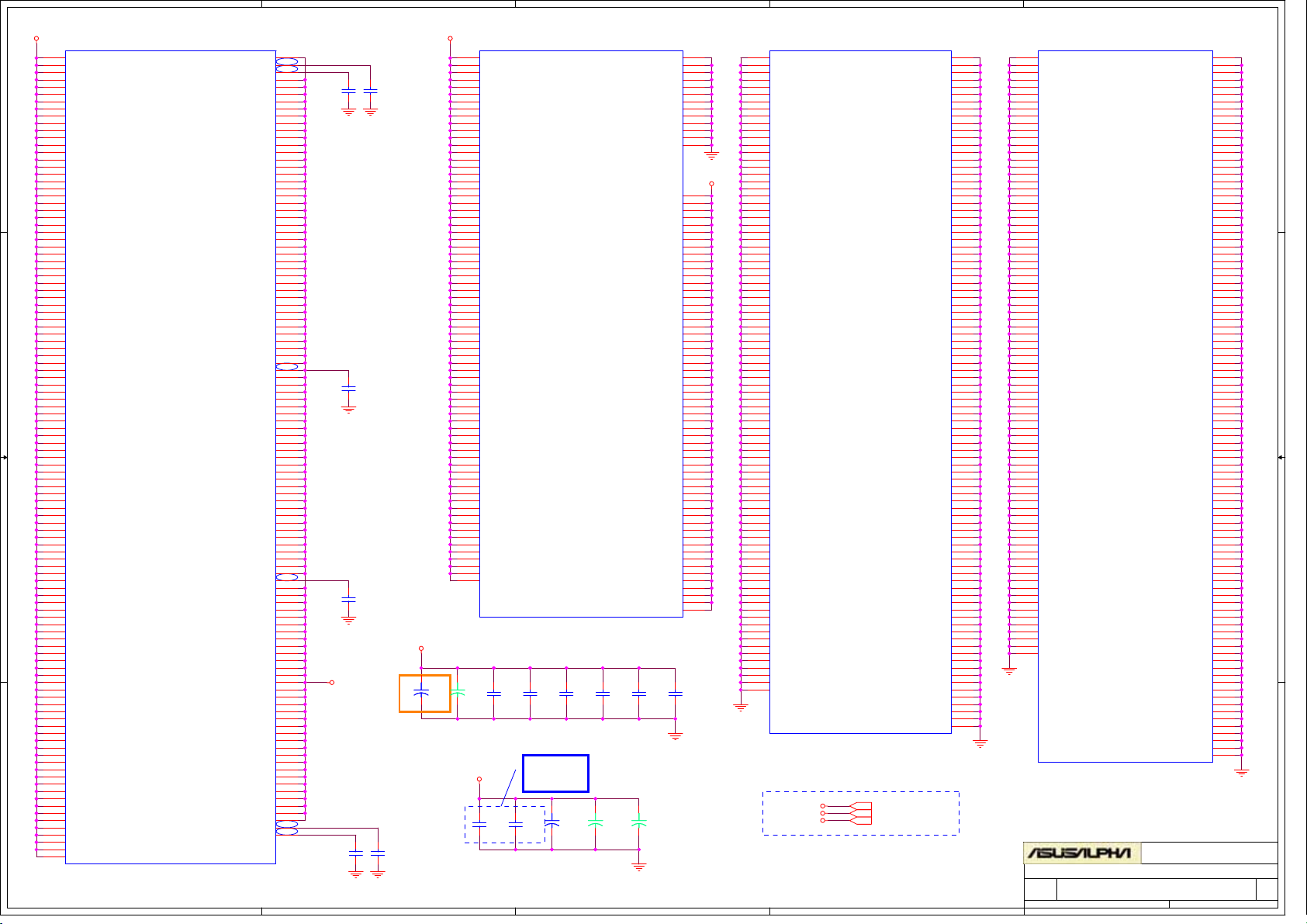

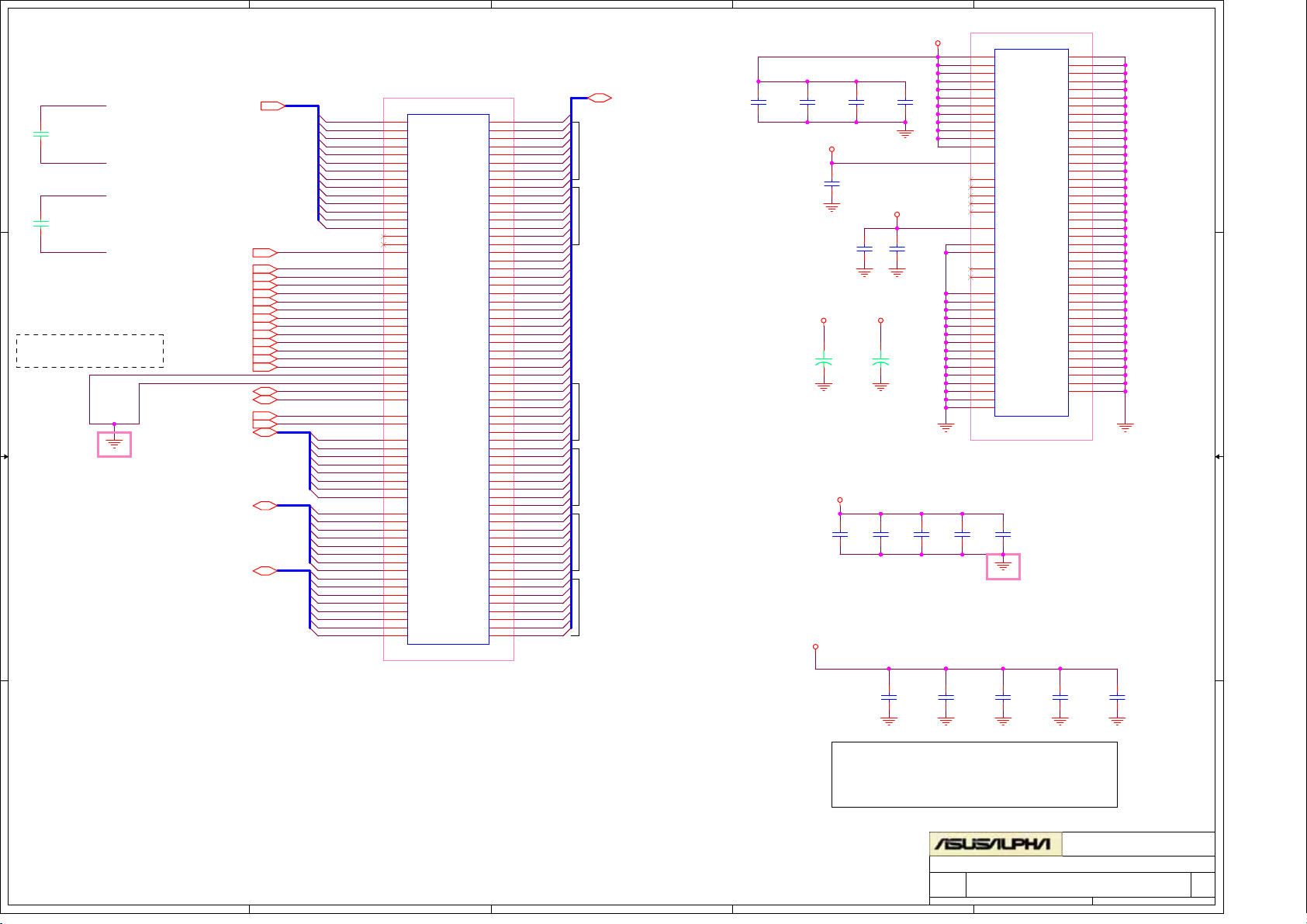

TERESA Block Diagram

3

2

1

FAN + SENSOR

ADM1032ARMZ

PAGE 4

D D

LVDS & INV

PAGE 12

CRT

C C

PAGE 13

T/P

PAGE 30

KEYPAD

MATRIX

PAGE 29

INSTANT KEY

PAGE 38

B B

LED Control

PAGE 30,38

EC IT8511E

PAGE 29,30

LPC

33MHz

Azalia

ISA

ROM

PAGE 24

(SATA)

MIC PHONE JACK

PAGE 23

HEADPHONE JACK

PAGE 22

A A

SPEAKER

PAGE 22

5

AUDIO AMP

PAGE 22

Azalia Codec

AD1986A

PAGE 21,22,23

MDC

PAGE 35

4

BTO

PAGE 28

PAGE 28

T2060

4xx,5xx Series

PAGE 2,3

GMCH-M

Calistoga

943GML

B0:02G010009121

PAGE 6,7,8,9,10,11

ICH7-M

B0:02G010008811

PAGE

17,18,19,20

SATA

HDD

ODD

IDE

3

FSB

533MHz

DMI Interface

USB

PAGE 36

DDR2-533MHz

PCIE *1

PCIE *1

PCI

33MHz

USB 2.0

CON X3

Dual Channel DDR2

SO-DIMM X 2

PAGE 14,15,16

MINI CARD

WLAN

PAGE 26

NEW

CARD

PAGE 25

10/100 LAN

RTL8100CL

PAGE 34,35

CardBus

R5C847

PAGE 43,44

2

BTO

BTO

BTO

ASUSALPHATeK COMPUTER INC.

ASUSALPHATeK COMPUTER INC.

ASUSALPHATeK COMPUTER INC.

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

TERESA

TERESA

TERESA

CPU

CLOCK GEN

ICS954310

PAGE 5

DISCHARGER

CIRCUIT

PAGE 37

Power On Sequence

PAGE 40

DC/BATT IN

PAGE 41

CPU VCORE

PAGE 50

SYSTEM PWR

PAGE 51

BAT & CHARGER

PAGE 57

PCMCIA

PAGE 44

MEDIA CARD SLOT

PAGE 33

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Horng Chou

Horng Chou

Horng Chou

1

157Monday, February 05, 2007

157Monday, February 05, 2007

157Monday, February 05, 2007

BTO

of

of

of

BTO

Rev

Rev

Rev

1.1

1.1

1.1

5

H_A#[16..3]6

H_REQ#[4..0]6

H_A#[31..17]6

4

3

2

1

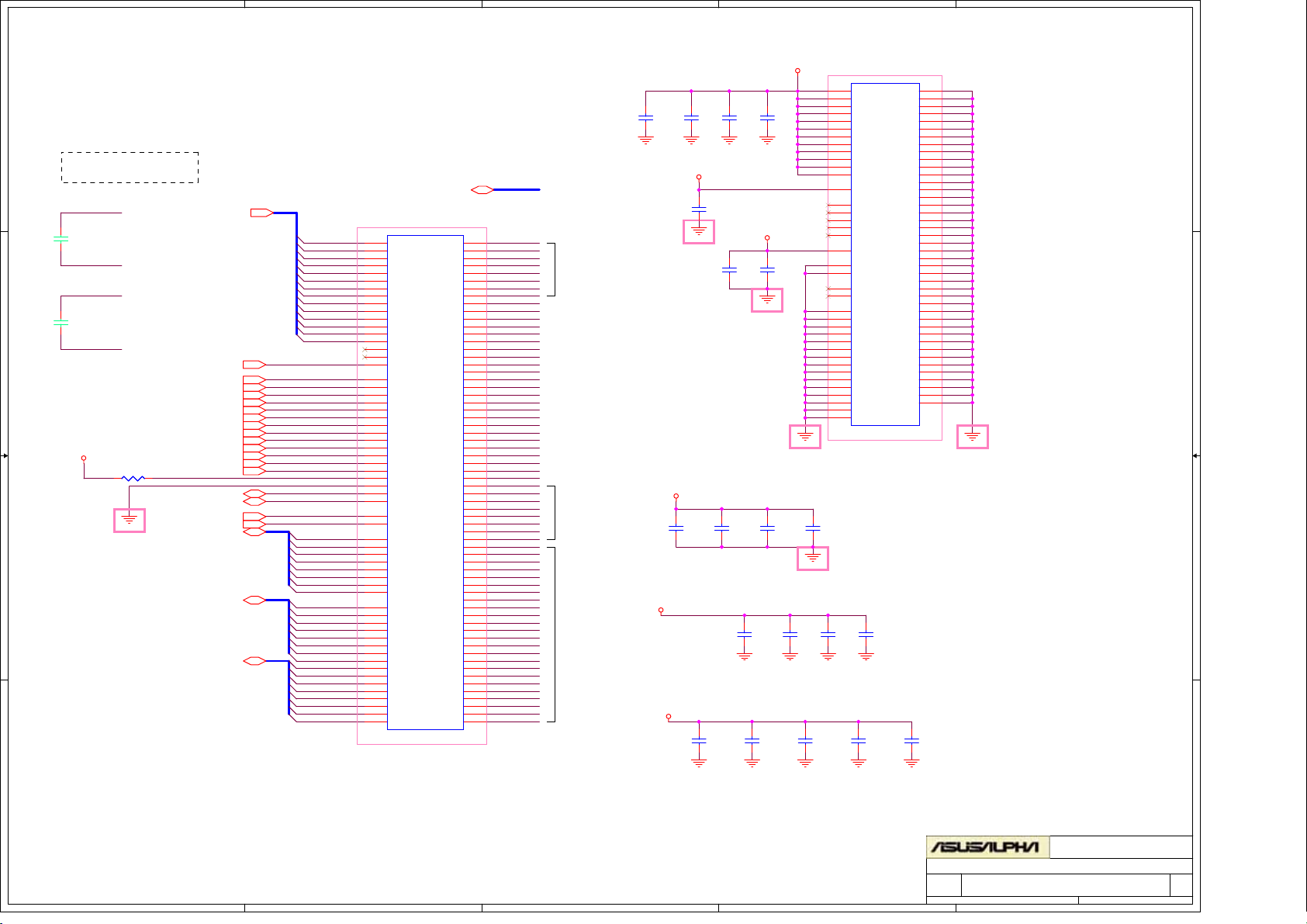

T202T202

U201A

D D

H_ADSTB#06

C C

H_ADSTB#16

H_A20M#17

H_FERR#17

H_IGNNE#17

H_STPCLK#17

H_INTR17

H_NMI17

H_SMI#17

B B

H_A#3

H_A#4

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_ADSTB#0

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_ADSTB#1 H_PROCHOT_S#

H_A20M#

H_FERR#

H_IGNNE#

H_STPCLK#

H_INTR

H_NMI

H_SMI#

U201A

J4

A[3]#

L4

A[4]#

M3

A[5]#

K5

A[6]#

M1

N2

J1

N3

P5

P2

L1

P4

P1

R1

L2

K3

H2

K2

J3

L5

Y2

U5

R3

W6

U4

Y5

U2

R4

T5

T3

W3

W5

Y4

W2

Y1

V4

A6

A5

C4

D5

C6

B4

A3

AA1

AA4

AB2

AA3

M4

N5

T2

V3

B2

C3

B25

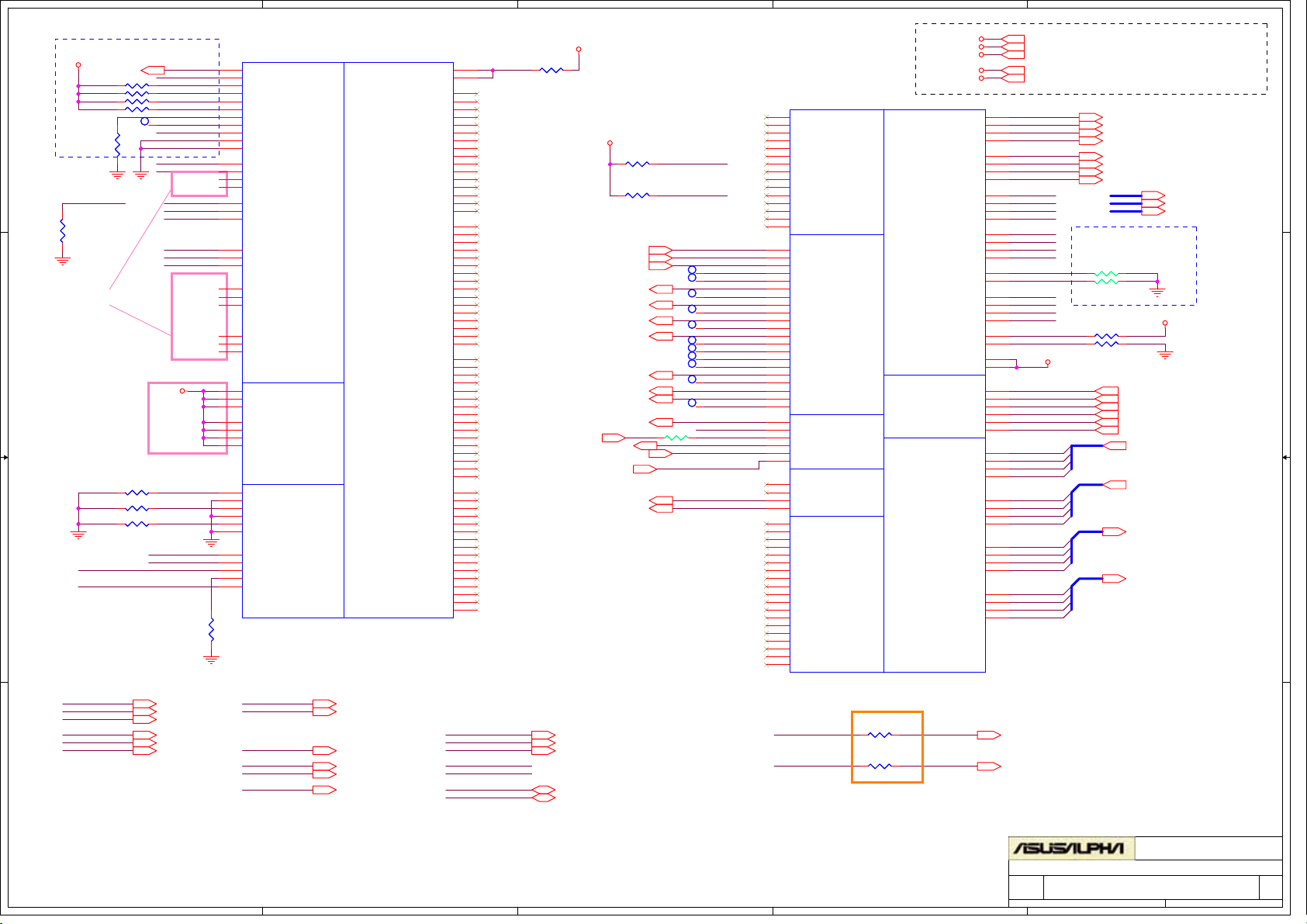

(070122)Change CPU Socket

into PN=12G011204796

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[1]

RSVD[2]

RSVD[3]

RSVD[4]

RSVD[5]

RSVD[6]

RSVD[7]

RSVD[8]

RSVD[9]

RSVD[10]

RSVD[11]

ADDR GROUP 0

ADDR GROUP 0

CONTROL

CONTROL

ADDR GROUP 1

ADDR GROUP 1

XDP/ITP SIGNALS

XDP/ITP SIGNALS

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

THERMHCLKRESERVED

THERMHCLKRESERVED

RSVD[12]

RSVD[A2]

RSVD[13]

RSVD[14]

RSVD[15]

RSVD[16]

RSVD[17]

RSVD[18]

RSVD[19]

RSVD[20]

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

DBR#

BCLK[0]

BCLK[1]

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

B1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

TDI

AB3

AB5

AB6

C20

D21

A24

A25

C7

A22

A21

T22

A2

D2

F6

D3

C1

AF1

D22

C23

C24

1

H_ADS#

H_BNR#

H_BPRI#H_A#5

H_DEFER#

H_DRDY#

H_DBSY#

H_BR0#

H_IERR#

H_INIT#

H_LOCK#

H_CPURST#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

H_HIT#

H_HITM#

PRDY#

H_PREQ#

H_TCK

H_TDI

H_TDO

H_TMS

H_TRST#

CPU_DBR#

CPU_THRM_DA

CPU_THRM_DC

PM_THRMTRIP#

CLK_CPU_BCLK

CLK_CPU_BCLK#

H_ADS# 6

H_BNR# 6

H_BPRI# 6

H_DEFER# 6

H_DRDY# 6

H_DBSY# 6

H_BR0# 6

H_INIT# 17

H_LOCK# 6

H_CPURST# 6

H_RS#0 6

H_RS#1 6

H_RS#2 6

H_TRDY# 6

H_HIT# 6

H_HITM# 6

+VCCP_AGTL+

T203T203

1

R203 56Ohm@R203 56Ohm@

1 2

R204 56OhmR204 56Ohm

1 2

R205 56OhmR205 56Ohm

1 2

R206 56Ohm@R206 56Ohm@

1 2

R207 56OhmR207 56Ohm

1 2

R208 56OhmR208 56Ohm

1 2

CPU_THRM_DA 4

CPU_THRM_DC 4

PM_THRMTRIP# 4,17

CLK_CPU_BCLK 5

CLK_CPU_BCLK# 5

68 ± 5% pull-up to Vcc1_05

If PROCHOT# is not used, then it must be terminated with a

56 pull-up resistor to VCCP.

If PROCHOT# is routed between CPU, IMVP and MCH,

pull-up resistor has to be 75 Ohm ± 5%

1 2

1

T201T201

GND

1

TPC28T

TPC28T

R201

R201

56Ohm

56Ohm

R202

R202

54.9Ohm @

54.9Ohm @

T204

T204

12

+VCCP_AGTL+

+VCCP_AGTL+

C201

C201

0.1UF/10V

0.1UF/10V

@

@

GND

+VCCP_AGTL+

12

R213

R213

2KOhm

2KOhm

1%

1%

R209

R209

1KOhm

1KOhm

1%

1%

1 2

<500 mil (55 Ohm)

T/B trace 5

Space 25

1 2

GND

For Celeron M

BCLK

GND

H_DSTBN#06

H_DSTBP#06

H_DINV#06

H_DSTBN#16

H_DSTBP#16

H_DINV#16

CPU_BSEL05

CPU_BSEL15

CPU_BSEL25

R214

@R214

@

1KOhm

1KOhm

R216

R216

51Ohm

51Ohm

533MHz

1 2

1 2

FSB

BSEL2

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DSTBN#1

H_DSTBP#1

H_DINV#1

GTL_REF

AD26

TEST1

TEST2

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

BSEL1BSEL0

HL133MHz L

U201B

U201B

E22

D[0]#

F24

D[1]#

E26

D[2]#

H22

D[3]#

F23

G25

E25

E23

K24

G24

H26

F26

K22

H25

H23

G22

N22

K25

P26

R23

L25

L22

L23

M23

P25

P22

P23

T24

R24

L26

T25

N24

M24

N25

M26

C26

D25

B22

B23

C21

J24

J23

J26

DATA GRP 0

DATA GRP 0

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

DATA GRP 1

DATA GRP 1

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

MISC

MISC

TEST1

TEST2

BSEL[0]

BSEL[1]

BSEL[2]

(070122)Change CPU Socket

into PN=12G011204796

PWRGOOD

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

DATA GRP 2DATA GRP 3

DATA GRP 2DATA GRP 3

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

SLP#

PSI#

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

W24

Y25

V23

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

AD23

AE24

AC20

R26

U26

U1

V1

E5

B5

D24

D6

D7

AE6

H_D#[0..63] 6

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DSTBN#2

H_DSTBP#2

H_DINV#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#3

H_DSTBP#3

H_DINV#3

H_COMP0

R210 27.4Ohm 1%R210 27.4Ohm 1%

H_COMP1

H_COMP2

H_COMP3

H_DPRSTP#

H_DPSLP#

H_DPWR#

H_PWRGD

1 2

R211 54.9Ohm 1%R211 54.9Ohm 1%

1 2

R212 27.4Ohm 1%R212 27.4Ohm 1%

1 2

R215 54.9Ohm 1%R215 54.9Ohm 1%

1 2

1

H_CPUSLP#

PM_PSI#

H_DSTBN#2 6

H_DSTBP#2 6

H_DINV#2 6

Layout Note:

Comp0,2 connect with Z0=27.4 ohm,

make trace length shorter than 0.5".

Comp1,3 connect with Z0=54.9 ohm,

make trace length shorter than 0.5".

Comp[3:0] at least 25 mils away from

any other toggling signal.

27.4 ohm connects with an ~18mil

wide trace to comp0.

54.9 ohm connect with 5mil-wide

to comp1

H_DSTBN#3 6

H_DSTBP#3 6

H_DINV#3 6

H_DPRSTP# 17,50

H_DPSLP# 17

H_DPWR# 6

H_PWRGD 17

T205T205

H_CPUSLP# 6,17

PM_PSI# 50

GND

+VCCP_AGTL+ +VCCP

1 2

A A

+VCCP_AGTL+

2.5A

+VCCP

JP201

JP201

SHORT_PIN

SHORT_PIN

5

@

@

+VCCP 6,9,20,52

+VCCP_AGTL+ 3,5,6,9

H_PROCHOT_S#29

H_PROCHOT_S# H_PWRGD

4

+VCCP_AGTL+

R217

R217

56Ohm

56Ohm

1 2

+VCCP_AGTL+

R218

R218

56Ohm@

56Ohm@

1 2

3

Title :

Title :

Title :

Engineer:

Engineer:

ASUSALPHATeK COMPUTER INC.

ASUSALPHATeK COMPUTER INC.

ASUSALPHATeK COMPUTER INC.

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

TERESA

TERESA

TERESA

Engineer:

1

YONAH CPU (1)

YONAH CPU (1)

YONAH CPU (1)

Horng Chou

Horng Chou

Horng Chou

257Monday, February 05, 2007

257Monday, February 05, 2007

257Monday, February 05, 2007

Rev

Rev

Rev

1.1

1.1

1.1

5

4

3

2

1

Celeron M FSB:533MHz

MIN TYP MAX

VCC 1.0V 1.2V 1.3V

C3 C2 C0

ICC 14.7A 16.5A 29Ah

D D

+VCORE

U201CU201C

A7

VCC[1]

A9

VCC[2]

A10

VCC[3]

A12

VCC[4]

A13

VCC[5]

A15

VCC[6]

A17

VCC[7]

A18

VCC[8]

A20

VCC[9]

B7

VCC[10]

B9

VCC[11]

B10

VCC[12]

B12

VCC[13]

B14

VCC[14]

B15

VCC[15]

B17

VCC[16]

B18

VCC[17]

B20

VCC[18]

C9

VCC[19]

C10

VCC[20]

C12

VCC[21]

C13

VCC[22]

C15

VCC[23]

C17

VCC[24]

C18

C C

B B

VCC[25]

D9

VCC[26]

D10

VCC[27]

D12

VCC[28]

D14

VCC[29]

D15

VCC[30]

D17

VCC[31]

D18

VCC[32]

E7

VCC[33]

E9

VCC[34]

E10

VCC[35]

E12

VCC[36]

E13

VCC[37]

E15

VCC[38]

E17

VCC[39]

E18

VCC[40]

E20

VCC[41]

F7

VCC[42]

F9

VCC[43]

F10

VCC[44]

F12

VCC[45]

F14

VCC[46]

F15

VCC[47]

F17

VCC[48]

F18

VCC[49]

F20

VCC[50]

AA7

VCC[51]

AA9

VCC[52]

AA10

VCC[53]

AA12

VCC[54]

AA13

VCC[55]

AA15

VCC[56]

AA17

VCC[57]

AA18

VCC[58]

AA20

VCC[59]

AB9

VCC[60]

AC10

VCC[61]

AB10

VCC[62]

AB12

VCC[63]

AB14

VCC[64]

VCC[65]

VCC[66]

VCC[67]

VCCSENSE

VSSSENSE

AB15

AB17

AB18

(070122)Change CPU Socket

into PN=12G011204796

VCC[68]

VCC[69]

VCC[70]

VCC[71]

VCC[72]

VCC[73]

VCC[74]

VCC[75]

VCC[76]

VCC[77]

VCC[78]

VCC[79]

VCC[80]

VCC[81]

VCC[82]

VCC[83]

VCC[84]

VCC[85]

VCC[86]

VCC[87]

VCC[88]

VCC[89]

VCC[90]

VCC[91]

VCC[92]

VCC[93]

VCC[94]

VCC[95]

VCC[96]

VCC[97]

VCC[98]

VCC[99]

VCC[100]

VCCP[1]

VCCP[2]

VCCP[3]

VCCP[4]

VCCP[5]

VCCP[6]

VCCP[7]

VCCP[8]

VCCP[9]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

AD6

AF5

AE5

AF4

AE3

AF2

AE2

AF7

AE7

Celeron M FSB:533MHz

MIN TYP MAX

VCCP 0.997V 1.05V 1.102V

MIN TYP MAX

ICCP 2.5A

Modity Table for Celeron M

+VCORE

+VCCA

+VCCP_AGTL+

7 8

+VCCA

120mA / 20mil

Close to Pin B26

12

C301

C301

10UF/10V

10UF/10V

H_VID0

1 2

0Ohm

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

VCCSENSE

VSSSENSE

0Ohm

3 4

0Ohm

0Ohm

5 6

0Ohm

0Ohm

7 8

0Ohm

0Ohm

1 2

0Ohm

0Ohm

3 4

0Ohm

0Ohm

5 6

0Ohm

0Ohm

1 2

12

R302

R302

100Ohm

100Ohm

R301

R301

100Ohm

100Ohm

JP301

JP301

2

112

1MM_OPEN_5MIL

1MM_OPEN_5MIL

@

@

0Ohm

0Ohm

12

C318

C318

0.01UF/25V

0.01UF/25V

checklist suggests

10uF POSCAP

GND

RN302A

RN302A

RN302B

RN302B

RN302C

RN302C

RN302D

RN302D

RN303A

RN303A

RN303B

RN303B

RN303C

RN303C

+1.5VO

RN303D

RN303D

VR_VID0 50

VR_VID1 50

VR_VID2 50

VR_VID3 50

VR_VID4 50

VR_VID5 50

VR_VID6 50

+VCORE

VCCSENSE 50

VSSSENSE 50

U201DU201D

A4

VSS[1]

A8

VSS[2]

A11

VSS[3]

A14

VSS[4]

A16

VSS[5]

A19

VSS[6]

A23

VSS[7]

A26

VSS[8]

B6

VSS[9]

B8

VSS[10]

B11

VSS[11]

B13

VSS[12]

B16

VSS[13]

B19

VSS[14]

B21

VSS[15]

B24

VSS[16]

C5

VSS[17]

C8

VSS[18]

C11

VSS[19]

C14

VSS[20]

C16

VSS[21]

C19

VSS[22]

C2

VSS[23]

C22

VSS[24]

C25

VSS[25]

D1

VSS[26]

D4

VSS[27]

D8

VSS[28]

D11

VSS[29]

D13

VSS[30]

D16

VSS[31]

D19

VSS[32]

D23

VSS[33]

D26

VSS[34]

E3

VSS[35]

E6

VSS[36]

E8

VSS[37]

E11

VSS[38]

E14

VSS[39]

E16

VSS[40]

E19

VSS[41]

E21

VSS[42]

E24

VSS[43]

F5

VSS[44]

F8

VSS[45]

F11

VSS[46]

F13

VSS[47]

F16

VSS[48]

F19

VSS[49]

F2

VSS[50]

F22

VSS[51]

F25

VSS[52]

G4

VSS[53]

G1

VSS[54]

G23

VSS[55]

G26

VSS[56]

H3

VSS[57]

H6

VSS[58]

H21

VSS[59]

H24

VSS[60]

J2

VSS[61]

J5

VSS[62]

J22

VSS[63]

J25

VSS[64]

K1

VSS[65]

K4

VSS[66]

K23

VSS[67]

K26

VSS[68]

L3

VSS[69]

L6

VSS[70]

L21

VSS[71]

L24

VSS[72]

M2

VSS[73]

M5

VSS[74]

M22

VSS[75]

M25

VSS[76]

N1

VSS[77]

N4

VSS[78]

N23

VSS[79]

N26

VSS[80]

P3

VSS[81]

(070122)Change CPU Socket

into PN=12G011204796

VSS[82]

VSS[83]

VSS[84]

VSS[85]

VSS[86]

VSS[87]

VSS[88]

VSS[89]

VSS[90]

VSS[91]

VSS[92]

VSS[93]

VSS[94]

VSS[95]

VSS[96]

VSS[97]

VSS[98]

VSS[99]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

+VCCP_AGTL+ 2,5,6,9

+VCORE 50

+1.5VS 7,9,10,20,25,26,37,52

+VCORE

1215---PWR comp

12

+

+

CE301

CE301

220UF/4V

220UF/4V

@

@

GND

Place the cap on North

of Secondary side

+VCCP_AGTL+

+VCORE

+1.5VS

Vcc Core Decoupling Caps

Primary side => Bottom side

Secondary side => Top side

(070131)Change 22UF into 10UF

Place these upper side inside socket cavity on L1

12

C302

C302

10UF/10V

10UF/10V

GND GND

12

C303

C303

10UF/10V

10UF/10V

12

C304

C304

10UF/10V

10UF/10V

GND

12

C305

C305

10UF/10V

10UF/10V

GND GND

12

C306

C306

10UF/10V

10UF/10V

12

C307

C307

10UF/10V

10UF/10V

GND

Place these lower side inside socket cavity on L1

12

C309

C309

10UF/10V

10UF/10V

GND GND

12

C311

C311

10UF/10V

10UF/10V

12

C308

C308

10UF/10V

10UF/10V

GND

12

C310

C310

10UF/10V

10UF/10V

GND

12

10UF/10V

10UF/10V

GND

C312

C312

12

C313

C313

10UF/10V

10UF/10V

GND

Place these upper side inside socket cavity on L6

12

C314

C314

10UF/10V

10UF/10V

GND

12

C315

C315

10UF/10V

10UF/10V

GND

12

C316

C316

10UF/10V

10UF/10V

GND

Place these lower side inside socket cavity on L6

12

C319

C319

10UF/10V

10UF/10V

GND

(061228)Change into 10UF/10V PN:11G236322636360

C302,C303,C309,C311

C314,C315,C316,C317

C319,C320,C321,C322

GNDGND

12

C320

C320

10UF/10V

10UF/10V

12

C321

C321

10UF/10V

10UF/10V

GNDGND

12

C317

C317

10UF/10V

10UF/10V

GND

12

C322

C322

10UF/10V

10UF/10V

GND

+VCCP_AGTL+

12

C323

C323

c0402

c0402

0.1UF/10V

0.1UF/10V

+1.05V Decoupling Capacitor

Place near CPU

12

12

C324

C324

c0402

c0402

0.1UF/10V

0.1UF/10V

C325

C325

c0402

c0402

0.1UF/10V

0.1UF/10V

12

C326

C326

c0402

c0402

0.1UF/10V

0.1UF/10V

12

C327

C327

c0402

c0402

0.1UF/10V

0.1UF/10V

12

0.1UF/10V

0.1UF/10V

C328

C328

c0402

c0402

12

GND

+

+

CE302

CE302

100UF/2.5V

100UF/2.5V

GND

Layout Note:

VCCSENSE/VSSSENSE lines between the

CPU and the VR should have a trace width of

A A

5

18 mils on 7 mils spacing, with trace

impedance of Zo=27.4 Ohm.

The VCCSENSE/VSSSENSE should be

length matched to within 25 mils.

These resistors should be placed within 2

inch of the CPU.

Title :

Title :

Title :

Engineer:

Engineer:

ASUSALPHATeK COMPUTER INC.

ASUSALPHATeK COMPUTER INC.

ASUSALPHATeK COMPUTER INC.

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

TERESA

TERESA

TERESA

Engineer:

1

Yonah CPU (2)

Yonah CPU (2)

Yonah CPU (2)

Horng Chou

Horng Chou

Horng Chou

357Monday, February 05, 2007

357Monday, February 05, 2007

357Monday, February 05, 2007

Rev

Rev

Rev

1.1

1.1

1.1

5

4

3

2

1

NC2

NC1

+5VS 13,19,20,21,22,28,29,30,34,37,38,50,61

+3VS 5,7,9,11,12,13,14,15,19,20,21,22,25,26,27,28,29,30,33,37,40,43,50,52,60,61

+3VA 12,22,29,37,38,40,41,54,59,63

6

5

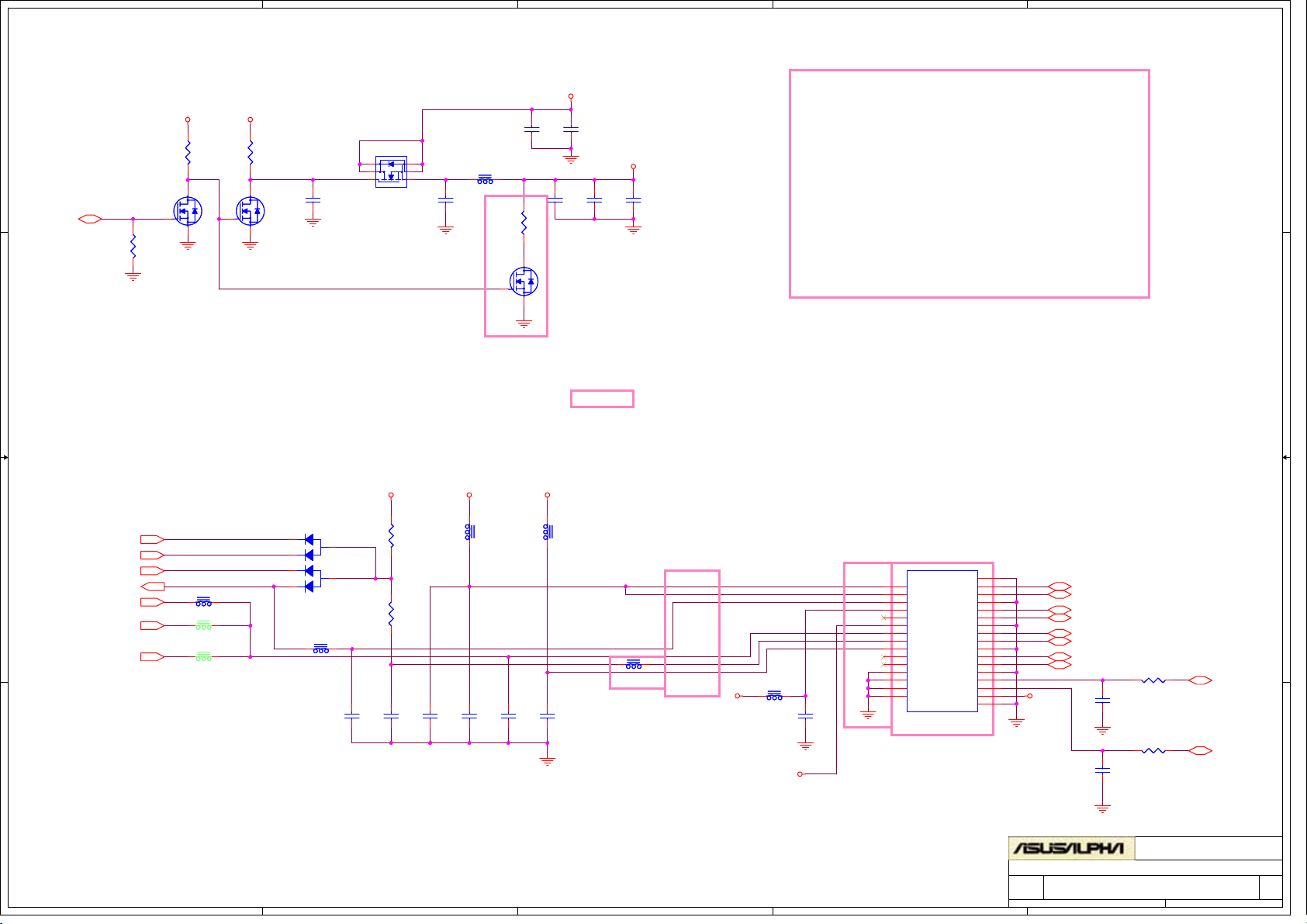

GND

+5VS

Fan Speed Control

+5VS

D D

C C

KBC will issue a

analog ( a voltage

level ) signal.

SW: FAN_DA1 must

be low during S3

FAN_PWM29

FAN0_TACH29

FAN_PWM

FAN0_TACH

+3VA

T403

T403

TPC28T

TPC28T

1

+3VS

R403

R403

10KOhm

10KOhm

1 2

12

C401

C401

2200PF/50V

2200PF/50V

GND

THERMAL PROTECTION

R402

R402

10KOhm

10KOhm

+3VS

12

+

+

CE401

CE401

100UF/10V

100UF/10V

@

@

GND

1 2

Unmount: CE401 and D1 New addition

D1

D1

1N4148W

1N4148W

@

@

1 2

12

GND

GNDGND

C403

C403

100PF/50V

100PF/50V

@

@

12

C408

C408

10UF/10V

10UF/10V

12

GND

GND

+3VS

+3VA

C402

C402

0.1UF/10V

0.1UF/10V

WtoB_CON_4P

WtoB_CON_4P

4

4

3

3

2

2

1

1

CON401

CON401

(070122)Change CON401 into

PN:12G171000047

PLACE UNDER CPU

R411

R411

7.68KOhm

7.68KOhm

1 2

1

R412

5

4

+3VA_EC

GND

1 2

3 2

3

3

R412

1

2

100KOhm

100KOhm

2

1

TPC28T

TPC28T

T401

T401

+5VS

D

D

Q403

Q403

2N7002

2N7002

T402

C407

C407

0.01UF/50V

0.01UF/50V

1

NC

2

SUB

GND3VOUT

T402

TPC28T

TPC28T

12

U402

U402

VCC

PST9013NR

PST9013NR

1

R409

R409

10KOhm

10KOhm

r0402

r0402

B B

Route H_THERMDA and H_THERMDC

on the same layer

------------------OTHER SIGNALS

12 mils

===============GND

10 mils

=========H_THERMDA(10 mils)

10 mils

A A

=========H_THERMDC(10 mils)

10 mils

=========GND

12 mils

---------------------OTHER SIGNALS

GND

THRM_CPU#29

Avoid BPSB,Power

5

4

(85 DEGREE C)

1

1

R414

R414

R413

R413

1

1

@

@

2

2

100KOhm

100KOhm

100KOhm

100KOhm

2

2

FORCE_OFF# 29,38,41,51,60

1

1

1

SMB1_CLK29

G

G

SMB1_DAT29

2

2

S

S

+3VS

105 -> 85, R411 need to be tuned

(1204)maybe R411=14.7K Ohm(10G213147213010)

1

1

R415

R415

R416

R416

1

1

@

@

@

@

100KOhm

100KOhm

2

@

@

2

2

100KOhm

100KOhm

2

(061214)Add 4 thermiters

(070130)Add 0ohm resister

1 2

R410

R410

4.7KOhm

4.7KOhm

+3VS

R408

R408

1 2

0Ohm

0Ohm

r0402

r0402

SMB1_CLK

SMB1_DAT

SMBALERT#

GND

+3VS_THM

+3VS_THM

12

C405

C405

0.1UF/10V

0.1UF/10V

c0402

c0402

8

7

6

5

ADM1032ARMZ_REEL

ADM1032ARMZ_REEL

(070110)

Add second sorce: 06G023048021

Standby Mode: 3uA(Max. 10uA)

Full Active: 0.5 mA(Max. 1mA)

U401

U401

VDD

SCLK

SDATA

ALERT#

THERM#

GND

3

+3VA

12

R405

1

1

1

G

G

R405

10KOhm

10KOhm

r0402

r0402

@

@

32

3

3

D

D

S

S

2

2

GND

TERESA

TERESA

TERESA

VSUS_ON

Q401

Q401

2N7002

2N7002

VSUS_ON 25,29,51

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

THER-SENSOR,FAN

THER-SENSOR,FAN

THER-SENSOR,FAN

Horng Chou

Horng Chou

Horng Chou

457Monday, February 05, 2007

457Monday, February 05, 2007

457Monday, February 05, 2007

Rev

Rev

Rev

1.1

1.1

1.1

+3VS

12

R406

R406

1MOhm

1MOhm

VSUS_ON_G

12

3

3

C404

Q402

TRIP_R

C406

C406

Q402

B

1

B

1

PMBS3904

PMBS3904

GND

CPU_THRM_DA 2

CPU_THRM_DC 2

R407

R407

PM_THRMTRIP#2,17

R417

R417

12

R418

R418

10KOhm

10KOhm

@

@

1 2

0Ohm

0Ohm

+3VS_THM

G

G

2

2

S

S

Q404 2N7002@

Q404 2N7002@

GMCH_THRMTRIP#7

1

CPU_THRM_DA

2

D+

CPU_THRM_DC

3

D-

4

1 2

330Ohm

330Ohm

4"-8"

12

2200PF/50V

2200PF/50V

1

1

1

3

3

32

D

D

4"-8"

EC_RST_SW# 29,38,41,51,60

(070110)Add R418 and Q404

to avoid error action

2

C404

C

C

0.22UF/6.3V

0.22UF/6.3V

E

E

2

2

GND

ASUSALPHATeK COMPUTER INC.

ASUSALPHATeK COMPUTER INC.

ASUSALPHATeK COMPUTER INC.

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

5

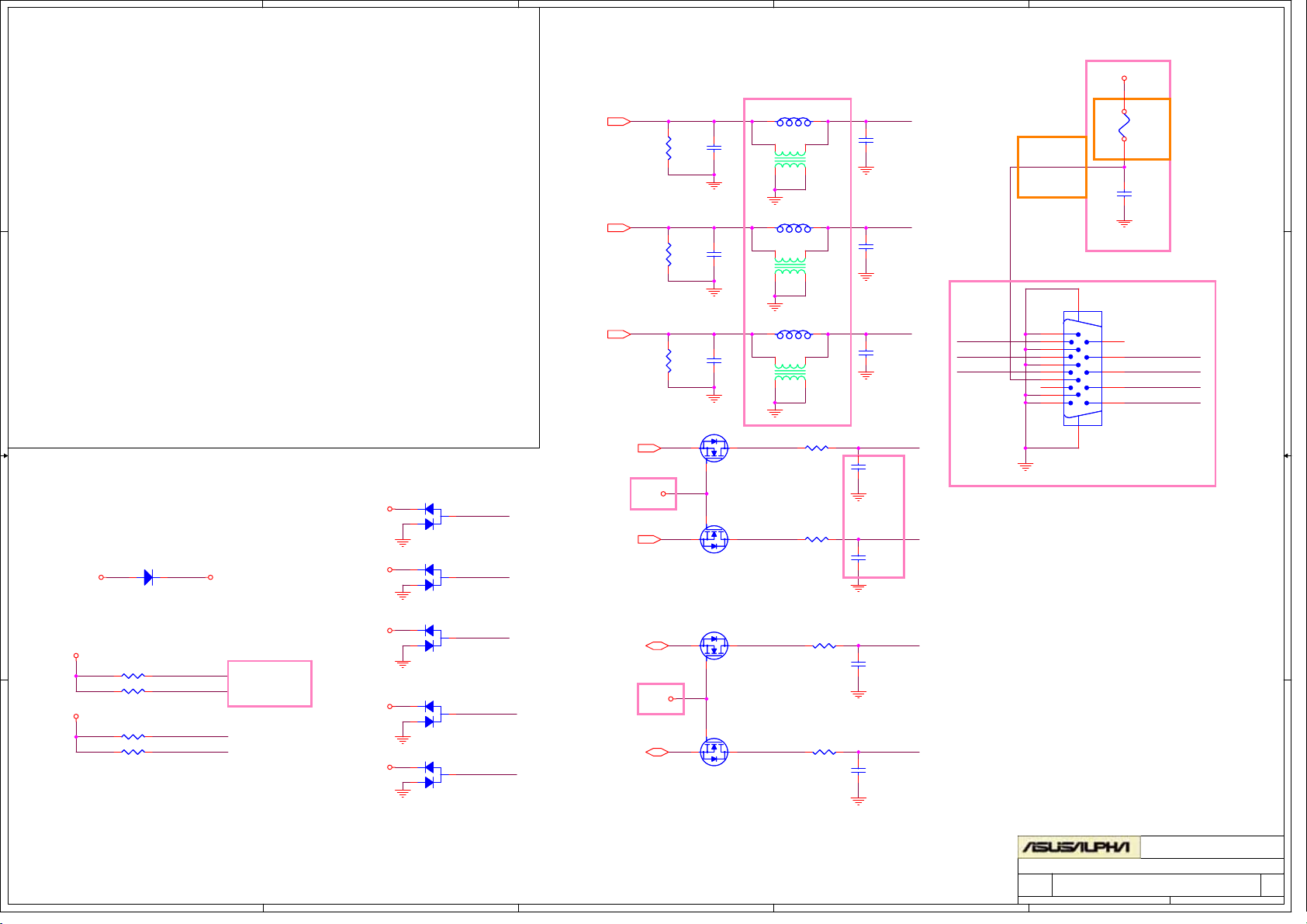

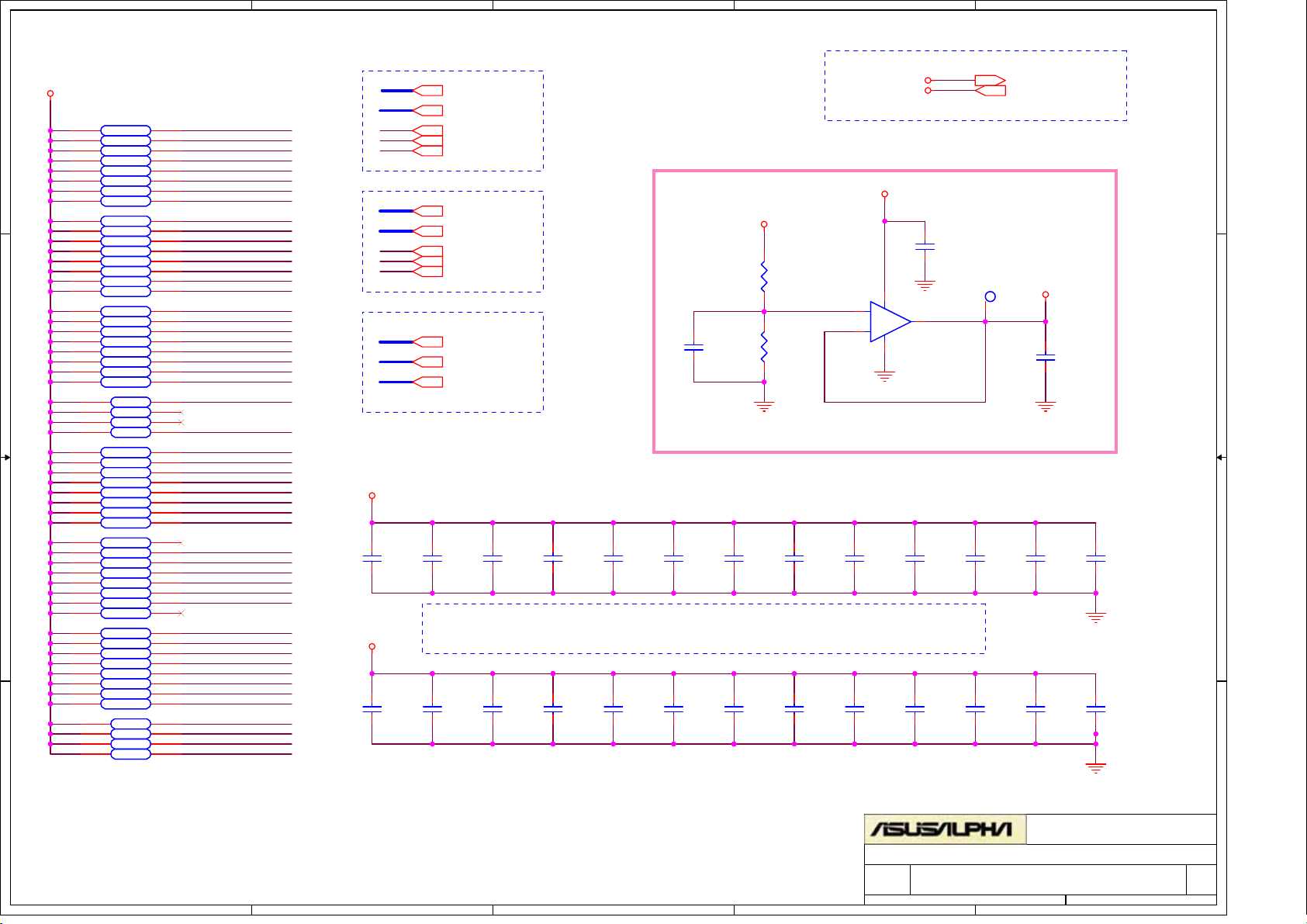

+VCCP_AGTL+

Request

Control net

PCIE_REQ1# PCIE0(#),PCIE6(#)

PCIE_REQ2#

PCIE_REQ3#

D D

PCIE_REQ4#

C C

B B

SELPCIE0_LCD#:

0-->pin17,pin18=LCDCLK(96MHz) or

27M/27M_SS

A A

SELLCD_27#/PCICLK_F1:

1-->pin17,pin18=LCDCLK(96MHz)

PCICLK2/REQ_SEL:

1-->pin40,pin41=PREQ1#,PREQ2#

ITP_EN/PCICLK_F0:

1-->CPU_ITP pair

PCIE1(#),PCIE8(#)

PCIE2(#),PCIE4(#)

PCIE3(#),PCIE5(#),

PCIE7(#)

(070130)Change C516

from 27PF to 33PF

CLK_LCD_SSCG7

CLK_LCD_SSCG#7

CLK_USB4819

CPU_BSEL02

CPU_BSEL12

CLK_LAN_PCI34

CLK_CBPCI43

Delete CLK_TPMPCI(connect to pin3)

CLK_FWHPCI26

CLK_ECPCI29

CLK_ICHPCI18

SMB_CLK_S14,15,19,25,26

SMB_DAT_S14,15,19,25,26

5

Net name

None

None

CLK_PCIE_MINICARD(#)

CLK_MCH_3GPLL(#)

+/-30ppm/20PF

+/-30ppm/20PF

X501

X501

14.318Mhz

14.318Mhz

12

12

12

12

C516

C516

C517

C517

33PF/50V

33PF/50V

33PF/50V

33PF/50V

GND

@

1 2

GND

Realtek:Mount R519,Remove R550 R534

GND

12

12

C515

C515

C514

C514

0.1UF/10V

0.1UF/10V

10UF/10V

10UF/10V

GND

GND

+3VS_CLK

+3VS_CLK

+3VS_CLK

C520 10PF/50V@C520 10PF/50V

C518 10PF/50V@C518 10PF/50V

@

C521 10PF/50V@C521 10PF/50V

C522 10PF/50V@C522 10PF/50V

C523 10PF/50V@C523 10PF/50V

C519 10PF/50V@C519 10PF/50V

@

@

@

@

1 2

1 2

1 2

1 2

1 2

4

R501

@R501

@

@R503

@

@R504

@

@R506

@

+3VS_CLK

4

12

12

12

12

12

GND

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

R558

R558

475Ohm

475Ohm

1KOhm

1KOhm

R503

1KOhm

1KOhm

R504

1KOhm

1KOhm

R506

1KOhm

1KOhm

R517

R517

2.2Ohm

2.2Ohm

R530 33OhmR530 33Ohm

1 2

R532 33OhmR532 33Ohm

1 2

R535 33OhmR535 33Ohm

1 2

R536 2.2KOhmR536 2.2KOhm

1 2

R539 33OhmR539 33Ohm

1 2

R540 10KOhmR540 10KOhm

1 2

R541 33OhmR541 33Ohm

1 2

R544 33OhmR544 33Ohm

1 2

R546 33OhmR546 33Ohm

1 2

R548 10KOhmR548 10KOhm

1 2

R550 10KOhmR550 10KOhm

1 2

R552 33OhmR552 33Ohm

1 2

R553 10KOhmR553 10KOhm

1 2

1 2

GND

R502 0OhmR502 0Ohm

1 2

R505 0OhmR505 0Ohm

1 2

R507 0OhmR507 0Ohm

1 2

Pin34 is PWRSAVE#

+3VS_VDDA

ICS_X1

ICS_X2

LCD_SSCG

LCD_SSCG#

FSA

PCICLK5

PCICLK4

PCICLK3

PCICLK2

PCICLK_F0

ICS_IREF

GND

MCH_BSEL0 7

MCH_BSEL1 7

MCH_BSEL2 7

+3VS

12

12

0.1UF/10V

0.1UF/10V

GND

U501

U501

21

VDDPCIEX1

28

VDDPCIEX2

42

VDDPCIEX3

34

VDD

50

VDDCPU

45

VDDA

46

GNDA

58

X1

57

X2

17

27FIX/LCD_SSCGT/PCIEX0T

18

27SS/LCD_SSCGC/PCIEX0C

12

FSLA/USB_48MHz

16

FSLB/TEST_MODE

5

SELPCIEX0_LCD#PCICLK5

4

PCICLK4

3

PCICLK3

64

PCICLK2/REQ_SEL

9

SELLCD_27#/PCICLK_F1

8

ITP_EN/PCICLK_F0

54

SCLK

55

SDATA

47

IREF

2

GND1

6

GND2

13

GND3

29

GND4

37

GND5

53

GND6

59

GND7

ICS954310CGLFT

ICS954310CGLFT

C501

C501

C502

C502

0.1UF/10V

0.1UF/10V

1

VDDPCI1

internal

pull high

Internal Pull-Up Resistor

Internal Pull-Down Resistor

3

FSLC FSLB FSLA

Bclk BSEL0

FSB

133

533

166

667

L501

L501

21

120Ohm/100Mhz

120Ohm/100Mhz

21

L502

L502

120Ohm/100Mhz

120Ohm/100Mhz

+3VS_VDDPCI

7

VDDPCI2

CPUCLKT2_ITP/PCIEXT8

CPUCLKC2_ITP/PCIEXC8

REF1/FSLC/TEST_SEL

3

12

12

C508

C508

0.1UF/10V

0.1UF/10V

0.1UF/10V

0.1UF/10V

VDD48

VDDREF

PCI/PCIEX_STOP#

CPU_STOP#

CPUCLKT1

CPUCLKC1

CPUCLKT0

CPUCLKC0

PEREQ1#/PCIEXT7

PEREQ2#/PCIEXC7

PCIEXT6

PCIEXC6

PCIEXT5

PCIEXC5

PCIEXT4

PCIEXC4

PCIEXT3

PCIEXC3

PCIEXT2

PCIEXC2

PCIEXT1

PCIEXC1

SATACLKT

SATACLKC

DOTT_96MHz

DOTC_96MHz

PEREQ3#

PEREQ4#

Vtt_PwrGd#/PD

REF0

C509

C509

BSEL1

BSEL2

L

LHHLH

+3VS_CLK

12

12

C504

C504

C503

C503

0.1UF/10V

0.1UF/10V

10UF/10V

10UF/10V

12

C510

C510

10UF/10V

10UF/10V

R513

R513

2.2Ohm

2.2Ohm

GND

+3VS_VDD48

11

+3VS_VDDREF

56

STP_PCI#

63

STP_CPU#

62

CLK_CPU

49

CLK_CPU#

48

CLK_MCH

52

CLK_MCH#

51

44

43

PEREQ#1

41

PEREQ#2

40

PCIE6

R537 33OhmR537 33Ohm

39

PCIE#6

R538 33OhmR538 33Ohm

38

36

35

PCIE4

R542 33OhmR542 33Ohm

30

PCIE#4

R543 33OhmR543 33Ohm

31

PCIE3

R545 33OhmR545 33Ohm

24

PCIE#3

R547 33OhmR547 33Ohm

25

PCIE2

R549 33OhmR549 33Ohm

22

PCIE#2

R551 33OhmR551 33Ohm

23

19

20

CLK_SATA

26

CLK_SATA#

27

DOT96

R556 33OhmR556 33Ohm

14

DOT96#

R557 33OhmR557 33Ohm

15

32

33

10

REF1

61

60

R563 2.2KOhmR563 2.2KOhm

REF0

R564 33OhmR564 33Ohm

+3VS_CLK

12

12

12

C506

C506

C505

C505

0.1UF/10V

0.1UF/10V

1 2

R526 33OhmR526 33Ohm

1 2

R527 33OhmR527 33Ohm

1 2

R523 33OhmR523 33Ohm

1 2

R524 33OhmR524 33Ohm

1 2

R531 10KOhmR531 10KOhm

R533 0OhmR533 0Ohm

R534 10KOhmR534 10KOhm

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

R554 33OhmR554 33Ohm

R555 33OhmR555 33Ohm

1 2

1 2

0.1UF/10V

0.1UF/10V

12

C511

C511

0.1UF/10V

0.1UF/10V

STP_PCI# 19

STP_CPU# 19,50

1 2

12

1 2

1 2

0.1UF/10V

0.1UF/10V

GND

12

10UF/10V

10UF/10V

GND

12

Remove 0ohm

1 2

1 2

2

+VCCP_AGTL+

+3VS

C507

C507

C512

C512

GND

CLK_PCIE_NEWCARD 25

CLK_PCIE_NEWCARD# 25

CLK_MCH_3GPLL 7

CLK_MCH_3GPLL# 7

CLK_PCIE_MINICARD 26

CLK_PCIE_MINICARD# 26

CLK_PCIE_ICH 18

CLK_PCIE_ICH# 18

CLK_UMA_96M 7

CLK_UMA_96M# 7

MCH_CLK_REQ# 7

CLK_MINICARD_REQ# 26

CPU_BSEL2 2

CLK_ICH14 19

2

R514

R514

1Ohm

1Ohm

1 2

C513

C513

1 2

0.1UF/10V

0.1UF/10V

CLK_CPU_BCLK 2

CLK_CPU_BCLK# 2

CLK_MCH_BCLK 6

CLK_MCH_BCLK# 6

+3VS

CLK_NEWCARD_REQ# 25

CLK_PCIE_SATA 17

CLK_PCIE_SATA# 17

1

+VCCP_AGTL+ 2,3,6,9

+3VS 4,7,9,11,12,13,14,15,19,20,21,22,25,26,27,28,29,30,33,37,40,43,50,52,60,61

Layout Note:

Place termination close to source IC

GND

CLK_MCH_BCLK

CLK_MCH_BCLK#

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_LCD_SSCG

CLK_LCD_SSCG#

CLK_UMA_96M

CLK_UMA_96M#

CLK_PCIE_MINICARD

CLK_PCIE_MINICARD#

CLK_PCIE_NEWCARD

CLK_PCIE_NEWCARD#

CLK_PCIE_SATA

CLK_PCIE_SATA#

R508 49.9Ohm

R508 49.9Ohm

1 2

R509 49.9Ohm

R509 49.9Ohm

1 2

R510 49.9Ohm

R510 49.9Ohm

1 2

R511 49.9Ohm

R511 49.9Ohm

1 2

R512 49.9Ohm

R512 49.9Ohm

1 2

R515 49.9Ohm

R515 49.9Ohm

1 2

R516 49.9Ohm

R516 49.9Ohm

1 2

R518 49.9Ohm

R518 49.9Ohm

1 2

R519 49.9Ohm

R519 49.9Ohm

1 2

R521 49.9Ohm

R521 49.9Ohm

1 2

R522 49.9Ohm

R522 49.9Ohm

1 2

R525 49.9Ohm

R525 49.9Ohm

1 2

R528 49.9Ohm

R528 49.9Ohm

1 2

R529 49.9Ohm

R529 49.9Ohm

1 2

R566 49.9Ohm

R566 49.9Ohm

1 2

R567 49.9Ohm

R567 49.9Ohm

1 2

R568 49.9Ohm

R568 49.9Ohm

1 2

R569 49.9Ohm

R569 49.9Ohm

1 2

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

r0402

PREQ#1

0=PCIEX 6/0 Not Controlled

1=PCIEX 6/0 Controlled

PREQ#2

0=PCIEX 8/1 Not Controlled

1=PCIEX 8/1 Controlled

+3VS_CLK

12

PREQ#3

0=PCIEX 4/2 Not Controlled

1=PCIEX 4/2 Controlled

R560

R560

10KOhm

10KOhm

@

@

CLK_EN# 50

PREQ#4

0=PCIEX 7/5/3 Not Controlled

1=PCIEX 7/5/3 Controlled

Title :

Title :

Title :

Engineer:

Engineer:

ASUSALPHATeK COMPUTER INC.

ASUSALPHATeK COMPUTER INC.

ASUSALPHATeK COMPUTER INC.

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

TERESA

TERESA

TERESA

Engineer:

1

CLOCK GEN

CLOCK GEN

CLOCK GEN

Horng Chou

Horng Chou

Horng Chou

557Monday, February 05, 2007

557Monday, February 05, 2007

557Monday, February 05, 2007

of

of

of

GND

Rev

Rev

Rev

1.1

1.1

1.1

5

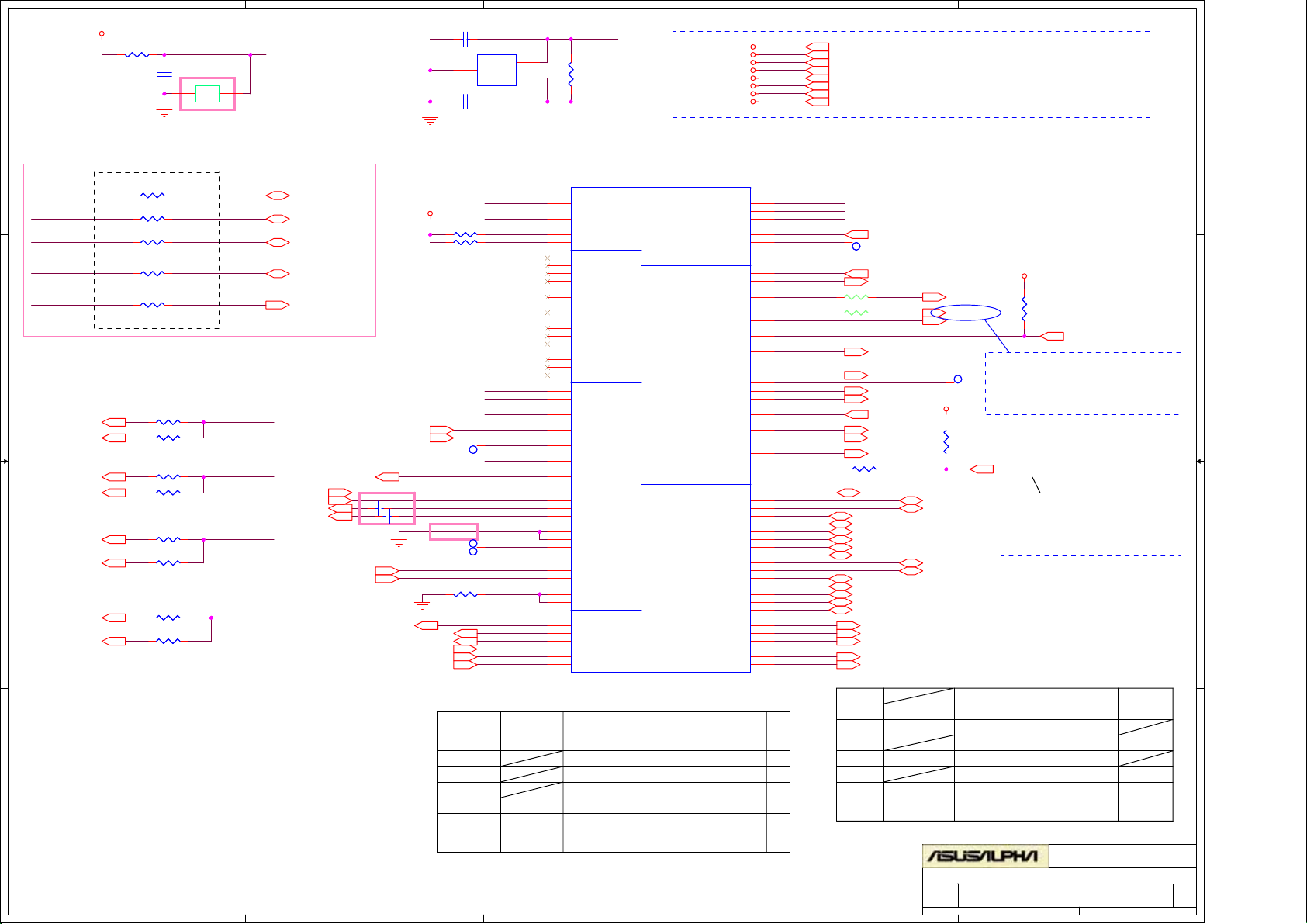

H_D#[0..63]2 H_A#[31..3] 2

U601A

H_D#0

H_D#1

H_D#2

H_D#3

5

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

CLK_MCH_BCLK

CLK_MCH_BCLK#

D D

C C

B B

CLK_MCH_BCLK5

A A

CLK_MCH_BCLK#5

U601A

F1

J1

H1

J6

H3

K2

G1

G2

K9

K1

K7

J8

H4

J3

K11

G4

T10

W11

T3

U7

U9

U11

T11

W9

T1

T8

T4

W7

U5

T9

W6

T5

AB7

AA9

W4

W3

Y3

Y7

W5

Y10

AB8

W2

AA4

AA7

AA2

AA6

AA10

Y8

AA1

AB4

AC9

AB11

AC11

AB3

AC2

AD1

AD9

AC1

AD7

AC6

AB5

AD10

AD4

AC8

E1

E2

E4

Y1

U1

W1

AG2

AG1

CALISTOGA_Q137

CALISTOGA_Q137

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

H_CLKIN

H_CLKIN#

HOST

HOST

4

H_ADSTB#_0

H_ADSTB#_1

H_CPURST#

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_SLPCPU#

4

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_ADS#

H_AVREF

H_BNR#

H_BPRI#

H_BREQ#0

H_DBSY#

H_DEFER#

H_DPWR#

H_DRDY#

H_DVREF

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_HIT#

H_HITM#

H_LOCK#

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_TRDY#

H9

C9

E11

G11

F11

G12

F9

H11

J12

G14

D9

J14

H13

J15

F14

D12

A11

C11

A12

A13

E13

G13

F12

B12

B14

C12

A14

C14

D14

E8

B9

C13

J13

C6

F6

C7

B7

A7

C3

J9

H8

K13

J7

W8

U3

AB10

K4

T7

Y5

AC4

K3

T6

AA5

AC5

D3

D4

B3

D8

G8

B8

F8

A8

B4

E6

D6

E3

E7

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_ADS#

H_ADSTB#0

H_ADSTB#1

H_VREF

H_BNR#

H_BPRI#

H_BR0#

H_CPURST#

H_DBSY#

H_DEFER#

H_DPWR#

H_DRDY#

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_HIT#

H_HITM#

H_LOCK#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

N_CPUSLP#

H_TRDY#

H_ADS# 2

H_ADSTB#0 2

H_ADSTB#1 2

H_BNR# 2

H_BPRI# 2

H_BR0# 2

H_CPURST# 2

H_DBSY# 2

H_DEFER# 2

H_DPWR# 2

H_DRDY# 2

H_DINV#0 2

H_DINV#1 2

H_DINV#2 2

H_DINV#3 2

H_DSTBN#0 2

H_DSTBN#1 2

H_DSTBN#2 2

H_DSTBN#3 2

H_DSTBP#0 2

H_DSTBP#1 2

H_DSTBP#2 2

H_DSTBP#3 2

H_HIT# 2

H_HITM# 2

H_LOCK# 2

R611

R611

0Ohm

0Ohm

12

3

+VCCP_AGTL+

<500 mil (55 Ohm)

T/B trace 5.5 ,

Space 25

12

C601

C601

0.1UF/10V

0.1UF/10V

GND

GND

R601

R601

100Ohm

100Ohm

1%

1%

1 2

R606

R606

200Ohm

200Ohm

1%

1%

1 2

Layout Note:

0.1uF should be placed 100mils or

less from GMCH pin.

H_REQ#[4..0] 2

H_RS#[0..2] 2

H_CPUSLP# 2,17

H_TRDY# 2

3

+VCCP

GND

+VCCP

GND

+VCCP

GND

2

R602

R602

54.9Ohm

54.9Ohm

1%

1%

1 2

H_XSCOMP

H_XRCOMP

R604

R604

24.9Ohm

24.9Ohm

1%

1%

1 2

R607

R607

221Ohm

221Ohm

1%

1%

1 2

R608

R608

100Ohm

100Ohm

1%

1%

1 2

R609

R609

221Ohm

221Ohm

1%

1%

1 2

R610

R610

100Ohm

100Ohm

1%

1%

1 2

2

+VCCP

+VCCP_AGTL+

+VCCP

R603

R603

54.9Ohm

54.9Ohm

1%

1%

1 2

H_YSCOMP

H_YRCOMP

1 2

GND

10/20mils

R605

R605

24.9Ohm

24.9Ohm

1%

1%

GND

5.5/20 mils

10/20mils

H_XSWING

12

C602

C602

0.1UF/10V

0.1UF/10V

Signal voltage level =

0.3125*VCCP

Trace should be 10 mil wide

with 20 mil spacing

H_YSWING

12

C603

C603

0.1UF/10V

0.1UF/10V

GND

ASUSALPHATeK COMPUTER INC.

ASUSALPHATeK COMPUTER INC.

ASUSALPHATeK COMPUTER INC.

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

TERESA

TERESA

TERESA

1

+VCCP 2,9,20,52

+VCCP_AGTL+ 2,3,5,9

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

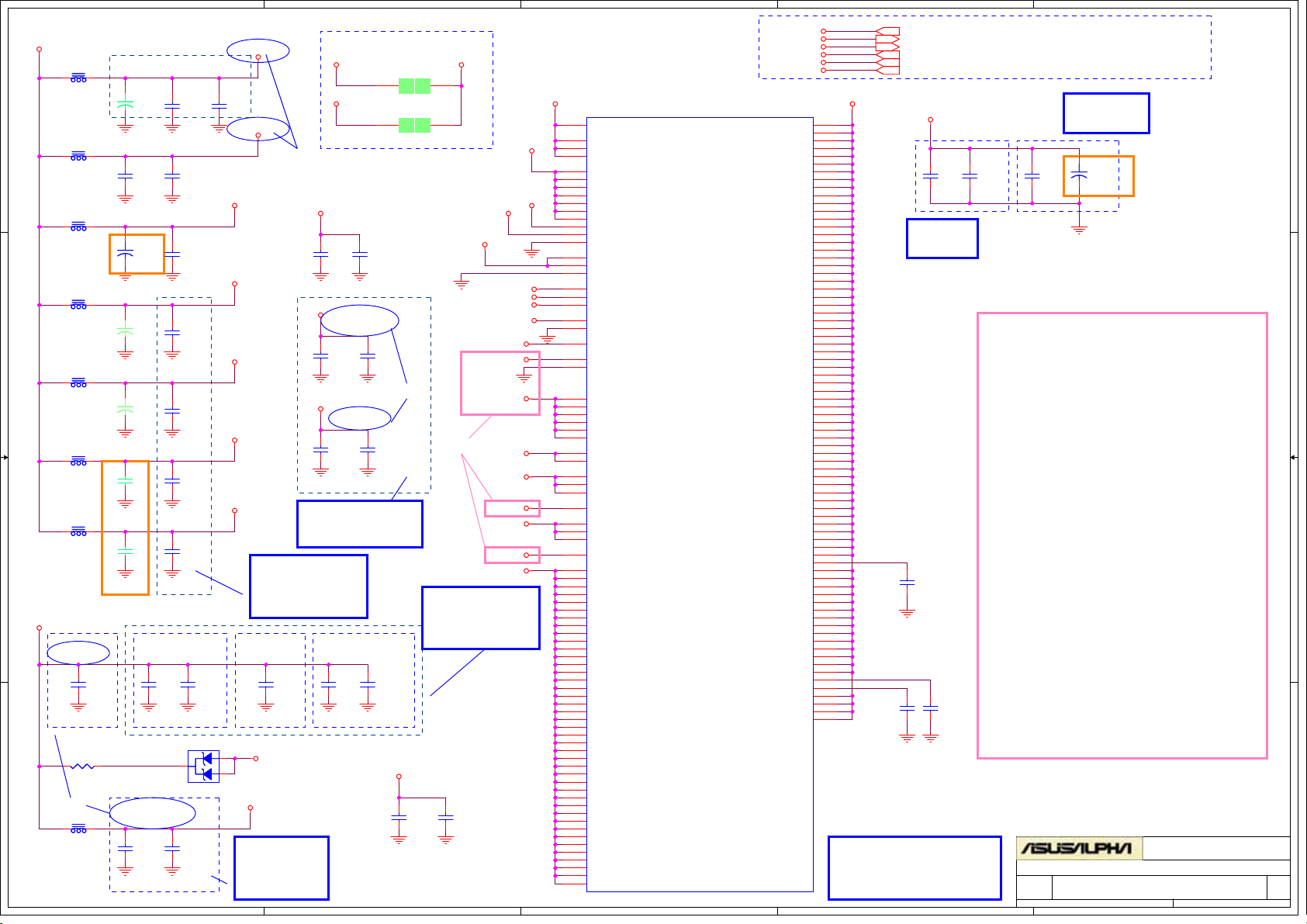

Calistoga GMCH (1)

Calistoga GMCH (1)

Calistoga GMCH (1)

Horng Chou

Horng Chou

Horng Chou

657Monday, February 05, 2007

657Monday, February 05, 2007

657Monday, February 05, 2007

Rev

Rev

Rev

1.1

1.1

1.1

of

of

of

5

4

3

2

1

+1.5VS_PCIE

R702

+3VS

L_BKLTCTL12

R703 10KOhmR703 10KOhm

1 2

R704 10KOhmR704 10KOhm

1 2

R705 10KOhmR705 10KOhm

1 2

R706 10KOhmR706 10KOhm

1 2

D D

R710

R710

100KOhm

100KOhm

1 2

GND

R707

R707

1.5KOhm

1.5KOhm

1%

1%

L_BKLTEN

GND

T702T702

12

GND

1

L_BKLTCTL

L_BKLTEN

L_CTLA_CLK

L_CTLB_DATA

EDID_CLK

EDID_DAT

L_IBG

L_VBG

L_VDDEN

L_VREFH

L_VREFL

LVDS_LCLKN

LVDS_LCLKP

LVDS_L0N

LVDS_L1N

LVDS_L2N

LVDS_L0P

LVDS_L1P

LVDS_L2P

Remove LVDS channel B

C C

+1.5VS

TV OUT disable way

R720 150Ohm

R720 150Ohm

R721 150Ohm

R721 150Ohm

R722 150Ohm

R722 150Ohm

GND

B B

A A

DAC_HSYNC_GM

DAC_VSYNC_GM

LVDS_L0N

LVDS_L2N

LVDS_L0P

LVDS_L1P

LVDS_L2P

CRT_BLUE

12

1%

1%

CRT_GREEN

12

1%

1%

CRT_RED

12

1%

1%

CRT_DDC_CLK

CRT_DDC_DATA

R725

R725

255Ohm

255Ohm

1%

1%

LVDS_L0N 12

LVDS_L1N 12

LVDS_L2N 12

LVDS_L0P 12

LVDS_L1P 12

LVDS_L2P 12

CRT_IREF

12

GND

U601C

U601C

D32

J30

H30

H29

G26

G25

B38

C35

F32

C33

C32

A33

A32

E27

E26

C37

B35

A37

B37

B34

A36

G30

D30

F29

F30

D29

F28

A16

C18

A19

J20

B16

B18

B19

E23

D23

C22

B22

A21

B21

GND

C26

C25

G23

J22

H23

CALISTOGA_Q137

CALISTOGA_Q137

L_BKLTCTL

L_BKLTEN

L_CLK_CTLA

L_DATA_CTLB

L_DDC_CLK

L_DDC_DATA

L_IBG

L_VBG

L_VDDEN

L_VREFH

L_VREFL

LA_CLK#

LA_CLK

LB_CLK#

LB_CLK

LA_DATA#_0

LA_DATA#_1

LA_DATA#_2

LA_DATA_0

LA_DATA_1

LA_DATA_2

LB_DATA#_0

LB_DATA#_1

LB_DATA#_2

LB_DATA_0

LB_DATA_1

LB_DATA_2

TV_DACA_OUT

TV_DACB_OUT

TV_DACC_OUT

TV_IREF

TV_IRTNA

TV_IRTNB

TV_IRTNC

CRT_BLUE

CRT_BLUE#

CRT_GREEN

CRT_GREEN#

CRT_RED

CRT_RED#

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_IREF

CRT_VSYNC

LVDS_LCLKN

LVDS_LCLKPLVDS_L1N

L_BKLTEN

EDID_CLK

EDID_DAT

L_VDDEN

LVDS

LVDS

TV

TV

VGA

VGA

LVDS_LCLKN 12

LVDS_LCLKP 12

L_BKLTEN 12

EDID_CLK 12

EDID_DAT 12

L_VDDEN 12

EXP_A_COMP

EXP_A_COMPI

EXP_A_COMPO

EXP_A_RXN_0

EXP_A_RXN_1

EXP_A_RXN_2

EXP_A_RXN_3

EXP_A_RXN_4

EXP_A_RXN_5

EXP_A_RXN_6

EXP_A_RXN_7

EXP_A_RXN_8

EXP_A_RXN_9

EXP_A_RXN_10

EXP_A_RXN_11

EXP_A_RXN_12

EXP_A_RXN_13

EXP_A_RXN_14

EXP_A_RXN_15

EXP_A_RXP_0

EXP_A_RXP_1

EXP_A_RXP_2

EXP_A_RXP_3

EXP_A_RXP_4

EXP_A_RXP_5

EXP_A_RXP_6

EXP_A_RXP_7

EXP_A_RXP_8

EXP_A_RXP_9

EXP_A_RXP_10

EXP_A_RXP_11

EXP_A_RXP_12

EXP_A_RXP_13

EXP_A_RXP_14

EXP_A_RXP_15

EXP_A_TXN_0

EXP_A_TXN_1

EXP_A_TXN_2

EXP_A_TXN_3

EXP_A_TXN_4

EXP_A_TXN_5

EXP_A_TXN_6

EXP_A_TXN_7

EXP_A_TXN_8

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

EXP_A_TXN_9

EXP_A_TXN_10

EXP_A_TXN_11

EXP_A_TXN_12

EXP_A_TXN_13

EXP_A_TXN_14

EXP_A_TXN_15

EXP_A_TXP_0

EXP_A_TXP_1

EXP_A_TXP_2

EXP_A_TXP_3

EXP_A_TXP_4

EXP_A_TXP_5

EXP_A_TXP_6

EXP_A_TXP_7

EXP_A_TXP_8

EXP_A_TXP_9

EXP_A_TXP_10

EXP_A_TXP_11

EXP_A_TXP_12

EXP_A_TXP_13

EXP_A_TXP_14

EXP_A_TXP_15

D40

D38

F34

G38

H34

J38

L34

M38

N34

P38

R34

T38

V34

W38

Y34

AA38

AB34

AC38

D34

F38

G34

H38

J34

L38

M34

N38

P34

R38

T34

V38

W34

Y38

AA34

AB38

F36

G40

H36

J40

L36

M40

N36

P40

R36

T40

V36

W40

Y36

AA40

AB36

AC40

D36

F40

G36

H40

J36

L40

M36

N40

P36

R40

T36

V40

W36

Y40

AA36

AB40

CRT_RED

CRT_GREEN

CRT_BLUE

DAC_HSYNC_GM

DAC_VSYNC_GM

CRT_DDC_CLK

CRT_DDC_DATA

R702

1 2

24.9Ohm

24.9Ohm

1%

1%

PM_DPRSLPVR19,50

CRT_RED 13

CRT_GREEN 13

CRT_BLUE 13

CRT_DDC_CLK 13

CRT_DDC_DATA 13

U601B

U601B

T32

RSVD_1

R32

RSVD_2

F3

+3VS

R708

R708

10KOhm

10KOhm

R709

R709

10KOhm

10KOhm

R718 0Ohm

R718 0Ohm

1 2

PM_EXTTS#0

PM_EXTTS#1

T703T703

T701T701

T704T704

T705T705

T706T706

T707T707

T708T708

T709T709

T710T710

T711T711

T712T712

@

@

MCH_BSEL0

MCH_BSEL1

MCH_BSEL2

MCH_CFG_3

1

MCH_CFG_4

1

MCH_CFG_5

MCH_CFG_6

1

MCH_CFG_7

MCH_CFG_8

1

MCH_CFG_9

MCH_CFG_10

1

MCH_CFG_11

MCH_CFG_12

1

MCH_CFG_13

1

MCH_CFG_14

1

MCH_CFG_15

1

MCH_CFG_16

MCH_CFG_17

1

MCH_CFG_18

MCH_CFG_19

MCH_CFG_20

1

PM_BMBUSY#

PM_EXTTS#0

PM_EXTTS#1

PM_THRMTRIP#

ICH_PWROK

RST_IN#_MCH

MCH_ICH_SYNC#

MCH_CLK_REQ#

1 2

1 2

MCH_BSEL05

MCH_BSEL15

MCH_BSEL25

MCH_CFG_511

MCH_CFG_711

MCH_CFG_911

MCH_CFG_1111

MCH_CFG_1611

MCH_CFG_1811

MCH_CFG_1911

PM_BMBUSY#19

GMCH_THRMTRIP#4

ICH_PWROK19,29

PLT_RST#18,19,25,26,28,29

MCH_ICH_SYNC#18

MCH_CLK_REQ#5

AG11

AF11

K30

A41

A35

A34

D28

D27

K16

K18

F18

E15

F15

E18

D19

D16

G16

E16

D15

G15

K15

C15

H16

G18

H15

K27

G28

F25

H26

AH33

AH34

H28

H27

K28

H32

C41

BA41

BA40

BA39

BA3

BA2

BA1

B41

AY41

AY1

AW41

AW1

A40

A39

F7

H7

J19

J29

J18

J25

J26

G6

D1

C1

B2

A4

A3

RSVD_3

RSVD_4

RSVD_5

RSVD_6

RSVD_7

RSVD_8

TV_DCONSEL_0

TV_DCONSEL_1

RSVD_11

RSVD_12

RSVD_13

RSVD_14

RSVD_15

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

PM_BMBUSY#

PM_EXTTS#_0

PM_EXTTS#_1

PM_THRMTRIP#

PWROK

RSTIN#

SDVO_CTRLCLK

SDVO_CTRLDATA

ICH_SYNC#

CLK_REQ#

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

CALISTOGA_Q137

CALISTOGA_Q137

RSVD

RSVD

CFG

CFG

PM

PM

MISC NC

MISC NC

DDR MUXINGCLK

DDR MUXINGCLK

DMI

DMI

(070123)Add 39ohm resisters

R715

R715

39Ohm

DAC_VSYNC_GM

DAC_HSYNC_GM

39Ohm

1 2

R716

R716

39Ohm

39Ohm

1 2

+3VS

M_VREF_MCH

+1.5VS

+1.5VS_PCIE

+1.8V

SM_CK_0

SM_CK_1

SM_CK_2

SM_CK_3

SM_CK#_0

SM_CK#_1

SM_CK#_2

SM_CK#_3

SM_CKE_0

SM_CKE_1

SM_CKE_2

SM_CKE_3

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_OCDCOMP_0

SM_OCDCOMP_1

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP#

SM_RCOMP

SM_VREF_0

SM_VREF_1

G_CLKIN#

G_CLKIN

D_REFCLKIN#

D_REFCLKIN

D_REFSSCLKIN#

D_REFSSCLKIN

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

+3VS 4,5,9,11,12,13,14,15,19,20,21,22,25,26,27,28,29,30,33,37,40,43,50,52,60,61

M_VREF_MCH 14,15,16

+1.5VS 9,10,20,25,26,37,52

+1.5VS_PCIE 9

+1.8V 10,14,15,16,37,53

M_CLK_DDR0

AY35

M_CLK_DDR1

AR1

M_CLK_DDR2

AW7

M_CLK_DDR3

AW40

M_CLK_DDR#0

AW35

M_CLK_DDR#1

AT1

M_CLK_DDR#2

AY7

M_CLK_DDR#3

AY40

M_CKE0

AU20

M_CKE1

AT20

M_CKE2

BA29

M_CKE3

AY29

M_CS#0

AW13

M_CS#1

AW12

M_CS#2

AY21

M_CS#3

AW21

M_OCDCOMP0

AL20

M_OCDCOMP1

AF10

M_ODT0

BA13

M_ODT1

BA12

M_ODT2

AY20

M_ODT3

AU21

M_RCOMP#

AV9

M_RCOMP

AT9

M_VREF_MCH

AK1

AK41

CLK_MCH_3GPLL#

AF33

CLK_MCH_3GPLL

AG33

CLK_UMA_96M#

A27

CLK_UMA_96M

A26

CLK_LCD_SSCG#

C40

CLK_LCD_SSCG

D41

DMI_TXN0

AE35

DMI_TXN1

AF39

DMI_TXN2

AG35

DMI_TXN3

AH39

DMI_TXP0

AC35

DMI_TXP1

AE39

DMI_TXP2

AF35

DMI_TXP3

AG39

DMI_RXN0

AE37

DMI_RXN1

AF41

DMI_RXN2

AG37

DMI_RXN3

AH41

DMI_RXP0

AC37

DMI_RXP1

AE41

DMI_RXP2

AF37

DMI_RXP3

AG41

DAC_VSYNC_BUF 28

DAC_HSYNC_BUF 28

M_CLK_DDR0 14

M_CLK_DDR1 14

M_CLK_DDR2 15

M_CLK_DDR3 15

M_CLK_DDR#0 14

M_CLK_DDR#1 14

M_CLK_DDR#2 15

M_CLK_DDR#3 15

M_CKE[0..3] 14,15,16

M_CS#[0..3] 14,15,16

M_ODT[0..3] 14,15,16

Layout Note:

Route as short as possible

R711 40.2Ohm @R711 40.2Ohm @

12

12

R712 40.2Ohm @R712 40.2Ohm @

R713 80.6Ohm 1%R713 80.6Ohm 1%

1 2

1 2

R714 80.6Ohm 1%R714 80.6Ohm 1%

GND

+1.8V

GND

CLK_MCH_3GPLL# 5

CLK_MCH_3GPLL 5

CLK_UMA_96M# 5

CLK_UMA_96M 5

CLK_LCD_SSCG# 5

CLK_LCD_SSCG 5

DMI_TXN[0..3] 18

DMI_TXP[0..3] 18

DMI_RXN[0..3] 18

DMI_RXP[0..3] 18

Title :

Title :

Title :

Calistoga PCI-E (2)

Calistoga PCI-E (2)

Calistoga PCI-E (2)

Horng Chou

Horng Chou

1

Horng Chou

757Monday, February 05, 2007

757Monday, February 05, 2007

757Monday, February 05, 2007

Rev

Rev

Rev

1.1

1.1

1.1

Engineer:

Engineer:

ASUSALPHATeK COMPUTER INC.

ASUSALPHATeK COMPUTER INC.

ASUSALPHATeK COMPUTER INC.

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

TERESA

TERESA

TERESA

Engineer:

5

D D

U601D

AJ35

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AK9

AN7

AK8

AK7

AP9

AN9

AT5

AL5

AY2

AW2

AP1

AN2

AV2

AT3

AN1

AL2

AG7

AF9

AG4

AF6

AG9

AH6

AF4

AF8

U601D

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

CALISTOGA_Q137

CALISTOGA_Q137

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

C C

B B

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

4

SA_BS_0

SA_BS_1

SA_BS_2

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

AU12

AV14

BA20

AY13

AJ33

AM35

AL26

AN22

AM14

AL9

AR3

AH4

AK33

AT33

AN28

AM22

AN12

AN8

AP3

AG5

AK32

AU33

AN27

AM21

AM12

AL8

AN3

AH5

AY16

AU14

AW16

BA16

BA17

AU16

AV17

AU17

AW17

AT16

AU13

AT17

AV20

AV12

AW14

AK23

AK24

AY14

M_A_BS#0

M_A_BS#1

M_A_BS#2

M_A_CAS#

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_RAS#

M_A_RCVENIN#

M_A_RCVENOUT#

M_A_WE#

M_A_DM[0..7] 14

M_A_DQS[0..7] 14

M_A_DQS#[0..7] 14

M_A_A[0..13] 14,16

M_A_DQ[0..63] 14

M_A_BS0 14,16

M_A_BS1 14,16

M_A_BS2 14,16

M_A_CAS# 14,16

T802T802

1

T801T801

1

M_A_WE# 14,16

3

U601E

AK39

AJ37

AP39

AR41

AJ38

AK38

AN41

AP41

AT40

AV41

AU38

AV38

AP38

AR40

AW38

AY38

BA38

AV36

AR36

AP36

BA36

AU36

AP35

AP34

AY33

BA33

AT31

AU29

AU31

AW31

AV29

AW29

AM19

AL19

AP14

AN14

AN17

AM16

AP15

AL15

AJ11

AH10

AN10

AK13

AH11

AK10

BA10

AW10

BA4

AW4

AY10

AY9

AW5

AY5

AV4

AR5

AK4

AK3

AT4

AK5

AJ9

AJ8

AJ5

AJ3

U601E

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

CALISTOGA_Q137

CALISTOGA_Q137

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

2

M_B_BS#0

AT24

SB_BS_0

SB_BS_1

SB_BS_2

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_MA_13

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

SB_WE#

AV23

AY28

AR24

AK36

AR38

AT36

BA31

AL17

AH8

BA5

AN4

AM39

AT39

AU35

AR29

AR16

AR10

AR7

AN5

AM40

AU39

AT35

AP29

AP16

AT10

AT7

AP5

AY23

AW24

AY24

AR28

AT27

AT28

AU27

AV28

AV27

AW27

AV24

BA27

AY27

AR23

AU23

AK16

AK18

AR27

M_B_BS#1

M_B_BS#2

M_B_CAS#

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_RAS#

M_B_RCVENIN#

M_B_RCVENOUT#

M_B_WE#

M_B_BS0 15,16

M_B_BS1 15,16

M_B_BS2 15,16

M_B_CAS# 15,16

T803T803

1

T804T804

1

M_B_DM[0..7] 15

M_B_DQS[0..7] 15

M_B_DQS#[0..7] 15

M_B_A[0..13] 15,16

M_B_DQ[0..63] 15

1

M_B_RAS# 15,16M_A_RAS# 14,16

M_B_WE# 15,16

A A

Title :

Title :

Title :

Calistoga DDR2 (3)

Calistoga DDR2 (3)

Calistoga DDR2 (3)

Horng Chou

Horng Chou

1

Horng Chou

857Monday, February 05, 2007

857Monday, February 05, 2007

857Monday, February 05, 2007

Rev

Rev

Rev

1.1

1.1

1.1

Engineer:

Engineer:

ASUSALPHATeK COMPUTER INC.

ASUSALPHATeK COMPUTER INC.

ASUSALPHATeK COMPUTER INC.

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

TERESA

TERESA

TERESA

Engineer:

5

Layout Note:

Place filter components

+1.5VS

close to GMCH

L902

L902

120Ohm/100Mhz

120Ohm/100Mhz

D D

L901

L901

30Ohm/100Mhz

30Ohm/100Mhz

L903

L903

80Ohm/100Mhz

80Ohm/100Mhz

(070131)

220UF=>150UF

L904

L904

30Ohm/100Mhz

30Ohm/100Mhz

C C

L906

L906

30Ohm/100Mhz

30Ohm/100Mhz

L907

L907

120Ohm/100Mhz

120Ohm/100Mhz

L908

L908

120Ohm/100Mhz

120Ohm/100Mhz

B B

Layout Note:

Caps should be on Top layer

21

12

+

+

CE902

CE902

150UF/4V

150UF/4V

@

@

GND

21

12

C904

C904

0.1UF/10V

0.1UF/10V

GND

21

12

+

+

CE903

CE903

150UF/4V

150UF/4V

GND

21

12

+

CE904

@+CE904

@

470UF/2.5V

470UF/2.5V

GND

21

12

+

CE905

@+CE905

@

470UF/2.5V

470UF/2.5V

GND

21

12

C923

C923

22UF/6.3V

22UF/6.3V

@

@

GND

21

12

C927

C927

22UF/6.3V

22UF/6.3V

@

@

GND

12

C902

C902

10UF/10V

10UF/10V

GND

12

10UF/10V

10UF/10V

GND

12

C909

C909

0.1UF/10V

0.1UF/10V

GND

12

C912

C912

0.1UF/10V

0.1UF/10V

GND

12

C918

C918

0.1UF/10V

0.1UF/10V