Page 1

5

4

3

2

1

http://hobi-elektronika.net

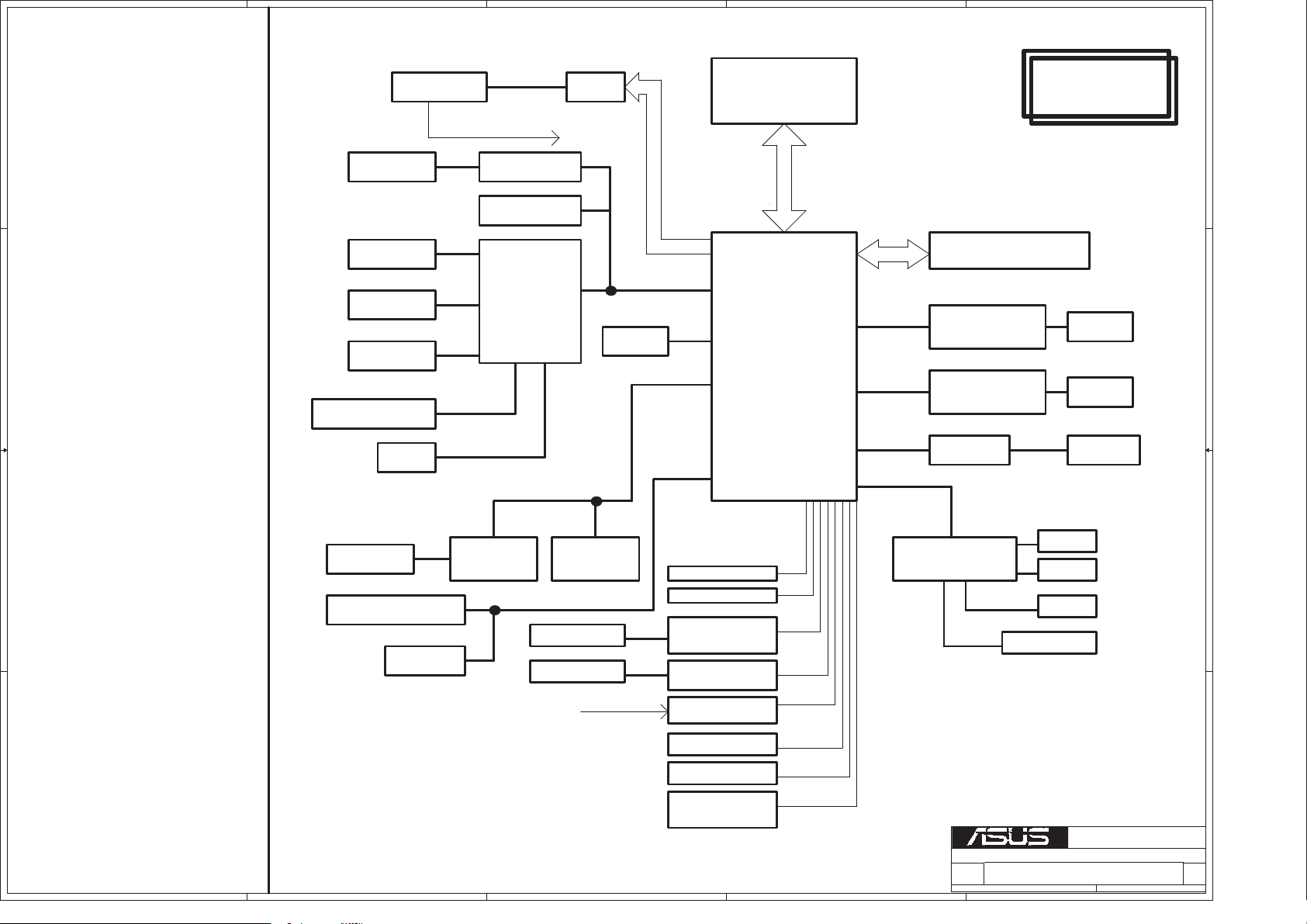

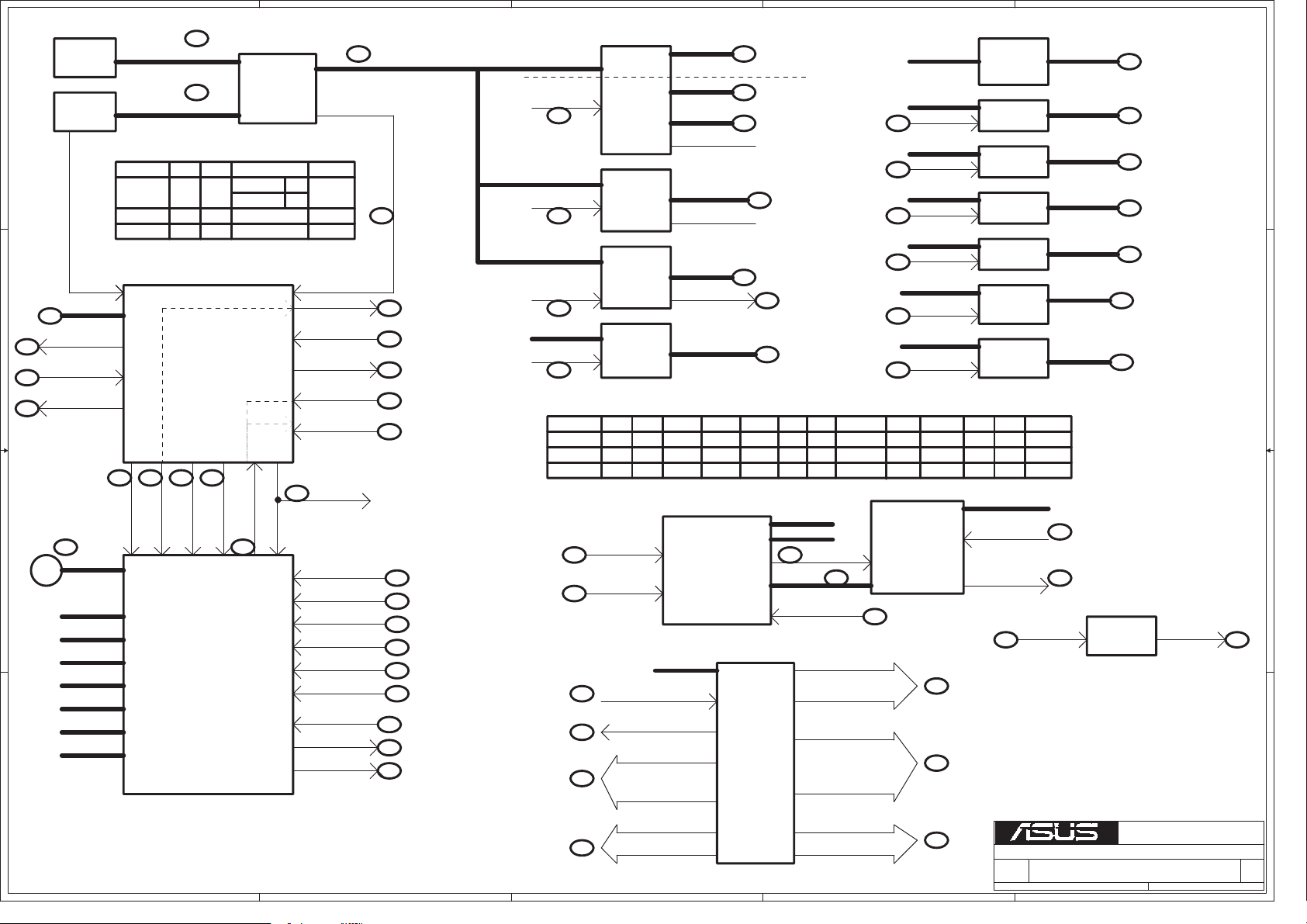

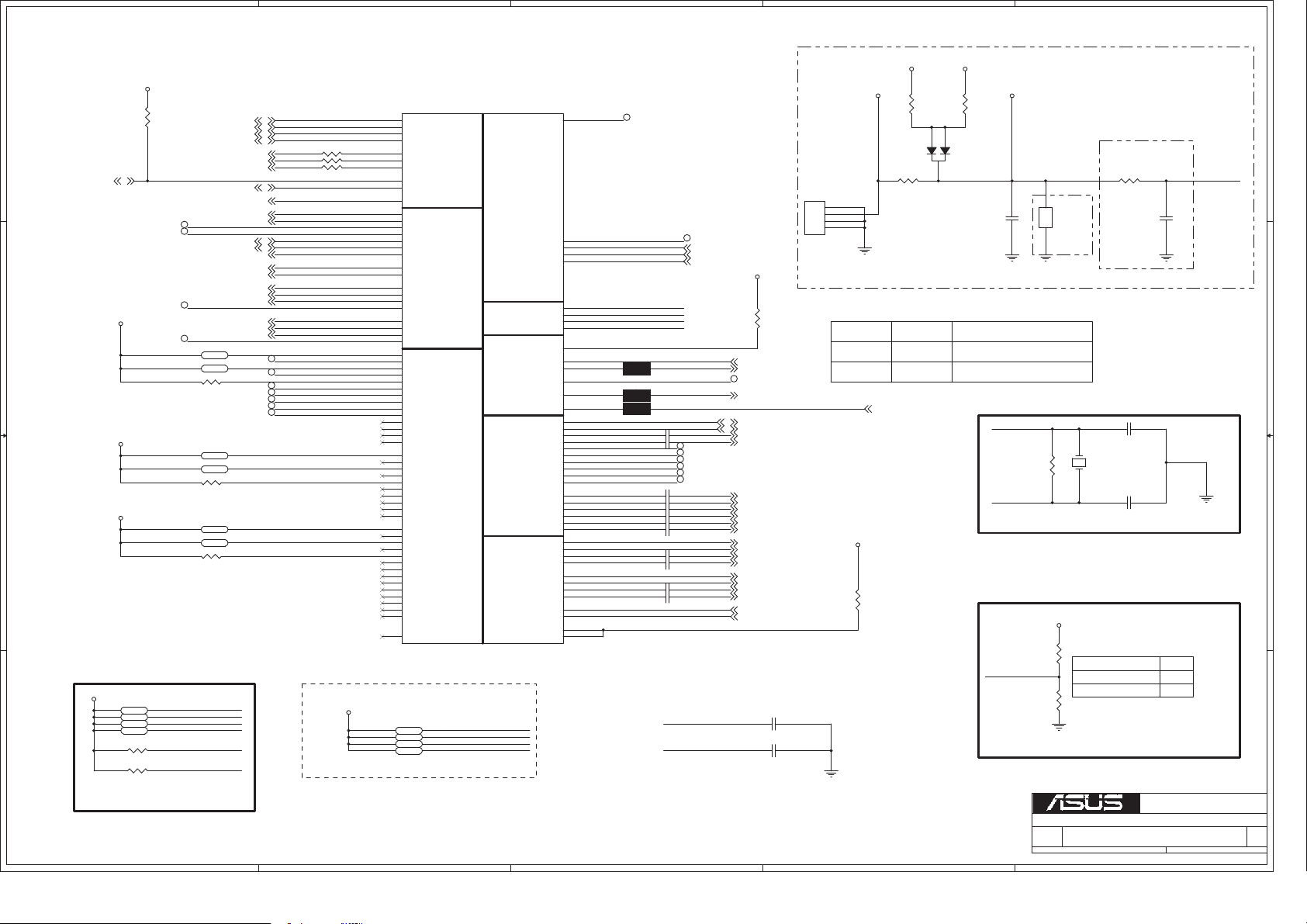

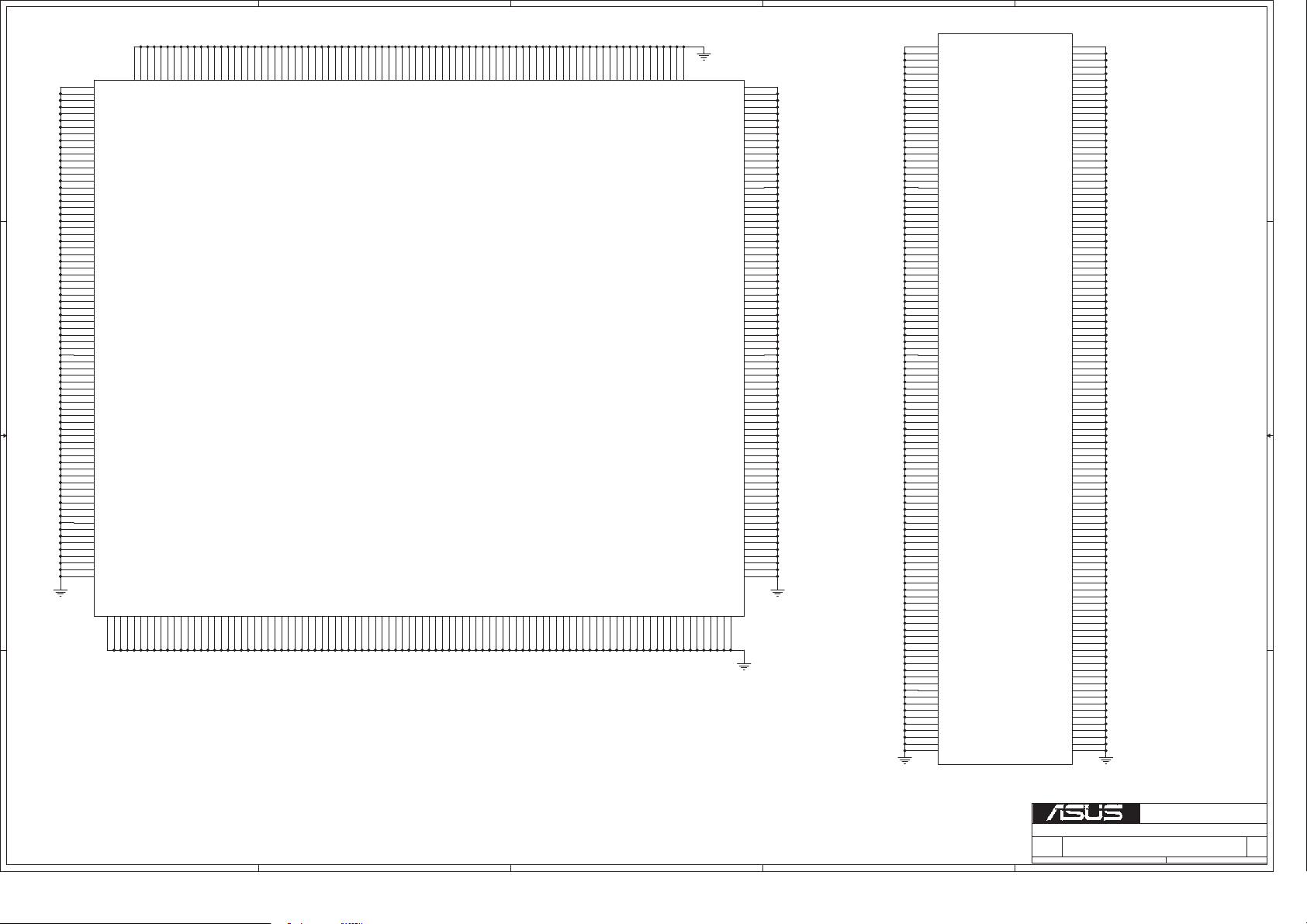

01_BLOCK DIAGRAM

02_SCH GPIO Setting

03_EC Pin Define

04_Power Sequrnse DC

05_Power Sequence AC

D D

06_Power Sequence Description

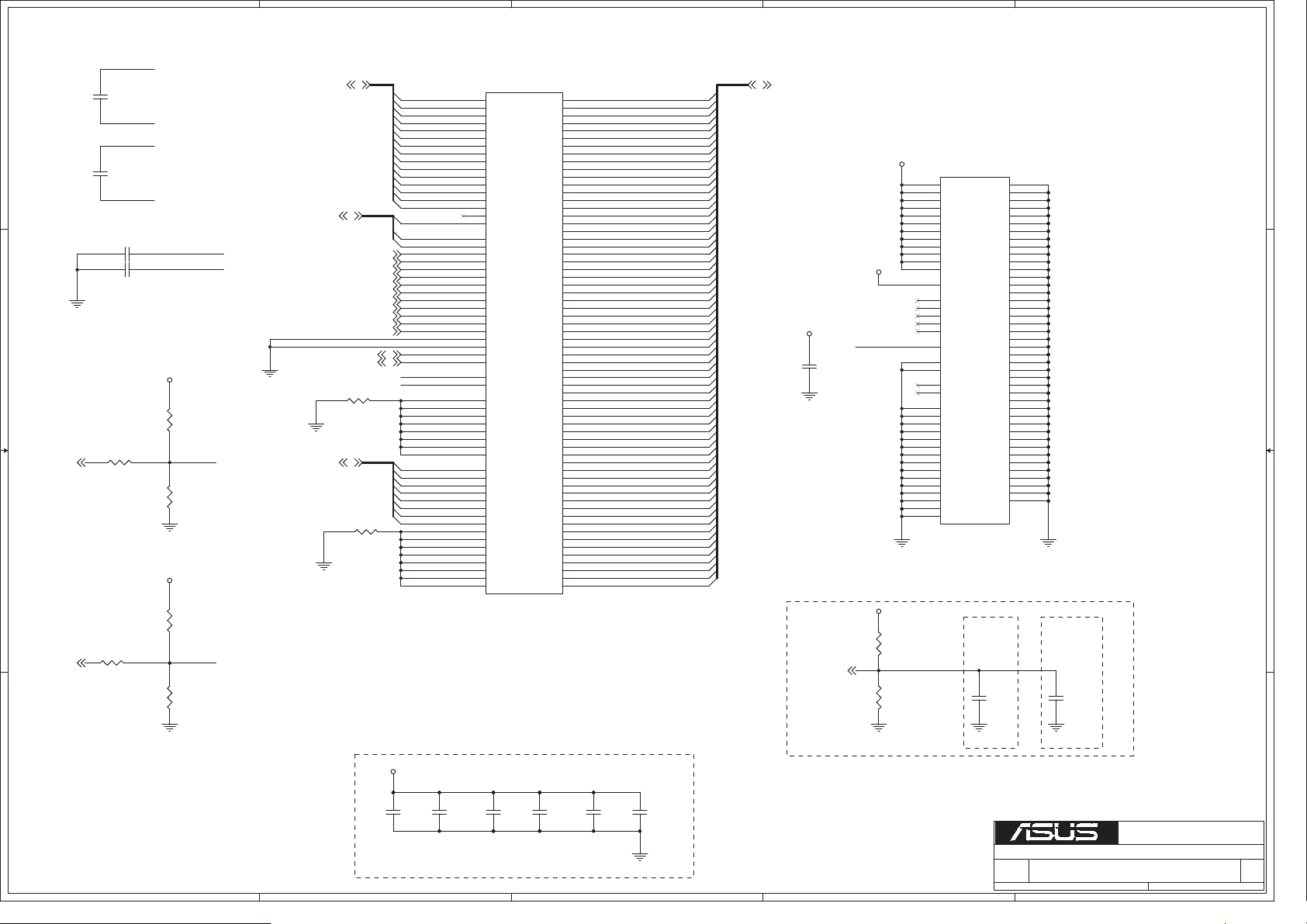

07_Clock Gen_ICS9LPR427

PANEL

TO TOUCH PANEL CONTROL

LVDS

08_CPU-SILVERTHORNE (1)

09_CPU-SILVERTHORNE (2)

Onboard GPS

LPC to UART

10_CPU-SILVERTHORNE (3)

11_SCH_Poulsbo_HOST (1)

12_SCH_Poulsbo_DDR2 (2)

Debug Conn

13_SCH_Poulsbo_LVDS/SDVO (3)

14_SCH_Poulsbo_PM/USB/IDE/AZ (4)

15_SCH_Poulsbo_STRAP(5)

SPI ROM 8M

16_SCH_Poulsbo_POWER (6)

17_SCH_Poulsbo_GND (7)

18_DDR2_SODIMM

19_DDR2_Termination

Keyboard

20_CH7317_SDVO_CRT

21_Onboard VGA

C C

22_LCD Conn_LID

Touch Pad

PS2

EC

ENE KB3310

LPC 33MHz

FM RADIO

Si4721

GPIO

(I2C)

23_PCIEx 3.5G & Ext. Antenna

24_Mini WIFI / BT

25_Bluetooth_BT253

26_FM_RADIO_Si4721

THERMAL SENSOR

SMBUS2

27_Onboard GPS

28_LAN_Atheros AR8113/AR8132

29_RJ45

30_Flash Conn

31_PATA_TO_SATA

32_USB Port

Battery

SMBUS1

SMBUS

IDE (ATA66/100)

33_Card Reader_AU6336C52

34_Camera Conn

35_Codec_ALC269

36_Audio Amp Jack

B B

37_EC_ENE KB3310

SATA SSD

38_EC_UART Contoller

39_SPI ROM_Debug Conn

40_Reset Map

CLOCK GEN ICS9LPR427

41_KB_Touch Pad

42_Thermal Sensor

43_Small_Board_Conn

44_G-Sensor

45_Discharge

46_PWR Jack

47_SCREW HOLE

SATA

G-Sensor

PATA TO SATA

JMH 330

PATA SSD

/X

SD Conn

SIM Card Conn

FROM PANEL

USB 2.0 Conn A

USB 2.0 Conn B

Card Reader

Alcor AU6336

DTV &3G module

Touch Panel

Controller

48_EMI

49_Power Flow

Bluetooth

50_Vcore

51_Power System

A A

52_Power_+1.8V & VTTDDR

53_Power_VCCP

54_Power_+1.5VS & +2.5VS

CameraConn.

2nd Card Reader

Alcor AU6336

55_Power_Charger

56_Power_Load Switch

57_Power Latch

5

4

3

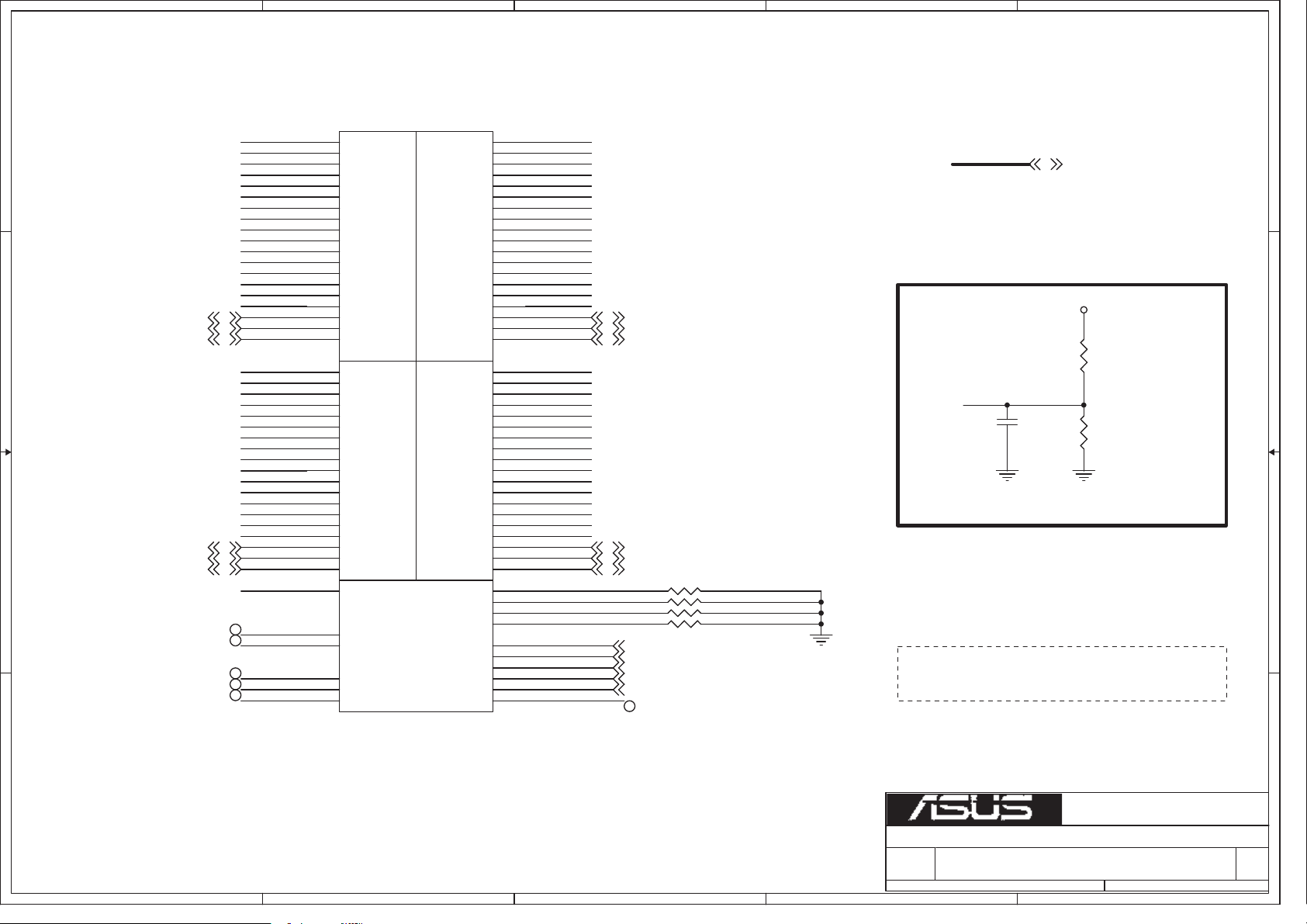

CPU

Silverthorne

441 Pins FCBGA8 14*13mm

FSB 400/533M HZ

Poulsbo

SCH

1249 Pins BGA 22*22mm

USB (0)

USB (1)

USB (2)

USB (3)

USB (4)

USB (5)

0.3M

USB (6)

USB (7)

DDR2

400/533M HZ 64Bits

PCIE _1

PCIE _2

SDVO

Azalia

AZALIA CODEC

ALC269

2

T91

SODIMM 200P

(1GB)

LAN

Atheros AR8132

MINICARD

0106 1025

ASUSTeK COMPUTER INC

Size Project Name

Custom

Tuesday, January 06, 2009

Date: Sheet of

16

CHIPs

CRT (RGB)

INT MIC

Speaker

MIC Jack

LINE OUT Jack

Title :

Engineer:

T91

RJ-45

WLAN

CRTCH7317

Block Diagram

1

1.2G

Jerry Liu

157

Rev

1.2G

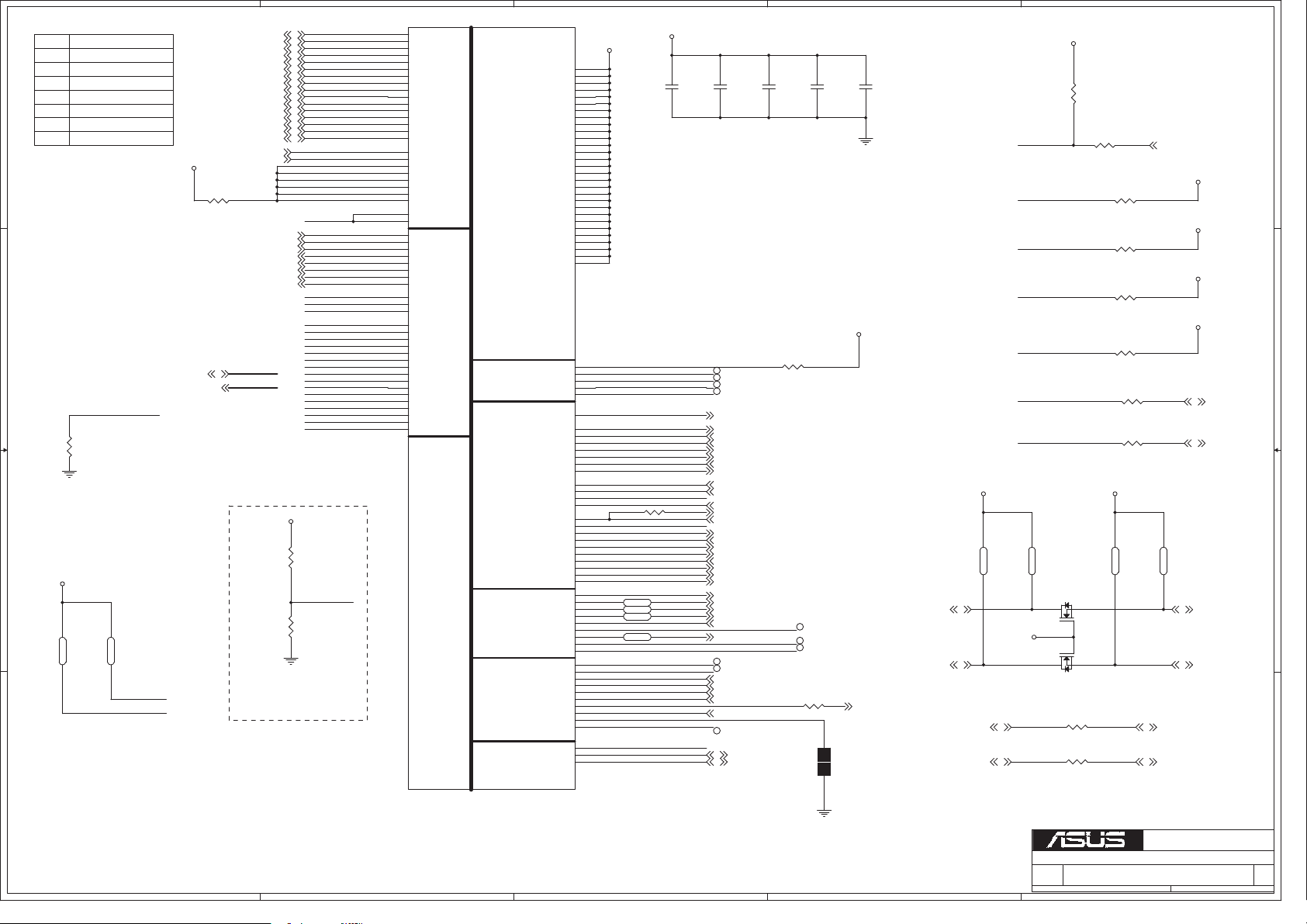

Page 2

5

4

3

2

1

http://hobi-elektronika.net

D D

C C

B B

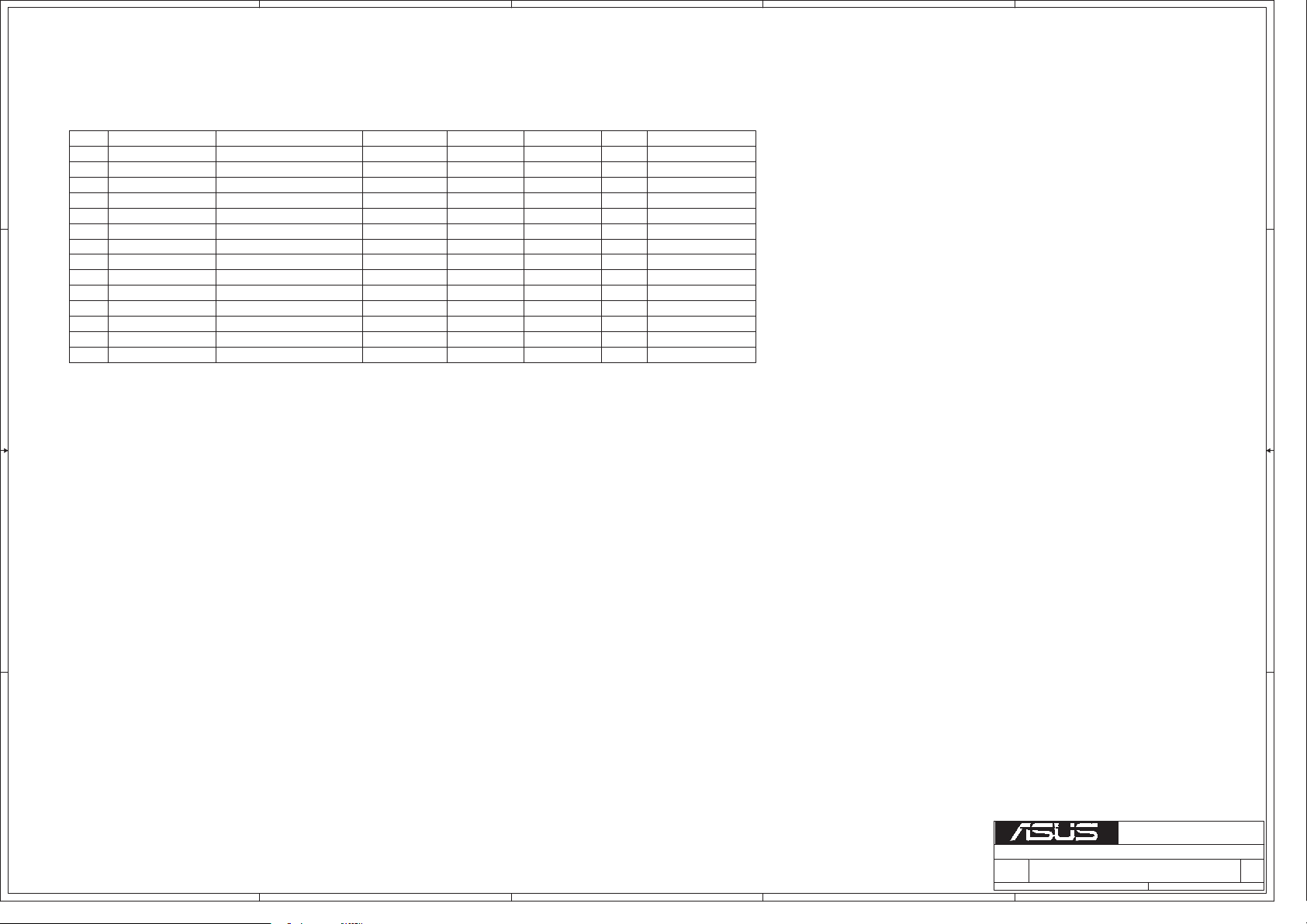

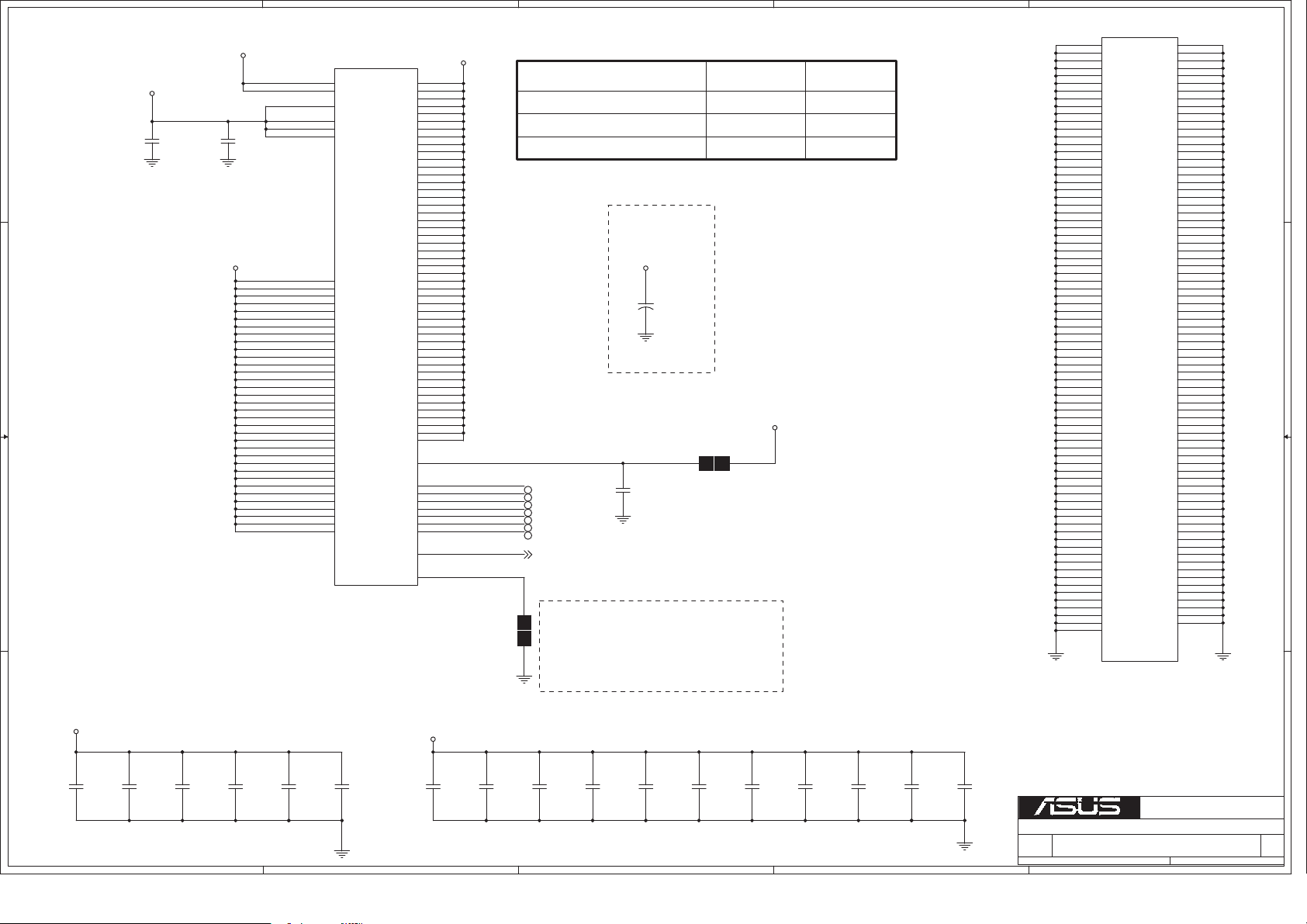

SCH GPIO SETTING

Pin

U41

N43

N45

R41

G29

K30

F34

G33

K36

H36

F36

J31

H34

K28

Pin Name

GPIOSUS1

GPIOSUS2

GPIOSUS3/ USBCC

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7/ SLPIOVR#

GPIO8/ PROCHOT#

GPIO9/ EXTTS1#

Connect to

PM_LEVELDOWN#

CPU_LEVELDOWN

PM_PWRBTN#

Test Point

Strap CMC/ BT_Disable

PCB ID

GPS_EN

Strap CMC

3GLAN_OFF

MINICARD_EN#

DDR_MEM_CONFIG

SLPIOVR#

CAMERA_EN Output

WLAN_LED

Type

I/O CMOS3.3GPIOSUS0

I/O CMOS3.3

I/O CMOS3.3

I/O CMOS3.3

I/O CMOS3.3

I/O CMOS3.3

I/O CMOS3.3

I/O CMOS3.3

I/O CMOS3.3

I/O CMOS3.3

I/O CMOS3.3

I/O CMOS3.3/ OD

I/O CMOS3.3

Power Well

Sus

Sus

Sus

Sus

Core

Core

Core

Core

Core

Core

Core

CoreI/O CMOS3.3

Core

Core

VIX-unknown

VIX-unknown

VIX-unknown

VIX-unknown

OFF

OFF

OFF

OFF

OFF

OFF

OFF OFF

OFF

OFF OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFFOFF

OFF

Input/Output SetS3 S4/ S5

Output

Input

Input

Input

Input

Input

Output

Input

Output

Output

Input

Output

Output

A A

0106 1025

SCH GPIO Setting

Title :

ASUSTek Computer INC.

Size Project Name

A3

5

4

3

2

Date: Sheet

T91

Engineer:

Jerry Liu

Rev

1

257Tuesday, January 06, 2009

1.2G

of

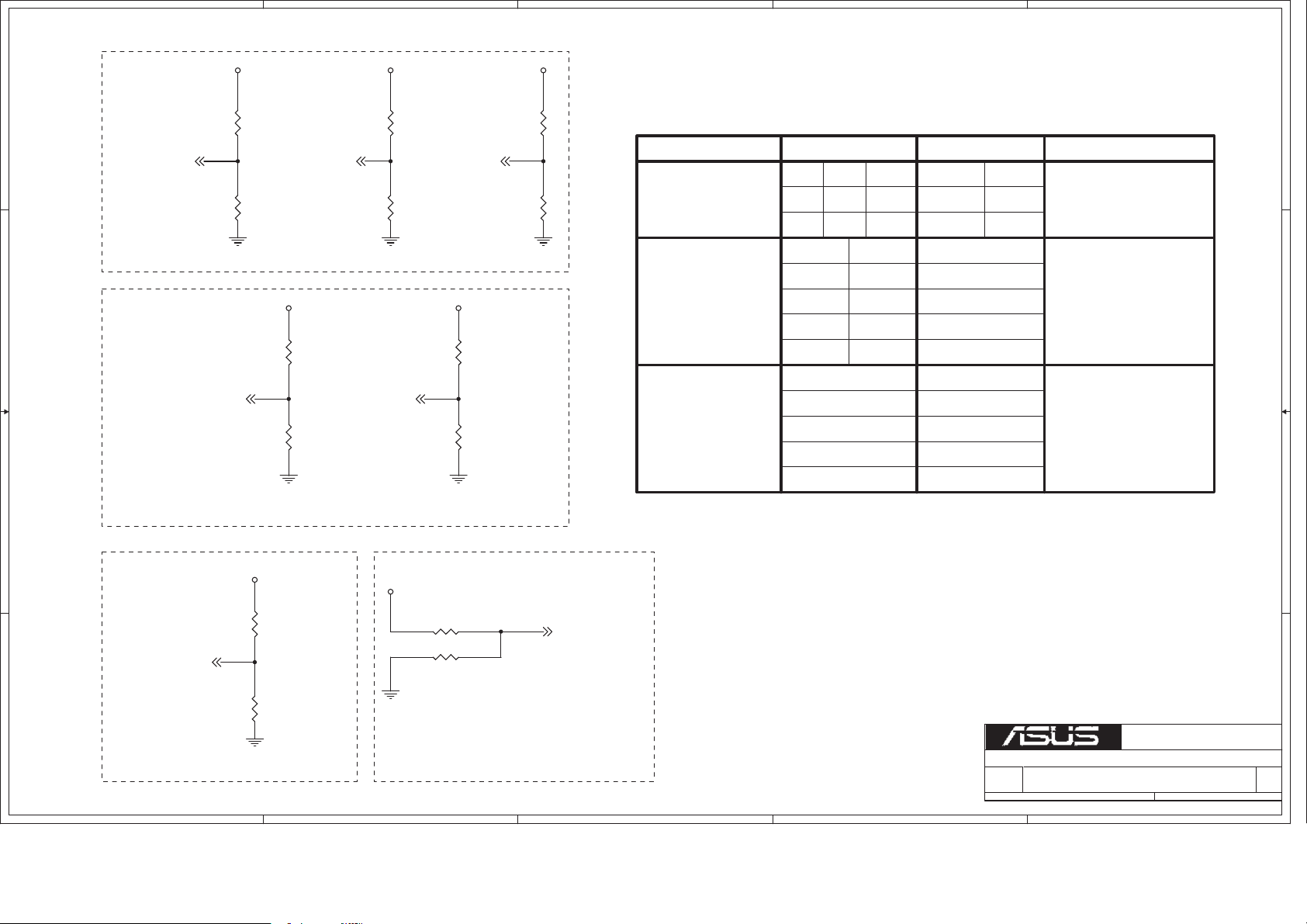

Page 3

5

4

3

2

1

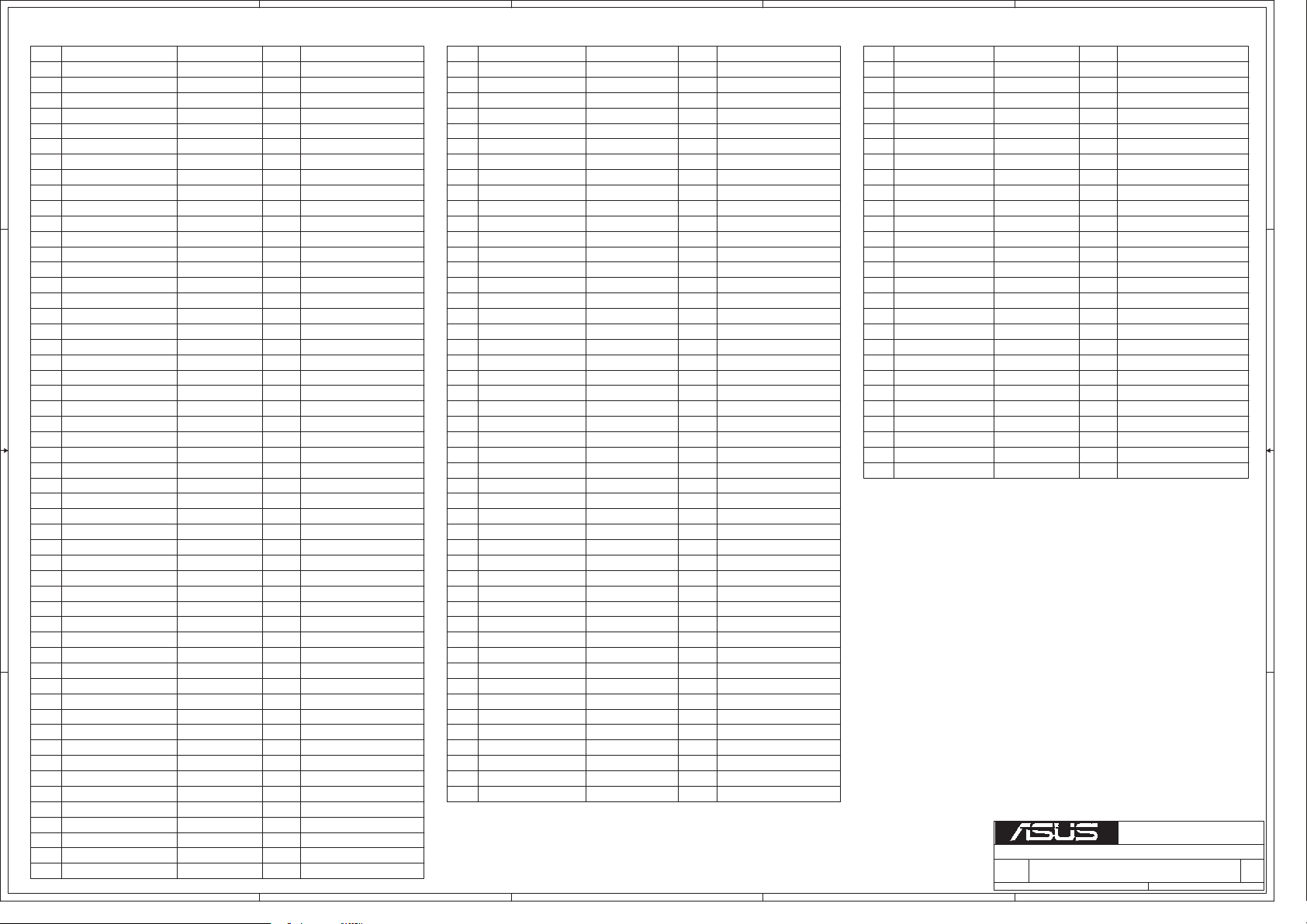

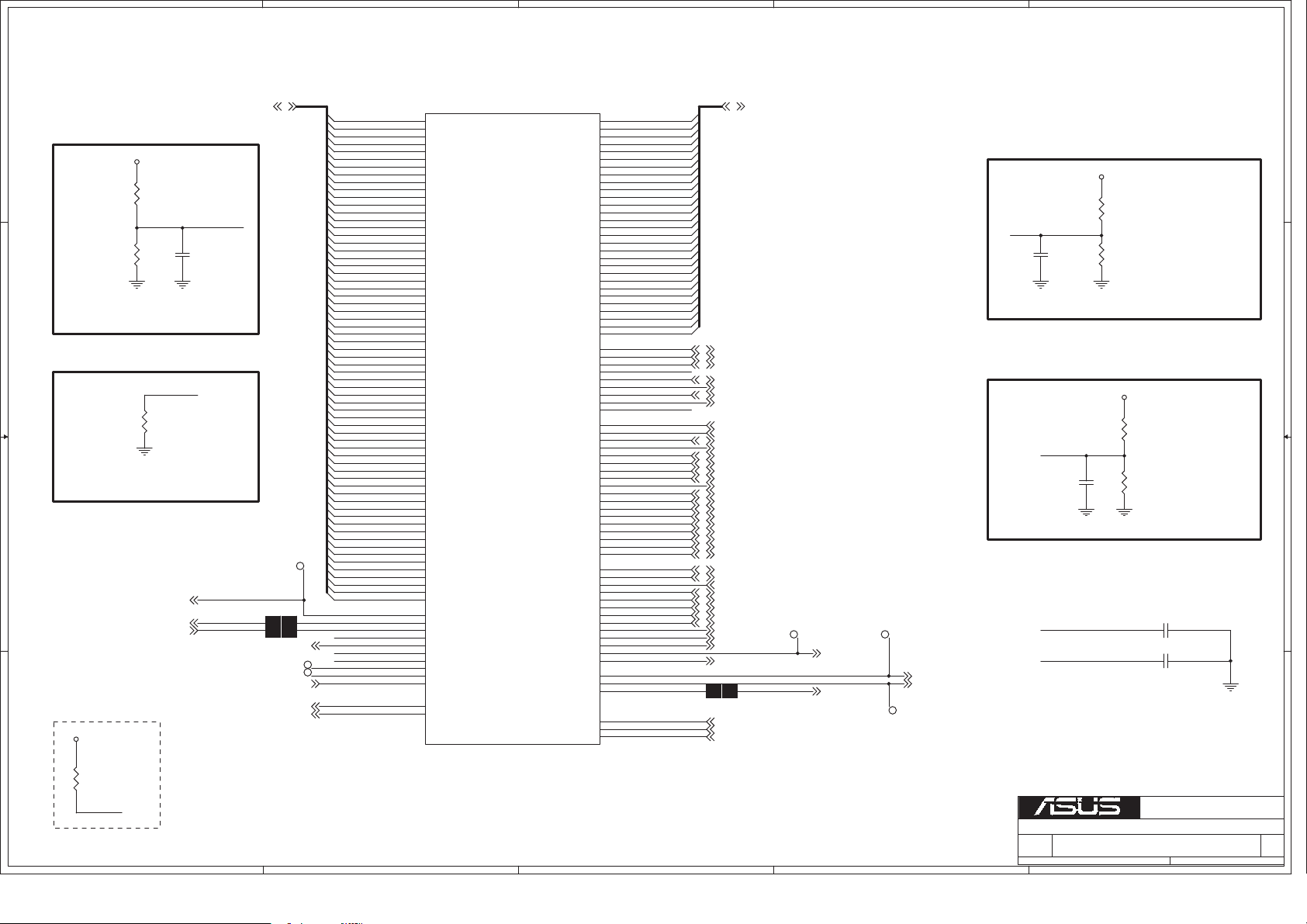

EC KB3310 GPIO SETTING

Pin

Pin Name

1

GPIO00/GA20

GPIO01/KBRST#

2

GPIO04

6

13

D D

C C

B B

A A

GPIO05/PCIRST#

14

GPIO07

15

GPIO08

16

GPIO0A

17

GPIO0B/ESB_CLK

18

GPIO0C/ESB_DAT

GPIO0D

19

GPIO0E/SCI#

20

21

GPIO0F/PWM0

GPIO10/PWM1

23

GPIO11/PWM2

25

GPIO12/FANPWM1

26

GPIO13/FANPWM2 85

27

28

GPIO14/FANFB1

29

GPIO15/FANFB2

GPIO16/E51_TX

30

GPIO17/E51_RX

31

32

GPIO18

GPIO19/PWM3

34

GPIO1A/NUMLED

36

GPIO1D/CLKRUN#

38

39

GPIO20/KSO0/TP_TEST

GPIO21/KSO1/TP_PLL

40

41

GPIO22/KSO2

GPIO23/KSO3

42

43

GPIO25/KSO5

44

GPIO26/KSO6

45

GPIO27/KSO7

46

GPIO28/KSO8

47

GPIO29/KSO9

48

GPIO2A/KSO10

50

GPIO2B/KSO11

GPIO2C/KSO12

51

GPIO2D/KSO13

52

GPIO2E/KSO14

53

54

GPIO2F/KSO15

GPIO30/KSI0

55

GPIO31/KSI1

56

GPIO32/KSI2

57

58

GPIO33/KSI3

GPIO34/KSI4

59

GPIO35/KSI5

60

61

GPIO36/KSI6

GPIO37/KSI7

62

GPI38/AD0

63

GPI39/AD1

64

65

GPIO3A/AD2

GPIO3B/AD3

66

GPO3C/DA0

68

5

Signal Name

A20GATE

RC_IN#

HOTKEY_SW0#

BUF_RST#

HOTKEY_SW1#

EXT_SMI#

LID_EC#

NC

NC

LID_EC_R#

KBC_SCI#

BL_PWM_DA

BATSEL#

PM_PWRBTN#

FAN0_PWM

FAN1_PWM

FAN0_TACH

FAN1_TACH

E51_TX

E51_RX

PWR_SW#

PS-ON CAP_LED#

NUM_LED#

LPC_CLKRUN#

KSO0

KSO1

KSO2

KSO3

KSO4

KSO5

KSO6

KSO7

KSO8

KSO9

KSO1049

KSO11

KSO12

KSO13

KSO14

KSO15

KSI0

KSI1

KSI2

KSI3

KSI4

KSI5

KSI6

KSI7

BAT_A

BAT_B

BAT_C

BAT_D

CHG_EN#

Note

Type

O

O

I

Internal pull high

I

Battery over temperature

I

OD

10K pull high to +3VSB

I

Internal pull high

Reserved for GPIO extende r

O

Reserved for GPIO extende r

O

I

Internal pull high

O

10K pull high to +3VSB

O

Battery critical capacity

I

OD

Internal pull high in ICH

O

CPU Fan

VGA Fan

O

CPU FanTach

I

VGA FanTach VCC

I

RS232 debug port

O

I

RS232 debug port

I

Internal pull high

O

latch power

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I

Internal pull high

I

Internal pull high

I

Internal pull high

I

Internal pull high

I

Internal pull high

I

Internal pull high

I

Internal pull high

I

Internal pull high

I

I

I

I

battery charger enabled

O

4

http://hobi-elektronika.net

Pin

Pin Name

GPO3D/DA1

70

GPO3E/DA2

71

GPO3F/DA3

72

GPIO40

73

74

GPIO41

GPI42

75

GPI43

76

GPIO44/SCL1

77

GPIO45/SDA1

78

GPIO46/SCL2

79

80

GPIO47/SDA2

81

GPIO48/KSO16

82

GPIO49/KSO17

83

GPIO4A/PSCLK1

GPIO4B/PSDAT1

84

GPIO4C/PSCLK2

GPIO4D/PSDAT2

86

GPIO4E/PSCLK3

87

GPIO4F/PSDAT3

88

GPIO50/SELIO#

89

GPIO52/E51_CS#

90

GPIO53/CAPLED

91

GPIO54

92

GPIO55/SCRLED

93

GPIO56

95

GPXOA00/SDICS#

97

GPXOA01/SDICLK

98

99

GPXOA02/SDIDO

GPXOA03

100

GPXOA04

101

GPXOA05

102

GPXOA06

103

104

GPXOA07

105

GPXOA08

106

GPXOA09

GPX0A10

107

GPXOA11

108

109

GPXID0/SDIDI

GPXID1

110

GPXID2

112

GPXID3114

115

GPXID4

GPXID5

116

GPXID6

117

GPXID7

118

GPIO57

121

126

GPIO57/SPICLK

127

GPIO59/TEST_CLK

Signal Name

LCD_BACKOFF#

THRO_CPU_VOLT#

BAT_LL#

AC_OK

PM_RSMRST#

BAT_IN

BAT2_IN

SMB0_CLK

SMB0_DAT

SMB1_CLK

SMB1_DAT

KB_ID0

KB_ID1 for KB type detection

N.C.

N.C.

N.C.

GS2_INT2

TP_CLK

TP_DAT

CHG_LED_GREEN#

CHG_LED_UP#

PWR_LED_UP

SCRL_LED#

GS1_INT1

SPI_MODE#

SUSC_ON

VSUS_ON

CPU_VRONGPIO24/KSO4

SUSB_ON

CNT1_CHG#

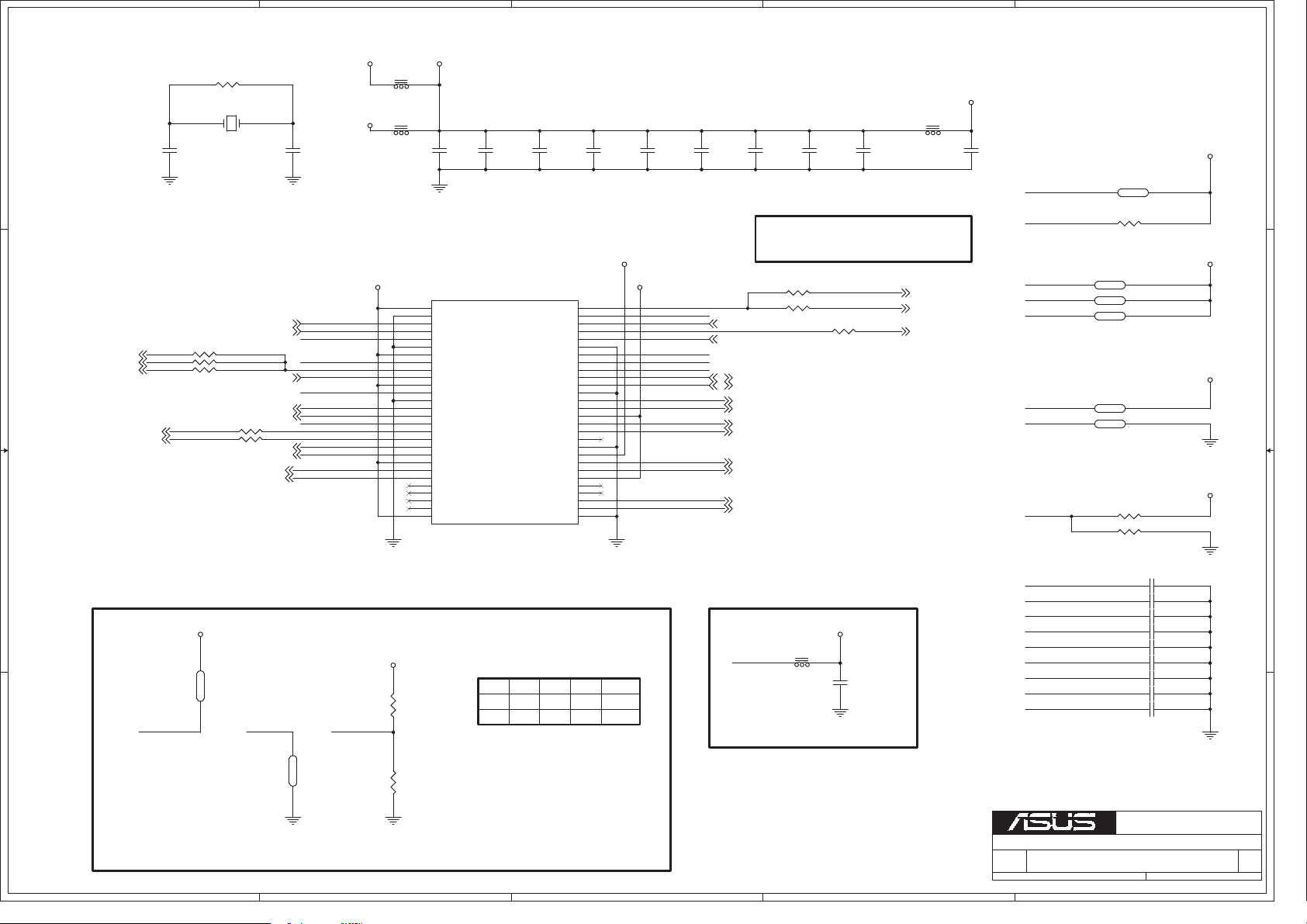

CNT1_DIS#

CNT2_CHG#

CNT2_CHG#

SPI_WP#

OP_SD#

BAT_LEARN

PM_PWROK

RST#

THRO_CPU

PM_SLPRDY#

SLPMODE

VRM_PWRGD

PM_RSTRDY#

RSTWARN

GS1_INT2

SPI_CLK

GS2_INT1

3

Type

O

O

O

I

O

Batt1 (Small/Internal):

I

1-present, 0-absent

Batt2 (Small/Internal):

I

1-present, 0-absent

I/OD

I/OD

I/OD

I/OD

I

I

O

O

O

O

I/OD

D

I/O

O

O

O

O

O

I

O

O

O

O

O

batt1 (Big/External) charging enabled. Batt1 is discharging priorit y in A C m ode.

O

batt1 discharging enabled

O

batt2 (Small/Internal) charging enabled. Batt2 is charging priority in AC mode.

O

batt2 discharging enabled

O

O

O

O

O

O

O

I

I

I

I

O

I

O

O

Note

Battery Low Low

AC Adaptor Plug in

10K pull down to GND

4.7K pull high to +3VA_EC

4.7K pull high to +3VA_EC

10K pull high to +3V

10K pull high to +3V

for KB type detection

10K pull high to +3V

10K pull high to +3V

Green charger LED

Orange charger LED

Internal pull high

4.7K pull down to GND

Audio OP

Battery parallel, H:1P, L:2P~3P

Active if CPU temperature over spec

SLPRDY#,100K pull down to GND

SUSC#,100K pull down to GND

Pull high to +3V

Internal pull high

EC KB3310 Other Pin SETTING

Pin

Pin Name

SERIRQ

4

LFRAME#

5

LAD3

7

LAD2

8

LAD1

VCC

9

LAD0

10

11

GND

PCICLK

12

22

VCC

24

GND

33

VCC

GND

35

37

ECRST#

AVCC

67

AGND

69

GND

94

96

VCC

111

113

GND

119

RD#/SPIDI

WR#/SPIDO

120

122

XCLKI

XCLKO

123

124

V18R

125

VCC

SPICS#/SELMEM#

128

2

Signal Name

INT_SERIRQ

LPC_FRAME#

LPC_AD3

LPC_AD2

LPC_AD1

+3VA

LPC_AD0

GND

CLK_PCI_EC

+3VA

GND

+3VA

GND

EC_RST#

+3VA_AEC

AGND

GND

+3VA

+3VA

GND

SPI_SO

SPI_SI

K_XCLKI

K_XCLKO

V18R

+3VA

SPI_CS#

0106 1025

ASUSTek Computer INC.

Size Project Name

A3

Date: Sheet

T91

Note

Type

10K pull high to +3V3

I/OD

I

I/O

I/O

I/O

P

I/O

P

I

P

P

P

P

100K pull high to +3VA_EC

I

P

P

P

P

P

P

I

O

I

O

Reserved 1uF to GND

P

P

O

Title :

Engineer:

1

EC Pin Define

Jerry Liu

357Tuesday, January 06, 2009

of

Rev

1.2G

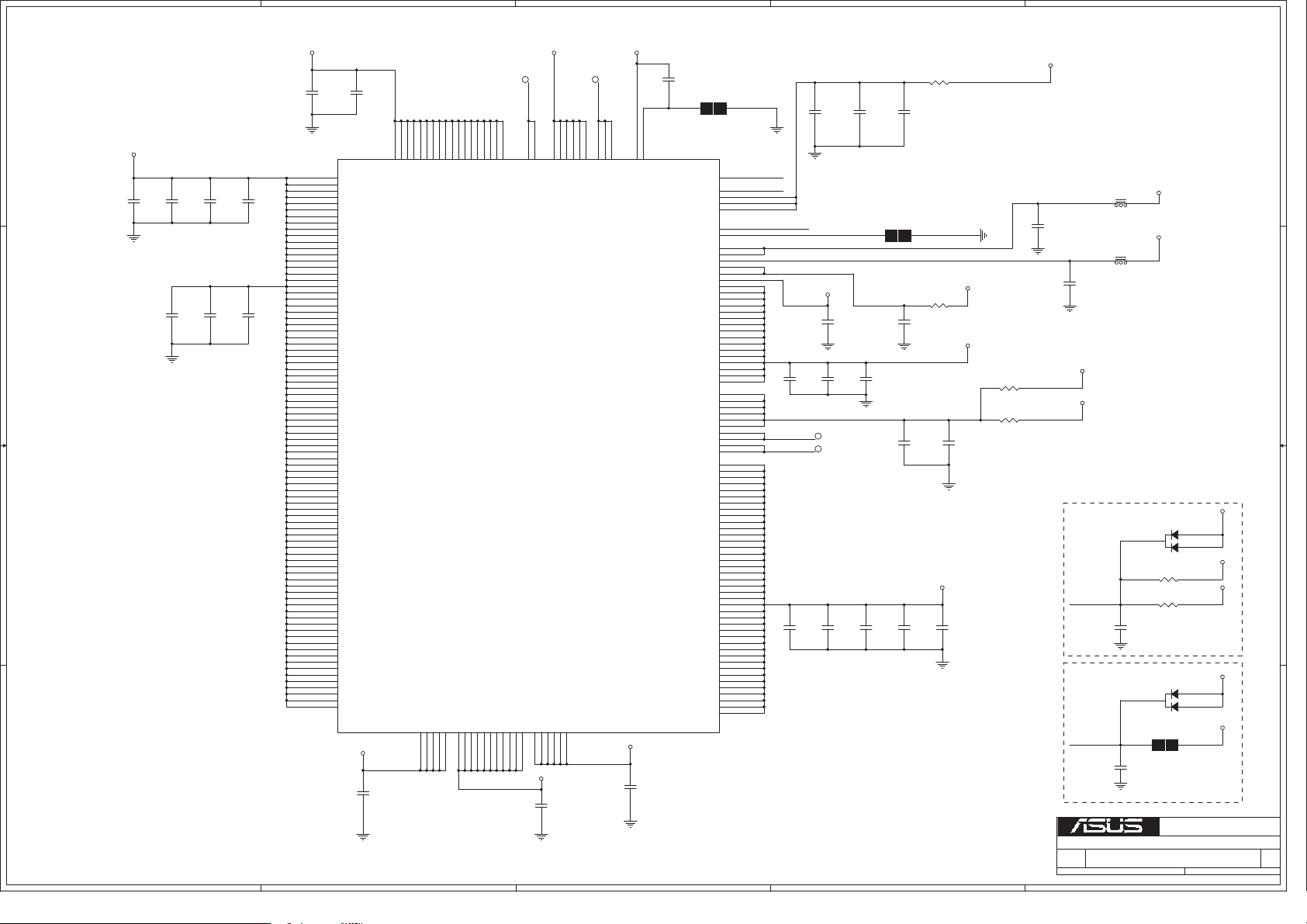

Page 4

5

4

3

2

1

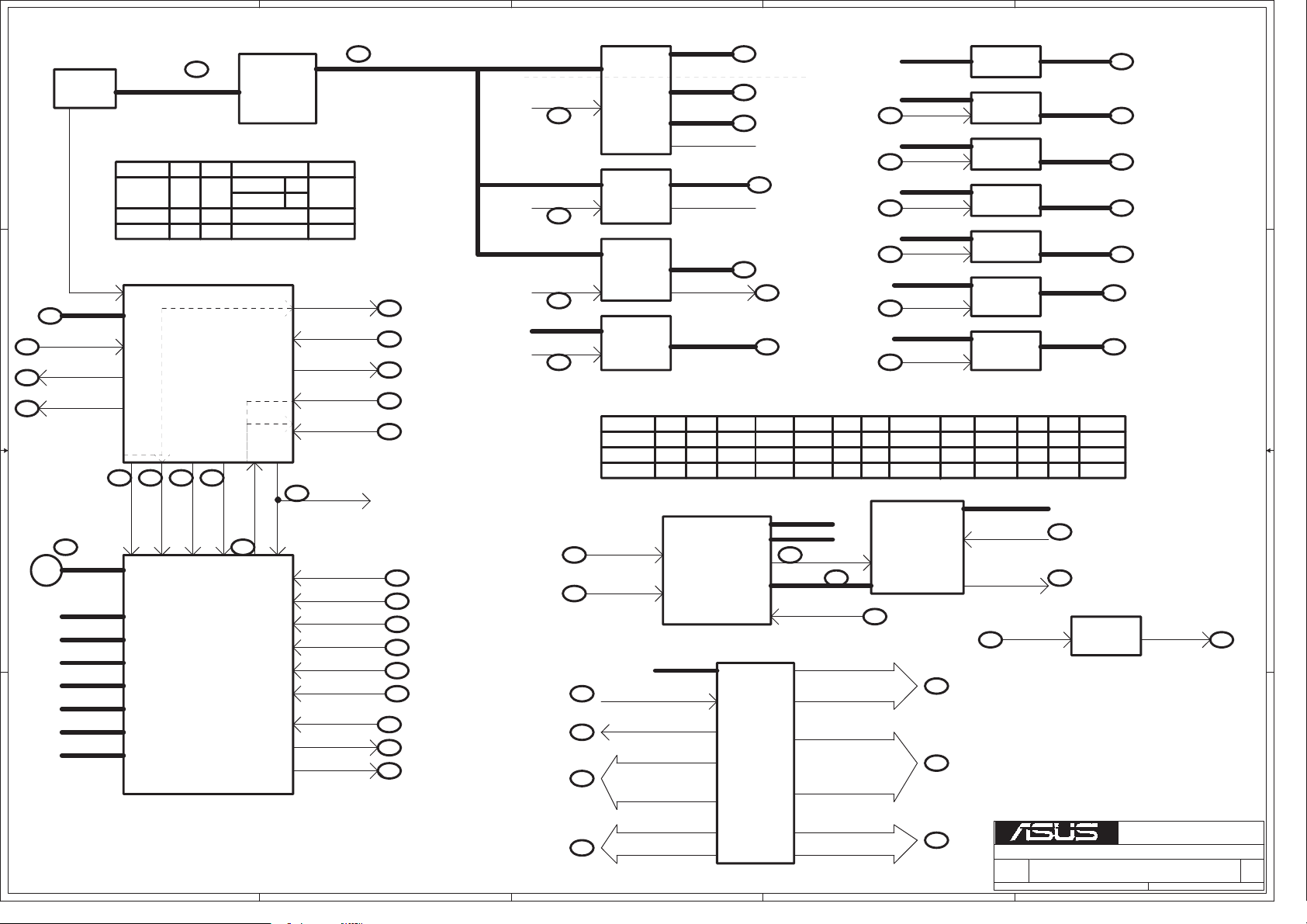

http://hobi-elektronika.net

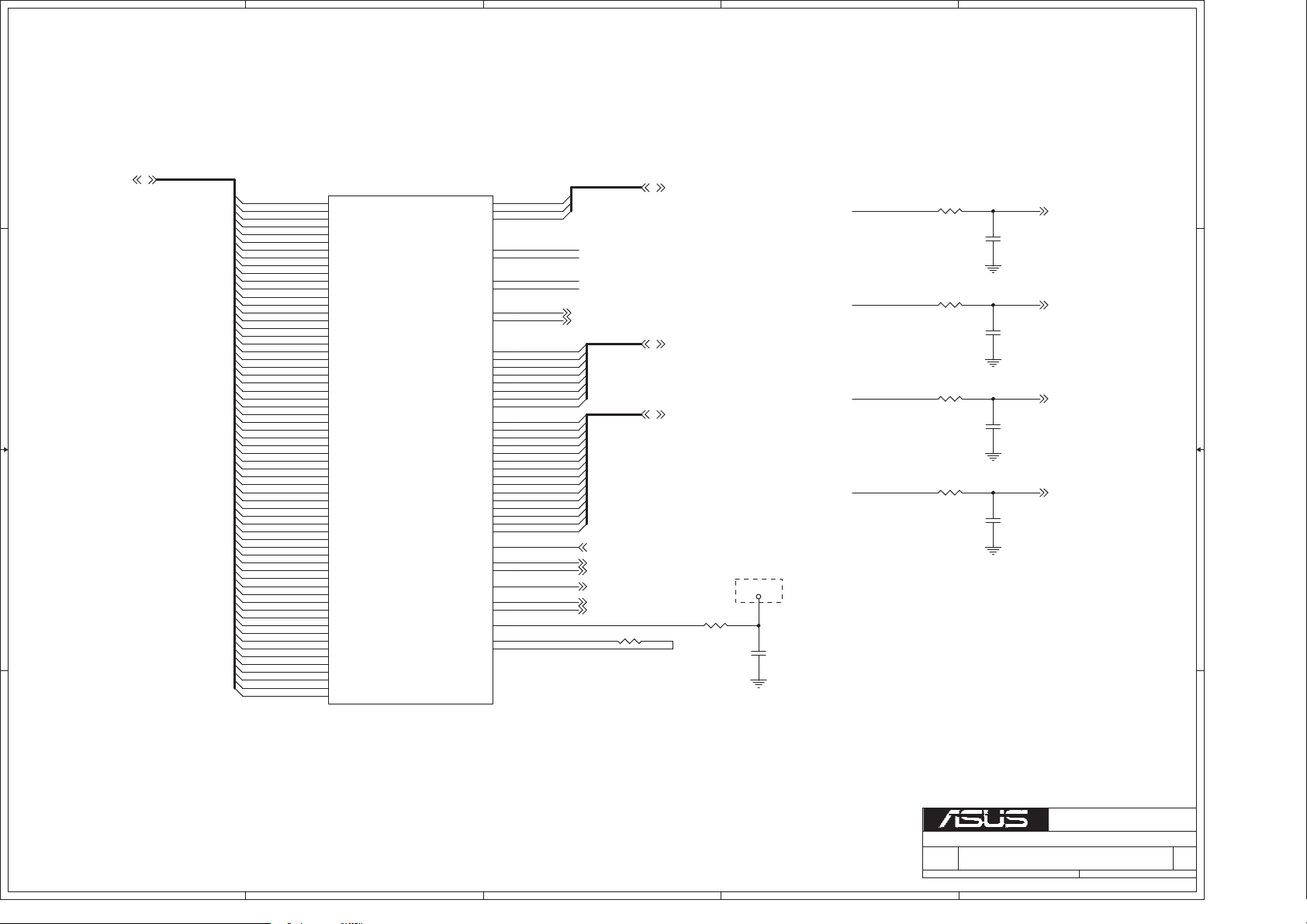

+5VA

RT8205

UP6111

EN

UP6111

EN

UP7711

EN

S0/S1

S3

S4/S5

Vccp_PWRGD

REF CLK 14M

ICH

PCI CLK 33M

SCH EC

DEBUG

UMA CLK 96M

SCH

3

LDO

+3VSUS

+5VSUS

VSUS_PWRGD

+1.8V

1.8V_PWRGD

Vccp

Vccp_PWRGD

VTT_DDR

+3VA

+5VA

V

V

V

SLIVERTHORNE

+3VSUS

2

3

Battery

D D

Signal

SUSB_ON

SUSC_ON

BAT1_IN

+3VA

5

C C

PWR_SW#

6

VSUS_ON

7

SUSC_ON

9

> 5ms

7

1

+

BATT

+VCC_RTC

+1.5VS

+1.8V

+3VS

+3VSUS

+5VS

+5VSUS

B B

A A

PM_PWRBTN#

Vccp

BAT

S0/S1

HH

H

> 5ms

ENE KB3310

21

20

11

EC_PWROK

PM_RSMRST#

Intel SCH

MB39A

S3

S4/S5 Power

HVSUS_ON

Adapter

Battery

L

L

HL

> 5ms

>

100us

PM_RSTRDY#

PM_RSTWARN

RST#

22

VSB

L

Main

DUALH

SUSB_ON

CLK_PCI_EC

CPU_VRON

VRM_PWRGD

BUF_RST#

RST#

23

CLK_PCI_SCH

CLK_REF_SCH

CLK_BCLK_SCH

CLK_PCIE_SCH

CLK_96M_UMA

CLK_LCD_LVDS

VRM_PWRGD

H_PWRGD

H_CPURST#

AC_BAT_SYS

12

15

16

19

24

15

15

15

15

15

15

19

25

26

AC_BAT_SYS

VSUS_ON

7

AC_BAT_SYS

SUSC_ON

9

AC_BAT_SYS

SUSB_ON

12

+1.8V

SUSB_ON

12

25

26

14

15

15

H_PWRGD

H_CPURST#

15

5

4

4

8

8

10

13

14

13

+3V

VV

V

V

V

V

V

VV

--

ICS9LPR426

V

--

--

Vccp

+1.5V

VID[6:0]

17

VCORE

CLK_BCLK_CPU

FSB CLK 100M

CPU MCH ITP

PCIE CLK 100M

SCH

MINICARD

LAN

LVDS CLK 100M

MCH

+1.8V

+5VSUS

+3VSUS

18

+5V

V

--

--

15

V

V

+5VA

+5VSUS

SUSC_ON +5V

9

+5VSUS

SUSB_ON

+3VSUS

SUSC_ON

9

+3VSUS

SUSB_ON +3VS

12

+3V

SUSC_ON

12

+3VS

SUSB_ON

12

VTT_DDR

V

--

--

Vccp

V

--

--

G923

SI7326

EN

SI7326

EN

SI7326

EN

SI7326

EN

UP7704

EN

UP7704

EN

+1.5VS

V

--

--

AC_BAT_SYS

CPU_VRON

MAX8796

VRM_PWRGD

15

15

15

2

+3VA

5

10

+5VS

+3V

1312

10

13

+3VS

V

--

--

+1.5VS

+2.5VS

+5VS

--

--

V

13

13

+2.5VS

V

--

--

16

19

RST# BUF_RST#

0106 1025

BUFFER

Title :

ASUSTek Computer INC.

Size Project Name

A3

Date: Sheet

T91

Engineer:

1

2423

Power Sequence DC

Jerry Liu

457Tuesday, January 06, 2009

Rev

1.2G

of

Page 5

5

4

3

2

1

2

Adapter

9

6

8

Battery

BAT_IN

+3VA

5

VSUS_ON

PWR_SW#

SUSC_ON

D D

C C

9

A/D_DOCK_IN

2

BAT

Signal

S0/S1

S3

HVSUS_ON

HH

L

SUSB_ON

SUSC_ON

H

HL

> 5ms

ENE KB3310

21

20

11

MB39A

S4/S5 Power

Adapter

Battery

L

> 5ms

>

100us

L

23

PM_RSTRDY#

EC_PWROK

PM_PWRBTN#

1

+

BATT

+VCC_RTC

Vccp

+1.5VS

+1.8V

+3VS

+3VSUS

+5VS

+5VSUS

B B

A A

PM_RSMRST#

Intel SCH

5

PM_RSTWARN

RST#

22

3

AC_BAT_SYS

VSB

Main

DUALH

SUSB_ON

CLK_PCI_EC

CPU_VRON

VRM_PWRGD

BUF_RST#

RST#

CLK_PCI_SCH

CLK_REF_SCH

CLK_BCLK_SCH

CLK_PCIE_SCH

CLK_96M_UMA

CLK_LCD_LVDS

VRM_PWRGD

H_PWRGD

H_CPURST#

3

AC_OK

12

15

16

19

24

15

15

15

15

15

15

19

25

26

4

http://hobi-elektronika.net

+5VA

AC_BAT_SYS

VSUS_ON

6

AC_BAT_SYS

SUSC_ON

9

AC_BAT_SYS

SUSB_ON

12

+1.8V

SUSB_ON

12

S0/S1

S3

S4/S5

25

26

14

15

15

15

RT8205

UP6111

EN

UP6111

EN

UP7111

EN

+5VA

V

V

V

H_PWRGD

H_CPURST#

Vccp_PWRGD

REF CLK 14M

ICH

PCI CLK 33M

SCH EC

DEBUG

UMA CLK 96M

SCH

LDO

+3VSUS

+5VSUS

VSUS_PWRGD

+1.8V

1.8V_PWRGD

Vccp

Vccp_PWRGD

VTT_DDR

+3VSUS+3VA

V

V

V

V

V

SLIVERTHORNE

+3VSUS

3

+5VSUS

V

V

VV

ICS9LPR426

4

7

7

10

13

14

13

+3V

+1.8V

V

V

V

V

-- --

--

Vccp

+1.5V

17

VCORE

CLK_BCLK_CPU

9

12

9

12

12

12

+5V

VTT_DDR +3VS

V

V

--

VID[6:0]

Vccp

V

VV

--

--

--

--

MAX8796

18

15

FSB CLK 100M

CPU MCH ITP

PCIE CLK 100M

SCH

MINICARD

LAN

LVDS CLK 100M

MCH

2

+5VSUS

SUSC_ON

+5VSUS

SUSB_ON

+3VSUS

SUSC_ON

+3VSUS

SUSB_ON

+3V

SUSC_ON

+3VS

SUSB_ON

+1.5VS

--

--

15

15

15

+5VA

V

+2.5VS

--

--

RST#

+3VA

+5V

+5VS

+3V

+3VS

+1.5VS

VTT_DDR

16

19

T91

5

10

13

10

13

13

13

BUFFER

Title :

Engineer:

BUF_RST#

Power Sequence AC

1

G923

SI7326

EN

SI7326

EN

SI7326

EN

SI7326

EN

UP7704

EN

UP7704

EN

EN

+5VS

V

V

--

--

--

AC_BAT_SYS

CPU_VRON

VRM_PWRGD

23 24

0106 1025

ASUSTek Computer INC.

Size Project Name

A3

Date: Sheet

Jerry Liu

557Tuesday, January 06, 2009

Rev

1.2G

of

Page 6

5

4

3

2

1

http://hobi-elektronika.net

S4/S5 to S0(Adapter Mode)

This sequence will occur whenever the system is in S4/S5

and the EC initiates a sleep exit sequence from S4/S5 to

D D

S0.

Initial EC state: VSUS_ON=0, SUSB_ON=0, SUSC_ON=0, A20GA=X,

KBRST=X, CPU_VRON=0, ICH_PWROK=0, RSTWARN=0, and

PM_RSMRST#=0, RESET#=0.

1.Waiting for AC_OK until adaptor power is good, then

2.At least 5mS after AC_OK is asserted, EC asserts VSUS_ON

to enable VSUS power.

3.At least 20mS after VSUS power is stable, waiting for

PWR_SW# until user is pressed. (Or waiting for SCH

deasserted SLPRDY#, too?)

4.EC asserts RSTWARN.

5.SUSC_ON is asserted at least 20mS (de-bounce) after

receiving PWR_SW#.

6.PM_RSMRST# is deasserted at least 5mS after SUSC power is

stable.

C C

7.At least 5mS after PM_RSMRST# is deasserted, SUSB_ON is

enabled.

8.CPU_VRON is deasserted at least 100mS after SUSB power

is stable.

9.Waiting for CPUPWR_GD (VRM_PWRGD) until CPU_VRON power is

stable.

10.At least 10mS after receiving CPUPWR_GD, PM_PWROK is

asserted, and then deasserts RSTWARN.

11.Waiting for RSTRDY# until deasserted by SCH.

12.RESET# can be deasserted at lease 100uS after PM_PWROK

is asserted.

This sequence will occur whenever the system is in S4/S5

and the EC initiates a sleep exit sequence from S4/S5 to

S0.

Initial EC state: VSUS_ON=0, SUSB_ON=0, SUSC_ON=0, A20GA=X,

KBRST=X, CPU_VRON=0, ICH_PWROK=0, RSTWARN=0, and

PM_RSMRST#=0, RESET#=0.

1.Waiting for BAT_IN until battery power is good, then

2.Waiting for PWR_SW# until user is pressed.

3.EC asserts VSUS_ON to enable VSUS power.

4.At least 20mS after VSUS power is stable.

5.EC asserts RSTWARN.

6.SUSC_ON is asserted at least 20mS (de-bounce) after

receiving PWR_SW#.

7.PM_RSMRST# is deasserted at least 5mS after SUSC power is

stable.

8.At least 5mS after PM_RSMRST# is deasserted, SUSB_ON is

enabled.

9.CPU_VRON is deasserted at least 10mS after SUSB power is

stable.

10.Waiting for CPUPWR_GD (VRM_PWRGD) until CPU_VRON power

is stable.

11.At least 10mS after receiving CPUPWR_GD, PM_PWROK is

asserted, and then deasserts RSTWARN.

12.Waiting for RSTRDY# until deasserted by SCH.

13.RESET# can be deasserted at lease 100uS after ICH_PWROK

is asserted.

Power Sequence Description: S3 to S0

This sequence will occur in S3, and wake event is detected

B B

by EC or SCH.

Initial EC state: SUSB_ON=0, CPU_VRON=0, ICH_PWROK=0,

PM_RSMRST#=1, PM_PWRBTN#=1, and VSUS_ON=1, RSTWARN=1,

SUSC_ON=1, RESET#=0.

1.For internal wake event, SCH deasserts SLPRDY# to EC,

than 4.

2.For external wake event (PWR_SW#, keyboard wake up), then

3.EC asserts PM_PWRBTN# at least 50mS to wake SCH, and

waiting for SLPRDY# until SCH deasserted.

4.EC asserts SUSB_ON to enable SUSB power.

5.CPU_VRON is deasserted at least 100mS after SUSB power

is stable.

6.Waiting for CPUPWR_GD (VRM_PWRGD) until CPU_VRON power is

stable.

7.At least 5mS after receiving CPUPWR_GD, ICH_PWROK is

A A

asserted.

The warm reset sequence results in reset without remove any

power supplies.

Initial EC state: SUSB_ON=1, CPU_VRON=1, ICH_PWROK=1,

PM_RSMRST#=1, PM_PWRBTN#=1, and VSUS_ON=1, RSTWARN=1,

SUSC_ON=1, RESET#=1.

1.SCH asserts RSTRDY# at the same time as driving SLPMODE=1

to EC.

2.EC asserts RSTWARN to SCH.

3.EC asserts RESET# for 1200mS to SCH after asserts

RSTWARN.

4.EC deasserts RSTWARN.

5.EC deasserts RESET# after at least 100uS delay from

RSTWARN.

S4/S5 to S0(Battery Mode)

Warm Reset (SLPMODE=1)

This sequence will occur when system entry to sleep states,

or all power planes are shut down.

Initial EC state: VSUS_ON=1, SUSB_ON=1, SUSC_ON=1,

CPU_VRON=1, ICH_PWROK=1, and PM_RSMRST#=1, RESET#=1,

RSTWARN=0, PM_PWRBTN#=1.

1.Waiting for PWR_SW# until user is pressed (go to 2),

or waiting for SLPRDY# is asserted (go to 3).

2.At least 20mS after PWR_SW# is asserted, EC asserts

PM_PWRBTN# (50mS width) to SCH.

3.Waiting for SLPRDY# until has been asserted.

4.EC asserts RSTWARN to SCH to begin internal sequence.

5.SCH asserts RSTRDY# to EC to indicate all outstanding

transactions are completed.

6.EC asserts RESET# after detecting RSTRDY# asserted.

7.EC deasserts ICH_PWROK.

8.EC deasserts SUSB_ON and CPU_VRON to turn off power

planes.

This completes the entry to S3

(SLPMODE=1).

If SLPMODE=0, this indicates S4/S5 was the desired state,

EC takes additional actions:

9.EC asserts PM_RSMRST#.

10.EC deasserts SUSC_ON to turn off the other power planes.

11.EC deasserts VSUS_ON if in battery mode.

12.EC deasserts RSTWARN to save more power.

The cold reset sequence results in a power cycling of all

but the RTC power well.

Initial EC state: SUSB_ON=1, CPU_VRON=1, ICH_PWROK=1,

PM_RSMRST#=1, PM_PWRBTN#=1, and VSUS_ON=1, RSTWARN=1,

SUSC_ON=1, RESET#=1.

1.SCH asserts RSTRDY# at the same time as driving SLPMODE=0

to EC.

2.EC asserts RSTWARN to SCH.

3.EC asserts RESET# to SCH after asserts RSTWARN.

4.EC deasserts PM_PWROK and disables SUSB_ON and CPU_VRON

power.

5.EC asserts PM_RSMRST# after CPU_VRON power is off.

6.EC disables SUSC_ON power for 3~5 seconds.

7.S4/S5 to S0 sequence is automatically followed to bring

the system back to S0 when SUSC_ON power is enable.

S0 to S3/S4/S5

Cold Reset (SLPMODE=0)

8.Deasserts RSTWARN after ICH_PWROK is asserted.

9.RESET# can be deasserted 100uS after RSTWARN is

deasserted.

5

4

3

2

0106 1025

ASUSTeK COMPUTER INC

Size Project Name

Custom

Date: Sheet

Power Sequence Description

Title :

Engineer:

T91

1

Jerry Liu

657Tuesday, January 06, 2009

Rev

1.2G

of

Page 7

5

4

3

2

1

http://hobi-elektronika.net

+3VS

CR1 Do Not Stuff

1 2

D D

C C

B B

A A

CLK_48M_UART38

CLK_48M_READER243

CLK_48M_READER33

CLK_LCD_LVDS14

CLK_LCD_LVDS#14

CLK_XIN

12

CC13

27PF/50V

GND

CR14 10Ohm

1 2

CR13 10Ohm /C52

1 2

CR4 10Ohm /C52

1 2

CR5 0Ohm

CR6 0Ohm

CLK_PCIE_MINICARD#24

+3V_CLK

56

CLK_FSLA CLK_FSLB CLK_FSLC

5

CX1

12

14.318Mhz

07G010Q01433

CLK_PEREQ#114

CLKREQ#_MINICARD24

VCCP_PWRGD50,53

CLK_96M_UMA14

CLK_96M_UMA#14

1 2

1 2

CLK_PCIE_SCH13

CLK_PCIE_SCH#13

CLK_PCIE_MINICARD24

CRN2C

8.2KOhm

/X

CLK_XOUT

120Ohm/100Mhz

+3V

12

CC14

27PF/50V

GND

CLK_PEREQ#1

CLK_PEREQ#2

CLK_FS4

CLK_ITP_EN

CLK_SEL_48# VDDREF

CLK_FSLA

CLK_96M

CLK_96M#

CLK_FSLB

CLK_LCD

CLK_LCD#

CLK_PCIE1

CLK_PCIE#1

CLK_PCIE2

CLK_PCIE#2

CRN2D

8.2KOhm

7 8

GND

Do Not Stuff

+3V_CLK

GND

+3V_CLK

GND

4

+3V_CLK

CL3

21

l0603

CL1

21

l0603 /X

12

GND

CU1

1

VDD1

2

GND1

3

PEREQ1#

4

PEREQ2#

5

FS4/PCICLK0

6

GND2

7

VDDPCI

8

ITP_EN/PCICLK_F0

9

SEL12_48#/12_48MHz

10

Vtt_PwrGd/PD#

11

VDD2

12

FSLA/USB_48MHz

13

GND3

14

DOTT_96MHzLR

15

DOTC_96MHzLR

16

FSLB

17

PCIeT_LR0

18

PCIeC_LR0

19

PCIeT_LR1

20

PCIeC_LR1

21

VDDPCIEX1

22

PCIeT_LR2

23

PCIeC_LR2

24

PCIeT_LR3

25

PCIeC_LR3

26

SATACLKT_LR

27

SATACLKC_LR

28 29

VDDPCIEX2 GND6

ICS9LPRS427AGLF

06G011552010

CC1

Do Not Stuff

/X

c0805

12

CC2

0.1UF/16V

PCI&PCIEX_STOP#

DOC_PEREQ3#/SELDOC#

CPUITPT_LR2/PCIeT_LR6

CPUITPC_LR2/PCIeC_LR6

FSC FSB FSA CPU PCIE

1 2

12

CR9

Do Not Stuff

/X

CR10

8.2KOhm

00

0111

12

CC3

0.1UF/16V

25MHz

CPU_STOP#

REF0/FSLC

GND4

VDDREF

SDATA

SCLK

GND5

CPUT_LR0

CPUC_LR0

VDDCPU

CPUT_LR1

CPUC_LR1

RESET#

GNDA

VDDA

VDDPCIEX3

PCIeT_LR5

PCIeC_LR5

PCIeT_LR4

PCIeC_LR4

X1

X2

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

133

100

12

CC4

0.1UF/16V

+3V_CLK_VDDA

+3V_CLK

GND

100

100

3

12

CC5

0.1UF/16V

PCI_STOP#

CLK_FSLC

CLK_PEREQ#3

CLK_XIN

CLK_XOUT

CLK_BCLK0

CLK_BCLK#0

CLK_BCLK1

CLK_BCLK#1

CLK_BCLK2

CLK_BCLK#2

CLK_PCIE4

CLK_PCIE#4

12

CC6

0.1UF/16V

STP_CPU# 14

CLK_PEREQ#3 28

S_SMB_DATA 14

S_SMB_CLK 14

CLK_BCLK_CPU 8

CLK_BCLK_CPU# 8

CLK_BCLK_MCH 11

CLK_BCLK_MCH# 11

CLK_BCLK_ITP 8

CLK_BCLK_ITP# 8

CLK_PCIE_LAN 28

CLK_PCIE_LAN# 28

VDDREF

RF solution

12

1:Disable

0:Enable

CR11 Do Not Stuff

CR12 33Ohm

12

CC8

0.1UF/16V

PEREQ1:PCIEx0 & PCIEx1

PEREQ2:PCIEx2 & PCIEx3 & SATA

PEREQ3:PCIEx4 & PCIEx5 & PCIEx6

1 2

1 2

CR3 33Ohm

CL4

21

120Ohm/100Mhz

l0603/RF

CC9

0.1UF/16V

/X

/P2S

1 2

+3V_CLK

12

GND

12

CC25

0.1UF/16V

/RF

CC10

0.1UF/16V

2

120Ohm/100Mhz

CLK_25M_LAN 28

CLK_25M_SATA 31

CLK_SCH14 14

CL2

l0603

+3V_CLK_VDDA

21

12

CC12

0.1UF/16V

PCI_STOP#

STP_CPU#

CLK_PEREQ#1

CLK_PEREQ#2

CLK_PEREQ#3

CLK_ITP_EN

CLK_SEL_48#

CLK_FS4

S_SMB_DATA

S_SMB_CLK

CLK_SCH14

CLK_LCD

CLK_LCD#

CLK_96M

CLK_96M#

CLK_25M_LAN

CLK_25M_SATA

0106 1025

ASUSTek Computer INC.

Size Project Name

A3

Date: Sheet of

T91

7 8

CR2 10KOhm

1 2

1 2

10KOhm

3 4

10KOhm

5 6

10KOhm

8.2KOhm

8.2KOhm

CR7 8.2KOhm

1 2

CR8 Do Not Stuff/X

1 2

Engineer:

CRN1D

10KOhm

+3V_CLK

CRN1A

CRN1B

CRN1C

+3V_CLK

CRN2A

12

CRN2B

34

+3V_CLK

CC15 10PF/50V

12

CC16 10PF/50V

12

CC17 10PF/50V

12

CC19 10PF/50V

12

CC20 10PF/50V

12

CC21 Do Not Stuff

12

CC22 Do Not Stuff

CC23 Do Not Stuff

CC24 Do Not Stuff

Title :

/X

12

/X

12

/X

12

/X

Clock Gen_ICS9LPRS427

Jerry Liu

757Tuesday, January 06, 2009

1

+3VS

GND

GND

GND

Rev

1.2G

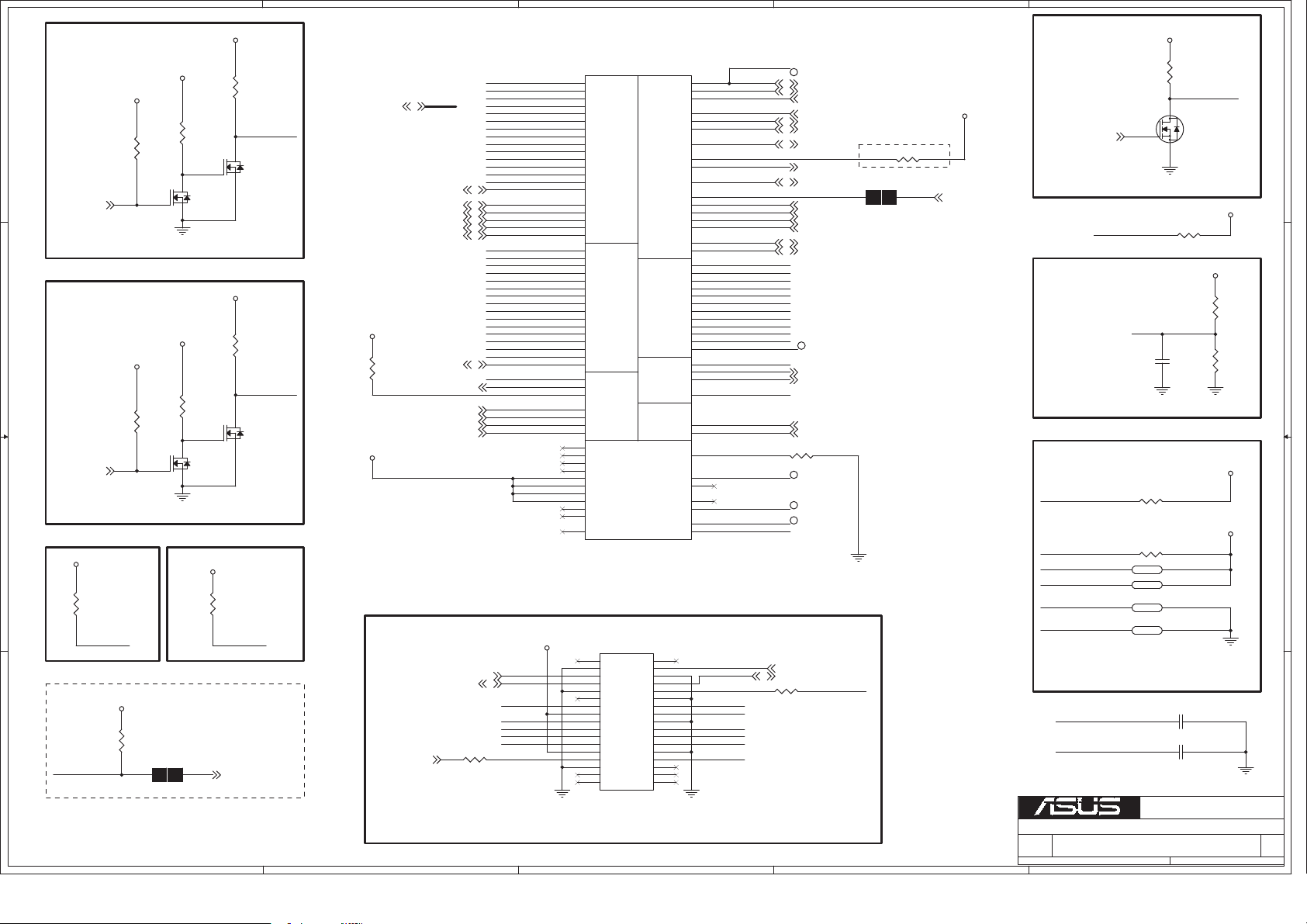

Page 8

5

4

3

2

1

+VCCP_C6

+3VA

+3VS

D D

R198

Do Not Stuff

/X

1 2

A20GATE37

A20M# Level Shift

C C

+3VS

R200

Do Not Stuff

/X

1 2

RC_IN#37

KBRST# Level Shift

B B

+VCCP

R197

10KOhm

1 2

34

5

GND

+3VA

R199

10KOhm

1 2

34

5

GND

2

Q1B

UM6K1N

+VCCP_C6

2

Q2B

UM6K1N

+VCCP_C6

1 2

61

1 2

61

R1

1KOhm

Q1A

UM6K1N

R7

1KOhm

Q2A

UM6K1N

H_A20M#

H_INIT#

1KOhm

H_A#[31..3]11

+VCCP_C6

R8

1 2

+VCCP_C6

H_ADSTB#011

H_REQ#011

H_REQ#111

H_REQ#211

H_REQ#311

H_REQ#411

H_ADSTB#111

H_PBE#11

H_STPCLK#11

http://hobi-elektronika.net

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A20M#

H_INTR11

H_NMI11

H_SMI#11

E22

A22

D21

E24

B17

A18

B23

A16

E18

D15

B19

A20

D17

B15

D19

B25

D23

E20

A24

B21

A12

E12

B13

E14

A10

D13

A14

B11

D11

G30

H27

H31

AE16

AF17

AD15

AD17

E10

K29

B5

D5

B9

A6

B7

A8

C4

J28

K1

L28

J26

D9

D7

E8

L30

J30

U1A

A[3]#

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD7

RSVD8

RSVD9

RSVD10

RSVD0

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD13

INT441

01G012610200

ADDR GROUP

0

ADDR GROUP 1

THERM

THERMTRIP#

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

XDP/ITP SIGNALS CONTROL

RSVD14

PROCHOT#

THRMDA

THRMDC

BCLK[0]

BCLK[1]

VSS0

RSVD11

NC HCLK

RSVD6

RSVD15

TEST4

TEST3

CMREF[1]

C26

H25

G24

B27

W28

D29

C28

H1

F31

D25

M5

D27

E28

E26

F25

E30

F29

F1

E2

F5

D3

E4

F7

L2

N2

TDI

M1

P1

J4

G26

H5

T5

U4

T1

P29

R28

K31

A26

E6

G28

U30

V27

AE26

1

H_IERR#

H_INIT#

H_CPURST_R#

H_RS#0

H_RS#1

H_RS#2

H_BPM#0

H_BPM#1

H_BPM#2

H_BPM#3

H_BPM#4

H_BPM#5

H_TCK

H_TDI

H_TDO

H_TMS

H_TRST#

H_PROCHOT_R#

PM_THRMTRIP#

CPU_CMREF

1

R10 Do Not Stuff/X

1

1

1

T1

H_ADS# 11

H_BNR# 11

H_BPRI# 11

H_DEFER# 11

H_DRDY# 11

H_DBSY# 11

H_BR0# 11

H_INIT# 11

H_LOCK# 11

H_RS#0 11

H_RS#1 11

H_RS#2 11

H_TRDY# 11

H_HIT# 11

H_HITM# 11

T213

H_THERMDA 42

H_THERMDC 42

CLK_BCLK_CPU 7

CLK_BCLK_CPU# 7

12

T3

T209

T4

GND

R2 1KOhm 1%

JP9

1 2

Do Not Stuff

+VCCP

12

H_CPURST# 11

Z530 : 01G011980000

R13

Do Not Stuff

1%

/X

1 2

H_STPCLK#

+VCCP

R16

120Ohm

A A

PM_THRMTRIP#

1 2

5

JP12

1 2

Do Not Stuff

R14

120Ohm

1 2

H_PBE#

PM_THRMTRIP#_R 11

Z520 C0 stage : 01G012610200

+VCCP

31

SMB_CLK14,18,24,44

H_TCK

H_TDO

H_BPM#0

H_BPM#2

H_BPM#4

HR4

Do Not Stuff

/ITP

ITP_PWRGD

H_PWRGD9,11

1 2

ITP Connector For Debug

4

11

13

15

17

19

21

23

25

27

29

32

GND GND

ITP1

SIDE1

1

1

3

3

5

5

7

7

9

9

11

13

15

17

19

21

23

25

27

29

SIDE2

Do Not Stuff

/ITP

Do Not Stuff

SIDE4

SIDE3

34

2

2

4

4

6

6

8

8

10

10

12

12

14

14

16

16

18

18

20

20

22

22

24

24

26

26

28

28

30

30

33

3

ITP_CPURST#

H_TMS

H_TDI

H_BPM#1

H_BPM#3

H_BPM#5

H_TRST#

CLK_BCLK_ITP 7

SMB_DATA 14,18,24,44CLK_BCLK_ITP#7

1 2

HR3

Do Not Stuff

/ITP

H_CPURST#

2

Processor Hot

THRO_CPU : H : throttle ON

THRO_CPU : L : throttle OFF

THRO_CPU37

H_CPURST#

CMOS Rreference

Voltage Level

H_BPM#5

H_TDO

H_TMS

H_TDI

H_TCK

H_TRST#

JTAG Interface When ITP/XDP

is not Implemented

CLK_BCLK_CPU

CLK_BCLK_CPU#

0106 1025

+VCCP

1 2

32

3

D

1

1

G

S

2

GND

1 2

CPU_CMREF

12

C2

0.1UF/16V

GND

HR1 56OHM

1 2

HR2 Do Not Stuff/ITP

1 2

1 2

3 4

5 6

7 8

HRN1A

56OHM

HRN1B

56OHM

HRN1C

56OHM

HRN1D

56OHM

C459 Do Not Stuff/X

C460 Do Not Stuff/X

Title :

ASUSTeK COMPUTER INC

Size Project Name

Custom

Date: Sheet

T91

Tuesday, January 06, 2009

Engineer:

1

R15

68Ohm

H_PROCHOT_R#

Q19

2N7002

+VCCP

R3

Do Not Stuff

/X

+VCCP_C6

12

R9

1KOhm

1%

12

R11

1KOhm

1%

GND

+VCCP_C6

+VCCP

GND

12

12

GND

CPU-SLIVERTHORNE(1)

Jerry Liu

857

of

Rev

1.2G

Page 9

5

4

3

2

1

http://hobi-elektronika.net

D D

H_DSTBN#011

H_DSTBP#011

C C

B B

H_DINV#011

H_DSTBN#111

H_DSTBP#111

H_DINV#111 H_DINV#3 11

T214

T215

T5

T6

T7

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

GTL_REF

1

1

1

1

1

Y27

AH27

Y31

AC30

AE30

AF29

AA26

AB31

W30

AC28

AD31

AF27

AD27

AG28

AB25

AC26

AA28

AA30

AE28

AE24

AC24

AJ20

AE20

AJ22

AF25

AH25

AH23

AH19

AF23

AE18

AH17

AD19

AJ24

AJ18

AF19

AF21

AH21

AE22

AJ26

P31

T31

R30

M31

U28

U1B

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

BSEL[0]

BSEL[1]

BSEL[2]

INT441

01G012610200

DATA GRP 1DATA GRP 0

DATA GRP 2

DSTBN[2]#

DSTBP[2]#

DATA GRP 3

DSTBN[3]#

DSTBP[3]#

MISC

PWRGOOD

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

SLP#

RSVD12

AE8

AD7

AH15

AF9

AH9

AE10

AJ16

AF13

AF7

AF15

AH13

AJ14

AJ12

AH7

AJ8

AJ10

AH11

AF11

AE12

AH5

AB5

AJ6

Y1

AF5

AG4

AF3

AC6

AE6

AE4

W4

AC2

AE2

AD1

AA2

AC4

AB1

AA4

Y5

AE14

AD13

E16

F15

G2

G6

V31

G4

J2

K27

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_COMP0

H_COMP1

H_COMP2

H_COMP3

H_DSTBN#2 11

H_DSTBP#2 11

H_DINV#2 11

H_DSTBN#3 11

H_DSTBP#3 11

R24 27.4OHM 1%

1 2

R25 54.9OHM 1%

1 2

R26 27.4OHM 1%

1 2

R27 54.9OHM 1%

1 2

H_DPRSTP# 11

H_DPSLP# 11

H_DPWR# 11

H_PWRGD 8,11

H_CPUSLP# 11

1

T8

GND

H_D#[63:0]

Near CPU

<500 mil (55 Ohm)

T/B trace 5.5 ,

Space 25

GTL_REF

12

GND

+VCCP_C6

C3

0.1UF/16V

H_D#[63:0] 11

R18

1KOhm

1%

1 2

R19

2KOhm

1%

GND

AGTL+ Reference Voltage Level

Layout Note

COMP 0 2 connect with Z0=27.4 ohm,L<0.5"

COMP 1 3 connect with Z0=55 ohm,L<0.5"

A A

5

4

3

0106 1025

Title :

ASUSTeK COMPUTER INC

Size Project Name

A4

Date: Sheet

Tuesday, January 06, 2009

2

T91

Engineer:

CPU-SLIVERTHORNE(1)

Jerry Liu

Rev

1.2G

957

1

of

Page 10

5

4

3

2

1

+VCCP_C6

U1C

AA14

AA10

AA12

AA16

AA18

AA20

AA22

AB11

AB13

AB15

AB17

AB19

AB21

AB23

W26

M27

AA8

AB7

AB9

H11

H13

H15

H17

H19

H21

H23

N26

R26

U26

J16

H7

H9

J8

J10

J12

J14

J18

J20

J22

L26

VCCP35

VCCP36

VCCPC60

VCCPC61

VCCPC62

VCCPC63

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCP17

VCCP18

VCCP19

VCCP20

VCCP21

VCCP22

VCCP23

VCCP24

VCCP25

VCCP26

VCCP27

VCCP28

VCCP29

VCCP30

VCCP31

VCCP32

VCCP33

VCCP34

INT441

01G012610200

VCCSENSE

VSSSENSE

+VCCP

130mA

D D

C C

B B

12

C458

0.1UF/16V

GND GND

12

+VCCP_C6

C4

0.1UF/16V

2.5A

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

L8

L10

L12

L14

L16

L18

L20

L22

L24

N6

N8

N10

N12

N14

N16

N18

N20

N22

N24

R6

R8

R10

R12

R14

R16

R18

R20

R22

R24

U6

U8

U10

U12

U14

U16

U18

U20

U22

U24

W8

W10

W12

W14

W16

W18

W20

W22

W24

N30

P5

R4

N4

K5

L4

R2

U2

W2

V1

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

VCCSENSE

VSSSENSE

http://hobi-elektronika.net

+VCORE

CPU TYPE

Silverthorne

Standard Voltage

Processor

Silverthorne

Medium Voltage

Processor

Silverthorne

Low Voltage

Processor

CPU +VCORE

Low-Frequency

Capacitors

+VCORE

12

+

CE1

100UF/6.3V

GND

+VCCA_CPU

JP8

Do Not Stuff

12

GND

C5

0.1UF/16V

1

T9

1

T10

1

T11

1

T12

1

T13

1

T14

1

T15

VCCSENSE 50

Layout Note:

Route VCCSENSE and VSSSENSE

traces at 27.4 Ohms with 18mil trace,

7mil vccsense to vsssense spacing. 25

1 2

mil spacing from others.

Place PU and PD within 1 inch of CPU.

GND

JP16

Do Not Stuff

Vcore Freq

0.98V @HFM

TBD @LFM

0.8V @HFM

TBD @LFM

0.76V @HFM

TBD @LFM

+1.5VS

12

TBD

TBD

TBD

A28

AA6

AA24

AB3

AB27

AB29

AC8

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AD3

AD5

AD9

AD11

AD21

AD23

AD25

AD29

AF1

AF31

AG2

AG6

AG8

AG10

AG12

AG14

AG16

AG18

AG20

AG22

AG24

AG26

AG30

AH3

AH29

AJ28

B29

C10

C12

C14

C16

C18

C20

C22

C24

C30

D31

F11

F13

F17

F19

F21

F23

F27

G10

G12

G14

G16

G18

G20

G22

H29

A4

AJ4

B3

C2

C6

C8

D1

F3

F9

G8

H3

J6

U1D

VSS1/NCTF

VSS2/NCTF

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25/NCTF

VSS26/NCTF

VSS27/NCTF

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39/NCTF

VSS41/NCTF

VSS42/NCTF

VSS45/NCTF

VSS46/NCTF

VSS48/NCTF

VSS49/NCTF

VSS51/NCTF

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62/NCTF

VSS63/NCTF

VSS64/NCTF

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

INT441

01G012610200

VSS162

VSS161

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

VSS100

VSS99

VSS98

VSS97

VSS96

VSS95

VSS94

VSS93

VSS92

VSS91

VSS90

VSS89

VSS88

VSS87

VSS86

VSS85

Y29

Y25

Y23

Y21

Y19

Y17

Y15

Y13

Y11

Y9

Y7

Y3

W6

V29

V25

V23

V21

V19

V17

V15

V13

V11

V9

V7

V5

V3

T29

T27

T25

T23

T21

T19

T17

T15

T13

T11

T9

T7

T3

P27

P25

P23

P21

P19

P17

P15

P13

P11

P9

P7

P3

N28

M29

M25

M23

M21

M19

M17

M15

M13

M11

M9

M7

M3

L6

K25

K23

K21

K19

K17

K15

K13

K11

K9

K7

K3

J24

GNDGND

+VCCP_C6

A A

12

C6

10UF/6.3V

12

C7

1UF/6.3V

5

12

C8

1UF/6.3V

12

C9

0.1UF/16V

12

C10

0.1UF/16V

GND

12

C11

0.1UF/16V

+VCORE

C12

1UF/6.3V

12

12

4

C13

1UF/6.3V

12

C14

1UF/6.3V

12

C15

1UF/6.3V

12

C16

1UF/6.3V

3

12

C17

1UF/6.3V

12

C18

1UF/6.3V

12

C19

1UF/6.3V

12

C20

1UF/6.3V

12

2

C21

1UF/6.3V

GND

12

C22

1UF/6.3V

0106 1025

ASUSTeK COMPUTER INC

Size Project Name

Custom

Tuesday, January 06, 2009

Date: Sheet

T91

Title :

Engineer:

1

CPU-SILVERTHORNE (2)

Jerry Liu

Rev

10 57

1.2G

of

Page 11

5

4

3

2

1

http://hobi-elektronika.net

H_A#[31..3] 8H_D#[63:0]9

H_ADS# 8

H_ADSTB#0 8

H_ADSTB#1 8

H_BNR# 8

H_BPRI# 8

H_BR0# 8

H_CPURST# 8

CLK_BCLK_MCH# 7

CLK_BCLK_MCH 7

H_DBSY# 8

H_DEFER# 8

H_DINV#0 9

H_DINV#1 9

H_DINV#2 9

H_DINV#3 9

H_DPWR# 9

H_DRDY# 8

H_DSTBN#0 9

H_DSTBN#1 9

H_DSTBN#2 9

H_DSTBN#3 9

H_DSTBP#0 9

H_DSTBP#1 9

H_DSTBP#2 9

H_DSTBP#3 9

H_HIT# 8

H_HITM# 8

H_LOCK# 8

H_REQ#0 8

H_REQ#1 8

H_REQ#2 8

H_REQ#3 8

H_REQ#4 8

H_RS#0 8

H_RS#1 8

H_RS#2 8

H_TRDY# 8

SCH_CFG0 15

SCH_CFG1 15

SCH_BSEL2 15

1

T17Do Not Stuff

H_CPUSLP# 9

H_DPRSTP# 9

1

1

2

T18Do Not Stuff

H_PWRGD 8,9

H_DPSLP# 9

T21Do Not Stuff

+VCCP

R37

1KOhm

1%

H_GVREF

12

C24

0.1UF/16V

GND GND

1 2

1 2

R39

2KOhm

1%

FSB Signals Reference Voltage

+VCCP

<500 mil (55 Ohm)

T/B trace 5.5 ,

Space 25

H_CGVREF

C25

0.1UF/16V

FSB Signals CMOS Reference Voltage

0106 1025

ASUSTeK COMPUTER INC

Size Project Name

Custom

Date: Sheet

GND GND

CLK_BCLK_MCH

CLK_BCLK_MCH

Tuesday, January 06, 2009

12

#

T91

R41

1KOhm

1%

1 2

R42

1KOhm

1%

1 2

C461 Do Not Stuff/X

12

C462 Do Not Stuff/X

12

Title :

Poulsbo_HOST (1)

Engineer:

Jerry Liu

1

GND

of

Rev

1.2G

5711

D D

+VCCP

R36

221Ohm

1%

1 2

R38

100Ohm

1%

1 2

FSB Compensation Circuits

C C

Rreference Voltage

H_RCOMPO

R40

24.9Ohm

1%

1 2

GND

GNDGND

12

C23

0.1UF/16V

H_SWING

FSB I/O Buffers Calibrating

B B

H_NMI8

JP10 Do Not Stuff

H_SMI#8

H_PBE#8

+VCCP

A A

R46

56OHM

1 2

H_TESTIN#

5

1 2

JP13 Do Not Stuff

1 2

H_STPCLK#8

T19 Do Not Stuff

T20 Do Not Stuff

PM_THRMTRIP#_R8

H_INIT#8

H_INTR8

T16

Do Not Stuff

1

1

1

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_TESTIN#

H_RCOMPO

RESERVED5

RESERVED4

AF4

AA1

AC1

AD2

AB2

AF2

AB4

AF8

AE1

AB8

AJ1

AH2

AM8

AN1

AK4

AG1

AH8

AK8

AP8

AK2

AR1

AT8

AT2

AH4

AP4

AP2

AV4

BB6

AV6

AY8

BA1

AU1

AT6

AV8

BB4

AT4

AY6

AV10

AV2

BC1

BB2

AY2

BD2

BH4

BD10

BK10

BD6

BD4

BF2

BE1

BD8

BF4

BH10

BK6

BB8

BF6

BF10

BH6

AB10

AB6

AH6

AD10

AK6

T10

AT10

AP10

AM6

AF10

AF6

V8

V2

V4

Y2

U1

Y8

V6

U2A

H_D0#

H_D1#

H_D2#

H_D3#

H_D4#

H_D5#

H_D6#

H_D7#

H_D8#

H_D9#

H_D10#

H_D11#

H_D12#

H_D13#

H_D14#

H_D15#

H_D16#

H_D17#

H_D18#

H_D19#

H_D20#

H_D21#

H_D22#

H_D23#

H_D24#

H_D25#

H_D26#

H_D27#

H_D28#

H_D29#

H_D30#

H_D31#

H_D32#

H_D33#

H_D34#

H_D35#

H_D36#

H_D37#

H_D38#

H_D39#

H_D40#

H_D41#

H_D42#

H_D43#

H_D44#

H_D45#

H_D46#

H_D47#

H_D48#

H_D49#

H_D50#

H_D51#

H_D52#

H_D53#

H_D54#

H_D55#

H_D56#

H_D57#

H_D58#

H_D59#

H_D60#

H_D61#

H_D62#

H_D63#

H_NMI

H_SMI#

H_PBE#

H_SWING

H_STPCLK#

H_TESTIN#

H_RCOMPO

RESERVED5

RESERVED4

H_THRMTRIP#

H_INIT#

H_INTR

02G010018704

HOST

H_CPUPWRGD

H_A3#

H_A4#

H_A5#

H_A6#

H_A7#

H_A8#

H_A9#

H_A10#

H_A11#

H_A12#

H_A13#

H_A14#

H_A15#

H_A16#

H_A17#

H_A18#

H_A19#

H_A20#

H_A21#

H_A22#

H_A23#

H_A24#

H_A25#

H_A26#

H_A27#

H_A28#

H_A29#

H_A30#

H_A31#

H_ADS#

H_ADSTB0#

H_ADSTB1#

H_GVREF

H_BNR#

H_BPRI#

H_BREQ0#

H_CPURST#

H_CGVREF

H_CLKINN

H_CLKINP

H_DBSY#

H_DEFER#

H_DINV0#

H_DINV1#

H_DINV2#

H_DINV3#

H_DPWR#

H_DRDY#

H_DSTBN0#

H_DSTBN1#

H_DSTBN2#

H_DSTBN3#

H_DSTBP0#

H_DSTBP1#

H_DSTBP2#

H_DSTBP3#

H_HIT#

H_HITM#

H_LOCK#

H_REQ0#

H_REQ1#

H_REQ2#

H_REQ3#

H_REQ4#

H_RS0#

H_RS1#

H_RS2#

H_CPUSLP#

H_TRDY#

H_DPSLP#

H_DPRSTP#

CFG0

CFG1

BSEL2

M2

M8

K4

P2

F4

G1

M4

F6

H6

D2

H2

J1

F2

D4

D12

H12

G11

A7

A9

A11

B6

H8

F10

B10

D6

D10

B12

B4

D8

K6

H4

B8

Y10

R1

P10

L1

M6

AD4

K10

M10

H10

AD6

AD8

AM2

AY10

BK8

P6

J9

Y4

AL1

AW1

BH8

W1

AM4

AY4

BF8

V10

T6

Y6

P4

N1

K8

P8

K2

T4

T2

T8

AH10

F12

AP6

F8

AK10

J27

B34

F28

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_GVREF

H_CGVREF

JP11 Do Not Stuff

1 2

US15W D2 stage : 02G010018704

4

3

Page 12

5

4

3

2

1

http://hobi-elektronika.net

D D

MA_DQ[63:0]18

MA_DQ0

MA_DQ1

MA_DQ2

MA_DQ3

MA_DQ4

MA_DQ5

MA_DQ6

MA_DQ7

MA_DQ8

MA_DQ9

MA_DQ10

MA_DQ11

MA_DQ12

MA_DQ13

MA_DQ14

MA_DQ15

MA_DQ16

MA_DQ17

C C

B B

MA_DQ18

MA_DQ19

MA_DQ20

MA_DQ21

MA_DQ22

MA_DQ23

MA_DQ24

MA_DQ25

MA_DQ26

MA_DQ27

MA_DQ28

MA_DQ29

MA_DQ30

MA_DQ31

MA_DQ32

MA_DQ33

MA_DQ34

MA_DQ35

MA_DQ36

MA_DQ37

MA_DQ38

MA_DQ39

MA_DQ40

MA_DQ41

MA_DQ42

MA_DQ43

MA_DQ44

MA_DQ45

MA_DQ46

MA_DQ47

MA_DQ48

MA_DQ49

MA_DQ50

MA_DQ51

MA_DQ52

MA_DQ53

MA_DQ54

MA_DQ55

MA_DQ56

MA_DQ57

MA_DQ58

MA_DQ59

MA_DQ60

MA_DQ61

MA_DQ62

MA_DQ63

BG49

BG47

BE45

BC43

BE47

BC47

BC45

BK44

BK42

BG41

BK40

BC41

BG43

BJ43

BJ39

BG39

BC39

BK38

BG37

BK36

BJ37

BG35

BJ35

BC35

BK34

BG31

BG33

BK30

BC33

BJ33

BJ31

BC31

BJ29

BG29

BK28

BC29

BE27

BK26

BG25

BJ25

BC25

BG23

BK22

BJ21

BK24

BJ23

BG21

BC21

BK20

BJ19

BG17

BJ17

BG19

BC19

BC17

BK16

BG15

BC15

BJ13

BK12

BK14

BJ15

BC13

BC11

U2D

SM_DQ0

SM_DQ1

SM_DQ2

SM_DQ3

SM_DQ4

SM_DQ5

SM_DQ6

SM_DQ7

SM_DQ8

SM_DQ9

SM_DQ10

SM_DQ11

SM_DQ12

SM_DQ13

SM_DQ14

SM_DQ15

SM_DQ16

SM_DQ17

SM_DQ18

SM_DQ19

SM_DQ20

SM_DQ21

SM_DQ22

SM_DQ23

SM_DQ24

SM_DQ25

SM_DQ26

SM_DQ27

SM_DQ28

SM_DQ29

SM_DQ30

SM_DQ31

SM_DQ32

SM_DQ33

SM_DQ34

SM_DQ35

SM_DQ36

SM_DQ37

SM_DQ38

SM_DQ39

SM_DQ40

SM_DQ41

SM_DQ42

SM_DQ43

SM_DQ44

SM_DQ45

SM_DQ46

SM_DQ47

SM_DQ48

SM_DQ49

SM_DQ50

SM_DQ51

SM_DQ52

SM_DQ53

SM_DQ54

SM_DQ55

SM_DQ56

SM_DQ57

SM_DQ58

SM_DQ59

SM_DQ60

SM_DQ61

SM_DQ62

SM_DQ63

02G010018704

SM_BS0

SM_BS1

SM_BS2

SM_CK0

SM_CK1

SM_CK0#

SM_CK1#

SM_CKE0

SM_CKE1

SM_DQS0

SM_DQS1

SM_DQS2

SM_DQS3

SM_DQS4

SM_DQS5

SM_DQS6

SM_DQS7

SM_MA0

SM_MA1

SM_MA2

SM_MA3

SM_MA4

SM_MA5

SM_MA6

SM_MA7

SM_MA8

SM_MA9

SM_MA10

SM_MA11

SM_MA12

SM_MA13

SM_MA14

SM_VREF

SM_RAS#

SM_CAS#

SM_WE#

SM_CS0#

SM_CS1#

DDR SYSTEM MEMORY

SM_RCOMPO

SM_RCVENIN

SM_RCVENOUT

BE25

BA35

BG45

BE11

BJ45

BG11

BE39

BE37

BJ47

BJ41

BC37

BK32

BG27

BE23

BK18

BG13

BJ27

BA19

BA27

BA25

BE29

BC23

BE31

BA31

BA33

BA29

BE17

BE35

BE33

BE19

BA37

BE43

BE21

BA13

BA17

BA23

BA15

BE13

BA39

BE41

MA_BA1

MA_BA2

M_CLK_DDR0_R

M_CLK_DDR1_R

M_CLK_DDR0#_R

M_CLK_DDR1#_R

MA_DQS0

MA_DQS1

MA_DQS2

MA_DQS3

MA_DQS4

MA_DQS5

MA_DQS6

MA_DQS7

MA_MA0

MA_MA1

MA_MA2

MA_MA3

MA_MA4

MA_MA5

MA_MA6

MA_MA7

MA_MA8

MA_MA9

MA_MA10

MA_MA11

MA_MA12

MA_MA13

MA_MA14

SM_RCOMPOUT

MA_RCVENIN

MA_RCVENOUT

MA_CKE0 18,19

MA_CKE1 18,19

DDR_VREF 18

MA_RAS# 18,19

MA_CAS# 18,19

MA_WE# 18,19

MA_CS#0 18,19

MA_CS#1 18,19

R48

Note: TOTAL LENGTH <1"

0Ohm

MA_BA0

BC27

MA_BA[2:0] 18,19

MA_DQS[7:0] 18

MA_MA[14:0] 18,19

12

R47

1 2

30.1Ohm

+VTT_DDR

12

C26

0.1UF/16V

GND

M_CLK_DDR0_R

M_CLK_DDR1_R

M_CLK_DDR0#_R

M_CLK_DDR1#_R

R192

1 2

0Ohm

R193

1 2

0Ohm

R194

1 2

0Ohm

R195

1 2

0Ohm

GND

GND

GND

GND

12

12

12

12

C465

Do Not Stuff

/X

C466

Do Not Stuff

/X

C467

Do Not Stuff

/X

C468

Do Not Stuff

/X

M_CLK_DDR0 18

M_CLK_DDR1 18

M_CLK_DDR0# 18

M_CLK_DDR1# 18

A A

0106 1025

Title :

ASUSTek Computer INC.

Size Project Name

Custom

Date: Sheet

5

4

3

2

T91

Engineer:

Poulsbo_DDR2 (2)

Jerry Liu

12 57Tuesday, January 06, 2009

1

Rev

1.2G

of

Page 13

5

4

3

2

1

http://hobi-elektronika.net

+3VA

+3VS

D D

LPC_CLKRUN#37,38

C C

B B

A A

R49

Do Not Stuff

/X

1 2

+3VS

+3VS

+3VS

+3VS

1 2

Do Not Stuff

3 4

Do Not Stuff

5 6

Do Not Stuff

7 8

Do Not Stuff

R62 Do Not Stuff/X

R63 10KOhm

LPC_AD037,38,39

LPC_AD137,38,39

LPC_AD237,38,39

LPC_AD337,38,39

CLK_PCI_EC37

CLK_PCI_UART38

CLK_PCI_DEBUG39

INT_SERIRQ37,38

LPC_FRAME#37,38,39

LBKLT_CTRL22

1

1

L_DDC_CLK22

L_DDC_DATA22

LVDD_EN22

LA_CLKP22

LA_CLKN22

LA_DATAN022

LA_DATAN122

LA_DATAN222

1

LA_DATAP022

LA_DATAP122

LA_DATAP222

1

1 2

10KOhm

3 4

10KOhm

Do Not Stuff/X

5 6

10KOhm

7 8

10KOhm

Do Not Stuff/X

1 2

10KOHM

3 4

10KOHM

Do Not Stuff/X

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

INT_SERIRQ

LBKLT_EN22

T195

T196

12

T197

T198

T199

T200

T201

12

12

T23

T24

T25

T26

RN18A

RN18B

R53

RN18C

RN18D

R54

RN19A

RN19B

R57

RN3A

/X

RN3B

/X

RN3C

/X

RN3D

/X

12

12

R60 33Ohm

1 2

R196 33Ohm

1 2

R61 33Ohm

1 2

L_CTLA_CLK

L_CTLB_DATA

SD0_CD#

1

SD0_CMD

1

SD0_WP

1

1

1

1

1

SD1_CD#

SD1_CMD

SD1_WP

SD2_CD#

SD2_CMD

SD2_WP

LVDS pull-up

+3VS

U2B

K38

LPC_AD0

J39

LPC_AD1

A35

LPC_AD2

L39

LPC_AD3

F38

LPC_CLKOUT0

B36

LPC_CLKOUT1

D38

LPC_CLKOUT2

D36

LPC_CLKRUN#

B38

LPC_SERIRQ

K40

LPC_FRAME#

A33

L_BKLTCTL

A31

L_BKLTEN

D28

L_CTLA_CLK

K26

L_CTLB_DATA

A27

L_DDCCLK

H28

L_DDCDATA

D30

L_VDDEN

AF48

LA_CLKP

AF50

LA_CLKN

AJ43

LA_DATAN0

AK48

LA_DATAN1

AH48

LA_DATAN2

AG45

LA_DATAN3

AJ45

LA_DATAP0

AK50

LA_DATAP1

AH50

LA_DATAP2

AG43

LA_DATAP3

B18

SD0_CD#

D18

SD0_CLK

J15

SD0_CMD

H18

SD0_LED

F18

SD0_WP

H20

SD0_PWR#

H16

SD0_DATA0

A17

SD0_DATA1

K18

SD0_DATA2

F16

SD0_DATA3

K16

SD0_DATA4

B16

SD0_DATA5

D16

SD0_DATA6

K20

SD0_DATA7

B22

SD1_CD#

H22

SD1_CLK

F20

SD1_CMD

A21

SD1_LED

B20

SD1_WP

D20

SD1_PWR#

F22

SD1_DATA0

J19

SD1_DATA1

K22

SD1_DATA2

D22

SD1_DATA3

K24

SD2_CD#

D26

SD2_CLK

B24

SD2_CMD

D24

SD2_LED

B26

SD2_WP

A19

SD2_PWR#

J23

SD2_DATA0

A25

SD2_DATA1

F26

SD2_DATA2

A23

SD2_DATA3

F24

SD2_DATA4

H24

SD2_DATA5

H26

SD2_DATA6

E25

SD2_DATA7

G21

RESERVED18

02G010018704

NOTE:L_BKLTEN AND L_VDDEN

PULL DOWN IN CONNECTOR

SHEET

1 2

10KOhm

3 4

10KOhm

5 6

10KOhm

7 8

10KOhm

RN4A

RN4B

RN4C

RN4D

LPC BUS

LVDS

SDIO / MMC

L_CTLA_CLK

L_CTLB_DATA

L_DDC_CLK

L_DDC_DATA

RESERVED8

RESERVED0

RESERVED1

MISC SIGNALSSYSTEM MGMTSDVOPCIE RTC

RESERVED2

RESERVED3

INTVRMEN

DPRSLPVR

SDVO_CTRLCLK

SDVO_CTRLDATA

SDVOB_CLK

SDVOB_CLK#

SDVOB_INT

SDVOB_INT#

SDVOB_STALL

SDVOB_STALL#

SDVOB_TVCLKIN

SDVOB_TVCLKIN#

SDVOB_RED

SDVOB_RED#

SDVOB_GREEN

SDVOB_GREEN#

SDVOB_BLUE

SDVOB_BLUE#

PCIE_PERn1

PCIE_PERp1

PCIE_PETn1

PCIE_PETp1

PCIE_PERn2

PCIE_PERp2

PCIE_PETn2

PCIE_PETp2

PCIE_CLKINN

PCIE_CLKINP

PCIE_ICOMPI

PCIE_ICOMPO

RTC_X1

RTC_X2

RTCRST#

EXTTS

PWROK

SLPRDY#

SLPMODE

RSMRST#

T22

BK50

E49

B32

BE15

BA21

F48

F50

F46

H48

D32

C49

J49

D34

L45

L43

F30

A29

AV48

AV50

AU47

AU49

AN45

AN43

AP48

AP50

AM50

AM48

AT50

AT48

AR45

AR43

AW45

AW43

BB48

BB50

BA43

BA45

BE49

BD50

AY48

AY50

BA47

BA49

1

RTC_X1

RTC_X2

SCH_INTVRMEN

RTC_RST#

JP1 Do Not Stuff

1 2

JP3 Do Not Stuff

JP4 Do Not Stuff

PM_DPRSLPVR

1 2

1 2

C30 0.1UF/16V

C31 0.1UF/16V

C32 0.1UF/16V

C33 0.1UF/16V

C34 0.1UF/16V

C35 0.1UF/16V

C36 0.1UF/16V

C37 0.1UF/16V

C38 0.1UF/16V

C39 0.1UF/16V

C40 0.1UF/16V

C41 0.1UF/16V

PEG_COMP

1

1 2

1 2

1

1

1

1

1

1

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

CLK_PCIE_SCH#

CLK_PCIE_SCH

T216

RESERVED1 15

RESERVED2 18

RESERVED3 18

R51

10KOhm

1

T27

T28

T29

T30

T31

T32

BT1

SIDE1

SIDE2

WTOB_CON_2P

12G17100002Q

+3VS

12

PM_PWROK 39

PM_SLPRDY# 24,37

T206

PM_SLPMODE 37

SDVO_I2CCLK_SCH 20

SDVO_I2CDATA_SCH 20

SDVO_CLK 20

SDVO_CLK# 20

SDVO_RED 20

SDVO_RED# 20

SDVO_GREEN 20

SDVO_GREEN# 20

SDVO_BLUE 20

SDVO_BLUE# 20

PCIE_RXN1 28

PCIE_RXP1 28

PCIE_TXN1 28

PCIE_TXP1 28

PCIE_RXN2 24

PCIE_RXP2 24

PCIE_TXN2 24

PCIE_TXP2 24

CLK_PCIE_SCH# 7

CLK_PCIE_SCH 7

C463 Do Not Stuff/X

12

C464 Do Not Stuff/X

12

+RTCBAT

R50

1 2

1KOhm

3

1

1

2

2

4

GND

PM_SLPMODEPM_SLPRDY#

0

PM_RSMRST# 39

+1.5VS

R58

24.9Ohm

1%

1 2

GND

LPC pulled-up for EC

5

4

3

2

+3V_PL

+VCC_RTC

R182

Do Not Stuff

/NON_LATCH/X

1 2

R183

1KOhm

/PL

1 2

1

2

D1

BAT54CW

3

12

C27

1UF/10V

GND

GND

System Behavior

10 SCH ready to enter S3

0

SCH ready to enter S4/S5

RTC_X1

R52

10MOhm

RTC_X2

+VCC_RTC

R55

10KOhm

SCH_INTVRMEN

R56

Do Not Stuff

/X

0106 1025

ASUSTeK COMPUTER INC

Size Project Name

Custom

Date: Sheet of

RTCRST# RC delay

18~25ms

SR1 20KOhm

1 2

12

CLRTC1

12

Do Not Stuff

Place Near

Open Door

RTC Battery & RTC Reset

C28 15PF/50V

12

X1

32.768Khz

1 2

C29 15PF/50V

1UF/16V

12

12

12

SC1

GND

RTC Crystal

SCH_INTVRMEN

1 2

Enable (default)

1

Disable 0

SCH internal VR enable strap

for +V1.5 & +V1.05 VRs

1 2

GND

Internal VRM Enable Strap

Poulsbo_LVDS/SDVO

Title :

Engineer:

T91

Tuesday, January 06, 2009

1

RTC_RST#

GND

Jerry Liu

Rev

1.2G

5713

Page 14

5

R66

1 2

10KOhm

USB_PN032

USB_PP032

USB_PN132

USB_PP132

USB_PN233

USB_PP233

USB_PN323

USB_PP323

USB_PN443

USB_PP443

USB_PN525

USB_PP525

USB_PN634

USB_PP634

USB_PN743

USB_PP743

USB_OC#032

USB_OC#132

IDE_DDREQ30,31

IDE_IORDY30,31

IDE_IRQ30,31

IDE_DDACK#30,31

IDE_DIOW#30,31

IDE_DIOR#30,31

IDE_DCS#330,31

IDE_DCS#130,31

IDE_DD[15:0]

IDE_DA[2:0]

PCB_VID SR 0

+3VS

Do Not Stuff

/X

1 2

8.2KOhm

1 2

GND

PCB ID

USB_OC#0

USB_OC#1

USB_OC#2

USB_OC#3

USB_OC#4

USB_OC#5

USB_OC#6

USB_OC#7

USBRBIAS_PN

IDE_DA2

IDE_DA1

IDE_DA0

IDE_DD15

IDE_DD14

IDE_DD13

IDE_DD12

IDE_DD11

IDE_DD10

IDE_DD9

IDE_DD8

IDE_DD7

IDE_DD6

IDE_DD5

IDE_DD4

IDE_DD3

IDE_DD2

IDE_DD1

IDE_DD0

R75

PCB_ID0

R80

USB 0

USB PORT

USB 1

USB PORT

Card Reader

USB 2

USB 3

3.5G

USB 4 Touch Panel

Bluetooth

USB 5

D D

USB 6

Camera

2'nd Card Reader

USB 7

+3V

C C

IDE_DD[15:0]30,31

IDE_DA[2:0]30,31

USBRBIAS_PN

R73

22.6Ohm

1%

1 2

GND

B B

A A

+3VS

RN7A

1 2

10KOHM

3 4

RN7B

10KOHM

IDE_IORDY

IDE_IRQ

5

4

AE47

AE49

AD48

AD50

AB50

AB48

AA49

AA47

AA45

AA43

AC45

AC43

4

W45

W43

Y48

Y50

V50

V48

U47

U49

T50

T48

R43

R45

U43

U45

J43

D46

G45

B46

A37

F44

C47

E47

K42

J45

H40

B40

E43

H42

D42

F40

A43