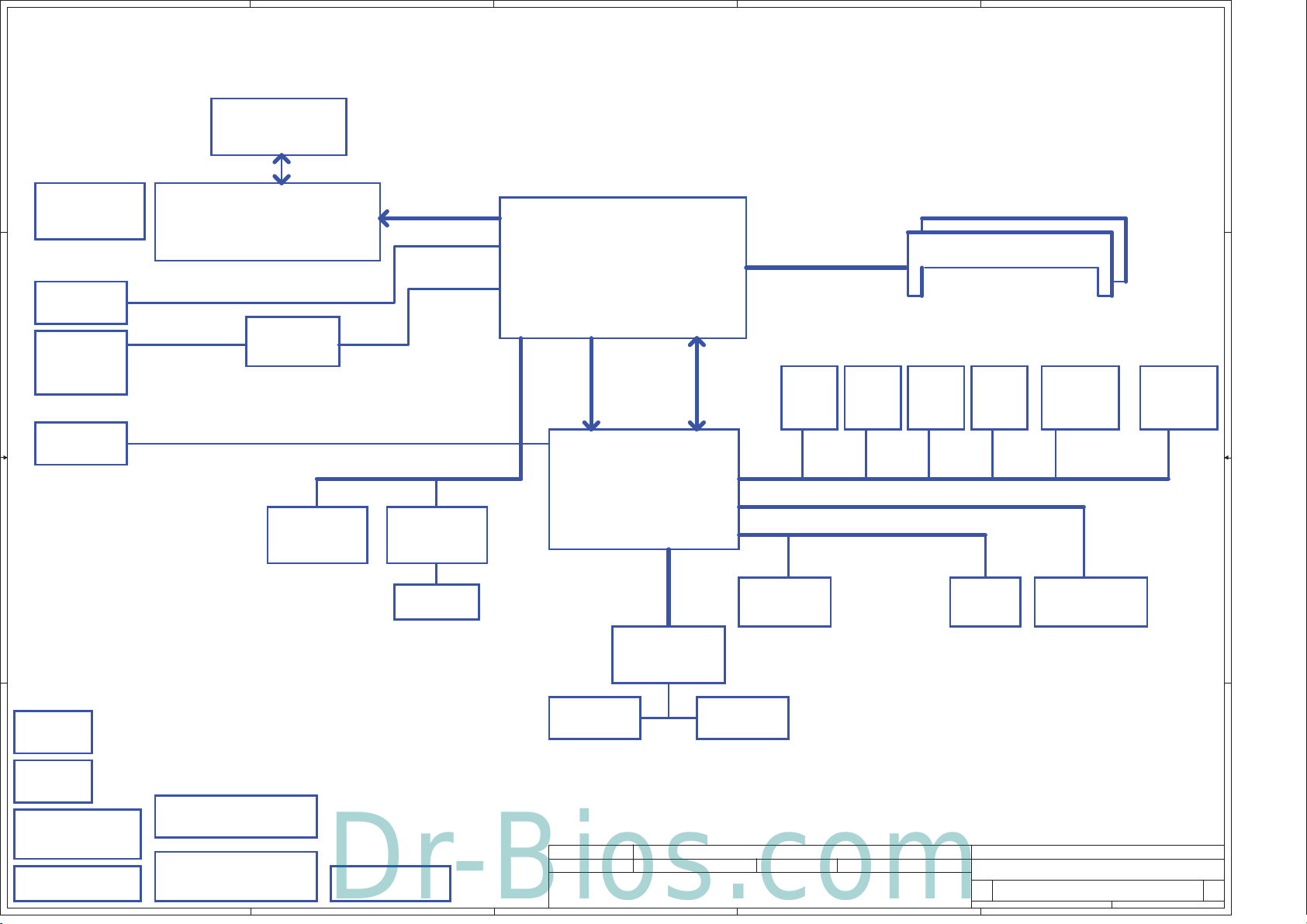

Asus K43T,K43TA,K43TK,K43TY Schematic

A

Dr-Bios.com

1 1

B

C

D

E

Compal Confidential

2 2

QBL50 Schematics Document

AMD Sabine

APU Llano / Hudson M2_M

UMA only / PX

3 3

Muxless with BACO

3 / Vancouver Whistler

2011-04-25

Rev:1.0

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/03/04 2011/12/31

2011/03/04 2011/12/31

2011/03/04 2011/12/31

pal Secret Data

pal Secret Data

pal Secret Data

Com

Com

Com

Deciphered Date

Deciphered Date

Deciphered Date

lectronics, Inc.

lectronics, Inc.

Compal E

Compal E

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal E

Cover Page

Cover Page

Cover Page

QB

QB

QB

L50 LA-7551P

L50 LA-7551P

L50 LA-7551P

lectronics, Inc.

153Wednesday, April 27, 2011

153Wednesday, April 27, 2011

153Wednesday, April 27, 2011

E

1.0

1.0

1.0

A

Dr-Bios.com

B

C

D

E

Com

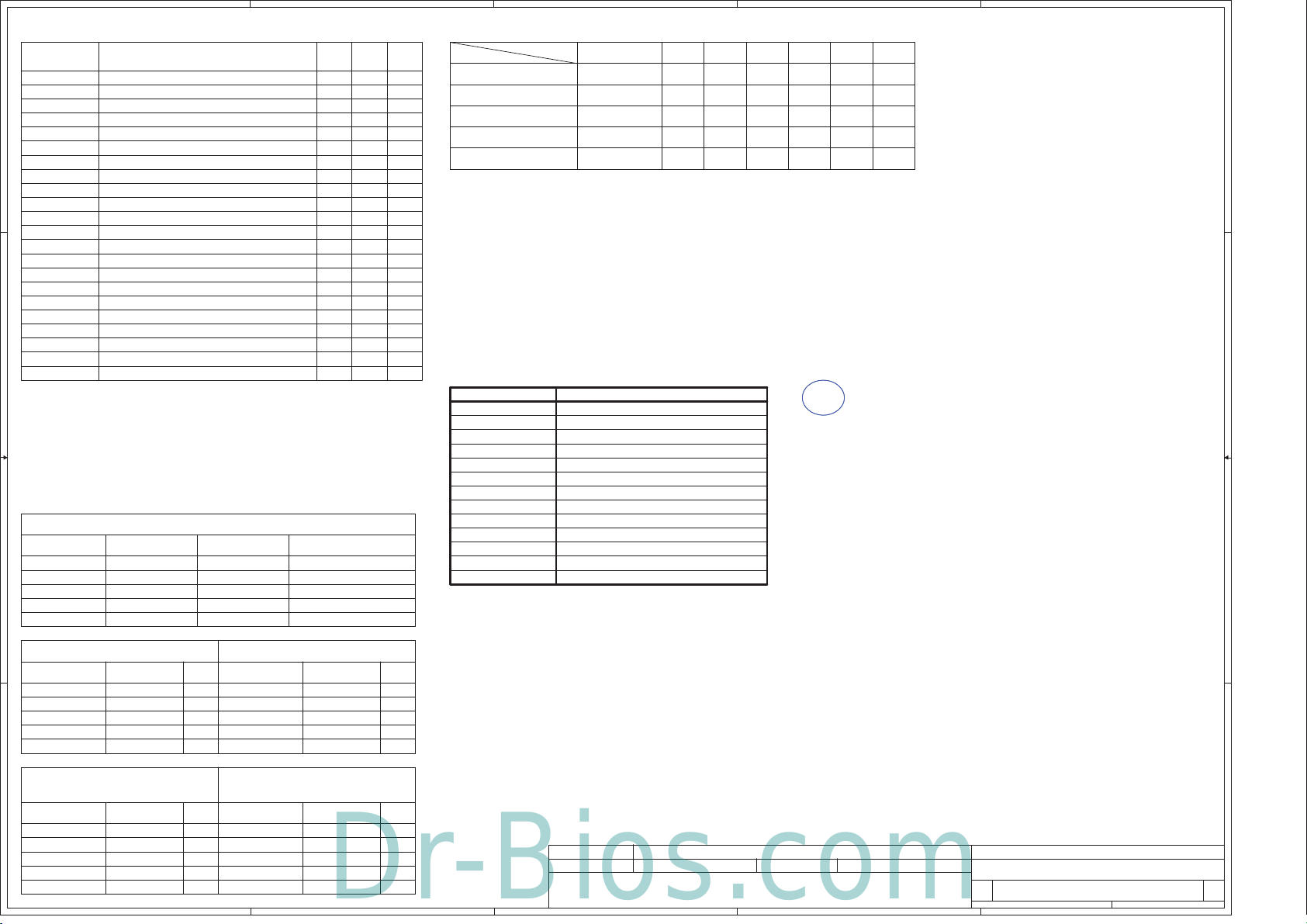

Model Nam

1 1

pal Confidential

e : QBL50

VRAM

128M16 x 4/8

1G/2G

page 23, 24

Sabine

DDR3

hermal Sensor

T

AD

M1032

page 19

Vancuver Whistler

ATI

uF

CBGA-962

Page 18~22

8

GF

X x 4

APU HDMI

(UMA / Muxless)

D

P x1 (DP0 T XP/N0)

Gen2GFX x

AMD FS1 APU

Llano

uP

GA-722 Package

Memory BUS(

D

ual Channel

1

.5V DDRIII 800~1333MHz

DDR3)

204pin DDRIII-SO-DIMM X

BANK 0, 1, 2, 3

Page 11,12

2

HDMI Conn.

page 28

LV

2 2

LVDS Conn.

DS

Reserve eDP

page 27

RT Conn.

C

page 27

Travis LVDS

Translator

page 26

F

CH CRT (VGA DAC)

GPP0GPP1

P_

GPP x 2

GEN1

DP

(DP1 TXP/ N 0~4)

Hudson-M2/M3

uFCBGA-656

MINI Card 1

WLAN

3 3

page 32

LAN(GbE)

RTL8111E-VL

RJ

45

page 29

page 29

Page 6~10

x 4

FCH

Page 13~17

UMI

LPC BUS

USB

B

US

3V 48MHz

3.

HD Au

dio

S-ATA

S

ATA HDD1

Conn.

page 33

2

page 34

Port 0 Port 5

3V 24.576MHz/48Mhz

3.

Gen

2

2/

USB

USB3.0

page 34

Port 10

USB

(LS-7322P)

port 0

2

page 30

CMOS

Ca

ODD

C

onn.

page 33

page 27

mera

Port2 Port 3

port 1

(with BT)

HDA Co

ALC269

Mi

ni Card

page 32

dec

page 30

C

ard Reader

RTS5137

page 31

Port 4

ENE KB930

page 36

ouch Pad Int.KBD

T

LED

page 37

RTC CKT.

4 4

page 25

DC/DC

Interface CKT

Po

wer Circuit

.

page 39

page 40~48

A

ernal board

Ext

L

S-7321P

Power/B

S-7322P

L

Audio BD

page 35

page 30

BIOS ROM

EC BIOS

(2M)

B

page 35

page 38

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/03/04 2011/12/31

2011/03/04 2011/12/31

2011/03/04 2011/12/31

page 38

pal Secret Data

pal Secret Data

pal Secret Data

Com

Com

Com

Deciphered Date

Deciphered Date

Deciphered Date

D

lectronics, Inc.

lectronics, Inc.

Compal E

Compal E

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal E

B

B

B

lock Diagrams

lock Diagrams

lock Diagrams

QB

QB

QB

L50 LA-7551P

L50 LA-7551P

L50 LA-7551P

lectronics, Inc.

253Wednesday, April 27, 2011

253Wednesday, April 27, 2011

253Wednesday, April 27, 2011

E

1.0

1.0

1.0

5

Dr-Bios.com

4

3

2

1

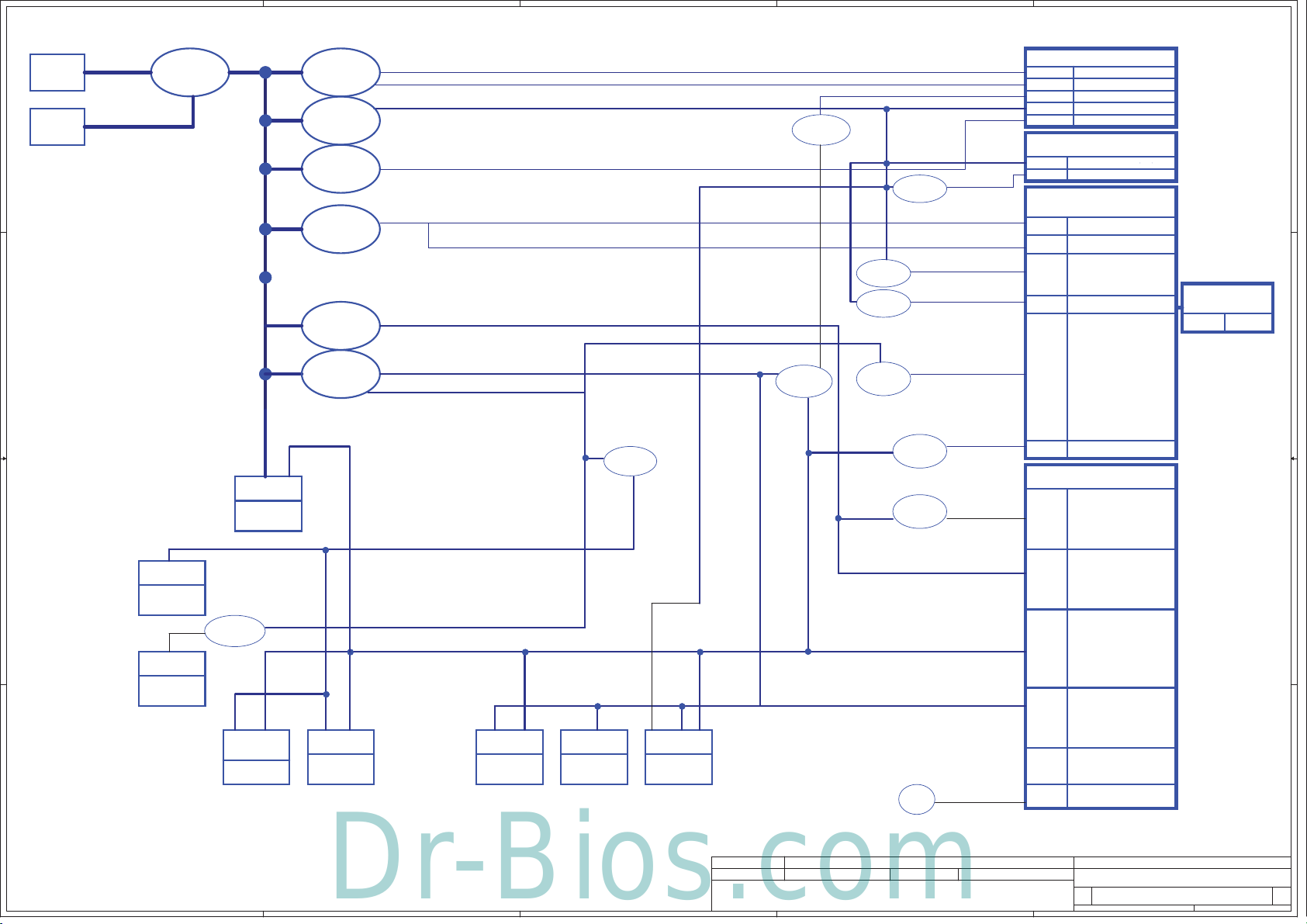

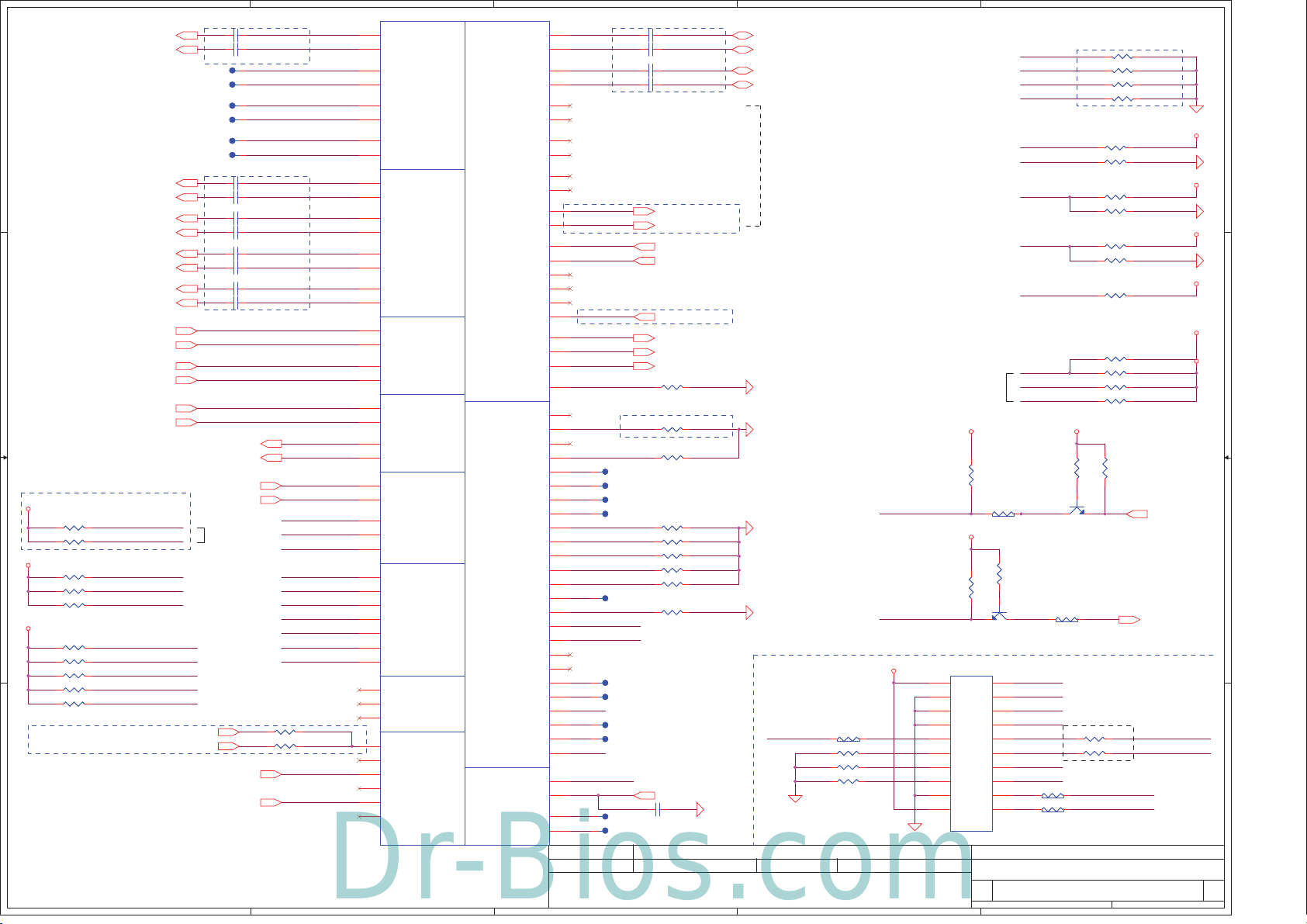

CL

OCK DISTRIBUTION

MEM_MB_CLK1_P/N

MEM_MB_CLK7_P/N

AM

S1 SOCKET

_AUX

DP0

A_

SODIMM

MEM_MA_CLK1_P/N

MEM_MA_CL

1066~1600MHz

K7_P/N

D

U_DISP_CLKP/N

AP

100M

Hz

U_CLKP/N

AP

100M

Hz

AM

I VGA

AT

histler

W

AMD

FCH

Huds

on-M2/M3

Internal CLK GEN

32.768KHz 25MHz

D

C

LK_PEG_VGAP/N

100M

Hz

PP_CLK

G

100M

Hz

D D

C C

B_

SODIMM

1066~1600MHz

CPU F

VDS Transtator

L

DISPLAY DISTRIBUTION

LVDS PATH

:

APU HDMI PATH

:

U_TXOUT[0:2]+/-

AP

APU_TXOUT_CLK+/APU_TZOUT[0:2]+/APU_TZOUT_CLK+/APU_LVDS_CLK/DATA

LVDS_OUT

R

TD2132

_IN

DP

TX

OUT[0:2]+/TXCLK+/TZOUT[0:2]+/TZCLK+/I2CC_SCL/DA

VDS CONN

L

R

C

0_TXP/N[0:1]

DP

0_AUXP/N

DP

B B

W

LAN

PP1

G

Gb

Mini PCI Socket

E LAN

25MHz

GPP0

AP

DP

FC

DP0

U

PC

IE_GFX[0:7]

1

PCIE_GFX[12:15]

C

C

PC

IE_GFX[0:7]

VGA

H

LS

R

A A

HDM

I CONNCRT CONN

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/08/04 2011/12/31

2010/08/04 2011/12/31

2010/08/04 2011/12/31

3

C

C

C

ompal Secret Data

ompal Secret Data

ompal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

CLOCK / DI

CLOCK / DI

CLOCK / DI

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

QBL50 LA-7551P

QBL50 LA-7551P

QBL50 LA-7551P

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

SPLAY DISTRIBUTION

SPLAY DISTRIBUTION

SPLAY DISTRIBUTION

1

1.0

1.0

353Wednesday, April 27, 2011

353Wednesday, April 27, 2011

353Wednesday, April 27, 2011

1.0

A

Dr-Bios.com

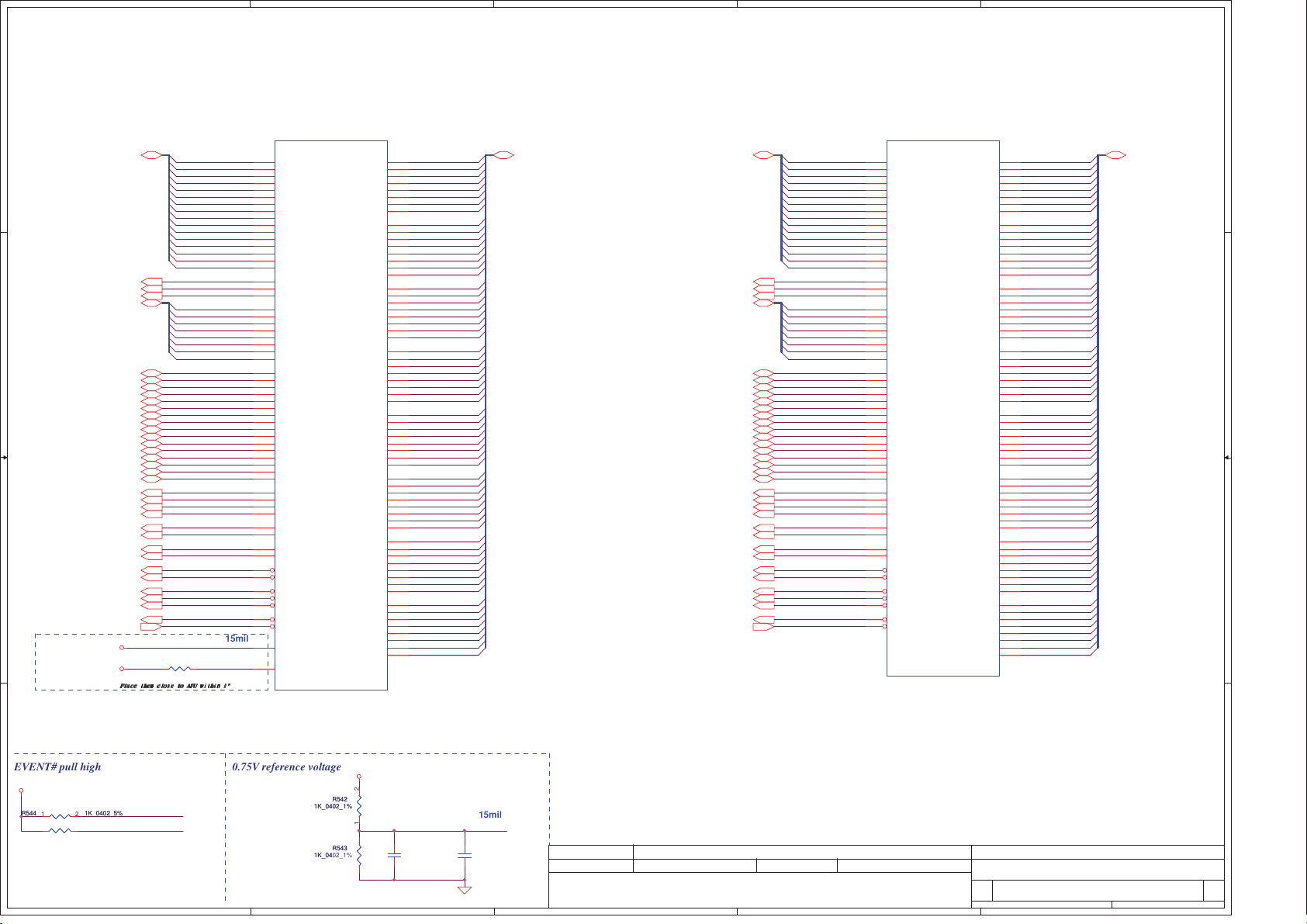

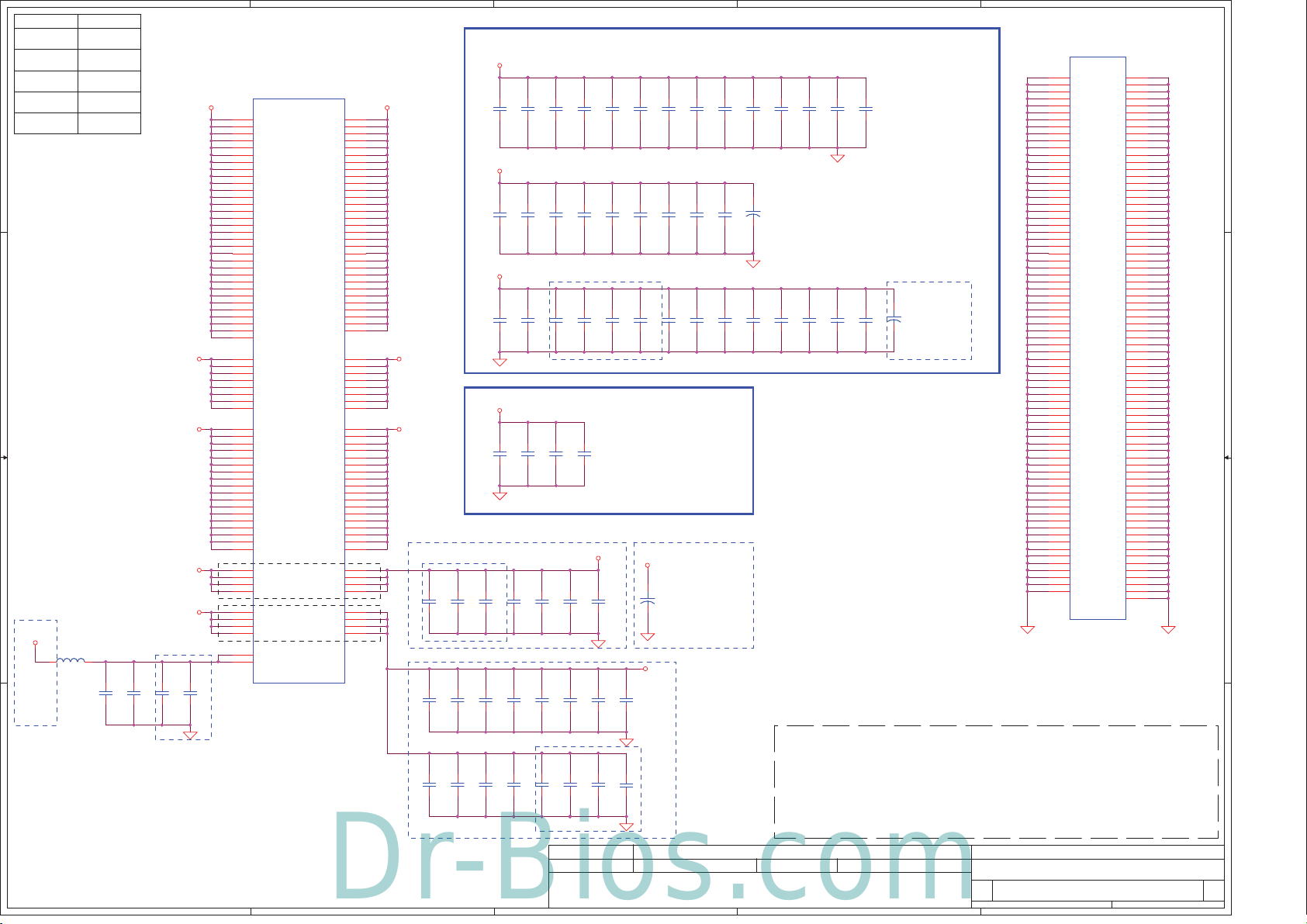

oltage Rails

V

Power Plane Description

VIN

B+

PU_CORE

+C

1 1

+C

PU_CORE_NB ON OFF OFF

+VGA_CORE OFFOFFON0.95-1.2V switched power rail

+0.75VS ONON OFF0.75V switc hed power rail f or DDR terminat or

+1.0VSG ON OFF OFF1.0V switched power rail for VGA

1ALW 1.1V switched power rail for FCH ON ON*ON

+1.

+1.1VS

+1.2VS ON OFF OFF

+1.5V ON

5VS

+1.

8VSG OFFON OFF1.8V switched power rail

+1.

+2.5VS

+3VALW

+LAN_IO ONONON

+3VS

+5VALW

+5VS

2 2

+VSB ON ON*

+R

TCVCC

ote : ON* means that t his power plane is ON only with A C power available, otherwise it is OFF .

N

Adapter power supply ( 19V)

AC or battery power rail for power circuit.

Core voltage for CPU

Vo

ltage for On-die VGA of A PU

1.2V switched power rail for APU

1

.5V power rail for CPU VDDIO and DDR

1.5V switched power rail

2.5V for CP U_VDDA

3.3V always on power rail

3.3V power rail for LAN

3.3V switched power rail

5V always on power rail

5V switched power rail

VSB always on power rail

RTC power

B

S3 S5

S1

N/A N/A N/A

ON OFF

ON OFF OFF1.1V switched power rail for FCH

ON OFF

ON

ON

ON

ON

ON

ON

N/AN/AN/A

OFF

OFF

ON

OFF

OFF

OFF

ON ON*

OFF

OFF

ON

ON*

OFF

OFFON

ONON

STATE

SIGNAL

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

BTO Opt

ion Table

BTO ItemBOM Structure

V

GA@ Use VGA (Mux)

M2@ Use Hudson-M2

M3@ Use Hudson-M3

RAM ID TableX76@

V

C

SLP_S3#

SLP_S4# SLP_S5# +VALW +V +VS Clock

HIGH HIGH HIGH

HIGHHIGHHIGH

HIGH

LOW

LOW

HIGH

HIGH

LOW

LOW

LOW

LOW

ON

ON

ON

ON

ON

ON

ON

ON

OFF

OFF

M3@U25

M3@

F

F

Part Number = SA000043ID0

Part Number = SA000043ID0

BOM

CH M3

CH M3

ON

ON

OFF

OFF

OFF

5

U2

Config

D

E

ON

LOW

OFF

OFF

OFF

USB30@ USB30 on M/B

USB20@ USB20 on M/B

x =

1 is read cmd, x= 0 is writee cmd.

External PCI Devices

D

evice

3 3

E

C SM Bus1 address EC SM Bus2 address

D

evice Address HEX

art Battery

Sm

FCH

Bus 0 address

SM

4 4

D

evice Address Device Address

DDR DIMM1

DDR DIMM2

ID

SEL#

0001 011X b

1101 000X b

1101 001X b

A

RE

Q#/GNT#

D

evice Address HEX

DI ADM1032 (VGA)

A

16H

(

APU)

TD2132S (TL)

R

I

nterrupts

FCH

Bus 1 address

SM

HE

X

D0

D2

1001 101X b

9A

H

HE

X

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2010/08/04 2011/12/31

2010/08/04 2011/12/31

2010/08/04 2011/12/31

pal Secret Data

pal Secret Data

pal Secret Data

Com

Com

Com

Deciphered Date

Deciphered Date

Deciphered Date

lectronics, Inc.

lectronics, Inc.

Compal E

Compal E

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal E

Notes List

Notes List

Notes List

QB

QB

QB

L50 LA-7551P

L50 LA-7551P

L50 LA-7551P

lectronics, Inc.

453Friday, April 29, 2011

453Friday, April 29, 2011

453Friday, April 29, 2011

E

1.0

1.0

1.0

5

Dr-Bios.com

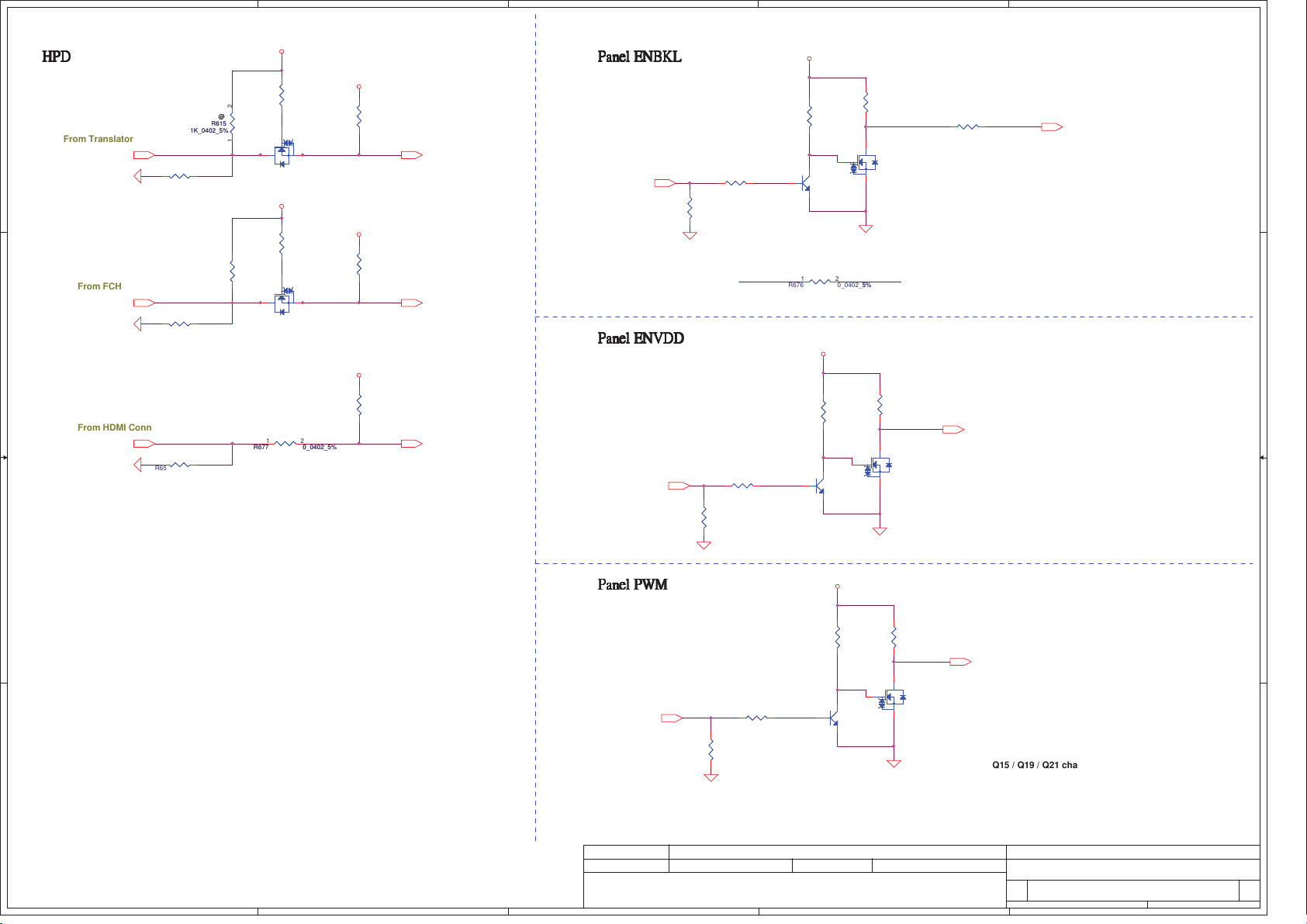

BAT

TERY

12.6V

AC ADAPTO

D D

19V 90W

BATT+

R

VI

PU101

CHARGER

N

B+

C C

+INVPWR_B+

LCD panel

15.6"

B+ 300mA

+3.

3 350mA

FA

B B

N Control

APL5607

+

5VS 500mA

U54/U55

AP2301MPG

+USB_VCCA

+USB_VCCB

P

U201

ISL6267HRZ-T

P

U501

RT8209MGQW

PU801

RT8209MGQW

P

U901

RT8237CZQW

U701

P

RT8209MGQW

U301

P

RT8205LZQW

+3VS

+5VS

USB X3

+5

V

Dual+1

2.5A

SA

TA

HDD*2

ODD*1

V 3A

+5

+3.3V

A A

A

udio Codec

ALC269-GR

+5V 45mA

+3.3VS 25mA

4

+CPU_CORE

+CPU_CORE_NB

+1.5V

+1.2VS

+VGA_CORE

+1.1VALW

+3VALW

+5VALW

+5VALW

EC

ENE KB930

+3.3VALW 30mA

+3.3VS 3mA

+3VS

+3VALW

LA

N

RTL8111E

+3.3VALW 201mA

U3

3

SI4800

3

+1.5VS

M

ini Card

+1.5VS 500mA

+3.3VS 1A

+3.3VALW 330mA

+2.5VS

PU603

APL5508-25DC

U4

0

SI4800

P

U602

APL5930KAI

U4

1

AO4430L

P

U401

SY8033BDBC

2

U601

P

APL5336KAI

+1.0VSG

+1.5VSG

+1.8VSG

J14

P

U3

9

AO4430L

RTC

Bettary

+0.75VS

+3VSG

+1.1VS

+CPU_CORE

+CPU_CORE_NB

+2.5VS

+1.5V

+1.2VS

+0.75VS

+VGA_CORE

+VDDCI

+1.0VSG

+1.5VSG

+1.8VSG

+3VSG

+1.1VS

+1.1VALW

+3VS

+3VALW

D APU FS1

AM

0.

0.

+2.5VS

+1.5V

+1.2VS

+1

+0.75VS

0.85~1.1V

0.

+1.

+1.5VSG

+1.8VSG

+3VSG

+1.1VS

+1.

+3VS

+3VALW

GND

VDD CORE 54A

7~1.475V

7~1.475V

VDDNB 27.5A

VDDA 500mA

VDDIO 4.6A

VDDR 6.7A

R

AM DDRIII SODIMM X2

VDD_

.5V

V

GA ATI

Whistler/Seymour/Granville

9~1.0V

0VSG

CH AMD Hudson M2/M3

F

1VALW

MEM 4A

TT_MEM 0.5A

V

VDDC 47A

VDDCI 4.6A

DPLL_VDDC: 125 mA

SPV10: 120 mA

PCIE_VDDC: 2000 mA

D

P[A:E]_VDD10: 680 mA

3400 mA

VDDR1:

PLL_PVDD:

75 mA

TSVDD: 20 mA

AVDD: 70 mA

VDD1DI: 100 mA

VDD2DI: 50 mA

A2VDDQ: 1.5 mA

VDD_CT: 110 mA

VDDR4: 170 mA

PCIE_PVDD: 40 mA

MPV18: 150 mA

SPV18: 75 mA

PCIE_VDDR: 400 mA

DP[A:F]_VDD18: 920 mA

DP[A:F]_PVDD: 120 mA

130 mA

A2VDD:

VDDR3: 60 mA

VDDPL_11_DAC: 7 mA

VDDAN_11_ML: 226 mA

VDDCR_11: 1007 mA

VDDAN_11_CLK: 340 mA

VDDAN_11_PCIE: 1088 mA

VDDAN_11_SATA: 1337 mA

VDDAN_11_USB_S: 140 mA

VDDCR_11_USB_S: 197 mA

VDDAN_11_SSUSB_S: 282 mA

VDDCR_11_SSUSB_S: 424 mA

VDDCR_11_S: 187 mA

VDDPL_11_SYS: 70 mA

V

DDIO_33_PCIGP: 131 mA

VDDPL_33_SYS:

VDDPL_33_DAC: 20 mA

VDDPL_33_ML: 20 mA

VDDAN_33_DAC: 200 mA

VDDPL_33_PCIE: 43 mA

VDDPL_33_SATA: 93 mA

VDDIO_AZ_S: 26 mA

VDDPL_33_SSUSB_S: 20 mA

VDDPL_33_USB_S: 17 mA

VDDAN_33_USB_S: 658 mA

VDDIO_33_S: 59 mA

VDDXL_33_S: 5 mA

VDDAN_33_HWM_S: 12 mA

VDDIO_33_GBE_S

VDDCR_11_GBE_S

VDDIO_GBE_S

VDDBT_RTC_GRTC BAT

47 mA

1

RAM 1GB/2GB

V

64M / 128Mx16 * 4 / 8

5VSG 2.4 A

+1.

5

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY TH IRD PARTY WITHOUT PRIOR WR ITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY TH IRD PARTY WITHOUT PRIOR WR ITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

MAY BE USED BY OR DISCLOSED TO ANY TH IRD PARTY WITHOUT PRIOR WR ITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/08/04 2011/12/31

2010/08/04 2011/12/31

2010/08/04 2011/12/31

Compal Secret Dat a

Compal Secret Dat a

Compal Secret Dat a

Deciphered Dat e

Deciphered Dat e

Deciphered Dat e

2

Title

Title

Title

POWER DELIVE RY CHART

POWER DELIVE RY CHART

POWER DELIVE RY CHART

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

QBL50 LA-7551P

QBL50 LA-7551P

QBL50 LA-7551P

Date: Sheet

Date: Sheet

Date: Sheet

1

553Wednesday, April 27, 2011

553Wednesday, April 27, 2011

553Wednesday, April 27, 2011

of

of

of

1.0

1.0

1.0

A

Dr-Bios.com

CIE_GTX_C_FRX_P[0..7]18

P

CIE_GTX_C_FRX_N[0..7]18

P

JC

JC

PU1A

PU1A

PCI EXPRESS

P

CIE_GTX_C_FRX_P0

CIE_GTX_C_FRX_N0

P

P

1 1

2 2

P

CIE_DTX_C_FRX_P029

CIE_DTX_C_FRX_N029

3 3

4 4

P

P

CIE_DTX_C_FRX_P132

CIE_DTX_C_FRX_N132

P

UMI_MTX_C_FRX_P013

UMI_MTX_C_FRX_N013

UMI_MTX_C_FRX_P113

UMI_MTX_C_FRX_N113

UMI_MTX_C_FRX_P213

UMI_MTX_C_FRX_N213

UMI_MTX_C_FRX_P313

UMI_MTX_C_FRX_N313

+1.2VS

CIE_GTX_C_FRX_P1

P

CIE_GTX_C_FRX_N1

P

CIE_GTX_C_FRX_P2

CIE_GTX_C_FRX_N2

P

CIE_GTX_C_FRX_P3

P

CIE_GTX_C_FRX_N3

P

P

CIE_GTX_C_FRX_P4

P

CIE_GTX_C_FRX_N4

P

CIE_GTX_C_FRX_P5

P

CIE_GTX_C_FRX_N5

CIE_GTX_C_FRX_P6

P

CIE_GTX_C_FRX_N6

P

CIE_GTX_C_FRX_P7

P

P

CIE_GTX_C_FRX_N7

1 2

R539 196_0402_1%R539 196_0402_1%

P_ZVDDP

AA8

AA9

Y7

Y8

W5

W6

W8

W9

V7

V8

U5

U6

U8

U9

T7

T8

R5

R6

R8

R9

P7

P8

N5

N6

N8

N9

M7

M8

L5

L6

L8

L9

AC5

AC6

AC8

AC9

AB7

AB8

AA5

AA6

AF8

AF7

AE6

AE5

AE9

AE8

AD8

AD7

K5

AMD_TOPEDO_FS-1

AMD_TOPEDO_FS-1

GFX_RXP0

P_

GFX_RXN0

P_

GFX_RXP1

P_

P_

GFX_RXN1

P_

GFX_RXP2

GFX_RXN2

P_

P_GFX_RXP3

GFX_RXN3

P_

P_

GFX_RXP4

GFX_RXN4

P_

P_

GFX_RXP5

P_

GFX_RXN5

P_GFX_RXP6

GFX_RXN6

P_

GFX_RXP7

P_

GFX_RXN7

P_

GFX_RXP8

P_

P_

GFX_RXN8

P_

GFX_RXP9

P_

GFX_RXN9

GFX_RXP10

P_

P_GFX_RXN10

GFX_RXP11

P_

P_

GFX_RXN11

GFX_RXP12

P_

P_

GFX_RXN12

P_

GFX_RXP13

P_

GFX_RXN13

GFX_RXP14

P_

GFX_RXN14

P_

GFX_RXP15

P_

GFX_RXN15

P_

P_

GPP_RXP0

P_

GPP_RXN0

P_GPP_RXP1

P_

GPP_RXN1

GPP_RXP2

P_

GPP_RXN2

P_

P_GPP_RXP3

P_GPP_RXN3

P_UMI_RXP0

P_UMI_RXN0

P_UMI_RXP1

P_UMI_RXN1

P_UMI_RXP2

P_UMI_RXN2

P_UMI_RXP3

P_UMI_RXN3

P_ZVDDP

PCI EXPRESS

GPPUMI-LINK GRAPHICS

GPPUMI-LINK GRAPHICS

B

CONN@

CONN@

GFX_TXP0

P_

GFX_TXN0

P_

GFX_TXP1

P_

P_

GFX_TXN1

P_

GFX_TXP2

GFX_TXN2

P_

P_GFX_TXP3

GFX_TXN3

P_

P_

GFX_TXP4

GFX_TXN4

P_

P_

GFX_TXP5

P_

GFX_TXN5

P_GFX_TXP6

GFX_TXN6

P_

GFX_TXP7

P_

GFX_TXN7

P_

GFX_TXP8

P_

P_

GFX_TXN8

P_

GFX_TXP9

P_

GFX_TXN9

GFX_TXP10

P_

P_GFX_TXN10

GFX_TXP11

P_

P_

GFX_TXN11

GFX_TXP12

P_

P_

GFX_TXN12

P_

GFX_TXP13

P_

GFX_TXN13

GFX_TXP14

P_

GFX_TXN14

P_

GFX_TXP15

P_

GFX_TXN15

P_

P_

GPP_TXP0

P_

GPP_TXN0

P_GPP_TXP1

P_

GPP_TXN1

GPP_TXP2

P_

GPP_TXN2

P_

P_GPP_TXP3

P_GPP_TXN3

P_UMI_TXP0

P_UMI_TXN0

P_UMI_TXP1

P_UMI_TXN1

P_UMI_TXP2

P_UMI_TXN2

P_UMI_TXP3

P_UMI_TXN3

P_ZVSS

PC

AA2

PC

AA3

PC

Y2

PC

Y1

PC

Y4

PC

Y5

PC

W2

PC

W3

PC

V2

PC

V1

PC

V4

PC

V5

PC

U2

PC

U3

PC

T2

PC

T1

T4

T5

R2

R3

P2

P1

P4

P5

P

N2

P

N3

P

M2

PCIE_FTX_GRX_N13

M1

P

M4

P

M5

P

L2

P

L3

PCIE_FTX_DRX_P0

AD4

PC

AD5

PC

AC2

PCIE_FTX_DRX_N1

AC3

AB2

AB1

AB4

AB5

UMI_FTX_MRX_P0

AF1

UMI_FTX_MRX_N0

AF2

UMI_FTX_MRX_P1

AF5

UMI_FTX_MRX_N1

AF4

UMI_FTX_MRX_P2

AE3

UMI_FTX_MRX_N2

AE2

UMI_FTX_MRX_P3

AD1

UMI_FTX_MRX_N3

AD2

P_ZVSS

K4

IE_FTX_GRX_P0

IE_FTX_GRX_N0

IE_FTX_GRX_P1

IE_FTX_GRX_N1

IE_FTX_GRX_P2

IE_FTX_GRX_N2

IE_FTX_GRX_P3

IE_FTX_GRX_N3

IE_FTX_GRX_P4

IE_FTX_GRX_N4

IE_FTX_GRX_P5

IE_FTX_GRX_N5

IE_FTX_GRX_P6

IE_FTX_GRX_N6

IE_FTX_GRX_P7

IE_FTX_GRX_N7

CIE_FTX_GRX_P12

CIE_FTX_GRX_N12

CIE_FTX_GRX_P13

CIE_FTX_GRX_P14

CIE_FTX_GRX_N14

CIE_FTX_GRX_P15

CIE_FTX_GRX_N15

IE_FTX_DRX_N0

IE_FTX_DRX_P1

1 2

R540 196_0402_1%R540 196_0402_1%

917 0.1U_0402_16V7KVGA@C917 0.1U_0402_16V7KVGA@

C

1 2

C

918 0.1U_0402_16V7KVGA@C918 0.1U_0402_16V7KVGA@

1 2

919 0.1U_0402_16V7KVGA@C919 0.1U_0402_16V7KVGA@

C

1 2

C

920 0.1U_0402_16V7KVGA@C920 0.1U_0402_16V7KVGA@

1 2

C

921 0.1U_0402_16V7KVGA@C921 0.1U_0402_16V7KVGA@

1 2

C

922 0.1U_0402_16V7KVGA@C922 0.1U_0402_16V7KVGA@

1 2

923 0.1U_0402_16V7KVGA@C923 0.1U_0402_16V7KVGA@

C

1 2

924 0.1U_0402_16V7KVGA@C924 0.1U_0402_16V7KVGA@

C

1 2

C

925 0.1U_0402_16V7KVGA@C925 0.1U_0402_16V7KVGA@

1 2

926 0.1U_0402_16V7KVGA@C926 0.1U_0402_16V7KVGA@

C

1 2

C

927 0.1U_0402_16V7KVGA@C927 0.1U_0402_16V7KVGA@

1 2

C928 0.1U_0402_16V7KVGA@C928 0.1U_0402_16V7KVGA@

1 2

C

929 0.1U_0402_16V7KVGA@C929 0.1U_0402_16V7KVGA@

1 2

930 0.1U_0402_16V7KVGA@C930 0.1U_0402_16V7KVGA@

C

1 2

931 0.1U_0402_16V7KVGA@C931 0.1U_0402_16V7KVGA@

C

1 2

932 0.1U_0402_16V7KVGA@C932 0.1U_0402_16V7KVGA@

C

1 2

C

C

950 0.1U_0402_16V7K

950 0.1U_0402_16V7K

1 2

C

C

951 0.1U_0402_16V7K

951 0.1U_0402_16V7K

1 2

C952 0.1U_0402_16V7KC952 0.1U_0402_16V7K

1 2

953 0.1U_0402_16V7K

953 0.1U_0402_16V7K

C

C

1 2

C956 0.1U_0402_16V7KC956 0.1U_0402_16V7K

1 2

C957 0.1U_0402_16V7KC957 0.1U_0402_16V7K

1 2

C958 0.1U_0402_16V7KC958 0.1U_0402_16V7K

1 2

C959 0.1U_0402_16V7KC959 0.1U_0402_16V7K

1 2

C960 0.1U_0402_16V7KC960 0.1U_0402_16V7K

1 2

C961 0.1U_0402_16V7KC961 0.1U_0402_16V7K

1 2

C962 0.1U_0402_16V7KC962 0.1U_0402_16V7K

1 2

C963 0.1U_0402_16V7KC963 0.1U_0402_16V7K

1 2

2

1

0

CK

C

To H

DMI

CIE_FTX_C_GRX_P[0..7] 18

P

CIE_FTX_C_GRX_N[0..7] 18

P

P

CIE_FTX_C_GRX_P0

CIE_FTX_C_GRX_N0

P

P

CIE_FTX_C_GRX_P1

P

CIE_FTX_C_GRX_N1

P

CIE_FTX_C_GRX_P2

CIE_FTX_C_GRX_N2

P

CIE_FTX_C_GRX_P3

P

CIE_FTX_C_GRX_N3

P

P

CIE_FTX_C_GRX_P4

P

CIE_FTX_C_GRX_N4

P

CIE_FTX_C_GRX_P5

P

CIE_FTX_C_GRX_N5

CIE_FTX_C_GRX_P6

P

CIE_FTX_C_GRX_N6

P

CIE_FTX_C_GRX_P7

P

P

CIE_FTX_C_GRX_N7

PC

IE_FTX_C_DRX_P0 29

IE_FTX_C_DRX_N0 29

PC

PC

IE_FTX_C_DRX_P1 32

IE_FTX_C_DRX_N1 32

PC

UMI_FTX_C_MRX_P0 13

UMI_FTX_C_MRX_N0 13

UMI_FTX_C_MRX_P1 13

UMI_FTX_C_MRX_N1 13

UMI_FTX_C_MRX_P2 13

UMI_FTX_C_MRX_N2 13

UMI_FTX_C_MRX_P3 13

UMI_FTX_C_MRX_N3 13

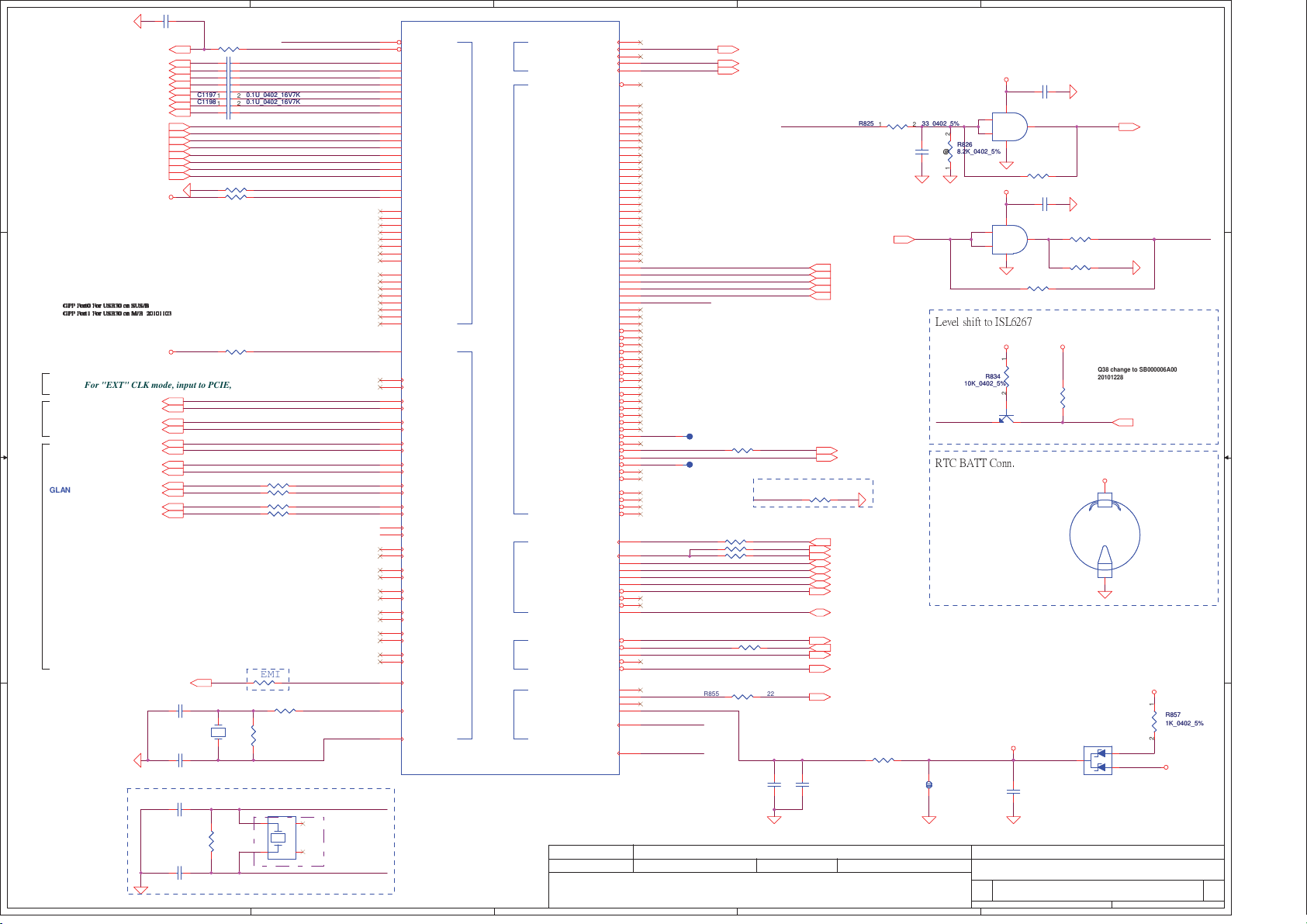

For U

GLAN

WLAN

MA Mux.

D

APU To HDM

CP

U TSI interface level shift

+3V

S

31.6K_0402_1%

31.6K_0402_1%

APU_

SID8,14

APU_

SIC8,14

Sequence of APU

Power

+1.

+2.5VS

+1.

+CPU_CORE

+CPU_CORE_NB

+1.2VS

R

R

535

535

1 2

SID

APU_

SH111 1N_SOT23-3

SH111 1N_SOT23-3

B

B

SIC

APU_

BSH111 1N_SOT23-3

BSH111 1N_SOT23-3

5V

5VS

I

P

C

C

935 0.1U_0402_16V4Z

935 0.1U_0402_16V4Z

1 2

R

R

536

536

1 2

30K_0402_1%

30K_0402_1%

G

G

2

Q9

Q9

C_SMB_DA

E

13

D

S

D

S

G

G

2

0

0

Q1

Q1

C_SMB_CK

E

13

D

S

D

S

P

CIE_FTX_GRX_P[12..15] 28

CIE_FTX_GRX_N[12..15] 28

BS

H111, the Vgs is:

min = 0.4V

Max = 1.3V

R537

R537

1 2

0_0402_5%

0_0402_5%

R538

R538

1 2

0_0402_5%

0_0402_5%

E

E

C_SMB_DA2 19,36

To

EC

E

C_SMB_CK2 19,36

Gr

oup A

Group B

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

pal Secret Data

pal Secret Data

pal Secret Data

Com

Com

2010/08/04 2011/12/31

2010/08/04 2011/12/31

2010/08/04 2011/12/31

Com

Deciphered Date

Deciphered Date

Deciphered Date

D

lectronics, Inc.

lectronics, Inc.

Compal E

Compal E

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal E

A

A

A

MD FS1 PCIE / UMI / TSI

MD FS1 PCIE / UMI / TSI

MD FS1 PCIE / UMI / TSI

QB

QB

QB

L50 LA-7551P

L50 LA-7551P

L50 LA-7551P

lectronics, Inc.

653Wednesday, April 27, 2011

653Wednesday, April 27, 2011

653Wednesday, April 27, 2011

E

1.0

1.0

1.0

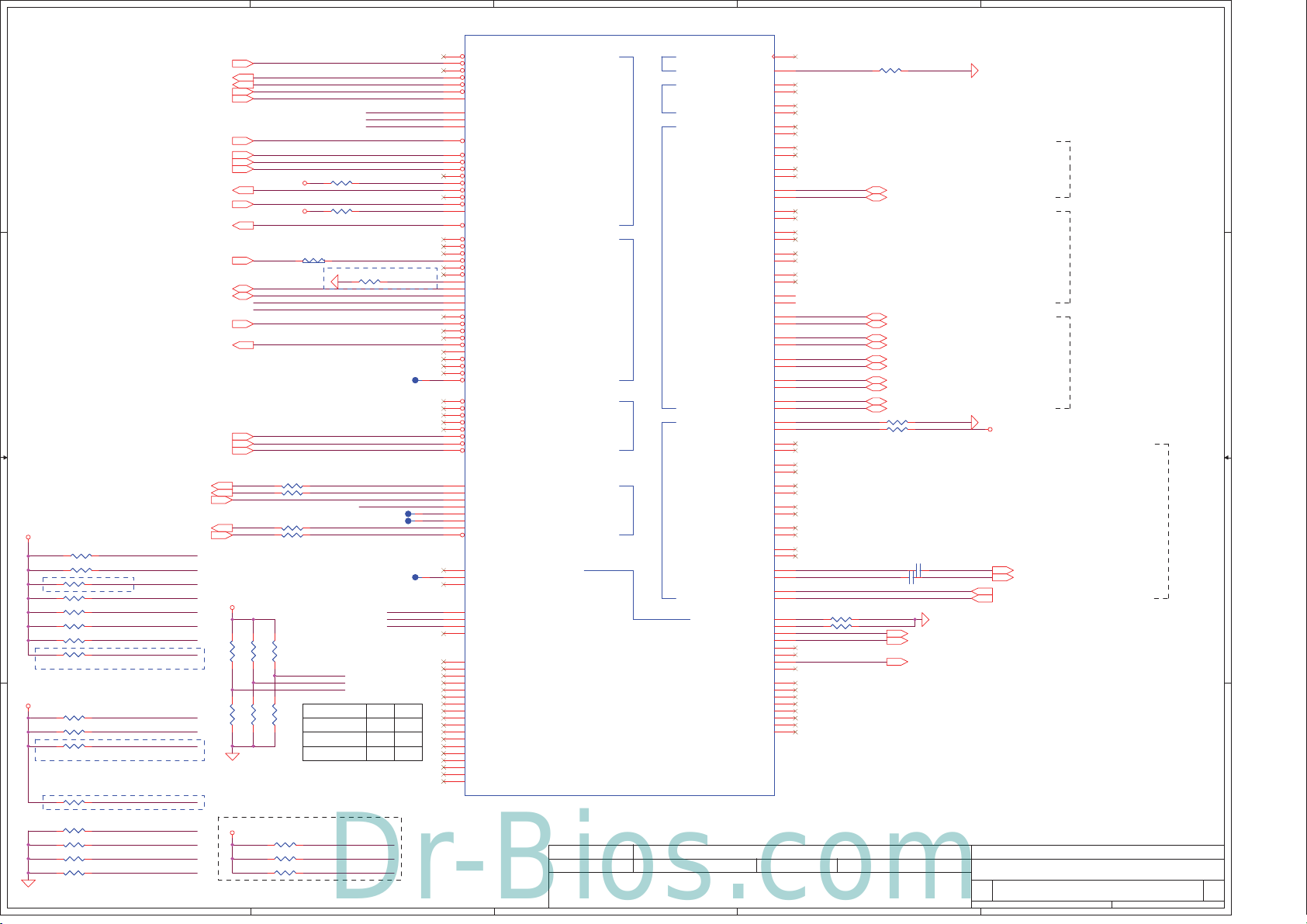

A

Dr-Bios.com

1 1

JC

JC

PU1B

PU1B

M

M

EMORY CHANNEL A

DDRA_

SMA[15..0]11

DDRA_

SBS0#11

DDRA_

SBS1#11

SBS2#11

DDRA_

DDRA_

SDM[7..0]11

2 2

SDQS011

DDRA_

SDQS0#11

DDRA_

SDQS111

DDRA_

DDRA_SDQS1#11

DDRA_

SDQS211

SDQS2#11

DDRA_

DDRA_SDQS311

SDQS3#11

DDRA_

DDRA_

SDQS411

SDQS4#11

DDRA_

SDQS511

DDRA_

DDRA_

SDQS5#11

DDRA_SDQS611

DDRA_

SDQS6#11

SDQS711

DDRA_

DDRA_SDQS7#11

DDRA_

CLK011

CLK0#11

DDRA_

CLK111

DDRA_

DDRA_

CLK1#11

DDRA_

CKE011

CKE111

DDRA_

DDRA_

ODT011

ODT111

DDRA_

SCS0#11

3 3

DDRA_

DDRA_

DDRA_

DDRA_

DDRA_SWE#11

M_MA_RST#11

ME

M

EM_MA_EVENT#11

+MEM_VREF

SCS1#11

SRAS#11

SCAS#11

+1.5V

Qmbdf!uifn!dmptf!up!BQV!xjuijo!2#

Qmbdf!uifn!dmptf!up!BQV!xjuijo!2#

Qmbdf!uifn!dmptf!up!BQV!xjuijo!2#Qmbdf!uifn!dmptf!up!BQV!xjuijo!2#

DDRA_

SMA0

SMA1

DDRA_

DDRA_

SMA2

SMA3

DDRA_

SMA4

DDRA_

DDRA_

SMA5

DDRA_SMA6

DDRA_

SMA7

SMA8

DDRA_

DDRA_

SMA9

DDRA_

SMA10

DDRA_

SMA11

SMA12

DDRA_

SMA13

DDRA_

DDRA_

SMA14

SMA15

DDRA_

SBS0#

DDRA_

DDRA_

SBS1#

DDRA_

SBS2#

SDM0

DDRA_

SDM1

DDRA_

DDRA_

SDM2

SDM3

DDRA_

DDRA_SDM4

SDM5

DDRA_

DDRA_

SDM6

DDRA_

SDM7

DDRA_

SDQS0

SDQS0#

DDRA_

DDRA_

SDQS1

SDQS1#

DDRA_

DDRA_SDQS2

DDRA_

SDQS2#

DDRA_

SDQS3

DDRA_

SDQS3#

SDQS4

DDRA_

DDRA_

SDQS4#

SDQS5

DDRA_

DDRA_

SDQS5#

SDQS6

DDRA_

DDRA_SDQS6#

DDRA_

SDQS7

SDQS7#

DDRA_

CLK0

DDRA_

DDRA_

CLK0#

CLK1

DDRA_

CLK1#

DDRA_

DDRA_CKE0

DDRA_

CKE1

DDRA_ODT0

ODT1

DDRA_

SCS0#

DDRA_

SCS1#

DDRA_

DDRA_SRAS#

DDRA_

SCAS#

SWE#

DDRA_

ME

M_MA_RST#

M

EM_MA_EVENT#

15m

1 2

R541 39.2_0402_1%R541 39.2_0402_1%

M_ZVDDIO

il

U20

M

R20

MA_ADD1

R21

M

P22

M

P21

MA_ADD4

N24

M

N23

M

N20

M

N21

M

M21

M

U23

M

M22

M

L24

M

AA25

MA_ADD13

L21

M

L20

M

U24

M

U21

M

L23

M

E14

MA

J17

MA_DM1

E21

MA

F25

MA

AD27

MA

AC23

MA

AD19

MA

AC15

MA

G14

M

H14

MA_DQS_L0

G18

M

H18

M

J21

M

H21

M

E27

M

E26

M

AE26

M

AD26

M

AB22

M

AA22

M

AB18

M

AA18

M

AA14

M

AA15

M

T21

M

T22

M

R23

M

R24

MA_CLK_L1

H28

M

H27

M

Y25

MA

AA27

MA

V22

M

AA26

MA_CS_L1

V21

M

W24

M

W23

MA

H25

M

T24

M

W20

M_VREF

W21

M_ZVDDIO

AMD_TOPEDO_FS-1

AMD_TOPEDO_FS-1

EMORY CHANNEL A

A_ADD0

A_ADD2

A_ADD3

A_ADD5

A_ADD6

A_ADD7

A_ADD8

A_ADD9

A_ADD10

A_ADD11

A_ADD12

A_ADD14

A_ADD15

A_BANK0

A_BANK1

A_BANK2

_DM0

_DM2

_DM3

_DM4

_DM5

_DM6

_DM7

A_DQS_H0

A_DQS_H1

A_DQS_L1

A_DQS_H2

A_DQS_L2

A_DQS_H3

A_DQS_L3

A_DQS_H4

A_DQS_L4

A_DQS_H5

A_DQS_L5

A_DQS_H6

A_DQS_L6

A_DQS_H7

A_DQS_L7

A_CLK_H0

A_CLK_L0

A_CLK_H1

A_CKE0

A_CKE1

_ODT0

_ODT1

A_CS_L0

A_RAS_L

A_CAS_L

_WE_L

A_RESET_L

A_EVENT_L

CONN@

CONN@

M

A_DATA0

MA_DATA1

M

A_DATA2

A_DATA3

M

MA_DATA4

M

A_DATA5

M

A_DATA6

A_DATA7

M

M

A_DATA8

A_DATA9

M

M

A_DATA10

A_DATA11

M

MA_DATA12

M

A_DATA13

A_DATA14

M

A_DATA15

M

M

A_DATA16

A_DATA17

M

A_DATA18

M

A_DATA19

M

MA_DATA20

M

A_DATA21

A_DATA22

M

M

A_DATA23

M

A_DATA24

A_DATA25

M

A_DATA26

M

M

A_DATA27

MA_DATA28

M

A_DATA29

A_DATA30

M

M

A_DATA31

M

A_DATA32

A_DATA33

M

A_DATA34

M

M

A_DATA35

A_DATA36

M

M

A_DATA37

A_DATA38

M

M

A_DATA39

A_DATA40

M

A_DATA41

M

A_DATA42

M

M

A_DATA43

A_DATA44

M

MA_DATA45

A_DATA46

M

M

A_DATA47

A_DATA48

M

M

A_DATA49

A_DATA50

M

M

A_DATA51

A_DATA52

M

MA_DATA53

M

A_DATA54

M

A_DATA55

A_DATA56

M

M

A_DATA57

A_DATA58

M

M

A_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

B

DDRA_

E13

J13

H15

J15

H13

F13

F15

E15

H17

F17

E19

J19

G16

H16

H19

F19

H20

F21

J23

H23

G20

E20

G22

H22

G24

E25

G27

G26

F23

H24

E28

F27

AB28

AC27

AD25

AA24

AE28

AD28

AB26

AC25

Y23

AA23

Y21

AA20

AB24

AD24

AA21

AC21

AA19

AC19

AC17

AA17

AB20

Y19

AD18

AD17

AA16

Y15

AA13

AC13

Y17

AB16

AB14

Y13

DDRA_

SDQ0

SDQ1

DDRA_

DDRA_

SDQ2

SDQ3

DDRA_

SDQ4

DDRA_

DDRA_

SDQ5

DDRA_SDQ6

DDRA_

SDQ7

DDRA_

SDQ8

DDRA_

SDQ9

DDRA_

SDQ10

SDQ11

DDRA_

SDQ12

DDRA_

DDRA_

SDQ13

SDQ14

DDRA_

DDRA_

SDQ15

DDRA_

SDQ16

DDRA_

SDQ17

SDQ18

DDRA_

SDQ19

DDRA_

SDQ20

DDRA_

DDRA_

SDQ21

SDQ22

DDRA_

DDRA_SDQ23

DDRA_

SDQ24

DDRA_

SDQ25

SDQ26

DDRA_

DDRA_

SDQ27

SDQ28

DDRA_

DDRA_

SDQ29

SDQ30

DDRA_

DDRA_SDQ31

DDRA_

SDQ32

DDRA_

SDQ33

SDQ34

DDRA_

DDRA_

SDQ35

SDQ36

DDRA_

DDRA_

SDQ37

SDQ38

DDRA_

DDRA_SDQ39

SDQ40

DDRA_

DDRA_

SDQ41

SDQ42

DDRA_

DDRA_

SDQ43

SDQ44

DDRA_

SDQ45

DDRA_

SDQ46

DDRA_

DDRA_SDQ47

SDQ48

DDRA_

DDRA_SDQ49

SDQ50

DDRA_

DDRA_

SDQ51

SDQ52

DDRA_

SDQ53

DDRA_

DDRA_

SDQ54

DDRA_SDQ55

SDQ56

DDRA_

DDRA_SDQ57

DDRA_

SDQ58

DDRA_

SDQ59

SDQ60

DDRA_

DDRA_SDQ61

DDRA_SDQ62

DDRA_SDQ63

SDQ[63..0] 11

C

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_SDQS1#12

DDRB_

DDRB_

DDRB_SDQS312

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_SDQS612

DDRB_

DDRB_

DDRB_SDQS7#12

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_SWE#12

M_MB_RST#12

ME

M

EM_MB_EVENT#12

SMA[15..0]12

SBS0#12

SBS1#12

SBS2#12

SDM[7..0]12

SDQS012

SDQS0#12

SDQS112

SDQS212

SDQS2#12

SDQS3#12

SDQS412

SDQS4#12

SDQS512

SDQS5#12

SDQS6#12

SDQS712

CLK012

CLK0#12

CLK112

CLK1#12

CKE012

CKE112

ODT012

ODT112

SCS0#12

SCS1#12

SRAS#12

SCAS#12

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_SMA6

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_SDM4

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_SDQS2

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_SDQS6#

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_

DDRB_CKE0

DDRB_

DDRB_ODT0

DDRB_

DDRB_

DDRB_

DDRB_SRAS#

DDRB_

DDRB_

ME

M_MB_RST#

M

EM_MB_EVENT#

SMA0

SMA1

SMA2

SMA3

SMA4

SMA5

SMA7

SMA8

SMA9

SMA10

SMA11

SMA12

SMA13

SMA14

SMA15

SBS0#

SBS1#

SBS2#

SDM0

SDM1

SDM2

SDM3

SDM5

SDM6

SDM7

SDQS0

SDQS0#

SDQS1

SDQS1#

SDQS2#

SDQS3

SDQS3#

SDQS4

SDQS4#

SDQS5

SDQS5#

SDQS6

SDQS7

SDQS7#

CLK0

CLK0#

CLK1

CLK1#

CKE1

ODT1

SCS0#

SCS1#

SCAS#

SWE#

D

T27

P24

P25

N27

N26

M28

M27

M24

M25

L26

U26

L27

K27

W26

K25

K24

U27

T28

K28

D14

A18

A22

C25

AF25

AG22

AH18

AD14

C15

B15

E18

D18

E22

D22

B26

A26

AG24

AG25

AG21

AF21

AG17

AG18

AH14

AG14

R26

R27

P27

P28

J26

J27

W27

Y28

V25

Y27

V24

V27

V28

J25

T25

JC

JC

PU1C

PU1C

M

M

EMORY CHANNEL B

EMORY CHANNEL B

M

B_ADD0

MB_ADD1

M

B_ADD2

B_ADD3

M

MB_ADD4

M

B_ADD5

M

B_ADD6

B_ADD7

M

B_ADD8

M

M

B_ADD9

B_ADD10

M

M

B_ADD11

B_ADD12

M

MB_ADD13

M

B_ADD14

B_ADD15

M

B_BANK0

M

M

B_BANK1

B_BANK2

M

_DM0

MB

MB_DM1

MB

_DM2

_DM3

MB

MB

_DM4

_DM5

MB

MB

_DM6

_DM7

MB

M

B_DQS_H0

MB_DQS_L0

M

B_DQS_H1

B_DQS_L1

M

M

B_DQS_H2

M

B_DQS_L2

M

B_DQS_H3

B_DQS_L3

M

B_DQS_H4

M

M

B_DQS_L4

B_DQS_H5

M

M

B_DQS_L5

B_DQS_H6

M

M

B_DQS_L6

M

B_DQS_H7

B_DQS_L7

M

B_CLK_H0

M

M

B_CLK_L0

B_CLK_H1

M

MB_CLK_L1

M

B_CKE0

M

B_CKE1

MB

_ODT0

_ODT1

MB

B_CS_L0

M

MB_CS_L1

M

B_RAS_L

M

B_CAS_L

_WE_L

MB

B_RESET_L

M

M

B_EVENT_L

AMD_TOPEDO_FS-1

AMD_TOPEDO_FS-1

CONN@

CONN@

M

B_DATA0

MB_DATA1

M

B_DATA2

B_DATA3

M

MB_DATA4

M

B_DATA5

M

B_DATA6

B_DATA7

M

M

B_DATA8

B_DATA9

M

M

B_DATA10

B_DATA11

M

MB_DATA12

M

B_DATA13

B_DATA14

M

B_DATA15

M

M

B_DATA16

B_DATA17

M

B_DATA18

M

B_DATA19

M

MB_DATA20

M

B_DATA21

B_DATA22

M

M

B_DATA23

M

B_DATA24

B_DATA25

M

B_DATA26

M

M

B_DATA27

MB_DATA28

M

B_DATA29

B_DATA30

M

M

B_DATA31

M

B_DATA32

B_DATA33

M

B_DATA34

M

M

B_DATA35

B_DATA36

M

M

B_DATA37

B_DATA38

M

M

B_DATA39

B_DATA40

M

B_DATA41

M

B_DATA42

M

M

B_DATA43

B_DATA44

M

MB_DATA45

B_DATA46

M

M

B_DATA47

B_DATA48

M

M

B_DATA49

B_DATA50

M

M

B_DATA51

B_DATA52

M

MB_DATA53

M

B_DATA54

M

B_DATA55

B_DATA56

M

M

B_DATA57

B_DATA58

M

M

B_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

A14

B14

D16

E16

B13

C13

B16

A16

C17

B18

B20

A20

E17

B17

B19

C19

C21

B22

C23

A24

D20

B21

E23

B23

E24

B25

B27

D28

B24

D24

D26

C27

AG26

AH26

AF23

AG23

AG27

AF27

AH24

AE24

AE22

AH22

AE20

AH20

AD23

AD22

AD21

AD20

AF19

AE18

AE16

AH16

AG20

AG19

AF17

AD16

AG15

AD15

AG13

AD13

AG16

AF15

AE14

AF13

DDRB_

SDQ0

SDQ1

DDRB_

DDRB_

SDQ2

SDQ3

DDRB_

SDQ4

DDRB_

DDRB_

SDQ5

DDRB_SDQ6

DDRB_

SDQ7

DDRB_

SDQ8

DDRB_

SDQ9

DDRB_

SDQ10

SDQ11

DDRB_

SDQ12

DDRB_

DDRB_

SDQ13

SDQ14

DDRB_

DDRB_

SDQ15

DDRB_

SDQ16

DDRB_

SDQ17

SDQ18

DDRB_

SDQ19

DDRB_

SDQ20

DDRB_

DDRB_

SDQ21

SDQ22

DDRB_

DDRB_SDQ23

DDRB_

SDQ24

DDRB_

SDQ25

SDQ26

DDRB_

DDRB_

SDQ27

SDQ28

DDRB_

DDRB_

SDQ29

SDQ30

DDRB_

DDRB_SDQ31

DDRB_

SDQ32

DDRB_

SDQ33

SDQ34

DDRB_

DDRB_

SDQ35

SDQ36

DDRB_

DDRB_

SDQ37

SDQ38

DDRB_

DDRB_SDQ39

SDQ40

DDRB_

DDRB_

SDQ41

SDQ42

DDRB_

DDRB_

SDQ43

SDQ44

DDRB_

SDQ45

DDRB_

SDQ46

DDRB_

DDRB_SDQ47

SDQ48

DDRB_

DDRB_SDQ49

SDQ50

DDRB_

DDRB_

SDQ51

SDQ52

DDRB_

SDQ53

DDRB_

DDRB_

SDQ54

DDRB_SDQ55

SDQ56

DDRB_

DDRB_SDQ57

DDRB_

SDQ58

DDRB_

SDQ59

SDQ60

DDRB_

DDRB_SDQ61

DDRB_SDQ62

DDRB_SDQ63

E

DDRB_

SDQ[63..0] 12

ENT# pull high 0.75V reference voltage

EV

+1.5V

4 4

R544 1K_0402_5%R544 1K_0402_5%

1 2

R545 1K_0402_5%R545 1K_0402_5%

1 2

MEM_MA_EVENT#

MEM_MB_EVENT# +MEM_VREF

A

R542

R542

1K_0402_1%

1K_0402_1%

R543

R543

1K_0402_1%

1K_0402_1%

+1.5V

1 2

1 2

B

1

C964

C964

1000P_0402_50V7K

1000P_0402_50V7K

2

15m

2

C965

C965

0.1U_0402_16V7K

0.1U_0402_16V7K

1

il

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2010/08/04 2011/12/31

2010/08/04 2011/12/31

2010/08/04 2011/12/31

pal Secret Data

pal Secret Data

pal Secret Data

Com

Com

Com

Deciphered Date

Deciphered Date

Deciphered Date

lectronics, Inc.

lectronics, Inc.

Compal E

Compal E

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal E

A

A

A

MD FS1 DDRIII I/F

MD FS1 DDRIII I/F

MD FS1 DDRIII I/F

QB

QB

QB

L50 LA-7551P

L50 LA-7551P

L50 LA-7551P

lectronics, Inc.

753Wednesday, April 27, 2011

753Wednesday, April 27, 2011

753Wednesday, April 27, 2011

E

1.0

1.0

1.0

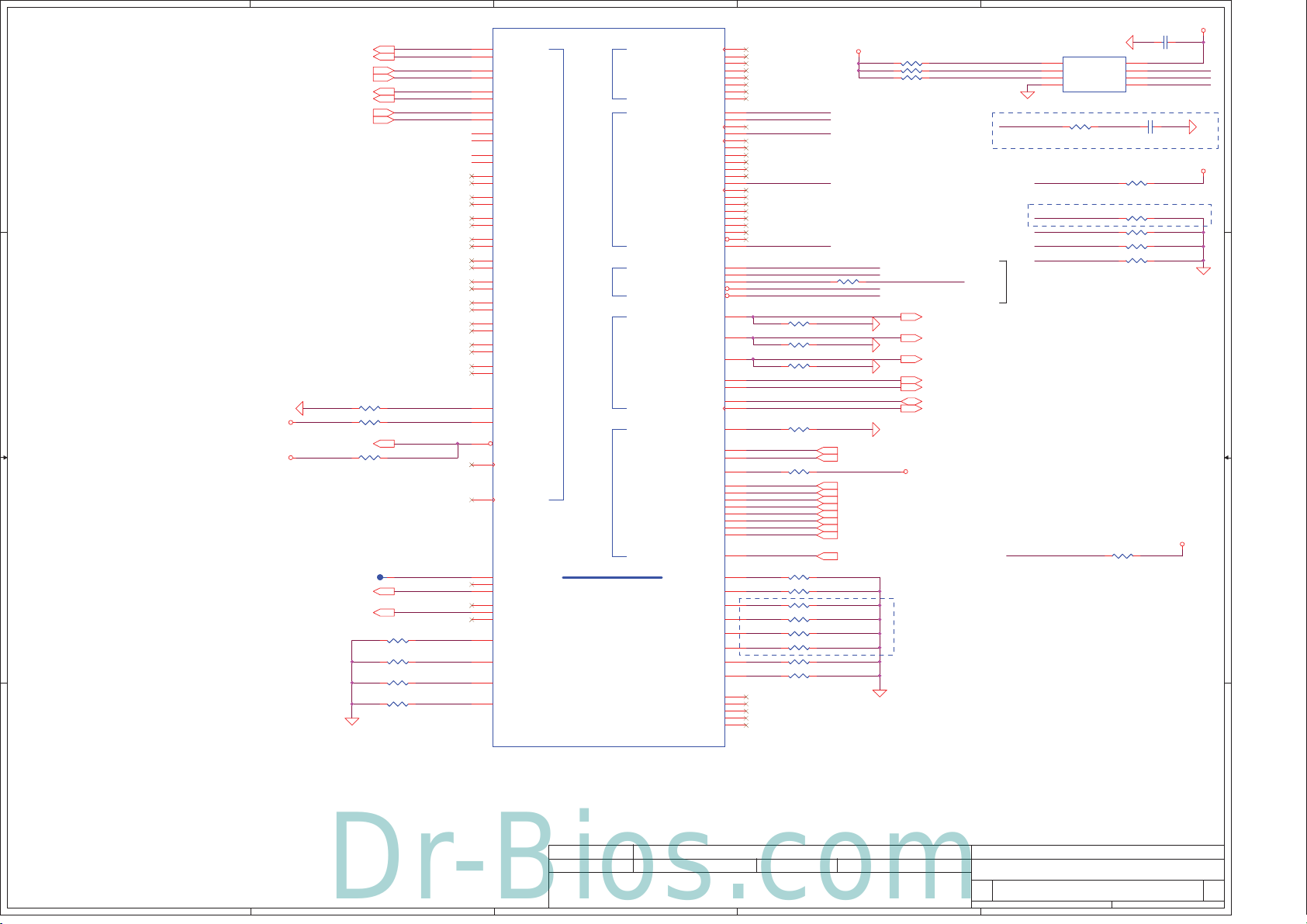

A

Dr-Bios.com

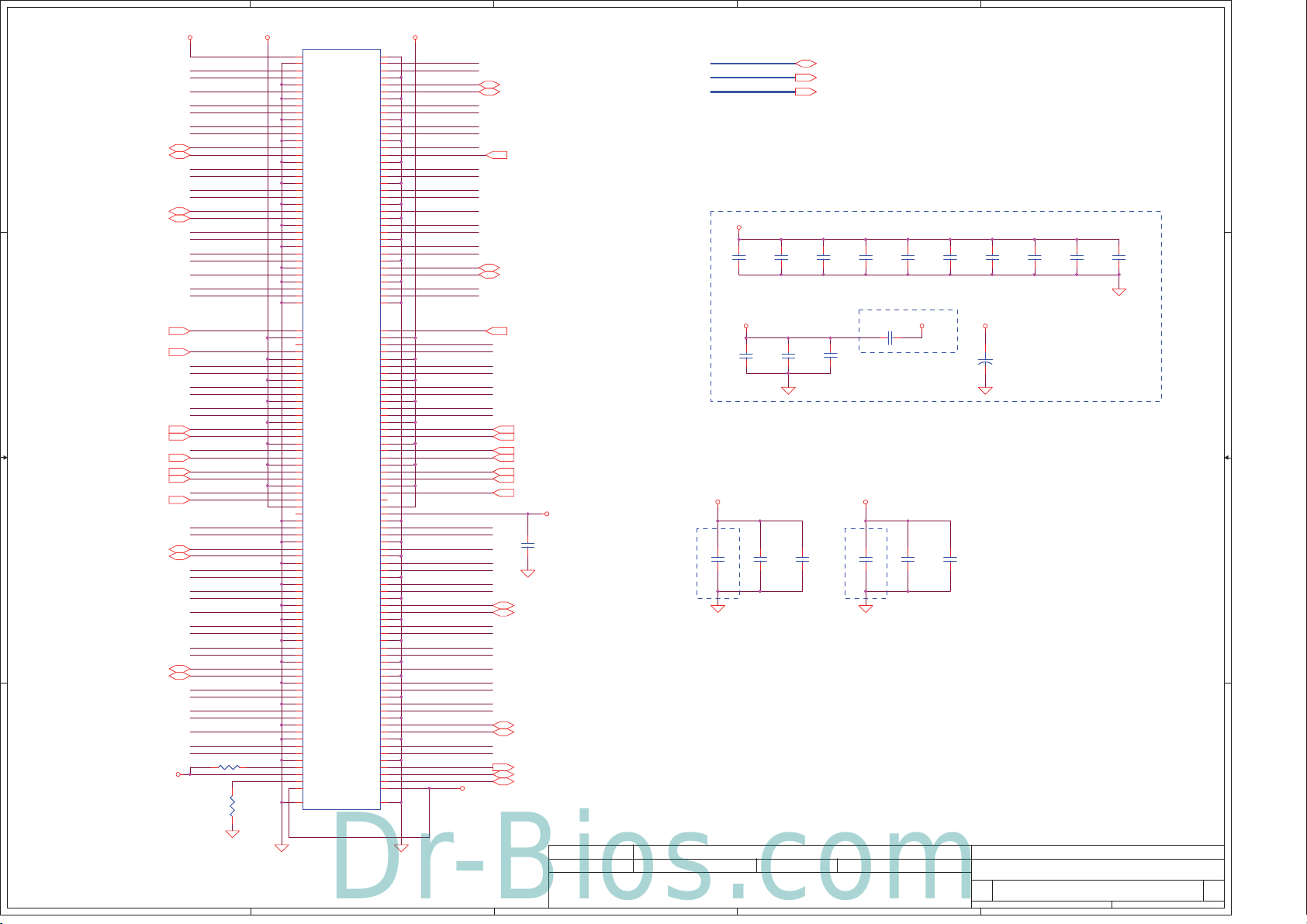

P

lace near APU

971 0.1U_0402_16V7K

971 0.1U_0402_16V7K

C

C

To LVD

S

Translator

1 1

T

o FCH VGA ML

100MHz

2 2

100MHz_NSS

+1.5V

R

R

575 1K_0402_5%

575 1K_0402_5%

576 1K_0402_5%

576 1K_0402_5%

R

R

+1.

5V

3 3

R579 1K_0402_5%R579 1K_0402_5%

581 1K_0402_5%

581 1K_0402_5%

R

R

791 1K_0402_5%

791 1K_0402_5%

R

R

+1.

5V

R592 1K_0402_5%R592 1K_0402_5%

R593 1K_0402_5%R593 1K_0402_5%

R594 1K_0402_5%R594 1K_0402_5%

R595 1K_0402_5%R595 1K_0402_5%

R596 300_0402_5%R596 300_0402_5%

ute as differentia l

Ro

with VSS_SENSE

APU_VDDNB_RUN_FB_L

APU_VDDNB_SEN route as differential

4 4

APU_VDD_RUN_FB_L

APU_VDD_SE N route as differential

C

20101111

1 2

1 2

1 2

1 2

1 2

Close to Header

1 2

1 2

1 2

1 2

1 2

P0_TXP0_C26

D

P0_TXN0_C26

D

L_VGA_TXP015

M

L_VGA_TXN015

M

M

L_VGA_TXP115

L_VGA_TXN115

M

M

L_VGA_TXP215

ML_VGA_TXN215

M

L_VGA_TXP315

M

L_VGA_TXN315

APU_CLKP13

PU_CLKN13

A

APU_

DISP_CLKP13

DISP_CLKN13

APU_

SVC47

APU_

SVD47

APU_

hang to PU +1.5VS (DG ref. )

APU_SVC

APU_

APU_

APU_SID

ERT_L

AL

APU_TDI

APU_TCK

APU_TMS

APU_TRST#

APU_DBREQ#

APU_VDDNB_RUN_FB_L47

APU_VDD_RUN_FB_L47

SVD

SIC

1 2

973 0.1U_0402_16V7K

973 0.1U_0402_16V7K

C

C

1 2

T25T25

T28T28

T19T19

T20T20

T21T21

T22T22

P

lace near APU

977 0.1U_0402_16V7K

977 0.1U_0402_16V7K

C

C

1 2

C

C

968 0.1U_0402_16V7K

968 0.1U_0402_16V7K

1 2

969 0.1U_0402_16V7K

969 0.1U_0402_16V7K

C

C

1 2

970 0.1U_0402_16V7K

970 0.1U_0402_16V7K

C

C

1 2

C

C

978 0.1U_0402_16V7K

978 0.1U_0402_16V7K

1 2

979 0.1U_0402_16V7K

979 0.1U_0402_16V7K

C

C

1 2

C

C

980 0.1U_0402_16V7K

980 0.1U_0402_16V7K

1 2

C981 0.1U_0402_16V7K

C981 0.1U_0402_16V7K

1 2

CLKP

APU_

CLKN

APU_

DISP_CLKP

APU_

DISP_CLKN

APU_

APU_

SVC

APU_

SVD

SIC6,14

APU_

TSI

APU_SID6,14

APU_

RST#13

PWRGD13

APU_

rial VID

Se

R597 0_0402_5%R597 0_0402_5%

R600 0_0402_5%R600 0_0402_5%

APU_VDDNB_SEN47

APU_VDD_SEN47

1 2

1 2

DP0

D

DP0

D

DP0_TXP2

D

DP0

D

DP1

D

DP1

D

DP1

D

DP1

D

SIC

APU_

SID

APU_

APU_

RST#

APU_

PWRGD

PROCHOT#

APU_

APU_

THERMTRIP#

ALERT_L

TDI

APU_

APU_TDO

TCK

APU_

APU_

TMS

TRST#

APU_

APU_DBRDY

APU_DBREQ#

APU_VDDNB_SEN

APU_VDD_SEN

A

_TXP0

P0_TXN0

_TXP1

P0_TXN1

P0_TXN2

_TXP3

P0_TXN3

_TXP0

P1_TXN0

_TXP1

P1_TXN1

_TXP2

P1_TXN2

_TXP3

P1_TXN3

B

PU1D

PU1D

JC

JC

F2

DP0

F1

D

E3

DP0

E2

D

D2

DP0

D1

D

C2

DP0

C3

D

K2

DP1

K1

D

J3

DP1

J2

D

H2

DP1_TXP2

H1

D

G2

DP1

G3

D

AH7

CL

AH6

CL

AH4

DI

AH3

DISP_CLKIN_L

B8

SVC

A8

SVD

AH11

SI

AG11

SI

AF10

RESET_

AE10

PW

AD10

PRO

AG12

THERM

AH12

AL

C12

TDI

A12

TD

A11

TC

D12

TM

B12

TRST_L

B11

DBRDY

C11

DBREQ_L

E8

RSVD_1

K21

RSVD_2

AC11

RSVD_3

B9

VSS_SENSE

C8

VDDP_SENSE

A9

VDDNB_SENSE

B10

VDDIO_SENSE

C9

VDD_SENSE

A10

VDDR_SENSE

AMD_TOPEDO_FS-1

AMD_TOPEDO_FS-1

B

_TXP0

P0_TXN0

_TXP1

P0_TXN1

_TXP2

P0_TXN2

_TXP3

P0_TXN3

_TXP0

P1_TXN0

_TXP1

P1_TXN1

P1_TXN2

S

_TXP3

P1_TXN3

KIN_H

KIN_L

SP_CLKIN_H

C

D

L

ROK

CHOT_L

TRIP_L

ERT_L

O

K

S

DISPLAY PORT 0DISPLAY PORT 1CLKSER.CTRLJTAG RSVDSENSE

DISPLAY PORT 0DISPLAY PORT 1CLKSER.CTRLJTAG RSVDSENSE

ystem DP

CONN@

CONN@

_AUXP

DP0

DP0

_AUXN

_AUXP

DP1

_AUXN

DP1

DP2

_AUXP

_AUXN

DP2

DP3

_AUXP

_AUXN

DP3

DP4

_AUXP

DP4_AUXN

_AUXP

DP5

DP5

_AUXN

P0_HPD

D

D

P1_HPD

P2_HPD

D

D

P3_HPD

P4_HPD

D

DP5_HPD

DP_

BLON

D

P_DIGON

VARY_BL

DP_

DP_

AUX_ZVSS

TEST6

TEST9

TEST10

TEST12

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST20

TEST21

TEST DISPLAY PORT MISC.

TEST DISPLAY PORT MISC.

TEST22

TEST23

TEST24

TE

ST25_H

TEST25_L

TEST28_H

TEST28_L

TEST30_H

TEST30_L

TEST31

TEST32_H

TEST32_L

TEST35

FS1R1

DMAACTIVE_L

THERMDA

THERMDC

C

Place near APU

_AUXP

DP0

D4

DP0

D5

L_VGA_AUXP

M

E5

M

L_VGA_AUXN

E6

J5

J6

H4

H5

G5

G6

APU_

F4

APU_

F5

D7

E7

J7

H7

G7

F7

C6

C5

C7

D8

AA1

0

0

G1

0

H1

2

H1

D9

E9

G9

H9

H1

1

1

G1

F12

1

E1

D1

1

F10

G1

2

AH10

AH9

K7

K8

AA12

AB12

K22

AB11

AA11

D10

Y11

AB10

AE12

AD12

Llano do not support this thermal die

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

972 0.1U_0402_16V7K

972 0.1U_0402_16V7K

C

C

_AUXN

974 0.1U_0402_16V7K

974 0.1U_0402_16V7K

C

C

C975 0.1U_0402_16V7K

C975 0.1U_0402_16V7K

976 0.1U_0402_16V7K

976 0.1U_0402_16V7K

C

C

HDMI_CLK

HDMI_DATA

P0_HPD

D

D

P1_HPD

P5_HPD

D

DP_ENBKL

DP_

ENVDD

INT_PWM

DP_

DP_

AUX_ZVSS

hang to unpop (DG ref.)

C

20101111

T6T6

T7T7

T8T8

T9T9

APU_TEST18

TEST19

APU_

TEST20

APU_

TEST21

APU_

APU_

TEST22

T10T10

APU_TEST24

TE

ST25_H

TEST25_L

T11T11

T12T12

M_TEST

T13T13

T14T14

TEST35

FS1R1

ALLOW_STOP

C639 0.1U_0402_16V4Z

C639 0.1U_0402_16V4Z

T15T15

T16T16

C

1 2

1 2

1 2

1 2

HDMI_CLK 28

APU_

APU_

HDMI_DATA 28

P0_HPD 10

D

P1_HPD 10

D

D

P5_HPD 10

D

P_ENBKL 10

DP_

D

P_INT_PWM 10

R

R

569 150_0402_1%

569 150_0402_1%

1 2

R573 0_0402_5%@R573 0_0402_5%@

1 2

574 1K_0402_5%

574 1K_0402_5%

R

R

1 2

R

R

582 1K_0402_5%

582 1K_0402_5%

1 2

583 1K_0402_5%

583 1K_0402_5%

R

R

1 2

584 1K_0402_5%

584 1K_0402_5%

R

R

1 2

585 1K_0402_5%

585 1K_0402_5%

R

R

1 2

R

R

589 1K_0402_5%

589 1K_0402_5%

1 2

R

R

590 1K_0402_5%

590 1K_0402_5%

1 2

ALLOW_STOP 13

1 2

@

@

2010/08/04 2011/12/31

2010/08/04 2011/12/31

2010/08/04 2011/12/31

LVDS

CRT

ENVDD 10

_AUXP_C 26

DP0

_AUXN_C 26

DP0

M

L_VGA_AUXP_C 15

L_VGA_AUXN_C 15

M

2~5 are for GFX interface

AUX

use, they could be selected to I2C

or AUX logic

VDDIO level

Need Level shift

VDDIO level

Need Level shift

I

HDM

V

DDIO level

Need Level shift

H

DT Debug conn

APU_TRST#

R601 10K_0402_5%R601 10K_0402_5%

R603 10K_0402_5%R603 10K_0402_5%

R605 10K_0402_5%R605 10K_0402_5%

pal Secret Data

pal Secret Data

pal Secret Data

Com

Com

Com

Deciphered Date

Deciphered Date

Deciphered Date

D

To LVD

S

Translator

To FCH

Asserted as an input to force the

processor into the HTC-active state

APU_

THERMTRIP shutdown

temperature: 125 degree

APU_

+1.5V

R598 0_0402_5%R598 0_0402_5%

1 2

1 2

1 2

1 2

D

PROCHOT#

THERMTRIP#

E

I

f not used, pins are left unconnected (DG ref.)

20101111

_AUXP

DP0

DP0

M

L_VGA_AUXP

L_VGA_AUXN

M

TEST25_L

TEST25_H

TEST35

_TEST

M

FS1R

FS1R

In laptop, seems no use

A

LLOW_STOP

MI

5V

+1.

R

R

1K_0402_5%

1K_0402_5%

1 2

R

R

591 0_0402_5%

591 0_0402_5%

+1.

5V

R

R

610

610

1K_0402_5%

1K_0402_5%

1 2

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

JP1

JP1

1

1

3

3

5

5

7

7

9

9

10

11

11

12

13

13

14

15

15

16

17

17

18

19

19

20

SAMTE_ASP-136446-07-B

SAMTE_ASP-136446-07-B

CONN@

CONN@

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

APU_

SC

APU_PWRGD

586

586

1 2

E

E

3 1

2

4

6

8

10K_0402_5%

10K_0402_5%

Indicates to the FCH that a thermal trip

12

has occurred. Its assertion will cause th e FCH to

transition the system to S5 immediately

609

609

R

R

10K_0402_5%

10K_0402_5%

B

B

2

Q1

Q1

2

2

C

C

R

R

APU_TCK

2

APU_TMS

4

APU_TDI

6

APU_TDO

8

10

12

APU_DBRDY

14

APU_DBREQ#

16

R606 0_0402_5%R606 0_0402_5%

1 2

18

R608 0_0402_5%R608 0_0402_5%

1 2

20

Compal E

Compal E

Compal E

AM

AM

AM

D FS1 Display / MISC / HDT

D FS1 Display / MISC / HDT

D FS1 Display / MISC / HDT

QB

QB

QB

L50 LA-7551P

L50 LA-7551P

L50 LA-7551P

554 1.8K_0402_5%

554 1.8K_0402_5%

R

R

_AUXN

1

1 : Control S5 Dual PWR plane

RST#

R

R

1

1

Q1

Q1

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

1 2

611 0_0402_5%

611 0_0402_5%

R555 1.8K_0402_5%

R555 1.8K_0402_5%

547 1.8K_0402_5%

547 1.8K_0402_5%

R

R

R

R

556 1.8K_0402_5%

556 1.8K_0402_5%

548 510_0402_1%

548 510_0402_1%

R

R

1 2

R

R

557 510_0402_1%

557 510_0402_1%

1 2

R

R

558 300_0402_5%

558 300_0402_5%

1 2

559 300_0402_5%@

559 300_0402_5%@

R

R

1 2

564 39.2_0402_1%@

564 39.2_0402_1%@

R

R

1 2

R

R

567 39.2_0402_1%

567 39.2_0402_1%

1 2

571 10K_0402_5%

571 10K_0402_5%

R

R

1 2

612 1K_0402_5%

612 1K_0402_5%

R

R

1 2

R

R

577 1K_0402_5%

577 1K_0402_5%

1 2

@

@

R

R

578 300_0402_5%

578 300_0402_5%

1 2

R

R

580 300_0402_5%

580 300_0402_5%

1 2

S

+3V

12

12

R

R

587

587

10K_0402_5%

10K_0402_5%

2

B

B

E

E

31

C

C

Cut on CPU side, Debug mount

R599 0_0402_5%@R599 0_0402_5%@

1 2

R602 0_0402_5%@R602 0_0402_5%@

1 2

lectronics, Inc.

lectronics, Inc.

lectronics, Inc.

E

12

12

12

12

588

588

H_

APU_TEST19

APU_TEST18

+1.

+1.

+1.

3VALW

+

+1.

+1.

E

C_THERM# 13,36,47

THERMTRIP# 14

APU_PWRGD

APU_RST#

853Wednesday, April 27, 2011

853Wednesday, April 27, 2011

853Wednesday, April 27, 2011

2VS

5V

5V

5V

5VS

1.0

1.0

1.0

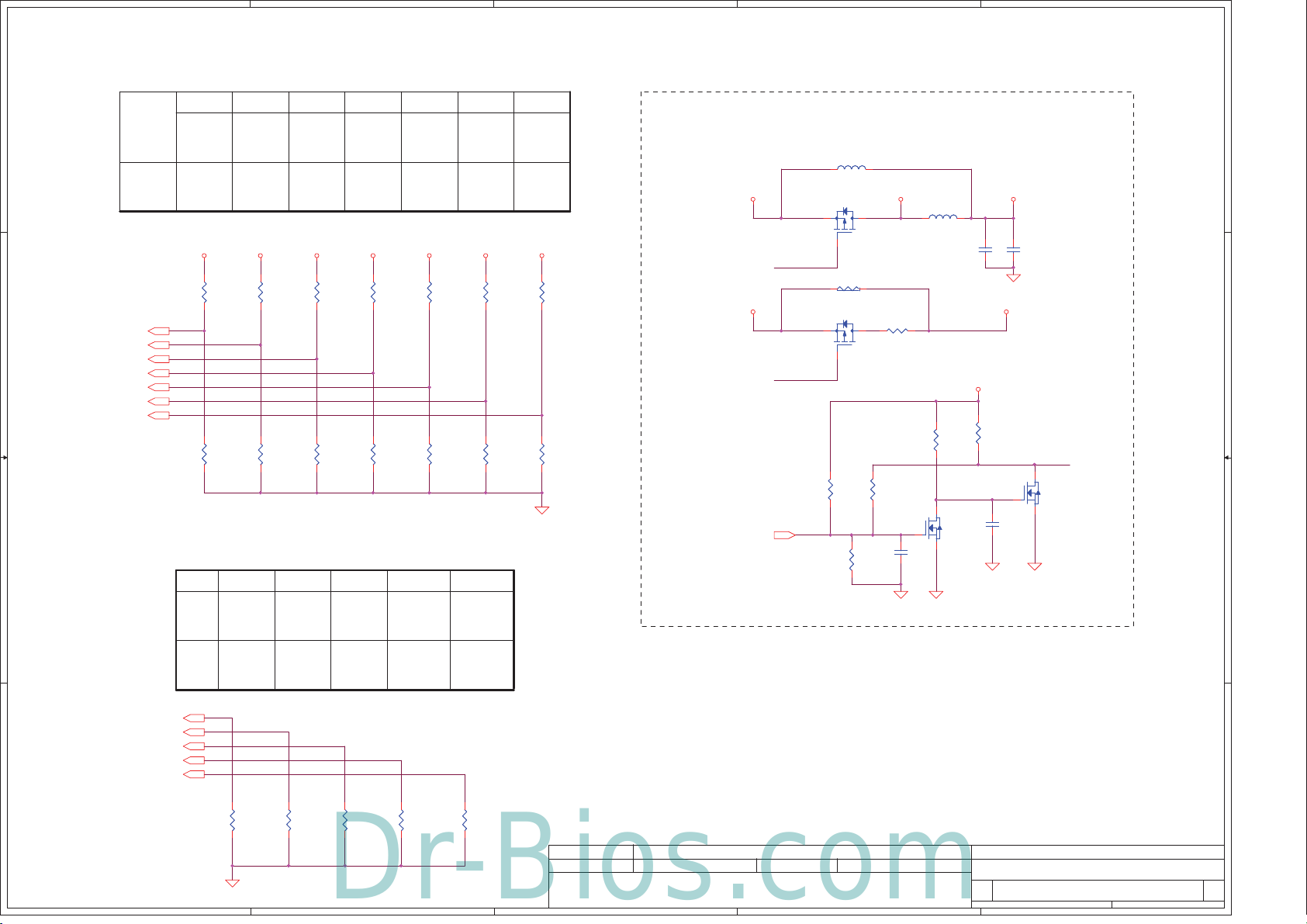

A

Dr-Bios.com

C

Power Name

D

VD

+C

PU_CORE

DDNB

V

+CPU_CORE_NB

V

DDIO

+1.5V

DDP / VDDR

V

+1.

2VS

DDA

V

1 1

+2.5VS

CORE_NB

330uF X 2

22uF X 4

2 2

3 3

+2.5VS

4 4

onsumption

50A

22.

5A

4A

/ 3.5A

3A

75A

0.

U_CORE

CP

330uF X 4

22uF X 11

+

CPU_CORE_NB

L1

L1

FBMA-L11-201209-221LMA30T_0805

FBMA-L11-201209-221LMA30T_0805

12

C

3300P_0402_50V7K

C

3300P_0402_50V7K

C

0.22U_0603_16V4Z

C

0.22U_0603_16V4Z

1040

1040

1041

1041

1

12

2

+CPU_CORE

5V

+1.

2VS

+1.

+1.2VS

il

40m

+VDDA_APU

4.7U_0805_10V4Z

4.7U_0805_10V4Z

C

180P_0402_50V8J@C

180P_0402_50V8J

1043

1043

C1

C1

1

1

8

8

2

C18 & C1043 follow A MD request

201012061900

Keep trace from resistor to APU

@

within 0.6"

2

Keep trace from Caps to APU

within 1.2"

JC

JC

PU1E

PU1E

C1

VDD

D3

VDD

D6

VDD

E1

VDD

F3

VDD

F6

VDD

F8

VDD

G1

VDD

H3

VDD

H6

VDD

H8

VDD

J1

VDD

K3

VDD

K6

VDD

L1

VDD

L11

VDD

L19

VDD

M3

VDD

M6

VDD

M10

VDD

M1

8

VDD

N1

VDD

1

N1

VDD

9

N1

VDD

P3

VDD

P6

VDD

0

P1

VDD

8

P1

VDD

R1

VDD

R1

1

VDD

9

R1

VDD

T3

VDD

J9

VDDNB

J10

VDDNB

J11

VDDNB

J12

VDDNB

J14

VDDNB

J16

VDDNB

K9

VDDNB

K1

0

VDDNB

G28

VDDI

H26

VDDI

J28

VDDI

K20

VDDI

K23

VDDI

K26

VDDI

L22

VDDI

L25

VDDI

L28

VDDI

M20

VDDI

M23

VDDI

M26

VDDI

N22

VDDIO

N25

VDDI

N28

VDDI

P20

VDDI

P23

VDDI

P26

VDDI

AG2

DDP_A_1

V

AG3

VDDP_A_2

AG4

V

DDP_A_3

AG5

V

DDP_A_4

AG

6

VDDR

7

AG

VDDR

AG

8

VDDR

AG9

VDDR

AE11

VDDA

AF11

VDDA

AMD_TOPEDO_FS-1

AMD_TOPEDO_FS-1

CONN@

CONN@

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

VDDI

VDDI

VDDI

VDDI

VDDI

VDDI

VDDI

VDDI

VDDI

VDDI

VDDI

VDDI

VDDIO

VDDI

VDDI

VDDI

VDDI

VDDI

VDDP_

VDDP_B_2

VDDP_

VDDP_

VDDR

VDDR

VDDR

VDDR

A

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

B

CPU BOTTOM

PU_CORE

+C

C

C

C

C

C

C

22U_0805_6.3V6M

22U_0805_6.3V6M

982

C7

C7

C

C

1045

1045

C

C

1053

1053

1

2

1

2

1

2

CPU_CORE_NB

+

+1.

+1.

10U

10U

_0603_6.3V6M

_0603_6.3V6M

C6

1

2

180P_0402_50V8J

180P_0402_50V8J

C1046

C1046

1

2

C1054

C1054

0.22U_0603_16V4Z

0.22U_0603_16V4Z

1

2

982

C

C

1000

1000

C

C

1012

1012

C

C

1027

1027

10U_0603_6.3V6MC610U_0603_6.3V6M

180P_0402_50V8J

180P_0402_50V8J

0.22U_0603_16V4Z

0.22U_0603_16V4Z

1

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

2

5V

22U_0805_6.3V6M

22U_0805_6.3V6M

1

2

5V

0.22U_0603_16V4Z

0.22U_0603_16V4Z

1

2

C

C

1034

1034

1

2

C

C

1047

1047

1

2

C

C

1055

1055

1

2

2000mil2000mil

+CPU_CORE

T6

T10

T18

U1

1

U1

9

U1

V3

V6

V1

0

8

V1

W1

W1

1

W1

3

5

W1

7

W1

W1

9

Y3

Y6

0

Y1

Y12

Y1

4

6

Y1

8

Y1

0

Y2

AA1

AB3

AB6

AC1

AD3

AD6

AE1

900mil900mil

1

K1

2

K1

K1

3

K14

K1

6

7

K1

K1

8

L18

160mil160mil

R22

O

R25

O

R28

O

T20

O

T23

O

T26

O

U22

O

U25

O

U28

O

V20

O

V23

O

V26

O

W22

W25

O

W28

O

Y24

O

Y26

O

AA28

O

A3

B_1

A4

B3

B_3

B4

B_4

A5

A6

B5

B6

+

CPU_CORE_NB

5V

+1.

DP decoupling

VD

120mil120mil

160mil160mil

B

10U

10U

_0603_6.3V6M

_0603_6.3V6M

C8

C8

1

2

DDR decoupling

V

180P_0402_50V8J

180P_0402_50V8J

C

C

1044

1044

1

2

C