Page 1

5

www.laptop-schematics.com

4

3

2

1

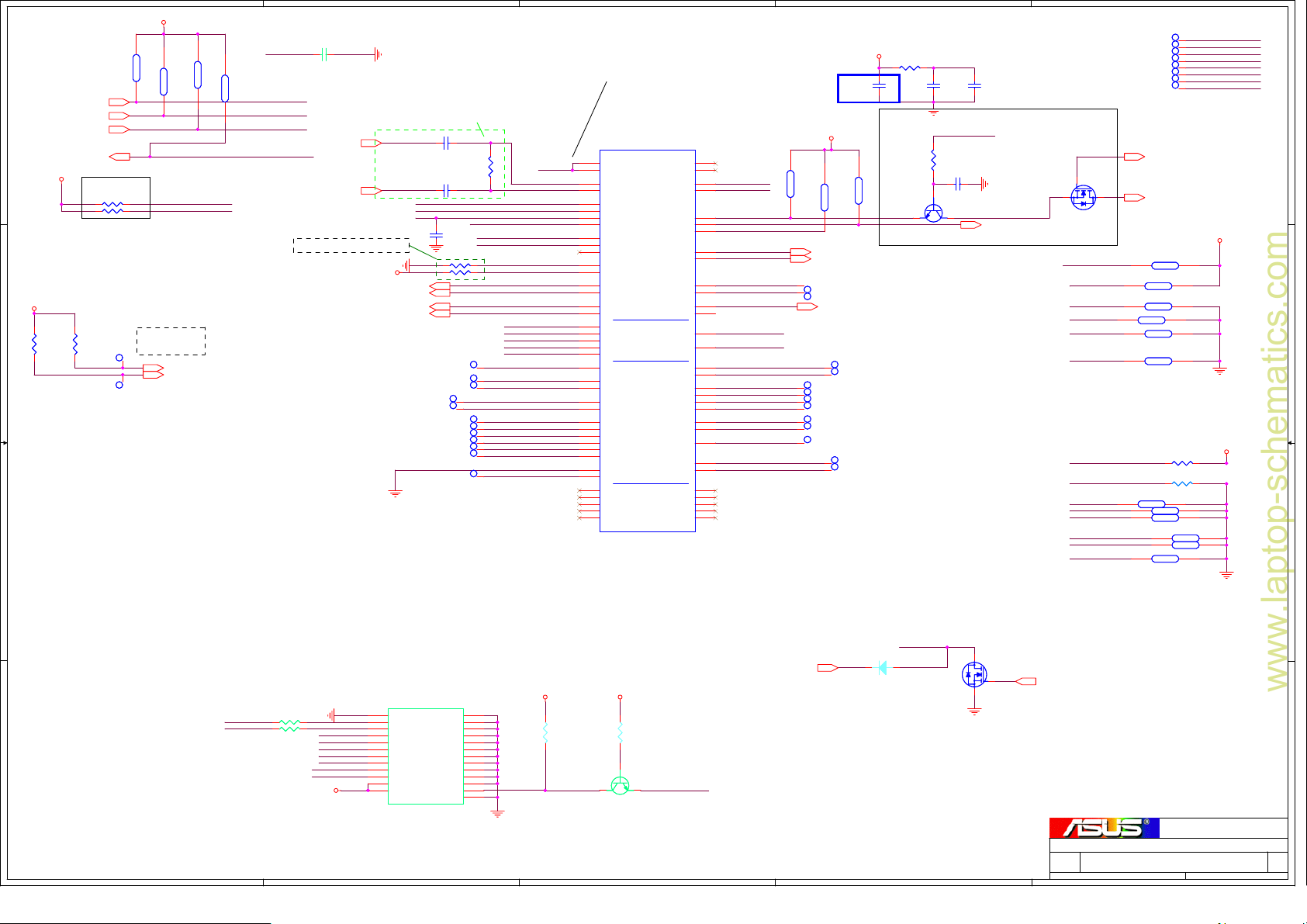

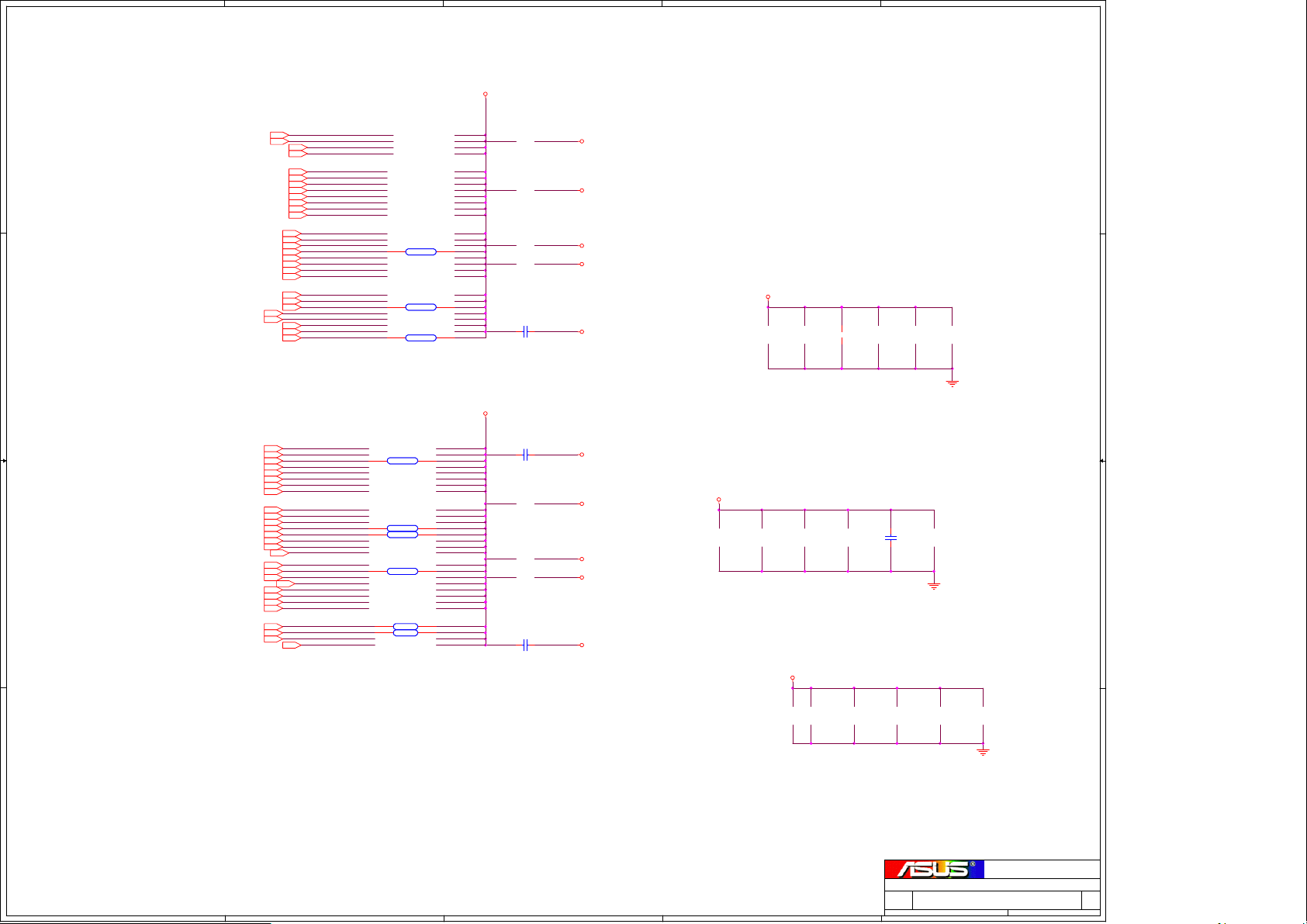

K40AB SCHEMATIC R1.3

D D

PAGE

Content

PAGE

SYSTEM PAGE REF.

3

SCHEMATIC INFORMATION

CPU-PENRYN(1)

4

CPU-PENRYN(2)

5

6

CPU CAP

DDR2 SO-DIMM_0

7

DDR2 SO-DIMM_1

8

DDR2 ADDRESS TERMINATION

9

NB_-CANTIGA--CPU (1)

10

NB_-CANTIGA--DDR2/PEG (2)

11

NB_-CANTIGA--DDR2 bus (3)

12

NB_-CANTIGA--POWER (4)

C C

B B

A A

13

NB_CANTIGA--POWER (5)

14

NB_-CANTIGA--GND/Strapping (6)

15

SB_-ICH9M--(1)-SATA,AUDIO,ACZ

20

SB_-ICH9M--(2)-PCI,PCI-E,USB

21

SB_-ICH9M--(3)-GPIO

22

SB_-ICH9M--(4)-PWR/GND

23

SB_-ICH9M--Other

24

SPI ROM

25

CLK-ICS9LPR363DGLF-T

29

EC-IT8512 (1)

30

EC-IT8512 (2)

31

POWER-ON SEQUENCE

32

PCI-E LAN_RTL8111C

33

RJ45

34

MDC

35

CODEC-ALC663

36

AUDIO_AMP-1431&HP

37

Microphone&Line-in

38

40

CARDBUS R5C833(PCI I/F)

CARDBUS R5C833(1394 & SD)

41

7 in 1 CARD READER

42

EXPRESS CARD

43

Debug

44

LVDS&INVERTER CONNECTOR

45

46

CRT

48

HDMI

50

Thermal Sensor

51

HDD & CDROM

52

USB Port X3

53

WLAN(MINI CARD)

56

LED & SW

57

DISCHARGE

58

ROBSON

60

DC & BAT IN

61

BLUE TOOTH

62

TPM & CAP sensor

63

Finger Print

65

SCREW HOLE & NUT & SPRING

66

E-SATA

69

History

70

VGA_nVIDIA_NB9X_PCIE

71

VGA_nVIDIA_NB9X_FB

72

VGA_nVIDIA_NB9X_Display

73

VGA_nVIDIA_NB9X_XTAL/Other

74

VGA_nVIDIA_NB9MGS_PCIE

75

VGA_nVIDIA_NB9X_GPIO

76

VGA_nVIDIA_NB9X_VRAM

77

VGA_nVIDIA_NB9X_VRAM

POWER PAGE REF.

80_POWER_VCORE

81_POWER_SYSTEM

82_POWER_I/O_1.5VS & 1.05VS

83_POWER_I/O_DDR & VTT

85_POWER_VGA_CORE & +1.1VO

87_POWER_SHUTDOWN#

88_POWER_CHARGER

90_POWER_PROTECT

91_POWER_LOAD SWITCH

92_POWER_PROTECT

93_POWER_SIGNAL

94_POWER_FLOWCHART

Content

5

4

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Wednesday, April 08, 2009

Wednesday, April 08, 2009

Wednesday, April 08, 2009

Date: Sheet

Date: Sheet

3

2

Date: Sheet

Engineer:

1

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

of

194

of

194

of

194

Rev

Rev

Rev

Page Reference

Page Reference

Page Reference

Title :

Title :

Title :

Engineer:

Engineer:

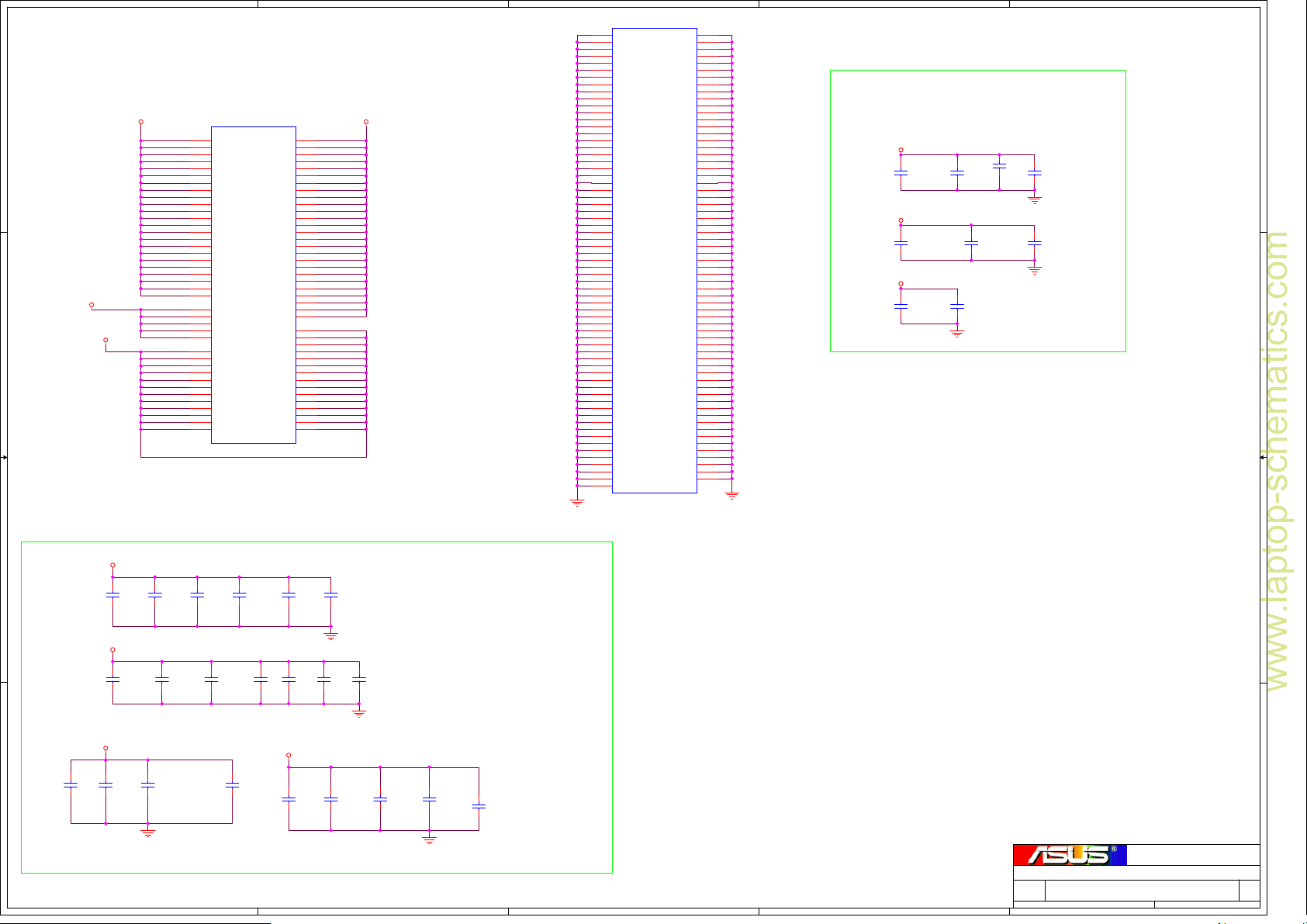

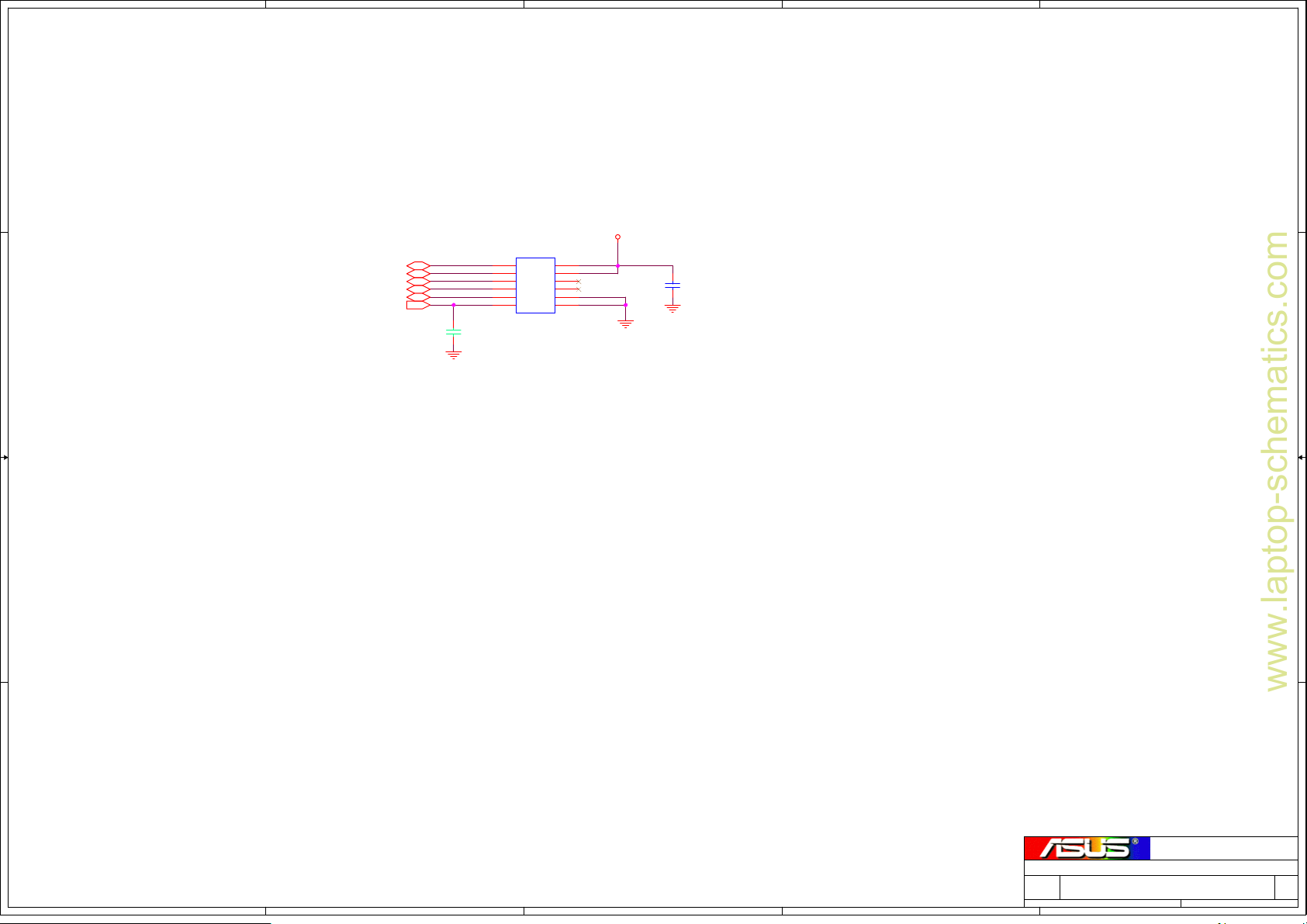

Page 2

5

www.laptop-schematics.com

4

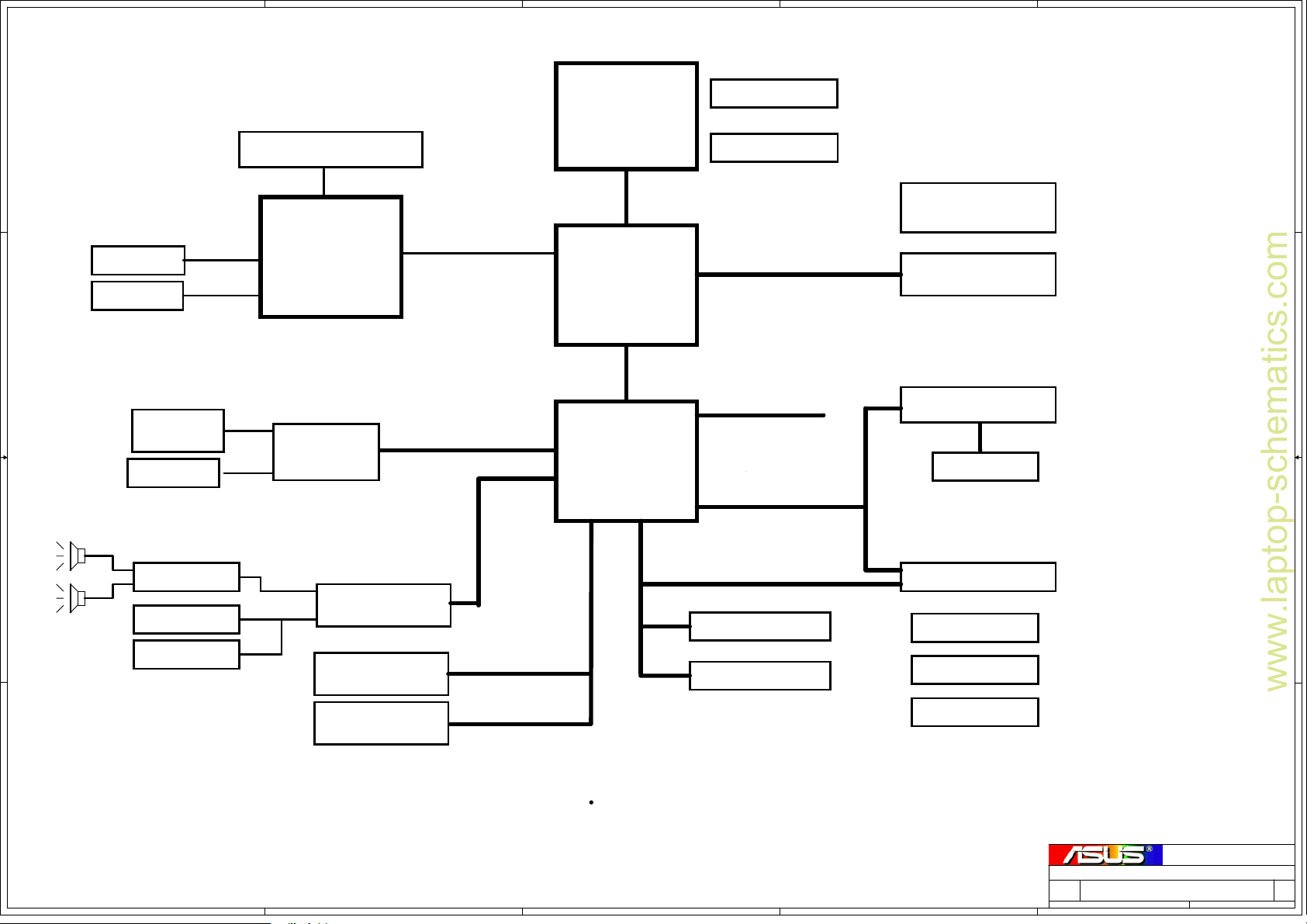

K40AB Block Diagram

3

2

1

AMD

D D

FAN + SENSOR

PAGE 50

S1G2 CPU

GDDR2 64M*16 x8

PAGE 74, 75

PAGE 3,4,5

HT 3.0

2.6GHZ

ATI

CRT

PAGE 46

LVDS & INV

C C

PAGE 45

M92/96

PAGE 70~76

PCI-E x16

AMD

RS780M

PAGE 10,11,12,13,14,15

A-LINK Interface

INTERNAL

KEYBOARD

BIOS SPI ROM

PAGE 31

PAGE 31

EC

ITE/IT8512

PAGE 30,31

LPC 33MHz

Azalia

AMD

SB700

PAGE 20,21,22,23,24

CPU VCORE

DDR2 800MHz

PCI 33MHz

PCI-E x1

USB

PAGE 80

CLOCK GEN

ICS/9LPR363

Dual Channel DDR2

SO-DIMM x2

PAGE 7,8,9

10/100/1000 LAN

Realtek RTL8112

RJ-45 CON

PAGE 34

PAGE 29

PAGE 33

B B

OPAMP

PAGE 37

USB

NewCard

PAGE 43,44

Azalia Codec

HP&SPDIF OUT

MIC IN

A A

5

PAGE 37

PAGE 38

VIA 1708S

SATA HDD

SATA ODD

PAGE 36, 37, 38, 39

PAGE 51

PAGE 51

4

SATA

USB

3

USB 2.0 CON x4

CMOS Camera

PAGE 52

PAGE 61

PAGE 45

SYSTEM PWR

BAT & CHARGER

Other PWR

PAGE 82, 83, 84, 85, 90, 91, 92, 93, 94

2

PAGE 81

PAGE 88

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size

Size

Size

Project Name

Project Name

Project Name

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

K40AB

Wednesday, April 08, 2009

Wednesday, April 08, 2009

Wednesday, April 08, 2009

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

Block Diagram

Block Diagram

Block Diagram

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

of

294

of

294

of

294

Rev

Rev

Rev

R1.3

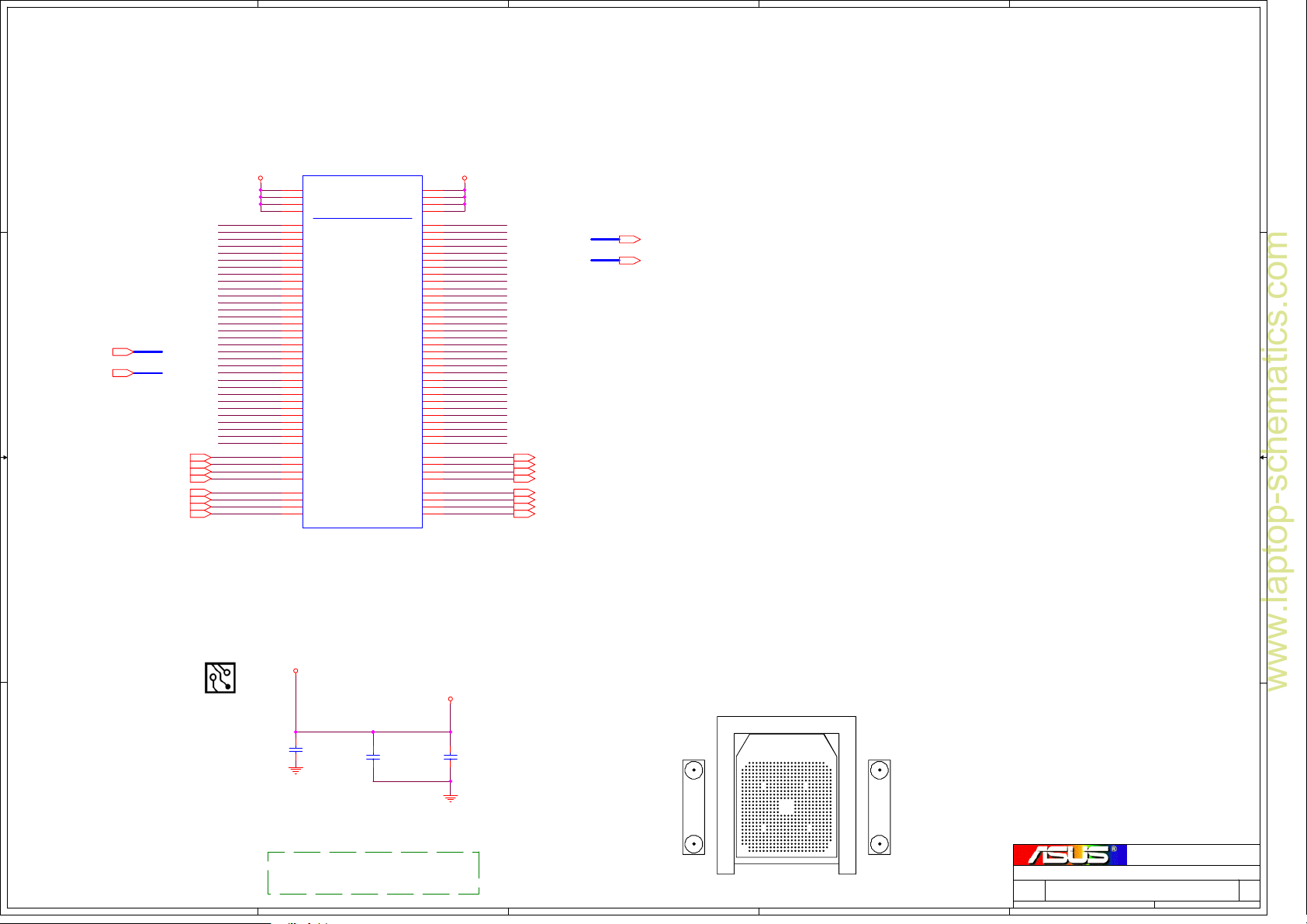

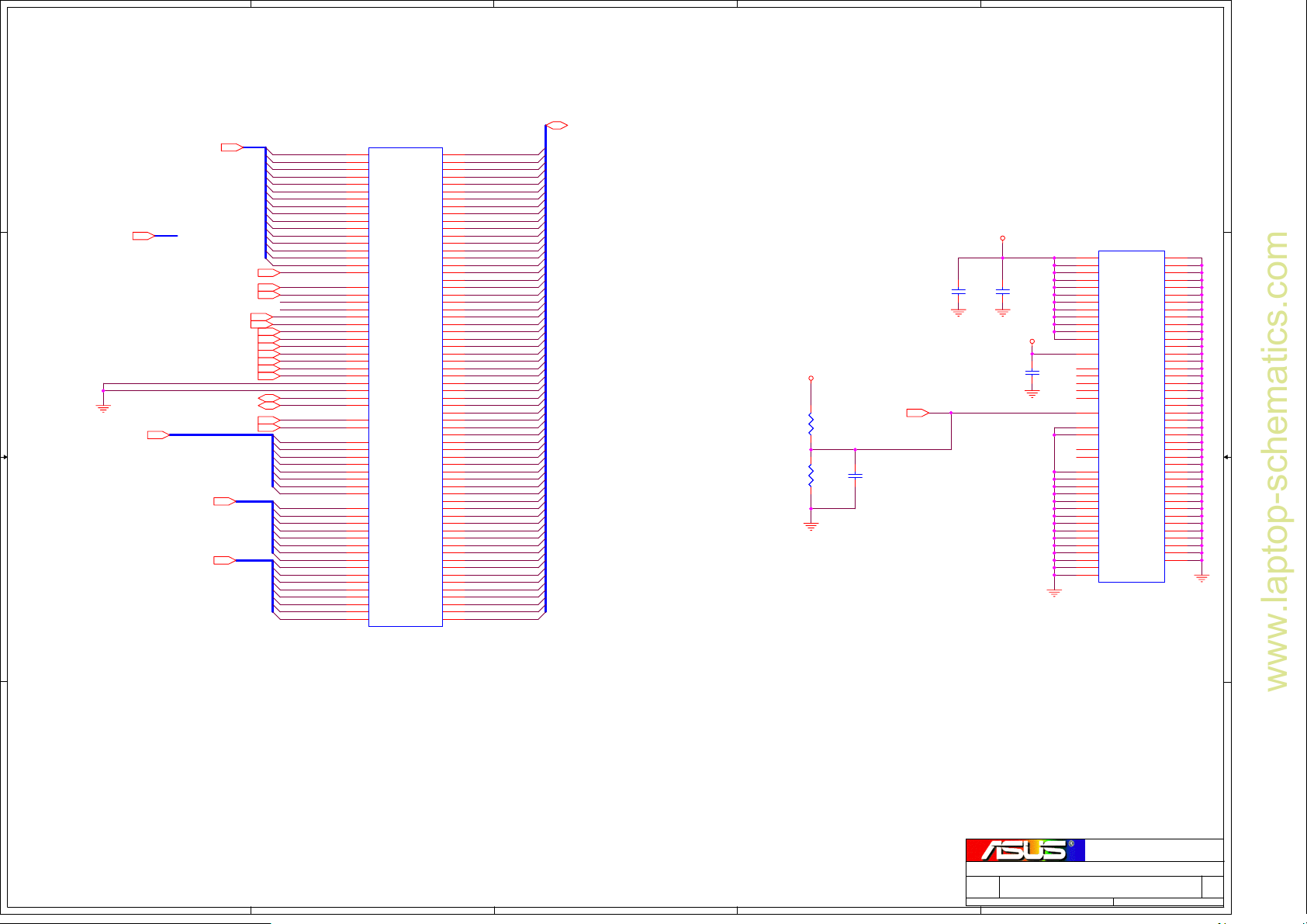

Page 3

5

www.laptop-schematics.com

4

3

2

1

D D

1.5A

U0301A

CPU_VLDT CPU_VLDT

HT_CPU_RXD0

HT_CPU_RXD#0

HT_CPU_RXD1

HT_CPU_RXD#1

HT_CPU_RXD2

HT_CPU_RXD#2

HT_CPU_RXD3

HT_CPU_RXD#3

HT_CPU_RXD4

HT_CPU_RXD#4

HT_CPU_RXD5

HT_CPU_RXD#5

HT_CPU_RXD6

HT_CPU_RXD#6

HT_CPU_RXD7

HT_CPU_RXD#7

HT_CPU_RXD8

C C

HT_CPU_RXD[0..15](10)

HT_CPU_RXD#[0..15](10)

HT_CPU_RX_CLK0(10)

HT_CPU_RX_CLK#0(10)

HT_CPU_RX_CLK1(10)

HT_CPU_RX_CLK#1(10)

HT_CPU_RX_CTL0(10)

HT_CPU_RX_CTL#0(10)

HT_CPU_RX_CTL1(10)

HT_CPU_RX_CTL#1(10)

B B

HT_CPU_RXD#8

HT_CPU_RXD9

HT_CPU_RXD#9

HT_CPU_RXD10

HT_CPU_RXD#10

HT_CPU_RXD11

HT_CPU_RXD#11

HT_CPU_RXD12

HT_CPU_RXD#12

HT_CPU_RXD13

HT_CPU_RXD#13

HT_CPU_RXD14

HT_CPU_RXD#14

HT_CPU_RXD15

HT_CPU_RXD#15

HT_CPU_RX_CLK0

HT_CPU_RX_CLK#0

HT_CPU_RX_CLK1

HT_CPU_RX_CLK#1

HT_CPU_RX_CTL0

HT_CPU_RX_CTL#0

HT_CPU_RX_CTL1

HT_CPU_RX_CTL#1

U0301A

HT LINK

D1

D2

D3

D4

E3

E2

E1

F1

G3

G2

G1

H1

J1

K1

L3

L2

L1

M1

N3

N2

E5

F5

F3

F4

G5

H5

H3

H4

K3

K4

L5

M5

M3

M4

N5

P5

J3

J2

J5

K5

N1

P1

P3

P4

HT LINK

VLDT_A2

VLDT_A3

VLDT_A1

VLDT_A4

L0_CADIN_H[0]

L0_CADIN_L[0]

L0_CADIN_H[1]

L0_CADIN_L[1]

L0_CADIN_H[2]

L0_CADIN_L[2]

L0_CADIN_H[3]

L0_CADIN_L[3]

L0_CADIN_H[4]

L0_CADIN_L[4]

L0_CADIN_H[5]

L0_CADIN_L[5]

L0_CADIN_H[6]

L0_CADIN_L[6]

L0_CADIN_H[7]

L0_CADIN_L[7]

L0_CADIN_H[8]

L0_CADIN_L[8]

L0_CADIN_H[9]

L0_CADIN_L[9]

L0_CADIN_H[10]

L0_CADIN_L[10]

L0_CADIN_H[11]

L0_CADIN_L[11]

L0_CADIN_H[12]

L0_CADIN_L[12]

L0_CADIN_H[13]

L0_CADIN_L[13]

L0_CADIN_H[14]

L0_CADIN_L[14]

L0_CADIN_H[15]

L0_CADIN_L[15]

L0_CLKIN_H[0]

L0_CLKIN_L[0]

L0_CLKIN_H[1]

L0_CLKIN_L[1]

L0_CTLIN_H[0]

L0_CTLIN_L[0]

L0_CTLIN_H[1]

L0_CTLIN_L[1]

SOCKET638

SOCKET638

Change P/N to 12G011306380

L0_CADOUT_H[0]

L0_CADOUT_L[0]

L0_CADOUT_H[1]

L0_CADOUT_L[1]

L0_CADOUT_H[2]

L0_CADOUT_L[2]

L0_CADOUT_H[3]

L0_CADOUT_L[3]

L0_CADOUT_H[4]

L0_CADOUT_L[4]

L0_CADOUT_H[5]

L0_CADOUT_L[5]

L0_CADOUT_H[6]

L0_CADOUT_L[6]

L0_CADOUT_H[7]

L0_CADOUT_L[7]

L0_CADOUT_H[8]

L0_CADOUT_L[8]

L0_CADOUT_H[9]

L0_CADOUT_L[9]

L0_CADOUT_H[10]

L0_CADOUT_L[10]

L0_CADOUT_H[11]

L0_CADOUT_L[11]

L0_CADOUT_H[12]

L0_CADOUT_L[12]

L0_CADOUT_H[13]

L0_CADOUT_L[13]

L0_CADOUT_H[14]

L0_CADOUT_L[14]

L0_CADOUT_H[15]

L0_CADOUT_L[15]

L0_CLKOUT_H[0]

L0_CLKOUT_L[0]

L0_CLKOUT_H[1]

L0_CLKOUT_L[1]

L0_CTLOUT_H[0]

L0_CTLOUT_L[0]

L0_CTLOUT_H[1]

L0_CTLOUT_L[1]

071113

VLDT_B1

VLDT_B2

VLDT_B3

VLDT_B4

AE2

AE3

AE4

AE5

HT_CPU_TXD0

AD1

HT_CPU_TXD#0

AC1

HT_CPU_TXD1

AC2

HT_CPU_TXD#1

AC3

HT_CPU_TXD2

AB1

HT_CPU_TXD#2

AA1

HT_CPU_TXD3

AA2

HT_CPU_TXD#3

AA3

HT_CPU_TXD4

W2

HT_CPU_TXD#4

W3

HT_CPU_TXD5

V1

HT_CPU_TXD#5

U1

HT_CPU_TXD6

U2

HT_CPU_TXD#6

U3

HT_CPU_TXD7

T1

HT_CPU_TXD#7

R1

HT_CPU_TXD8

AD4

HT_CPU_TXD#8

AD3

HT_CPU_TXD9

AD5

HT_CPU_TXD#9

AC5

HT_CPU_TXD10

AB4

HT_CPU_TXD#10

AB3

HT_CPU_TXD11

AB5

HT_CPU_TXD#11

AA5

HT_CPU_TXD12

Y5

HT_CPU_TXD#12

W5

HT_CPU_TXD13

V4

HT_CPU_TXD#13

V3

HT_CPU_TXD14

V5

HT_CPU_TXD#14

U5

HT_CPU_TXD15

T4

HT_CPU_TXD#15

T3

HT_CPU_TX_CLK0

Y1

W1

Y4

Y3

R2

R3

T5

R5

HT_CPU_TX_CLK#0

HT_CPU_TX_CLK1

HT_CPU_TX_CLK#1

HT_CPU_TX_CTL0

HT_CPU_TX_CTL#0

HT_CPU_TX_CTL1

HT_CPU_TX_CTL#1

HT_CPU_TX_CLK0

HT_CPU_TX_CLK#0

HT_CPU_TX_CLK1

HT_CPU_TX_CLK#1

HT_CPU_TX_CTL0

HT_CPU_TX_CTL#0

HT_CPU_TX_CTL1

HT_CPU_TX_CTL#1 (10)

Do not cross plane.

(10)

(10)

(10)

(10)

(10)

(10)

(10)

HT_CPU_TXD[0..15]

HT_CPU_TXD#[0..15]

(10)

(10)

+1.2VS

2009.01.02

del L0302

12

C0302

c0805_h37

c0805_h37

C0302

10UF/6.3V

10UF/6.3V

C0304

C0304

1UF/6.3V

1UF/6.3V

12

GND

A A

Place close to socket

* If VLDT is connected only on one side,

one 4.7uF cap should be added to

the island side

5

4

CPU_VLDT

12

C0305

C0305

1UF/6.3V

1UF/6.3V

GND

AB26

K26

Y26

U26

L26

E26

J26

R26

T26

V26

M26C26

AA26

W26

P26

N26

L25

R25

P25

U25

V25

T25

M25

AA25

Y25

W25

N25

L24

R24

V24

P24

W24

N24

M24

U24

T24

AA24

Y24

AA23

W23

N23

R23

V23P23

T23

M23

U23

L23

Y23

L22

P22

W22

V22

N22

AA22

M22

U22

T22

R22

Y22

L21

V21

N21

W21

P21

M21

U21

AA21

T21

R21

Y21

V20K9K20

M20

N20

R20

AA20

U20

Y20

L20

P20

T20

AA19

Y19

U19N19

L19

V19J19 P19

R19

M19

U18

N18

W18

V18

AA18

L18

P18

Y18

T18

M18

R18

W17

U17

N17

T17

P17

L17

R17

V17

M17

Y17

AA17

L16

N16

AA16

R16

T16

M16

W16

Y16

P16

V16

U16

Y15

L15

AA15

W15

T15

U15

V15

U14

Y14

L14

T14

W14

AA14

V14

U13

L13

AA13

W13

Y13

T13

V13

U12

Y12

AA12

W12

T12

V12

L12

N11

M11

L11 AE11

U11

T11

AA11

P11

W11

V11

R11

Y11

M10

L10

U10

P10 AA10

Y10

V10

T10 AE10

W10

R10

N10

R9

L9

U9W8W9

N9

P9

V9

M9

Y9

T9

AA9

R8

L8

U8N8

M8

P8

AA8

T8

V8

L7

U7

N7

R7

T7

M7

V7R6AA7

W7

P7

P6

W6

V6

N6

M6

Y6

T6

U6

L6

AA6

AA5

R5

W5

P5

M5

Y5

V5

T5

U5

N5K3F5

L5

M4

AA4

N4

V4

W4

P4G4

Y4

R4

T4

U4

L4

Y3

V3D3

AA3

P3

L3

R3

N3

T3

U3

T2

R2

P2

V2

U2

Y2

M2M3AA2

N2

L2

W2

Y1

T1

V1

AA1

P1

L1

M1

U1

W1

R1

N1

AD26

AC26

AB25

AE25

AD25

AC25

AB24

AD24

AF24

AC24

AE24

AD23

AF23

AB23

AC23

AE23

AD22

AB22

AC22

AF22

AE22

AF21

AD21

AC21

AE21

AB21

AE20

AC20

AF20

AD20

AB20

AE19

AD19

AF19T19

AC19

AB19

AC18

AE18

AB18

AF18

AD18

AC17

AE17

AF17

AB17

AD17

AC16

AF16

AB16

AD16

AE16

AF15

AC15

AB15J15

AD15

AE15H15

AD14

AB14

AF14

AC14

AE14

AD13

AF13

AB13

AE13

AC13

AD12

AC12

AB12

AF12

AE12

AC11

AF11

AC10

AD10

AB10

AF10

AE9

AB9

AC9

AD9

AF9

AC8

AE8

AD8

AF8

AB8

AC7

AD7

AB7

AE7

AF7

AC6

AD6

AE6

AB6

AF6

AE5

AC5

AD5

AB5

AF5

AF4

AE4

AC4

AB4

AD4

AC3

AB3

AE3

AD3

AD2

AC2

AE2

AB2

AD1

AB1

AC1

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size

Size

Size

Project Name

Project Name

Project Name

Custom

Custom

Custom

Wednesday, April 08, 2009

Wednesday, April 08, 2009

Wednesday, April 08, 2009

Date: Sheet

Date: Sheet

2

Date: Sheet

Engineer:

K40AB

Title :

Title :

Title :

1

Griffin HT I/F

Griffin HT I/F

Griffin HT I/F

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

R1.3

of

394

of

394

of

394

Rev

Rev

Rev

F26

D26

G26

H26

C25

G25

F25

B25

K25

D25

H25

E25

J25

G24

K24

A24

F24

C24

D24

J24

B24

H24

E24

F23

G23

C23

B23

H23

J23

K23

D23

A23

E23

F22

H22

G22

B22

A22

K22

J22

C22

E22

D22

D21

J21

H21

G21

F21

A21

K21

C21

B21

E21

A20

F20

H20

D20

B20

E20

C20

J20

F19

E19

H19

A19

B19

K19

C19

D19

E18

H18

K18

A18

G18

F18

C18

D18

J18

B18

G17

H17

K17

E17

F17

A17

J17

C17

B17

D17

B16B3H16

K16

E16

G16

J16

C16

F16

A16

D16

K15

G15

A15

C15

F15

E15

B15

D15

E14

H14

G14

J14

K14

A14

F14

D14

B14

C14

K13

D13

J13

C13

B13

E13

H13

A13

F13

G13

E12

D12

C12

K12

F12

H12

A12

G12

J12

B12

H11

G11 AD11

C11

K11

F11

A11

D11

E11

B11 AB11

J11

G10

K10

C10

J10

F10

E10

B10

A10

D10

H10

C9

E9

F9

A9

H9

G9

D9

J9

B9

D8

F8

H8

K8

E8

A8

C8

J8

B8

H7

K7

B7

J7

C7

D7

E7

A7

F7

H6

D6

J6

G6

E6

C6

K6

A6

F6

B6

J5

K5

H5

E5

G5

A5

B5

D5

C5

H4

J4

C4

A4

D4

B4

K4

F4

E4

H3

E3

J3 W3

F3

C3

A3

G3

E2

D2

H2

C2

J2

G2

F2

K2

E1

F1

H1

D1

J1

C1

K1

G1

A1

BGA638_50_26SQ_S1G2_OEM

3

Page 4

5

www.laptop-schematics.com

4

3

2

1

place close to PROCESSOR within 1.5 inch place close to PROCESSOR within 1.5 inch

MEM_MA0_CLK_H7

12

0.75A

PLACE THEM CLOSE TO

CPU WITHIN 1"

D D

T0401 TPC28TT0401 TPC28T

T0402TPC28T T0402TPC28T

T0403TPC28T T0403TPC28T

MEM_MA0_CS#0(7,9)

MEM_MA0_CS#1(7,9)

MEM_MA_ADD[0..15](7,9)

C C

1KOhm

1KOhm

B B

1KOhm

1KOhm

c0805_h37

c0805_h37

A A

+1.8V

R0403

R0403

1%

1%

R0404

R0404

1%

1%

+1.8V

+0.9V

12

0.1UF/16V

0.1UF/16V

1

1 2

1 2

C0434

C0434

1

1

+0.9V

12

10UF/6.3V

10UF/6.3V

GND

MEM_MA1_ODT0

MEM_MA1_ODT1

MEM_MA_CKE0(7,9)

MEM_MA_CKE1(7,9)

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H7

MEM_MA0_CLK_L7

MEM_MA_BANK0(7,9)

MEM_MA_BANK1(7,9)

MEM_MA_BANK2(7,9)

MEM_MA_RAS#(7,9)

MEM_MA_CAS#(7,9)

MEM_MA_WE#(7,9)

C0432

C0432

12

C0435

C0435

0.1UF/16V

0.1UF/16V

5

R0401 39.2OHMR0401 39.2OHM

1 2

1 2

R0402 39.2OHMR0402 39.2OHM

MEM_MA0_ODT0(7,9)

MEM_MA0_ODT1(7,9)

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

CPU_M_VREF

12

C0403

C0403

0.1UF/16V

0.1UF/16V

GND

12

10UF/6.3V

10UF/6.3V

GND

12

0.1UF/16V

0.1UF/16V

MEM_MA_RESET#

sensing point for

op-amp feedback

routed near CPU

c0805_h37

c0805_h37

C0433

C0433

12

C0436

C0436

C0437

C0437

0.1UF/16V

0.1UF/16V

GND

M_ZP

M_ZN

AD10

AF10

AE10

AA16

D10

C10

B10

H16

T19

V22

U21

V19

T20

U19

U20

V20

J22

J20

N19

N20

E16

F16

Y16

P19

P20

N21

M20

N22

M19

M22

L20

M24

L21

L19

K22

R21

L22

K20

V24

K24

K19

R20

R23

J21

R19

T22

T24

U0301B

U0301B

VTT2

VTT8

VTT3

VTT1

M_ZP

M_ZN

RSVD8

MA0_ODT[0]

MA0_ODT[1]

MA1_ODT[0]

MA1_ODT[1]

MA0_CS_L[0]

MA0_CS_L[1]

MA1_CS_L[0]

MA1_CS_L[1]

MA_CKE[0]

MA_CKE[1]

MA_CLK_H[5]

MA_CLK_L[5]

MA_CLK_H[1]

MA_CLK_L[1]

MA_CLK_H[7]

MA_CLK_L[7]

MA_CLK_H[4]

MA_CLK_L[4]

MA_ADD[0]

MA_ADD[1]

MA_ADD[2]

MA_ADD[3]

MA_ADD[4]

MA_ADD[5]

MA_ADD[6]

MA_ADD[7]

MA_ADD[8]

MA_ADD[9]

MA_ADD[10]

MA_ADD[11]

MA_ADD[12]

MA_ADD[13]

MA_ADD[14]

MA_ADD[15]

MA_BANK[0]

MA_BANK[1]

MA_BANK[2]

MA_RAS_L

MA_CAS_L

MA_WE_L

SOCKET638

SOCKET638

+0.9V

12

C0430

C0430

0.1UF/16V

0.1UF/16V

MEM:CMD/CTRL/CLK

MEM:CMD/CTRL/CLK

VTT_SENSE

MB0_ODT[0]

MB0_ODT[1]

MB1_ODT[0]

MB0_CS_L[0]

MB0_CS_L[1]

MB1_CS_L[0]

MB_CKE[0]

MB_CKE[1]

MB_CLK_H[5]

MB_CLK_L[5]

MB_CLK_H[1]

MB_CLK_L[1]

MB_CLK_H[7]

MB_CLK_L[7]

MB_CLK_H[4]

MB_CLK_L[4]

MB_ADD[0]

MB_ADD[1]

MB_ADD[2]

MB_ADD[3]

MB_ADD[4]

MB_ADD[5]

MB_ADD[6]

MB_ADD[7]

MB_ADD[8]

MB_ADD[9]

MB_ADD[10]

MB_ADD[11]

MB_ADD[12]

MB_ADD[13]

MB_ADD[14]

MB_ADD[15]

MB_BANK[0]

MB_BANK[1]

MB_BANK[2]

MB_RAS_L

MB_CAS_L

MB_WE_L

12

C0431

C0431

0.1UF/16V

0.1UF/16V

GND

VTT4

VTT5

VTT6

VTT7

VTT9

M_VREF

RSVD6

W10

AC10

AB10

AA10

A10

VTT_SENSE

Y10

W17

MEM_MB_RESET#

B18

W26

W23

MEM_MB1_ODT0

Y26

V26

W25

U22

J25

H26

P22

R22

MEM_MB0_CLK_H1

A17

MEM_MB0_CLK_L1

A18

MEM_MB0_CLK_H7

AF18

MEM_MB0_CLK_L7

AF17

R26

R25

MEM_MB_ADD0

P24

MEM_MB_ADD1

N24

MEM_MB_ADD2

P26

MEM_MB_ADD3

N23

MEM_MB_ADD4

N26

MEM_MB_ADD5

L23

MEM_MB_ADD6

N25

MEM_MB_ADD7

L24

MEM_MB_ADD8

M26

MEM_MB_ADD9

K26

MEM_MB_ADD10

T26

MEM_MB_ADD11

L26

MEM_MB_ADD12

L25

MEM_MB_ADD13

W24

MEM_MB_ADD14

J23

MEM_MB_ADD15

J24

R24

U26

J26

U25

U24

U23

PLACE CLOSE TO CPU

MEM_MA_DQS[0..7](7)

MEM_MA_DQS#[0..7](7)

MEM_MB_DQS[0..7](8)

MEM_MB_DQS#[0..7](8)

4

+0.9V+0.9V

071115

1

T0417 TPC28TT0417 TPC28T

1

T0411

T0411

MEM_MB_CKE0 (8,9)

MEM_MB_CKE1 (8,9)

MEM_MB_BANK0 (8,9)

MEM_MB_BANK1 (8,9)

MEM_MB_BANK2 (8,9)

MEM_MB_RAS# (8,9)

MEM_MB_CAS# (8,9)

MEM_MB_WE# (8,9)

09/23 2.0

T0410TPC28T T0410TPC28T

1

MEM_MB0_ODT0 (8,9)

MEM_MB0_ODT1 (8,9)

TPC28T

TPC28T

MEM_MB0_CS#0 (8,9)

MEM_MB0_CS#1 (8,9)

MEM_MB_ADD[0..15] (8,9)

CPU_M_VREF

MEM_MA0_CLK#1(7)

MEM_MB_DATA[0..63](8)

MEM_MB_DM[0..7](8) MEM_MA_DM[0..7] (7)

3

C0405 1.5PF/50V MLCC/+/-0.1PFC0405 1.5PF/50V MLCC/+/-0.1PF

MEM_MA0_CLK_L7

MEM_MA0_CLK_H1

12

C0406 1.5PF/50V MLCC/+/-0.1PFC0406 1.5PF/50V MLCC/+/-0.1PF

MEM_MA0_CLK_L1

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

To SODIMM socket 1

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

MEM_MB_DQS0

MEM_MB_DQS#0

MEM_MB_DQS1

MEM_MB_DQS#1

MEM_MB_DQS2

MEM_MB_DQS#2

MEM_MB_DQS3

MEM_MB_DQS#3

MEM_MB_DQS4

MEM_MB_DQS#4

MEM_MB_DQS5

MEM_MB_DQS#5

MEM_MB_DQS6

MEM_MB_DQS#6

MEM_MB_DQS7

MEM_MB_DQS#7

Processor Memory Interface

AA24

AA23

AD24

AE24

AA26

AA25

AD26

AE25

AC22

AD22

AE20

AF20

AF24

AF23

AC20

AD20

AD18

AE18

AC14

AD14

AF19

AC18

AF16

AF15

AF13

AC12

AB11

AE14

AF14

AF11

AD11

AB26

AE22

AC16

AD12

AC25

AC26

AF21

AF22

AE16

AD16

AF12

AE12

C11

A11

A14

B14

G11

E11

D12

A13

A15

A16

A19

A20

C14

D14

C18

D18

D20

A21

D24

C25

B20

C20

B24

C24

E23

E24

G25

G26

C26

D26

G23

G24

Y11

A12

B16

A22

E25

C12

B12

D16

C16

A24

A23

F26

E26

071114

U0301C

U0301C

MB_DATA[0]

MB_DATA[1]

MB_DATA[2]

MB_DATA[3]

MB_DATA[4]

MB_DATA[5]

MB_DATA[6]

MB_DATA[7]

MB_DATA[8]

MB_DATA[9]

MB_DATA[10]

MB_DATA[11]

MB_DATA[12]

MB_DATA[13]

MB_DATA[14]

MB_DATA[15]

MB_DATA[16]

MB_DATA[17]

MB_DATA[18]

MB_DATA[19]

MB_DATA[20]

MB_DATA[21]

MB_DATA[22]

MB_DATA[23]

MB_DATA[24]

MB_DATA[25]

MB_DATA[26]

MB_DATA[27]

MB_DATA[28]

MB_DATA[29]

MB_DATA[30]

MB_DATA[31]

MB_DATA[32]

MB_DATA[33]

MB_DATA[34]

MB_DATA[35]

MB_DATA[36]

MB_DATA[37]

MB_DATA[38]

MB_DATA[39]

MB_DATA[40]

MB_DATA[41]

MB_DATA[42]

MB_DATA[43]

MB_DATA[44]

MB_DATA[45]

MB_DATA[46]

MB_DATA[47]

MB_DATA[48]

MB_DATA[49]

MB_DATA[50]

MB_DATA[51]

MB_DATA[52]

MB_DATA[53]

MB_DATA[54]

MB_DATA[55]

MB_DATA[56]

MB_DATA[57]

MB_DATA[58]

MB_DATA[59]

MB_DATA[60]

MB_DATA[61]

MB_DATA[62]

MB_DATA[63]

MB_DM[0]

MB_DM[1]

MB_DM[2]

MB_DM[3]

MB_DM[4]

MB_DM[5]

MB_DM[6]

MB_DM[7]

MB_DQS_H[0]

MB_DQS_L[0]

MB_DQS_H[1]

MB_DQS_L[1]

MB_DQS_H[2]

MB_DQS_L[2]

MB_DQS_H[3]

MB_DQS_L[3]

MB_DQS_H[4]

MB_DQS_L[4]

MB_DQS_H[5]

MB_DQS_L[5]

MB_DQS_H[6]

MB_DQS_L[6]

MB_DQS_H[7]

MB_DQS_L[7]

SOCKET638

SOCKET638

MEM_MB0_CLK7(8)MEM_MA0_CLK7(7)

MEM_MB0_CLK#7(8)MEM_MA0_CLK#7(7)

MEM_MB0_CLK1(8)MEM_MA0_CLK1(7)

MEM_MB0_CLK#1(8)

MEM:DATA

MEM:DATA

MA_DATA[10]

MA_DATA[11]

MA_DATA[12]

MA_DATA[13]

MA_DATA[14]

MA_DATA[15]

MA_DATA[16]

MA_DATA[17]

MA_DATA[18]

MA_DATA[19]

MA_DATA[20]

MA_DATA[21]

MA_DATA[22]

MA_DATA[23]

MA_DATA[24]

MA_DATA[25]

MA_DATA[26]

MA_DATA[27]

MA_DATA[28]

MA_DATA[29]

MA_DATA[30]

MA_DATA[31]

MA_DATA[32]

MA_DATA[33]

MA_DATA[34]

MA_DATA[35]

MA_DATA[36]

MA_DATA[37]

MA_DATA[38]

MA_DATA[39]

MA_DATA[40]

MA_DATA[41]

MA_DATA[42]

MA_DATA[43]

MA_DATA[44]

MA_DATA[45]

MA_DATA[46]

MA_DATA[47]

MA_DATA[48]

MA_DATA[49]

MA_DATA[50]

MA_DATA[51]

MA_DATA[52]

MA_DATA[53]

MA_DATA[54]

MA_DATA[55]

MA_DATA[56]

MA_DATA[57]

MA_DATA[58]

MA_DATA[59]

MA_DATA[60]

MA_DATA[61]

MA_DATA[62]

MA_DATA[63]

MA_DQS_H[0]

MA_DQS_L[0]

MA_DQS_H[1]

MA_DQS_L[1]

MA_DQS_H[2]

MA_DQS_L[2]

MA_DQS_H[3]

MA_DQS_L[3]

MA_DQS_H[4]

MA_DQS_L[4]

MA_DQS_H[5]

MA_DQS_L[5]

MA_DQS_H[6]

MA_DQS_L[6]

MA_DQS_H[7]

MA_DQS_L[7]

2

MEM_MB0_CLK_H7

12

C0407 1.5PF/50V MLCC/+/-0.1PFC0407 1.5PF/50V MLCC/+/-0.1PF

MEM_MB0_CLK_L7

MEM_MB0_CLK_H1

12

C0408 1.5PF/50V MLCC/+/-0.1PFC0408 1.5PF/50V MLCC/+/-0.1PF

MEM_MB0_CLK_L1

MEM_MA_DATA0

G12

MA_DATA[0]

MA_DATA[1]

MA_DATA[2]

MA_DATA[3]

MA_DATA[4]

MA_DATA[5]

MA_DATA[6]

MA_DATA[7]

MA_DATA[8]

MA_DATA[9]

MA_DM[0]

MA_DM[1]

MA_DM[2]

MA_DM[3]

MA_DM[4]

MA_DM[5]

MA_DM[6]

MA_DM[7]

F12

H14

G14

H11

H12

C13

E13

H15

E15

E17

H17

E14

F14

C17

G17

G18

C19

D22

E20

E18

F18

B22

C23

F20

F22

H24

J19

E21

E22

H20

H22

Y24

AB24

AB22

AA21

W22

W21

Y22

AA22

Y20

AA20

AA18

AB18

AB21

AD21

AD19

Y18

AD17

W16

W14

Y14

Y17

AB17

AB15

AD15

AB13

AD13

Y12

W11

AB14

AA14

AB12

AA12

E12

C15

E19

F24

AC24

Y19

AB16

Y13

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_DQS0

MEM_MA_DQS#0

MEM_MA_DQS1

MEM_MA_DQS#1

MEM_MA_DQS2

MEM_MA_DQS#2

MEM_MA_DQS3

MEM_MA_DQS#3

MEM_MA_DQS4

MEM_MA_DQS#4

MEM_MA_DQS5

MEM_MA_DQS#5

MEM_MA_DQS6

MEM_MA_DQS#6

MEM_MA_DQS7

MEM_MA_DQS#7

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Date: Sheet

Date: Sheet

Date: Sheet

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Wednesday, April 08, 2009

Wednesday, April 08, 2009

Wednesday, April 08, 2009

MEM_MA_DATA[0..63] (7)

To SODIMM socket 0

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

Griffin DDR2 MEMORY I/F

Griffin DDR2 MEMORY I/F

Griffin DDR2 MEMORY I/F

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

494

494

494

Rev

Rev

Rev

of

of

of

Page 5

5

E

E

E

www.laptop-schematics.com

+1.8VS

RN0501C

RN0501C

300Ohm

300Ohm

CPU_PWRGD(20)

D D

CPU_LDT_STOP#(12,20)

CPU_LDT_RST#(20)

NB_ALLOW_LDTSTOP(12,20)

+1.8V

R0504 390OhmR0504 390Ohm

R0505 390OhmR0505 390Ohm

08/11 change to 390OHM

1 2

1 2

RN0501D

RN0501D

300Ohm

300Ohm

5 6

RN0501B

RN0501B

300Ohm

300Ohm

7 8

CPU_SIC

CPU_SID

RN0501A

RN0501A

300Ohm

300Ohm

3 4

1 2

CPU_PWRGD

CPU_PWRGD

CPU_LDT_STOP#

CPU_LDT_RST#

CPU_LDT_REQ#_CPU

2008.03.04

add C503 optional to /X

5PF/50V

5PF/50V

1 2

C0503

C0503

/X

/X

SRC_CPU_HT_CLKP(29)

SRC_CPU_HT_CLKN(29)

080424

add R554 R555 R556

place them to CPU within 1.5"

+1.8V

12

12

C C

R0560

R0560

1KOhm

1KOhm

R0507

R0507

1KOhm

1KOhm

TPC28T

TPC28T

TF14

TF14

1

1

TF15

TF15

TPC28T

TPC28T

route as diff

pair

5/5/5,10mil

CPU_SVC (81)

CPU_SVD (81)

Serial VID Interface clock/data

B B

CPU_VLDT

CPU_VDD0_RUN_FB_H(81)

CPU_VDD0_RUN_FB_L(81)

CPU_VDD1_RUN_FB_H(81)

CPU_VDD1_RUN_FB_L(81)

4

GND

keep trace fromresistor to

CPU within 0.6"

keep trace from caps to

CPU within 1.2"

3900PF/50V

3900PF/50V

3900PF/50V

3900PF/50V

20080716

20080716

R1.1

GND

R0513 44.2OhmR0513 44.2Ohm

GND

R0514 44.2OhmR0514 44.2Ohm

T0501 TPC28TT0501 TPC28T

T0502 TPC28TT0502 TPC28T

T0503 TPC28TT0503 TPC28T

T0504 TPC28TT0504 TPC28T

T0505 TPC28TT0505 TPC28T

T0506 TPC28TT0506 TPC28T

T0507 TPC28TT0507 TPC28T

T0508 TPC28TT0508 TPC28T

T0509 TPC28TT0509 TPC28T

T0510 TPC28TT0510 TPC28T

T0511 TPC28TT0511 TPC28T

T0513 TPC28TT0513 TPC28T

GND

C0501

C0501

12

169Ohm

169Ohm

C0507

C0507

12

CPU_LDT_RST#

CPU_PWRGD

CPU_LDT_STOP#

12

C0540

C0540

1000PF/50V

1000PF/50V

N/A

N/A

1 2

1 2

1

1

LAYOUT: ROUTE VDDA TRACE APPROX.

50 mils WIDE (USE 2x25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

U0301D

F10

AF4

AF5

AE6

AB6

G10

AA9

AC9

AD9

AF9

AD7

H10

AB8

AF7

AE7

AE8

AC8

AF8

AA6

F8

F9

A9

A8

B7

A7

C6

R6

P6

F6

E6

Y6

G9

E9

E8

C2

A3

A5

B3

B5

C1

U0301D

VDDA2

VDDA1

CLKIN_H

CLKIN_L

RESET_L

PWROK

LDTSTOP_L

LDTREQ_L

SIC

SID

ALERT_L

HTREF0

HTREF1

VDD0_FB_H

VDD0_FB_L

VDD1_FB_H

VDD1_FB_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST23

TEST18

TEST19

TEST25_H

TEST25_L

TEST21

TEST20

TEST24

TEST22

TEST12

TEST27

TEST9

TEST6

RSVD7

RSVD10

RSVD2

RSVD11

RSVD9

SOCKET638

SOCKET638

R0512

R0512

CPU_CLK_H_C

1 2

CPU_CLK_L_C

CPU_LDT_REQ#_CPU

CPU_SIC

CPU_SID

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPU_TEST23

1

CPU_TEST18

1

CPU_TEST19

1

CPU_TEST25_H

CPU_TEST25_L

CPU_TEST21

1

CPU_TEST20

1

CPU_TEST24

1

CPU_TEST22

1

CPU_TEST12

1

CPU_TEST27

1

CPU_TEST9_ANALOGIN

CPU_TEST6_DIECRACKMON

1

0.25A

VDDA

CPU_HTREF0

CPU_HTREF1

3

THERMTRIP_L

PROCHOT_L

MEMHOT_L

THERMDC

THERMDA

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

DBREQ_L

TEST28_H

TEST28_L

TEST17

TEST16

TEST15

TEST14

TEST7

TEST10

TEST8

TEST29_H

TEST29_L

RSVD4

RSVD3

RSVD1

RSVD5

RSVD12

KEY1

KEY2

SVC

SVD

TDO

M11

W18

A6

A4

AF6

AC7

AA8

W7

W8

W9

Y9

H6

G6

E10

AE9

J7

H8

D7

E7

F7

C7

C3

K8

C4

C9

C8

H18

H19

AA7

D5

C5

放在

RN0502A

RN0502A

CPU_SVC

CPU_SVD

300Ohm

300Ohm

CPU_THRMTRIP#_1.8V

CPU_PROCHOT#

CPU_MEMHOT#_1.8V

CPU_VDDIO_SUS_FB_H

CPU_VDDIO_SUS_FB_L

CPU_VDDNB_RUN_FB_H

CPU_DBREQ#

CPU_TDO

CPU_TEST28_H

CPU_TEST28_L

CPU_TEST17

CPU_TEST16

CPU_TEST15

CPU_TEST14

CPU_TEST7_ANALOG_T

CPU_TEST10_ANALOGOUT

CPU_TEST8_DIG_T

CPU_TEST29_H_FBCLKOUT_P

CPU_TEST29_L_FBCLKOUT_N

20080719

power

100UF/6.3V

100UF/6.3V

+1.8V

RN0502C

RN0502C

RN0502B

RN0502B

300Ohm

300Ohm

300Ohm

300Ohm

1 2

3 4

CPU_THRM_DC (50)

CPU_THRM_DA

1

T0534 TPC28TT0534 TPC28T

1

T0533 TPC28TT0533 TPC28T

CPU_VDDNB_RUN_FB_H (81)

1

1

T0524TPC28T T0524TPC28T

1

T0525TPC28T T0525TPC28T

1

T0526TPC28T T0526TPC28T

1

T0527TPC28T T0527TPC28T

1

T0528TPC28T T0528TPC28T

1

T0529TPC28T T0529TPC28T

1

T0530TPC28T T0530TPC28T

1

1

1

+2.5V_CPU_VDDA

12

C504

C504

5 6

(50)

T0522TPC28T T0522TPC28T

T0523TPC28T T0523TPC28T

T0531TPC28T T0531TPC28T

T0532TPC28T T0532TPC28T

2

R0580

R0580

1 2

C0504

C0504

1UF/6.3V

1UF/6.3V

0Ohm

0Ohm

12

GND

1 2

B

B

E12

E12

Q0503

Q0503

PMBS3904

PMBS3904

VDDA

C0570

C0570

CPU_PWRGD

R0523

R0523

10KOhm

10KOhm

C0502

C0502

1 2

C

C

3

3

12

0.1UF/16V

0.1UF/16V

0.1UF/10V

0.1UF/10V

GND

CPU_PROCHOT# (20)

1

T0514 TPC28TT0514 TPC28T

T0515 TPC28TT0515 TPC28T

T0516 TPC28TT0516 TPC28T

T0517 TPC28TT0517 TPC28T

T0518 TPC28TT0518 TPC28T

T0519 TPC28TT0519 TPC28T

T0520 TPC28TT0520 TPC28T

T0521 TPC28TT0521 TPC28T

1

1

1

G

G

3

2

3

2

32

D

D

S

S

2N7002

2N7002

Q0580

Q0580

CPU_DBREQ#

CPU_TEST27

CPU_TEST20

CPU_TEST21

CPU_TEST22

CPU_TEST24

0103 change R0527 R0529 R0533 TO 300ohm

CPU_TEST25_L

CPU_TEST25_H

CPU_TEST12

CPU_TEST15

CPU_TEST14

CPU_TEST18

CPU_TEST19

CPU_TEST23

5 6

1 2

3 4

7 8

3 4

1 2

1

1

1

1

1

1

1

1

BUF_PLT_RST# (20,30,70)

FORCE_OFF# (30,57,60,86,87)

7 8

300Ohm

300Ohm

RN0503C

RN0503C

300Ohm

300Ohm

RN0503A

RN0503A

300Ohm

300Ohm

RN0506B

RN0506B

300Ohm

300Ohm

RN0503D

RN0503D

300Ohm

300Ohm

RN0503B

RN0503B

300Ohm

300Ohm

N/A

N/A

R0528 510Ohm

R0528 510Ohm

1 2

R0530

R0530

1 2

RN0506A

RN0506A

300Ohm

300Ohm

5 6

300Ohm

300Ohm

7 8

300Ohm

300Ohm

1 2

300Ohm

300Ohm

3 4

300Ohm

300Ohm

5 6

300Ohm

300Ohm

CPU_CLK_H_C

CPU_CLK_L_C

CPU_LDT_STOP#

CPU_PWRGD

CPU_VDD0_RUN_FB_H

CPU_VDD0_RUN_FB_L

CPU_VDD1_RUN_FB_H

CPU_VDD1_RUN_FB_L

+1.8V

RN0502D

RN0502D

GND

+1.8V

510OhmN/A

510OhmN/A

RN0505C

RN0505C

RN0505D

RN0505D

RN0505A

RN0505A

RN0505B

RN0505B

RN0506C

RN0506C

GND

to CPU

CPU_PROCHOT#

N/A

N/A

VRHOT#(81)

P0500

P0500

1

CPU_LDT_RST#

1 2

CPU_PWRGD

A A

5

R05440Ohm /XR05440Ohm /X

1 2

R05450Ohm /XR05450Ohm /X

+1.8V

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

NC

3

DBREQ_L1

5

DBRDY1

7

DBREQ_L2

9

DBRDY2

11

DBREQ_L3

13

DBRDY3

15

DBREQ_L4

17

DBRDY4

19

DBREQ_L5

21

DBRDY5

23

DBREQ_L6

ASP_68200_07_K25

ASP_68200_07_K25

/X

/X

4

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

DBRDY7

DBREQ_L7

DBRDY6

GND9

GND10

2

4

6

8

10

12

14

16

18

20

22

24

26

+3VS +1.8V

12

R0541

R0541

/X

10KOhm

10KOhm

/X

PMBS3904

PMBS3904

/X

/X

12

R0540

R0540

10KOhm

10KOhm

/X

/X

B

B

Q0505

Q0505

E12

E12

CPU_LDT_RST#

3

C

C

3

3

EC to CPU/PWR

12

D502 RB751V-40

D502 RB751V-40

2

2N7002

2N7002

Q0504

Q0504

S

S

GND

32

3

3

D

D

1

1

1

G

G

2

2

THRO_CPU (30)

From EC.

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Wednesday, April 08, 2009

Wednesday, April 08, 2009

Wednesday, April 08, 2009

Date: Sheet

Date: Sheet

Date: Sheet

Engineer:

1

Griffin CNTL/DEBUG/TH

Griffin CNTL/DEBUG/TH

Griffin CNTL/DEBUG/TH

Title :

Title :

Title :

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Rev

Rev

Rev

of

594

of

594

of

594

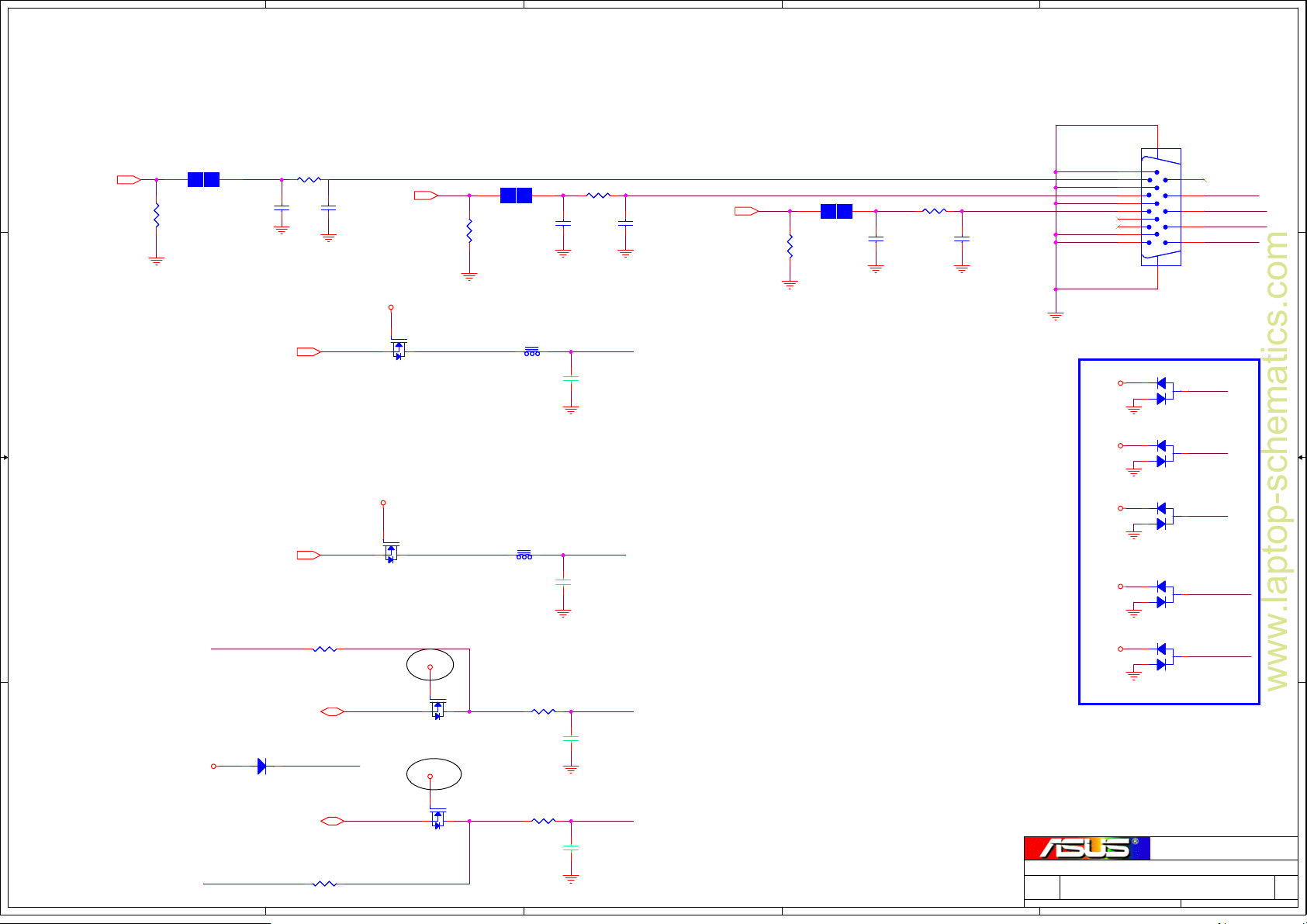

Page 6

5

www.laptop-schematics.com

D D

+CPU_VDDNB

3A

C C

+CPU_VDD0 +CPU_VDD1

+1.8V

2A

18A 18A

U0301E

U0301E

J11

J13

J15

K10

K12

K14

L11

L13

L15

M10

N11

K16

M16

P16

T16

V16

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

G4

H2

J9

K6

L4

L7

L9

M2

M6

M8

N7

N9

VDD0_22

VDD0_2

VDD0_15

VDD0_5

VDD0_6

VDD0_7

VDD0_21

VDD0_4

VDD0_8

VDD0_9

VDD0_23

VDD0_10

VDD0_11

VDD0_16

VDD0_17

VDD0_18

VDD0_1

VDD0_3

VDD0_12

VDD0_19

VDD0_13

VDD0_14

VDD0_20

VDDNB1

VDDNB3

VDDNB4

VDDNB5

VDDNB2

VDDIO27

VDDIO13

VDDIO14

VDDIO8

VDDIO7

VDDIO11

VDDIO20

VDDIO15

VDDIO9

VDDIO10

VDDIO12

VDDIO21

SOCKET638

SOCKET638

VDD1_8

VDD1_20

VDD1_2

VDD1_9

VDD1_10

VDD1_21

VDD1_4

VDD1_25

VDD1_17

VDD1_24

VDD1_22

VDD1_23

VDD1_18

VDD1_19

VDD1_11

VDD1_12

VDD1_13

VDD1_26

VDD1_7

VDD1_14

VDD1_15

VDD1_16

VDD1_6

VDD1_3

VDD1_5

VDD1_1

VDDIO26

VDDIO25

VDDIO23

VDDIO24

VDDIO19

VDDIO18

VDDIO5

VDDIO6

VDDIO3

VDDIO17

VDDIO22

VDDIO4

VDDIO1

VDDIO2

VDDIO16

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

W4

Y2

AC4

AD2

Y25

V25

V23

V21

V18

U17

T25

T23

T21

T18

R17

P25

P23

P21

P18

4

GND

AA11

AA13

AA15

AA17

AA19

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

AA4

AB2

AB7

AB9

AD6

AD8

B11

B13

B15

B17

B19

B21

B23

B25

D11

D13

D15

D17

D19

D21

D23

D25

F11

F13

F15

F17

F19

F21

F23

F25

H21

H23

B4

B6

B8

B9

D6

D8

D9

E4

F2

H7

H9

J4

3

U0301F

U0301F

VSS49

VSS128

VSS78

VSS75

VSS77

VSS79

VSS48

VSS39

VSS90

VSS93

VSS97

VSS129

VSS86

VSS85

VSS83

VSS82

VSS74

VSS40

VSS91

VSS94

VSS73

VSS87

VSS84

VSS88

VSS81

VSS80

VSS76

VSS122

VSS123

VSS124

VSS42

VSS119

VSS13

VSS20

VSS21

VSS23

VSS17

VSS18

VSS4

VSS92

VSS125

VSS41

VSS24

VSS19

VSS16

VSS22

VSS14

VSS15

VSS3

VSS7

VSS47

VSS45

VSS126

VSS1

VSS9

VSS10

VSS2

VSS11

VSS5

VSS12

VSS113

VSS89

VSS8

VSS6

VSS44

SOCKET638

SOCKET638

VSS30

VSS116

VSS115

VSS26

VSS27

VSS28

VSS29

VSS46

VSS35

VSS69

VSS31

VSS32

VSS33

VSS34

VSS120

VSS37

VSS98

VSS99

VSS100

VSS101

VSS36

VSS38

VSS52

VSS25

VSS102

VSS71

VSS54

VSS103

VSS104

VSS53

VSS72

VSS55

VSS56

VSS105

VSS106

VSS58

VSS107

VSS108

VSS57

VSS117

VSS118

VSS109

VSS110

VSS111

VSS112

VSS50

VSS63

VSS114

VSS127

VSS59

VSS60

VSS61

VSS62

VSS51

VSS70

VSS121

VSS64

VSS65

VSS66

VSS67

VSS68

VSS96

VSS95

VSS43

2

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

AC6

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

GND

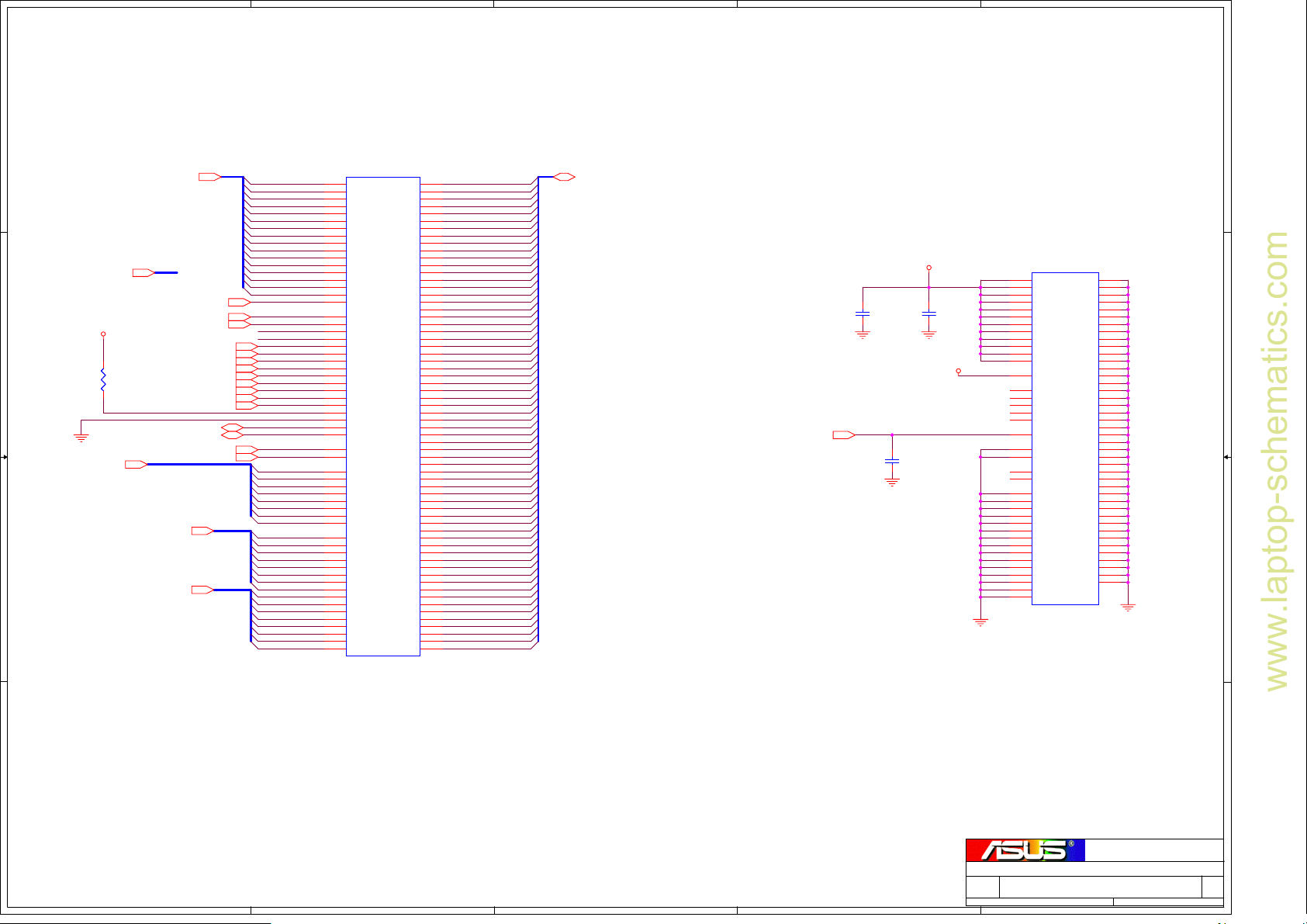

Decoupling between Processor and

DIMMs, Place close to Porcessor as

possible

c0805_h37

c0805_h37

+1.8V

+1.8V

12

12

10UF/6.3V

10UF/6.3V

+1.8V

12

0.1UF/16V

0.1UF/16V

C0601

C0601

1UF/6.3V

1UF/6.3V

C0605

C0605

C0609

C0609

c0805_h37

c0805_h37

GND

12

C0602

C0602

0.1UF/16V

0.1UF/16V

12

10UF/6.3V

10UF/6.3V

12

C0610

C0610

0.1UF/16V

0.1UF/16V

C0606

C0606

12

C0603

C0603

0.1UF/16V

0.1UF/16V

12

C0604

C0604

0.1UF/16V

0.1UF/16V

GND

c0805_h37

c0805_h37

12

C0608

C0608

10UF/6.3V

10UF/6.3V

GND

place close to socket

1

+CPU_VDD0

B B

A A

C0650

C0650

22UF/6.3V

22UF/6.3V

0103 add C0650

C0628

C0628

22UF/6.3V

22UF/6.3V

C0635

C0635

22UF/6.3V

22UF/6.3V

12

12

22UF/6.3V

22UF/6.3V

+CPU_VDD1

12

+CPU_VDDNB

12

C0643

C0643

22UF/6.3V

22UF/6.3V

/X

/X

C0629

C0629

22UF/6.3V

22UF/6.3V

Bottom side decoupling

12

12

C0630

C0630

22UF/6.3V

22UF/6.3V

C0636

C0636

5

12

C0681

C0681

0.1UF/16V

0.1UF/16V

GND

12

C0637

C0637

22UF/6.3V

22UF/6.3V

12

12

0.1UF/16V

0.1UF/16V

C0638

C0638

22UF/6.3V

22UF/6.3V

12

C0682

C0682

0.1UF/16V

0.1UF/16V

C0632

C0632

/X

/X

22UF/6.3V

22UF/6.3V

12

C0644

C0644

12

0.1UF/16V

0.1UF/16V

12

0.1UF/16V

0.1UF/16V

+1.8V

12

C0634

C0634

C634

C634

C0645

C0645

22UF/6.3V

22UF/6.3V

12

C0633

C0633

0.1UF/16V

0.1UF/16V

GND

12

C0640

C0640

0.1UF/16V

0.1UF/16V

12

12

0.1UF/16V

0.1UF/16V

GND

C0641

C0641

12

C0646

C0646

1UF/6.3V

1UF/6.3V

4

GND

12

C0647

C0647

1UF/6.3V

1UF/6.3V

12

C635

C635

0.1UF/16V

0.1UF/16V

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Wednesday, April 08, 2009

Wednesday, April 08, 2009

Wednesday, April 08, 2009

Date: Sheet

Date: Sheet

3

2

Date: Sheet

Engineer:

1

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

of

694

of

694

of

694

Rev

Rev

Rev

Griffin POWER

Griffin POWER

Griffin POWER

Title :

Title :

Title :

Engineer:

Engineer:

Page 7

5

www.laptop-schematics.com

4

3

2

1

D D

MEM_MA_ADD[0..15](4,9)

MEM_MA0_CS#[0..1](4,9)

MEM_MA_BANK2(4,9)

MEM_MA_BANK0(4,9)

MEM_MA_BANK1(4,9)

MEM_MA0_CLK1(4)

MEM_MA0_CLK#1(4)

MEM_MA0_CLK7(4)

MEM_MA0_CLK#7(4)

C C

MEM_MA_DM[0..7](4)

B B

MEM_MA_CKE0(4,9)

MEM_MA_CKE1(4,9)

MEM_MA_CAS#(4,9)

MEM_MA_RAS#(4,9)

MEM_MA_WE#(4,9)

SMBCLK_DRAM(8,21,29)

SMBDATA_DRAM(8,21,29)

MEM_MA0_ODT0(4,9)

MEM_MA0_ODT1(4,9)

MEM_MA_DQS[0..7](4)

MEM_MA_DQS#[0..7](4)

20080716 Change to 12G025C22004

J0701A

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA0_CS#0

MEM_MA0_CS#1

MEM_MA_DM0

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM1

MEM_MA_DM6

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM7

MEM_MA_DQS0

MEM_MA_DQS2

MEM_MA_DQS3

MEM_MA_DQS1

MEM_MA_DQS6

MEM_MA_DQS4

MEM_MA_DQS5

MEM_MA_DQS7

MEM_MA_DQS#0

MEM_MA_DQS#2

MEM_MA_DQS#3

MEM_MA_DQS#1

MEM_MA_DQS#6

MEM_MA_DQS#4

MEM_MA_DQS#5

MEM_MA_DQS#7

J0701A

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10/AP

90

A11

89

A12

116

A13

86

A14

84

A15

85

A16_BA2

107

BA0

106

BA1

110

S0#

115

S1#

30

CK0

32

CK0#

164

CK1

166

CK1#

79

CKE0

80

CKE1

113

CAS#

108

RAS#

109

WE#

198

SA0

200

SA1

197

SCL

195

SDA

114

ODT0

119

ODT1

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

11

DQS#0

29

DQS#1

49

DQS#2

68

DQS#3

129

DQS#4

146

DQS#5

167

DQS#6

186

DQS#7

DDR2_DIMM_200P

DDR2_DIMM_200P

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

MEM_MA_DATA1

5

MEM_MA_DATA0

7

MEM_MA_DATA7

17

MEM_MA_DATA6

19

MEM_MA_DATA4

4

MEM_MA_DATA5

6

MEM_MA_DATA3

14

MEM_MA_DATA2

16

MEM_MA_DATA22

23

MEM_MA_DATA21

25

MEM_MA_DATA18

35

MEM_MA_DATA19

37

MEM_MA_DATA20

20

MEM_MA_DATA17

22

MEM_MA_DATA16

36

MEM_MA_DATA23

38

MEM_MA_DATA25

43

MEM_MA_DATA29

45

MEM_MA_DATA30

55

MEM_MA_DATA27

57

MEM_MA_DATA24

44

MEM_MA_DATA28

46

MEM_MA_DATA31

56

MEM_MA_DATA26

58

MEM_MA_DATA14

61

MEM_MA_DATA15

63

MEM_MA_DATA9

73

MEM_MA_DATA8

75

MEM_MA_DATA11

62

MEM_MA_DATA10

64

MEM_MA_DATA12

74

MEM_MA_DATA13

76

123

125

135

137

124

126

134

136

MEM_MA_DATA36

141

MEM_MA_DATA39

143

MEM_MA_DATA33

151

MEM_MA_DATA38

153

MEM_MA_DATA32

140

MEM_MA_DATA37

142

MEM_MA_DATA34

152

MEM_MA_DATA35

154

MEM_MA_DATA44

157

MEM_MA_DATA40

159

MEM_MA_DATA42

173

MEM_MA_DATA43

175

MEM_MA_DATA41

158

MEM_MA_DATA45

160

MEM_MA_DATA47

174

MEM_MA_DATA46

176

MEM_MA_DATA56

179

MEM_MA_DATA57

181

MEM_MA_DATA63

189

MEM_MA_DATA62

191

MEM_MA_DATA60

180

MEM_MA_DATA61

182

MEM_MA_DATA59

192

MEM_MA_DATA58

194

MEM_MA_DATA54

MEM_MA_DATA51

MEM_MA_DATA53

MEM_MA_DATA48

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA52

MEM_MA_DATA55

MEM_MA_DATA[0..63] (4)

+1.8V

GND

1 2

1 2

R0701

R0701

1KOhm

1KOhm

1%

1%

R0702

R0702

1KOhm

1KOhm

1%

1%

M_VREF_DIMM(8)

12

C0713

C0713

0.1UF/16V

0.1UF/16V

12

c0805_h37 C0705

c0805_h37

C0705

10UF/6.3V

10UF/6.3V

+1.8V

12

M_VREF_DIMM

2A

C0711

C0711

0.1UF/10V

0.1UF/10V

+3VS

12

C712

/X C712

/X

0.1UF/10V

0.1UF/10V

J0701B

J0701B

112

VDD1

111

VDD2

117

VDD3

96

VDD4

95

VDD5

118

VDD6

81

VDD7

82

VDD8

87

VDD9

103

VDD10

88

VDD11

104

VDD12

199

VDDSPD

83

NC1

120

NC2

50

NC3

69

NC4

163

NCTEST

1

VREF

201

GND0

202

GND1

203

NP_NC1

204

NP_NC2

47

VSS1

133

VSS2

183

VSS3

77

VSS4

12

VSS5

48

VSS6

184

VSS7

78

VSS8

71

VSS9

72

VSS10

121

VSS11

122

VSS12

196

VSS13

193

VSS14

8

VSS15

DDR2_DIMM_200P

DDR2_DIMM_200P

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

18

24

41

53

42

54

59

65

60

66

127

139

128

145

165

171

172

177

187

178

190

9

21

33

155

34

132

144

156

168

2

3

15

27

39

149

161

28

40

138

150

162

High

A A

DDR2 SO-DIMM0

DDR2 SO-DIMM0

DDR2 SO-DIMM0

Title :

Title :

Title :

Engineer:

Engineer:

5

4

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Wednesday, April 08, 2009

Wednesday, April 08, 2009

3

2

Wednesday, April 08, 2009

Engineer:

1

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

of

794

of

794

of

794

Rev

Rev

Rev

Page 8

5

www.laptop-schematics.com

D D

MEM_MB_ADD[0..15](4,9)

MEM_MB0_CS#[0..1](4,9)

MEM_MB_BANK2(4,9)

MEM_MB_BANK0(4,9)

R0802

R0802

4.7KOhm

4.7KOhm

MEM_MB_DQS[0..7](4)

MEM_MB_DQS#[0..7](4)

MEM_MB_BANK1(4,9)

MEM_MB0_CLK1(4)

MEM_MB0_CLK#1(4)

MEM_MB0_CLK7(4)

MEM_MB0_CLK#7(4)

MEM_MB_CKE0(4,9)

MEM_MB_CKE1(4,9)

MEM_MB_CAS#(4,9)

MEM_MB_RAS#(4,9)

MEM_MB_WE#(4,9)

SMBCLK_DRAM(7,21,29)

SMBDATA_DRAM(7,21,29)

MEM_MB0_ODT0(4,9)

MEM_MB0_ODT1(4,9)

+3VS

C C

12

GND

MEM_MB_DM[0..7](4)

B B

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB0_CS#0

MEM_MB0_CS#1

MEM_MB_DM0

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM1

MEM_MB_DM6

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM7

MEM_MB_DQS0

MEM_MB_DQS2

MEM_MB_DQS3

MEM_MB_DQS1

MEM_MB_DQS6

MEM_MB_DQS4

MEM_MB_DQS5

MEM_MB_DQS7

MEM_MB_DQS#0

MEM_MB_DQS#2

MEM_MB_DQS#3

MEM_MB_DQS#1

MEM_MB_DQS#6

MEM_MB_DQS#4

MEM_MB_DQS#5

MEM_MB_DQS#7

J0802A

J0802A

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10/AP

90

A11

89

A12

116

A13

86

A14

84

A15

85

A16_BA2

107

BA0

106

BA1

110

S0#

115

S1#

30

CK0

32

CK0#

164

CK1

166

CK1#

79

CKE0

80

CKE1

113

CAS#

108

RAS#

109

WE#

198

SA0

200

SA1

197

SCL

195

SDA

114

ODT0

119

ODT1

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

11

DQS#0

29

DQS#1

49

DQS#2

68

DQS#3

129

DQS#4

146

DQS#5

167

DQS#6

186

DQS#7

DDR_DIMM_200P

DDR_DIMM_200P

4

MEM_MB_DATA6

5

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

MEM_MB_DATA1

7

MEM_MB_DATA3

17

MEM_MB_DATA2

19

MEM_MB_DATA0

4

MEM_MB_DATA5

6

MEM_MB_DATA7

14

MEM_MB_DATA4

16

23

25

35

37

20

22

36

38

MEM_MB_DATA29

43

MEM_MB_DATA25

45

MEM_MB_DATA30

55

MEM_MB_DATA31

57

MEM_MB_DATA24

44

MEM_MB_DATA28

46

MEM_MB_DATA27

56

MEM_MB_DATA26

58

MEM_MB_DATA14

61

MEM_MB_DATA15

63

MEM_MB_DATA9

73

MEM_MB_DATA8

75

MEM_MB_DATA11

62

MEM_MB_DATA10

64

MEM_MB_DATA13

74

MEM_MB_DATA12

76

123

125

135

137

124

126

134

136

141

143

151

153

140

142

152

154

MEM_MB_DATA46

157

MEM_MB_DATA40

159

MEM_MB_DATA42

173

MEM_MB_DATA43

175

MEM_MB_DATA45

158

MEM_MB_DATA44

160

MEM_MB_DATA41

174

MEM_MB_DATA47

176

179

181

189

191

180

182

192

194

MEM_MB_DATA20

MEM_MB_DATA17

MEM_MB_DATA22

MEM_MB_DATA16

MEM_MB_DATA21

MEM_MB_DATA23

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA53

MEM_MB_DATA48

MEM_MB_DATA52

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA59

MEM_MB_DATA58

3

MEM_MB_DATA[0..63] (4)

c0805_h37 C0805

c0805_h37

M_VREF_DIMM(7)

2

12

C0805

10UF/6.3V

10UF/6.3V

M_VREF_DIMM

12

C0808

C0808

0.1UF/10V

0.1UF/10V

/X

/X

+1.8V

12

C0811

C0811

0.1UF/10V

0.1UF/10V

+3VS

112

VDD1

111

VDD2

117

VDD3

96

VDD4

95

VDD5

118

VDD6

81

VDD7

82

VDD8

87

VDD9

103

VDD10

88

VDD11

104

VDD12

199

VDDSPD

83

NC1

120

NC2

50

NC3

69

NC4

163

NCTEST

1

VREF

201

GND0

202

GND1

203

NP_NC1

204

NP_NC2

47

VSS1

133

VSS2

183

VSS3

77

VSS4

12

VSS5

48

VSS6

184

VSS7

78

VSS8

71

VSS9

72

VSS10

121

VSS11

122

VSS12

196

VSS13

193

VSS14

8

VSS15

J0802B

J0802B

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

DDR_DIMM_200P

DDR_DIMM_200P

1

18

24

41

53

42

54

59

65

60

66

127

139

128

145

165

171

172

177

187

178

190

9

21

33

155

34

132

144

156

168

2

3

15

27

39

149

161

28

40

138

150

162

low

A A

DDR2 SO-DIMM1

DDR2 SO-DIMM1

DDR2 SO-DIMM1

Title :

Title :

Title :

Engineer:

Engineer:

5

4

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Wednesday, April 08, 2009

Wednesday, April 08, 2009

3

2

Wednesday, April 08, 2009

Engineer:

1

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

of

894

of

894

of

894

Rev

Rev

Rev

Page 9

5

4

+0.9V

3

2

1

0.3A

D D

C C

MEM_MA_CKE1(4,7)

MEM_MA_ADD11(4,7)

MEM_MA_BANK0(4,7)

MEM_MA_WE#(4,7)

MEM_MA0_CS#0(4,7)

MEM_MA_RAS#(4,7)

MEM_MA_BANK1(4,7)

MEM_MA_CAS#(4,7)

MEM_MA_ADD13(4,7)

MEM_MA0_ODT0(4,7)

MEM_MA0_CS#1(4,7)

MEM_MA0_ODT1(4,7)

MEM_MA_CKE0(4,7)

MEM_MA_BANK2(4,7)

MEM_MA_ADD12(4,7)

MEM_MA_ADD9(4,7)

MEM_MA_ADD8(4,7)

MEM_MA_ADD5(4,7)

MEM_MA_ADD3(4,7)

MEM_MA_ADD1(4,7)

MEM_MA_ADD4(4,7)

MEM_MA_ADD6(4,7)

MEM_MA_ADD7(4,7)

MEM_MA_ADD14(4,7)

MEM_MA_ADD15(4,7)

MEM_MA_ADD2(4,7)

MEM_MA_ADD0(4,7)

MEM_MA_ADD10(4,7)

MEM_MA_CKE1

MEM_MA_ADD11

MEM_MA_BANK0

MEM_MA_WE#

MEM_MA0_CS#0

MEM_MA_RAS#

MEM_MA_BANK1

MEM_MA_CAS#

MEM_MA_ADD13

MEM_MA0_ODT0

MEM_MA0_CS#1

MEM_MA0_ODT1

MEM_MA_CKE0

MEM_MA_BANK2

MEM_MA_ADD12

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD5

MEM_MA_ADD3

MEM_MA_ADD1

MEM_MA_ADD4

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_ADD2

MEM_MA_ADD0

MEM_MA_ADD10

20080803 Remove R907

47Ohm

47Ohm

47Ohm

47Ohm

47Ohm

47Ohm

RN0904F

RN0904F

611

RN0903B

RN0903B

215

RN0903H

RN0903H

89

C0916 0.1UF/16VC0916 0.1UF/16V

1 2

+0.9V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+0.9V

1

GND

0.3A

MEM_MB_ADD14(4,8)

MEM_MB_ADD1(4,8)

MEM_MB_ADD11(4,8)

MEM_MB_ADD7(4,8)

MEM_MB_ADD6(4,8)

MEM_MB_ADD4(4,8)

MEM_MB_ADD0(4,8)

MEM_MB_ADD2(4,8)

MEM_MB_ADD12(4,8)

MEM_MB_ADD9(4,8)

MEM_MB_ADD8(4,8)

MEM_MB_CKE1(4,8)

MEM_MB_ADD15(4,8)

MEM_MB_ADD5(4,8)

MEM_MB_ADD3(4,8)

MEM_MB_BANK2(4,8)

MEM_MB_RAS#(4,8)

B B

MEM_MB_BANK1(4,8)

MEM_MB_CAS#(4,8)

MEM_MB0_ODT1(4,8)

MEM_MB_WE#(4,8)

MEM_MB_BANK0(4,8)

MEM_MB_ADD10(4,8)

MEM_MB0_CS#1(4,8)

MEM_MB0_CS#0(4,8)

MEM_MB0_ODT0(4,8)

MEM_MB_ADD13(4,8)

MEM_MB_CKE0(4,8)

MEM_MB_ADD14

MEM_MB_ADD1

MEM_MB_ADD11

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD4

MEM_MB_ADD0

MEM_MB_ADD2

MEM_MB_ADD12

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_CKE1

MEM_MB_ADD15

MEM_MB_ADD5

MEM_MB_ADD3

MEM_MB_BANK2

MEM_MB_RAS#

MEM_MB_BANK1

MEM_MB_CAS#

MEM_MB0_ODT1

MEM_MB_WE#

MEM_MB_BANK0

MEM_MB_ADD10

MEM_MB0_CS#1

MEM_MB0_CS#0

MEM_MB0_ODT0

MEM_MB_ADD13

MEM_MB_CKE0

47Ohm

47Ohm

47Ohm

47Ohm

47Ohm

47Ohm

47Ohm

47Ohm

47Ohm

47Ohm

47Ohm

47Ohm

611

89

611

413

12

34

RN0905F

RN0905F

RN0906H

RN0906H

RN0906F

RN0906F

RN0907D

RN0907D

RN0908A

RN0908A

RN0908B

RN0908B

C0917 0.1UF/16VC0917 0.1UF/16V

1 2

C932 0.1UF/16VC932 0.1UF/16V

1 2

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+0.9V

12

C0924

C0924

0.1UF/16V

0.1UF/16V

GND

+1.8V

PLACE CLOSE TO SOCKET( PER EMI/EMC)

A A

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet

Wednesday, April 08, 2009

Wednesday, April 08, 2009

Wednesday, April 08, 2009

Date: Sheet

5

4

3

2

Date: Sheet

GND

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

DDR2_TERMINATIONS

DDR2_TERMINATIONS

DDR2_TERMINATIONS

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Rev

Rev

Rev

of

994

of

994

of

994

Page 10

5

www.laptop-schematics.com

D D

C C

4

3

2

1

B B

A A

Title :

Title :

Title :

MIC&LINEIN

MIC&LINEIN

5

4

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

Engineer:

1

MIC&LINEIN

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

38 94Wednesday, April 08, 2009

38 94Wednesday, April 08, 2009

38 94Wednesday, April 08, 2009

Rev

Rev

Rev

Page 11

www.laptop-schematics.com

Page 12

www.laptop-schematics.com

Page 13

www.laptop-schematics.com

Page 14

www.laptop-schematics.com

Page 15

www.laptop-schematics.com

Page 16

5

www.laptop-schematics.com

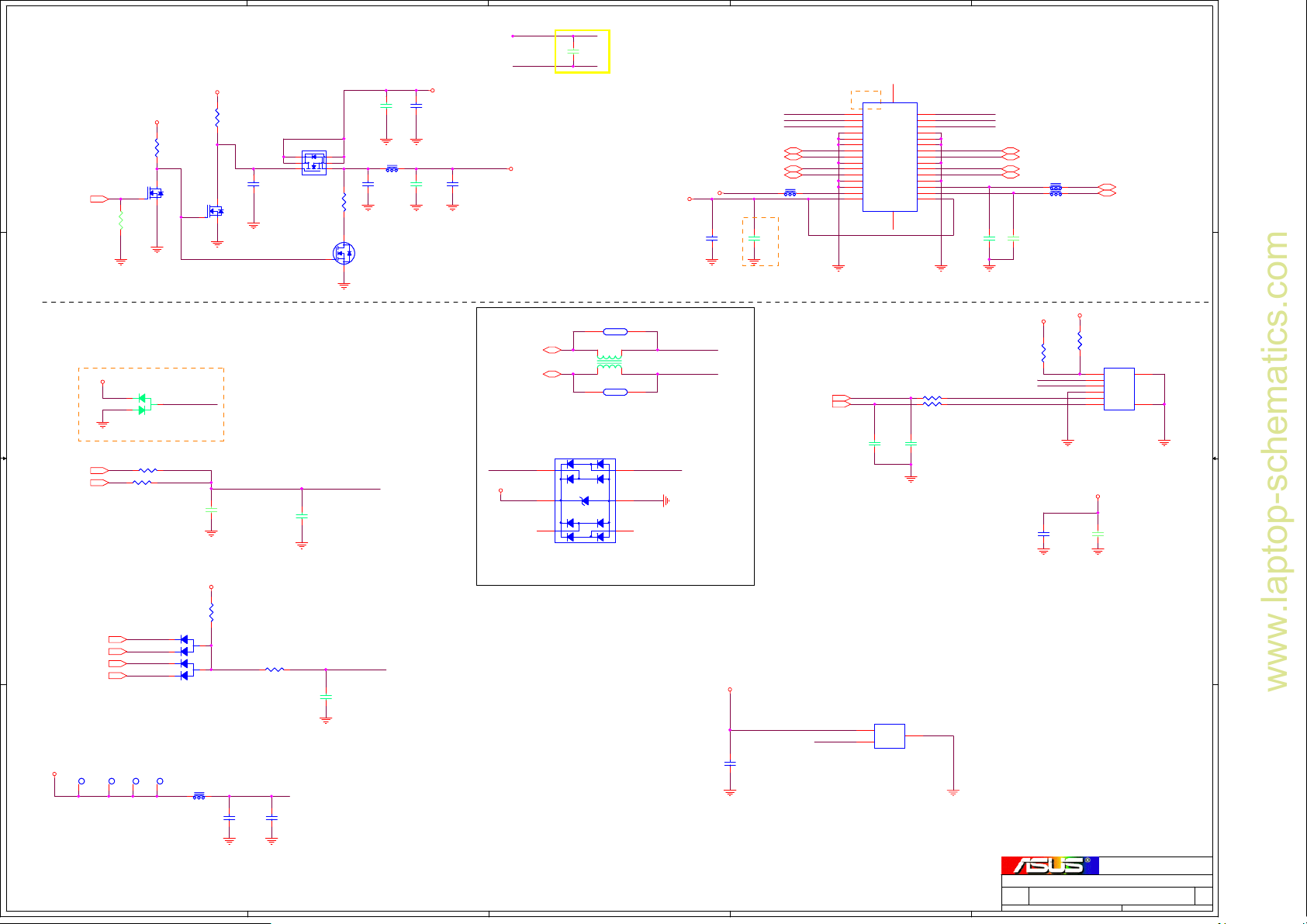

D D

LPC_FRAME#(20,30)

LPC_CLKDEBUG(20,24)

C C

4

J4401

J4401

1

2

3

4

5

6

7

8

9

10

11

12

FPC_CON_12P

FPC_CON_12P

/Debug/@

/Debug/@

1

3

5

7

9

11

C4403

C4403

10PF/50V

10PF/50V

@

@

2

4

6

8

10

12

LPC_AD0(20,30)

LPC_AD1(20,30)

LPC_AD2(20,30)

LPC_AD3(20,30)

1 2

GND

+3VS

GND

3

12

C4406

C4406

0.1UF/10V

0.1UF/10V

/Debug/@

/Debug/@

GND

2

1

If don't support NewCard Debug Card,Pls do

(a) DNI all components of block A

(b) Mount Block C (RN5401,R6975)

B B

For PCMCIA Debug Card

If support NewCard Debug Card,

Pls don't mount all components.

A A

DEBUG

DEBUG

5

4

Title :

Title :

Title :

Engineer:

Engineer:

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

ASUSTeK COMPUTER INC. NB1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet

Engineer:

1

DEBUG

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

of

44 94Wednesday, April 08, 2009