Page 1

5

4

3

2

1

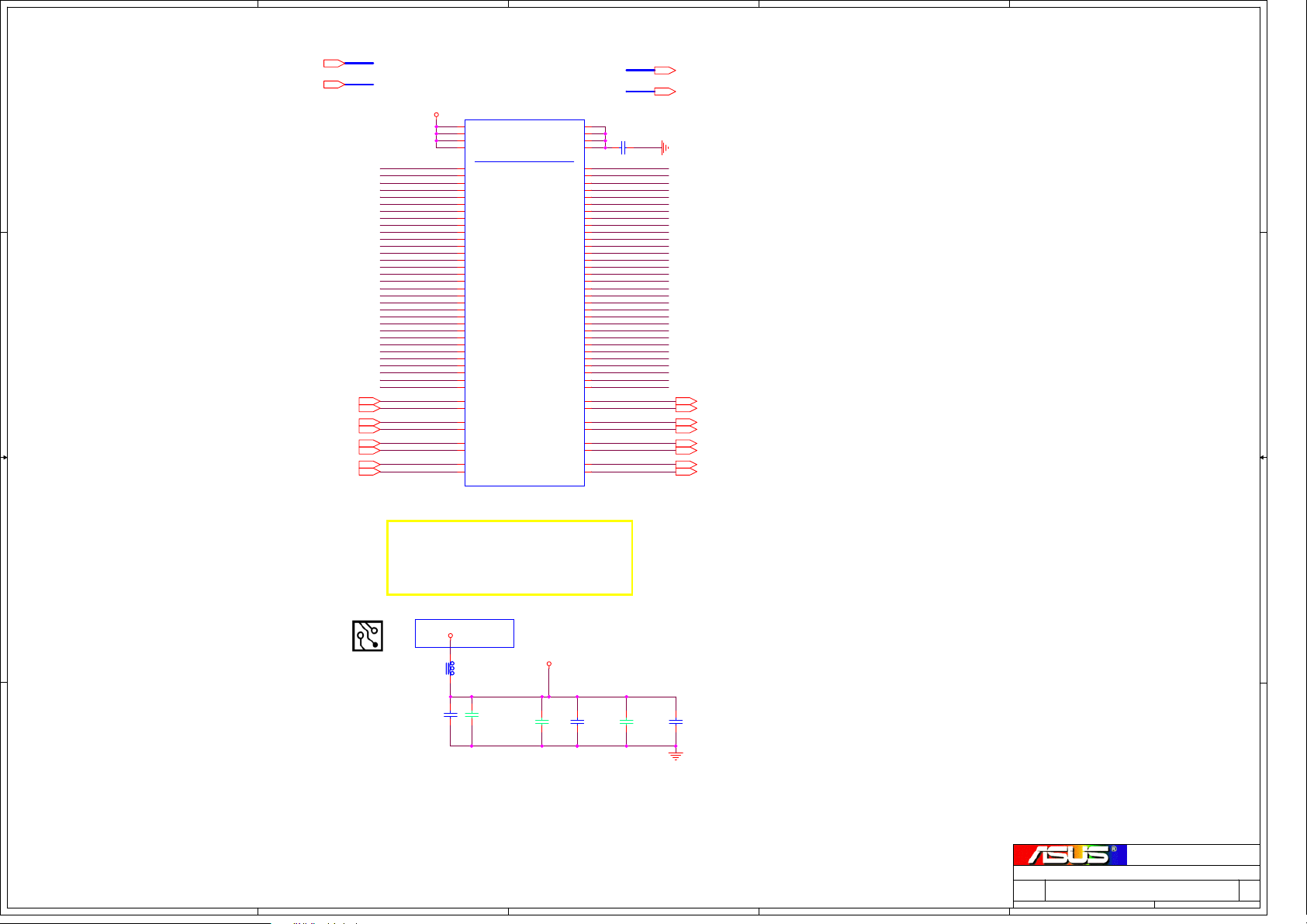

AMD CPU

BLOCK DIAGRAM

D D

Conesus

18W

Page 3 ~ 6

DDR2

667

HT LINK

800MHZ

LVDS

CRT

HDMI

C C

MINICARD

Page 53

Page 45

Page 46

Page 48

M92

PCI-E X16(8)

AMD

RS780MN

PCI-E

Page 10 ~ 18

PCIE

X4

LPC

RTL8111C

Page 33 ~ 34

AMD

SB710

NEWCARD

Page 43

SATA USB

SATA HDD

B B

Page 51

SATA ODD

Page 51

USB 2.0 X4

Page 52

USB CCD

Page 45

Page 20 ~ 28

AZALIA

Card Reader

AU6371

Dual Channel DDR2

SO-DIMM X 2

Page 7 ~ 9

EC ITE8512 SPI ROM

KB/TOUCH PAD

Debug Conn.

TPM 1.2

Codec ALC663

MDC Header

Page 40

LED

Page 30 ~ 31

Amp

FAN + SENSOR

FAN + SENSOR

Discharge

Page 30

Page 30

Page 44

Page 62

Page 36

Page 30

Page 35

Page 29

Page 50

Page 50

Page 30

HP/MIC/LINE IN

Page 30

4

BT Module

Page 61

4 in 1 Card

Reader

3

Page 40

Title :

Title :

Title :

Block Diagram

Block Diagram

Block Diagram

Ice_wang

Ice_wang

Engineer:

Engineer:

ASUSTeK Computer INC

ASUSTeK Computer INC

ASUSTeK Computer INC

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

F83T

F83T

F83T

Engineer:

Ice_wang

191Tuesday, May 26, 2009

191Tuesday, May 26, 2009

191Tuesday, May 26, 2009

1

Rev

Rev

Rev

1.0

1.0

1.0

of

of

of

A A

5

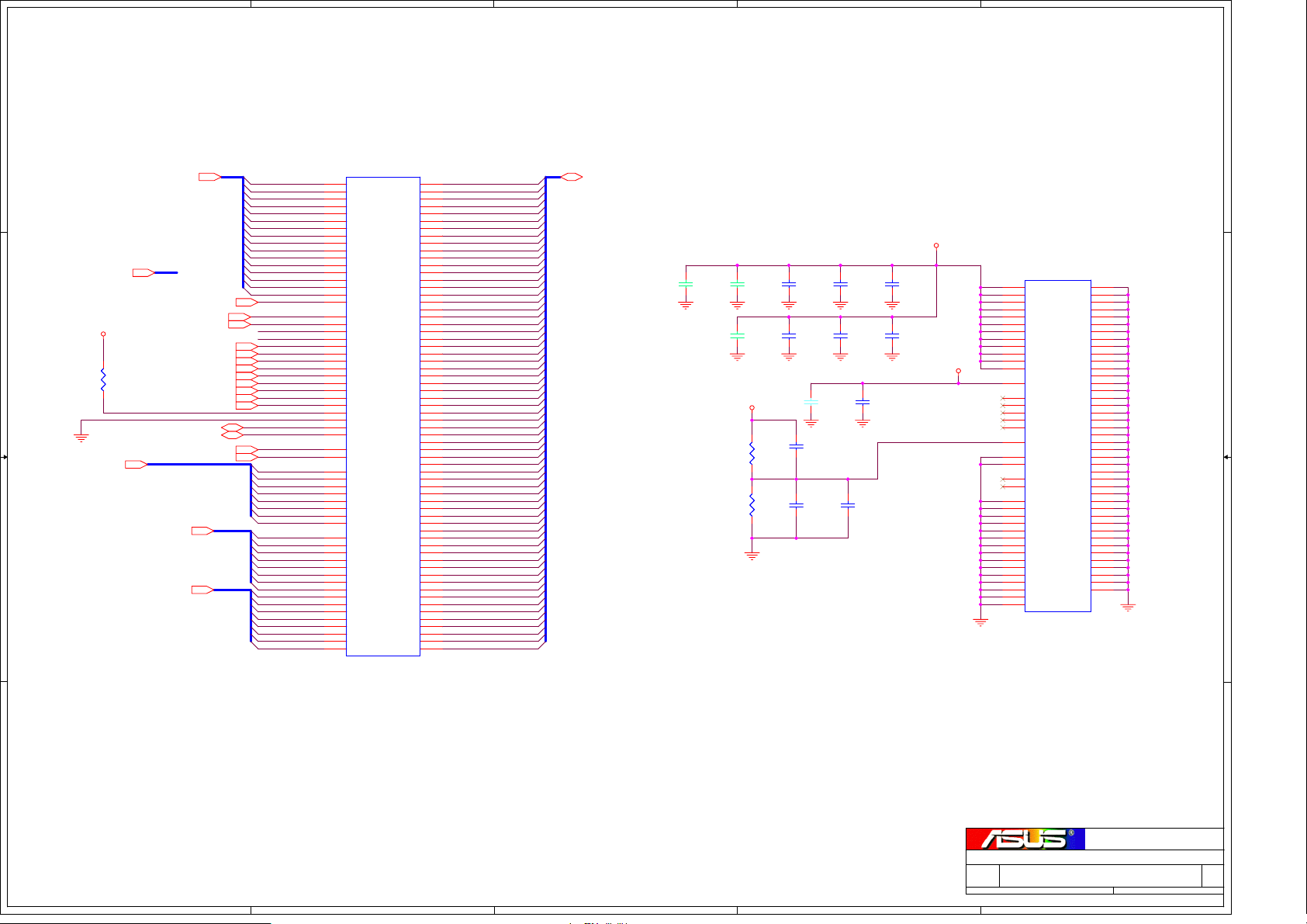

Page 2

5

4

3

2

1

Reset IC

AC mode: VSUS_ON assert after EC_RST#

BAT Mode: VSUS_ON assert after Press button

D D

1

AC_BAT_SYS

C C

SUS_PWRGD

+2.5_CPU_VDDA

B B

+1.1V_NB

+CPU_VDD0

+1.2VSUS

+0.9V

+1.8V

+3V

+5V

+12V

+1.5VS

+1.8VS

+3VS

+5VS

+12VS

+3VA

+5VA

+3VSUS

+3VA_EC

3

VSUS_ON

4

SUS_PWRGD

8'

SUSC_EC#

ALL_SYSTEM_PWRGD

10

SUSB_EC#

9'

11

CPU_VRON

EC

KBRST#

RC_IN#

EC_RST#

8

PM_SUSC#

9

PM_SUSB#

15

PWR_SW#

2

EC

5

SLP_S5#

SLP_S3#

KBRST#

7

PM_RSMRST#

(South Bridge)

PM_PWRBTN#

SB710

+CPU_VDD1

+VCC_NB

+1.2V_CPU_NB_SB

+CPU_VDDNB

VRM_PWRGD

12

PM_PWROK_EC

13

PWR_GOOD

NB_PWRGD

6

18

A_RST#

LDT_PG

LDT_RST#

Power On

SWITCH

17

19

16

18

14

CPU_PWRGD

CPU_LDT_RST#

CPU_LDT_STOP#

A_RST#

NB_PWRGD

PWROK

RESET_L

AMD Conesus CPU

LDTSTOP_L

LDTSTOP#LDT_STP#

RS780MN

SYSRESET#A_RST#

(North Bridge)

POWERGOOD

A A

5

10

+3VS POWER-UP

CLK GEN

VDDxxx

Title :

Title :

Title :

Power sequence

Power sequence

Power sequence

<OrgAddr1>

<OrgAddr1>

Engineer:

Engineer:

ASUSTeK.Computer.INC

ASUSTeK.Computer.INC

ASUSTeK.Computer.INC

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

F83T

F83T

F83T

Engineer:

1

<OrgAddr1>

291Tuesday, May 26, 2009

291Tuesday, May 26, 2009

291Tuesday, May 26, 2009

of

of

of

Rev

Rev

Rev

2.05

2.05

2.05

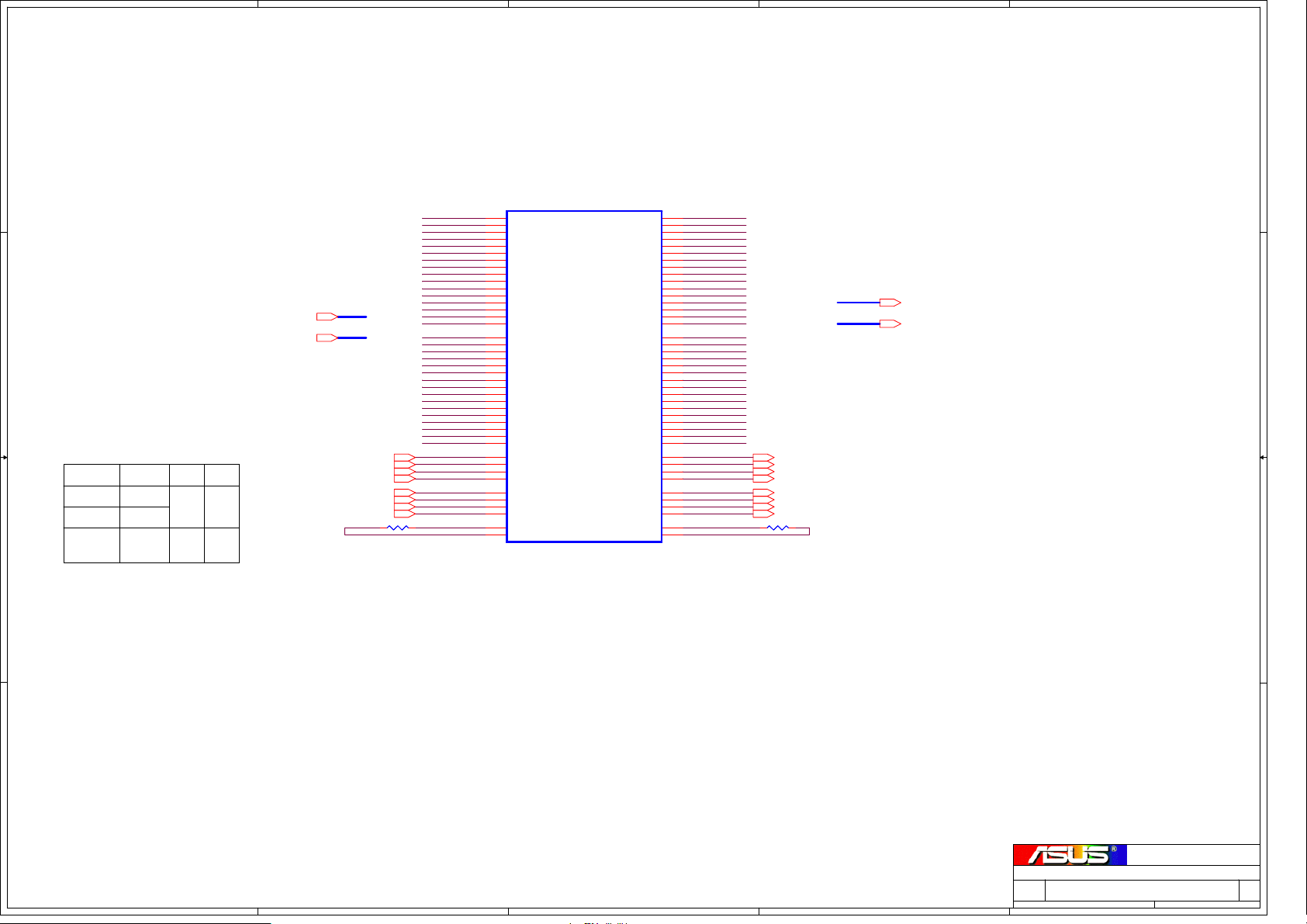

Page 3

5

4

3

2

1

HT_CPU_RXD[0..15][10]

HT_CPU_RXD#[0..15][10]

CPU_VLDT

U0301A

D D

HT_CPU_RXD15

HT_CPU_RXD#15

HT_CPU_RXD14

HT_CPU_RXD#14

HT_CPU_RXD13

HT_CPU_RXD#13

HT_CPU_RXD12

HT_CPU_RXD#12

HT_CPU_RXD11

HT_CPU_RXD#11

HT_CPU_RXD10

HT_CPU_RXD#10

HT_CPU_RXD9

HT_CPU_RXD#9

HT_CPU_RXD8

HT_CPU_RXD#8

HT_CPU_RXD7

HT_CPU_RXD#7

HT_CPU_RXD6

HT_CPU_RXD#6

HT_CPU_RXD5

HT_CPU_RXD#5

HT_CPU_RXD4

HT_CPU_RXD#4

HT_CPU_RXD3

C C

HT_CPU_RX_CLK1[10]

HT_CPU_RX_CLK#1[10]

HT_CPU_RX_CLK0[10]

HT_CPU_RX_CLK#0[10]

HT_CPU_RX_CTL1[10]

HT_CPU_RX_CTL#1[10]

HT_CPU_RX_CTL0[10]

HT_CPU_RX_CTL#0[10]

HT_CPU_RXD#3

HT_CPU_RXD2

HT_CPU_RXD#2

HT_CPU_RXD1

HT_CPU_RXD#1

HT_CPU_RXD0

HT_CPU_RXD#0

HT_CPU_RX_CLK1

HT_CPU_RX_CLK#1

HT_CPU_RX_CLK0

HT_CPU_RX_CLK#0

HT_CPU_RX_CTL1

HT_CPU_RX_CTL#1

HT_CPU_RX_CTL0

HT_CPU_RX_CTL#0

U0301A

AL4

VLDT_B1

AL3

VLDT_B2

AL2

VLDT_B3

AL1

VLDT_B4

Y6

L0_CADIN_H[15]

Y5

L0_CADIN_L[15]

W7

L0_CADIN_H[14]

W6

L0_CADIN_L[14]

U6

L0_CADIN_H[13]

U5

L0_CADIN_L[13]

R7

L0_CADIN_H[12]

R6

L0_CADIN_L[12]

M8

L0_CADIN_H[11]

M7

L0_CADIN_L[11]

L6

L0_CADIN_H[10]

L5

L0_CADIN_L[10]

J6

L0_CADIN_H[9]

J5

L0_CADIN_L[9]

H4

L0_CADIN_H[8]

H3

L0_CADIN_L[8]

T3

L0_CADIN_H[7]

T4

L0_CADIN_L[7]

T2

L0_CADIN_H[6]

T1

L0_CADIN_L[6]

P3

L0_CADIN_H[5]

P4

L0_CADIN_L[5]

P2

L0_CADIN_H[4]

P1

L0_CADIN_L[4]

M2

L0_CADIN_H[3]

M1

L0_CADIN_L[3]

K3

L0_CADIN_H[2]

K4

L0_CADIN_L[2]

K2

L0_CADIN_H[1]

K1

L0_CADIN_L[1]

H2

L0_CADIN_H[0]

H1

L0_CADIN_L[0]

P6

L0_CLKIN_H[1]

P5

L0_CLKIN_L[1]

M3

L0_CLKIN_H[0]

M4

L0_CLKIN_L[0]

P8

L0_CTLIN_H[1]

P9

L0_CTLIN_L[1]

V2

L0_CTLIN_H[0]

V1

L0_CTLIN_L[0]

AMGMV40OAX4DX

AMGMV40OAX4DX

VLDT_A1

VLDT_A2

VLDT_A3

VLDT_A4

L0_CADOUT_H[15]

L0_CADOUT_L[15]

L0_CADOUT_H[14]

L0_CADOUT_L[14]

L0_CADOUT_H[13]

L0_CADOUT_L[13]

L0_CADOUT_H[12]

L0_CADOUT_L[12]

L0_CADOUT_H[11]

L0_CADOUT_L[11]

L0_CADOUT_H[10]

L0_CADOUT_L[10]

L0_CADOUT_H[9]

L0_CADOUT_L[9]

L0_CADOUT_H[8]

L0_CADOUT_L[8]

L0_CADOUT_H[7]

L0_CADOUT_L[7]

L0_CADOUT_H[6]

L0_CADOUT_L[6]

L0_CADOUT_H[5]

L0_CADOUT_L[5]

L0_CADOUT_H[4]

L0_CADOUT_L[4]

L0_CADOUT_H[3]

L0_CADOUT_L[3]

L0_CADOUT_H[2]

L0_CADOUT_L[2]

L0_CADOUT_H[1]

L0_CADOUT_L[1]

L0_CADOUT_H[0]

L0_CADOUT_L[0]

L0_CLKOUT_H[1]

L0_CLKOUT_L[1]

L0_CLKOUT_H[0]

L0_CLKOUT_L[0]

L0_CTLOUT_H[1]

L0_CTLOUT_L[1]

L0_CTLOUT_H[0]

L0_CTLOUT_L[0]

F4

F3

F2

F1

1 2

HT_CPU_TXD15

Y9

HT_CPU_TXD#15

Y8

HT_CPU_TXD14

AB6

HT_CPU_TXD#14

AB5

HT_CPU_TXD13

AC7

HT_CPU_TXD#13

AC6

HT_CPU_TXD12

AE6

HT_CPU_TXD#12

AE5

HT_CPU_TXD11

AE9

HT_CPU_TXD#11

AE8

HT_CPU_TXD10

AH3

HT_CPU_TXD#10

AH4

HT_CPU_TXD9

AK3

HT_CPU_TXD#9

AK4

HT_CPU_TXD8

AK1

HT_CPU_TXD#8

AK2

HT_CPU_TXD7

Y1

HT_CPU_TXD#7

Y2

HT_CPU_TXD6

Y4

HT_CPU_TXD#6

Y3

HT_CPU_TXD5

AB1

HT_CPU_TXD#5

AB2

HT_CPU_TXD4

AB4

HT_CPU_TXD#4

AB3

HT_CPU_TXD3

AD4

HT_CPU_TXD#3

AD3

HT_CPU_TXD2

AF1

HT_CPU_TXD#2

AF2

HT_CPU_TXD1

AF4

HT_CPU_TXD#1

AF3

HT_CPU_TXD0

AH1

HT_CPU_TXD#0

AH2

HT_CPU_TX_CLK1

AF6

HT_CPU_TX_CLK#1

AF5

HT_CPU_TX_CLK0

AD1

HT_CPU_TX_CLK#0

AD2

HT_CPU_TX_CTL1

AB8

HT_CPU_TX_CTL#1

AB9

HT_CPU_TX_CTL0

V4

HT_CPU_TX_CTL#0

V3

C0302

C0302

HT_CPU_TXD[0..15] [10]

HT_CPU_TXD#[0..15] [10]

4.7uF/6.3V

4.7uF/6.3V

GND

HT_CPU_TX_CLK1 [10]

HT_CPU_TX_CLK#1 [10]

HT_CPU_TX_CLK0 [10]

HT_CPU_TX_CLK#0 [10]

HT_CPU_TX_CTL1 [10]

HT_CPU_TX_CTL#1 [10]

HT_CPU_TX_CTL0 [10]

HT_CPU_TX_CTL#0 [10]

DESIGN NOTE:

VLDT must be routed as a pour or a trace at least 200 mils wide.

VLDT may be routed from the source to either ALx balls or Fx balls.

Choose whichever makes routing simpler.

B B

A A

5

These six capacitors must be placed very near the selected balls.

The "other" set of balls must be decoupled with a 4.7uF cap.

4

+1.2V_CPU_NB_SB

C0303

C0303

4.7uF/6.3V

4.7uF/6.3V

21

L0301

L0301

30Ohm/100Mhz

30Ohm/100Mhz

Irat=1A

Irat=1A

12

Change L0301 to Irat=1A 090407

CPU_VLDT

12

C0304

C0304

4.7uF/6.3V

4.7uF/6.3V

C0305

C0305

0.22UF/6.3V

0.22UF/6.3V

12

@

@

MLCC 180PF/50V (0402) NPO 5%

MLCC 180PF/50V (0402) NPO 5%

12

C0306

C0306

0.22UF/6.3V

0.22UF/6.3V

12

@

@

C0307

C0307

180PF/50V

180PF/50V

3

12

C0308

C0308

180PF/50V

180PF/50V

MLCC 180PF/50V (0402) NPO 5%

MLCC 180PF/50V (0402) NPO 5%

GND

Title :

Title :

Title :

Conesus HT I/F

Conesus HT I/F

Conesus HT I/F

<OrgAddr1>

<OrgAddr1>

Engineer:

Engineer:

ASUSTeK.Computer.INC

ASUSTeK.Computer.INC

ASUSTeK.Computer.INC

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

F83T

F83T

F83T

Engineer:

1

<OrgAddr1>

391Friday, May 29, 2009

391Friday, May 29, 2009

391Friday, May 29, 2009

of

of

of

Rev

Rev

Rev

2.05

2.05

2.05

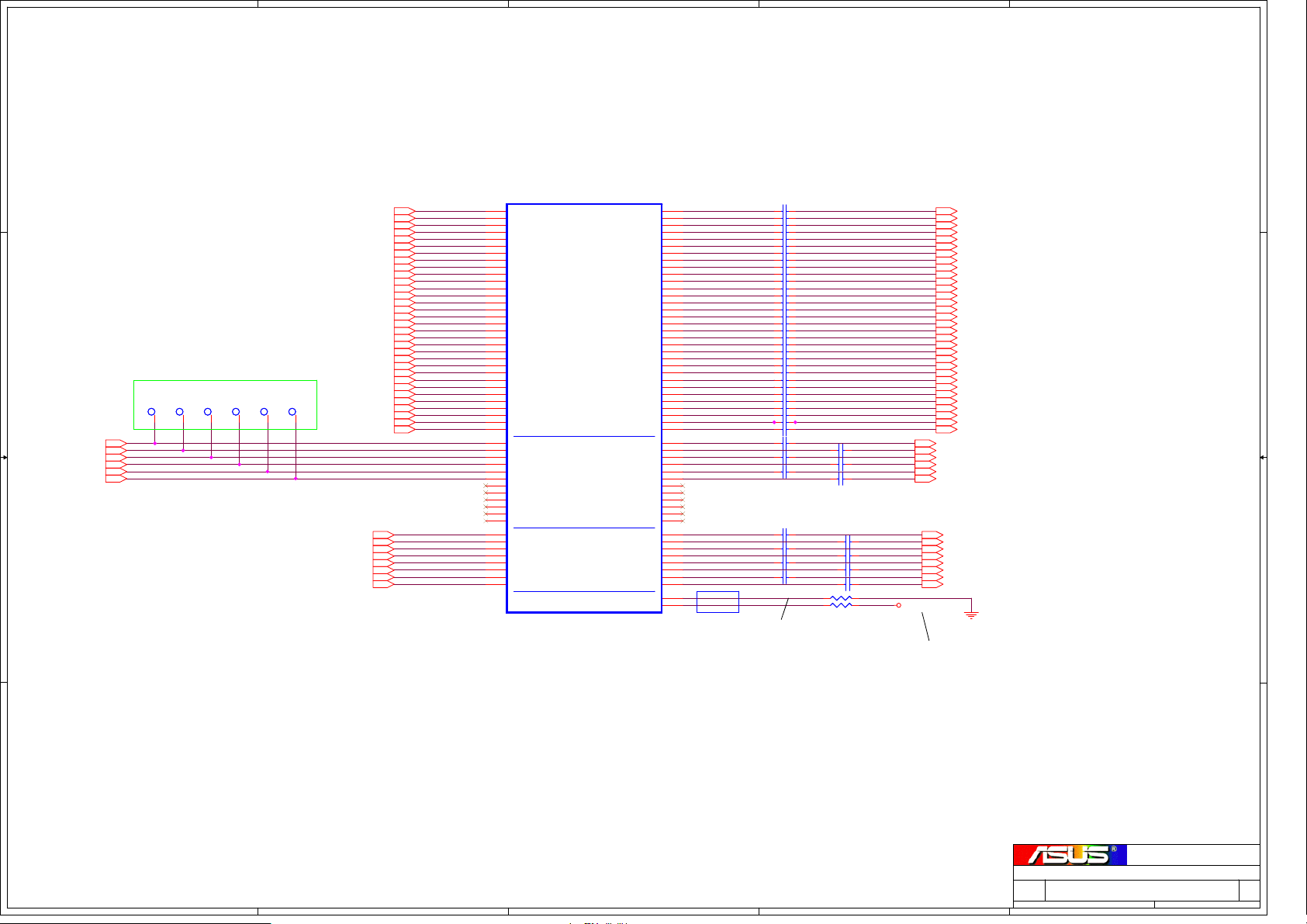

Page 4

5

4

3

2

1

MEM_MB_DATA[0..63][8]

U0301C

AN13

AL14

AL16

AN17

AN12

AM12

AM16

AN16

AL18

AN19

AM24

AN24

AM18

AN18

AL22

AN23

AM25

AL26

AN28

AL28

AL24

AN25

AN27

AM28

AM29

AL30

AL32

AL33

AK28

AN29

AM31

AM32

E33

D31

B31

A31

F33

F31

C32

B32

C30

A29

B26

A26

B30

A30

A27

C26

A24

B24

C18

A18

A25

C24

C20

A19

C16

A16

B14

A13

B18

A17

C14

A14

K33

K31

G32

F32

L33

K32

H31

G33

H33

AN15

AN20

AK26

AN31

C33

C28

A20

D14

J33

H32

AM14

AN14

AL20

AM20

AN26

AM26

AN30

AM30

D33

D32

B28

A28

A21

B20

B16

A15

AMGMV40OAX4DX

AMGMV40OAX4DX

U0301C

MB_DATA[63]

MB_DATA[62]

MB_DATA[61]

MB_DATA[60]

MB_DATA[59]

MB_DATA[58]

MB_DATA[57]

MB_DATA[56]

MB_DATA[55]

MB_DATA[54]

MB_DATA[53]

MB_DATA[52]

MB_DATA[51]

MB_DATA[50]

MB_DATA[49]

MB_DATA[48]

MB_DATA[47]

MB_DATA[46]

MB_DATA[45]

MB_DATA[44]

MB_DATA[43]

MB_DATA[42]

MB_DATA[41]

MB_DATA[40]

MB_DATA[39]

MB_DATA[38]

MB_DATA[37]

MB_DATA[36]

MB_DATA[35]

MB_DATA[34]

MB_DATA[33]

MB_DATA[32]

MB_DATA[31]

MB_DATA[30]

MB_DATA[29]

MB_DATA[28]

MB_DATA[27]

MB_DATA[26]

MB_DATA[25]

MB_DATA[24]

MB_DATA[23]

MB_DATA[22]

MB_DATA[21]

MB_DATA[20]

MB_DATA[19]

MB_DATA[18]

MB_DATA[17]

MB_DATA[16]

MB_DATA[15]

MB_DATA[14]

MB_DATA[13]

MB_DATA[12]

MB_DATA[11]

MB_DATA[10]

MB_DATA[9]

MB_DATA[8]

MB_DATA[7]

MB_DATA[6]

MB_DATA[5]

MB_DATA[4]

MB_DATA[3]

MB_DATA[2]

MB_DATA[1]

MB_DATA[0]

MB_CHECK[7]

MB_CHECK[6]

MB_CHECK[5]

MB_CHECK[4]

MB_CHECK[3]

MB_CHECK[2]

MB_CHECK[1]

MB_CHECK[0]

MB_DM[8]

MB_DM[7]

MB_DM[6]

MB_DM[5]

MB_DM[4]

MB_DM[3]

MB_DM[2]

MB_DM[1]

MB_DM[0]

MB_DQS_H[8]

MB_DQS_L[8]

MB_DQS_H[7]

MB_DQS_L[7]

MB_DQS_H[6]

MB_DQS_L[6]

MB_DQS_H[5]

MB_DQS_L[5]

MB_DQS_H[4]

MB_DQS_L[4]

MB_DQS_H[3]

MB_DQS_L[3]

MB_DQS_H[2]

MB_DQS_L[2]

MB_DQS_H[1]

MB_DQS_L[1]

MB_DQS_H[0]

MB_DQS_L[0]

MA_DATA[63]

MA_DATA[62]

MA_DATA[61]

MA_DATA[60]

MA_DATA[59]

MA_DATA[58]

MA_DATA[57]

MA_DATA[56]

MA_DATA[55]

MA_DATA[54]

MA_DATA[53]

MA_DATA[52]

MA_DATA[51]

MA_DATA[50]

MA_DATA[49]

MA_DATA[48]

MA_DATA[47]

MA_DATA[46]

MA_DATA[45]

MA_DATA[44]

MA_DATA[43]

MA_DATA[42]

MA_DATA[41]

MA_DATA[40]

MA_DATA[39]

MA_DATA[38]

MA_DATA[37]

MA_DATA[36]

MA_DATA[35]

MA_DATA[34]

MA_DATA[33]

MA_DATA[32]

MA_DATA[31]

MA_DATA[30]

MA_DATA[29]

MA_DATA[28]

MA_DATA[27]

MA_DATA[26]

MA_DATA[25]

MA_DATA[24]

MA_DATA[23]

MA_DATA[22]

MA_DATA[21]

MA_DATA[20]

MA_DATA[19]

MA_DATA[18]

MA_DATA[17]

MA_DATA[16]

MA_DATA[15]

MA_DATA[14]

MA_DATA[13]

MA_DATA[12]

MA_DATA[11]

MA_DATA[10]

MA_DATA[9]

MA_DATA[8]

MA_DATA[7]

MA_DATA[6]

MA_DATA[5]

MA_DATA[4]

MA_DATA[3]

MA_DATA[2]

MA_DATA[1]

MA_DATA[0]

MA_CHECK[7]

MA_CHECK[6]

MA_CHECK[5]

MA_CHECK[4]

MA_CHECK[3]

MA_CHECK[2]

MA_CHECK[1]

MA_CHECK[0]

MA_DQS_H[8]

MA_DQS_L[8]

MA_DQS_H[7]

MA_DQS_L[7]

MA_DQS_H[6]

MA_DQS_L[6]

MA_DQS_H[5]

MA_DQS_L[5]

MA_DQS_H[4]

MA_DQS_L[4]

MA_DQS_H[3]

MA_DQS_L[3]

MA_DQS_H[2]

MA_DQS_L[2]

MA_DQS_H[1]

MA_DQS_L[1]

MA_DQS_H[0]

MA_DQS_L[0]

+0.9V

D D

LAYOUT NOTE: Keep

trace to resistors less

than 1.5" from CPU pin.

C C

B B

+1.8V

MEM_MA_ADD[0..15][7,9]

R0403

R0403

1KOhm

1KOhm

R0404

R0404

1KOhm

1KOhm

T0409

T0409

TPC28T

TPC28T

R0440

R0440

39.2Ohm

39.2Ohm

1

1 2

1 2

GND

CPU_VTT_SUS_SENSE

R0441

R0441

39.2Ohm

39.2Ohm

MEM_MA0_CS#1[7,9]

MEM_MA0_CS#0[7,9]

MEM_MB0_CS#1[8,9]

MEM_MB0_CS#0[8,9]

MEM_MB_CKE1[8,9]

MEM_MB_CKE0[8,9]

MEM_MA_CKE1[7,9]

MEM_MA_CKE0[7,9]

MEM_MA_BANK2[7,9]

MEM_MA_BANK1[7,9]

MEM_MA_BANK0[7,9]

MEM_MA_RAS#[7,9]

MEM_MA_CAS#[7,9]

MEM_MA_WE#[7,9]

+1.8V

Mount R0405 , Un -Mount U0401 , C0401 ,

R0406, R0408, R0409 for cost down

change from 15ohm to 1Kohm

1 2

12

C0402

C0402

1 2

1000PF/16V

1000PF/16V

@

@

CPU_M_VREF

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

R0403 & R0404 change to 15ohm 1%

M_ZN

M_ZP

U0301B

U0301B

A12

VTT1

B12

VTT2

C12

VTT3

D12

VTT4

AK10

VTT5

AN10

VTT6

AL10

VTT7

AM10

VTT8

B11

VTT9

A11

M_VREF

B10

VTT_SENSE

AG9

M_ZN

AH9

M_ZP

AH29

RSVD1

AE29

RSVD2

AH30

MA0_CS_L[1]

AF29

MA0_CS_L[0]

AK33

RSVD3

AF33

RSVD4

AJ32

MB0_CS_L[1]

AF31

MB0_CS_L[0]

N33

MB_CKE[1]

P32

MB_CKE[0]

M30

MA_CKE[1]

M28

MA_CKE[0]

P30

MA_ADD[15]

M29

MA_ADD[14]

AG28

MA_ADD[13]

P28

MA_ADD[12]

T30

MA_ADD[11]

AC28

MA_ADD[10]

P27

MA_ADD[9]

R26

MA_ADD[8]

R27

MA_ADD[7]

U28

MA_ADD[6]

V30

MA_ADD[5]

U27

MA_ADD[4]

Y30

MA_ADD[3]

AB29

MA_ADD[2]

W29

MA_ADD[1]

AC26

MA_ADD[0]

R29

MA_BANK[2]

AC29

MA_BANK[1]

AE28

MA_BANK[0]

AC27

MA_RAS_L

AF30

MA_CAS_L

AE27

MA_WE_L

AMGMV40OAX4DX

AMGMV40OAX4DX

sensing point for

op-amp feedback

routed near CPU

MA0_CLK_H[2]

MA0_CLK_L[2]

MA0_CLK_H[1]

MA0_CLK_L[1]

MA0_CLK_H[0]

MA0_CLK_L[0]

MB0_CLK_H[2]

MB0_CLK_L[2]

MB0_CLK_H[1]

MB0_CLK_L[1]

MB0_CLK_H[0]

MB0_CLK_L[0]

12

C0403

C0403

0.1UF/16V

0.1UF/16V

GND

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

MB0_ODT[0]

RSVD18

MA0_ODT[0]

MB_ADD[15]

MB_ADD[14]

MB_ADD[13]

MB_ADD[12]

MB_ADD[11]

MB_ADD[10]

MB_ADD[9]

MB_ADD[8]

MB_ADD[7]

MB_ADD[6]

MB_ADD[5]

MB_ADD[4]

MB_ADD[3]

MB_ADD[2]

MB_ADD[1]

MB_ADD[0]

MB_BANK[2]

MB_BANK[1]

MB_BANK[0]

MB_RAS_L

MB_CAS_L

MB_WE_L

12

@

@

AH17

AG17

E20

E19

AB27

AB26

MEM_MA0_CLK2_P

AK18

MEM_MA0_CLK2_N

AJ17

MEM_MA0_CLK1_P

D18

MEM_MA0_CLK1_N

F19

Y28

Y27

AN21

AM21

A22

A23

AB33

AB32

MEM_MB0_CLK2_P

AN22

MEM_MB0_CLK2_N

AM22

MEM_MB0_CLK1_P

C22

MEM_MB0_CLK1_N

B22

AA32

AA33

AH31

AH33

AF27

AG29

MEM_MB_ADD15

P33

MEM_MB_ADD14

P31

MEM_MB_ADD13

AJ33

MEM_MB_ADD12

T32

MEM_MB_ADD11

T31

MEM_MB_ADD10

AD32

MEM_MB_ADD9

T33

MEM_MB_ADD8

V32

MEM_MB_ADD7

U33

MEM_MB_ADD6

V33

MEM_MB_ADD5

V31

MEM_MB_ADD4

W33

MEM_MB_ADD3

Y31

MEM_MB_ADD2

Y33

MEM_MB_ADD1

Y32

MEM_MB_ADD0

AC33

R33

AD33

AE33

AF32

AH32

AG33

CPU_M_VREF

C0404

C0404

1000PF/16V

1000PF/16V

PLACE CLOSE TO CPU

MEM_MA0_CLK2_P [7]

MEM_MA0_CLK2_N [7]

MEM_MA0_CLK1_P [7]

MEM_MA0_CLK1_N [7]

MEM_MB0_CLK2_P [8]

MEM_MB0_CLK2_N [8]

MEM_MB0_CLK1_P [8]

MEM_MB0_CLK1_N [8]

MEM_MB0_ODT1 [8,9]

MEM_MB0_ODT0 [8,9]

MEM_MA0_ODT1 [7,9]

MEM_MA0_ODT0 [7,9]

MEM_MB_BANK2 [8,9]

MEM_MB_BANK1 [8,9]

MEM_MB_BANK0 [8,9]

MEM_MB_RAS# [8,9]

MEM_MB_CAS# [8,9]

MEM_MB_WE# [8,9]

MEM_MB_ADD[0..15] [8,9]

congo

平臺省掉了一個

是否要預留另一組

place close to RROCESSOR within 1.5 inch

MEM_MA0_CLK1_P

12

C0410 1.5PF/50V MLCC/+/-0.1PFC0410 1.5PF/50V MLCC/+/-0.1PF

MEM_MA0_CLK1_N

MEM_MB0_CLK2_P

12

C0407 1.5PF/50V MLCC/+/-0.1PFC0407 1.5PF/50V MLCC/+/-0.1PF

MEM_MB0_CLK2_N

ODT

MEM_MA_DQS[0..7][7]

MEM_MA_DQS#[0..7][7]

MEM_MB_DQS[0..7][8]

MEM_MB_DQS#[0..7][8]

C0409 1.5PF/50V MLCC/+/-0.1PFC0409 1.5PF/50V MLCC/+/-0.1PF

C0408 1.5PF/50V MLCC/+/-0.1PFC0408 1.5PF/50V MLCC/+/-0.1PF

MEM_MA0_CLK2_P

12

MEM_MA0_CLK2_N

MEM_MB0_CLK1_P

12

MEM_MB0_CLK1_N

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

MEM_MB_DQS7

MEM_MB_DQS#7

MEM_MB_DQS6

MEM_MB_DQS#6

MEM_MB_DQS5

MEM_MB_DQS#5

MEM_MB_DQS4

MEM_MB_DQS#4

MEM_MB_DQS3

MEM_MB_DQS#3

MEM_MB_DQS2

MEM_MB_DQS#2

MEM_MB_DQS1

MEM_MB_DQS#1

MEM_MB_DQS0

MEM_MB_DQS#0

MA_DM[8]

MA_DM[7]

MA_DM[6]

MA_DM[5]

MA_DM[4]

MA_DM[3]

MA_DM[2]

MA_DM[1]

MA_DM[0]

MEM_MA_DATA63

AG11

MEM_MA_DATA62

AH11

MEM_MA_DATA61

AJ12

MEM_MA_DATA60

AJ14

MEM_MA_DATA59

AF11

MEM_MA_DATA58

AF12

MEM_MA_DATA57

AG12

MEM_MA_DATA56

AH12

AK14

AF15

AH19

AK20

AF14

AG14

AF17

AG19

MEM_MA_DATA47

AG20

MEM_MA_DATA46

AJ20

MEM_MA_DATA45

AF22

MEM_MA_DATA44

AK24

MEM_MA_DATA43

AF19

MEM_MA_DATA42

AF20

MEM_MA_DATA41

AJ23

MEM_MA_DATA40

AG23

AF23

AF25

AH27

AK30

AJ25

AG25

AJ26

AJ28

MEM_MA_DATA31

D28

MEM_MA_DATA30

G28

MEM_MA_DATA29

D26

MEM_MA_DATA28

E26

MEM_MA_DATA27

F30

MEM_MA_DATA26

E29

MEM_MA_DATA25

F27

MEM_MA_DATA24

H26

H25

D24

H22

E22

F26

G26

D22

G23

MEM_MA_DATA15

G22

MEM_MA_DATA14

G20

MEM_MA_DATA13

G15

MEM_MA_DATA12

F15

MEM_MA_DATA11

D20

MEM_MA_DATA10

F22

MEM_MA_DATA9

D16

MEM_MA_DATA8

E17

H15

H14

G12

H12

E15

E14

E11

F11

K30

J29

G29

F29

L28

L29

H29

H27

H30

MEM_MA_DM7

AL12

MEM_MA_DM6

AK16

MEM_MA_DM5

AK22

MEM_MA_DM4

AJ27

MEM_MA_DM3

E27

MEM_MA_DM2

E23

MEM_MA_DM1

H19

MEM_MA_DM0

G14

J27

J26

MEM_MA_DQS7

AJ11

MEM_MA_DQS#7

AK12

MEM_MA_DQS6

AG15

MEM_MA_DQS#6

AH15

MEM_MA_DQS5

AH22

MEM_MA_DQS#5

AG22

MEM_MA_DQS4

AG26

MEM_MA_DQS#4

AH26

MEM_MA_DQS3

E28

MEM_MA_DQS#3

F28

MEM_MA_DQS2

E25

MEM_MA_DQS#2

F25

MEM_MA_DQS1

G17

MEM_MA_DQS#1

H17

MEM_MA_DQS0

E12

MEM_MA_DQS#0

F12

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

MEM_MA_DATA[0..63] [7]

MEM_MA_DM[0..7] [7]MEM_MB_DM[0..7][8]

A A

Title :

Title :

Title :

Conesus DDR2 MEM I/F

Conesus DDR2 MEM I/F

Conesus DDR2 MEM I/F

<OrgAddr1>

<OrgAddr1>

Engineer:

Engineer:

F83T

F83T

F83T

Engineer:

1

ASUSTeK.Computer.INC

ASUSTeK.Computer.INC

ASUSTeK.Computer.INC

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

<OrgAddr1>

of

of

of

491Tuesday, May 26, 2009

491Tuesday, May 26, 2009

491Tuesday, May 26, 2009

Rev

Rev

Rev

2.05

2.05

2.05

Page 5

5

4

3

2

1

+1.8VS

12

R0501

R0501

300Ohm

D D

CPU_PWRGD[20]

CPU_LDT_STOP#[12,20]

CPU_LDT_RST#[20]

CPU_LDT_RST#

for warm reset

2

JP0501

JP0501

2

@

@

SGL_JUMP

SGL_JUMP

1

1

GND

C C

PROCHOT

EC to CPU/PWR

CPU_SIC[50]

CPU_SID[50]

CPU_PROCHOT#

PWRLIMIT#[30,89]

D0501 RB751V-40

D0501 RB751V-40

THRNTRIP

B B

CPU_THRMTRIP# FORCE_OFF#

+1.8V

@

@

E12

E12

Q0506

Q0506

PMBS3904

PMBS3904

@

@

A A

300Ohm

CPU_SIC

CPU_SID

SRC_CPU_HT_CLKP

R0599

R0599

071204

261OHM

261OHM

1 2

SRC_CPU_HT_CLKN

@

@

SRC_CPU_HT_CLKP[29]

SRC_CPU_HT_CLKN[29]

3

@

@

E12

E12

Q0505

Q0505

PMBS3904

PMBS3904

1 2

B

B

C

C

12

CPU_PWRGD

12

B

B

BUF_PLT_RST#[20,30,33,40,43,53,71]

R0515

R0515

10KOhm

10KOhm

3

3

D

D

S

S

GND

R0541

R0541

10KOhm

10KOhm

1 2

C0507 0.1UF/16VC0507 0.1UF/16V

C

C

3

3

T0514 TPC28TT0514 TPC28T

+3VS

1 2

@

@

3

2

2

CPU_RESETCPU_LDT_RST#

Debug 預留 090405

12

12

R0503

R0503

R0502

R0502

300Ohm

300Ohm

300Ohm

300Ohm

T0515 TPC28TT0515 TPC28T

C0501

C0501

12

3900PF/50V

3900PF/50V

MLCC/+/-10%

MLCC/+/-10%

3900PF/50V

3900PF/50V

MLCC/+/-10%

MLCC/+/-10%

Q0504

Q0504

2N7002

2N7002

1

1

G

G

R0512

R0512

169Ohm 1%

169Ohm 1%

C0502

C0502

12

SRC_CPU_HT_CLKP

SRC_CPU_HT_CLKN

THRO_CPU [30]

From EC.

1 2

NOTICE r0541

2N7002

2N7002

Q0507

Q0507

S

S

2

2

G

G

1

1

1

HDT

R0563

R0563

4.7KOhm

4.7KOhm

If PWROK,RESET_L,LDTSTOP_L are driven by open-drain driver,

a 300 ohm pull up to VDDIO.

CPU_PWRGD

LDT_STOP#

CPU_LDT_RST#

1

CPU_VLDT

GND

T510 TPC28TT510 TPC28T

T511 TPC28TT511 TPC28T

T512 TPC28TT512 TPC28T

T513 TPC28TT513 TPC28T

D

D

3

3

CPU_LDT_RST#

CPU_PWRGD

R0516 0Ohm

R0516 0Ohm

1 2

R0517 0Ohm

R0517 0Ohm

1 2

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

+1.8V

FORCE_OFF# [30,86,87]

GND

J0500

J0500

1

NC

3

DBREQ_L1

/x

/x

5

DBRDY1

/x

/x

7

DBREQ_L2

9

DBRDY2

11

DBREQ_L3

13

DBRDY3

15

DBREQ_L4

17

DBRDY4

19

DBREQ_L5

21

DBRDY5

23

DBREQ_L6

ASP_68200_07_K25

ASP_68200_07_K25

/X

/X

NOTICE

mount cap C0503 (AMD

power LDO

CPU_LDT_RST#

CPU_PWRGD

LDT_STOP#

CPU_SIC

CPU_SID

1%

1%

R0513 44.2Ohm

R0513 44.2Ohm

1 2

R0514 44.2Ohm

R0514 44.2Ohm

1 2

1%

CPU_THRM_DC[50]

CPU_THRM_DA[50]

1%

T0509 TPC28TT0509 TPC28T

T0510 TPC28TT0510 TPC28T

T0511 TPC28TT0511 TPC28T

T0512 TPC28TT0512 TPC28T

T0513 TPC28TT0513 TPC28T

DBREQ_L7

1

1

1

1

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

DBRDY7

DBRDY6

GND9

GND10

CPU_VDD_FB_H

CPU_VDD_FB_L

CPU_VDDIO_SUS_FB_H

CPU_VDDIO_SUS_FB_L

2

4

6

8

10

12

14

16

18

20

22

24

26

+2.5V_CPU_VDDA

100UF/6.3V

100UF/6.3V

部分輸出是否可以省掉一個

VDDA CPU_PROCHOT#

CPU_HTREF0

CPU_HTREF1

CPU_CLK_H_C

CPU_CLK_L_C

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPU_TEST25_H

CPU_TEST25_L

CPU_TEST19

CPU_TEST18

GND

CPU_TEST17

1

CPU_TEST16

1

CPU_TEST15

1

CPU_TEST14

1

CPU_TEST12

1

CPU_RESET

GND

C0503

C0503

要求)

12

@

@

A8

B8

AK6

AM2

AM6

AN4

AN5

V10

V9

E2

E1

AM9

AK9

A6

A7

AH8

AN8

AK8

AL8

AM8

A9

B9

A5

B6

AJ9

H8

J8

C8

D9

H7

AN3

C6

AH7

AL6

AM5

AJ5

AJ7

M31

L32

M33

M32

W27

W26

AJ29

P26

M26

AJ30

AMGMV40OAX4DX

AMGMV40OAX4DX

30Ohm/100Mhz

30Ohm/100Mhz

C0504

C0504

4.7UF/6.3V

4.7UF/6.3V

10uf cap

U0301D

U0301D

VDDA1

VDDA2

RESET_L

PWROK

LDTSTOP_L

SIC

SID

HTREF1

HTREF0

VDD_FB_H

VDD_FB_L

VDDIO_FB_H

VDDIO_FB_L

CLKIN_H

CLKIN_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

THERMDC

THERMDA

TEST3

TEST2

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

L0501

21

GND

Irat=1AL0501

Irat=1A

12

0.22UF/6.3V

0.22UF/6.3V

VDDA

12

C0505

C0505

THERMTRIP_L

PROCHOT_L

VID[5]

VID[4]

VID[3]

VID[2]

VID[1]

VID[0]

CPU_PRESENT_L

PSI_L

DBREQ_L

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

TDO

VSS

12

C0506

C0506

3300PF/50V

3300PF/50V

12

R0523

R0523

300Ohm

300Ohm

CPU_THRMTRIP#

AJ6

AN6

1 2

CPU_DBREQ#

CPU_TDO

GND

VID5 is optional

T0526T0526

1

R0561 80.6OHMR0561 80.6OHM

1 2

T0518T0518

1

T0519T0519

1

T0520T0520

1

T0523T0523

1

T0524T0524

1

T0525T0525

1

CPU_VID5

B2

CPU_VID4

C2

CPU_VID3

C1

CPU_VID2

D2

CPU_VID1

D1

CPU_VID0

D3

R0559 1KOhmR0559 1KOhm

AM3

PSI_L

E4

PSI_L is a Power Status Indicator signal.

AN9

AN7

CPU_TEST29_H_FBCLKOUT_P

E9

CPU_TEST29_L_FBCLKOUT_N

D10

CPU_TEST24

AH6

CPU_TEST23

AG8

CPU_TEST22

AN11

CPU_TEST21

F9

CPU_TEST20

AM7

CPU_TEST28_H

G11

CPU_TEST28_L

H11

AJ8

CPU_TEST26

AM4

D7

B5

L27

B25

G6

A10

B7

E8

G5

G7

AB31

AB30

AK31

AD31

AD30

AK32

+1.8V

+1.8V

12

R0524

R0524

300Ohm

300Ohm

12

R0525

R0525

300Ohm

300Ohm

1

1

1

1

T0531T0531

1

CPU_PROCHOT# [20]

T0527T0527

T0528T0528

CPU_VID3 [81]

CPU_VID2 [81]

T0529T0529

T0530T0530

CPU_DBREQ#

3 4

CPU_SIC

5 6

CPU_TEST25_H

R0562 510OhmR0562 510Ohm

CPU_TEST26

7 8

Change 300 ohm to 4R8P 090405

CPU_TEST24

CPU_TEST22

CPU_TEST20

CPU_TEST21

CPU_TEST25_L

CPU_TEST19

CPU_TEST18

R0506 1KOhmR0506 1KOhm

1 2

1 2

300OHM

300OHM

1 2

300OHM

300OHM

3 4

300OHM

300OHM

5 6

300OHM

300OHM

7 8

300OHM

300OHM

R0560 510OhmR0560 510Ohm

1 2

300OHM

300OHM

300OHM

300OHM

1 2

300OHM

300OHM

R0528B

R0528B

R0528C

R0528C

R0528D

R0528D

R0528A

R0528A

R0530A

R0530A

R0530B

R0530B

R0530C

R0530C

R0530D

R0530D

+1.8V

GND

GND

GND

GND

GND

GND

Title :

Title :

Title :

Conesus CNT/DBG/THERM

Conesus CNT/DBG/THERM

Conesus CNT/DBG/THERM

<OrgAddr1>

<OrgAddr1>

Engineer:

Engineer:

F83

F83

F83

Engineer:

1

ASUSTeK.Computer.INC

ASUSTeK.Computer.INC

ASUSTeK.Computer.INC

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

<OrgAddr1>

of

of

of

591Tuesday, May 26, 2009

591Tuesday, May 26, 2009

591Tuesday, May 26, 2009

Rev

Rev

Rev

2.05

2.05

2.05

Page 6

5

+VCORE +VCORE +1.8V

U0301E

U0301E

A3

VDD1

A4

VDD2

B3

VDD3

B4

VDD4

C3

VDD5

D D

C C

C4

VDD6

D4

VDD7

D5

VDD8

D6

VDD9

E5

VDD10

E6

VDD11

E7

VDD12

F5

VDD13

F6

VDD14

F7

VDD15

F8

VDD16

G8

VDD17

G9

VDD18

H9

VDD19

J9

VDD20

J10

VDD21

J12

VDD22

J14

VDD23

J18

VDD24

J20

VDD25

J21

VDD26

J23

VDD27

K10

VDD28

K12

VDD29

K14

VDD30

K18

VDD31

K20

VDD32

K21

VDD33

K23

VDD34

K25

VDD35

L7

VDD36

L9

VDD37

L11

VDD38

L13

VDD39

M5

VDD40

M10

VDD41

M12

VDD42

M25

VDD43

N9

VDD44

N11

VDD45

N24

VDD46

N25

VDD47

P15

VDD48

P18

VDD49

P20

VDD50

P24

VDD51

P25

VDD52

AMGMV40OAX4DX

AMGMV40OAX4DX

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

VDD77

VDD78

VDD79

VDD80

VDD81

VDD82

VDD83

VDD84

VDD85

VDD86

VDD87

VDD88

VDD89

VDD90

VDD91

VDD92

VDD93

VDD94

VDD95

AA10

AA12

AA24

AA25

AB11

AB13

AC5

AC10

AC12

AC24

AC25

AD9

AD11

AD12

AD14

AD18

AD21

AD25

AE12

AE14

AE18

AE21

AE23

V25

V24

Y19

Y16

Y14

W20

W18

W15

W5

V19

V16

V14

T20

T18

T15

T10

R19

R16

R14

R5

4

AG32

AG30

AE30

AE26

AC32

AC30

AE32

AB28

AA30

W32

W30

W28

AF28

Y29

U29

R28

P29

U30

N30

U32

R32

R30

N32

U26

Y26

M27

U0301F

U0301F

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

AMGMV40OAX4DX

AMGMV40OAX4DX

3

U0301G

U0301G

A32

VSS1

AA1

VSS2

AA2

VSS3

AA4

VSS4

AA9

VSS5

AA11

VSS6

AA22

VSS7

AA23

VSS8

AB10

VSS9

AB12

VSS10

AB21

VSS11

AB22

VSS12

AB23

VSS13

AB24

VSS14

AB25

VSS15

AC11

VSS16

AC1

VSS17

AC2

VSS18

AC4

VSS19

AC8

VSS20

AC9

VSS21

AC13

VSS22

AC21

VSS23

AC22

VSS24

AC23

VSS25

AD10

VSS26

AD13

VSS27

AD16

VSS28

AD20

VSS29

AD22

VSS30

AD23

VSS31

AD24

VSS32

AE1

VSS33

AE2

VSS34

AE4

VSS35

AE7

VSS36

AE10

VSS37

AE11

VSS38

AE13

VSS39

AE16

VSS40

AE20

VSS41

AE22

VSS42

AE24

VSS43

AE25

VSS44

AF7

VSS45

AF8

VSS46

AF9

VSS47

AF26

VSS48

AG1

VSS49

AG2

VSS50

AG4

VSS51

AG6

VSS52

AG7

VSS53

AG27

VSS54

AH5

VSS55

AH14

VSS56

AH20

VSS57

AH23

VSS58

AH25

VSS59

AH28

VSS60

AMGMV40OAX4DX

AMGMV40OAX4DX

GND GND

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

G4

G2

G1

F23

F20

F14

E32

E30

D30

D29

D27

D25

D23

D21

D19

D17

D15

D13

D11

D8

C31

B33

B29

B27

B21

B19

B17

B15

B13

C10

AN32

AN2

AM33

AM27

AM23

AM19

AM17

AM15

AM13

AM11

AM1

AL31

AK29

AK27

AK25

AK23

AK21

AK19

AK17

AK15

AK13

AK11

AK7

AK5

AJ22

AJ19

AJ15

AJ4

AJ2

AJ1

2

U0301H

U0301H

G19

VSS121

G25

VSS122

G27

VSS123

G30

VSS124

H5

VSS125

H6

VSS126

H20

VSS127

H23

VSS128

H28

VSS129

J1

VSS130

J2

VSS131

J4

VSS132

J7

VSS133

J11

VSS134

J13

VSS135

J16

VSS136

J22

VSS137

J24

VSS138

J25

VSS139

J28

VSS140

J30

VSS141

J32

VSS142

K11

VSS143

K13

VSS144

K16

VSS145

A2

VSS146

K22

VSS147

K24

VSS148

K9

VSS149

L1

VSS150

L2

VSS151

L4

VSS152

L8

VSS153

L10

VSS154

L12

VSS155

L21

VSS156

L22

VSS157

L23

VSS158

L24

VSS159

L25

VSS160

L26

VSS161

L30

VSS162

M6

VSS163

M9

VSS164

M11

VSS165

M13

VSS166

M21

VSS167

M22

VSS168

M23

VSS169

M24

VSS170

N1

VSS171

N2

VSS172

N4

VSS173

N10

VSS174

N12

VSS175

N22

VSS176

N23

VSS177

P7

VSS178

P10

VSS179

P14

VSS180

P16

VSS181

P19

VSS182

AMGMV40OAX4DX

AMGMV40OAX4DX

GND

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

R1

R2

R4

R8

R15

R18

R20

T9

T14

T16

T19

T24

T25

V15

V18

V20

U1

U2

U4

U7

U8

W1

W2

W4

W8

W14

W16

W19

Y7

Y10

Y15

Y18

Y20

Y24

Y25

F17

AB7

AG5

B23

B1

GND

1

Remove C0602, C0603, C0604 090406

C0601

C0601

22UF/6.3V

22UF/6.3V

C0610

C0610

0.22UF/6.3V

0.22UF/6.3V

C0614

C0614

22UF/6.3V

22UF/6.3V

+VCORE

+VCORE

+1.8V

@

@

12

Bottom side decoupling

12

12

C0611

0.22UF/6.3V

0.22UF/6.3V

12

22UF/6.3V

22UF/6.3V

C0611

C0615

C0615

C0612

C0612

0.01UF/16V

0.01UF/16V

12

5

12

180PF/50V

180PF/50V

C0617

C0617

4.7uF/6.3V

4.7uF/6.3V

C0613

C0613

C0605

C0605

22UF/6.3V

22UF/6.3V

1 2

12

C0607

C0607

22UF/6.3V

22UF/6.3V

180pF

12

GND

12

C0608

C0608

22UF/6.3V

22UF/6.3V

的電容最好用

C0620

C0620

0.22UF/6.3V

0.22UF/6.3V

12

0.01UF/16V

0.01UF/16V

12

C0606

C0606

22UF/6.3V

22UF/6.3V

12

GND

C0619

C0619

0.22UF/6.3V

0.22UF/6.3V

12

22UF/6.3V

22UF/6.3V

C0621

C0621

4

C0609

C0609

12

GND

NPO的(AMD

12

12

C0622

C0622

180PF/50V

180PF/50V

C0623

C0623

180PF/50V

180PF/50V

建議)

12

@

@

3

B B

A A

LAYOUT NOTE: Decoupling between CPU and DIMMs,

Place close to CPU as possible

NOTICE 1,8v cap placement

C0625

C0625

4.7uF/6.3V

4.7uF/6.3V

C0629

C0629

4.7uF/6.3V

4.7uF/6.3V

C0637

C0637

4.7uF/6.3V

4.7uF/6.3V

+0.9V

+0.9V

+1.8V

12

12

4.7uF/6.3V

4.7uF/6.3V

12

4.7uF/6.3V

4.7uF/6.3V

C0630

C0630

C0638

C0638

C0626

C0626

4.7uF/6.3V

4.7uF/6.3V

12

@

@

12

@

@

12

C0631

C0631

0.22UF/6.3V

0.22UF/6.3V

C0639

C0639

0.22UF/6.3V

0.22UF/6.3V

C0627

C0627

0.22UF/6.3V

0.22UF/6.3V

12

12

12

C0628

C0628

0.22UF/6.3V

0.22UF/6.3V

2

090410

12

GND

C0633

C0633

1000PF/16V

1000PF/16V

C0641

C0641

1000PF/16V

1000PF/16V

12

12

12

C0636

C0636

180PF/50V

180PF/50V

GND

12

C0643

C0643

180PF/50V

180PF/50V

GND

ASUSTeK.Computer.INC

ASUSTeK.Computer.INC

ASUSTeK.Computer.INC

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

F83

F83

F83

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

Conesus Power

Conesus Power

Conesus Power

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

of

of

of

691Tuesday, May 26, 2009

691Tuesday, May 26, 2009

691Tuesday, May 26, 2009

Rev

Rev

Rev

2.05

2.05

2.05

Page 7

5

4

3

2

1

D D

J0701A

MEM_MA_ADD[0..15][4,9]

MEM_MA0_CS#[0..1][4,9]

MEM_MA_BANK2[4,9]

MEM_MA_BANK0[4,9]

MEM_MA_BANK1[4,9]

MEM_MA0_CLK1_P[4]

MEM_MA0_CLK1_N[4]

MEM_MA0_CLK2_P[4]

MEM_MA0_CLK2_N[4]

C C

B B

MEM_MA_CKE0[4,9]

MEM_MA_CKE1[4,9]

MEM_MA_CAS#[4,9]

MEM_MA_RAS#[4,9]

MEM_MA_WE#[4,9]

SMBCLK_DRAM[8,21,29,44]

SMBDATA_DRAM[8,21,29,44]

MEM_MA0_ODT0[4,9]

MEM_MA0_ODT1[4,9]

MEM_MA_DM[0..7][4]

MEM_MA_DQS[0..7][4]

MEM_MA_DQS#[0..7][4]

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA0_CS#0

MEM_MA0_CS#1

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_DQS0

MEM_MA_DQS1

MEM_MA_DQS2

MEM_MA_DQS3

MEM_MA_DQS4

MEM_MA_DQS5

MEM_MA_DQS6

MEM_MA_DQS7

MEM_MA_DQS#0

MEM_MA_DQS#1

MEM_MA_DQS#2

MEM_MA_DQS#3

MEM_MA_DQS#4

MEM_MA_DQS#5

MEM_MA_DQS#6

MEM_MA_DQS#7

J0701A

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10/AP

90

A11

89

A12

116

A13

86

A14

84

A15

85

A16_BA2

107

BA0

106

BA1

110

S0#

115

S1#

30

CK0

32

CK0#

164

CK1

166

CK1#

79

CKE0

80

CKE1

113

CAS#

108

RAS#

109

WE#

198

SA0

200

SA1

197

SCL

195

SDA

114

ODT0

119

ODT1

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

11

DQS#0

29

DQS#1

49

DQS#2

68

DQS#3

129

DQS#4

146

DQS#5

167

DQS#6

186

DQS#7

DDR_DIMM_200P

DDR_DIMM_200P

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

MEM_MA_DATA1

5

MEM_MA_DATA0

7

MEM_MA_DATA2

17

MEM_MA_DATA3

19

MEM_MA_DATA4

4

MEM_MA_DATA5

6

MEM_MA_DATA6

14

MEM_MA_DATA7

16

MEM_MA_DATA8

23

MEM_MA_DATA9

25

MEM_MA_DATA11

35

MEM_MA_DATA14

37

MEM_MA_DATA12

20

MEM_MA_DATA13

22

MEM_MA_DATA15

36

MEM_MA_DATA10

38

MEM_MA_DATA20

43

MEM_MA_DATA22

45

MEM_MA_DATA18

55

MEM_MA_DATA19

57

MEM_MA_DATA17

44

MEM_MA_DATA21

46

MEM_MA_DATA16

56

MEM_MA_DATA23

58

61

63

73

75

62

64

74

76

MEM_MA_DATA39

123

MEM_MA_DATA34

125

MEM_MA_DATA32

135

MEM_MA_DATA37

137

MEM_MA_DATA38

124

MEM_MA_DATA35

126

MEM_MA_DATA33

134

MEM_MA_DATA36

136

141

143

151

153

140

142

152

154

MEM_MA_DATA53

157

MEM_MA_DATA49

159

MEM_MA_DATA51

173

MEM_MA_DATA55

175

MEM_MA_DATA52

158

MEM_MA_DATA48

160

MEM_MA_DATA54

174

MEM_MA_DATA50

176

179

181

189

191

180

182

192

194

MEM_MA_DATA25

MEM_MA_DATA29

MEM_MA_DATA27

MEM_MA_DATA30

MEM_MA_DATA28

MEM_MA_DATA26

MEM_MA_DATA24

MEM_MA_DATA31

MEM_MA_DATA42

MEM_MA_DATA40

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA41

MEM_MA_DATA45

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA60

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA61

MEM_MA_DATA59

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA[0..63] [4]

12

+

+

CE0701

CE0701

470UF/2.5V

470UF/2.5V

@

@

+1.8V

C0701

C0701

2.2UF/10V

2.2UF/10V

12

@

@

12

@

@

C0702

C0702

2.2UF/10V

2.2UF/10V

C0706

C0706

0.1UF/16V

0.1UF/16V

+1.8V

R0701

R0701

1KOhm

1KOhm

1%

1%

1 2

R0702

R0702

1KOhm

1KOhm

1%

1%

1 2

GND

12

12

@

@

C0703

C0703

2.2UF/10V

2.2UF/10V

C0711

C0711

0.1UF/16V

0.1UF/16V

12

C0710

C0710

0.1UF/16V

0.1UF/16V

12

C0713

C0713

0.1UF/16V

0.1UF/16V

12

12

12

C0712

C0712

2.2UF/6.3V@

2.2UF/6.3V@

@

@

C0704

C0704

2.2UF/10V

2.2UF/10V

C0707

C0707

0.1UF/16V

0.1UF/16V

12

C0714

C0714

1000PF/16V

1000PF/16V

12

12

12

C0709

C0709

0.1UF/16V

0.1UF/16V

M_VREF_DIMM0

C0705

C0705

2.2UF/10V

2.2UF/10V

C0708

C0708

0.1UF/16V

0.1UF/16V

+3VS

112

VDD1

111

VDD2

117

VDD3

96

VDD4

95

VDD5

118

VDD6

81

VDD7

82

VDD8

87

VDD9

103

VDD10

88

VDD11

104

VDD12

199

VDDSPD

83

NC1

120

NC2

50

NC3

69

NC4

163

NCTEST

1

VREF

201

GND0

202

GND1

203

NP_NC1

204

NP_NC2

47

VSS1

133

VSS2

183

VSS3

77

VSS4

12

VSS5

48

VSS6

184

VSS7

78

VSS8

71

VSS9

72

VSS10

121

VSS11

122

VSS12

196

VSS13

193

VSS14

8

VSS15

J0701B

J0701B

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

DDR_DIMM_200P

DDR_DIMM_200P

12G025122006

18

24

41

53

42

54

59

65

60

66

127

139

128

145

165

171

172

177

187

178

190

9

21

33

155

34

132

144

156

168

2

3

15

27

39

149

161

28

40

138

150

162

12

@

@

P/N:12G025122006

A A

<Variant Name>

<Variant Name>

<Variant Name>

Title :

Title :

Title :

DDR2 SO-DIMM0

DDR2 SO-DIMM0

1

DDR2 SO-DIMM0

791Tuesday, May 26, 2009

791Tuesday, May 26, 2009

791Tuesday, May 26, 2009

of

of

of

Rev

Rev

Rev

2.05

2.05

2.05

Engineer:

Engineer:

ASUSTeK COMPUTER INC

ASUSTeK COMPUTER INC

ASUSTeK COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

F5Z

F5Z

F5Z

Engineer:

Page 8

5

D D

MEM_MB_ADD[0..15][4,9]

MEM_MB0_CS#[0..1][4,9]

MEM_MB_BANK2[4,9]

MEM_MB_BANK0[4,9]

R0802

R0802

4.7KOhm

4.7KOhm

MEM_MB_DQS[0..7][4]

MEM_MB_DQS#[0..7][4]

MEM_MB_BANK1[4,9]

MEM_MB0_CLK1_P[4]

MEM_MB0_CLK1_N[4]

MEM_MB0_CLK2_P[4]

MEM_MB0_CLK2_N[4]

MEM_MB_CKE0[4,9]

MEM_MB_CKE1[4,9]

MEM_MB_CAS#[4,9]

MEM_MB_RAS#[4,9]

MEM_MB_WE#[4,9]

SMBCLK_DRAM[7,21,29,44]

SMBDATA_DRAM[7,21,29,44]

MEM_MB0_ODT0[4,9]

MEM_MB0_ODT1[4,9]

+3VS

C C

12

GND

MEM_MB_DM[0..7][4]

B B

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB0_CS#0

MEM_MB0_CS#1

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

MEM_MB_DQS0

MEM_MB_DQS1

MEM_MB_DQS2

MEM_MB_DQS3

MEM_MB_DQS4

MEM_MB_DQS5

MEM_MB_DQS6

MEM_MB_DQS7

MEM_MB_DQS#0

MEM_MB_DQS#1

MEM_MB_DQS#2

MEM_MB_DQS#3

MEM_MB_DQS#4

MEM_MB_DQS#5

MEM_MB_DQS#6

MEM_MB_DQS#7

CON0801A

CON0801A

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10/AP

90

A11

89

A12

116

A13

86

A14

84

A15

85

A16_BA2

107

BA0

106

BA1

110

S0#

115

S1#

30

CK0

32

CK0#

164

CK1

166

CK1#

79

CKE0

80

CKE1

113

CAS#

108

RAS#

109

WE#

198

SA0

200

SA1

197

SCL

195

SDA

114

ODT0

119

ODT1

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

11

DQS#0

29

DQS#1

49

DQS#2

68

DQS#3

129

DQS#4

146

DQS#5

167

DQS#6

186

DQS#7

DDR2_DIMM_200P

DDR2_DIMM_200P

4

MEM_MB_DATA0

5

DQ0

MEM_MB_DATA1

7

DQ1

MEM_MB_DATA2

17

DQ2

MEM_MB_DATA3

19

DQ3

MEM_MB_DATA5

4

DQ4

MEM_MB_DATA6

6

DQ5

MEM_MB_DATA4

14

DQ6

MEM_MB_DATA7

16

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

23

25

35

37

20

22

36

38

MEM_MB_DATA20

43

MEM_MB_DATA17

45

MEM_MB_DATA22

55

MEM_MB_DATA23

57

MEM_MB_DATA21

44

MEM_MB_DATA16

46

MEM_MB_DATA18

56

MEM_MB_DATA19

58

61

63

73

75

62

64

74

76

MEM_MB_DATA35

123

MEM_MB_DATA38

125

MEM_MB_DATA32

135

MEM_MB_DATA34

137

MEM_MB_DATA36

124

MEM_MB_DATA37

126

MEM_MB_DATA33

134

MEM_MB_DATA39

136

141

143

151

153

140

142

152

154

MEM_MB_DATA53

157

MEM_MB_DATA52

159

MEM_MB_DATA54

173

MEM_MB_DATA50

175

MEM_MB_DATA48

158

MEM_MB_DATA49

160

MEM_MB_DATA55

174

MEM_MB_DATA51

176

179

181

189

191

180

182

192

194

MEM_MB_DATA9

MEM_MB_DATA12

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA13

MEM_MB_DATA8

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA29

MEM_MB_DATA24

MEM_MB_DATA30

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA25

MEM_MB_DATA31

MEM_MB_DATA26

MEM_MB_DATA46

MEM_MB_DATA41

MEM_MB_DATA45

MEM_MB_DATA47

MEM_MB_DATA44

MEM_MB_DATA40

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA62

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA63

MEM_MB_DATA59

3

MEM_MB_DATA[0..63] [4]

2

+1.8V

12

@

@

C0801

C0801

2.2UF/10V

2.2UF/10V

12

@

@

12

@

@

C0802

C0802

2.2UF/10V

2.2UF/10V

C0810

C0810

0.1UF/16V

0.1UF/16V

+1.8V

1 2

1 2

GND

R0801

R0801

1KOhm

1KOhm

1%

1%

R0803

R0803

1KOhm

1KOhm

1%

1%

12

12

@

@

C0803

C0803

2.2UF/10V

2.2UF/10V

C0811

C0811

0.1UF/16V

0.1UF/16V

12

C0807

@ C0807

@

2.2UF/10V

2.2UF/10V

12

C0809

C0809

0.1UF/16V

0.1UF/16V

12

C0813

C0813

0.1UF/16V

0.1UF/16V

12

12

@

@

C0804

C0804

2.2UF/10V

2.2UF/10V

C0806

C0806

0.1UF/16V

0.1UF/16V

12

@

@

12

C0814

C0814

1000PF/16V

1000PF/16V

C0808

C0808

0.1UF/16V

0.1UF/16V

12

C0805

C0805

2.2UF/10V

2.2UF/10V

12

C0812

C0812

0.1UF/16V

0.1UF/16V

M_VREF_DIMM1

+3VS

CON0801B

CON0801B

112

VDD1

111

VDD2

117

VDD3

96

VDD4

95

VDD5

118

VDD6

81

VDD7

82

VDD8

87

VDD9

103

VDD10

88

VDD11

104

VDD12

199

VDDSPD

83

NC1

120

NC2

50

NC3

69

NC4

163

NCTEST

1

VREF

201

GND0

202

GND1

203

NP_NC1

204

NP_NC2

47

VSS1

133

VSS2

183

VSS3

77

VSS4

12

VSS5

48

VSS6

184

VSS7

78

VSS8

71

VSS9

72

VSS10

121

VSS11

122

VSS12

196

VSS13

193

VSS14

8

VSS15

DDR2_DIMM_200P

DDR2_DIMM_200P

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

1

18

24

41

53

42

54

59

65

60

66

127

139

128

145

165

171

172

177

187

178

190

9

21

33

155

34

132

144

156

168

2

3

15

27

39

149

161

28

40

138

150

162

PN:12G025C22003

REV.

A A

Title :

Title :

Title :

DDR2 SO-DIMM1

DDR2 SO-DIMM1

1

DDR2 SO-DIMM1

891Tuesday, May 26, 2009

891Tuesday, May 26, 2009

891Tuesday, May 26, 2009

of

of

of

Rev

Rev

Rev

2.05

2.05

2.05

Engineer:

Engineer:

ASUSTeK COMPUTER INC

ASUSTeK COMPUTER INC

ASUSTeK COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

5

4

3

2

F83T

F83T

F83T

Engineer:

Page 9

5

4

3

2

1

RN0912F47OHM RN0912F47OHM

RN0912A47OHM RN0912A47OHM

RN0912E47OHM RN0912E47OHM

RN0912B47OHM RN0912B47OHM

RN0910E47OHM RN0910E47OHM

RN0910G47OHM RN0910G47OHM

RN0910A47OHM RN0910A47OHM

RN0910B47OHM RN0910B47OHM

RN0910D47OHM RN0910D47OHM

RN0910C47OHM RN0910C47OHM

RN0914E47OHM RN0914E47OHM

RN0910H47OHM RN0910H47OHM

RN0912G47OHM RN0912G47OHM

RN0912H47OHM RN0912H47OHM

RN0912C47OHM RN0912C47OHM

RN0912D47OHM RN0912D47OHM

RN0914H47OHM RN0914H47OHM

RN0914G47OHM RN0914G47OHM

RN0914A47OHM RN0914A47OHM

RN0914D47OHM RN0914D47OHM

RN0914C47OHM RN0914C47OHM

RN0914F47OHM RN0914F47OHM

RN0910F47OHM RN0910F47OHM

RN0914B47OHM RN0914B47OHM

RN0916D

RN0916D

RN0916B

RN0916B

RN0916C

RN0916C

RN0916A

RN0916A

MB0_ODT1

+0.9V

C0901 0.1UF/16VC0901 0.1UF/16V

1 2

C0902 0.1UF/16VC0902 0.1UF/16V

1 2

C0903 0.1UF/16VC0903 0.1UF/16V

1 2

C0912 0.1UF/16VC0912 0.1UF/16V

1 2

C0913 0.1UF/16VC0913 0.1UF/16V

1 2

C0914 0.1UF/16VC0914 0.1UF/16V

1 2

C0915 0.1UF/16VC0915 0.1UF/16V

1 2

C0916 0.1UF/16VC0916 0.1UF/16V

1 2

+0.9V

C0917 0.1UF/16VC0917 0.1UF/16V

1 2

C0918 0.1UF/16VC0918 0.1UF/16V

1 2

C0919 0.1UF/16VC0919 0.1UF/16V

1 2

C0927 0.1UF/16VC0927 0.1UF/16V

1 2

C0929 0.1UF/16VC0929 0.1UF/16V

1 2

C0930 0.1UF/16VC0930 0.1UF/16V

1 2

C0931 0.1UF/16VC0931 0.1UF/16V

1 2

C0932 0.1UF/16VC0932 0.1UF/16V

1 2

+1.8V

+1.8V

+1.8V

12

+1.8V

@

@

+0.9V

12

0.1UF/16V

0.1UF/16V

0.1UF/16V

0.1UF/16V

C0904

C0904

C0905

C0905

Remove1.8V C0926,C0928 0.1uF 090405

12

0.1UF/16V

0.1UF/16V

0.1UF/16V

0.1UF/16V

12

C0920

C0920

0.1UF/16V

0.1UF/16V

C0933

C0933

C0921

C0921

12

@

@

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

是否用排容?

090330

+0.9V

PLACE CLOSE TO SOCKET( PER EMI/EMC)

3

2

Remove1.8V C0910,C0911 0.1uF 090405

12

12

0.1UF/16V

0.1UF/16V

0.1UF/16V

0.1UF/16V

C0907

C0907

C0906

C0906

12

12

0.1UF/16V

0.1UF/16V

0.1UF/16V

0.1UF/16V

C0922

C0922

C0923

C0923

12

12

0.1UF/16V

0.1UF/16V

C0934

C0934

0.1UF/16V

0.1UF/16V

C0935

C0935

@

@

@

@

12

12

0.1UF/16V

0.1UF/16V

C0908

C0908

12

0.1UF/16V

0.1UF/16V

C0924

C0924

0.1UF/16V

0.1UF/16V

C0936

C0936

ASUSTeK COMPUTER INC

ASUSTeK COMPUTER INC

ASUSTeK COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

0.1UF/16V

0.1UF/16V

12

@

@

C0909

C0909

0.1UF/16V

0.1UF/16V

C0937

C0937

12

F5Z

F5Z

F5Z

12

0.1UF/16V

0.1UF/16V

C0925

C0925

12

@

@

GND

0.1UF/16V

0.1UF/16V

C0938

C0938

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

GND

GND

DDR2_TERMINATIONS

DDR2_TERMINATIONS

DDR2_TERMINATIONS

991Tuesday, May 26, 2009

991Tuesday, May 26, 2009

991Tuesday, May 26, 2009

Rev

Rev

Rev

2.05

2.05

2.05

of

of

of

change to 8R16P 090405

MEM_MA_ADD[0..15][4,7]

D D

071219

Del Bank2 to Bus

071207

MEM_MA_BANK2[4,7]

MEM_MA_BANK1[4,7]

C C

MEM_MA_BANK0[4,7]

MEM_MA0_ODT0[4,7]

MEM_MA0_ODT1[4,7]

MEM_MA_CKE0[4,7]

MEM_MA_CKE1[4,7]

MEM_MA_RAS#[4,7]

MEM_MA_CAS#[4,7]

MEM_MA_WE#[4,7]

MEM_MA0_CS#0[4,7]

MEM_MA0_CS#1[4,7]

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA0_ODT0

MEM_MA0_ODT1

MEM_MA_CKE0

MEM_MA_CKE1

MEM_MA_RAS#

MEM_MA_CAS#

MEM_MA_WE#

MEM_MA0_CS#0

MEM_MA0_CS#1

MEM_MA_ADD1

MEM_MA_ADD3

MEM_MA_ADD5

MEM_MA_ADD8

MEM_MA0_CS#1

MEM_MA_CAS#

MEM_MA_WE#

MEM_MA_ADD9

MEM_MA_ADD12

MEM_MA_BANK2

MEM_MA_CKE0

MEM_MA_ADD7

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_CKE1

MEM_MA_RAS#

MEM_MA_BANK1

MEM_MA_ADD4

MEM_MA0_ODT0

MEM_MA_ADD13

MEM_MA0_CS#0

MEM_MA_ADD2

MEM_MA_ADD6

MEM_MA_ADD0

MEM_MA_ADD11

MEM_MA0_ODT1

MEM_MA_BANK0

MEM_MA_ADD10

3 14

2 15

1 16

8 9

7 10

8 9

5 12

3 14

4 13

5 12

2 15

4 13

7 10

6 11

1 16

6 11

4 13

8 9

3 14

1 16

2 15

6 11

7 10

5 12

5 6

47Ohm

47Ohm

7 8

47Ohm

47Ohm

1 2

47Ohm

47Ohm

3 4

47Ohm

47Ohm

add MA0_ODT1睿MB0_ODT1

090417

RN0901C47OHM RN0901C47OHM

RN0901B47OHM RN0901B47OHM

RN0901A47OHM RN0901A47OHM

RN0903H47OHM RN0903H47OHM

RN0901G47OHM RN0901G47OHM

RN0901H47OHM RN0901H47OHM

RN0901E47OHM RN0901E47OHM

RN0903C47OHM RN0903C47OHM

RN0903D47OHM RN0903D47OHM

RN0903E47OHM RN0903E47OHM

RN0903B47OHM RN0903B47OHM

RN0901D47OHM RN0901D47OHM

RN0903G47OHM RN0903G47OHM

RN0903F47OHM RN0903F47OHM

RN0903A47OHM RN0903A47OHM

RN0901F47OHM RN0901F47OHM

RN0905D47OHM RN0905D47OHM

RN0905H47OHM RN0905H47OHM

RN0905C47OHM RN0905C47OHM

RN0905A47OHM RN0905A47OHM

RN0905B47OHM RN0905B47OHM

RN0905F47OHM RN0905F47OHM

RN0905G47OHM RN0905G47OHM

RN0905E47OHM RN0905E47OHM

RN0909C

RN0909C

RN0909D

RN0909D

RN0909A

RN0909A

RN0909B

RN0909B

change to 8R16P 090405

MEM_MB_ADD[0..15][4,8]

B B

MEM_MB_ADD14

MEM_MB_ADD7

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD10

MEM_MB_ADD0

MEM_MB0_ODT0

MEM_MB_ADD13

MEM_MB_RAS#

MEM_MB0_CS#0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD15

MEM_MB_CKE1

MEM_MB_BANK2

MEM_MB_CKE0

MEM_MB0_CS#1

MEM_MB_CAS#

MEM_MB_ADD8

MEM_MB_ADD3

MEM_MB_ADD6

MEM_MB_WE#

MEM_MB_BANK0

MEM_MB_ADD4

MEM_MB_ADD9

MEM_MB0_ODT1

MEM_MB_ADD5

MEM_MB_BANK1

6 11

1 16

5 12

2 15

5 12

7 10

1 16

2 15

4 13

3 14

5 12

8 9

7 10

8 9

3 14

4 13

8 9

7 10

1 16

4 13

3 14

6 11

6 11

2 15

7 8

47Ohm

47Ohm

3 4

47Ohm

47Ohm

5 6

47Ohm

47Ohm

1 2

47Ohm

47Ohm

071211

MEM_MB_BANK2[4,8]

MEM_MB_BANK1[4,8]

MEM_MB_BANK0[4,8]

MEM_MB0_ODT0[4,8]

MEM_MB0_ODT1[4,8]

A A

MEM_MB_CKE0[4,8]

MEM_MB_CKE1[4,8]

MEM_MB_RAS#[4,8]

MEM_MB_CAS#[4,8]

MEM_MB_WE#[4,8]

MEM_MB0_CS#0[4,8]

MEM_MB0_CS#1[4,8]

5

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB0_ODT0

MEM_MB0_ODT1

MEM_MB_CKE0

MEM_MB_CKE1

MEM_MB_RAS#

MEM_MB_CAS#

MEM_MB_WE#

MEM_MB0_CS#0

MEM_MB0_CS#1

add MA0_ODT1

睿

090417

4

Page 10

5

D D

4

3

2

1

R1.11 080319

Change the NB Part number to RS780 (A13)

U1001A

AC24

AC25

AB25

AB24

AA24

AA25

W21

W20

AB23

AA22

Y25

Y24

V22

V23

V25

V24

U24

U25

T25

T24

P22

P23

P25

P24

N24

N25

Y22

Y23

V21

V20

U20

U21

U19

U18

T22

T23

M22

M23

R21

R20

C23

A24

U1001A

HT_RXCAD0P

HT_RXCAD0N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD15P

HT_RXCAD15N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCTL0P

HT_RXCTL0N

HT_RXCTL1P

HT_RXCTL1N

HT_RXCALP

HT_RXCALN

RS780MN

RS780MN

HT_CPU_RXD0

HT_TXCALP

HT_TXCALN

D24

D25

E24

E25

F24

F25

F23

F22

H23

H22

J25

J24

K24

K25

K23

K22

F21

G21

G20

H21

J20

J21

J18

K17

L19

J19

M19

L18

M21

P21

P18

M18

H24

H25

L21

L20

M24

M25