Page 1

A

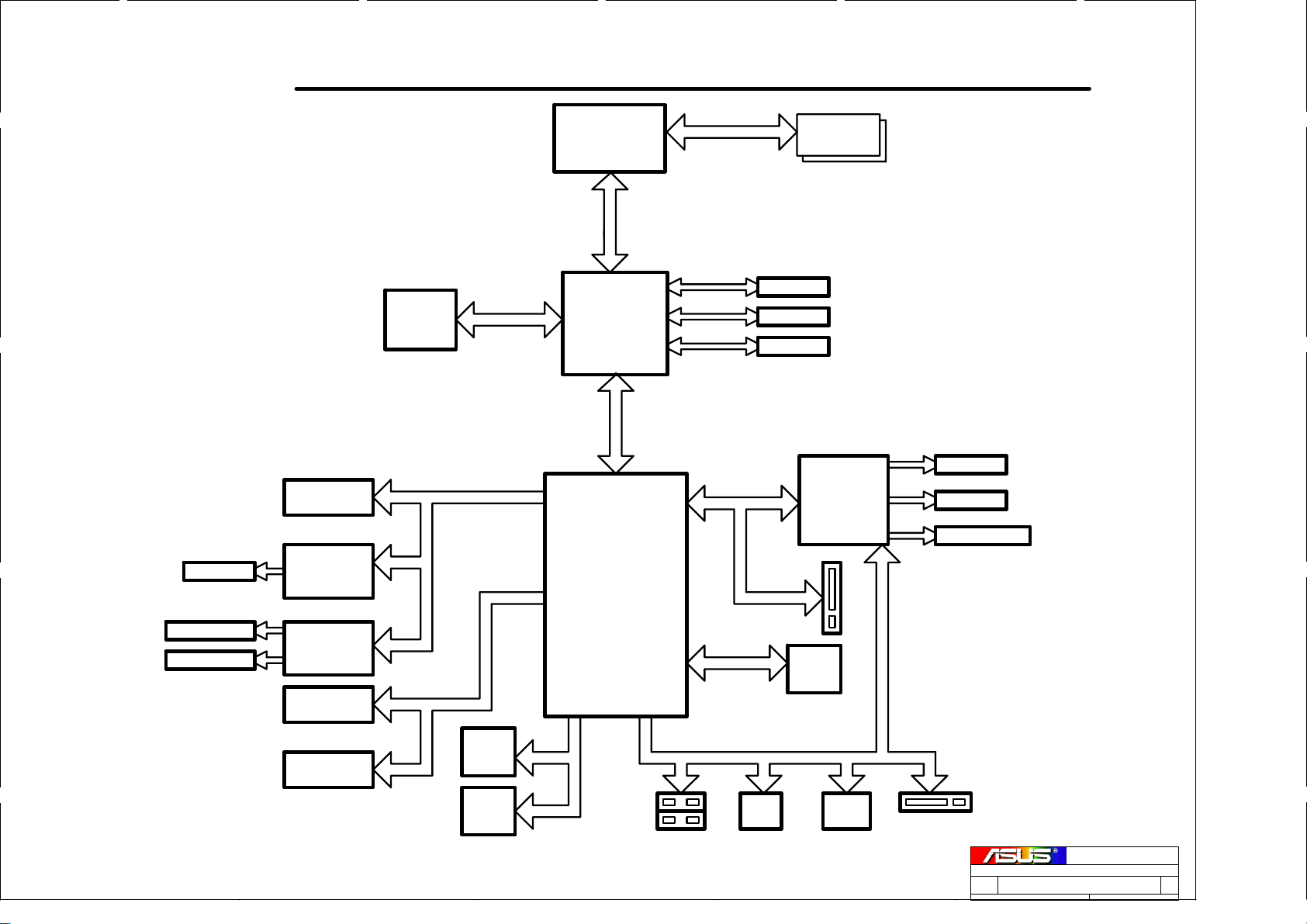

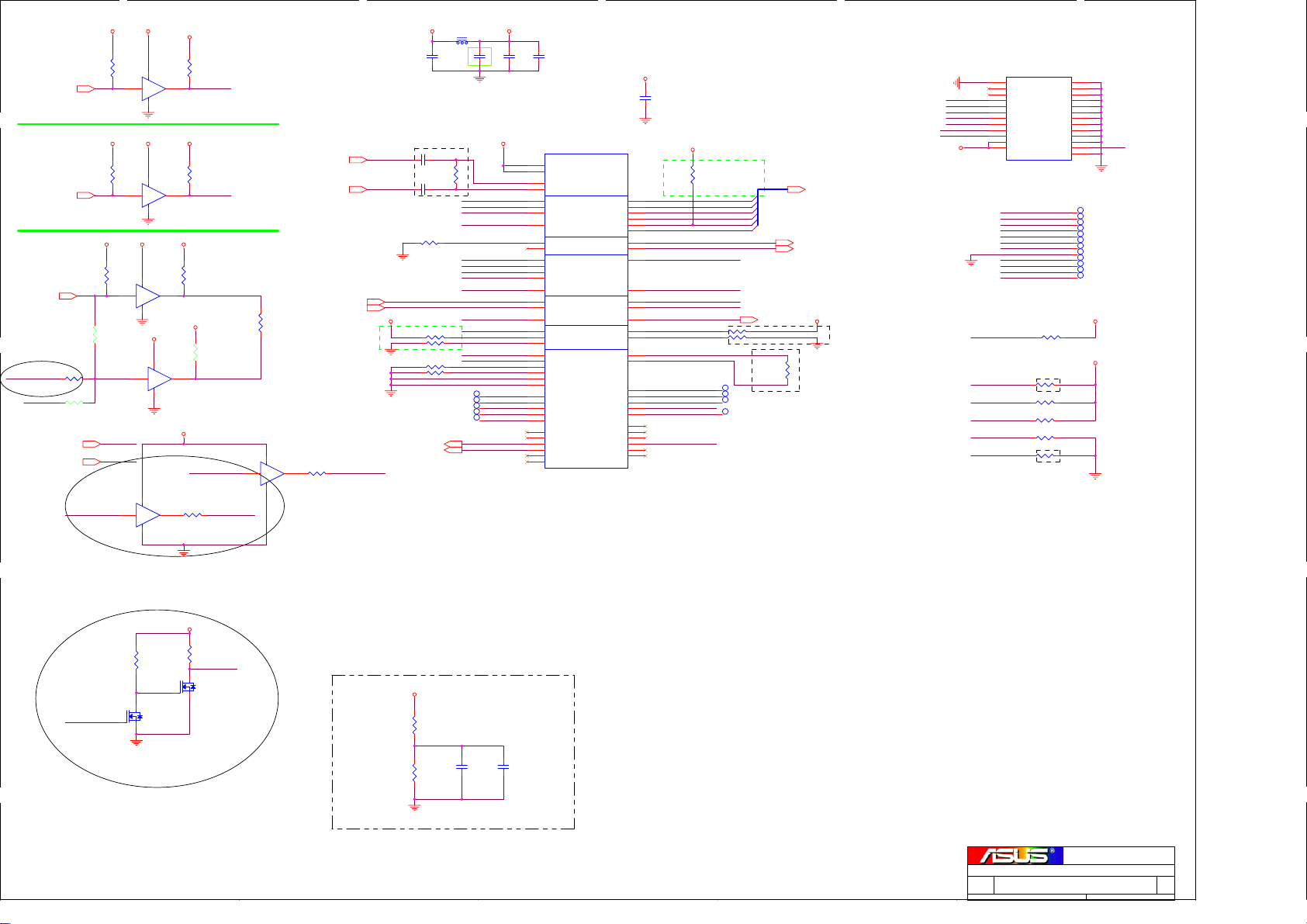

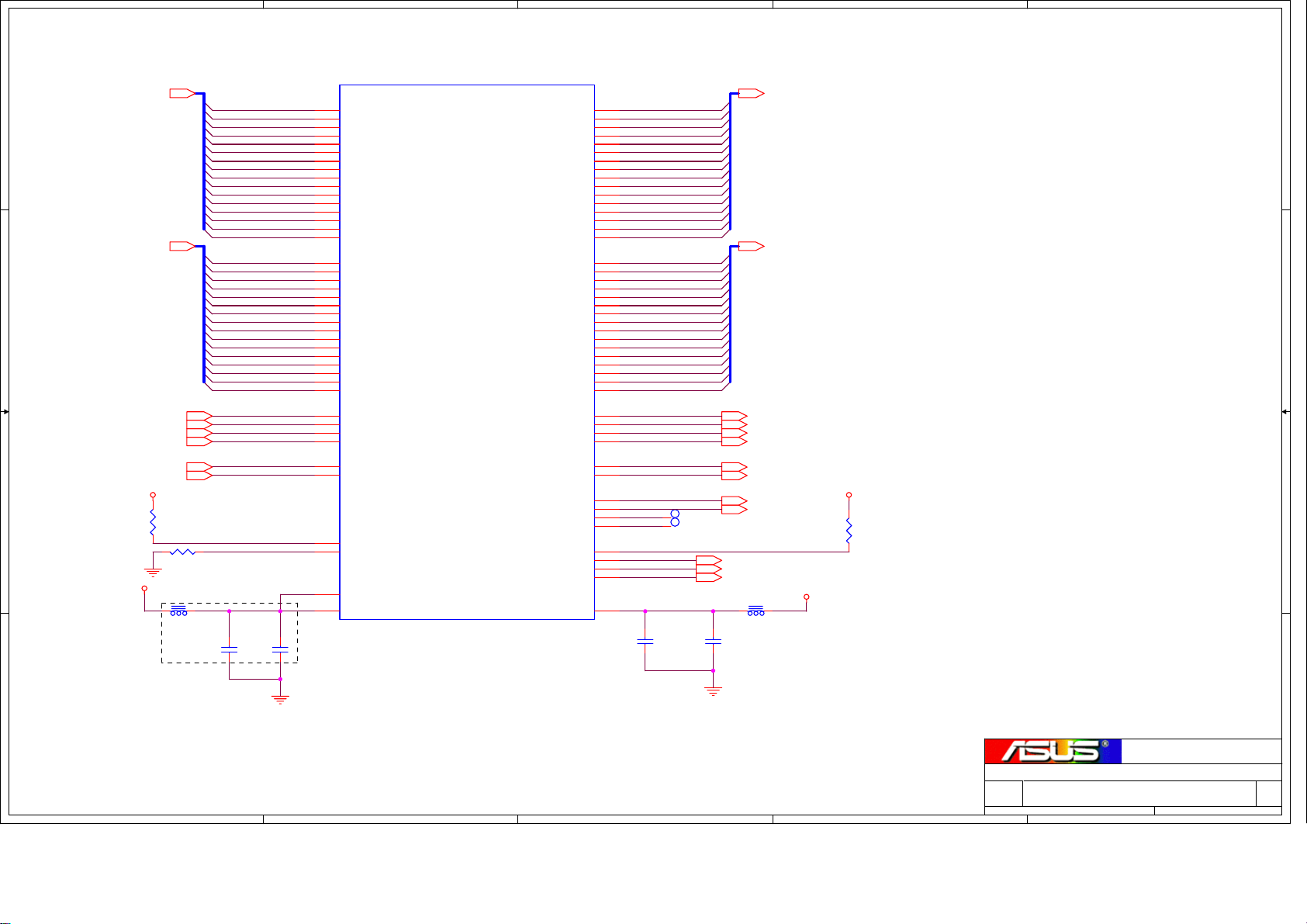

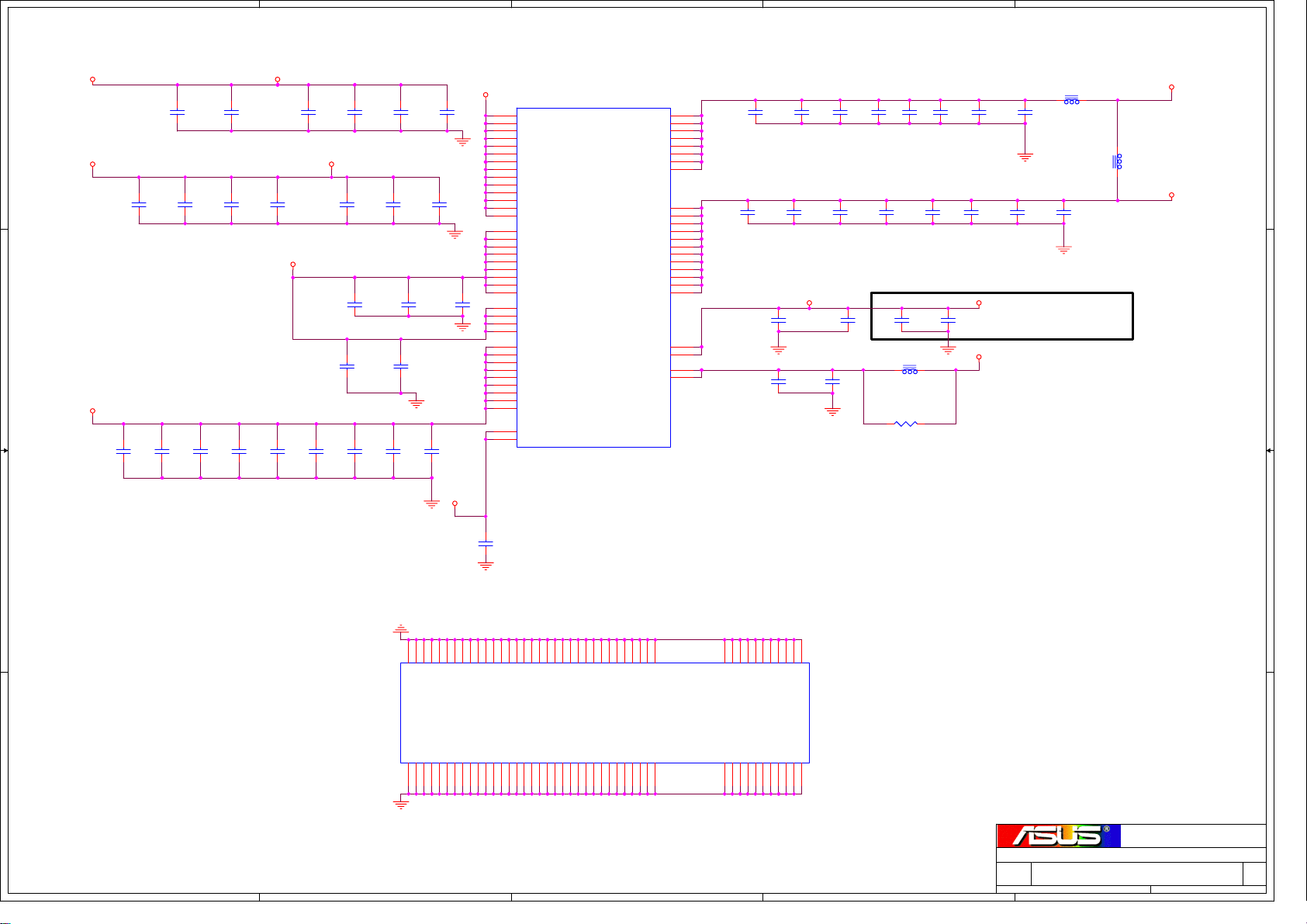

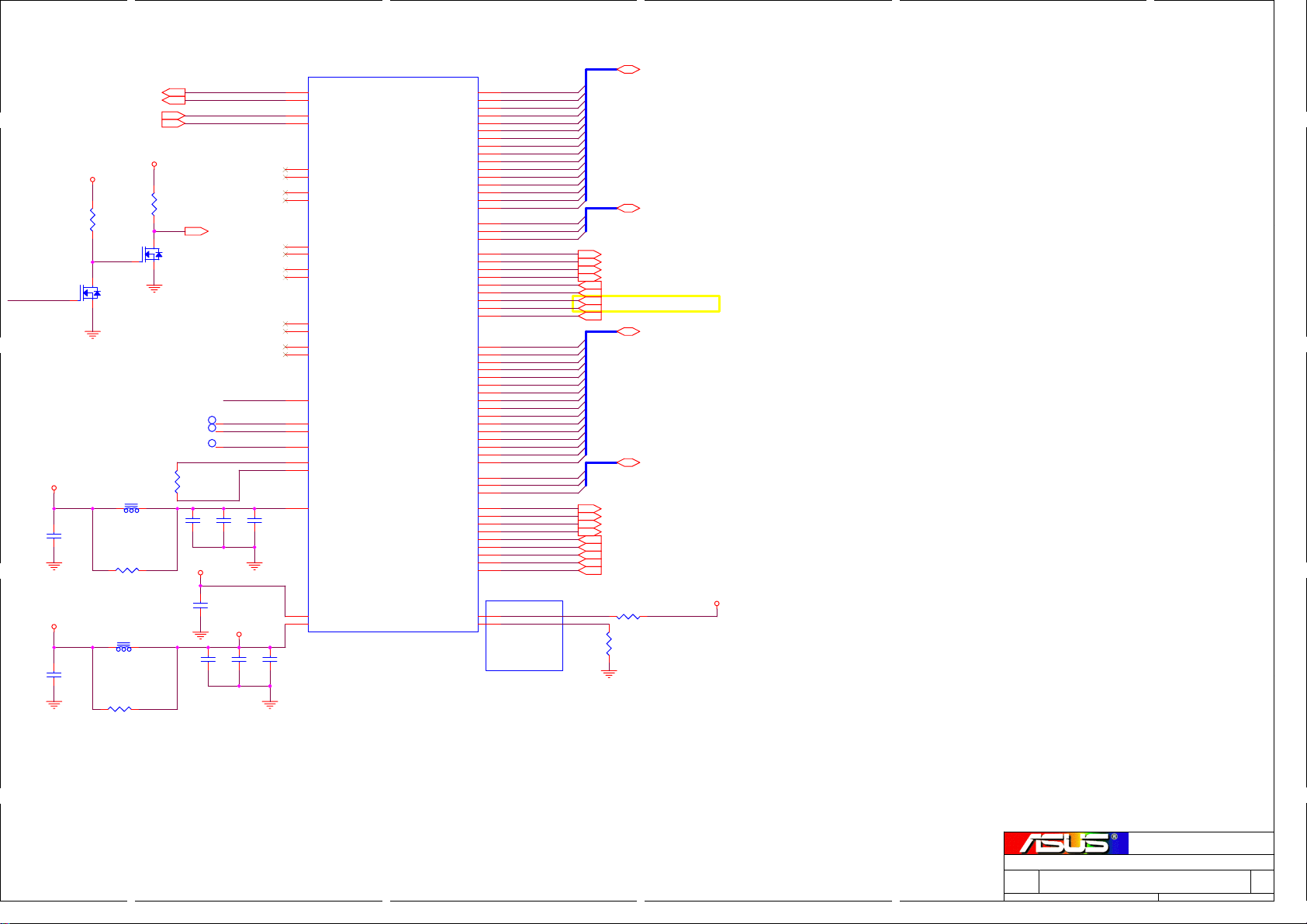

01.BLOCK DIAGRAM

5

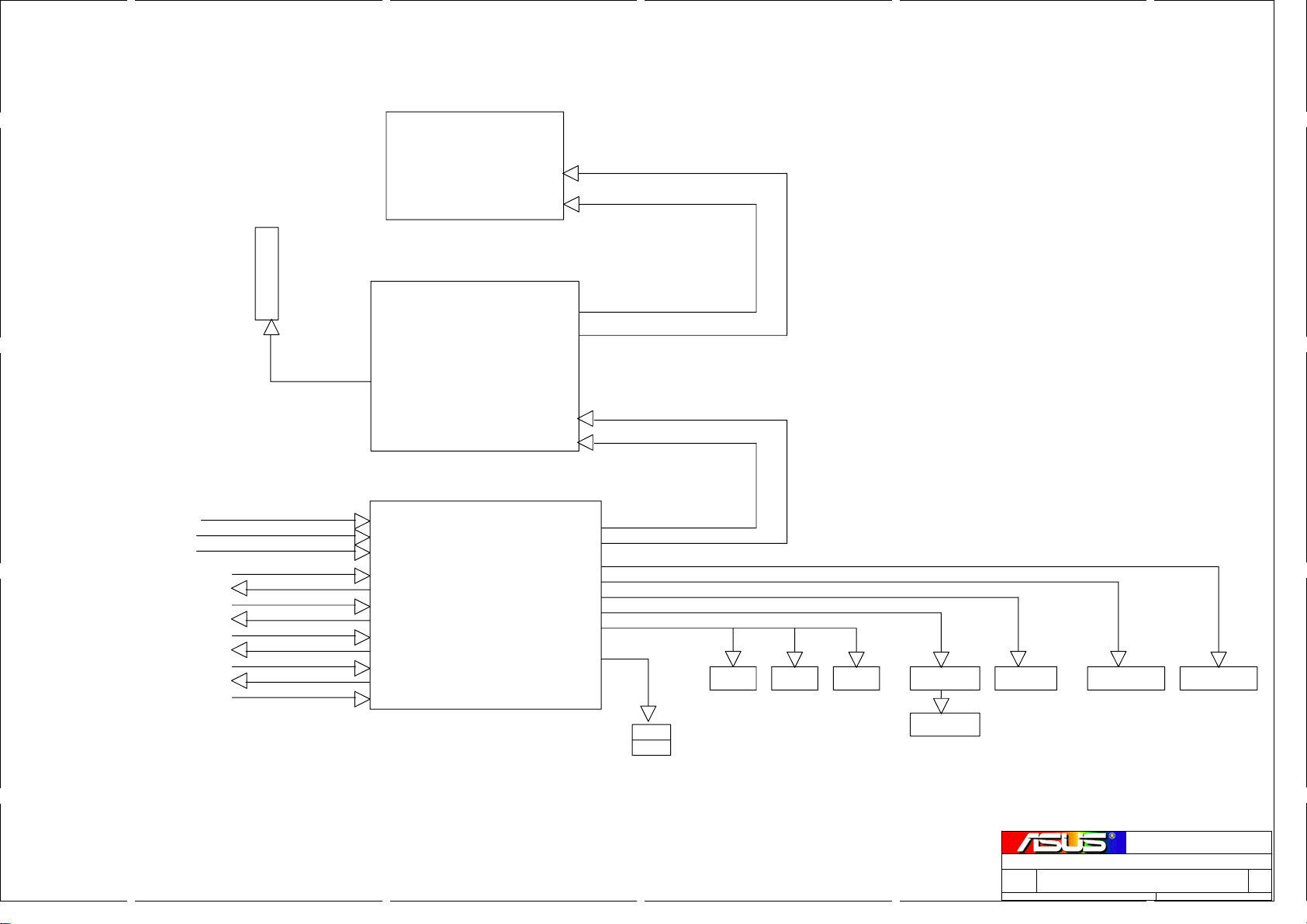

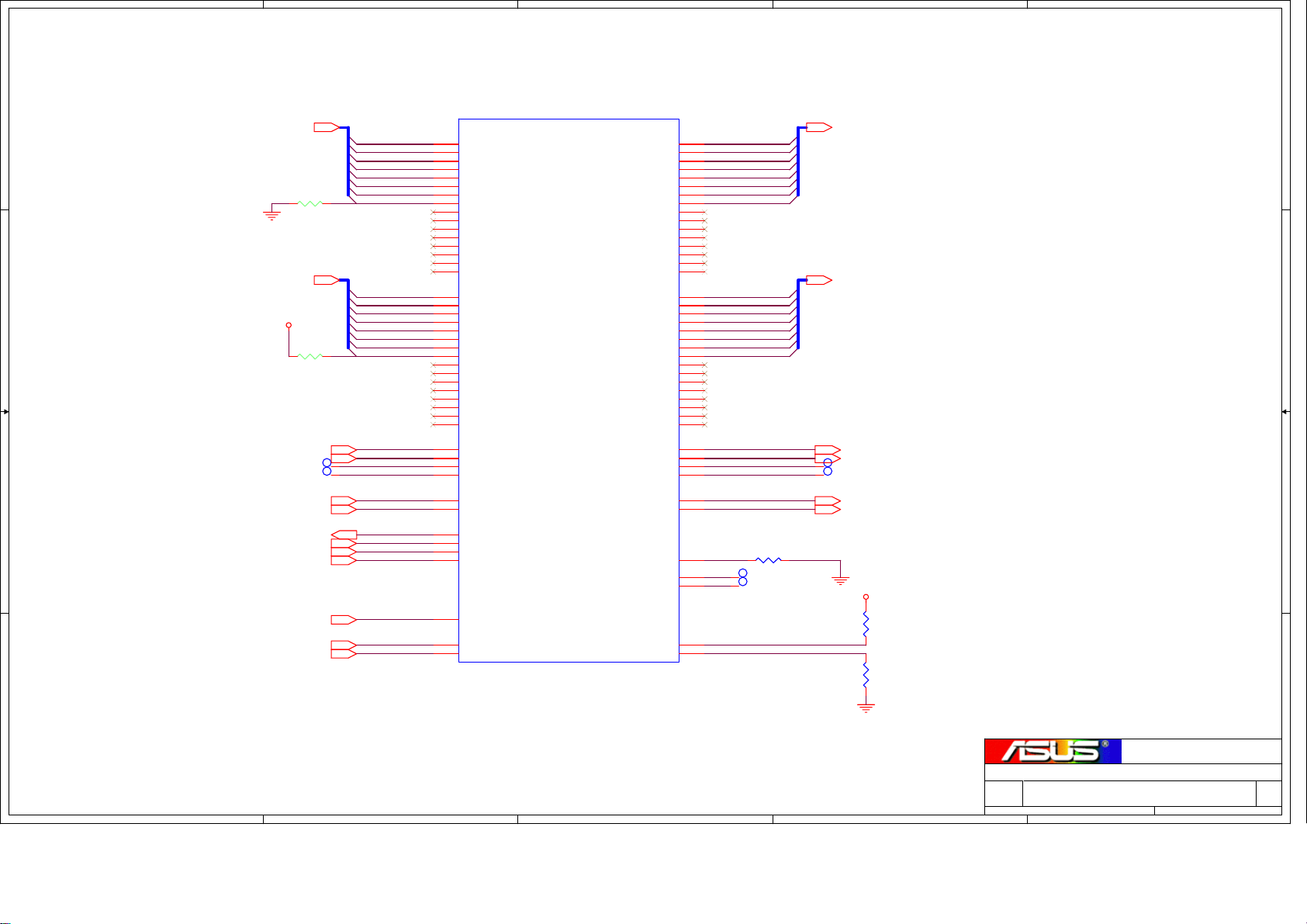

02.RESET MAP

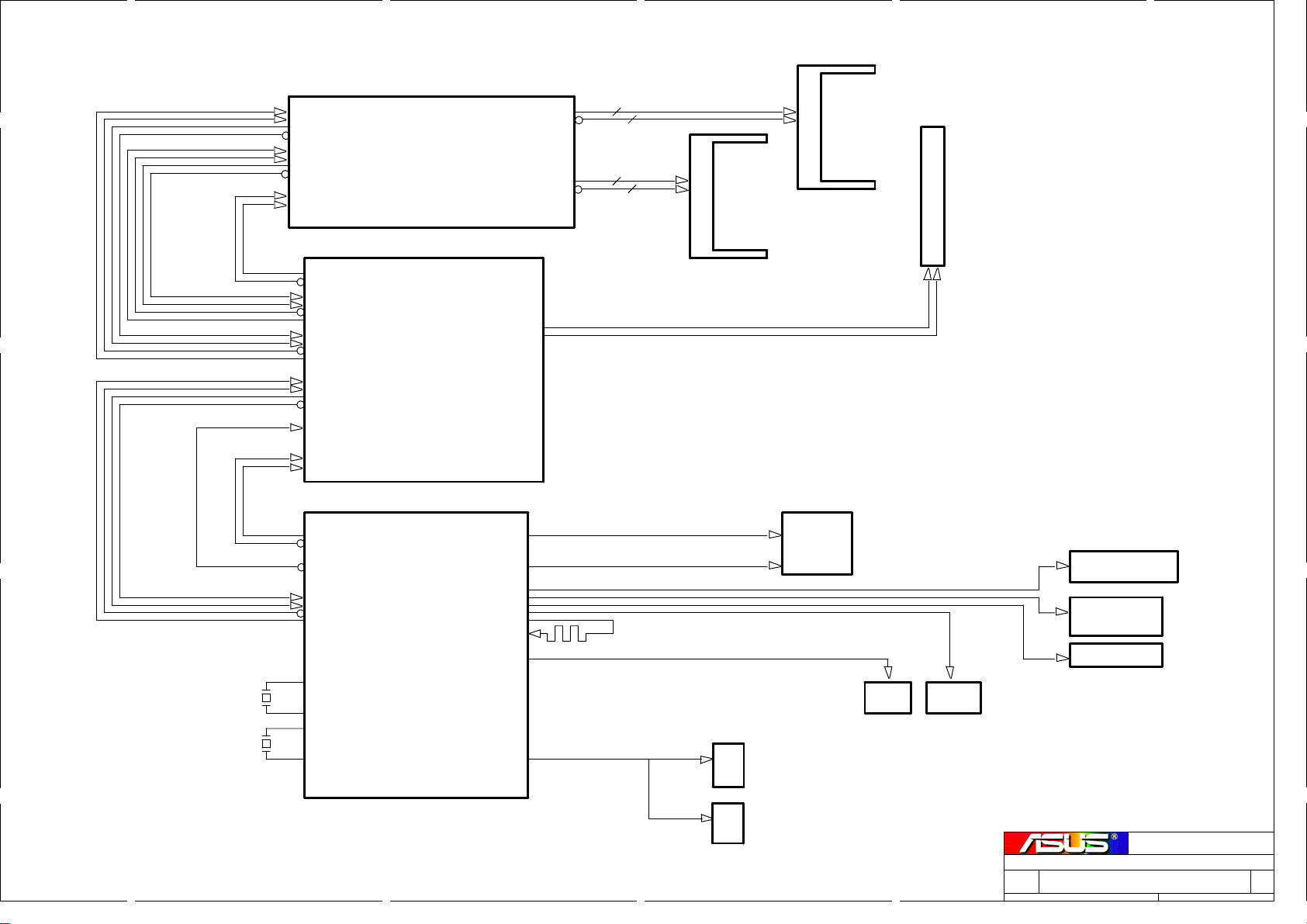

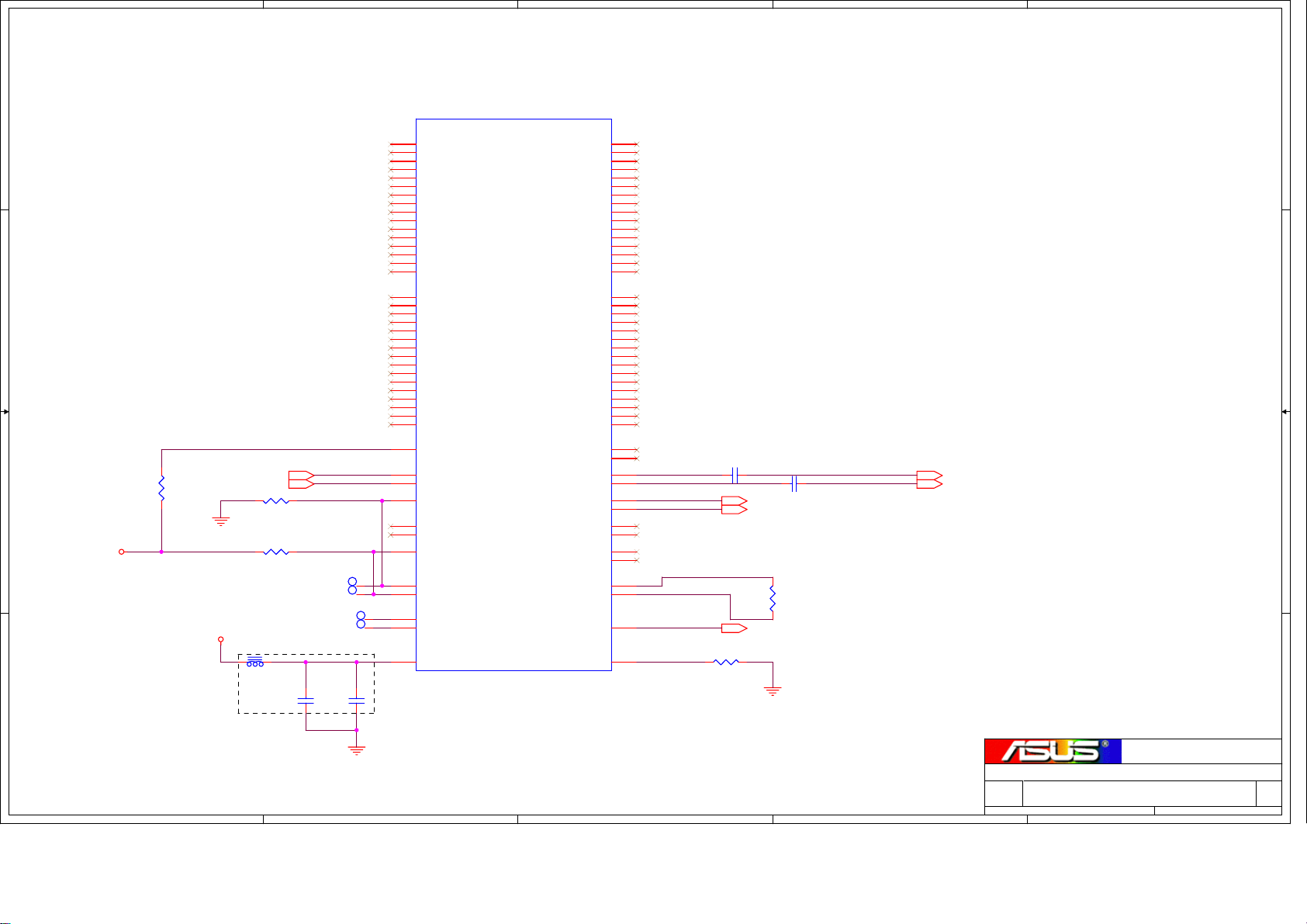

03.CLOCK MAP

04.S1_HT_C51

05.S1_DDR2

06.S1_CNTL/DEBUG/THERM

07.S1_POWER

08.DDR2_SODIMM

D D

09.DDR2 TER/FETGAGE

10.C51_HT_CPU

11.C51_HT_MCP

12.C51_PCIE

13.C51_VIDEO

14.C51_VCC_GND

15.FAN/THERM SENSOR

16.MCP51_HT

17.MCP51_PCI/LPC

18.MCP51_IDE/SATA

19.MCP51_USB/AC97/SMB

20.MCP51_RGMI/XTAL

21.MCP51_VCC

22.G73M_PCIE

23.G73M_FB I/F

24.G73M_LVDS/GND

25.G73M_VGA/TV

26.G73M_TMDS/GPIO

27.G73M_XTAL/ROM STRAP

C C

28.G73M_STRAPS

29.G73M_MEM_PART1

30.G73M_MEM_PART2

31.HDD/CDROM

32.MINI PCI

33.CARD BUS

34.PCMCIA

35.1394/SD_CARD

36.SIO/SIR

37.FWH

38.KBC

39.USB/BLUE TOOTH

40.CRT/TV CON

41.LVDS/INVERTER

42.ALC880

43.AMP

44.MIC/LINE-IN JACK

45.RJ45/11/MDC

B B

46.LAN

47.BLANK

48.FUNCTION KEY

49.LED

50.POWER SEQEUNCE(1)

51.POWER SEQUENCE(2)

52.SCREW HOLE

53.Battery

54.CHARGE

55.BATLOW/SD#

56.LOAD SWITCH

57.BLANK

58.BLANK

59.BLANK

60.POWER SEQUENCE BLCOK

61.POWER BUDGET BLOCK

62.BLANK

5

SIR

AUDIO DJ KEY

INSTANT KEY

SUPPER I/O

LPC47N217

KBC 38857

AZALIA CODEC

ALC660

MDC

HEADER

4

A6M

Gigabit

Ethernet

RTL8111B

FWH

LPC BUS

4

33MHz

PCI-E x1

CD-ROM

HDD

Pri

Sec

3

AMD S1g1

638 PIN

PACKAGE

x16

200/400/800

MHz

HyperTransport

nVIDIA

C51MV

BGA 468

X8 /X4

200/400/800

HyperTransport

nVIDIA

MCP51

BGA 508

IDE BUS

3

REVISION: 2.0

128-BIT

Channel A/B

LVDS

CRT

TV OUT

MHz

33MHz

PCI BUS

MINI-PCI

/WIRE LESS

SATA 2 /SATA

USB BUS

USB

CCD

USB 2.0 X4

2

Unbuffer

DDR2

SO-DIMM

R5C841

BLUE

TOOTH

2

PCMCIA

1394

CARD READER

MiniCard

/WIRE LESS

1

final_1.00

Title :

ASUSTECH CO.,LTD.

Size Project Name

C

Date: Sheet

Engineer:

A6M

1

BLOCK DIAGRAM

Jefing_Li

of

173Friday, March 10, 2006

Rev

1.0

A

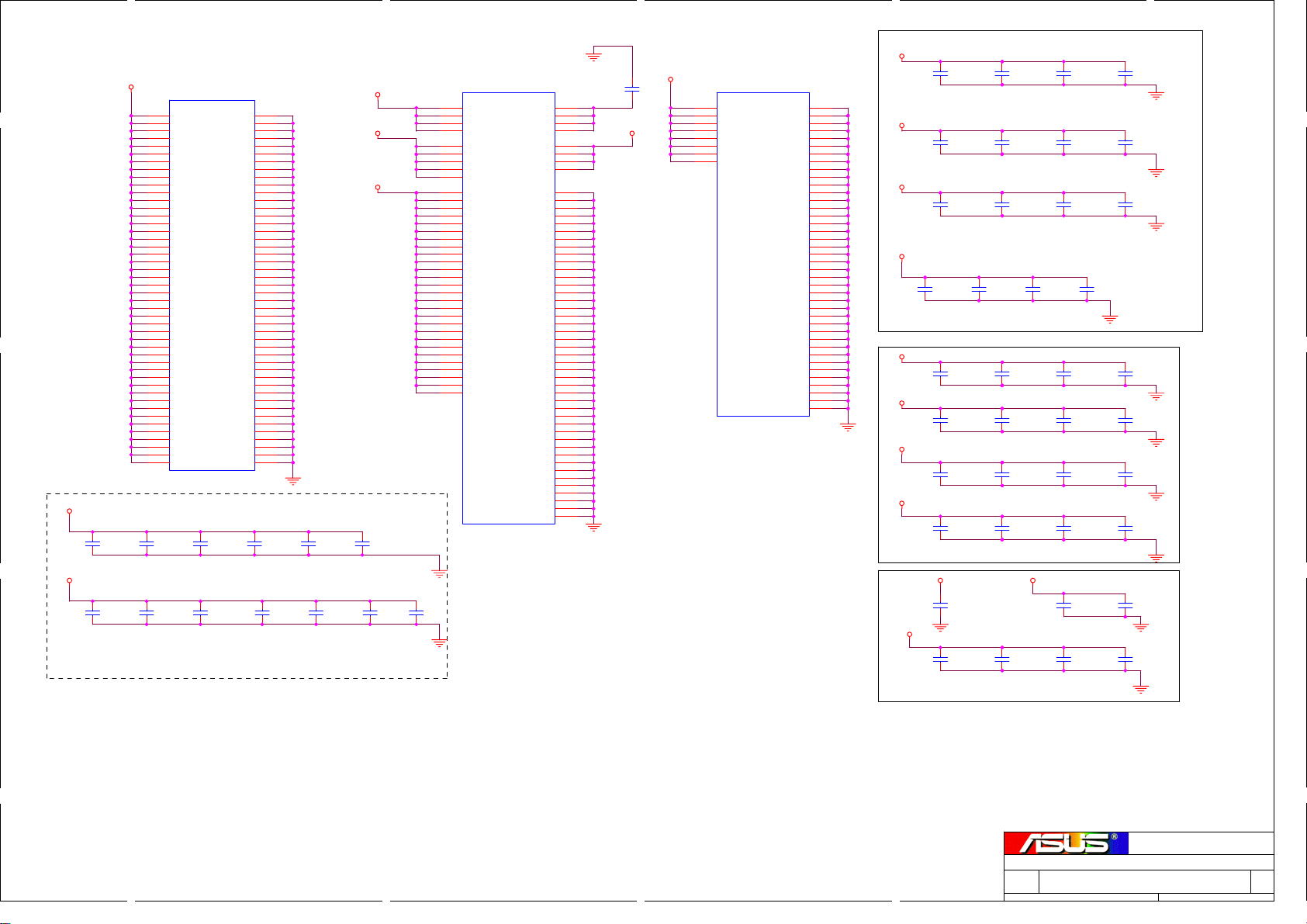

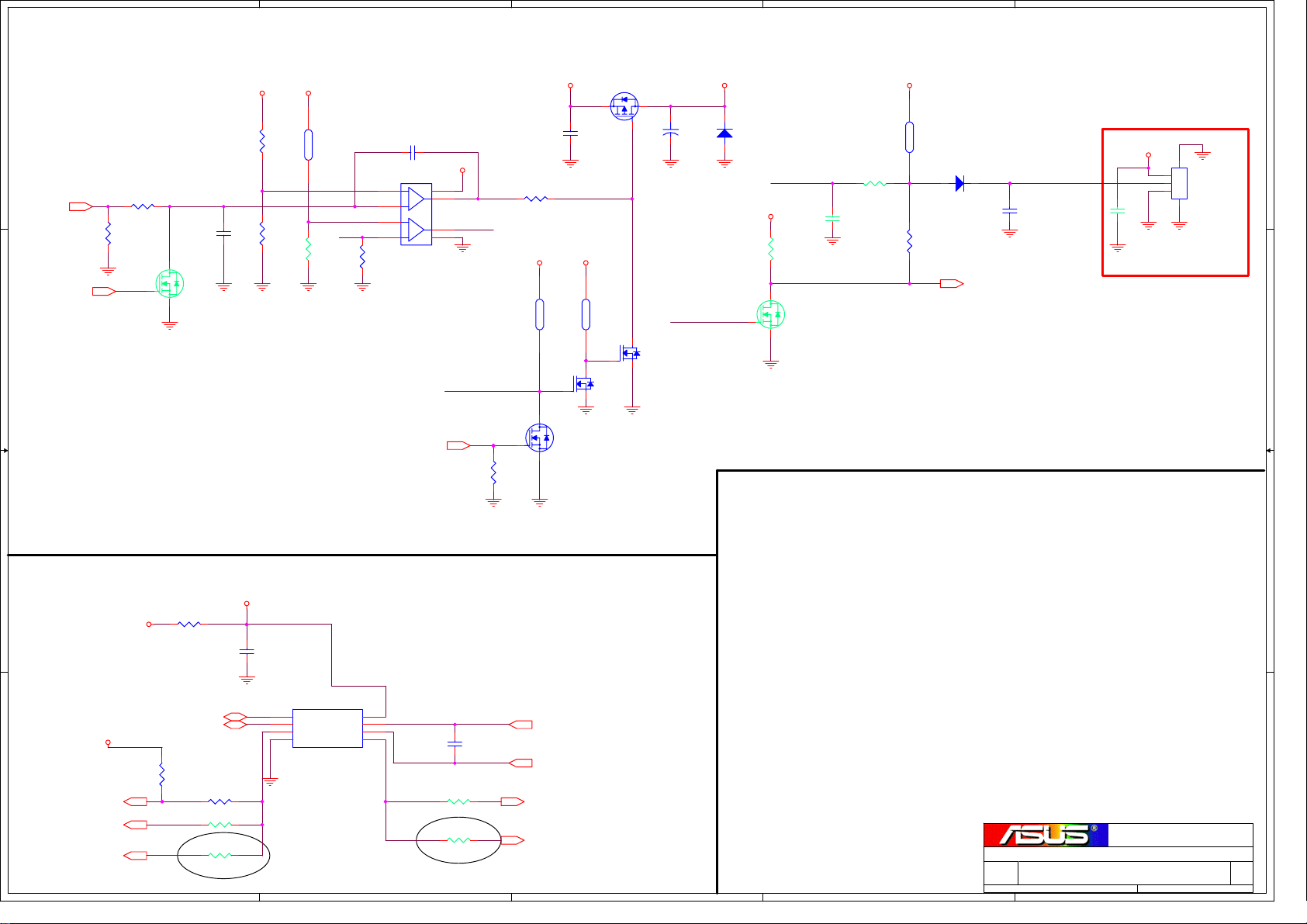

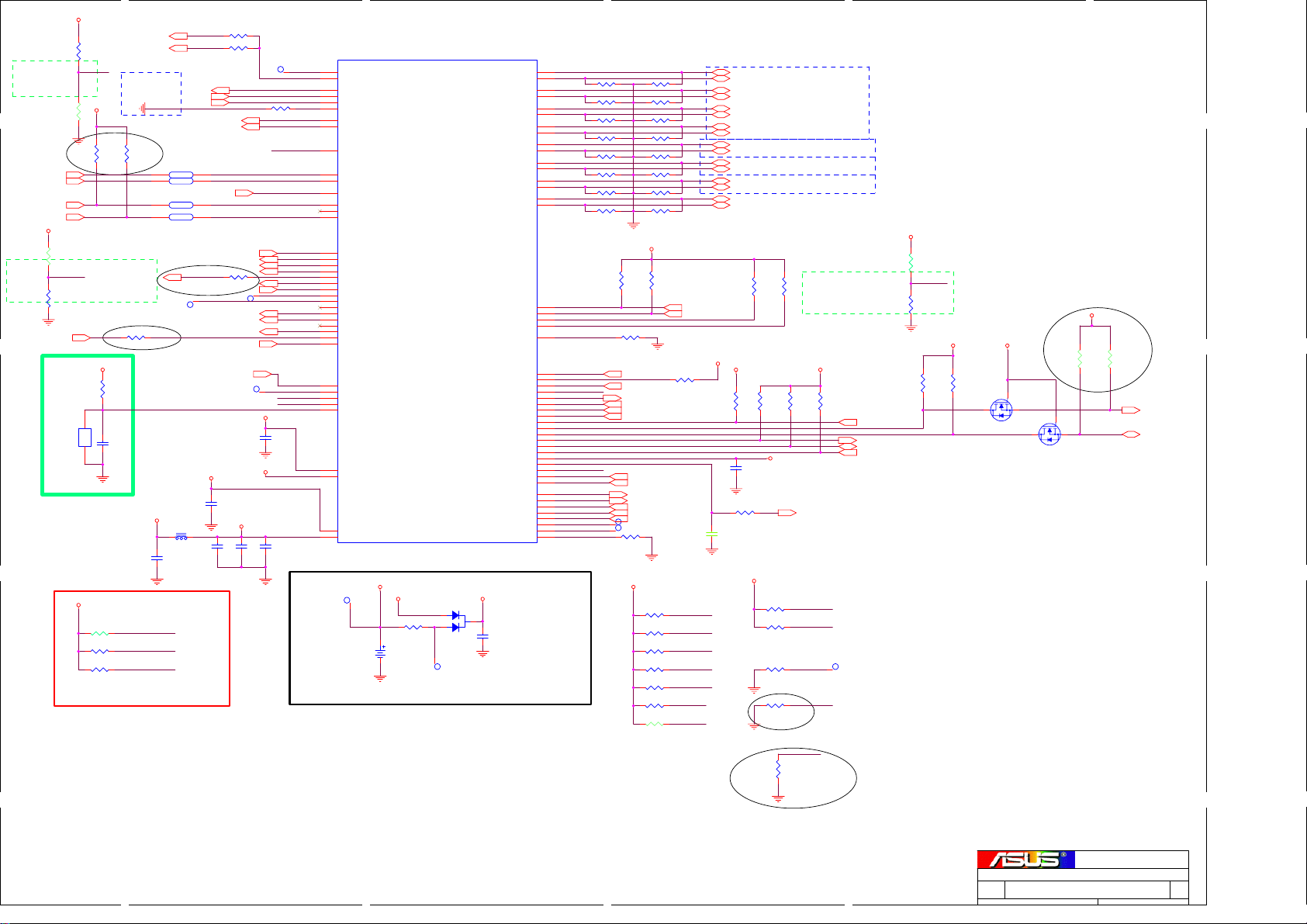

Page 2

5

A

4

3

2

1

SKT638 S1 CPU

D D

RESET#

PWROK

C51MV

G73M

HT_CPU_PWRGD

C C

PE_RESET#

PCIE RST*

HT_CPU_RST#

HT_MCP_PWRGD

HT_MCP_RESET#

CPU_PWROK

CPU_RESET#

RESET MAP

MCP51

POWER SWTCH

RESET Button

KBC

B B

PWRBTN#

RSTBTN#

KBRST#

HT_VLD

HTVDD_EN

CPU_VLD

CPUVDD_EN

PWRGD

SUSB#

MEM_VLD

SUSC#

PWRGD_SB

PWRBTN#

RSTBTN#

KBRDRSTIN#

HT_VLD

HTVDD_EN

CPU_VLD

CPUVDD_EN

PWRGD

SLP_S3#

MEM VLD

SLP_S5#

PWRGD_SB

HT_MCP_RST#

HT_MCP_PWRGD

PCI RST0#

PCI RST1#

PCI RST2#

PCI RST3#

LPC_RST#

AC_RESET#

HT_MCP_RST#

HT_MCP_PWRGD

MINI_PCI_RST#

CARD_PCI_RST#

LAN_PCI_RST#

PCI_IDE_RST#

LPC_RST#

AC_RESET#

MDC

AUDIO

SIO

FLASH

KBC

IDE

CD ROM

88E8001.

CARDBUS

MINI PCI

A

final_1.00

Title :

ASUSTECH CO.,LTD.

Size Project Name

A3

5

4

3

2

Date: Sheet

A6T

Engineer:

1

RESET MAP

Jefing_Li

of

273Monday, March 06, 2006

Rev

1.0

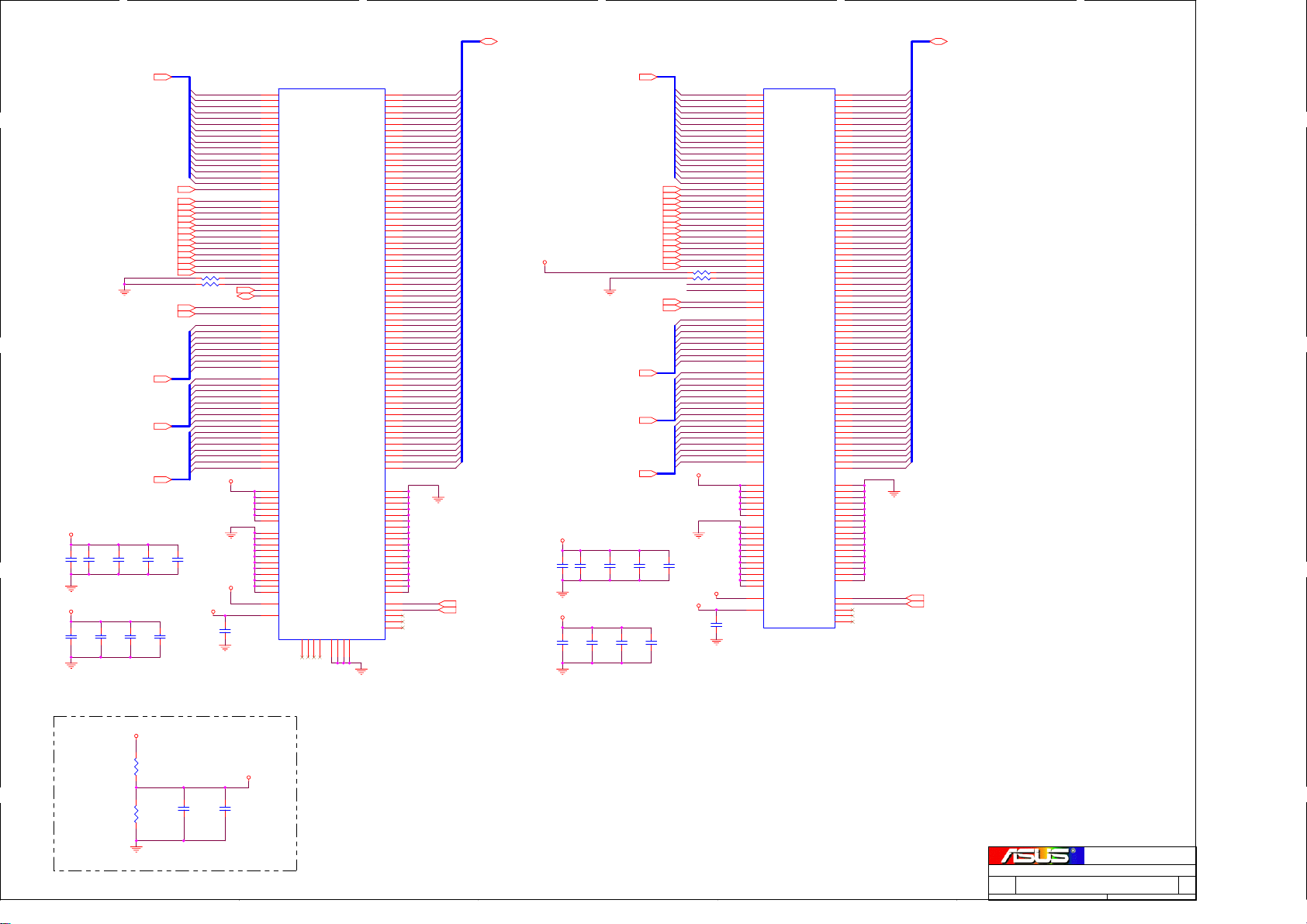

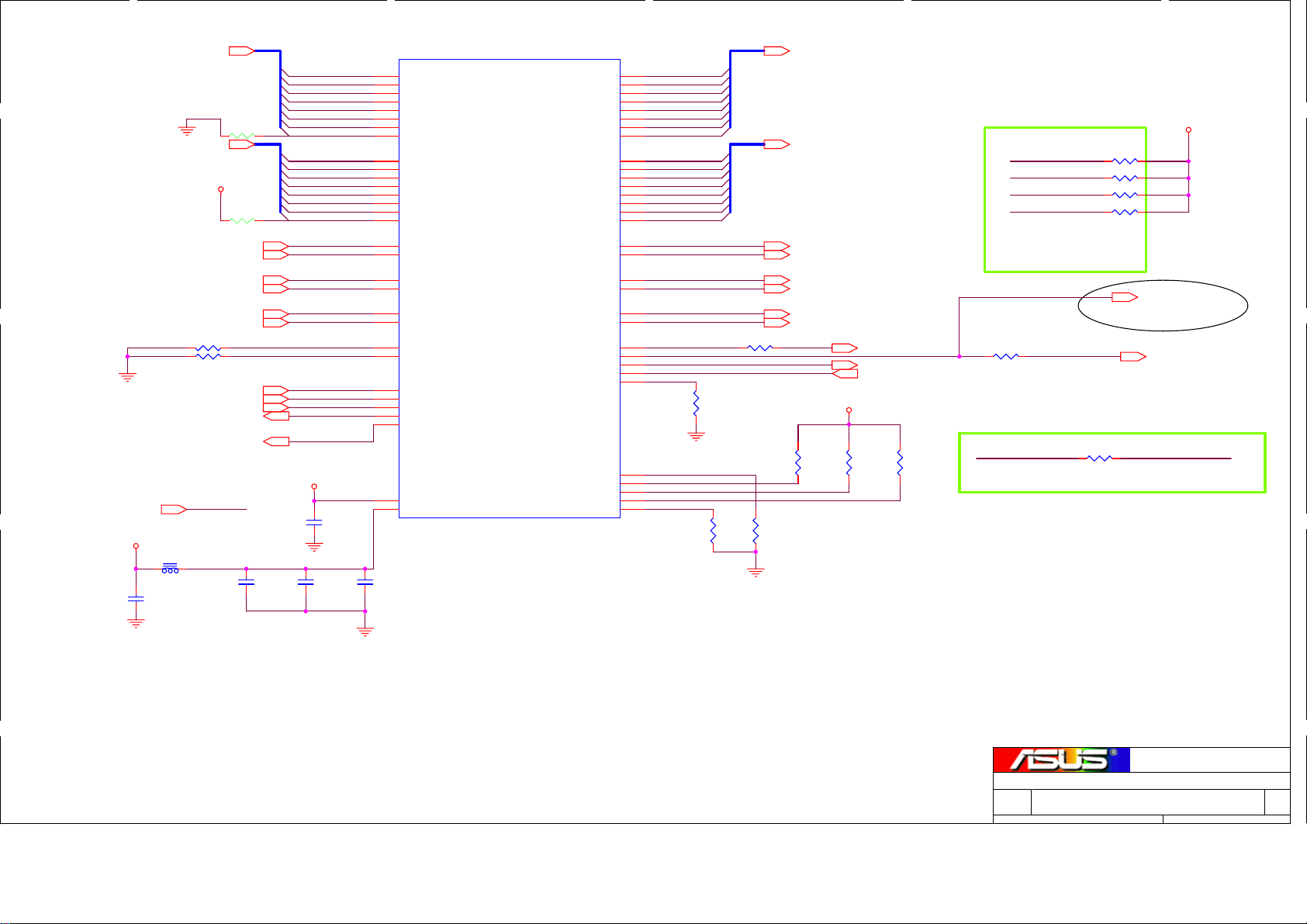

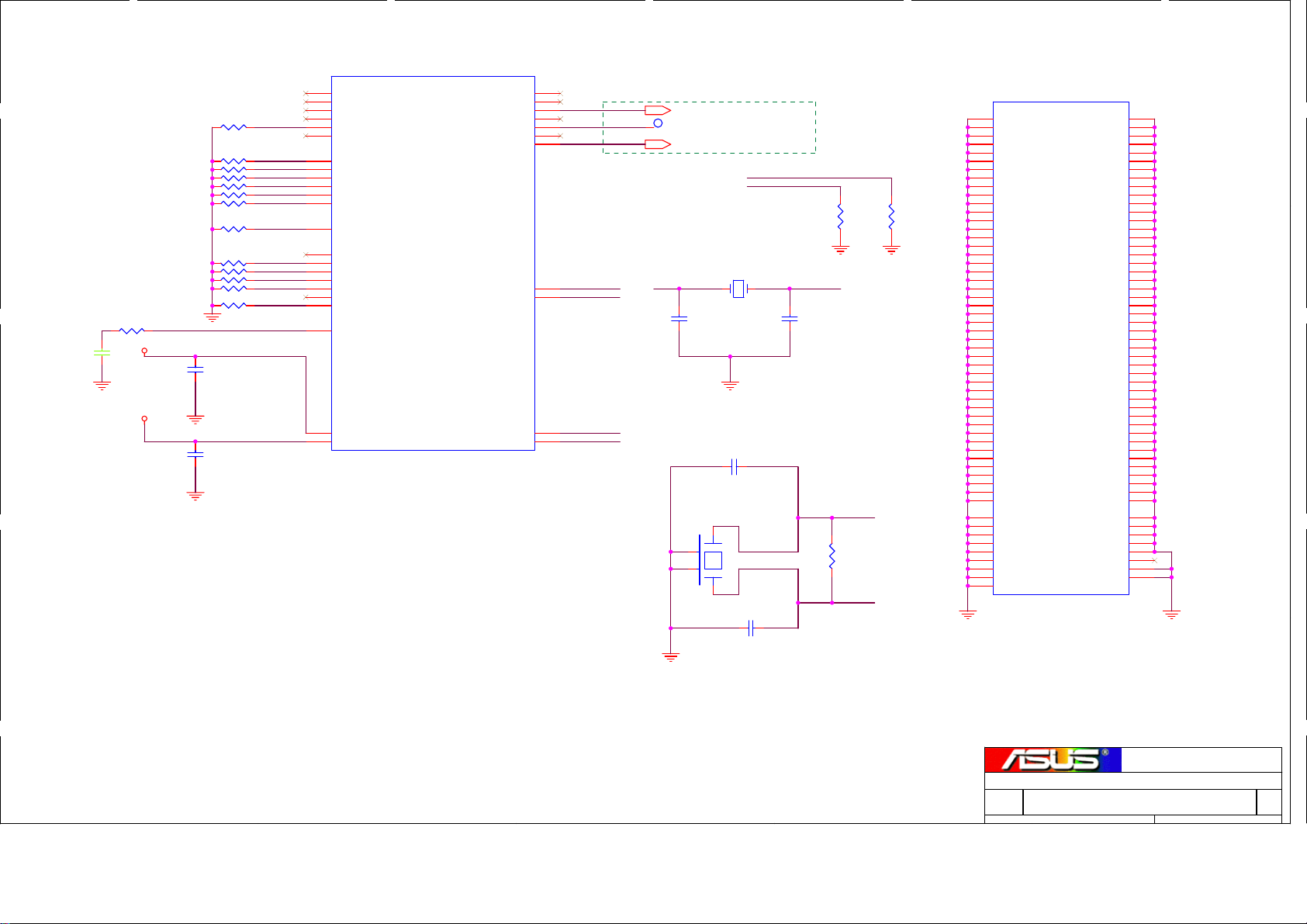

Page 3

5

A

4

3

2

1

CLOCK MAP

SKT638 S1 CPU

HT_CPU_RXCLK0

D D

C C

B B

HT_CPU_RXCLK0*

HT_CPU_TXCLK0

HT_CPU_TXCLK0*

HT_CPU_RXCLK1

HT_CPU_RXCLK1*

HT_CPU_TXCLK1

HT_CPU_TXCLK1*

CPUCLK_IN*

CPUCLK_IN

CLKOUT_200MHZ

CLKOUT_200MHZ*

HT_CPU_RXCLK1*

HT_CPU_RXCLK1

HT_CPU_TXCLK1*

HT_CPU_TXCLK1

HT_CPU_RXCLK0*

HT_CPU_RXCLK0

HT_CPU_TXCLK0*

HT_CPU_TXCLK0

HT_MCP_RXCLK0

HT_MCP_RXCLK0*

HT_MCP_TXCLK0

HT_MCP_TXCLK0*

CLKIN_25MHZ

CLKIN_200MHZ*

CLKIN_200MHZ

MCPCLK_OUT

MCPCLK_OUT*

25MHZ_CLKOUT

HT_MCP_RXCLK0*

HT_MCP_RXCLK0

HT_MCP_TXCLK0*

HT_MCP_TXCLK0

C51M

MCP51M

MEMORY_A_CLK[2:1]

MEMORY_A_CLK[2:1]*

MEMORY_B_CLK[2:1]

MEMORY_B_CLK[2:1]*

PE0_REFCLK

PE0_REFCLK*

PE1_REFCLK

PE1_REFCLK*

PE2_REFCLK

PE2_REFCLK*

XTAL_IN

XTAL_OUT

BUF_SIO

SUSCLK

LPC_CLK0

PCI_CLK0

PCI_CLK1

PCI_CLK2

PCI_CLK3

PCI_CLK4

PCI_CLK_FB

LPC_CLK1

14.31818MHZ

33MHZ

33MHZ

33MHZ

2

2

2

2

SO-DIMM 0

G73M

SO-DIMM 1

SIO

MINI PCI

R5C841

CARDBUS

CONTROLLER

KBC

32.768 KHZ

25.0 MHZ

RTC_XTAL

XTAL_IN

XTAL_OUT

BUF_25MHZ

MII_RXCLK

MII_TXCLK

AC_BITCLK

AC_BITCLK

FLASH

MDC

88E8001

A

24MHZ

5

4

3

ALC880

final_1.00

Title :

ASUSTECH CO.,LTD.

Size Project Name

A3

Date: Sheet

A6T

Engineer:

2

1

CLOCK MAP

Jefing_Li

373Monday, March 06, 2006

of

Rev

1.0

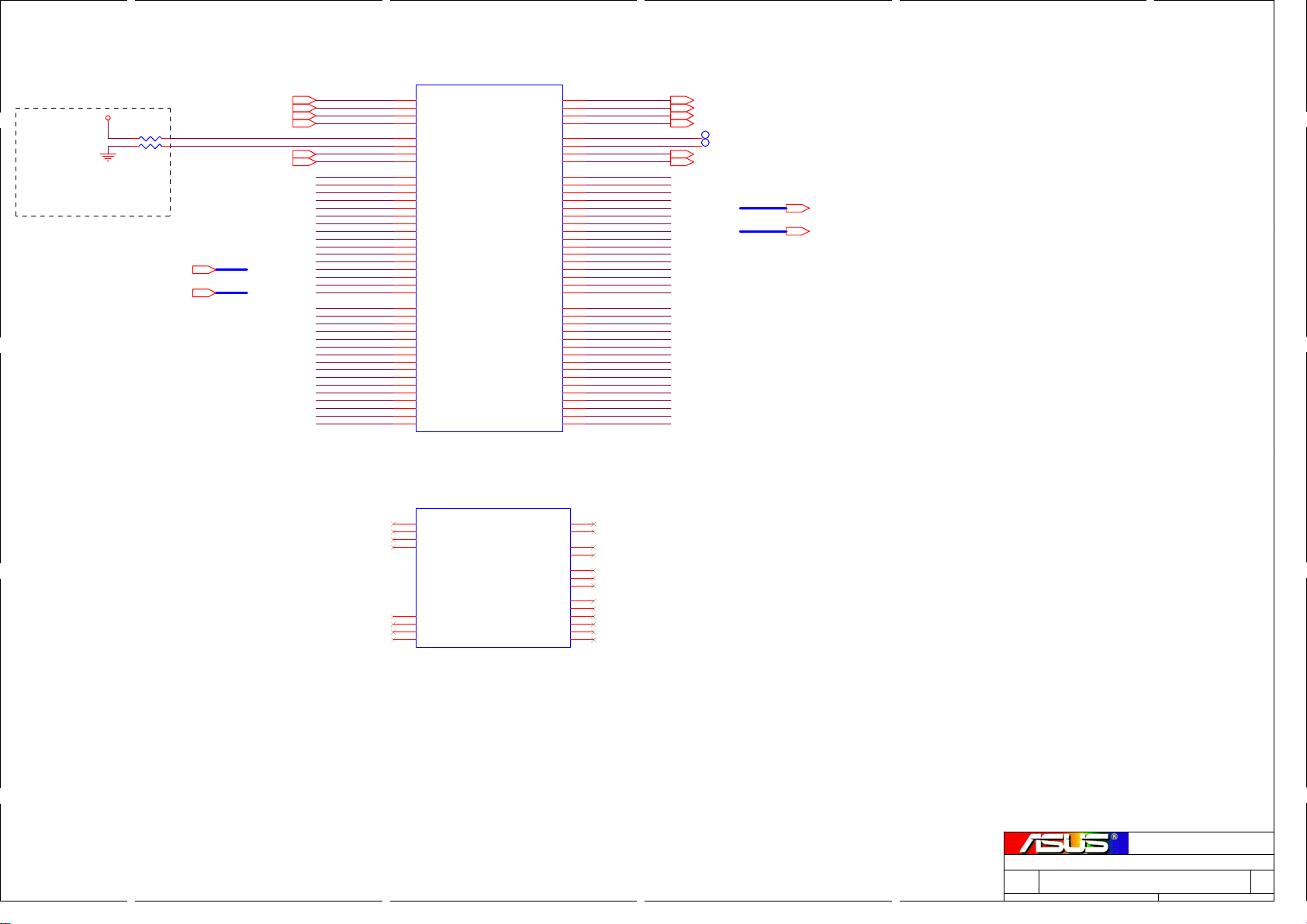

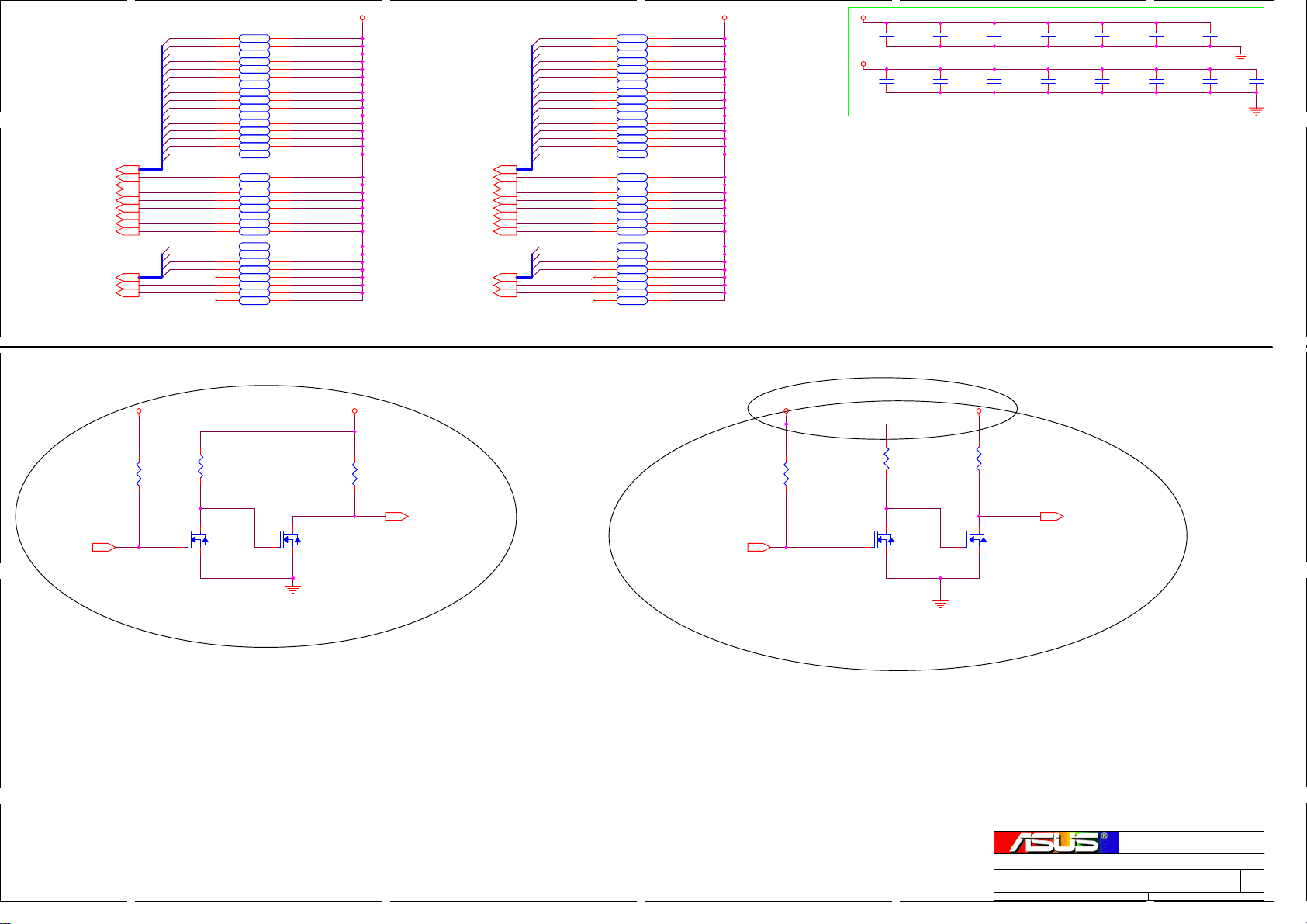

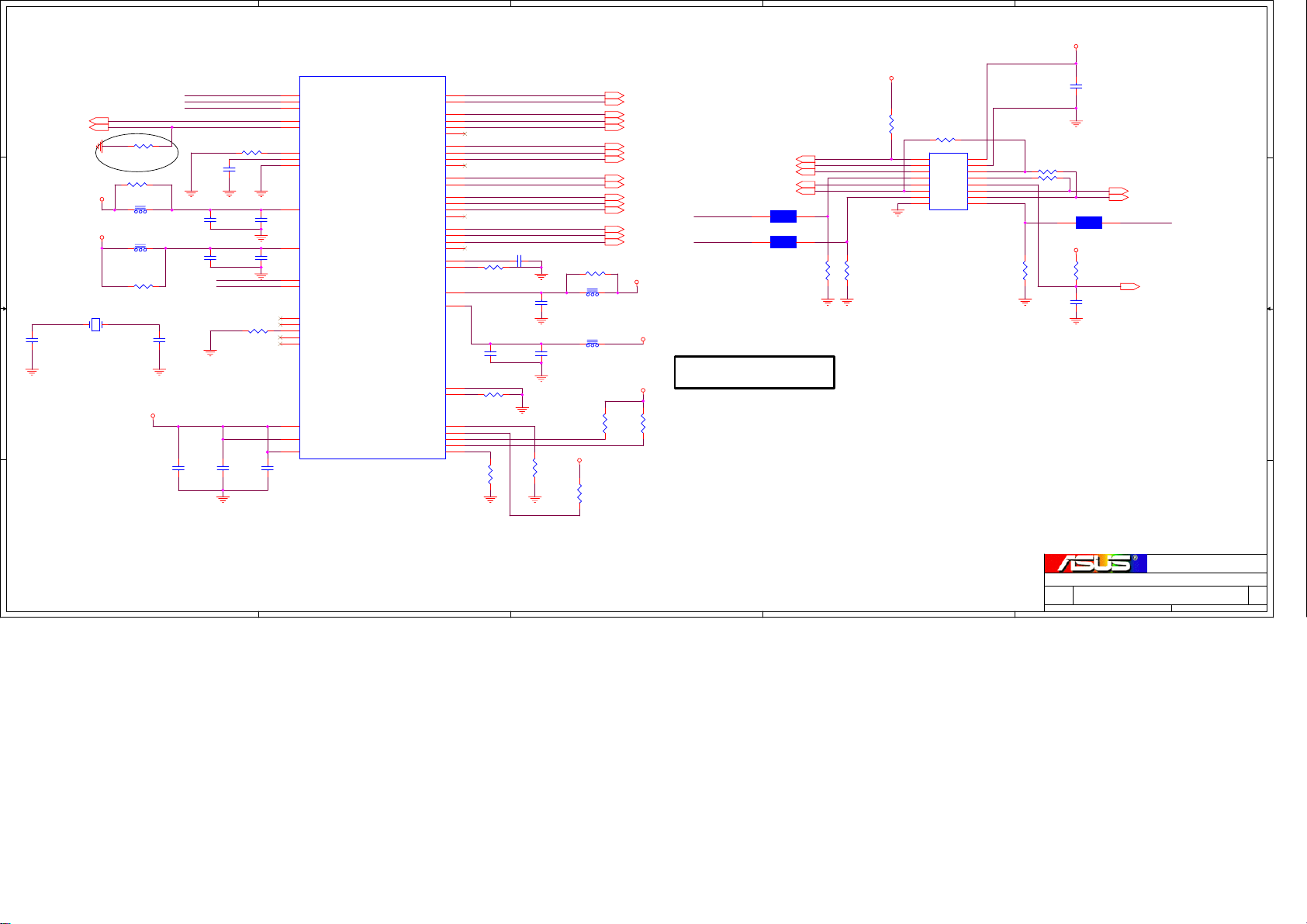

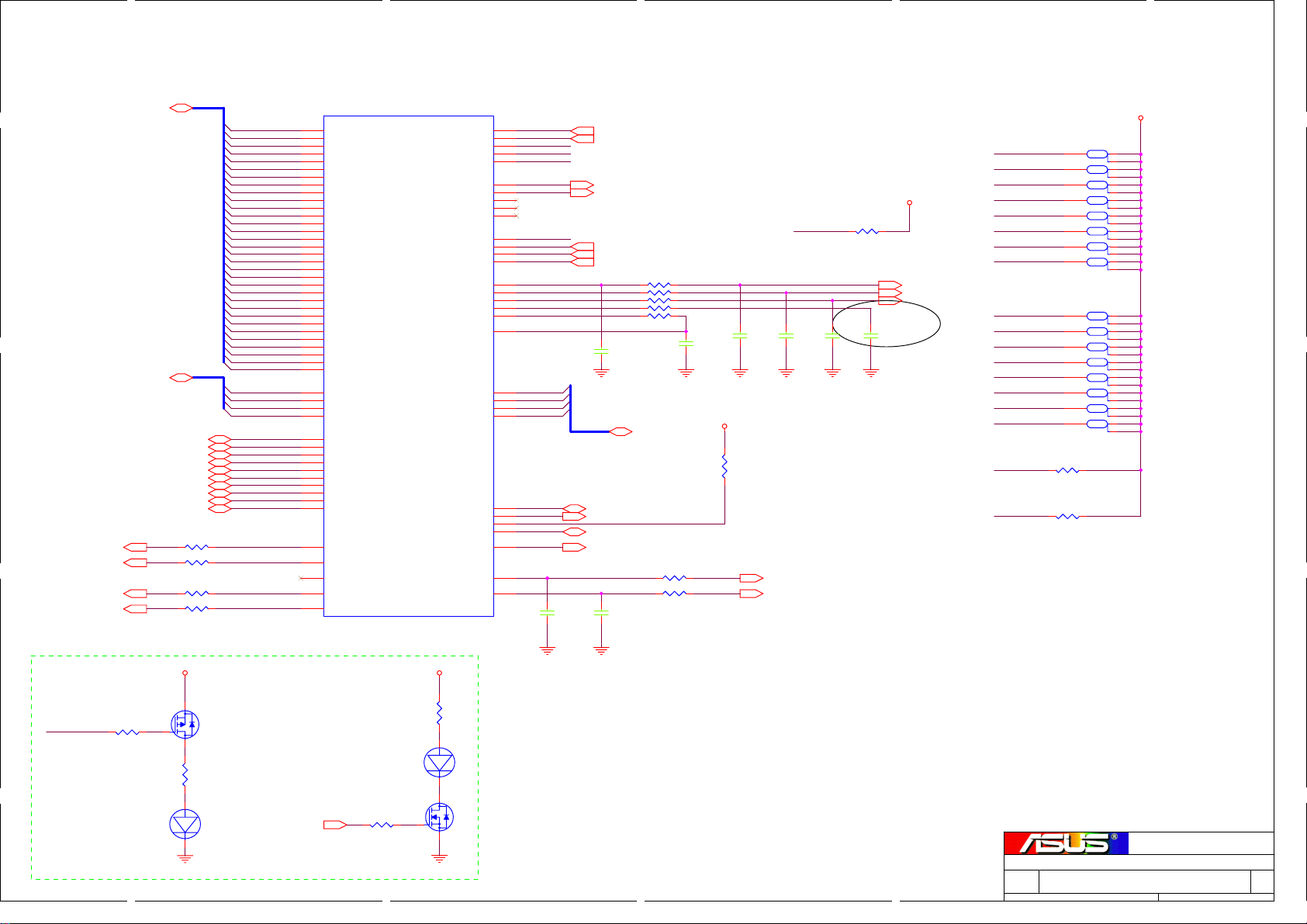

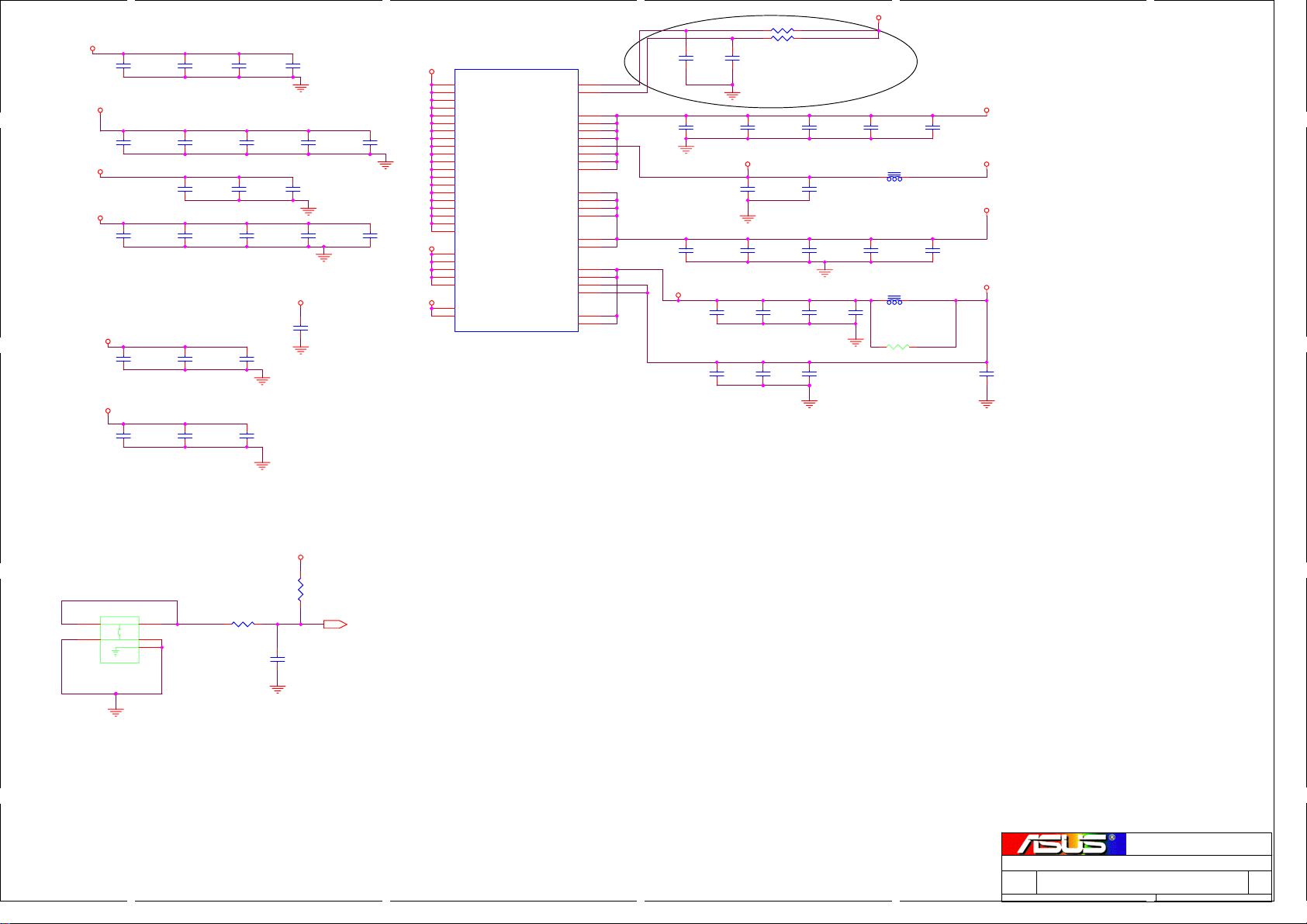

Page 4

5

A

4

3

2

1

HT_CPU_TX_CLK_H1[10]

D D

LAYOUT: PLACE NEAR CPU

STUFF WHEN CONFIGURED AS

16-BIT LINK

+1.2V_HT

R401 49.9Ohm

1 2

R402 49.9Ohm

1 2

HT_CPU_TX_CAD_L[0..15][10]

HT_CPU_TX_CAD_H[0..15][10]

HT_CPU_TX_CLK_L1[10]

HT_CPU_TX_CLK_H0[10]

HT_CPU_TX_CLK_L0[10]

HT_CPU_TX_CTL_H0[10]

HT_CPU_TX_CTL_L0[10]

C C

HT_CPU_TX_CLK_H1

HT_CPU_TX_CLK_L1

HT_CPU_TX_CLK_H0

HT_CPU_TX_CLK_L0

HT_CPU_TX_CTL_H1

HT_CPU_TX_CTL_L1

HT_CPU_TX_CTL_H0

HT_CPU_TX_CTL_L0

HT_CPU_TX_CAD_H15

HT_CPU_TX_CAD_L15

HT_CPU_TX_CAD_H14

HT_CPU_TX_CAD_L14

HT_CPU_TX_CAD_H13

HT_CPU_TX_CAD_L13

HT_CPU_TX_CAD_H12

HT_CPU_TX_CAD_L12

HT_CPU_TX_CAD_H11

HT_CPU_TX_CAD_L11

HT_CPU_TX_CAD_H10

HT_CPU_TX_CAD_L10

HT_CPU_TX_CAD_H9

HT_CPU_TX_CAD_L9

HT_CPU_TX_CAD_H8

HT_CPU_TX_CAD_L8

HT_CPU_TX_CAD_H7

HT_CPU_TX_CAD_L7

HT_CPU_TX_CAD_H6

HT_CPU_TX_CAD_L6

HT_CPU_TX_CAD_H5

HT_CPU_TX_CAD_L5

HT_CPU_TX_CAD_H4

HT_CPU_TX_CAD_L4

HT_CPU_TX_CAD_H3

HT_CPU_TX_CAD_L3

HT_CPU_TX_CAD_H2

HT_CPU_TX_CAD_L2

HT_CPU_TX_CAD_H1

HT_CPU_TX_CAD_L1

HT_CPU_TX_CAD_H0

HT_CPU_TX_CAD_L0

J5

K5

J3

J2

P3

P4

N1

P1

N5

P5

M3

M4

L5

M5

K3

K4

H3

H4

G5

H5

F3

F4

E5

F5

N3

N2

L1

M1

L3

L2

J1

K1

G1

H1

G3

G2

E1

F1

E3

E2

U1A

SOCKET638

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

HYPERTRANSPORT

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

HT_CPU_RX_CLK_H1

Y4

HT_CPU_RX_CLK_L1

Y3

HT_CPU_RX_CLK_H0

Y1

HT_CPU_RX_CLK_L0

W1

HT_CPU_RX_CTL_H1

T5

HT_CPU_RX_CTL_L1

R5

HT_CPU_RX_CTL_H0

R2

HT_CPU_RX_CTL_L0

R3

HT_CPU_RX_CAD_H15

T4

HT_CPU_RX_CAD_L15

T3

HT_CPU_RX_CAD_H14

V5

HT_CPU_RX_CAD_L14

U5

HT_CPU_RX_CAD_H13

V4

HT_CPU_RX_CAD_L13

V3

HT_CPU_RX_CAD_H12

Y5

HT_CPU_RX_CAD_L12

W5

HT_CPU_RX_CAD_H11

AB5

HT_CPU_RX_CAD_L11

AA5

HT_CPU_RX_CAD_H10

AB4

HT_CPU_RX_CAD_L10

AB3

HT_CPU_RX_CAD_H9

AD5

HT_CPU_RX_CAD_L9

AC5

HT_CPU_RX_CAD_H8

AD4

HT_CPU_RX_CAD_L8

AD3

HT_CPU_RX_CAD_H7

T1

HT_CPU_RX_CAD_L7

R1

HT_CPU_RX_CAD_H6

U2

HT_CPU_RX_CAD_L6

U3

HT_CPU_RX_CAD_H5

V1

HT_CPU_RX_CAD_L5

U1

HT_CPU_RX_CAD_H4

W2

HT_CPU_RX_CAD_L4

W3

HT_CPU_RX_CAD_H3

AA2

HT_CPU_RX_CAD_L3

AA3

HT_CPU_RX_CAD_H2

AB1

HT_CPU_RX_CAD_L2

AA1

HT_CPU_RX_CAD_H1

AC2

HT_CPU_RX_CAD_L1

AC3

HT_CPU_RX_CAD_H0

AD1

HT_CPU_RX_CAD_L0

AC1

HT_CPU_RX_CLK_H1 [10]

HT_CPU_RX_CLK_L1 [10]

HT_CPU_RX_CLK_H0 [10]

HT_CPU_RX_CLK_L0 [10]

T401 TPC26TN/A

1

T402 TPC26TN/A

1

HT_CPU_RX_CTL_H0 [10]

HT_CPU_RX_CTL_L0 [10]

HT_CPU_RX_CAD_L[0..15] [10]

HT_CPU_RX_CAD_H[0..15] [10]

Do not cross plane.

U1E

P20

RSVD_MA0_CLK_H3

P19

RSVD_MA0_CLK_L3

N20

RSVD_MA0_CLK_H0

N19

RSVD_MA0_CLK_L0

B B

R26

RSVD_MB0_CLK_H3

R25

RSVD_MB0_CLK_L3

P22

RSVD_MB0_CLK_H0

R22

RSVD_MB0_CLK_L0

SOCKET638

RSVD_MA_RESET_L

RSVD_MB_RESET_L

RSVD_VIDSTRB1

RSVD_VIDSTRB0

RSVD_VDDNB_FB_H

RSVD_VDDNB_FB_L

RSVD_CORE_TYPE

MISC

INTERNAL

FREE5

FREE6

FREE4

FREE1

FREE2

FREE3

H16

B18

B3

C1

H6

G6

D5

R24

W18

R23

AA8

H18

H19

A

final_1.00

Title :

ASUSTECH CO.,LTD.

Size Project Name

A3

5

4

3

2

Date: Sheet

A6T

Engineer:

1

S1_HT_C51

Jefing_Li

473Thursday, March 09, 2006

of

Rev

1.0

Page 5

5

A

4

3

2

1

C502

1.5PF/50V

C504

1.5PF/50V

MEM_MB0_CLK_H2

12

MEM_MB0_CLK_L2

MEM_MB0_CLK_H1

12

MEM_MB0_CLK_L1

U1C

AF18

MB0_CLK_H2

AF17

MB0_CLK_L2

A17

MB0_CLK_H1

A18

MB0_CLK_L1

Y26

MB0_CS_L3

J24

MB0_CS_L2

W24

MB0_CS_L1

U23

MB0_CS_L0

W23

MB0_ODT1

W26

MB0_ODT0

V26

MB_CAS_L

U22

MB_WE_L

U24

MB_RAS_L

K26

MB_BANK2

T26

MB_BANK1

U26

MB_BANK0

H26

MB_CKE1

J23

MB_CKE0

J25

MB_ADD15

J26

MB_ADD14

W25

MB_ADD13

L23

MB_ADD12

L25

MB_ADD11

U25

MB_ADD10

L24

MB_ADD9

M26

MB_ADD8

L26

MB_ADD7

N23

MB_ADD6

N24

MB_ADD5

N25

MB_ADD4

N26

MB_ADD3

P24

MB_ADD2

P26

MB_ADD1

T24

MB_ADD0

AF12

MB_DQS_H7

AE12

MB_DQS_L7

AE16

MB_DQS_H6

AD16

MB_DQS_L6

AF21

MB_DQS_H5

AF22

MB_DQS_L5

AC25

MB_DQS_H4

AC26

MB_DQS_L4

F26

MB_DQS_H3

E26

MB_DQS_L3

A24

MB_DQS_H2

A23

MB_DQS_L2

D16

MB_DQS_H1

C16

MB_DQS_L1

C12

MB_DQS_H0

B12

MB_DQS_L0

AD12

MB_DM7

AC16

MB_DM6

AE22

MB_DM5

AB26

MB_DM4

E25

MB_DM3

A22

MB_DM2

B16

MB_DM1

A12

MB_DM0

SOCKET638

MEMORY

INTERFACE

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

AD11

AF11

AF14

AE14

Y11

AB11

AC12

AF13

AF15

AF16

AC18

AF19

AD14

AC14

AE18

AD18

AD20

AC20

AF23

AF24

AF20

AE20

AD22

AC22

AE25

AD26

AA25

AA26

AE24

AD24

AA23

AA24

G24

G23

D26

C26

G26

G25

E24

E23

C24

B24

C20

B20

C25

D24

A21

D20

D18

C18

D14

C14

A20

A19

A16

A15

A13

D12

E11

G11

B14

A14

A11

C11

MEM_MB_DATA63

MEM_MB_DATA62MEM_MA0_CLK_L1

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41MEM_MB_ADD15

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MA0_CLK_H2

MEM_MA0_CLK_H2[8]

MEM_MA0_CLK_L2[8]

MEM_MA0_CLK_H1[8]

D D

C C

MEM_MA0_CLK_L1[8]

MEM_MA0_CS_L[0..3][8,9]

MEM_MA0_ODT[0..1][8,9]

MEM_MA_CAS_L[8,9]

MEM_MA_WE_L[8,9]

MEM_MA_RAS_L[8,9]

MEM_MA_BANK[0..2][8,9]

MEM_MA_CKE[0..1][8,9]

MEM_MA_ADD[0..15][8,9]

MEM_MA_DQS_H[0..7][8]

MEM_MA_DQS_L[0..7][8]

B B

MEM_MA_DM[0..7][8]

12

C501

MEM_MA0_CLK_L2

1.5PF/50V

MEM_MA0_CLK_H1

12

C503

MEM_MA0_CLK_L1

1.5PF/50V

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA0_CLK_H1

MEM_MA0_CS_L3

MEM_MA0_CS_L2

MEM_MA0_CS_L1

MEM_MA0_CS_L0

MEM_MA0_ODT1 MEM_MB_DATA55

MEM_MA0_ODT0 MEM_MB_DATA54

MEM_MA_CAS_L

MEM_MA_WE_L

MEM_MA_RAS_L

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_CKE1

MEM_MA_CKE0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

the cap close to cpu less than 1200mil

max neckdown to & from caps is 500mil

U1B

Y16

MA0_CLK_H2

AA16

MA0_CLK_L2

M19

M20

M24

M22

N22

N21

R21

W12

W13

W15

AB19

AB20

AD23

AC23

G22

G21

C22

C21

G16

G15

G13

H13

AB16

AC24

E19

C15

E12

E16

F16

V19

J22

V22

T19

V20

U19

U20

U21

T20

K22

R20

T22

J20

J21

K19

K20

V24

K24

L20

R19

L19

L22

L21

Y15

Y13

Y19

F24

MA0_CLK_H1

MA0_CLK_L1

MA0_CS_L3

MA0_CS_L2

MA0_CS_L1

MA0_CS_L0

MA0_ODT1

MA0_ODT0

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK2

MA_BANK1

MA_BANK0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

SOCKET638

MEMORY

INTERFACE

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

AA12

MEM_MA_DATA62

AB12

MEM_MA_DATA61

AA14

MEM_MA_DATA60

AB14

MEM_MA_DATA59

W11

MEM_MA_DATA58

Y12

MEM_MA_DATA57

AD13

MEM_MA_DATA56

AB13

MEM_MA_DATA55

AD15

MEM_MA_DATA54

AB15

MEM_MA_DATA53

AB17

MEM_MA_DATA52

Y17

MEM_MA_DATA51

Y14

MEM_MA_DATA50

W14

MEM_MA_DATA49

W16

MEM_MA_DATA48 MEM_MB_BANK2

AD17

MEM_MA_DATA47

Y18

MEM_MA_DATA46

AD19

MEM_MA_DATA45

AD21

MEM_MA_DATA44

AB21

MEM_MA_DATA43

AB18

MEM_MA_DATA42

AA18

MEM_MA_DATA41

AA20

MEM_MA_DATA40

Y20

AA22

MEM_MA_DATA38

Y22

MEM_MA_DATA37

W21

MEM_MA_DATA36

W22

MEM_MA_DATA35

AA21

MEM_MA_DATA34

AB22

MEM_MA_DATA33

AB24

MEM_MA_DATA32

Y24

MEM_MA_DATA31

H22

H20

MEM_MA_DATA29

E22

MEM_MA_DATA28

E21

MEM_MA_DATA27

J19

MEM_MA_DATA26

H24

MEM_MA_DATA25

F22

MEM_MA_DATA24

F20

MEM_MA_DATA23

C23

MEM_MA_DATA22

B22

MEM_MA_DATA21

F18

MEM_MA_DATA20

E18

MEM_MA_DATA19

E20

MEM_MA_DATA18

D22

MEM_MA_DATA17

C19

MEM_MA_DATA16

G18

MEM_MA_DATA15

G17

MEM_MA_DATA14

C17

MEM_MA_DATA13

F14

MEM_MA_DATA12

E14

MEM_MA_DATA11

H17

MEM_MA_DATA10

E17

MEM_MA_DATA9

E15

MEM_MA_DATA8

H15

MEM_MA_DATA7

E13

MEM_MA_DATA6

C13

MEM_MA_DATA5

H12

MEM_MA_DATA4

H11

MEM_MA_DATA3

G14

MEM_MA_DATA2

H14

MEM_MA_DATA1

F12

MEM_MA_DATA0

G12

MEM_MA_DATA[0..63] [8] MEM_MB_DATA[0..63] [8]

MEM_MB0_CS_L[0..3][8,9]

MEM_MB0_ODT[0..1][8,9]

MEM_MB_CAS_L[8,9]

MEM_MB_WE_L[8,9]

MEM_MB_RAS_L[8,9]

MEM_MB_BANK[0..2][8,9]

MEM_MB_CKE[0..1][8,9]

MEM_MB_ADD[0..15][8,9]

MEM_MB_DQS_H[0..7][8]

MEM_MB_DQS_L[0..7][8]

MEM_MB_DM[0..7][8]

MEM_MB0_CLK_H2[8]

MEM_MB0_CLK_L2[8]

MEM_MB0_CLK_H1[8]

MEM_MB0_CLK_L1[8]

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB0_CLK_H1MEM_MA_DATA63

MEM_MB0_CLK_L1

MEM_MB0_CS_L3

MEM_MB0_CS_L2

MEM_MB0_CS_L1

MEM_MB0_CS_L0

MEM_MB0_ODT1

MEM_MB0_ODT0

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_RAS_L

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB_CKE1

MEM_MB_CKE0

MEM_MB_ADD14

MEM_MB_ADD13MEM_MA_DATA39

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4MEM_MA_DATA30

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

A

final_1.00

Title :

ASUSTECH CO.,LTD.

Size Project Name

A3

5

4

3

2

Date: Sheet

A6T

Engineer:

S1_DDR2

Jefing_Li

573Thursday, March 09, 2006

Rev

1.0

of

1

Page 6

5

A

+2.5VS

R601

1KOhm

1 2

CPU_PWROK[10]

1 2

147

U2A

VCC

GND

SN74LVC07APWR

+1.8V

R602 300Ohm

_CPU_PWROK

1 2

D D

+1.8V+3VSUS+2.5VS

147

U2B

VCC

3 4

GND

SN74LVC07APWR

147

U2C

VCC

GND

SN74LVC07APWR

+3VSUS

147

VCC

9 8

GND

147

U2E

VCC

GND

SN74LVC07APWR

R604 300Ohm

1 2

+1.8V+3VSUS

R610 300Ohm

_CPU_RESET#

1 2

+3VS

U2D

SN74LVC07APWR

+3VSUS

R7119 0Ohm

1 2

_CPU_LDTSTOP#

R629

1KOhm

/X

1 2

_PWROK

_CPU_PWROK

R7113

0Ohm

1 2

147

U2F

VCC

13 12

GND

SN74LVC07APWR

R7117 0Ohm

1 2

R603

1KOhm

/X

_PWROK

+2.5VS

1 2

1 2

R7114

0Ohm

/X

_PWROK

1 2

R609

1KOhm

5 6

11 10

CPU_LDTSTOP#[10]

CPU_RESET#[10]

C C

3/1

HT_VLD

_HT_MCP_PWRGD[16]

R7115 0Ohm

1 2

R7150 0Ohm

1 2

HT_VLD[16,64]

_HT_MCP_PWRGD

CPU_CLK_H[10]

CPU_CLK_L[10]

CPU_VDD_FB[61]

CPU_VDD_FB#[61]

Keep trace to

resistors less

than 1.5" from

CPU pin

_CPU_LDTSTOP#

4

+2.5VS +2.5V_VDDA+3VSUS

C601

12

100UF/6.3V

close to the ferrite bead

Keep trace to resistors

less than 600mils from

CPU pin and trace to AC

caps less than 1250mils

CPU_CLK_H

CPU_CLK_L

Not use,

pull up.

C606

12

3900PF/50V

C607

12

3900PF/50V

R607 300Ohm

route as diff

pair

5/5/5,10mil

+1.8V

R612 39.2Ohm

1 2

R615 39.2Ohm

1 2

R616 300Ohm

1 2

R618 300Ohm

1 2

CPU_THERMADC[15]

CPU_THERMADA[15]

169Ohm

4.7UF/6.3V

R605

12

30Ohm/100Mhz

T614 TPC26TN/A

T616 TPC26TN/A

T618 TPC26TN/A

T619 TPC26TN/A

T621 TPC26TN/A

L601

21

12

C602

0.22UF/6.3V

1 2

_CPU_PWROK

_CPU_LDTSTOP#

_CPU_RESET#

CPU_PRESENT#

CPU_SIC

CPU_TDI

CPU_TRST#

CPU_TCK

CPU_TMS

CPU_DBREQ#

CPU_VCORE_FB_H

CPU_VCORE_FB_L

CPU_VTT_SENSE

CPU_M_VREF

CPU_TEST25_H

CPU_TEST25_L

1

1

1

1

1

CPU_THERMADC

CPU_THERMADA

12

C603

+2.5V_VDDA

12

C604

3300PF/50V

Need decoupling

capacitors

U1D

F8

VDDA1

F9

VDDA2

A9

CLKIN_H

A8

CLKIN_L

A7

PWROK

F10

LDTSTOP_L

B7

RESET_L

AC6

CPU_PRESENT_L

AF4

SIC

AF5

SID

AF9

TDI

AD9

TRST_L

AC9

TCK

AA9

TMS

E10

DBREQ_L

F6

VDD_FB_H

E6

VDD_FB_L

Y10

VTT_SENSE

W17

M_VREF

AE10

M_ZN

AF10

M_ZP

E9

TEST25_H

E8

TEST25_L

G9

TEST19

H10

TEST18

AA7

TEST13

C2

TEST9

D7

TEST17

E7

TEST16

F7

TEST15

C7

TEST14

AC8

TEST12

C3

TEST7

AA6

TEST6

W7

THERMDC

W8

THERMDA

Y6

TEST3

AB6

TEST2

SOCKET638

3

THERMTRIP_L

PROCHOT_L

MISC

VDDIO_FB_H

VDDIO_FB_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

0.1UF/10V

VID5

VID4

VID3

VID2

VID1

VID0

TDO

DBRDY

PSI_L

TEST8

C605

+1.8V

12

A5

C6

A6

A4

C5

B5

AF6

AC7

AE9

G10

W9

Y9

A3

P6

R6

C9

C8

AE7

AD7

AE8

AB8

AF7

J7

H8

AF8

AE6

K8

C4

2

VDDIO +1.8V

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

+1.8V

Required for

R606

compatibility

with future

300Ohm

processors

1 2

CPU_VID5

CPU_VID4

CPU_VID3

CPU_VID2

CPU_VID1

CPU_VID0

_CPU_THERMTRIP#

_CPU_PROCHOT# +1.8V_DRAM_FB

CPU_TDO

CPU_DBRDY

+1.8V_DRAM_FB

+1.8V_DRAM_FB#

CPU_PSI#

CPU_TEST29_H

CPU_TEST29_L

T613 TPC26TN/A

T615 TPC26TN/A

T617 TPC26TN/A

CPU_TEST21

T620 TPC26TN/A

CPU_TEST26

R611 44.2Ohm

R613 44.2Ohm

1 2

1 2

1

1

1

1

CPU_PSI# [61]

R617

80.6Ohm

CPU_VID[0..5] [61]

_CPU_THERMTRIP# [9]

_CPU_PROCHOT# [9]

+1.2V_HT

Route as 80Ohm

differential

impedance.

Keep trace to

resistors less

1 2

than 1" from

CPU pin

Keep trace to

resistors less

than 1.5" from

CPU pin

+1.8V

CPU_VTT_SENSE

Erratum 133,

Revision Guide

for AMD NPT

0Fh Processors

CPU_TEST26

CPU_PRESENT#

CPU_TEST25_H

CPU_TEST25_L

CPU_TEST21

P601

1

NC

3

DBREQ_L1

5

DBRDY1

7

DBREQ_L2

9

DBRDY2

11

DBREQ_L3

13

DBRDY3

15

DBREQ_L4

17

DBRDY4

19

DBREQ_L5

DBREQ_L7

21

DBRDY5

23

DBREQ_L6

ASP_68200_07_K25

/X

CPU_CLK_H

CPU_CLK_L

CPU_VCORE_FB_H

CPU_VCORE_FB_L

CPU_TEST29_H

CPU_TEST29_L

+1.8V_DRAM_FB#

_CPU_PWROK

_CPU_LDTSTOP#

_CPU_RESET#

_CPU_THERMTRIP#

1 2

R619 300Ohm

1 2

R620 1KOhm

1 2

R621 510Ohm

1 2

R622 510Ohm

1 2

R623 300Ohm

1 2

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

DBRDY7

DBRDY6

GND9

GND10

T601 TPC26TN/A

T602 TPC26TN/A

T603 TPC26TN/A

T604 TPC26TN/A

T605 TPC26TN/A

T606 TPC26TN/A

T607 TPC26TN/A

T608 TPC26TN/A

T609 TPC26TN/A

T610 TPC26TN/A

T611 TPC26TN/A

T612 TPC26TN/A

R614

0Ohm /x

1

2

4

6

8

10

12

14

16

18

20

22

H_CPU_RESET#

24

26

1

1

1

1

1

1

1

1

1

1

1

1

+0.9V

+1.8V

R634

8.2KOhm

Q601A

UM6K1N

2

3/1

+3VS

12

H_CPU_RESET#

61

3/1

+1.8V

CPU_M_VREF

15mil trace.20mil space

R624

2KOhm

shorter than 6 inches

1%

R628

2KOhm

CPU_M_VREF

12

12

C608

C609

1000PF/50V

1%

0.1UF/10V

final_1.00

Title :

S1_CNTL/DEBUG/THERM

ASUSTECH CO.,LTD.

Size Project Name

C

3

2

Date: Sheet

Engineer:

A6T

Jefing_Li

Rev

1.0

of

673Thursday, March 09, 2006

1

1 2

1 2

4

B B

12

R633

8.2KOhm

34

Q601B

UM6K1N

CPU_RESET#

5

GND

5

A

Page 7

5

A

4

3

2

1

DRAM_VTT 0.9V

+VCORE

+VCORE

D D

C C

+VCORE

12

C701

22UF/6.3V

C735

22UF/6.3V

AC4

AD2

K10

K12

K14

L11

L13

M10

N11

P10

R11

T10

T12

T14

U11

U13

V10

V12

V14

12

G4

H2

J9

J11

J13

K6

L4

L7

L9

M2

M6

M8

N7

N9

P8

R4

R7

R9

T2

T6

T8

U7

U9

V6

V8

W4

Y2

22UF/6.3V

U1F

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

SOCKET638

C736

AA4

VSS1

AA11

VSS2

AA13

VSS3

AA15

VSS4

AA17

VSS5

AA19

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

AB23

VSS10

AB25

VSS11

AC11

VSS12

AC13

VSS13

AC15

VSS14

AC17

VSS15

AC19

VSS16

AC21

VSS17

AD6

VSS18

AD8

VSS19

AD25

VSS20

AE11

VSS21

VDD

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

AE13

AE15

AE17

AE19

AE21

AE23

B4

B6

B8

B9

B11

B13

B15

B17

B19

B21

B23

B25

D6

D8

D9

D11

D13

D15

D17

place under socket on bottom side

12

C737

22UF/6.3V

12

C738

22UF/6.3V

12

C739

22UF/6.3V

+1.8V

12

+1.2V_HT

+0.9V

D10

C10

B10

AD10

W10

H25

K18

K21

K23

K25

M18

M21

M23

M25

N17

P18

P21

P23

P25

R17

T18

T21

T23

T25

U17

V18

V21

V23

V25

Y25

D4

D3

D2

D1

J17

L17

U1H

VLDT_A4

VLDT_A3

VLDT_A2

VLDT_A1

VTT8

VTT7

VTT6

VTT5

VTT9

VDDIO23

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO24

VDDIO25

VDDIO26

VDDIO27

SOCKET638

I O

POWER

VLDT_B4

VLDT_B3

VLDT_B2

VLDT_B1

VTT4

VTT3

VTT2

VTT1

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

AE5

AE4

AE3

AE2

AC10

AB10

AA10

A10

D19

D21

D23

D25

E4

F2

F11

F13

F15

F17

F19

F21

F23

F25

H7

H9

H21

H23

J4

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

M11

4.7UF/16V

C706

+0.9V

12

J15

K16

L15

M16

P16

T16

U15

V16

U1G

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD

SOCKET638

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS130

VSS131

VSS132

VSS133

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

+1.8V

+1.8V

+1.8V

+1.8V

place close to socket

C702

0.22UF/6.3V

C707

4.7UF/6.3V

C711

0.01UF/10V

12

12

12

C703

0.22UF/6.3V

C708

4.7UF/6.3V

C712

0.01UF/10V

12

12

12

C704

0.22UF/6.3V

C709

4.7UF/6.3V

C713

180PF/50V

12

12

12

0.22UF/6.3V

4.7UF/6.3V

place under socket on bottom side

C715

22UF/6.3V

+0.9V

4.7UF/6.3V

+0.9V

0.22UF/6.3V

+0.9V

1000PF/50V

+0.9V

180PF/50V

C719

C723

C727

C731

12

C716

22UF/6.3V

12

4.7UF/6.3V

12

0.22UF/6.3V

12

1000PF/50V

12

12

C720

C724

C728

C732

180PF/50V

12

C717

0.22UF/6.3V

place close to socket

12

12

12

12

0.22UF/6.3V

C721

4.7UF/6.3V

C725

0.22UF/6.3V

C729

1000PF/50V

C733

180PF/50V

C718

12

12

12

12

4.7UF/6.3V

0.22UF/6.3V

1000PF/50V

C705

C710

C714

180PF/50V

12

C722

C726

C730

C734

180PF/50V

12

12

12

12

12

12

12

B B

+VCORE

C743

22UF/6.3V

12

C744

22UF/6.3V

5

12

C745

22UF/6.3V

12

C746

0.22UF/6.3V

12

0.22UF/6.3V

C747

12

0.01UF/10V

C748

12

180PF/50V

4

C749

12

3

C740

4.7UF/6.3V

+1.2V_HT

0.22UF/6.3V

2

C750

+1.2V_HT

12

12

C751

0.22UF/6.3V

+1.2V_HT

4.7UF/6.3V

12

final_1.00

place close to socket

12

C741

12

C752

180PF/50V

C742

4.7UF/6.3V

180PF/50V

C753

12

12

Title :

ASUSTECH CO.,LTD.

Size Project Name

A3

Date: Sheet

A6T

Engineer:

1

S1_POWER

Jefing_Li

773Monday, March 06, 2006

of

Rev

1.0

A

Page 8

5

A

4

3

2

1

MEM_MA_DATA[0..63] [5]

MEM_MA_ADD[0..15][5,9]

D D

MEM_MA_BANK2[5,9]

MEM_MA_BANK0[5,9]

MEM_MA_BANK1[5,9]

MEM_MA0_CS_L0[5,9]

MEM_MA0_CS_L1[5,9]

MEM_MA0_CLK_H1[5]

MEM_MA0_CLK_L1[5]

MEM_MA0_CLK_H2[5]

MEM_MA0_CLK_L2[5]

MEM_MA_CKE0[5,9]

MEM_MA_CKE1[5,9]

MEM_MA_CAS_L[5,9]

MEM_MA_RAS_L[5,9]

MEM_MA_WE_L[5,9]

MEM_MA0_ODT0[5,9]

MEM_MA0_ODT1[5,9]

C C

MEM_MA_DM[0..7][5]

MEM_MA_DQS_H[0..7][5]

MEM_MA_DQS_L[0..7][5]

+1.8V

12

12

C801

4.7UF/6.3V

B B

+1.8V

12

C813

10UF/10V

C802

4.7UF/6.3V

12

0.1UF/10V

C814

12

C803

1UF/16V

12

0.1UF/10V

12

C815

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3 MEM_MB_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

I2C_CLK0_S[15,19]

I2C_DATA0_S[15,19]

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_DQS_H0

MEM_MA_DQS_H1

MEM_MA_DQS_H2

MEM_MA_DQS_H3

MEM_MA_DQS_H4

MEM_MA_DQS_H5

MEM_MA_DQS_H6

MEM_MA_DQS_H7

MEM_MA_DQS_L0

MEM_MA_DQS_L1

MEM_MA_DQS_L2

MEM_MA_DQS_L3

MEM_MA_DQS_L4

MEM_MA_DQS_L5

MEM_MA_DQS_L6

MEM_MA_DQS_L7

+3VS

MEM_M_VREF

C812

12

12

+1.8V

12

1KOhm

1KOhm

0.1UF/10V

C804

1UF/16V

12

0.1UF/10V

C816

R801

R804

12

C805

1UF/16V

CON1A

A102

A:A0

A101

A:A1

A100

A:A2

A99

A:A3

A98

A:A4

A97

A:A5

A94

A:A6

A92

A:A7

A93

A:A8

A91

A:A9

A105

A:A10/AP

A90

A:A11

A89

A:A12

A116

A:A13

A86

A:A14

A84

A:A15

A85

A:A16_BA2

A107

A:BA0

A106

A:BA1

A110

A:S0#

A115

A:S1#

A30

A:CK0

A32

A:CK0#

A164

A:CK1

A166

A:CK1#

A79

A:CKE0

A80

A:CKE1

A113

A:CAS#

A108

A:RAS#

A109

A:WE#

A198

A:SA0

A200

A:SA1

A197

A:SCL

A195

A:SDA

A114

A:ODT0

A119

A:ODT1

A10

A:DM0

A26

A:DM1

A52

A:DM2

A67

A:DM3

A130

A:DM4

A147

A:DM5

A170

A:DM6

A185

A:DM7

A13

A:DQS0

A31

A:DQS1

A51

A:DQS2

A70

A:DQS3

A131

A:DQS4

A148

A:DQS5

A169

A:DQS6

A188

A:DQS7

A11

A:DQS0#

A29

A:DQS1#

A49

A:DQS2#

A68

A:DQS3#

A129

A:DQS4#

A146

A:DQS5#

A167

A:DQS6#

A186

A:DQS7#

A112

A:VDD1

A96

A:VDD4

A118

A:VDD6

A82

A:VDD8

A88

A:VDD11

A104

A:VDD12

A12

A:VSS5

A48

A:VSS6

A184

A:VSS7

A78

A:VSS8

A72

A:VSS10

A122

A:VSS12

A196

A:VSS13

A8

A:VSS15

A18

A:VSS16

A24

A:VSS17

A42

A:VSS20

A199

A:VDDSPD

A1

A:VREF

DDR_DIMM_331P

MEM_MA_DATA3

A5

A:DQ0

MEM_MA_DATA7

A7

A:DQ1

MEM_MA_DATA5

A17

A:DQ2

MEM_MA_DATA2

A19

A:DQ3

MEM_MA_DATA0

A4

A:DQ4

MEM_MA_DATA6

A6

A:DQ5

MEM_MA_DATA4

A14

A:DQ6

MEM_MA_DATA1

A16

A:DQ7

MEM_MA_DATA8

A23

A:DQ8

MEM_MA_DATA9

A25

A:DQ9

MEM_MA_DATA15

A35

A:DQ10

MEM_MA_DATA11

A37

A:DQ11

MEM_MA_DATA12

A20

A:DQ12

MEM_MA_DATA13

A22

A:DQ13

MEM_MA_DATA14

A36

A:DQ14

MEM_MA_DATA10

A38

A:DQ15

MEM_MA_DATA23

A43

A:DQ16

MEM_MA_DATA22

A45

A:DQ17

MEM_MA_DATA19

A55

A:DQ18

MEM_MA_DATA18

A57

A:DQ19

MEM_MA_DATA17

A44

A:DQ20

MEM_MA_DATA20

A46

A:DQ21

MEM_MA_DATA16

A56

A:DQ22

MEM_MA_DATA21

A58

A:DQ23

MEM_MA_DATA24

A61

A:DQ24

MEM_MA_DATA25

A63

A:DQ25

MEM_MA_DATA26

A73

A:DQ26

MEM_MA_DATA31

A75

A:DQ27

MEM_MA_DATA28

A62

A:DQ28

MEM_MA_DATA29

A64

A:DQ29

MEM_MA_DATA30

A74

A:DQ30

MEM_MA_DATA27

A76

A:DQ31

MEM_MA_DATA36

A123

A:DQ32

MEM_MA_DATA38

A125

A:DQ33

MEM_MA_DATA34

A135

A:DQ34

MEM_MA_DATA35

A137

A:DQ35

MEM_MA_DATA33

A124

A:DQ36

MEM_MA_DATA32

A126

A:DQ37

MEM_MA_DATA39

A134

A:DQ38

MEM_MA_DATA37

A136

A:DQ39

MEM_MA_DATA45

A141

A:DQ40

MEM_MA_DATA44

A143

A:DQ41

MEM_MA_DATA47

A151

A:DQ42

MEM_MA_DATA46

A153

A:DQ43

MEM_MA_DATA40

A140

A:DQ44

MEM_MA_DATA41

A142

A:DQ45

MEM_MA_DATA42

A152

A:DQ46

MEM_MA_DATA43

A154

A:DQ47

MEM_MA_DATA48

A157

A:DQ48

MEM_MA_DATA53

A159

A:DQ49

MEM_MA_DATA50

A173

A:DQ50

MEM_MA_DATA51

A175

A:DQ51

MEM_MA_DATA49

A158

A:DQ52

MEM_MA_DATA52

A160

A:DQ53

MEM_MA_DATA55

A174

A:DQ54

MEM_MA_DATA54

A176

A:DQ55

MEM_MA_DATA57

A179

A:DQ56

MEM_MA_DATA56

A181

A:DQ57

MEM_MA_DATA62

A189

A:DQ58

MEM_MA_DATA58

A191

A:DQ59

MEM_MA_DATA60

A180

A:DQ60

MEM_MA_DATA61

A182

A:DQ61

MEM_MA_DATA63

A192

A:DQ62

MEM_MA_DATA59

A194

A:DQ63

A54

A:VSS21

A60

A:VSS24

A66

A:VSS25

A128

A:VSS28

A172

A:VSS32

A178

A:VSS35

A190

A:VSS36

A34

A:VSS41

A132

A:VSS42

A144

A:VSS43

A156

A:VSS44

A168

A:VSS45

A2

A:VSS46

A28

A:VSS53

A40

A:VSS54

A138

A:VSS55

A150

A:VSS56

A162

A:VSS57

A83

A:NC1

A120

A:NC2

A50

A:NC3

A69

A:NC4

A163

NP_NC1

201

202

A:NCTEST

NP_NC2

NP_NC3

NP_NC4

GND1

GND2

GND4

GND3

203

204

205

206

207

208

MEM_MA0_CS_L2 [5,9]

MEM_MA0_CS_L3 [5,9]

4.7UF/6.3V

+3VS

C806

+1.8V

+1.8V

12

12

C817

10UF/10V

MEM_MB_ADD[0..15][5,9]

MEM_MB_DM[0..7][5]

MEM_MB_DQS_H[0..7][5]

MEM_MB_DQS_L[0..7][5]

12

C807

4.7UF/6.3V

12

0.1UF/10V

C818

1KOhm

1KOhm

B102

B101

B100

B99

B98

B97

B94

B92

B93

B91

B105

B90

B89

B116

B86

B84

B85

B107

B106

B110

B115

B30

B32

B164

B166

B79

B80

B113

B108

B109

B198

B200

B197

B195

B114

B119

B10

B26

B52

B67

B130

B147

B170

B185

B13

B31

B51

B70

B131

B148

B169

B188

B11

B29

B49

B68

B129

B146

B167

B186

B111

B117

B95

B81

B87

B103

B47

B133

B183

B77

B71

B121

B193

B41

B53

B59

B65

B199

B1

CON1B

B:A0

B:A1

B:A2

B:A3

B:A4

B:A5

B:A6

B:A7

B:A8

B:A9

B:A10/AP

B:A11

B:A12

B:A13

B:A14

B:A15

B:A16_BA2

B:BA0

B:BA1

B:S0#

B:S1#

B:CK0

B:CK0#

B:CK1

B:CK1#

B:CKE0

B:CKE1

B:CBS#

B:RAS#

B:WE#

B:SA0

B:SA1

B:SCL

B:SDA

B:ODT0

B:ODT1

B:DM0

B:DM1

B:DM2

B:DM3

B:DM4

B:DM5

B:DM6

B:DM7

B:DQS0

B:DQS1

B:DQS2

B:DQS3

B:DQS4

B:DQS5

B:DQS6

B:DQS7

B:DQS0#

B:DQS1#

B:DQS2#

B:DQS3#

B:DQS4#

B:DQS5#

B:DQS6#

B:DQS7#

B:VDD2

B:VDD3

B:VDD5

B:VDD7

B:VDD9

B:VDD10

B:VSS1

B:VSS2

B:VSS3

B:VSS4

B:VSS9

B:VSS11

B:VSS14

B:VSS18

B:VSS19

B:VSS22

B:VSS23

B:VDDSPD

B:VREF

DDR_DIMM_331P

B:DQ0

B:DQ1

B:DQ2

B:DQ3

B:DQ4

B:DQ5

B:DQ6

B:DQ7

B:DQ8

B:DQ9

B:DQ10

B:DQ11

B:DQ12

B:DQ13

B:DQ14

B:DQ15

B:DQ16

B:DQ17

B:DQ18

B:DQ19

B:DQ20

B:DQ21

B:DQ22

B:DQ23

B:DQ24

B:DQ25

B:DQ26

B:DQ27

B:DQ28

B:DQ29

B:DQ30

B:DQ31

B:DQ32

B:DQ33

B:DQ34

B:DQ35

B:DQ36

B:DQ37

B:DQ38

B:DQ39

B:DQ40

B:DQ41

B:DQ42

B:DQ43

B:DQ44

B:DQ45

B:DQ46

B:DQ47

B:DQ48

B:DQ49

B:DQ50

B:DQ51

B:DQ52

B:DQ53

B:DQ54

B:DQ55

B:DQ56

B:DQ57

B:DQ58

B:DQ59

B:DQ60

B:DQ61

B:DQ62

B:DQ63

B:VSS26

B:VSS27

B:VSS29

B:VSS30

B:VSS31

B:VSS33

B:VSS34

B:VSS37

B:VSS38

B:VSS39

B:VSS40

B:VSS47

B:VSS48

B:VSS49

B:VSS50

B:VSS51

B:VSS52

B:NC1

B:NC2

B:NC3

B:NC4

B:NCTEST

B5

B7

B17

B19

B4

B6

B14

B16

B23

B25

B35

B37

B20

B22

B36

B38

B43

B45

B55

B57

B44

B46

B56

B58

B61

B63

B73

B75

B62

B64

B74

B76

B123

B125

B135

B137

B124

B126

B134

B136

B141

B143

B151

B153

B140

B142

B152

B154

B157

B159

B173

B175

B158

B160

B174

B176

B179

B181

B189

B191

B180

B182

B192

B194

B127

B139

B145

B165

B171

B177

B187

B9

B21

B33

B155

B3

B15

B27

B39

B149

B161

B83

B120

B50

B69

B163

MEM_MB_DATA5

MEM_MB_DATA7

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_DATA6

MEM_MB_DATA4

MEM_MB_DATA13

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA8

MEM_MB_DATA12

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA22

MEM_MB_DATA20

MEM_MB_DATA18

MEM_MB_DATA16

MEM_MB_DATA21

MEM_MB_DATA17

MEM_MB_DATA19

MEM_MB_DATA23

MEM_MB_DATA29

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA24

MEM_MB_DATA28

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA44

MEM_MB_DATA40

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA41

MEM_MB_DATA45

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA57

MEM_MB_DATA63

MEM_MB_DATA56

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_BANK2[5,9]

MEM_MB_BANK0[5,9]

MEM_MB_BANK1[5,9]

MEM_MB0_CS_L0[5,9]

MEM_MB0_CS_L1[5,9]

MEM_MB0_CLK_H1[5]

MEM_MB0_CLK_L1[5]

MEM_MB0_CLK_H2[5]

MEM_MB0_CLK_L2[5]

MEM_MB_CKE0[5,9]

MEM_MB_CKE1[5,9]

MEM_MB_CAS_L[5,9]

MEM_MB_RAS_L[5,9]

MEM_MB_WE_L[5,9]

MEM_MB0_ODT0[5,9]

MEM_MB0_ODT1[5,9]

12

C808

1UF/16V

12

C819

0.1UF/10V

MEM_MB_ADD15

R802

12

R803

12

I2C_CLK0_S

I2C_DATA0_S

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

MEM_MB_DQS_H0

MEM_MB_DQS_H1

MEM_MB_DQS_H2

MEM_MB_DQS_H3

MEM_MB_DQS_H4

MEM_MB_DQS_H5

MEM_MB_DQS_H6

MEM_MB_DQS_H7

MEM_MB_DQS_L0

MEM_MB_DQS_L1

MEM_MB_DQS_L2

MEM_MB_DQS_L3

MEM_MB_DQS_L4

MEM_MB_DQS_L5

MEM_MB_DQS_L6

MEM_MB_DQS_L7 MEM_MB_DATA62

+1.8V

12

12

C809

C810

1UF/16V

1UF/16V

+3VS

MEM_M_VREF

12

C811

0.1UF/10V

12

C820

0.1UF/10V

MEM_MB_DATA[0..63] [5]

MEM_MB0_CS_L2 [5,9]

MEM_MB0_CS_L3 [5,9]

MEM_M_VREF

+1.8V

15mil trace.20mil space

shorter than 6 inches

R805

2KOhm

1%

1 2

1 2

5

R806

2KOhm

1%

12

C821

0.1UF/10V

1000PF/50V

C822

MEM_M_VREF

12

A

final_1.00

Title :

DDR2_SODIMM

ASUSTECH CO.,LTD.

Size Project Name

C

4

3

2

Date: Sheet

Engineer:

A6T

1

Jefing_Li

873Thursday, March 09, 2006

Rev

1.0

of

Page 9

A

DDR2 TERMINATION

D D

MEM_MA_ADD[0..15][5,8]

MEM_MA_CAS_L[5,8]

MEM_MA_RAS_L[5,8]

MEM_MA_WE_L[5,8]

MEM_MA_BANK0[5,8]

MEM_MA_BANK1[5,8]

MEM_MA_BANK2[5,8]

MEM_MA_CKE1[5,8]

MEM_MA_CKE0[5,8]

MEM_MA0_CS_L[0..3][5,8]

MEM_MA0_ODT0[5,8]

MEM_MA0_ODT1[5,8]

5

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_CAS_L

MEM_MA_RAS_L

MEM_MA_WE_L

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_CKE1

MEM_MA_CKE0

MEM_MA0_CS_L0

MEM_MA0_CS_L1

MEM_MA0_CS_L2

MEM_MA0_CS_L3

MEM_MA0_ODT0

MEM_MA0_ODT1

1 2

47OHM

3 4

47OHM

1 2

47OHM

5 6

47OHM

3 4

47OHM

3 4

47OHM

1 2

47OHM

7 8

47OHM

7 8

47OHM

1 2

47OHM

5 6

47OHM

5 6

47OHM

1 2

47OHM

5 6

47OHM

5 6

47OHM

3 4

47OHM

3 4

47OHM

1 2

47OHM

1 2

47OHM

3 4

47OHM

7 8

47OHM

7 8

47OHM

5 6

47OHM

7 8

47OHM

7 8

47OHM

5 6

47OHM

3 4

47OHM

7 8

47OHM

5 6

47OHM

3 4

47OHM

1 2

47OHM

7 8

47OHM

RN908A

RN908B

RN913A

RN913C

RN914B

RN913B

RN914A

RN914D

RN913D

RN906A

RN907C

RN914C

RN905A

RN911C

RN905C

RN905B

RN911B

RN907A

RN912A

RN907B

RN907D

RN905D

RN906C

RN906D

RN912D

RN912C

RN906B

RN911D

RN908C

RN912B

RN911A

RN908D

4

+0.9V +0.9V

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_ADD[0..15][5,8]

MEM_MB_CAS_L[5,8]

MEM_MB_RAS_L[5,8]

MEM_MB_WE_L[5,8]

MEM_MB_BANK0[5,8]

MEM_MB_BANK1[5,8]

MEM_MB_BANK2[5,8]

MEM_MB_CKE1[5,8]

MEM_MB_CKE0[5,8]

MEM_MB0_CS_L[0..3][5,8]

MEM_MB0_ODT0[5,8]

MEM_MB0_ODT1[5,8]

MEM_MB_CAS_L

MEM_MB_RAS_L

MEM_MB_WE_L

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_CKE1

MEM_MB_CKE0

MEM_MB0_CS_L0

MEM_MB0_CS_L1

MEM_MB0_CS_L2

MEM_MB0_CS_L3

MEM_MB0_ODT0

MEM_MB0_ODT1

3

3 4

47OHM

7 8

47OHM

5 6

47OHM

7 8

47OHM

1 2

47OHM

1 2

47OHM

3 4

47OHM

1 2

47OHM

3 4

47OHM

5 6

47OHM

3 4

47OHM

7 8

47OHM

5 6

47OHM

1 2

47OHM

5 6

47OHM

3 4

47OHM

7 8

47OHM

7 8

47OHM

5 6

47OHM

1 2

47OHM

5 6

47OHM

7 8

47OHM

7 8

47OHM

1 2

47OHM

3 4

47OHM

5 6

47OHM

3 4

47OHM

3 4

47OHM

1 2

47OHM

1 2

47OHM

7 8

47OHM

5 6

47OHM

RN916B

RN916D

RN901C

RN910D

RN901A

RN910A

RN901B

RN902A

RN910B

RN910C

RN903B

RN901D

RN909C

RN904A

RN902C

RN902B

RN903D

RN915D

RN903C

RN903A

RN915C

RN909D

RN902D

RN909A

RN915B

RN904C

RN909B

RN904B

RN916A

RN915A

RN904D

RN916C

+0.9V

0.1UF/10V

+0.9V

0.1UF/10V

C901

C908

2

12

12

C902

0.1UF/10V

C909

0.1UF/10V

12

12

C903

0.1UF/10V

C910

0.1UF/10V

12

12

C904

0.1UF/10V

C911

0.1UF/10V

12

12

place behind DIMMs

12

C905

0.1UF/10V

12

C912

0.1UF/10V

C906

0.1UF/10V

C913

0.1UF/10V

1

C907

0.1UF/10V

C914

0.1UF/10V

12

12

0.1UF/10V

C915

12

12

12

C C

LAYOUT :COULD BE SWAP

3/7

R918

300Ohm

5

+1.8V

1 2

34

Q908B

UM6K1N

_CPU_PROCHOT# [6]CPU_THERMTRIP# [15,16]

4.7KOhm

Q906B

UM6K1N

+3VS

R912

1 2

+1.8V +3VS

12

R914

300Ohm

1 2

_CPU_THERMTRIP#[6] CPU_PROCHOT#[15,19]

R905

10KOhm

61

Q906A

2

UM6K1N

34

5

R916

4.7KOhm

12

R906

10KOhm

1 2

61

Q908A

2

UM6K1N

B B

GND

2/8

GND

2/8

A

final_1.00

Title :

DDR2 TER/FETGAGE

ASUSTECH CO.,LTD.

Size Project Name

A3

5

4

3

2

Date: Sheet

A6T

Engineer:

Jefing_Li

Rev

1.0

of

973Thursday, March 09, 2006

1

Page 10

5

HT_CPU_RX_CAD_H[0..15][4]

D D

HT_CPU_RX_CAD_L[0..15][4]

C C

HT_CPU_RX_CLK_H0[4]

HT_CPU_RX_CLK_L0[4]

HT_CPU_RX_CLK_H1[4]

HT_CPU_RX_CLK_L1[4]

HT_CPU_RX_CTL_H0[4]

HT_CPU_RX_CTL_L0[4]

+1.2V_HT

B B

R1001

150Ohm

1 2

R1003 150Ohm

+1.2V_C51_PLL

12

L1001

21

30Ohm/100Mhz

C1001

1UF/16V

HT_CPU_RX_CAD_H0

HT_CPU_RX_CAD_H1

HT_CPU_RX_CAD_H2

HT_CPU_RX_CAD_H3

HT_CPU_RX_CAD_H4

HT_CPU_RX_CAD_H5

HT_CPU_RX_CAD_H6

HT_CPU_RX_CAD_H7

HT_CPU_RX_CAD_H8

HT_CPU_RX_CAD_H9

HT_CPU_RX_CAD_H10

HT_CPU_RX_CAD_H11

HT_CPU_RX_CAD_H12

HT_CPU_RX_CAD_H13

HT_CPU_RX_CAD_H14

HT_CPU_RX_CAD_H15

HT_CPU_RX_CAD_L0

HT_CPU_RX_CAD_L1

HT_CPU_RX_CAD_L2

HT_CPU_RX_CAD_L3

HT_CPU_RX_CAD_L4

HT_CPU_RX_CAD_L5

HT_CPU_RX_CAD_L6

HT_CPU_RX_CAD_L7

HT_CPU_RX_CAD_L8

HT_CPU_RX_CAD_L9

HT_CPU_RX_CAD_L10

HT_CPU_RX_CAD_L11

HT_CPU_RX_CAD_L12

HT_CPU_RX_CAD_L13

HT_CPU_RX_CAD_L14

HT_CPU_RX_CAD_L15

HT_CPU_RX_CLK_H0

HT_CPU_RX_CLK_L0

HT_CPU_RX_CLK_H1

HT_CPU_RX_CLK_L1

HT_CPU_RX_CTL_H0

HT_CPU_RX_CTL_L0

HT_CPU_CAL_1P2V

HT_CPU_CAL_GND

+1.2V_PLLHTCPU

12

C1004

0.1UF/10V

12

Y23

HT_CPU_RXD0_P

W24

HT_CPU_RXD1_P

V24

HT_CPU_RXD2_P

U22

HT_CPU_RXD3_P

R24

HT_CPU_RXD4_P

P24

HT_CPU_RXD5_P

P22

HT_CPU_RXD6_P

N22

HT_CPU_RXD7_P

Y21

HT_CPU_RXD8_P

V21

HT_CPU_RXD9_P

W21

HT_CPU_RXD10_P

T21

HT_CPU_RXD11_P

R18

HT_CPU_RXD12_P

P16

HT_CPU_RXD13_P

N20

HT_CPU_RXD14_P

M17

HT_CPU_RXD15_P

Y22

HT_CPU_RXD0_N

W23

HT_CPU_RXD1_N

V23

HT_CPU_RXD2_N

U21

HT_CPU_RXD3_N

R23

HT_CPU_RXD4_N

P23

HT_CPU_RXD5_N

P21

HT_CPU_RXD6_N

N21

HT_CPU_RXD7_N

Y20

HT_CPU_RXD8_N

W20

HT_CPU_RXD9_N

W22

HT_CPU_RXD10_N

U20

HT_CPU_RXD11_N

R19

HT_CPU_RXD12_N

P17

HT_CPU_RXD13_N

N19

HT_CPU_RXD14_N

N18

HT_CPU_RXD15_N

T23

HT_CPU_RX_CLK0_P

T22

HT_CPU_RX_CLK0_N

R21

HT_CPU_RX_CLK1_P

R20

HT_CPU_RX_CLK1_N

M23

HT_CPU_RXCTL_P

M22

HT_CPU_RXCTL_N

W19

HT_CPU_CAL_1P2V

Y19

HT_CPU_CAL_GND

N16

+1.2V_PLLHTCPU

T13

+1.2V_PLLHTMCP

U3A

C51MV

4

HT_CPU_TXD0_P

HT_CPU_TXD1_P

HT_CPU_TXD2_P

HT_CPU_TXD3_P

HT_CPU_TXD4_P

HT_CPU_TXD5_P

HT_CPU_TXD6_P

HT_CPU_TXD7_P

HT_CPU_TXD8_P

HT_CPU_TXD9_P

HT_CPU_TXD10_P

HT_CPU_TXD11_P

HT_CPU_TXD12_P

HT_CPU_TXD13_P

HT_CPU_TXD14_P

HT_CPU_TXD15_P

HT_CPU_TXD0_N

HT_CPU_TXD1_N

HT_CPU_TXD2_N

HT_CPU_TXD3_N

HT_CPU_TXD4_N

HT_CPU_TXD5_N

HT_CPU_TXD6_N

HT_CPU_TXD7_N

HT_CPU_TXD8_N

HT_CPU_TXD9_N

HT_CPU_TXD10_N

HT_CPU_TXD11_N

HT_CPU_TXD12_N

HT_CPU_TXD13_N

HT_CPU_TXD14_N

HT_CPU_TXD15_N

HT_CPU_TX_CLK0_P

HT_CPU_TX_CLK0_N

HT_CPU_TX_CLK1_P

HT_CPU_TX_CLK1_N

HT_CPU_TXCTL_P

HT_CPU_TXCTL_N

CLKOUT_PRI_200MHZ_P

CLKOUT_PRI_200MHZ_N

CLKOUT_SEC_200MHZ_P

CLKOUT_SEC_200MHZ_N

HT_CPU_REQ*

HT_CPU_STOP*

HT_CPU_RESET*

HT_CPU_PWRGD

+2.5V_PLLHTCPU

C23

D23

E22

F23

H22

J21

K21

K23

D21

F19

F21

G20

J19

L17

L20

L18

C24

D24

E23

F24

H23

J22

K22

K24

D22

E20

E21

G19

J18

K17

K19

L19

G23

G24

G22

G21

L23

L24

B24

B23

A22

B21

F18

G18

D20

E19

L16

C1002

4.7UF/6.3V

3

HT_CPU_TX_CAD_H0

HT_CPU_TX_CAD_H1

HT_CPU_TX_CAD_H2

HT_CPU_TX_CAD_H3

HT_CPU_TX_CAD_H4

HT_CPU_TX_CAD_H5

HT_CPU_TX_CAD_H6

HT_CPU_TX_CAD_H7

HT_CPU_TX_CAD_H8

HT_CPU_TX_CAD_H9

HT_CPU_TX_CAD_H10

HT_CPU_TX_CAD_H11

HT_CPU_TX_CAD_H12

HT_CPU_TX_CAD_H13

HT_CPU_TX_CAD_H14

HT_CPU_TX_CAD_H15

HT_CPU_TX_CAD_L0

HT_CPU_TX_CAD_L1

HT_CPU_TX_CAD_L2

HT_CPU_TX_CAD_L3

HT_CPU_TX_CAD_L4

HT_CPU_TX_CAD_L5

HT_CPU_TX_CAD_L6

HT_CPU_TX_CAD_L7

HT_CPU_TX_CAD_L8

HT_CPU_TX_CAD_L9

HT_CPU_TX_CAD_L10

HT_CPU_TX_CAD_L11

HT_CPU_TX_CAD_L12

HT_CPU_TX_CAD_L13

HT_CPU_TX_CAD_L14

HT_CPU_TX_CAD_L15

HT_CPU_TX_CLK_H0

HT_CPU_TX_CLK_L0

HT_CPU_TX_CLK_H1

HT_CPU_TX_CLK_L1

HT_CPU_TX_CTL_H0

HT_CPU_TX_CTL_L0

CPU_CLK_H

CPU_CLK_L

T1001 TPC26TN/A

1

T1002 TPC26TN/A

1

CPU_LDTSTOP#

CPU_RESET#

CPU_PWROK

+2.5V_PLLTHCPU

12

C1003

0.1UF/10V

HT_CPU_TX_CLK_H0 [4]

HT_CPU_TX_CLK_L0 [4]

HT_CPU_TX_CLK_H1 [4]

HT_CPU_TX_CLK_L1 [4]

HT_CPU_TX_CTL_H0 [4]

HT_CPU_TX_CTL_L0 [4]

CPU_CLK_H [6]

CPU_CLK_L [6]

CPU_LDTSTOP# [6]

CPU_RESET# [6]

CPU_PWROK [6]

L1002

30Ohm/100Mhz

12

HT_CPU_TX_CAD_H[0..15] [4]

HT_CPU_TX_CAD_L[0..15] [4]

+2.5VS

R1002

22KOHM

1 2

+2.5VS

21

2

1

Place on back side

A A

5

4

3

2

final_1.00

Title :

ASUSTECH CO.,LTD.

Size Project Name

B

Date: Sheet

A6T

Engineer:

1

C51_HT_CPU

Jefing_Li

of

10 73Thursday, March 09, 2006

Rev

1.0

Page 11

5

4

3

2

1

D D

HT_MCP_RX_H[0..7][16]

49.9Ohm

R1101

/X

1 2

HT_MCP_RX_H0

HT_MCP_RX_H1

HT_MCP_RX_H2

HT_MCP_RX_H3

HT_MCP_RX_H4

HT_MCP_RX_H5

HT_MCP_RX_H6

HT_MCP_RX_H7

FOR 4X4 LINK TO FLOAT UNUSED PIN

HT_MCP_RX_L[0..7][16]

C C

R1102

+1.2VS

49.9Ohm

/X

1 2

HT_MCP_RX_L0

HT_MCP_RX_L1

HT_MCP_RX_L2

HT_MCP_RX_L3

HT_MCP_RX_L4

HT_MCP_RX_L5

HT_MCP_RX_L6

HT_MCP_RX_L7

FOR 4X4 LINK TO FLOAT UNUSED PIN

HT_MCP_RX_CLK_H0[16]

HT_MCP_RX_CLK_L0[16]

T1101TPC26T N/A

T1103TPC26T N/A

B B

A A

5

HT_MCP_RX_CTL_H[16]

HT_MCP_REQ#[16]

HT_MCP_STOP#[16]

HT_MCP_RST#[16]

HT_MCP_PWRGD[16]

MCP_OUT_25M[16]

MCP_OUT_200M_H[16]

MCP_OUT_200M_L[16]

HT_MCP_RX_CLK_H0

HT_MCP_RX_CLK_L0

HT_MCP_C_CLK_H1

1

HT_MCP_C_CLK_L1

1

HT_MCP_RX_CTL_H

HT_MCP_RX_CTL_L

HT_MCP_REQ#

HT_MCP_STOP#

HT_MCP_RST#

HT_MCP_PWRGD

MCP_OUT_25M

MCP_OUT_200M_H

MCP_OUT_200M_L

4

U3B

AD6

HT_MCP_RXD0_P

AC7

HT_MCP_RXD1_P

AA8

HT_MCP_RXD2_P

AA9

HT_MCP_RXD3_P

AD10

HT_MCP_RXD4_P

AD11

HT_MCP_RXD5_P

AC12

HT_MCP_RXD6_P

AC13

HT_MCP_RXD7_P

AA6

HT_MCP_RXD8_P

W7

HT_MCP_RXD9_P

Y8

HT_MCP_RXD10_P

V9

HT_MCP_RXD11_P

Y10

HT_MCP_RXD12_P

AA11

HT_MCP_RXD13_P

V11

HT_MCP_RXD14_P

W12

HT_MCP_RXD15_P

AC6

HT_MCP_RXD0_N

AB7

HT_MCP_RXD1_N

AB8

HT_MCP_RXD2_N

AB9

HT_MCP_RXD3_N

AC10

HT_MCP_RXD4_N

AC11

HT_MCP_RXD5_N

AB12

HT_MCP_RXD6_N

AB13

HT_MCP_RXD7_N

Y6

HT_MCP_RXD8_N

Y7

HT_MCP_RXD9_N

AA7

HT_MCP_RXD10_N

W9

HT_MCP_RXD11_N

W10

HT_MCP_RXD12_N

Y12

HT_MCP_RXD13_N

W11

HT_MCP_RXD14_N

V13

HT_MCP_RXD15_N

AD9

HT_MCP_RX_CLK0_P

AC9

HT_MCP_RX_CLK0_N

U10

HT_MCP_RX_CLK1_P

T10

HT_MCP_RX_CLK1_N

AD14

HT_MCP_RXCTL_P

AC14

HT_MCP_RXCTL_N

AB5

HT_MCP_REQ*

AA5

HT_MCP_STOP*

AC5

HT_MCP_RESET*

AD5

HT_MCP_PWRGD

AC4

CLKIN_25MHZ

Y5

CLKIN_200MHZ_P

W5

CLKIN_200MHZ_N

C51MV

HT_MCP_TXD0_P

HT_MCP_TXD1_P

HT_MCP_TXD2_P

HT_MCP_TXD3_P

HT_MCP_TXD4_P

HT_MCP_TXD5_P

HT_MCP_TXD6_P

HT_MCP_TXD7_P

HT_MCP_TXD8_P

HT_MCP_TXD9_P

HT_MCP_TXD10_P

HT_MCP_TXD11_P

HT_MCP_TXD12_P

HT_MCP_TXD13_P

HT_MCP_TXD14_P

HT_MCP_TXD15_P

HT_MCP_TXD0_N

HT_MCP_TXD1_N

HT_MCP_TXD2_N

HT_MCP_TXD3_N

HT_MCP_TXD4_N

HT_MCP_TXD5_N

HT_MCP_TXD6_N

HT_MCP_TXD7_N

HT_MCP_TXD8_N

HT_MCP_TXD9_N

HT_MCP_TXD10_N

HT_MCP_TXD11_N

HT_MCP_TXD12_N

HT_MCP_TXD13_N

HT_MCP_TXD14_N

HT_MCP_TXD15_N

HT_MCP_TX_CLK0_P

HT_MCP_TX_CLK0_N

HT_MCP_TX_CLK1_P

HT_MCP_TX_CLK1_N

HT_MCP_TXCTL_P

HT_MCP_TXCTL_N

CLKOUT_CTERM_GND

SCLKIN_MCLKOUT_200MHZ_P

SCLKIN_MCLKOUT_200MHZ_N

HT_MCP_CAL_1P2V

HT_MCP_CAL_GND

3

HT_MCP_TX_H0

AC24

HT_MCP_TX_H1

AD23

HT_MCP_TX_H2

AC22

HT_MCP_TX_H3

AC20

HT_MCP_TX_H4

AB18

HT_MCP_TX_H5

AA17

HT_MCP_TX_H6

AB16

HT_MCP_TX_H7

AC16

AB21

AB20

AB19

W18

W15

AA15

Y14

W13

HT_MCP_TX_L0

AC23

HT_MCP_TX_L1

AD22

HT_MCP_TX_L2

AC21

HT_MCP_TX_L3

AD20

HT_MCP_TX_L4

AC18

HT_MCP_TX_L5

AB17

HT_MCP_TX_L6

AB15

HT_MCP_TX_L7

AD16

AB22

AA20

AA19

V17

V15

Y15

W14

Y13

HT_MCP_TX_CLK_H0

AC19

HT_MCP_TX_CLK_L0

AD19

HT_C_MCP_CLK_H1

Y17

HT_C_MCP_CLK_L1

W17

HT_MCP_TX_CTL_H

AC15

HT_MCP_TX_CTL_L

AD15

B22

T1105 TPC26TN/A

A20

T1106 TPC26TN/A

B20

AB23

AB24

R1103

1 2

1

1

HT_MCP_CAL_1P2V

HT_MCP_CAL_GND

2.37KOhm

HT_MCP_TX_H[0..7] [16]

HT_MCP_TX_L[0..7] [16]

T1102N/A

1

T1104N/A

1

1%

150Ohm

1%

150Ohm

1%

HT_MCP_TX_CLK_H0 [16]

HT_MCP_TX_CLK_L0 [16]

HT_MCP_TX_CTL_H [16]

HT_MCP_TX_CTL_L [16]HT_MCP_RX_CTL_L[16]

+1.2VS

R1104

1 2

R1105

1 2

2

final_1.00

Title :

ASUSTECH CO.,LTD.

Size Project Name

B

Date: Sheet

A6T

Engineer:

1

C51_HT_MCP

Jefing_Li

of

11 73Thursday, March 09, 2006

Rev

1.0

Page 12

5

4

3

2

1

D D

C C

PE0_PRSENT#

12

R1201

10KOhm

B B

+3VS

A A

5

PE1_X1_RX_P[46]

PE1_X1_RX_N[46]

R1202

10KOhm

R1203

10KOhm

+1.2V_C51_PLL

L1201

30Ohm/100Mhz

1UF/16V

Place on back side

PE1_X1_RX_P

PE1_X1_RX_N

PE1_PRSENT#

12

PE2_PRSENT#

12

C1234

1

1

1

1

12

T1201TPC26T N/A

T1202TPC26T N/A

T1203TPC26T N/A

T1204TPC26T N/A

21

12

C1233

0.1UF/10V

U3C

J8

PE0_RX0_P

J6

PE0_RX1_P

K9

PE0_RX2_P

L6

PE0_RX3_P

L7

PE0_RX4_P

M9

PE0_RX5_P

N8

PE0_RX6_P

N6

PE0_RX7_P

R6

PE0_RX8_P

P3

PE0_RX9_P

R8

PE0_RX10_P

U6

PE0_RX11_P

T8

PE0_RX12_P

U7

PE0_RX13_P

V4

PE0_RX14_P

Y3

PE0_RX15_P

J7

PE0_RX0_N

J5

PE0_RX1_N

J9

PE0_RX2_N

L5

PE0_RX3_N

L8

PE0_RX4_N

M8

PE0_RX5_N

N7

PE0_RX6_N

N5

PE0_RX7_N

R5

PE0_RX8_N

P4

PE0_RX9_N

R7

PE0_RX10_N

U5

PE0_RX11_N

T9

PE0_RX12_N

U8

PE0_RX13_N

V3

PE0_RX14_N

AA3

PE0_RX15_N

D1

PE0_PRSNT*

G6

PE1_RX_P

H6

PE1_RX_N

E2

PE1_PRSNT*

J4

PE2_RX_P

K3

PE2_RX_N

E3

PE2_PRSNT*

D3

PE1_CLKREQ*/CLK

E4

PE2_CLKREQ*/DATA

AC3

PE_REFCLKIN_P

AB3

PE_REFCLKIN_N

T11

+1.2V_PLLPE

C51MV

4

PE0_TX0_P

PE0_TX1_P

PE0_TX2_P

PE0_TX3_P

PE0_TX4_P

PE0_TX5_P

PE0_TX6_P

PE0_TX7_P

PE0_TX8_P

PE0_TX9_P

PE0_TX10_P

PE0_TX11_P

PE0_TX12_P

PE0_TX13_P

PE0_TX14_P

PE0_TX15_P

PE0_TX0_N

PE0_TX1_N

PE0_TX2_N

PE0_TX3_N

PE0_TX4_N

PE0_TX5_N

PE0_TX6_N

PE0_TX7_N

PE0_TX8_N

PE0_TX9_N

PE0_TX10_N

PE0_TX11_N

PE0_TX12_N

PE0_TX13_N

PE0_TX14_N

PE0_TX15_N

PE0_REFCLK_P

PE0_REFCLK_N

PE1_TX_P

PE1_TX_N

PE1_REFCLK_P

PE1_REFCLK_N

PE2_TX_P

PE2_TX_N

PE2_REFCLK_P

PE2_REFCLK_N

PE_TSTCLK_P

PE_TSTCLK_N

PE_RESET*

PE_CTERM_GND

L1

L3

L4

M4

P1

R1

R3

R4

U4

V1

W1

W3

AA1

AB1

AC1

AD2

L2

M2

M3

N3

P2

R2

T2

T3

U3

V2

W2

Y2

AA2

AB2

AC2

AD3

K1

K2

RPE1_X1_TX_P

G4

RPE1_X1_TX_N

G5

G2

G3

H4

J3

H2

H3

F1

F2

G1

PE_CTERM_GND+1.2V_PLLPE

D2

PE1_X1_CLK_P

PE1_X1_CLK_N

PE_RESET#

3

1 2

C1235 0.1UF/10V

PE1_X1_CLK_P [46]

PE1_X1_CLK_N [46]

R1204

100Ohm

/X

PE_RESET# [46]

R1205 2.37KOhm

1 2

1 2

C1236 0.1UF/10V

1 2

PE1_X1_TX_P

PE1_X1_TX_N

2

PE1_X1_TX_P [46]

PE1_X1_TX_N [46]

final_1.00

ASUSTECH CO.,LTD.

Size Project Name

B

Date: Sheet

A6M

Title :

Engineer:

1

C51_PCIE

Jefing_Li

12 73Thursday, March 09, 2006

Rev

1.0

of

Page 13

5

4

3

2

+5VS

1

D D

CRT_HSYNC[40]

CRT_VSYNC[40]

R1350

1 2

1KOhm

3/1

R1323

1 2

+3VS

47Ohm/100Mhz

/C61MP

C C

C61M_XTAL_OUT C61M_XTAL_IN

C1313

18PF/50V

1 2

/C61M

B B

+2.5VS

X1301

12

27Mhz

/C61M

30Ohm/100Mhz

/C61MP

R1324

1 2

C1314

18PF/50V

/C61M

+1.2V_C51_PLL

L1301

L1302

0.1UF/10V