ASIX AX88860 Datasheet

ASIX ELECTRONICS CORPORATION

2F, NO.13, Industry East Rd. II, Science-based Industrial Park, Hsin-Chu City, Taiwan, R.O.C.

TEL: 886-3-579-9500 FAX: 886-3-579-9558

AX8886

0

100BASE-TX/FX Repeater Controlle

r

A

S

I

X

ASIX AX88860

10/100BASE-TX/FX

Repeater Controller

Data Sheet(11/03/’97)

DOCUMENT NO. : AX860D2.DOC

This data sheets contain new products information. ASIX ELECTRONICS reserves the rights to modify the products

specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent

accompany the sale of the product.

AX88860 PRELIMINARY

ASIX ELECTRONICS CORPORATION

2

CONTENTS

1.0 AX88860 OVERVIEW..............................................................................................................................................4

1.1 GENERAL DESCRIPTION ............................................................................................................................................4

1.2 FEATURES.................................................................................................................................................................5

1.3 BLOCK DIAGRAM......................................................................................................................................................6

1.4 PIN CONNECTION DIAGRAM (MODE 0)......................................................................................................................7

1.5 PIN CONNECTION DIAGRAM (MODE 1)......................................................................................................................8

2.0 PIN DESCRIPTION..................................................................................................................................................9

2.1 SHARED MII INTERFACE...........................................................................................................................................9

2.2 DEDICATED MII INTERFACE...................................................................................................................................10

2.3 EXPANSION BUS INTERFACE ...................................................................................................................................11

2.4 LED DISPLAY.........................................................................................................................................................12

2.5 MISCELLANEOUS.....................................................................................................................................................13

3.0 FUNCTIONAL DESCRIPTION...........................................................................................................................14

3.1 REPEATER STATE MACHINE....................................................................................................................................15

3.2 RXE /TXE CONTROL.........................................................................................................................................15

3.3 JABBER STATE MACHINE ........................................................................................................................................16

3.4 PARTITION STATE MACHINE ...................................................................................................................................16

3.5 EXPANSION LOGIC(CASCADE INTERFACE)..............................................................................................................16

3.6 DATA FLOW CONTROL ............................................................................................................................................17

3.7 RID RECEIVE-TRANSMIT INTERFACE(DAISY CHAIN LOGIC) ..................................................................................17

3.8 LED DISPLAY INTERFACE ......................................................................................................................................17

4.0 INTERNAL REGISTERS.......................................................................................................................................19

4.1 CONFIGURATION REGISTER (CONFIG) ..................................................................................................................19

4.2 REPEATER ID REGISTER(RPTR_ID).......................................................................................................................19

5.0 ELECTRICAL SPECIFICATION AND TIMING...............................................................................................20

5.1 ABSOLUTE MAXIMUM RATINGS..............................................................................................................................20

5.2 GENERAL OPERATION CONDITIONS ........................................................................................................................20

5.3 DC CHARACTERISTICS............................................................................................................................................20

5.4 AC SPECIFICATIONS................................................................................................................................................21

5.4.1 MII Interface Timing Tx & Rx........................................................................................................................21

5.4.2 Expansion Bus.................................................................................................................................................22

5.4.3 LED DISPLAY.................................................................................................................................................23

5.4.4 LED Display After Reset................................................................................................................................23

5.4.5 Repeater ID Daisy Chain................................................................................................................................24

6.0 PACKAGE INFORMATION.................................................................................................................................25

AX88860 PRELIMINARY

ASIX ELECTRONICS CORPORATION

3

FIGURES

FIG - 1 CHIP BLOCK DIAGRAM ...........................................................................................................................................6

FIG - 2 PIN CONNECTION DIAGRAM FOR MODE 0...............................................................................................................7

FIG - 3 PIN CONNECTION DIAGRAM FOR MODE 1................................................................................................................8

FIG - 4 FUNCTIONAL BLOCK DIAGRAM ............................................................................................................................14

FIG - 5 APPLICATION FOR LED DISPLAY ..........................................................................................................................18

AX88860 PRELIMINARY

ASIX ELECTRONICS CORPORATION

4

1.0 AX88860 Overview

The AX88860 10/100Mbps Repeater Controller is design for low cost dumb HUB

application. The AX88860 directly supports up-to night 10/100Mbps links with its shared 8

ports MII interfaces and 1 dedicated MII interface. Maximum up-to 72 ports can be constructed

when using expansion bus cascades 8 AX88860s. The AX88860 is designed base on IEEE

802.3u clause 27 “ Repeater for 100Mb/s base-band networks” . It is fully compatible with

IEEE 802.3u standard=.

1.1 General Description

The AX88860 Repeater Controller is a subset of a repeater set containing all the

repeater-specific components and functions, exclusive of PHY components and functions. The

AX88860 has only Media Independent Interface (MII) to connect to PHY devices. Other then

AX88850 serial chips that has 2 kinds of interfaces. There are Physical coding sub-layer (PCS)

interface and Media Independent Interface (MII).

The AX88860 supports one shared bus (8 ports) MII interfaces, 1 dedicated MII ports

interface, a port expansion interface and LED display interface.

The AX88860 dedicated MII ports can connect to PHY or optional directly connect to 2

ports bridge, switch or MAC that has standard MII interface.

The AX88860 has two application modes.

Mode 0 Single chip repeater application.

Mode 1 Multiple chips cascaded repeater application.

= Note : To simplify the design of 10BASE Ethernet repeater. The portion of 10Mb/p repeater

will follow the specification as below :

(1) The PHY interface defines as standard MII interface with 2.5MHz transmit and

receive clock and 4 bits data format.

(2) The repeater core state machine follow IEEE 802.3u clause 27 “Repeater for 100

Mb/s baseband networks” with ten times of time scale. It is important that it is no

longer follows the legacy 10BASE repeater state machine.

AX88860 PRELIMINARY

ASIX ELECTRONICS CORPORATION

5

1.2 Features

• IEEE 802.3u repeater compatible

• Supports 10/100 Mbps alternative

• Supports 8+1 network connections

• 8 ports share MII interfaces direct interface to PHY chip with MII interface

• 1 dedicated MII interfaces can also support 100BASE-T4/FX PHY interfaces

• The 1dedicated MII interfaces can also easily connect to bridging device with MII interface

• Up-to 8 repeater chips can be cascaded for large HUB application

• Low latency design supports Class II repeater implementation with large port number

• All ports can be separately isolated or partitioned in response to fault condition

• Separate jabber and partition state machines for each port

• Encoded or direct LED drivers

• Per-port LED display for Jabber, Partition, Activity. Global collision, utilization and

collision (%) presentation

• Power on LED diagnosis. All the LED display will follow the “ON-OFF-ON-OFF-

Normal” operation procedure during/after power on reset ( mode 1 only ).

• 100-pin PQFP

AX88860 PRELIMINARY

ASIX ELECTRONICS CORPORATION

6

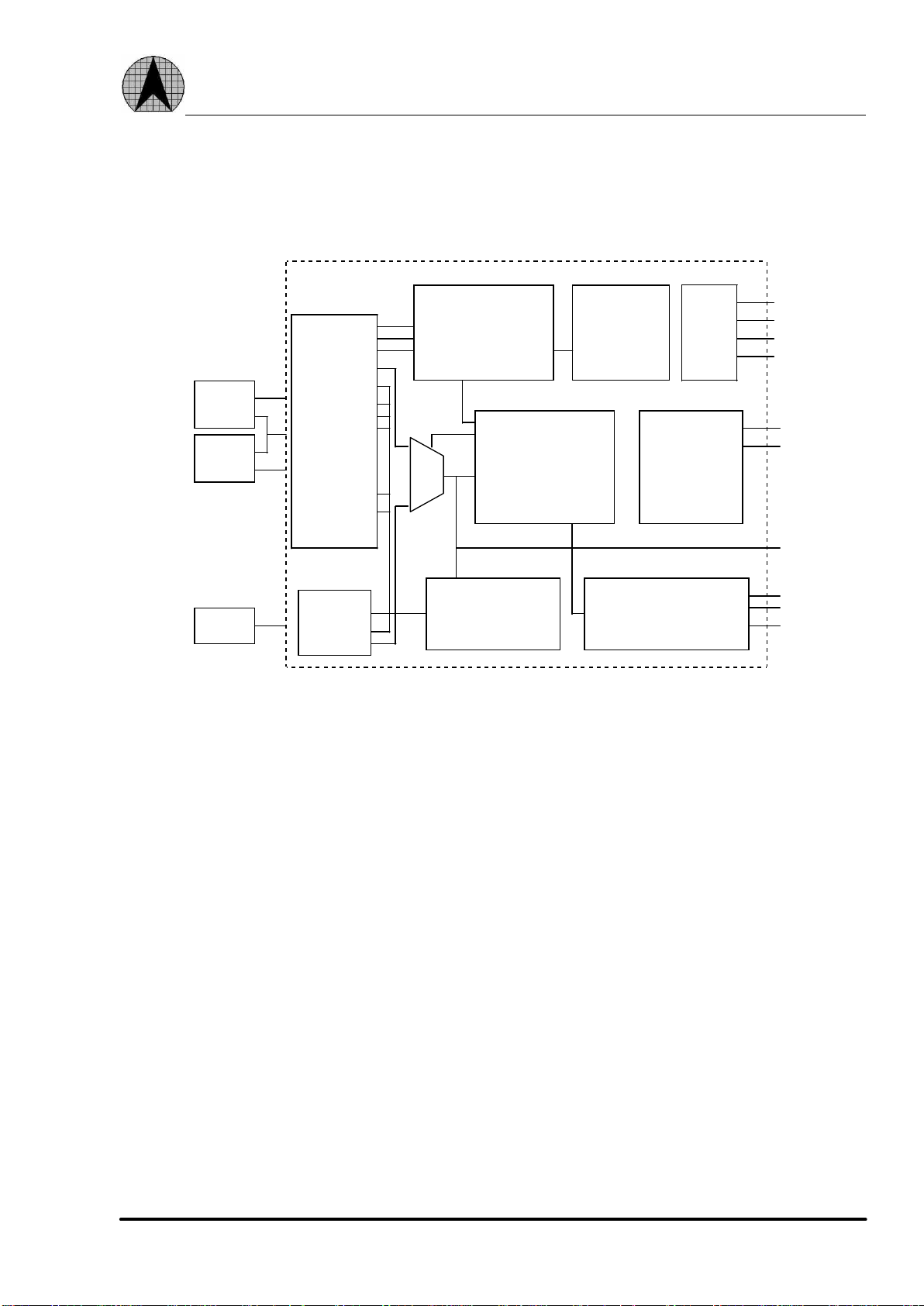

1.3 Block Diagram

Q-PHY

PHY

MII

I/F

MII

interface

Reconciliation layer

Port 0 Port 7

MII

Port 8

Elasticity Buffer

MUX

Repeater State

Machine

Collision Handling Logic

Per port Jabber ctl,

auto-partition SM &

Per port Collision ,

Partition counters.

Setup

Registers

Cascade

Arbitration

Logic

........

Q-PHY

MII

I/F

led

display

Fig - 1 Chip Block Diagram

AX88860 PRELIMINARY

ASIX ELECTRONICS CORPORATION

7

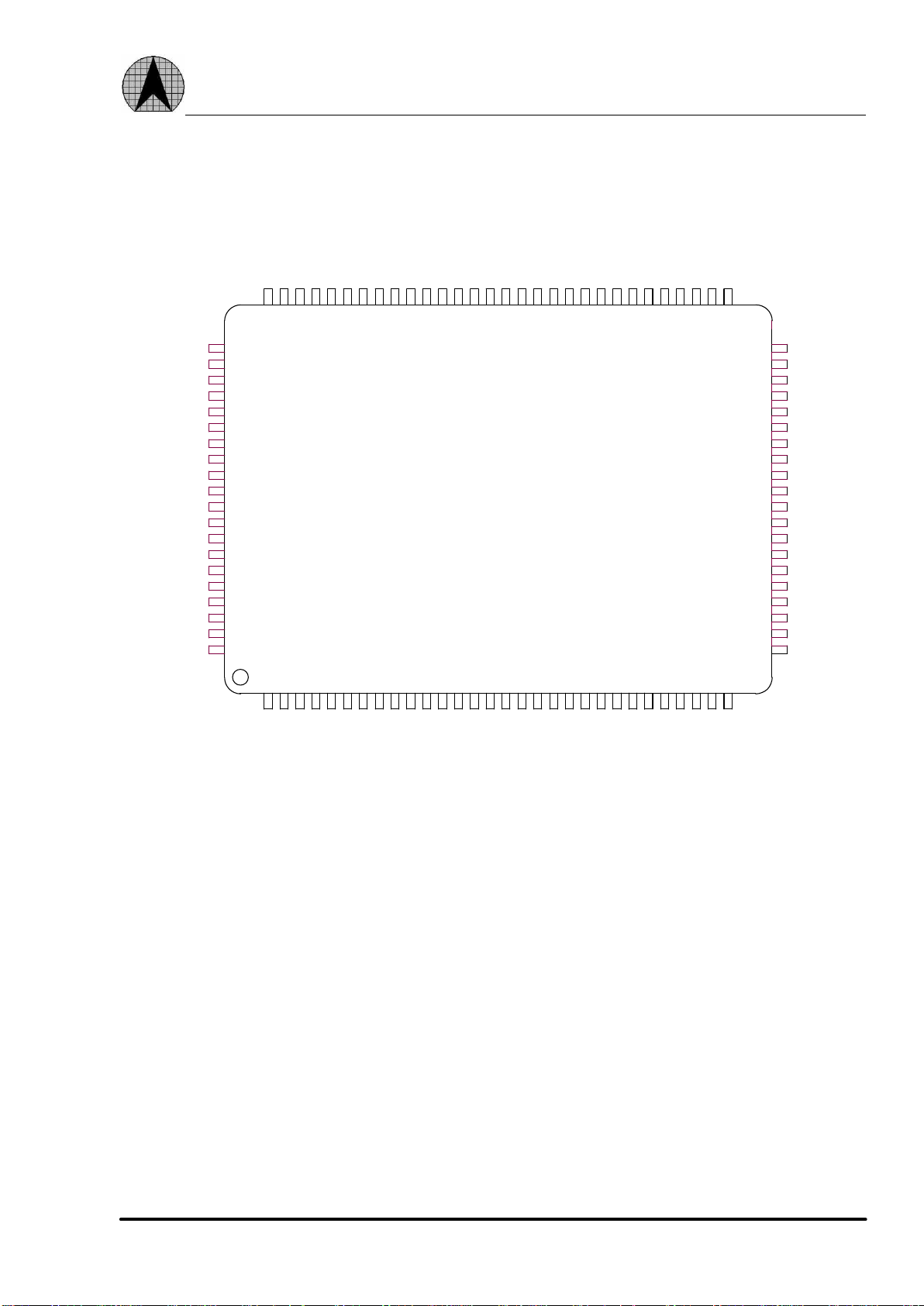

1.4 Pin Connection Diagram (mode 0)

1

564

7

2

3

8

9

101112131415161718

19

23

24

22

20

21

48

49

50

51

52

ASIX

AX88860

( Mode 0)

25

29

30

28

31

26

27

32

33

34

35

36

37

38

39

40

41

42

43

47

46

44

45

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

100

99

97

98

96

95

94

93

92

91

90

86

85

84

83

82

81

53

VDD

NC

DCRS

VSS

DRXD2

DRXD1

DRX_CLK

VSS

VDD

DRX_ER

DRXD0

DTX_EN

DRX_DV

VDD

DRXD3

/LACT<0>

/LUTI<3>

TEST

/LUTI<4>

/LCOL

/RST

VSS

LCLK

/LUTI<5>

VDD

VSS

NC

COL

VSS

VSS

VSS

VDD

VSS

RXD0

RXD1

RXD2

RXD3

RXER

RX_CLK

RX_DV

TXD0

TXD1

TXD2

TXD3

TXER

CRS0

CRS1

CRS2

CRS3

TXEN0

TXEN1

TXEN2

TXEN3

RXEN0

CRS4

CRS5

CRS6

CRS7

RXEN1

RXEN2

RXEN3

TXEN4

TXEN5

TXEN6

TXEN7

RXEN4

RXEN5

RXEN6

RXEN7

VSS

NC

VDD

88

89

87

VSS

VSS

VSS

VSS

MODE

VDD

/BRIDGE

B100

/LUTI<0>

/LUTI<1>

/LUTI<2>

/LPART<0>

/LPART<1>

/LPART<2>

/LPART<D>

/LPART<3>

/LPART<4>

/LPART<5>

/LPART<6>

/LPART<7>

/LACT<1>

/LACT<2>

/LACT<3>

/LACT<4>

/LACT<5>

/LACT<6>

/LACT<7>

/LACT<D>

Fig - 2 Pin Connection Diagram for mode 0

AX88860 PRELIMINARY

ASIX ELECTRONICS CORPORATION

8

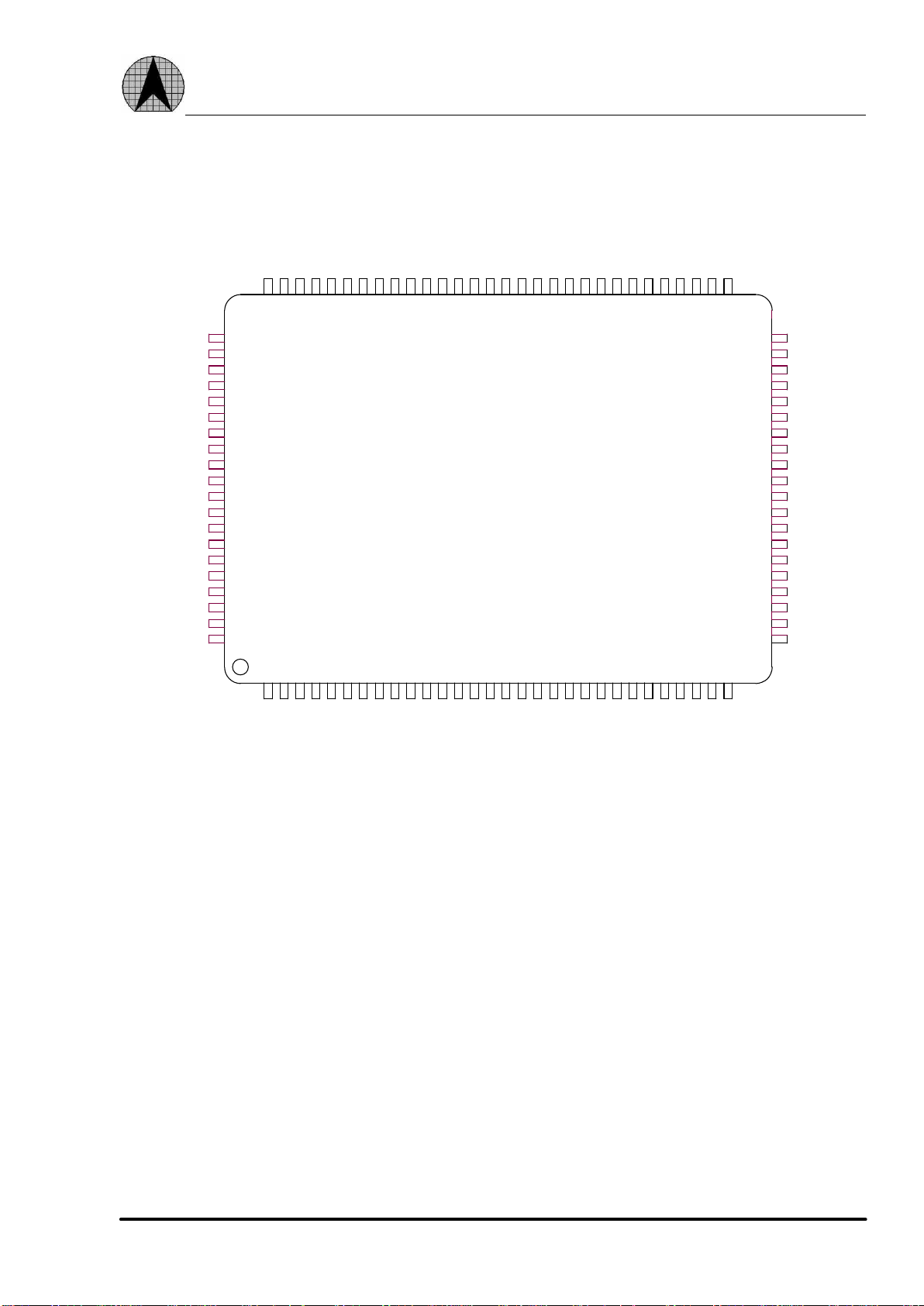

1.5 Pin Connection Diagram (mode 1)

1

564

7

2

3

8

9

101112131415161718

19

23

24

22

20

21

48

49

50

51

52

ASIX

AX88860

( Mode 1)

25

29

30

28

31

26

27

32

33

34

35

36

37

38

39

40

41

42

43

47

46

44

45

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

100

99

97

98

96

95

94

93

92

91

90

86

85

84

83

82

81

53

VDD

COL

DCRS

VSS

DRXD2

DRXD1

DRX_CLK

VSS

VDD

DRX_ER

DRXD0

DTX_EN

DRX_DV

VDD

DRXD3

IRD_ODIR

IRD<2>

IRD<0>

/IR_ACTI<4>

IRD<1>

LED_CK

TEST

RID<0>

/IRD_V

RID<2>

/RST

VSS

LCLK

IRD<3>

RID<1>

VDD

VSS

/IR_ACTO<7>

RST_DLY

DAISY_OUT

DAISY_IN

NC

VSS

VSS

VSS

VDD

VSS

RXD0

RXD1

RXD2

RXD3

RXER

RX_CLK

RX_DV

TXD0

TXD1

TXD2

TXD3

TXER

CRS0

CRS1

CRS2

CRS3

TXEN0

TXEN1

TXEN2

TXEN3

RXEN0

CRS4

CRS5

CRS6

CRS7

RXEN1

RXEN2

RXEN3

TXEN4

TXEN5

TXEN6

TXEN7

RXEN4

RXEN5

RXEN6

RXEN7

/IR_ACTI<3>

/IR_ACTI<2>

/IR_ACTI<1>

/IR_ACTI<0>

/IR_ACTI<5>

/IR_ACTI<6>

/IR_ACTI<7>

/IR_ACTO<6>

/IR_ACTO<5>

/IR_ACTO<4>

/IR_ACTO<3>

/IR_ACTO<2>

/IR_ACTO<1>

/IR_ACTO<0>

VSS

/DIS_DAISY

/DIS_DMII

VDD

88

89

87

/IRD_ER

IRD_CK

VSS

VSS

VSS

VSS

MODE

VDD

/BRIDGE

B100

LED<0>

LED<2>

LED<1>

Fig - 3 Pin Connection Diagram for mode 1

Loading...

Loading...